# Intel<sup>®</sup> 31154 133 MHz PCI Bridge Design Guide

**Design Guide**

**April 2004**

Order Number: 278944-001

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO SALE AND/OR USE OF INTEL PRODUCTS, INCLUDING LIABILITY OR WARRANTIES RELATING TO FINESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT, OR OTHER INTELLECTUAL PROPERTY RIGHT.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel<sup>®</sup> 31154 133 MHz PCI Bridge may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

This Design Guide as well as the software described in it is furnished under license and may only be used or copied in accordance with the terms of the license. The information in this manual is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by Intel Corporation. Intel Corporation assumes no responsibility or liability for any errors or inaccuracies that may appear in this document or any software that may be provided in association with this document.

Except as permitted by such license, no part of this document may be reproduced, stored in a retrieval system, or transmitted in any form or by any means without the express written consent of Intel Corporation.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

AnyPoint, AppChoice, BoardWatch, BunnyPeople, CablePort, Celeron, Chips, CT Media, Dialogic, DM3, EtherExpress, ETOX, FlashFile, i386, i486, i960, iCOMP, InstantIP, Intel, Intel Centrino, Intel Iogo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Create & Share, Intel GigaBlade, Intel InBusiness, Intel Inside, Intel Inside Iogo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel Play, Intel Play Iogo, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel TeamStation, Intel Xeon, Intel XScale, IPLink, Itanium, MCS, MMX, MMX Iogo, Optimizer Iogo, OverDrive, Paragon, PC Dads, PC Parents, PDCharm, Pentium II Xeon, Pentium III Xeon, Performance at Your Command, RemoteExpress, SmartDie, Solutions960, Sound Mark, StorageExpress, The Computer Inside, The Journey Inside, TokenExpress, VoiceBrick, VTune, and Xircom are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

$\ensuremath{^{\star}}\xspace \mbox{Other}$  names and brands may be claimed as the property of others.

Copyright © 2004, Intel Corporation

| 1 | Abou                     | t This Do          | ocument                                                                                                  | 7        |

|---|--------------------------|--------------------|----------------------------------------------------------------------------------------------------------|----------|

|   | 1.1                      | Termin             | nology and Definitions                                                                                   | 7        |

| 2 | Introd                   | duction            |                                                                                                          | 9        |

|   | 2.1<br>2.2<br>2.3<br>2.4 | Featur<br>Relate   | es List                                                                                                  | 10<br>11 |

| 3 | Pack                     | age Info           | rmation                                                                                                  | 13       |

|   | 3.1                      | Total S            | Signal Count                                                                                             | 17       |

| 4 | Term                     | inations           |                                                                                                          | 19       |

| 5 |                          |                    | erface                                                                                                   |          |

| J | 5.1                      |                    | CI-X Voltage Levels                                                                                      |          |

|   | 5.2                      |                    | pt Routing                                                                                               |          |

|   | 5.3                      |                    | Lines                                                                                                    |          |

|   |                          | 5.3.1              | Primary IDSEL Line                                                                                       |          |

|   |                          | 5.3.2              | Secondary IDSEL Lines                                                                                    |          |

|   |                          | 5.3.3              | Secondary IDSEL Masking                                                                                  | 31       |

|   |                          | 5.3.4              | Secondary Clock Control                                                                                  | 31       |

|   | 5.4                      |                    | actPCI* Hot Swap Mode Select                                                                             |          |

|   | 5.5                      |                    | e Memory Region Enable                                                                                   |          |

|   | 5.6                      |                    | Initialization Clocking Modes                                                                            |          |

|   |                          | 5.6.1              | Primary PCI Clocking Mode                                                                                |          |

|   |                          | 5.6.2              | Secondary PCI Clocking Mode                                                                              |          |

|   |                          | 5.6.3              | Primary-to-Secondary Frequency Limits                                                                    |          |

| 6 |                          | Routing Guidelines |                                                                                                          |          |

|   | 6.1                      |                    | alk                                                                                                      |          |

|   | 6.2                      |                    | onsiderations                                                                                            |          |

|   | 6.3                      |                    | Distribution and Decoupling                                                                              |          |

|   |                          | 6.3.1              | Decoupling Recommendations                                                                               |          |

|   | 6.4                      |                    | Impedance                                                                                                |          |

| 7 |                          | •                  | Guidelines                                                                                               |          |

|   |                          |                    | ock Layout Guidelines                                                                                    |          |

|   | 7.2                      |                    | Topology Layout Guidelines                                                                               |          |

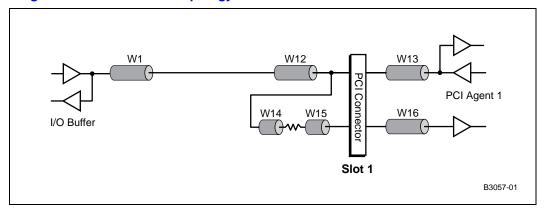

|   |                          | 7.2.1              | Single Slot at 133 MHz                                                                                   | 45       |

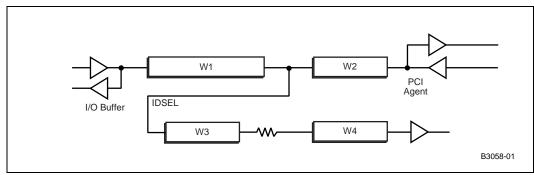

|   |                          | <del>-</del>       | 7.2.1.1 Intel® 31154 133 MHz PCI Bridge Embedded Application at 133 MHz                                  |          |

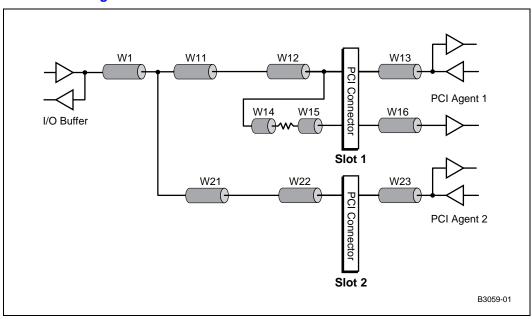

|   |                          | 7.2.2              | Dual-Slot at 100 MHz                                                                                     |          |

|   |                          | 700                | 7.2.2.1 Embedded Intel <sup>®</sup> 31154 133 MHz PCI Bridge Application at 100 MHz Quad-Slots at 66 MHz |          |

|   |                          | 7.2.3              | 7.2.3.1 Embedded Intel <sup>®</sup> 31154 133 MHz PCI Bridge Application at 66 MHz.                      |          |

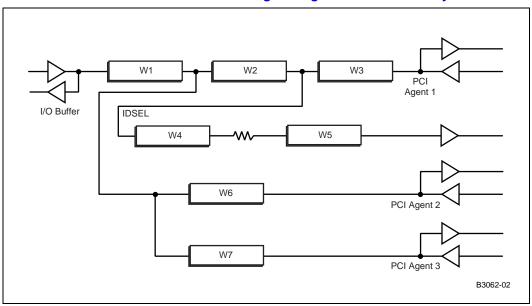

|   |                          | 7.2.4              | PCI-X at 33 MHz                                                                                          |          |

|   |                          | 1.4.7              | 7.2.4.1 Embedded PCI-X Specification PICMG 1.2 Overview                                                  | 52       |

#### Contents

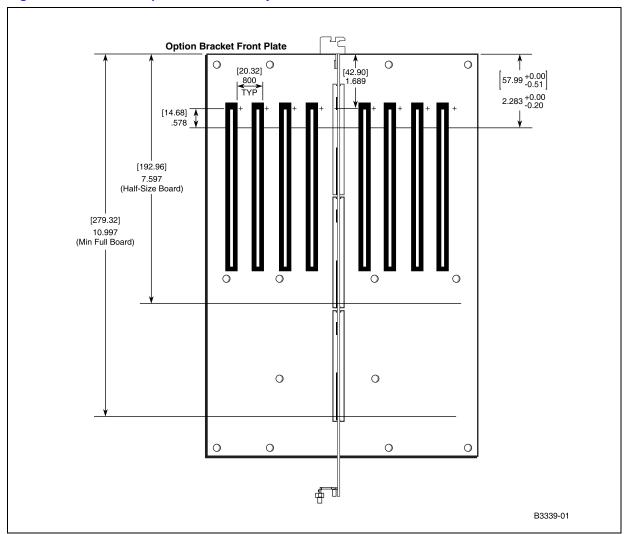

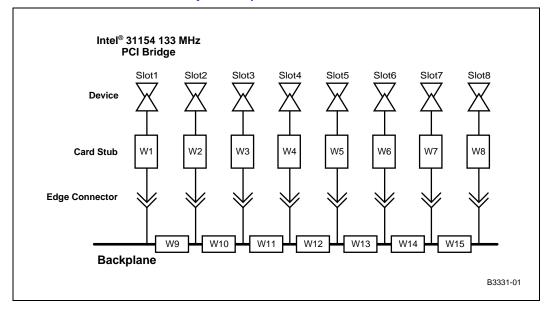

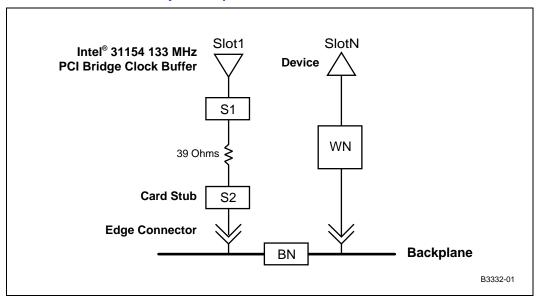

|          | 7.2.4.2 PICMG 1.2 System Overview                                                                   | 52 |

|----------|-----------------------------------------------------------------------------------------------------|----|

| 8        | Power Considerations                                                                                | 57 |

|          | 8.1 Analog Power Pins                                                                               | 57 |

|          | 8.2 Power Sequencing                                                                                |    |

| 9        | Customer Reference Board                                                                            | 59 |

| 10       | Debug Connectors and Logic Analyzer Connectivity                                                    | 61 |

|          | 10.1 Probing PCI-X Signals                                                                          | 61 |

| 11       | Thermal Solutions                                                                                   | 69 |

| 12       | References                                                                                          | 71 |

|          | 12.1 Related Documents                                                                              |    |

|          | 72.1 Rolated Bournelle                                                                              |    |

| _        | ures                                                                                                | _  |

| 1        | Intel® 31154 133 MHz PCI Bridge Applications                                                        |    |

| 2        | Intel® 31154 133 MHz PCI Bridge PackageIntel® 31154 133 MHz PCI Bridge Ball Map—Top View, Left Side |    |

| 4        | Intel® 31154 133 MHz PCI Bridge Ball Map—Top View, Left Side                                        |    |

| 5        | IDSEL Mapping                                                                                       |    |

| 6        | Crosstalk Effects on Trace Distance and Height                                                      |    |

| 7        | PCB Ground Layout Around Connectors                                                                 |    |

| 8        | PCI Clock Distribution and Matching Requirements                                                    |    |

| 9        | Single-Slot Point-to-Point Topology                                                                 |    |

| 10       |                                                                                                     |    |

| 11       |                                                                                                     |    |

| 12       | = = ::::::::::::::::::::::::::::::::::                                                              |    |

| 13       |                                                                                                     |    |

| 14       |                                                                                                     |    |

| 15       |                                                                                                     |    |

| 16       | , , , ,                                                                                             |    |

| 17       |                                                                                                     |    |

| 18       |                                                                                                     |    |

| 19       | <del>-</del>                                                                                        |    |

| 20<br>21 |                                                                                                     |    |

|          | oles                                                                                                |    |

|          |                                                                                                     | 7  |

| 1<br>2   | Terminology and DefinitionPCI-to-PCI Bridge Configurations                                          |    |

| 3        | Features ListFeatures List                                                                          |    |

| 4        | Total Signal Count                                                                                  |    |

| 5        | Pull-Up/Pull-Down Terminations                                                                      |    |

| 6        | PCI/PCI-X Voltage Levels                                                                            |    |

| 7        | HS_FREQ Encoding                                                                                    |    |

| 8        | PCI-X Clocking Modes                                                                                |    |

#### Contents

| 9  | Secondary Bus Frequency Initialization                     | 33 |

|----|------------------------------------------------------------|----|

| 10 | PCI-X Initialization Pattern                               | 34 |

| 11 | Intel® 31154 133 MHz PCI Bridge Decoupling Recommendations | 38 |

| 12 | Add-in Card Routing Parameters                             | 41 |

| 13 | PCI-X Slot Guidelines                                      | 44 |

| 14 | Wiring Lengths for 133 MHz Slot                            | 45 |

| 15 | Wiring Lengths for Embedded 133 MHz Design                 | 46 |

| 16 | Wiring Lengths for 100 MHz Dual-Slot                       | 47 |

| 17 | Wiring Lengths for Embedded 100 MHz Design                 | 48 |

| 18 | Wiring Lengths for 66 MHz Quad-Slot                        | 49 |

| 19 | Wiring Lengths for Embedded 66 MHz Design                  | 51 |

| 20 | Wiring Lengths for PICMG 1.2 Backplane                     | 54 |

| 21 | PCI-X Clock Wiring Lengths for PICMG Backplane             | 55 |

| 22 | Customer Reference Board Stackup                           | 60 |

| 23 | Logic Analyzer Pod 1                                       | 62 |

| 24 | Logic Analyzer Pod 2                                       | 63 |

| 25 | Logic Analyzer Pod 3                                       | 64 |

| 26 | Logic Analyzer Pod 4                                       | 65 |

| 27 | Logic Analyzer Pod 5                                       | 66 |

| 28 | Logic Analyzer Pod 6                                       | 67 |

| 29 | Operational Power                                          | 69 |

| 30 | Design Reference Material                                  | 71 |

| 31 | Intel® Related Documentation                               | 71 |

## **Revision History**

| Date       | Revision | Description     |

|------------|----------|-----------------|

| April 2004 | 001      | Initial release |

## **About This Document**

1

This document provides layout information and guidelines for designing platform or add-in board applications with the Intel® 31154 133 MHz PCI Bridge.

This document is intended to be used as a guideline only. Intel recommends that you employ best-known design practices with board-level simulation, signal-integrity testing, and validation for a robust design. Please note that this design guide focuses on specific design considerations for the 31154 Bridge and is not intended to be an all-inclusive list of all good design practices. Use this guide as a starting point, and use empirical data to optimize your particular design.

## 1.1 Terminology and Definitions

#### Table 1. Terminology and Definition (Sheet 1 of 2)

| Term       | Definition                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                |  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 31154      | Intel® 31154 133 MHz PCI Bridge                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                |  |

| Stripline  |                                                                                                                                                                                                                                 | Stripline in a PCB is composed of the conductor inserted in a dielectric with GND planes to the top and bottom, as shown in the cross-section diagram at left.  NOTE: An easy way to distinguish stripline from microstrip is that you need to strip away layers of the board to view the trace on stripline.                                                                  |  |

| Microstrip |                                                                                                                                                                                                                                 | Microstrip in a PCB is composed of the conductor on the top layer above the dielectric with a ground plane below, as shown in the cross-section diagram at left.                                                                                                                                                                                                               |  |

| Prepreg    | Prepreg is material used for the lamination process of manufacturing PCBs. It consists of a layer of epoxy material that is placed between two cores. This layer melts into epoxy when heated and forms around adjacent traces. |                                                                                                                                                                                                                                                                                                                                                                                |  |

| Core       | Core material is used for the lamination process of manufacturing PCBs. This material is two-sided laminate with copper on each side. The core is an internal layer that is etched.                                             |                                                                                                                                                                                                                                                                                                                                                                                |  |

| РСВ        | Layer 1: copper Prepreg Layer 2: GND  Core Layer 3: V <sub>CC</sub> Prepreg Layer 4: copper  Example of a cross-section of a four-layer stack                                                                                   | Printed circuit board: An example PCB manufacturing process consists of the following steps:  A PCB consists of alternating layers of core and prepreg stacked.  The finished PCB is heated and cured.  The via holes are drilled.  Plating covers holes and outer surfaces.  Etching removes unwanted copper.  The PCB is tinned, coated with solder mask, and silk-screened. |  |

Table 1. Terminology and Definition (Sheet 2 of 2)

| Term       | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

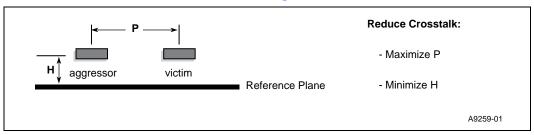

| Aggressor  | An aggressor network is a network that transmits a coupled signal to another network.  Zo  Zo  Aggressor Network  B3337-01                                                                                                                                                                                                                                                                                                                                                                          |  |

| Victim     | A network that receives a coupled cross-talk signal from another network is a called the victim network.                                                                                                                                                                                                                                                                                                                                                                                            |  |

| Network    | A network is the trace of a PCB that completes an electrical connection between two or more components.                                                                                                                                                                                                                                                                                                                                                                                             |  |

| Stub       | A stub is a branch from a trunk terminating at the pad of an agent.                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| ISI        | Inter-Symbol Interference (ISI) occurs when a transition that has not been completely dissipated interferes with a signal being transmitted down a transmission line. ISI can impact both timing and signal integrity. It is dependent on frequency, time delay of the line, and the refection coefficient at the driver and receiver. Examples of ISI patterns that can be used in testing at the maximum allowable frequencies are the sequences shown below:  0101 0101 0101 0101 0011 0011 0011 |  |

| Device     | A device is a component of a PCI system that connects to a PCI bus. As defined by PCI 2.3, a device can be a single-function or a multi-function device.                                                                                                                                                                                                                                                                                                                                            |  |

| Downstream | A transaction that targets the secondary side of the bridge is a downstream transaction.                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| Upstream   | A transaction that targets the primary side of the bridge is an upstream transaction.                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| SHB        | SHB is a system host board in a PICMIG 1.2 backplane. The removable CPU board provides clocks and arbitration signals as well as an optional ATX power supply control.                                                                                                                                                                                                                                                                                                                              |  |

| ePCI-X     | Embedded PCI-X specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| CRB        | Customer Reference Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

## Introduction

## 2.1 Product Overview

The Intel<sup>®</sup> 31154 133 MHz PCI Bridge (called hereafter the "31154") is a PCI component that functions as a highly concurrent, low-latency transparent bridge between two PCI buses. The 31154 can operate as a PCI-to-PCI bridge in the configurations shown in Table 2.

Table 2. PCI-to-PCI Bridge Configurations

| Primary Bus Interface | Secondary Bus Interface |

|-----------------------|-------------------------|

| PCI 2.3               | PCI 2.3                 |

| PCI 2.3               | PCI-X                   |

| PCI-X                 | PCI 2.3                 |

| PCI-X                 | PCI-X                   |

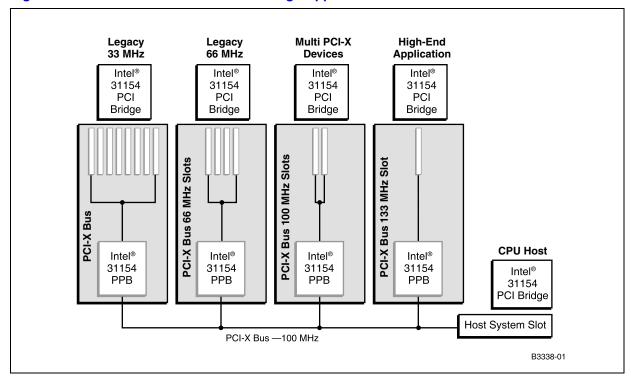

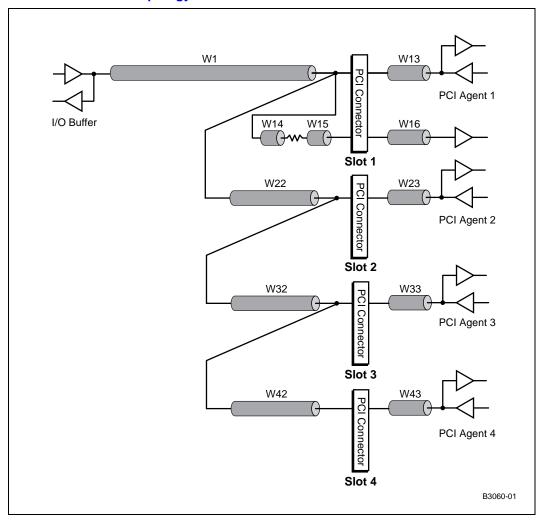

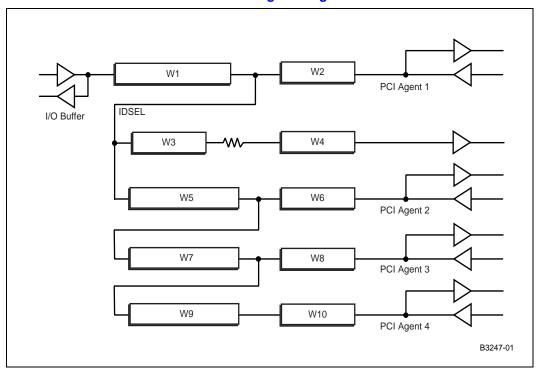

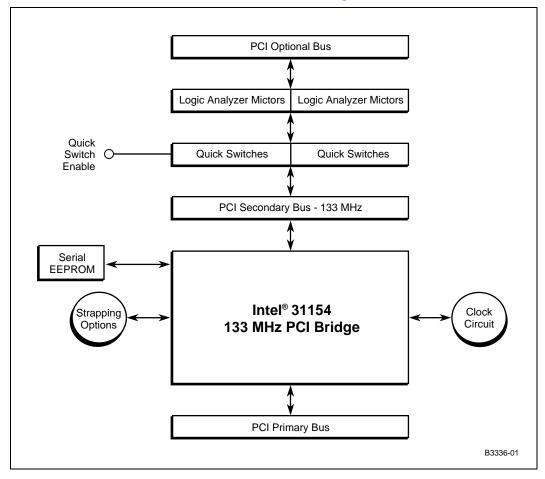

The 31154 is used on motherboards to provide additional I/O expansion slots. It is also used on PCI add-in cards to mitigate the restrictive electrical loading constraints imposed on an expansion slot, enabling multiple conventional PCI or multiple PCI-X devices to reside on a single PCI I/O adapter. The 31154 block diagram in Figure 1 indicates potential 31154 applications for a range of PCI bus speeds.

Figure 1. Intel<sup>®</sup> 31154 133 MHz PCI Bridge Applications

The 31154 has additional hardware support for CompactPCI\* Hot Swap and Redundant System Slot via queue flush, arbiter lock, and clock output tristating.

The 31154 supports any combination of 32-bit and 64-bit data transfers on its primary and secondary bus interfaces. The 31154 is 33/66 MHz capable in conventional PCI mode, and can run at 66 MHz, 100 MHz, or 133 MHz when operating in PCI-X mode, depending upon its surrounding environment.

### 2.2 Features List

#### Table 3. Features List

- PCI bus interfaces (2):

- PCI Local Bus Specification, Revision 2.3 compliant

- *PCI-to-PCI Bridge Architecture* Specification, Revision 1.2 compliant

- PCI Bus Power Management Interface Specification, Revision 1.1 compliant

- PCI-X Addendum to the PCI Local Bus Specification, Revision 1.0b compliant

- External SROM support

- Vital Products Data (VPD) support

- 64-bit initiator/target capable

- 64-bit addressing

- Hardware support for dual-host cPCI configurations

- Compact PCI Hot Swap Specification, Revision 2.1 R2.0 support

- Secondary clock generation with 10 clock outputs

- Secondary bus arbitration:

- Internal arbiter supports nine agents in addition to the 31154.

- Internal arbiter can be disabled.

- Optimized for PCI-X mode

- Bus parking on bridge or last master

- Improved buffer architecture:

- 8 KBytes data buffers in each direction

- Improved level of concurrency:

Up to nine outstanding transactions on each bus simultaneously

- Scalability and flexibility:

- Conventional PCI 32/64-bit 33/66 MHz, 3.3 V

- 5 V tolerant inputs

- PCI-X 32/64-bit 66/100/133 MHz, 3.3 V

- JTAG interface

- GPIO interface:

- Allows simple software-controlled signaling protocols

## 2.3 Related External Specifications

- PCI Local Bus Specification, Revision 2.3

- PCI-to-PCI Bridge Architecture Specification, Revision 1.1

- PCI Bus Power Management Interface Specification, Revision 1.1

- Compact PCI Hot Swap Specification, Revision 2.1 R2.0

- PCI-X Addendum to the PCI Local Bus Specification, Revision 1.1

- Embedded PCI-X Specification PICMG 1.2 R1.0

## 2.4 References

This section lists references that can be useful with a 31154 application. These documents are available on the Intel Developer website (http://developer.intel.com):

- Intel® 31154 133 MHz PCI Bridge Datasheet (278821)

- Intel<sup>®</sup> 31154 133 MHz PCI Bridge Developer's Manual (278848)

- Intel® 31154 133 MHz PCI Bridge Specification Update (300826)

- Intel<sup>®</sup> 31154 133 MHz PCI Bridge Design Checklist (300959)

- Intel® 31154 133 MHz PCI Bridge Evaluation Board Schematics (278839)

**§** §

THIS PAGE INTENTIONALLY LEFT BLANK

# Package Information

3

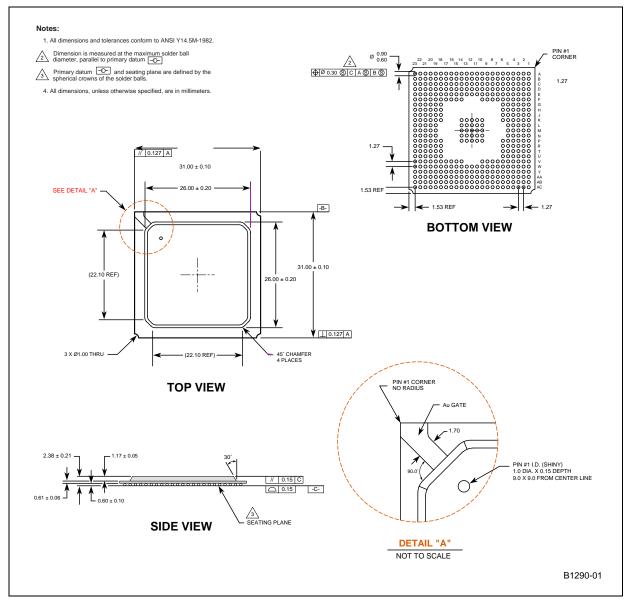

The Intel<sup>®</sup> 31154 133 MHz PCI Bridge is offered in a 421-lead PBGA package. The mechanical dimensions for this package are provided in Figure 2 on page 14.

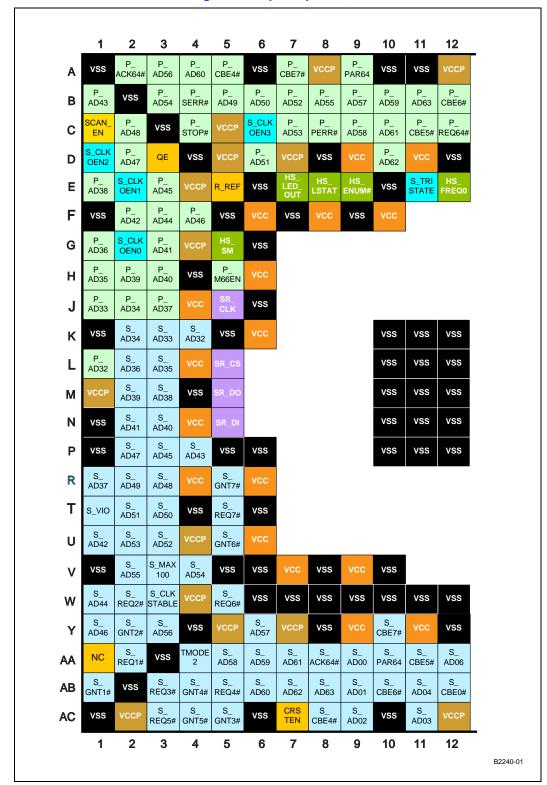

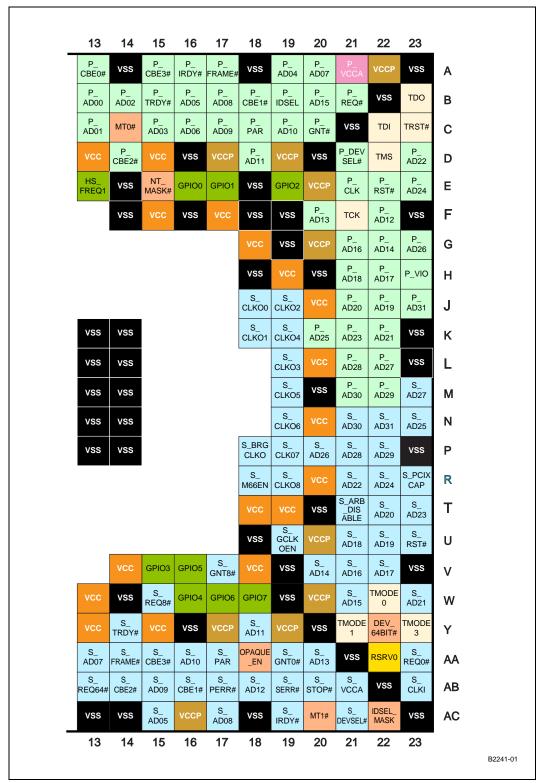

Figure 3 on page 15 and Figure 4 on page 16 show the 421-lead PBGA, mapped by pin function. These figures are helpful in placing components around the 31154 for the layout of a PCB. To simplify routing and minimize the number of cross traces, keep this layout in mind when placing components on your board. The signals, by design, are located on the PBGA package to simplify signal routing and system implementation. Figure 3 shows the left side of the 31154 ball map, and Figure 4 shows the right side of the ball map.

Figure 2. Intel® 31154 133 MHz PCI Bridge Package

Figure 3. Intel® 31154 133 MHz PCI Bridge Ball Map—Top View, Left Side

Figure 4. Intel® 31154 133 MHz PCI Bridge Ball Map—Top View, Right Side

## 3.1 Total Signal Count

## Table 4. Total Signal Count

| Interface             | Signals |

|-----------------------|---------|

| PCI bus interface     | 112     |

| PCI 64-bit extensions | 78      |

| Clock and reset       | 20      |

| JTAG                  | 12      |

| Serial ROM interface  | 4       |

| CompactPCI* Hot Swap  | 6       |

| Hardware strap        | 5       |

| Miscellaneous         | 17      |

| Total                 | 254     |

**§** §

THIS PAGE INTENTIONALLY LEFT BLANK

# **Terminations**

4

This chapter details all the recommended Intel® 31154 133 MHz PCI Bridge terminations required for the different operating modes.

The chapter provides the recommended pull-up and pull-down terminations for a 31154 layout. Table 5 lists these 31154 termination values. Note that for motherboards, the *PCI Local Bus Specification*, Revision 2.3 requires that the PCI signals provide the termination resistors.

Table 5. Pull-Up/Pull-Down Terminations (Sheet 1 of 9)

| Signal              | Pull-Up/Pull-Down or Termination (See Note 1)                                                                                                                                           | Comments |  |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|

| PCI Reset           |                                                                                                                                                                                         |          |  |  |

| P_RST#              | Connect to bus RST# signal on primary PCI bus.                                                                                                                                          |          |  |  |

| S_RST#              | Connect to bus RST# signal on secondary PCI bus.                                                                                                                                        |          |  |  |

| Primary PCI Signals |                                                                                                                                                                                         |          |  |  |

| P_AD[31:0]          | Connect to primary PCI bus AD[31:0].                                                                                                                                                    |          |  |  |

| P_AD[63:32]         | For 64-bit primary PCI bus:  Connect to the AD[63:32] bits of the primary PCI bus.  For 32 bit Primary PCI Bus:  Pull up through individual external resistors (see Note 2 and Note 3). |          |  |  |

| P_CBE[3:0]          | Connect to the CBE[3:0]# bits of the primary PCI bus.                                                                                                                                   |          |  |  |

| P_CBE[7:4]#         | For 64-bit primary PCI bus:  Connect to the CBE[7:4]# bits of the primary PCI bus.  For 32-bit primary PCI Bus:  Pull up through individual external resistors (see Note 2 and Note 3). |          |  |  |

| P_FRAME#            | Connect to FRAME# of the primary PCI bus.                                                                                                                                               |          |  |  |

| P_DEVSEL#           | Connect to DEVSEL# of the primary PCI bus.                                                                                                                                              |          |  |  |

| P_IRDY#             | Connect to IRDY# of the primary PCI bus.                                                                                                                                                |          |  |  |

| P_TRDY#             | Connect to TRDY# of the primary PCI bus.                                                                                                                                                |          |  |  |

| P_STOP#             | Connect to STOP# of the primary PCI bus.                                                                                                                                                |          |  |  |

- 1. The recommended value for pull-up resistors for PCI applications is 5.6 K $\Omega$  (note that the minimum value for PCI 3.3 V signaling R<sub>MIN</sub> = 2.42 K $\Omega$ , R<sub>TYP</sub> = 8.2 K $\Omega$ , as per the *PCI Local Bus Specification*, Revision 2.3, section 4.3.3).

- 2. The recommended value for pull-up resistors for PCI-X applications is 8.2 K $\Omega$ . For PCI-X, the minimum pull-up resistor value is 5 K $\Omega$ , as per the *PCI-X Addendum to the PCI Local Bus Specification*, Revision 1.0b, section 9.7.

- 3. For plug-in card implementations, the pull-up must be on the motherboard.

- 4. Connect PVIO and SVIO pull-up resistors to 5 V or 3.3 V power supply through an external resistor—25  $\Omega$  (5 V) or 0  $\Omega$  (3.3 V), depending on the signaling level of the primary/secondary PCI bus. Refer to the power-sequencing guidelines in Section 8.2 on page 58.

Table 5. Pull-Up/Pull-Down Terminations (Sheet 2 of 9)

| Signal                                                                                | Pull-Up/Pull-Down or Termination (See Note 1)                                                                                           | Comments                                                         |

|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| P_GNT#                                                                                | Connect to GNT# of the primary PCI bus.                                                                                                 |                                                                  |

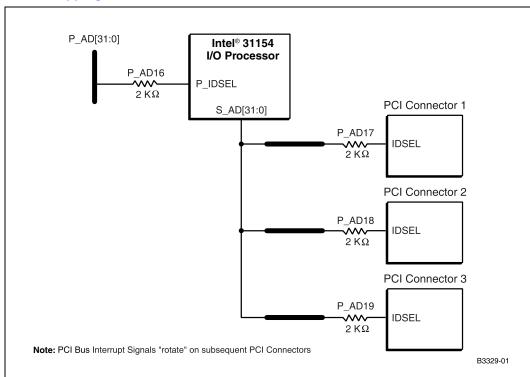

| P_IDSEL#                                                                              | Connect to one of the AD lines of the primary PCI bus or to the IDSEL# signal of the PCI edge connector (for add-in card applications). | Refer to Section 5.3, "IDSEL Lines" on page 30 for more details. |

| P_M66EN                                                                               | Connect to the M66EN signal of the primary PCI bus of the PCI add-in card finger.                                                       |                                                                  |

| P_PAR                                                                                 | Connect to PAR of the primary PCI bus.                                                                                                  |                                                                  |

| P_PAR64                                                                               | Connect to PERR# of the primary PCI bus.                                                                                                |                                                                  |

| P_PERR#                                                                               | Connect to PERR# of the primary PCI bus.                                                                                                |                                                                  |

| P_REQ#                                                                                | Connect to one of the PCI bus request signals of the primary PCI bus.                                                                   |                                                                  |

| P_SERR#                                                                               | Connect to SERR# of the primary PCI bus.                                                                                                |                                                                  |

| Secondary PCI Signa                                                                   | Is                                                                                                                                      |                                                                  |

| S_AD[63:32]                                                                           | Pull up to VCC33 through external 8.2 K $\Omega$ resistors.                                                                             |                                                                  |

| S_CBE[7:4]#                                                                           | Pull up to VCC33 through external 8.2 K $\Omega$ resistors.                                                                             |                                                                  |

| S_REQ64#                                                                              | Pull up to VCC33 through external 8.2 K $\Omega$ resistors.                                                                             |                                                                  |

| S_ACK64#                                                                              | Pull up to VCC33 through external 8.2 K $\Omega$ resistors.                                                                             |                                                                  |

| S_FRAME#,<br>S_IRDY#,<br>S_TRDY#,<br>S_STOP#,<br>S_DEVSEL#,<br>S_PERR#,<br>S_SERR#    | Pull up to VCC33 voltage through external 8.2 K $\Omega$ resistors.                                                                     |                                                                  |

| S_REQ[8:1]#,<br>S_REQ0#/BR_GNT#,<br>S_GNT0#/BR_REQ#                                   | Pull up to VCC33 voltage through external 8.2 K $\Omega$ resistors.                                                                     | Pull-up for both internal and external arbiter mode.             |

| Secondary GNT# S_GNT1#, S_GNT2#, S_GNT3#, S_GNT4#, S_GNT5#, S_GNT6#, S_GNT7#, S_GNT8# | Connect to GNT# input of the PCI devices on the secondary PCI bus.  NC when not used.                                                   |                                                                  |

- 1. The recommended value for pull-up resistors for PCI applications is 5.6  $\rm K\Omega$  (note that the minimum value for PCI 3.3  $\rm V$ signaling  $R_{MIN}=2.42~K\Omega$ ,  $R_{TYP}=8.2~K\Omega$ , as per the *PCI Local Bus Specification*, Revision 2.3, section 4.3.3). 2. The recommended value for pull-up resistors for PCI-X applications is 8.2  $K\Omega$ . For PCI-X, the minimum pull-up resistor value

- is 5 K $\Omega$ , as per the *PCI-X Addendum to the PCI Local Bus Specification*, Revision 1.0b, section 9.7.

- 3. For plug-in card implementations, the pull-up must be on the motherboard.

- 4. Connect PVIO and SVIO pull-up resistors to 5 V or 3.3 V power supply through an external resistor—25  $\Omega$  (5 V) or  $0~\Omega$  (3.3 V), depending on the signaling level of the primary/secondary PCI bus. Refer to the power-sequencing guidelines in Section 8.2 on page 58.

Table 5. Pull-Up/Pull-Down Terminations (Sheet 3 of 9)

| Signal      | Pull-Up/Pull-Down or Termination (See Note 1)                                                                                                                                                                                                      | Comments                                                                                                                                                                                                                                                                                                                                        |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S_AD[31:17] | These signals can be used as IDSEL lines and are connected to IDSEL of the secondary PCI bus through an external series coupling resistor (a resistor of 2 K $\Omega$ is used on the customer reference board).                                    |                                                                                                                                                                                                                                                                                                                                                 |

| PCI Clocks  |                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                 |

| P_CLK       | Connect to the PCI clock on the primary PCI bus.                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                 |

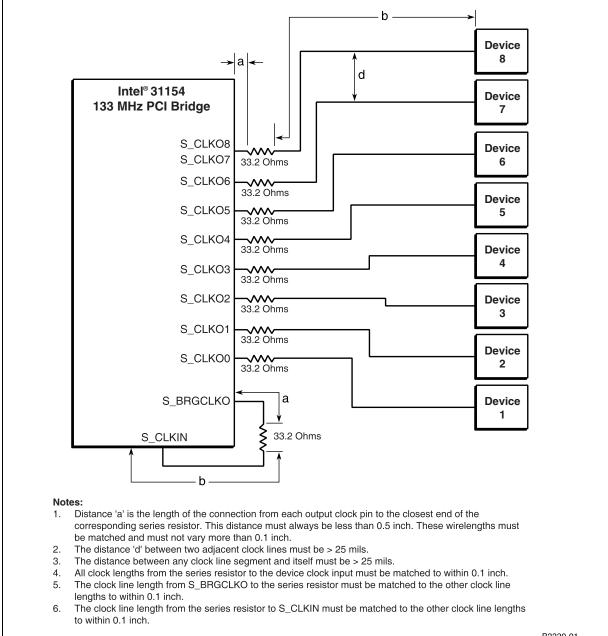

| S_BRGCLKO   | When the internal clock of the 31154 is used, connect to S_CLKI through a 33.2 $\Omega$ series resistor. NC when external clock is used.                                                                                                           | All S_CLKO[8:0] and S_BRGCLKO must match in length.  When there are PCI slots in the design, S_BRGCLKO must be 3" longer to compensate for the 2.5" trace length from the connector to the PCI device on a PCI add-in card.                                                                                                                     |

| S_CLKO[8:0] | When the internal clock of the 31154 is used, connect to the PCI clock input of the secondary PCI devices through a 33.2 $\Omega$ series resistor. Each clock can be connected to only one PCI device.                                             | These clocks can be disabled by strapping the S_CLKOEN[3:0] during reset.  All S_CLKO[8:0] and S_BRGCLKO must match in length.  For asynchronous mode, there is no maximum skew between P_CLK and S_CLKI.  NOTE: These clocks can be disabled by strapping the S_CLKOEN[3:0] during reset.                                                      |

| S_CLKI      | When the internal clock of the 31154 is used, connect to S_BRGCLKO.  When an external clock is used, connect to external clock source.                                                                                                             | When using the internal clock, refer to S_BRGCLKO (above) for additional information.  When using an external clock source, all secondary clocks must have matching length.  When using PCI slots in the design, S_BRGCLKO must be 3" longer to compensate for the 2.5" trace length from the connector to the PCI device on a PCI add-in card. |

| S_CLKSTABLE | When the internal clock of the 31154 is used, S_CLKSTABLE must be tied high to VCC33 through an external 8.2 K $\Omega$ resistor. When an external clock source is used, connect to logic that outputs high after the secondary clocks are stable. |                                                                                                                                                                                                                                                                                                                                                 |

- The recommended value for pull-up resistors for PCI applications is 5.6 KΩ (note that the minimum value for PCI 3.3 V signaling R<sub>MIN</sub> = 2.42 KΩ, R<sub>TYP</sub> = 8.2 KΩ, as per the *PCI Local Bus Specification*, Revision 2.3, section 4.3.3).

The recommended value for pull-up resistors for PCI-X applications is 8.2 KΩ. For PCI-X, the minimum pull-up resistor value

- is 5 K $\Omega$ , as per the *PCI-X* Addendum to the *PCI Local Bus Specification*, Revision 1.0b, section 9.7.

- For plug-in card implementations, the pull-up must be on the motherboard.

Connect PVIO and SVIO pull-up resistors to 5 V or 3.3 V power supply through an external resistor—25 Ω (5 V) or  $0~\Omega$  (3.3 V), depending on the signaling level of the primary/secondary PCI bus. Refer to the power-sequencing guidelines in Section 8.2 on page 58.

Table 5. Pull-Up/Pull-Down Terminations (Sheet 4 of 9)

| Signal        | Pull-Up/Pull-Down or Termination (See Note 1)                                                                                                                                                                                                                                                                               | Comments                                                                                                          |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

|               | When the internal clock of the 31154 is used, pull high to VCC33 through an external 8.2 K $\Omega$ resistor.                                                                                                                                                                                                               |                                                                                                                   |

| S_GCLKOEN     | When an external clock source is used, tie to GND through a 330 $\Omega$ external resistor. All secondary clock outputs (S_CLKO[8:0] and S_BRGCLKO) asynchronously tristate.                                                                                                                                                |                                                                                                                   |

|               | When an external clock source is used, tie S_CLKOEN[3:0] to a stable value. Refer to S_CLKOEN[3:0], below.                                                                                                                                                                                                                  |                                                                                                                   |

|               | These are strapping pins to enable or tristate S_CLKO[8:0] after reset.                                                                                                                                                                                                                                                     | NOTE: This strapping is meaningful only when S_GCLKOEN is pulled high.                                            |

| S_CLKOEN[3:0] | <ul> <li>To enable all S_CLKO[8:0], pull each<br/>S_CLKOEN[3:0] pin to 3.3 V through an<br/>external 8.2 KΩ resistor.</li> </ul>                                                                                                                                                                                            | When external clocks are used, tie S_GCLKOEN low and tie S_CLKOEN[3:0] to some stable value (0000b, for example). |

|               | To selectively disable some of the<br>S_CLKO[8:0], refer to 31154 Control<br>Register 2, bits[8:0].                                                                                                                                                                                                                         |                                                                                                                   |

| Hot Swap      |                                                                                                                                                                                                                                                                                                                             |                                                                                                                   |

| HS_ENUM#      | For Hot Swap:     Connect the interrupt input pin to the host.     When not using Hot Swap:     NC (there is a weak internal pull-up).                                                                                                                                                                                      |                                                                                                                   |

| HS_LSTAT      | For Hot Swap:  Connect to cPCI ejector switch.  When not using Hot Swap:  Tie low to GND.                                                                                                                                                                                                                                   |                                                                                                                   |

| HS_LED_OUT    | For Hot Swap:  Connect to cPCI blue LED.  When not using Hot Swap:  NC                                                                                                                                                                                                                                                      |                                                                                                                   |

| HS_SM         | For Hot Swap:  0 = The 31154 retries any Type 0 configuration cycles addressed to it until serial ROM preload has completed (default)  1 = The 31154 ignores (causes master abort) any Type 0 configuration cycles addressed to it until its serial ROM preload has completed.  When not using Hot Swap:  • Tie low to GND. | 0 =  Tie low to GND. $1 =  Pull high to  3.3  V through an external  8.2  KΩ$ resistor.                           |

- 1. The recommended value for pull-up resistors for PCI applications is 5.6 KΩ (note that the minimum value for PCI 3.3 V signaling R<sub>MIN</sub> = 2.42 KΩ, R<sub>TYP</sub> = 8.2 KΩ, as per the *PCI Local Bus Specification*, Revision 2.3, section 4.3.3).

- 2. The recommended value for pull-up resistors for PCI-X applications is 8.2 KΩ. For PCI-X, the minimum pull-up resistor value is 5 KΩ, as per the *PCI-X Addendum to the PCI Local Bus Specification*, Revision 1.0b, section 9.7.

- 3. For plug-in card implementations, the pull-up must be on the motherboard.

- 4. Connect PVIO and SVIO pull-up resistors to 5 V or 3.3 V power supply through an external resistor— $25 \Omega$  (5 V) or  $0 \Omega$  (3.3 V), depending on the signaling level of the primary/secondary PCI bus. Refer to the power-sequencing guidelines in Section 8.2 on page 58.

Table 5. Pull-Up/Pull-Down Terminations (Sheet 5 of 9)

| Signal                       | Pull-Up/Pull-Down or Termination (See Note 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Comments                                                                                                  |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| HS_FREQ[1:0]                 | For Hot Swap:  • Depending on Primary PCI Bus frequency  00 = PCI Mode, 33 or 66 MHz (default)  01 = PCI-X 66 MHz  10 = PCI-X 100 MHz  11 = PCI-X 133 MHz  When not using Hot Swap:  • Tie low to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Only valid when HS_SM = 1.  0 = Tie low to GND.  1 = Pull high to 3.3 V through external 8.2 KΩ resistor. |

| Hardware Straps (san         | npled at the edge of P_RST#)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                           |

| S_ARB_DISABLE/<br>S_ARB_LOCK | <ul> <li>To disable internal secondary arbiter:</li> <li>Pull up to 3.3 V through an external 8.2 KΩ resistor.</li> <li>S_GNT0# becomes the secondary PCI bus request output of the 31154, and S_REQ0# becomes the secondary PCI bus grant input of the 31154.</li> <li>To enable internal secondary arbiter:</li> <li>Pull down to GND through an external 220 Ω resistor (default).</li> <li>S_ARB_LOCK (after trailing edge of P_RST#):</li> <li>Sampled as 1b, the internal secondary bus arbiter of the 31154 locks and provides the grant only to itself.</li> <li>When internal arbiter is used and 1b is sampled after the trailing edge of P_RST#, the internal secondary bus arbiter of the 31154 locks and provide grant only to itself.</li> </ul> | NOTE: S_ARB_LOCK has an effect only when the internal arbiter is enabled.                                 |

| S_MAX100                     | To limit secondary bus frequency to maximum of 100 MHz:  • Pull high to 3.3 V through an external 8.2 K $\Omega$ resistor.  Otherwise:  • Pull low to GND through an external 330 $\Omega$ resistor (default).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                           |

| S_TRISTATE                   | GND during normal operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                           |

- 1. The recommended value for pull-up resistors for PCI applications is 5.6 K $\Omega$  (note that the minimum value for PCI 3.3 V signaling  $R_{MIN} = 2.42 \text{ K}\Omega$ ,  $R_{TYP} = 8.2 \text{ K}\Omega$ , as per the *PCI Local Bus Specification*, Revision 2.3, section 4.3.3). 2. The recommended value for pull-up resistors for PCI-X applications is 8.2 K $\Omega$ . For PCI-X, the minimum pull-up resistor value

- is 5 K $\Omega$ , as per the PCI-X Addendum to the PCI Local Bus Specification, Revision 1.0b, section 9.7.

- 3. For plug-in card implementations, the pull-up must be on the motherboard.

- 4. Connect PVIO and SVIO pull-up resistors to 5 V or 3.3 V power supply through an external resistor—25  $\Omega$  (5 V) or  $0~\Omega$  (3.3 V), depending on the signaling level of the primary/secondary PCI bus. Refer to the power-sequencing guidelines in Section 8.2 on page 58.

Table 5. Pull-Up/Pull-Down Terminations (Sheet 6 of 9)

| Signal        | Pull-Up/Pull-Down or Termination (See Note 1)                                                                                                                                              | Comments                                                                                   |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

|               | To enable Opaque Memory Base/Limit Registers to establish a private memory space for secondary bus usage:                                                                                  |                                                                                            |

| OPAQUE_EN     | • Pull high to 3.3 V through an external 8.2 K $\Omega$ resistor.                                                                                                                          |                                                                                            |

|               | To disable Opaque Memory Base/Limit Registers:                                                                                                                                             |                                                                                            |

|               | • Pull low to GND through an external 220 $\Omega$ resistor (default).                                                                                                                     |                                                                                            |

|               | To enable device hiding after reset (in other words, to hide device numbers 16–21 from the host):                                                                                          |                                                                                            |

|               | Pull high to 3.3 V through an external resistor.                                                                                                                                           |                                                                                            |

| IDOEL MACK    | To disable device hiding after reset:                                                                                                                                                      |                                                                                            |

| IDSEL_MASK    | • Pull low to GND through an external 220 $\Omega$ resistor (default).                                                                                                                     |                                                                                            |

|               | After reset, device hiding can be performed through software through the Secondary IDSEL Select Register (Offset 5Ch).                                                                     |                                                                                            |

|               | This bit is used by the system management software to help the user identify the best slot for an add-in card:                                                                             |                                                                                            |

| DEV_64BIT#    | <ul> <li>When the 31154 is installed on an add-in card<br/>and the add-in card implements a 64-bit PCI<br/>connector, pull up to 3.3 V through an external<br/>8.2 KΩ resistor.</li> </ul> |                                                                                            |

|               | • When the 31154 is not installed on an add-in card or the add-in card implements only a 32-bit PCI connector, pull low to GND through a 220 $\Omega$ external resistor (default).         |                                                                                            |

| Serial EEPROM |                                                                                                                                                                                            |                                                                                            |

|               | Serial ROM clock input:                                                                                                                                                                    |                                                                                            |

| SR_CLK        | Connect to the clock input of the EEPROM.                                                                                                                                                  |                                                                                            |

|               | NC when EEPROM is not required in design.                                                                                                                                                  |                                                                                            |

| SR_DI         | Serial ROM data input:     Connect to the DI input of the EEPROM.                                                                                                                          |                                                                                            |

| SK_DI         | NC when EEPROM is not required in design.                                                                                                                                                  |                                                                                            |

|               | Serial ROM data output:                                                                                                                                                                    | NOTE: When EEPROM is present but register                                                  |

| SR_DO         | Connect to the DO output of the EEPROM.                                                                                                                                                    | preload is not desired, bits[7:6] of the first<br>byte can be any value except the preload |

|               | <ul> <li>Tie high or pull to GND when EEPROM is not<br/>required in design.</li> </ul>                                                                                                     | enable value (10b).                                                                        |

|               | Serial ROM chip select:                                                                                                                                                                    |                                                                                            |

| SR_CS         | Connect to the chip select of the EEPROM.      NO when EEPROM is not required in design.                                                                                                   |                                                                                            |

|               | NC when EEPROM is not required in design.                                                                                                                                                  |                                                                                            |

- 1. The recommended value for pull-up resistors for PCI applications is 5.6  $\rm K\Omega$  (note that the minimum value for PCI 3.3  $\rm V$

- signaling  $R_{MIN}=2.42~K\Omega$ ,  $R_{TYP}=8.2~K\Omega$ , as per the *PCI Local Bus Specification*, Revision 2.3, section 4.3.3). 2. The recommended value for pull-up resistors for PCI-X applications is 8.2 K $\Omega$ . For PCI-X, the minimum pull-up resistor value is 5 K $\Omega$ , as per the PCI-X Addendum to the PCI Local Bus Specification, Revision 1.0b, section 9.7.

- 3. For plug-in card implementations, the pull-up must be on the motherboard.

- 4. Connect PVIO and SVIO pull-up resistors to 5 V or 3.3 V power supply through an external resistor—25 Ω (5 V) or  $0~\Omega$  (3.3 V), depending on the signaling level of the primary/secondary PCI bus. Refer to the power-sequencing guidelines in Section 8.2 on page 58.

Table 5. Pull-Up/Pull-Down Terminations (Sheet 7 of 9)

| Signal        | Pull-Up/Pull-Down or Termination (See Note 1)                                                                                                                                                                                                                        | Comments                                                                                                                                                                                                    |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JTAG          |                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                             |

| тск           | Pull low when not used.                                                                                                                                                                                                                                              |                                                                                                                                                                                                             |

| TDI           | When not used, pull up to 3.3 V through an external 8.2 K $\Omega$ resistor.                                                                                                                                                                                         |                                                                                                                                                                                                             |

| TDO           | NC when not used                                                                                                                                                                                                                                                     |                                                                                                                                                                                                             |