# SM8000 SERIES

# **OPTICAL SWITCH**

**USER'S MANUAL**

P/N: 82-0052-000 Released February 13, 2006

VXI Technology, Inc.

2031 Main Street Irvine, CA 92614-6509 (949) 955-1894

# TABLE OF CONTENTS

| INTRODUCTION                                      |    |

|---------------------------------------------------|----|

| Certification                                     | 6  |

| Warranty                                          | 6  |

| Limitation of Warranty                            | 6  |

| Restricted Rights Legend                          |    |

| DECLARATION OF CONFORMITY                         |    |

| GENERAL SAFETY INSTRUCTIONS                       |    |

| Terms and Symbols                                 |    |

| Warnings                                          |    |

| SUPPORT RESOURCES                                 |    |

| SECTION 1                                         | 13 |

| INTRODUCTION                                      | 13 |

| Overview                                          | 13 |

| SM8000 Series - Optical Switch Controller         |    |

| SM8001 / SM8002 - Multi-Channel Switches          | 15 |

| Configurations                                    |    |

| SM8001 / SM8002 Multi Switch Specifications       |    |

| SM8003 - Prism Switches                           | 18 |

| Configurations                                    |    |

| SM8101 / SM8102 - Optical Attenuators             | 20 |

| SECTION 2                                         | 21 |

| Preparation for Use                               | 21 |

| Introduction                                      | 21 |

| Calculating System Power and Cooling Requirements | 21 |

| Setting the Chassis Backplane Jumpers             |    |

| Setting the Logical Address                       |    |

| Example 1                                         | 22 |

| Example 2                                         | 23 |

| Selecting the Extended Memory Space               |    |

| Optical Connections                               |    |

| Cleaning Optical Connectors                       |    |

| Mating Optical Connectors                         | 24 |

| SECTION 3                                         | 25 |

| OPERATION                                         | 25 |

| General Description                               |    |

| SM8001 / SM8002 - Multi-Channel Switches          |    |

| SM8003 - Prism Switches                           | 26 |

| SM8101 / SM8102 - Optical Attenuators             | 27 |

| Operation                                         | 28 |

| SM8001 / SM8002 - Multi-Channel Switches          | 28 |

| Resetting the Switch                              | 28 |

| Relay Registers - Output Channel Selection        | 28 |

1 x N Switch Configuration

29

Duplex 1 x N Switch Configuration

30

2 x N Blocking Switch Configuration

31

2 x N Non-Blocking Switch Configuration

32

Calculating Switching Time

33

SM8003 - Prism Switches

34

SM8101 / SM8102 - Optical Attenuators

34

Starting the Device

35

| Control Modes                                                             | 35 |

|---------------------------------------------------------------------------|----|

| Uncalibrated Operation - Move-To-Absolute-Step                            | 35 |

| Calibrated Operation                                                      |    |

| BUSY Signal                                                               |    |

| ERROR Status                                                              | 36 |

| Resetting the Device                                                      | 36 |

| Commanding the Devices                                                    | 36 |

| SECTION 4                                                                 | 37 |

| Programming                                                               | 37 |

| Register Access                                                           |    |

| Addressing                                                                |    |

| SMIP II Registers - A16                                                   |    |

| Module Registers - SM8000 Series Controller - A24 / A32 - Extended Memory | 48 |

| DEVICE MEMORY                                                             |    |

| Module Relay Control Address - SM8000 Series Optical Switch Controller    | 54 |

| Relay Register Offset                                                     |    |

| Writing to the Relay Registers                                            |    |

| PROGRAMMING EXAMPLES                                                      |    |

| Typical Optical Multi-Switch Control Example                              | 57 |

| Typical Optical Attenuator Control Example                                |    |

| COMMAND REGISTER                                                          |    |

| Write Example                                                             | 60 |

| Read Example                                                              | 60 |

| Command Set                                                               | 61 |

| 30h                                                                       | 62 |

| 31h                                                                       | 62 |

| 32h                                                                       | 63 |

| 35h                                                                       | 63 |

| 43h                                                                       | 63 |

| 6Ch                                                                       | 64 |

| 80h                                                                       | 64 |

| 81h                                                                       | 65 |

| 82h                                                                       | 65 |

| 83h                                                                       | 66 |

| 89h                                                                       | 66 |

| 8Ah                                                                       | 67 |

| 8Bh                                                                       | 67 |

| 8Ch                                                                       | 68 |

| 8Dh                                                                       | 68 |

| 8Eh                                                                       | 69 |

| 90h                                                                       |    |

| 96h                                                                       | 71 |

| A2h                                                                       | 71 |

|                                                                           |    |

VXI Technology, Inc.

#### **CERTIFICATION**

VXI Technology, Inc. (VTI) certifies that this product met its published specifications at the time of shipment from the factory. VTI further certifies that its calibration measurements are traceable to the United States National Institute of Standards and Technology (formerly National Bureau of Standards), to the extent allowed by that organization's calibration facility, and to the calibration facilities of other International Standards Organization members.

#### WARRANTY

The product module referred to herein is warranted against defects in material and workmanship for a period of one year from the receipt date of the product at customer's facility. The same warranty applies to the optical device options (SM8XXX) for a period of one year. The sole and exclusive remedy for breach of any warranty concerning these goods shall be repair or replacement of defective parts, or a refund of the purchase price, to be determined at the option of VTI.

For warranty service or repair, this product must be returned to a VXI Technology authorized service center. The product shall be shipped prepaid to VTI and VTI shall prepay all returns of the product to the buyer. However, the buyer shall pay all shipping charges, duties, and taxes for products returned to VTI from another country.

VTI warrants that its software and firmware designated by VTI for use with a product will execute its programming when properly installed on that product. VTI does not however warrant that the operation of the product, or software, or firmware will be uninterrupted or error free.

#### LIMITATION OF WARRANTY

The warranty shall not apply to defects resulting from improper or inadequate maintenance by the buyer, buyer-supplied products or interfacing, unauthorized modification or misuse, operation outside the environmental specifications for the product, or improper site preparation or maintenance.

VXI Technology, Inc. shall not be liable for injury to property other than the goods themselves. Other than the limited warranty stated above, VXI Technology, Inc. makes no other warranties, express or implied, with respect to the quality of product beyond the description of the goods on the face of the contract. VTI specifically disclaims the implied warranties of merchantability and fitness for a particular purpose.

#### RESTRICTED RIGHTS LEGEND

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subdivision (b)(3)(ii) of the Rights in Technical Data and Computer Software clause in DFARS 252.227-7013.

VXI Technology, Inc. 2031 Main Street Irvine, CA 92614-6509 U.S.A.

# DECLARATION OF CONFORMITY

#### Declaration of Conformity According to ISO/IEC Guide 22 and EN 45014

MANUFACTURER'S NAME VXI Technology, Inc.

MANUFACTURER'S ADDRESS 2031 Main Street

Irvine, California 92614-6509

PRODUCT NAME Optical Switch

MODEL NUMBER(S) SM8000

PRODUCT OPTIONS All

PRODUCT CONFIGURATIONS All

VXI Technology, Inc. declares that the aforementioned product conforms to the requirements of the Low Voltage Directive 73/23/EEC and the EMC Directive 89/366/EEC (inclusive 93/68/EEC) and carries the "CE" mark accordingly. The product has been designed and manufactured according to the following specifications:

**SAFETY** EN61010 (2001)

EMC EN61326 (1997 w/A1:98) Class A

CISPR 22 (1997) Class A VCCI (April 2000) Class A

ICES-003 Class A (ANSI C63.4 1992) AS/NZS 3548 (w/A1 & A2:97) Class A

FCC Part 15 Subpart B Class A

EN 61010-1:2001

The product was installed into a C-size VXI mainframe chassis and tested in a typical configuration.

I hereby declare that the aforementioned product has been designed to be in compliance with the relevant sections of the specifications listed above as well as complying with all essential requirements of the Low Voltage Directive.

February 2006

Steve Mauga, QA Manager

VXI Technology, Inc.

# **GENERAL SAFETY INSTRUCTIONS**

Review the following safety precautions to avoid bodily injury and/or damage to the product. These precautions must be observed during all phases of operation or service of this product. Failure to comply with these precautions, or with specific warnings elsewhere in this manual, violates safety standards of design, manufacture, and intended use of the product.

Service should only be performed by qualified personnel.

#### TERMS AND SYMBOLS

These terms may appear in this manual:

**WARNING** Indicates that a procedure or condition may cause bodily injury or death.

CAUTION Indicates that a procedure or condition could possibly cause damage to

equipment or loss of data.

These symbols may appear on the product:

ATTENTION - Important safety instructions

Frame or chassis ground

Indicates that the product was manufactured after August 13, 2005. This mark is placed in accordance with EN 50419, Marking of electrical and electronic equipment in accordance with Article 11(2) of Directive 2002/96/EC (WEEE). End-of-life product can be returned to VTI by obtaining an RMA number. Fees for take-back and recycling will apply if not prohibited by national law.

#### WARNINGS

Follow these precautions to avoid injury or damage to the product:

**Use Proper Power Cord**To avoid hazard, only use the power cord specified for this product.

Use Proper Power Source To avoid electrical overload, electric shock, or fire hazard, do not

use a power source that applies other than the specified voltage.

Use Proper Fuse To avoid fire hazard, only use the type and rating fuse specified for

this product.

#### WARNINGS (CONT.)

#### **Avoid Electric Shock**

To avoid electric shock or fire hazard, do not operate this product with the covers removed. Do not connect or disconnect any cable, probes, test leads, etc. while they are connected to a voltage source. Remove all power and unplug unit before performing any service. Service should only be performed by qualified personnel.

#### **Ground the Product**

This product is grounded through the grounding conductor of the power cord. To avoid electric shock, the grounding conductor must be connected to earth ground.

#### **Operating Conditions**

To avoid injury, electric shock or fire hazard:

- Do not operate in wet or damp conditions.

- Do not operate in an explosive atmosphere.

- Operate or store only in specified temperature range.

- Provide proper clearance for product ventilation to prevent overheating.

- DO NOT operate if any damage to this product is suspected.

Product should be inspected or serviced only by qualified personnel.

Improper Use

The operator of this instrument is advised that if the equipment is used in a manner not specified in this manual, the protection provided by the equipment may be impaired. Conformity is checked by inspection.

# **SUPPORT RESOURCES**

Support resources for this product are available on the Internet and at VXI Technology customer support centers.

#### VXI Technology World Headquarters

VXI Technology, Inc. 2031 Main Street Irvine, CA 92614-6509

Phone: (949) 955-1894 Fax: (949) 955-3041

#### VXI Technology Cleveland Instrument Division

5425 Warner Road Suite 13 Valley View, OH 44125

Phone: (216) 447-8950 Fax: (216) 447-8951

#### VXI Technology Lake Stevens Instrument Division

VXI Technology, Inc. 1924 - 203 Bickford Snohomish, WA 98290

Phone: (425) 212-2285 Fax: (425) 212-2289

#### **Technical Support**

Phone: (949) 955-1894 Fax: (949) 955-3041

E-mail: support@vxitech.com

*Visit http://www.vxitech.com for worldwide support sites and service plan information.*

VXI Technology, Inc.

# **SECTION 1**

# **INTRODUCTION**

#### **OVERVIEW**

The SM8000 series optical switching modules are members of the VXI Technology SMIP  $II^{TM}$  family. They offer a modular design allowing custom switching configurations. Due to the nature of routing fiber optic cables and modules, the SM8000 series cannot be mixed in one base unit with other standard SMIP II products. They have their own single-slot or double-slot base units (SMIP II platform). The SM8000 series can combine different switch modules within themselves, and then install into a mainframe with other SMIP II products for a complete switching solution.

FIGURE 1-1: SM8000 SERIES OPTICAL SWITCH MODULES

#### SM8000 SERIES - OPTICAL SWITCH CONTROLLER

The SM8000 high-density optical switch controller module is designed to handle many different combinations of optical switching modules. This includes up to 12 single mode prism switches, or 4 multi-switch modules of various configurations, or 4 variable attenuators or tunable filters. The optical modules may be mixed and matched on a single SM8000. Please contact VXI Technology, Inc. directly for available configurations.

The SM8000 was designed to mount into either a single or double-slot VXI instrument carrier. The selection of the size of the carrier is dependent on the optical modules that are being controlled by the SM8000.

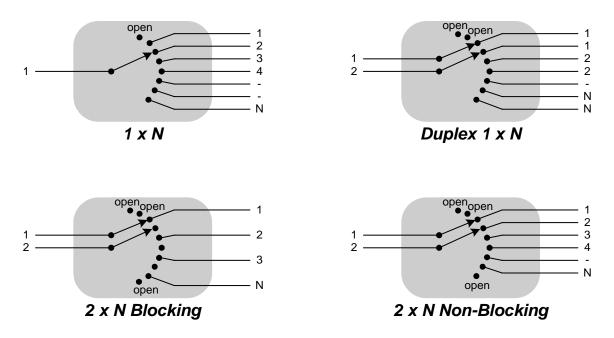

#### SM8001 / SM8002 - MULTI-CHANNEL SWITCHES

The SM8001 and SM8002 base units house the 1xN and 2xN multi-channel switches. They each hold up to four optical switch modules. Each switch module can be either a 1xN (where N ranges from 1 to 32) or a 2xN (where N ranges from 2 to 30). The SM8001 is a single-slot base unit, or platform, while the SM8002 is a double-slot base unit.

#### **Configurations**

The following configurations are available for the SM8001 and SM8002:

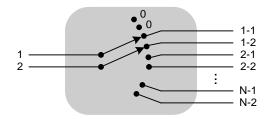

SM8001 and SM8002 - Multi-channel Switches: 1 x N

Duplex 1 x N 2 x N Blocking 2 x N Non-Blocking

The total number of available connectors per base unit is:

SM8001 Single-Slot, Multi-channel Base Unit: 12 ST connectors

16 SC connectors 12 FC connectors

SM8002 Double-slot, Multi-channel Base Unit: 24 ST connectors

32 SC connectors 24 FC connectors

FIGURE 1-2: SM8001 / 8002 SWITCHES

## SM8001 / SM8002 MULTI SWITCH SPECIFICATIONS

| GENERAL SPECIFICATIONS         |                                       |

|--------------------------------|---------------------------------------|

| WAVELENGTH RANGE               |                                       |

|                                | 780 – 1650 nm                         |

| INSERTION LOSS <sup>2</sup>    |                                       |

|                                | 0.6 dB typical, 1.2 dB maximum        |

| BACK REFLECTION                |                                       |

| Single-Mode Fiber <sup>3</sup> | -60 dB typical, - 55 dB maximum       |

| Multi-Mode Fiber <sup>3</sup>  | -20 dB typical                        |

| SWITCHING TIME <sup>4</sup>    |                                       |

|                                | 300 ms + 16 ms per channel maximum    |

| ISOLATION                      |                                       |

|                                | -80 dB maximum                        |

| DURABILITY                     |                                       |

|                                | 10 million cycles minimum             |

| REPEATABILITY <sup>5</sup>     |                                       |

|                                | ±0.03 dB maximum                      |

| PDL <sup>6</sup>               |                                       |

|                                | 0.05 dB maximum                       |

| OPERATING TEMPERATURE          |                                       |

|                                | 0°C – 50°C                            |

| STORAGE TEMPERATURE            |                                       |

|                                | -20°C – 70°C                          |

| HUMIDITY                       |                                       |

|                                | 40°C / 90% Relative Humidity / 5 days |

|                                | · · · · · · · · · · · · · · · · · · · |

| No | otes                                                                           |

|----|--------------------------------------------------------------------------------|

| 1  | All specifications referenced without connectors.                              |

| 2  | Measured at $23^{\circ}C \pm 5^{\circ}C$ .                                     |

| 3  | Based on standard 1-meter pigtail length.                                      |

| 4  | Based on BUSY output pulse. Actual optical switching time may be faster.       |

| 5  | Sequential repeatability for 100 cycles at constant temperature after warm-up. |

| 6  | Measured at 1550 nm, single-mode only.                                         |

#### **SM8003 - PRISM SWITCHES**

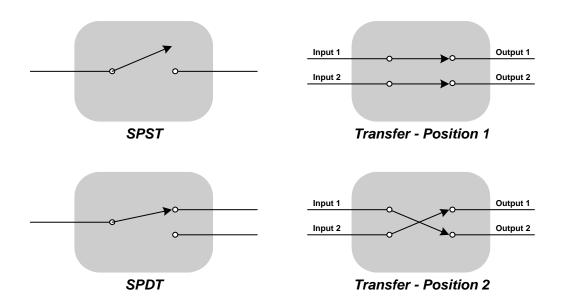

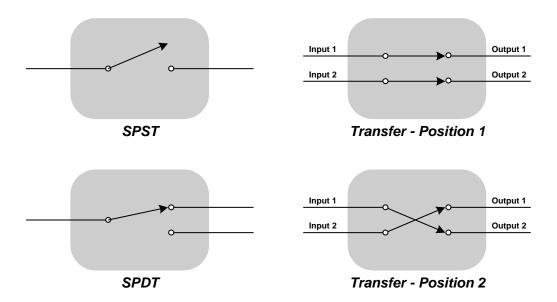

The SM8003 is a single-slot Prism switch base unit. SPST, SPDT and Transfer switches can be mixed and matched within the same SM8003 base unit.

#### **Configurations**

The following configurations are available for the SM8003:

SM8003 - Prism Switches: SPST

SPDT Transfer

The total number of available connectors per base unit is:

SM8003 Single-slot, Prism Switch Base Unit: 12 ST connectors

12 FC connectors

16 SC connectors (Transfer switches only)

FIGURE 1-3: 8003 PRISM SWITCHES

# SM8003 PRISM SWITCH SPECIFICATIONS

| GENERAL SPECIFICATIONS      |                                        |

|-----------------------------|----------------------------------------|

| WAVELENGTH RANGE            |                                        |

|                             | 780 – 1570 nm                          |

| Insertion Loss <sup>2</sup> |                                        |

|                             | 0.6 dB typical, 1.1 dB maximum         |

| BACK REFLECTION             |                                        |

| Single-Mode                 | - 55 dB maximum                        |

| Multi-Mode                  | -20 dB typical                         |

| CROSS-TALK                  |                                        |

|                             | -80 dB maximum                         |

| DURABILITY                  |                                        |

|                             | 10 million cycles minimum              |

| REPEATABILITY <sup>2</sup>  |                                        |

|                             | ±0.01 dB maximum                       |

| PDL <sup>3</sup>            |                                        |

|                             | 0.05 dB maximum                        |

| OPERATING TEMPERATURE       |                                        |

|                             | -20°C – 75°C                           |

| STORAGE TEMPERATURE         |                                        |

|                             | -40°C – 85°C                           |

| HUMIDITY                    |                                        |

|                             | 60°C / 90% Relative Humidity / 14 days |

# Notes 1 All specifications referenced without connectors. 2 Repeatability for 100 cycles at constant temperature. 3 Measured at 1550 nm, single-mode only.

#### SM8101 / SM8102 - OPTICAL ATTENUATORS

The SM8101 and SM8102 are single-slot VXIbus modules. The SM8101 is a single-channel variable attenuator, and the SM8102 is a two-channel variable attenuator.

#### SM8101/SM8102 SPECIFICATIONS

| ATTENUATOR                            |                                          |                       |            |  |  |  |  |  |  |

|---------------------------------------|------------------------------------------|-----------------------|------------|--|--|--|--|--|--|

| ATTENUATION RANGE <sup>2</sup>        | 0 – 10 dB                                | 11 – 30 dB            | 31 – 60 dB |  |  |  |  |  |  |

| Resolution                            | 0.10 dB                                  | 0.12 dB               | 0.15 dB    |  |  |  |  |  |  |

| Repeatability                         | ±0.05 dB                                 | ±0.10 dB              | ±0.10 dB   |  |  |  |  |  |  |

| Absolute Accuracy                     | $\pm 0.10 \text{ dB}$                    | $\pm 0.20 \text{ dB}$ | ±0.25 dB   |  |  |  |  |  |  |

| PDL <sup>3</sup>                      | 0.08 dB                                  | 0.10 dB               | 0.30 dB    |  |  |  |  |  |  |

| INSERTION LOSS                        |                                          |                       |            |  |  |  |  |  |  |

|                                       | 0.6 dB typical,                          | 1.5 dB maximum        |            |  |  |  |  |  |  |

| BACK REFLECTION                       |                                          |                       |            |  |  |  |  |  |  |

|                                       | -50 dB maximum                           |                       |            |  |  |  |  |  |  |

| TURNING SPEED                         |                                          |                       |            |  |  |  |  |  |  |

|                                       | 50 ms minimum                            | n, 1400 ms maximun    | 1          |  |  |  |  |  |  |

| DAMAGE THRESHOLD                      |                                          |                       |            |  |  |  |  |  |  |

|                                       | 24 dBm maxim                             | num                   |            |  |  |  |  |  |  |

| OPERATING TEMPERATURE                 |                                          |                       |            |  |  |  |  |  |  |

|                                       | $0^{\circ}\text{C} - 50^{\circ}\text{C}$ |                       |            |  |  |  |  |  |  |

| STORAGE TEMPERATURE                   |                                          |                       |            |  |  |  |  |  |  |

|                                       | -20°C − 70°C                             |                       |            |  |  |  |  |  |  |

| HUMIDITY                              |                                          |                       |            |  |  |  |  |  |  |

|                                       | 40°C / 90% Re                            | lative Humidity / 5 d | ays        |  |  |  |  |  |  |

| 10 C / 7070 Remarks Humberty / 5 days |                                          |                       |            |  |  |  |  |  |  |

#### <u>Notes</u>

- 1 All specifications referenced without connectors.

- 2 Maximum attenuation for multi-mode components is 40 dB.

- 3 Measured at 1550 nm, single-mode only.

# **SECTION 2**

# PREPARATION FOR USE

#### Introduction

When the SMIP II is unpacked from its shipping carton, the contents should include the following items:

- (1) SMIP II VXIbus module

- (1) SM8000 Series Optical Switch User's Manual (this manual)

All components should be immediately inspected for damage upon receipt of the unit.

Once the SMIP II is assessed to be in good condition, it may be installed into an appropriate C-size or D-size VXIbus chassis in any slot other than slot zero. The chassis should be checked to ensure that it is capable of providing adequate power and cooling for the SMIP II. Once the chassis is found adequate, the SMIP's logical address and the chassis' backplane jumpers should be configured prior to the SMIP's installation.

#### CALCULATING SYSTEM POWER AND COOLING REQUIREMENTS

It is imperative that the chassis provide adequate power and cooling for this module. Referring to the chassis user's manual, confirm that the power budget for the system (the chassis and all modules installed therein) is not exceeded and that the cooling system can provide adequate airflow at the specified backpressure.

It should be noted that if the chassis cannot provide adequate power to the module, the instrument may not perform to specification or possibly not operate at all. In addition, if adequate cooling is not provided, the reliability of the instrument will be jeopardized and permanent damage may occur. Damage found to have occurred due to inadequate cooling would also void the warranty of the module.

#### SETTING THE CHASSIS BACKPLANE JUMPERS

Please refer to the chassis operation manual for further details on setting the backplane jumpers.

#### **SETTING THE LOGICAL ADDRESS**

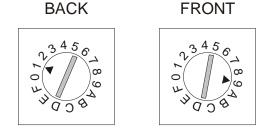

The logical address of the SMIP II is set by two rotary switches located on the top edge of the interface card, near the backplane connectors. Each switch is labeled with positions 0 through F. The switch closer to the front panel of the module is the least significant bit (LSB or "Front"), and the switch located towards the back of the module is the most significant bit (MSB or "Back"). To set the Logical Address (LA), simply rotate the pointer to the desired value. For example, to set the LA to 25, first convert the decimal number to the hexadecimal value of 19. Next, set the back switch to 1, and the front switch to 9. Two examples are provided below:

#### Example 1

| LA<br>(decimal) | Divide<br>by 16 |   | MSB  | LSB            |                                                                             |

|-----------------|-----------------|---|------|----------------|-----------------------------------------------------------------------------|

| 25              | 25 / 16         | = | 1    | w/ 9 remaining | Divide the decimal value by 16 to get the MSB and the LSB.                  |

|                 |                 | = | 0001 | 1001           | The 1 is the MSB, and the remainder of 9 is the LSB.                        |

|                 |                 | = | 1    | 9              | Convert to hexadecimal. Set the back switch to 1 and the front switch to 9. |

FIGURE 2-1: LOGICAL ADDRESS EXAMPLE 1

#### Example 2

| LA<br>(decimal) | Divide<br>by 16 |   | MSB  | LSB           |                                                                             |

|-----------------|-----------------|---|------|---------------|-----------------------------------------------------------------------------|

| 200             | 200 / 16        | = | 12   | w/8 remaining | Divide by 16.                                                               |

|                 |                 | = | 1100 | 1000          | Convert to MSB and LSB.                                                     |

|                 |                 | = | C    | 8             | Convert to hexadecimal. Set the back switch to C and the front switch to 8. |

|                 |                 |   | BAC  | K             | FRONT                                                                       |

|                 |                 |   | 2345 | 7 8 9         | 73456                                                                       |

FIGURE 2-2: LOGICAL ADDRESS EXAMPLE 2

Here is another way of looking at the conversion:  $LA = (back \ switch \ x \ 16) + front \ switch$

$LA = (1 \times 16) + 9$  LA = 16 + 9LA = 25

Set the address switches to **FF** for dynamic configuration. Upon power-up, the resource manager will assign a logical address. See Section F - Dynamic Configuration in the *VXIbus Specification* for further information.

There is only one logical address per SMIP II base unit. Address assignments for individual modules are handled through the A24/A32 address space allocation.

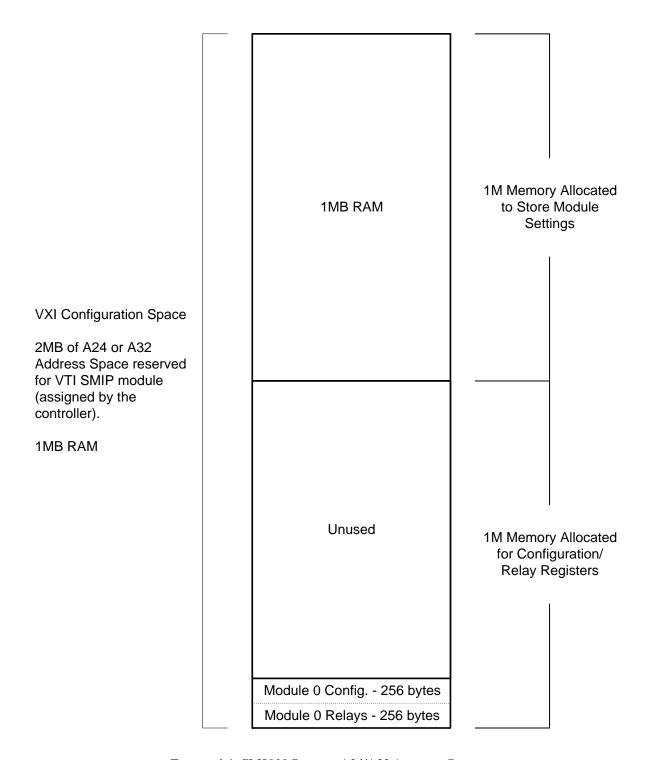

#### SELECTING THE EXTENDED MEMORY SPACE

The Extended Memory Space of the SMIP *II* is set by a dip-switch that is located on the bottom edge of the interface card. Position 1, located to the left on the dip-switch, selects between A24 and A32 memory address space. In the UP position, the SMIP *II* will request A24 space. In the DOWN position, the SMIP *II* will request A32 space. (Position 2 is not currently used.) The selection of the address space should be based upon the memory allocation requirements of the system that the SMIP *II* module will be installed. The amount of memory allocated to the SMIP *II* module is independent of the address space selected.

#### **OPTICAL CONNECTIONS**

The SM8000 series are all shipped with dust caps over each optical connector. These dust caps should remain in place at all times while the instrument is not in use.

#### **Cleaning Optical Connectors**

- 1. Clean both connectors to remove any dirt or particles, which could decrease performance or permanently damage the connector.

- a) Using high-grade isopropyl alcohol (or equivalent) dampen a cotton swab and shake off any excess alcohol before cleaning. The cotton swab should be moist but not wet.

- b) Gently clean the surface of the connector and around the connector ferrule.

- c) Allow the connectors to dry for at least one minute.

Service should only be performed by qualified personnel.

#### **Mating Optical Connectors**

- Smoothly insert the appropriate connector ferrule into the adapter taking caution not to allow the fiber tip to make contact with any surface. If this happens, re-clean the connector and start again.

- Tighten the connector finger-tight; do not over-tighten. If the loss is unacceptable, remove the connector, re-clean both connectors and start again. These steps may need to be repeated several times before a low-loss connection is made.

- 3. After the connection is made, monitor the stability of the optical throughput for a few minutes until stable. If the loss is unacceptable, re-clean the connectors and start again.

# **SECTION 3**

# **OPERATION**

#### **GENERAL DESCRIPTION**

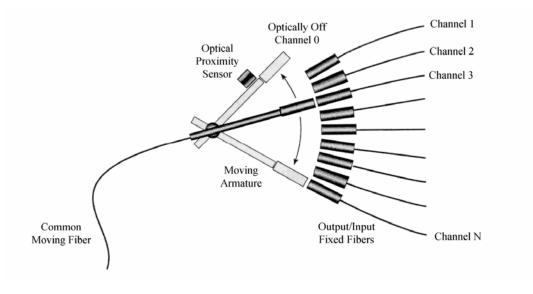

#### SM8001 / SM8002 - Multi-Channel Switches

The multi-channel optical switches are optical-mechanical switches that allow selection of an individual fiber channel by means of a high-resolution stepper motor. The stepper motor moves the common fiber into direct alignment with the output fiber. The switch module is optically passive, operating independently of data rate, data format, and optical signal direction.

FIGURE 3-1: MULTI-CHANNEL SWITCH - INTERNAL COMPONENTS

SM8000 Series Operation 25

#### SM8003 - Prism Switches

The SPST switch provides channel control from one input fiber to one output fiber using a moving shutter between fixed collimators.

The SPDT switch provides channel selection from one input fiber to two output fibers using a moving prism between fixed collimators.

The Transfer switch provides channel selection from two input fibers to two output fibers using a moving prism between fixed collimators.

The prism switches are actuated electrically and they operate independently of data rate and signal format.

FIGURE 3-2: SM8003 PRISM SWITCHES

#### SM8101 / SM8102 - Optical Attenuators

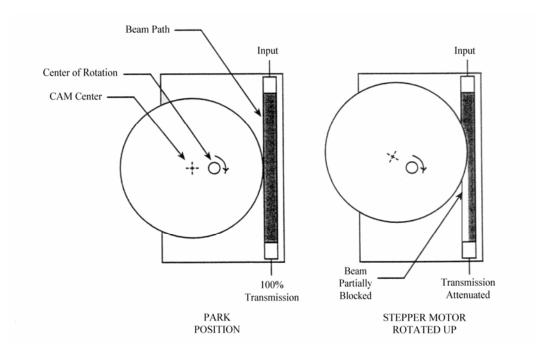

The Optical Attenuators are based on precise-resolution stepper motors, which mechanically position a beam block. See Figure 3-3 for the basic concepts.

The attenuator stepper motor is attached to an off-axis cam. A pair of fiber collimators is positioned on either side of the cam, with a short open-air beam path between them. As the motor rotates, the cam is driven slowly into the beam path, attenuating the beam. See Figure 3-2.

When the cam is fully rotated out of the beam path, the attenuator is in park, or reset position. When in park position, the loss is limited to the intrinsic loss of the two collimators and the air gap, known as Insertion or Residual loss.

As the cam rotates into the beam path, attenuation increases. The relationship between motor step position and attenuation is not linear. The incremental increases in attenuation per motor step are very small at first. In the low range (0 dB to 5 dB), the incremental attenuation per step is approximately 0.05 dB. In the high range (50 dB to 60 dB), attenuation increases much more quickly at approximately 0.25 dB per step.

FIGURE 3-3: ATTENUATOR DIAGRAM

#### **OPERATION**

#### SM8001 / SM8002 - Multi-Channel Switches

When controlling multi-switch modules, the operation is quite similar to that of any other SMIP *II* family product, but the data sent is operated on a little bit differently. The SM8000 must be configured to control the multi-switch device on one of four ports. This is done at the factory with hardware selectable jumpers. Once configured for multi-switch operation, the control of the switch is accomplished by writing to the appropriate Relay Register. Relay registers 02 through 08 are used to control the multi-switch modules. The value written to the multi-switch module is dependent on the type/size of the switch.

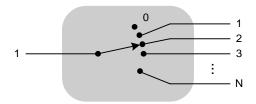

For example, if the switch is a 1xN switch, writing the value of **00h** to Relay Register 02 would optically connect the switches input to the first output. A write of **0Ah** would connect the input to the 11<sup>th</sup> output, and so on. Data lines 4 through 0 are used to transfer data to the switch modules.

The Busy signal from the optical module may be monitored to indicate when the optical module has completed moving to the commanded switch setting. The optical module also generates an Error signal that may be monitored. This signal might be used to provide a confidence check that the module is being controlled properly.

#### Resetting the Switch

When the switch is in reset (park) position, channel zero, or optical off, there is no optical connection to any output channel. Set the switch to the reset position to prevent optical data from passing through the switch, or to reset the stepper motor. During a reset operation, optical noise may appear on various output channels as the armature rotates.

There are two ways to reset the switch. The first is to cycle power to return the switch to the reset position. The second is to return the switch to the reset position using a sequence of writes to the SMIP module rather than interrupting the supply power. See the example of a multi-switch reset write sequence as described later in this manual. The BUSY output remains high until the reset operation is complete and the device is ready to receive additional instructions.

#### Relay Registers - Output Channel Selection

The following sections show information to select channels for the SM8001/8002 through the relay registers. Each configuration section includes an optical input/output relation figure, followed by a table that lists the control codes for channel selection.

# 1 x N Switch Configuration

FIGURE 3-4: 1 x N SWITCH CONFIGURATION

TABLE 3-1: CONTROL CODES FOR 1XN CONFIGURATION

| RESET* | D4 | D3 | D2 | D1 | <b>D</b> 0 | Active Channel |

|--------|----|----|----|----|------------|----------------|

| 0      | X  | X  | X  | X  | X          | 0 reset        |

| 1      | 0  | 0  | 0  | 0  | 0          | 1              |

| 1      | 0  | 0  | 0  | 0  | 1          | 2              |

| 1      | 0  | 0  | 0  | 1  | 0          | 3              |

| 1      | 0  | 0  | 0  | 1  | 1          | 4              |

| 1      | 0  | 0  | 1  | 0  | 0          | 5              |

| 1      | 0  | 0  | 1  | 0  | 1          | 6              |

| 1      | 0  | 0  | 1  | 1  | 0          | 7              |

| 1      | 0  | 0  | 1  | 1  | 1          | 8              |

| 1      | 0  | 1  | 0  | 0  | 0          | 9              |

| 1      | 0  | 1  | 0  | 0  | 1          | 10             |

| 1      | 0  | 1  | 0  | 1  | 0          | 11             |

| 1      | 0  | 1  | 0  | 1  | 1          | 12             |

| 1      | 0  | 1  | 1  | 0  | 0          | 13             |

| 1      | 0  | 1  | 1  | 0  | 1          | 14             |

| 1      | 0  | 1  | 1  | 1  | 0          | 15             |

| 1      | 0  | 1  | 1  | 1  | 1          | 16             |

| 1      | 1  | 0  | 0  | 0  | 0          | 17             |

| 1      | 1  | 0  | 0  | 0  | 1          | 18             |

| 1      | 1  | 0  | 0  | 1  | 0          | 19             |

| 1      | 1  | 0  | 0  | 1  | 1          | 20             |

| 1      | 1  | 0  | 1  | 0  | 0          | 21             |

| 1      | 1  | 0  | 1  | 0  | 1          | 22             |

| 1      | 1  | 0  | 1  | 1  | 0          | 23             |

| 1      | 1  | 0  | 1  | 1  | 1          | 24             |

| 1      | 1  | 1  | 0  | 0  | 0          | 25             |

| 1      | 1  | 1  | 0  | 0  | 1          | 26             |

| 1      | 1  | 1  | 0  | 1  | 0          | 27             |

| 1      | 1  | 1  | 0  | 1  | 1          | 28             |

| 1      | 1  | 1  | 1  | 0  | 0          | 29             |

| 1      | 1  | 1  | 1  | 0  | 1          | 30             |

| 1      | 1  | 1  | 1  | 1  | 0          | 31             |

| 1      | 1  | 1  | 1  | 1  | 1          | 32             |

SM8000 Series Operation 29

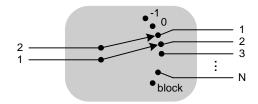

Duplex 1 x N Switch Configuration

FIGURE 3-5: DUPLEX 1 x N SWITCH CONFIGURATION

TABLE 3-2: CONTROL CODES FOR DUPLEX 1 x N CONFIGURATION

| RESET* | D4 | D3 | D2 | D1 | D0 | Common 1 Active Channel | Common 2 Active Channel |

|--------|----|----|----|----|----|-------------------------|-------------------------|

| 0      | X  | X  | X  | X  | X  | 0 reset                 | 0 reset                 |

| 1      | 0  | 0  | 0  | 0  | 0  | 1-1                     | 1-2                     |

| 1      | 0  | 0  | 0  | 0  | 1  | 2-1                     | 2-2                     |

| 1      | 0  | 0  | 0  | 1  | 0  | 3-1                     | 3-2                     |

| 1      | 0  | 0  | 0  | 1  | 1  | 4-1                     | 4-2                     |

| 1      | 0  | 0  | 1  | 0  | 0  | 5-1                     | 5-2                     |

| 1      | 0  | 0  | 1  | 0  | 1  | 6-1                     | 6-2                     |

| 1      | 0  | 0  | 1  | 1  | 0  | 7-1                     | 7-2                     |

| 1      | 0  | 0  | 1  | 1  | 1  | 8-1                     | 8-2                     |

| 1      | 0  | 1  | 0  | 0  | 0  | 9-1                     | 9-2                     |

| 1      | 0  | 1  | 0  | 0  | 1  | 10-1                    | 10-2                    |

| 1      | 0  | 1  | 0  | 1  | 0  | 11-1                    | 11-2                    |

| 1      | 0  | 1  | 0  | 1  | 1  | 12-1                    | 12-2                    |

| 1      | 0  | 1  | 1  | 0  | 0  | 13-1                    | 13-2                    |

| 1      | 0  | 1  | 1  | 0  | 1  | 14-1                    | 14-2                    |

| 1      | 0  | 1  | 1  | 1  | 0  | 15-1                    | 15-2                    |

| 1      | 0  | 1  | 1  | 1  | 1  | 16-1                    | 16-2                    |

| 1      | 1  | 0  | 0  | 0  | 0  | 17-1                    | 17-2                    |

| 1      | 1  | 0  | 0  | 0  | 1  | 18-1                    | 18-2                    |

| 1      | 1  | 0  | 0  | 1  | 0  | 19-1                    | 19-2                    |

| 1      | 1  | 0  | 0  | 1  | 1  | 20-1                    | 20-2                    |

| 1      | 1  | 0  | 1  | 0  | 0  | 21-1                    | 21-2                    |

| 1      | 1  | 0  | 1  | 0  | 1  | 22-1                    | 22-2                    |

| 1      | 1  | 0  | 1  | 1  | 0  | 23-1                    | 23-2                    |

| 1      | 1  | 0  | 1  | 1  | 1  | 24-1                    | 24-2                    |

| 1      | 1  | 1  | 0  | 0  | 0  | 25-1                    | 25-2                    |

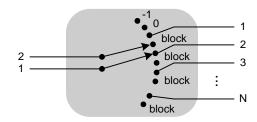

## 2 x N Blocking Switch Configuration

FIGURE 3-62 X N BLOCKING SWITCH CONFIGURATION

TABLE 3-3: CONTROL CODES FOR 2 X N BLOCKING CONFIGURATION

| RESET* | D4 | D3 | D2 | D1 | D0 | Common 1 Output Channel | Common 2<br>Output Channel |

|--------|----|----|----|----|----|-------------------------|----------------------------|

| 0      | X  | X  | X  | X  | X  | 0 reset                 | -1 reset                   |

| 1      | 0  | 0  | 0  | 0  | 0  | 1                       | 0 block                    |

| 1      | 0  | 0  | 0  | 0  | 1  | block                   | 1                          |

| 1      | 0  | 0  | 0  | 1  | 0  | 2                       | block                      |

| 1      | 0  | 0  | 0  | 1  | 1  | block                   | 2                          |

| 1      | 0  | 0  | 1  | 0  | 0  | 3                       | block                      |

| 1      | 0  | 0  | 1  | 0  | 1  | block                   | 3                          |

| 1      | 0  | 0  | 1  | 1  | 0  | 4                       | block                      |

| 1      | 0  | 0  | 1  | 1  | 1  | block                   | 4                          |

| 1      | 0  | 1  | 0  | 0  | 0  | 5                       | block                      |

| 1      | 0  | 1  | 0  | 0  | 1  | block                   | 5                          |

| 1      | 0  | 1  | 0  | 1  | 0  | 6                       | block                      |

| 1      | 0  | 1  | 0  | 1  | 1  | block                   | 6                          |

| 1      | 0  | 1  | 1  | 0  | 0  | 7                       | block                      |

| 1      | 0  | 1  | 1  | 0  | 1  | block                   | 7                          |

| 1      | 0  | 1  | 1  | 1  | 0  | 8                       | block                      |

| 1      | 0  | 1  | 1  | 1  | 1  | block                   | 8                          |

| 1      | 1  | 0  | 0  | 0  | 0  | 9                       | block                      |

| 1      | 1  | 0  | 0  | 0  | 1  | block                   | 9                          |

| 1      | 1  | 0  | 0  | 1  | 0  | 10                      | block                      |

| 1      | 1  | 0  | 0  | 1  | 1  | block                   | 10                         |

| 1      | 1  | 0  | 1  | 0  | 0  | 11                      | block                      |

| 1      | 1  | 0  | 1  | 0  | 1  | block                   | 11                         |

| 1      | 1  | 0  | 1  | 1  | 0  | 12                      | block                      |

| 1      | 1  | 0  | 1  | 1  | 1  | block                   | 12                         |

| 1      | 1  | 1  | 0  | 0  | 0  | 13                      | block                      |

| 1      | 1  | 1  | 0  | 0  | 1  | block                   | 13                         |

| 1      | 1  | 1  | 0  | 1  | 0  | 14                      | block                      |

| 1      | 1  | 1  | 0  | 1  | 1  | block                   | 14                         |

| 1      | 1  | 1  | 1  | 0  | 0  | 15                      | block                      |

| 1      | 1  | 1  | 1  | 0  | 1  | block                   | 15                         |

| 1      | 1  | 1  | 1  | 1  | 0  | 16                      | block                      |

| 1      | 1  | 1  | 1  | 1  | 1  | block                   | 16                         |

# 2 x N Non-Blocking Switch Configuration

FIGURE 3-7: 2 x N Non-Blocking Switch Configuration

TABLE 3-4: CONTROL CODES FOR 2 X N NON-BLOCKING CONFIGURATION

| RESET* | D4 | D3 | D2 | D1 | <b>D</b> 0 | Common 1 Active Channel | Common 2 Active Channel |

|--------|----|----|----|----|------------|-------------------------|-------------------------|

| 0      | X  | X  | X  | X  | X          | 0 reset                 | -1 reset                |

| 1      | 0  | 0  | 0  | 0  | 0          | 1                       | 0 block                 |

| 1      | 0  | 0  | 0  | 0  | 1          | 2                       | 1                       |

| 1      | 0  | 0  | 0  | 1  | 0          | 3                       | 2                       |

| 1      | 0  | 0  | 0  | 1  | 1          | 4                       | 3                       |

| 1      | 0  | 0  | 1  | 0  | 0          | 5                       | 4                       |

| 1      | 0  | 0  | 1  | 0  | 1          | 6                       | 5                       |

| 1      | 0  | 0  | 1  | 1  | 0          | 7                       | 6                       |

| 1      | 0  | 0  | 1  | 1  | 1          | 8                       | 7                       |

| 1      | 0  | 1  | 0  | 0  | 0          | 9                       | 8                       |

| 1      | 0  | 1  | 0  | 0  | 1          | 10                      | 9                       |

| 1      | 0  | 1  | 0  | 1  | 0          | 11                      | 10                      |

| 1      | 0  | 1  | 0  | 1  | 1          | 12                      | 11                      |

| 1      | 0  | 1  | 1  | 0  | 0          | 13                      | 12                      |

| 1      | 0  | 1  | 1  | 0  | 1          | 14                      | 13                      |

| 1      | 0  | 1  | 1  | 1  | 0          | 15                      | 14                      |

| 1      | 0  | 1  | 1  | 1  | 1          | 16                      | 15                      |

| 1      | 1  | 0  | 0  | 0  | 0          | 17                      | 16                      |

| 1      | 1  | 0  | 0  | 0  | 1          | 18                      | 17                      |

| 1      | 1  | 0  | 0  | 1  | 0          | 19                      | 18                      |

| 1      | 1  | 0  | 0  | 1  | 1          | 20                      | 19                      |

| 1      | 1  | 0  | 1  | 0  | 0          | 21                      | 20                      |

| 1      | 1  | 0  | 1  | 0  | 1          | 22                      | 21                      |

| 1      | 1  | 0  | 1  | 1  | 0          | 23                      | 22                      |

| 1      | 1  | 0  | 1  | 1  | 1          | 24                      | 23                      |

| 1      | 1  | 1  | 0  | 0  | 0          | 25                      | 24                      |

| 1      | 1  | 1  | 0  | 0  | 1          | 26                      | 25                      |

| 1      | 1  | 1  | 0  | 1  | 0          | 27                      | 26                      |

| 1      | 1  | 1  | 0  | 1  | 1          | 28                      | 27                      |

| 1      | 1  | 1  | 1  | 0  | 0          | 29                      | 28                      |

| 1      | 1  | 1  | 1  | 0  | 1          | 30                      | 29                      |

| 1      | 1  | 1  | 1  | 1  | 0          | 31                      | 30                      |

| 1      | 1  | 1  | 1  | 1  | 1          | block <sup>a</sup>      | 31                      |

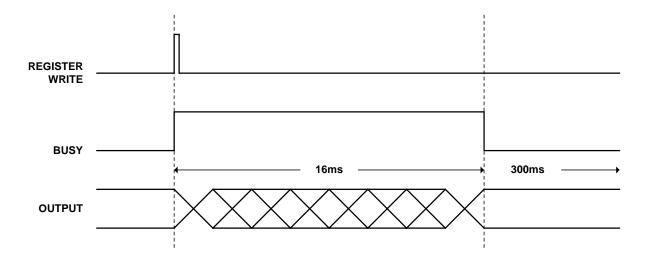

FIGURE 3-8: MULTI-SWITCH TIMING

#### Calculating Switching Time

The time-period for switching a channel can be divided into three constituent periods. The first time-period ends when the BUSY signal goes high. For calculating switching time, however, only the last two periods are used.

The second time-period starts when BUSY goes high and the switch armature begins to move. There is a 16 ms period until the armature reaches the specified output channel. There is a 16 ms period for each switched channel, including duplex and blocked channels. During this period, optical output is invalid; optical noise may appear on various output channels as the armature rotates.

The third time-period is called the debounce period. It ends when the armature is steady, the switch has established a valid optical connection, and BUSY goes low. The debounce period lasts for 300 ms.

Switching time is the sum of the second and third time-periods. For example:

Switch from Channel 15 to Channel 1 (1 x N Configuration) Switches through 14 channels  $(14 \times 16 \text{ ms}) + 300 \text{ ms} = 524 \text{ ms}$

Switch from Channel 2 to Channel 6 (2 x N Blocking Configuration) Switches through 2 x 4 (8) channels  $(8 \times 16 \text{ ms}) + 300 \text{ ms} = 428 \text{ ms}$

#### SM8003 - Prism Switches

When controlling single mode prism switches the operation of the SM8000 is also similar to that of any other SMIP *II* family product. The switches are directly controlled by register writes to the Relay Register. See *Writing to the Relay Register* in the Programming section for a detailed explanation of this type of operation. Only relay register 00h is used to control the prism switches.

#### SM8101 / SM8102 - Optical Attenuators

The attenuator modules are internally controlled via an I<sup>2</sup>C bus interface. Operation of this type of module is accomplished by loading the proper command and attenuator data information into the proper registers inside the SM8000.

The SM8000 must be configured to control the attenuator modules on one of four ports. These same ports are used for the multi-switch devices. This is done at the factory with hardware selectable jumpers. Once configured for attenuator module operation, the control of the attenuator module consists of writing the control word and the attenuator data word to the SM8000. This operation is more fully discussed in the Programming section of this manual.

Once the Relay Register (02 through 08) has been configured to control an attenuator, and has been written to, the command sequence is initiated and the module begins to move to the newly commanded setting. The Busy signal from the optical module may be monitored to indicate when the optical module has finished moving to the commanded attenuation. The optical module also generates an Error signal that may be monitored. This signal might be used to provide a confidence check that the module is being controlled properly.

#### Starting the Device

The device resets upon application of power. The Optical Attenuators park at the minimum-loss position.

#### Control Modes

The Optical Attenuators can be operated in two modes: uncalibrated and calibrated. The uncalibrated mode is called Move-To-Absolute-Step mode. In this mode, the user sends movement requests to the internal stepping motor through the Move-To-Absolute-Step interface. The internal stepping motor responds by moving one step up, or one step down as requested. In this mode, there is no conversion of step number to absolute attenuation.

Move-To-Absolute-Step is the simplest mode of operation. This method of operation is typically used when devices are used in a feedback loop to maintain a particular attenuation regardless of absolute position.

The calibrated, absolute conversion mode of operation sends absolute attenuation requests to the Optical Attenuator. The circuitry then translates the commanded absolute request into a motor-step position and rotates the motor accordingly. This method of operation is typically used when the devices are used to calibrate other devices, or to set absolute references within a system.

Both modes of operation are described in detail in the following sections.

#### Uncalibrated Operation - Move-To-Absolute-Step

The motorized Optical Attenuators are all based on stepping motor technology. The easiest method of using these devices is to simply command the motor to step in one direction, or the other. For our purposes, stepping will increase attenuation, while stepping down will decrease attenuation.

To utilize this mode of operation, simply command the Optical Attenuator to Move-To-Absolute-Step. See the Attenuator Command Set in the *Programming* section.

#### Calibrated Operation

The Optical Attenuators are all based on stepping motor technology. Operating in the calibrated mode requires use of the I<sup>2</sup>C interface on the optical modules.

The I<sup>2</sup>C interface is a linearized controller, allowing users to select for the attenuator, he absolute attenuation in dB.

It is also possible to command uncalibrated step movements while operating in calibrated mode. Note that following an uncalibrated step, a Query Attenuation command will return invalid data. A subsequent calibrated movement will restore query command validity.

#### **BUSY Signal**

The BUSY bit is driven high by the device whenever a Set Attenuation command is received, or when a RESET signal is received. The BUSY signal remains high whenever a command is executed and the stepper motor is moving. During this time, no other commands should be sent to the device, as this may corrupt the internal state of the device requiring a RESET to clear.

#### **ERROR Status**

The ERROR bit is driven high by the device whenever an Out of Range error, or a RESET error is detected. RESET errors occur when the unit does not find its Park position correctly, and may indicate a hardware problem.

#### Resetting the Device

See the RESET commands in the Programming section.

#### Commanding the Devices

#### Step 1 - Power Up and Initialize

The device will reset when power is applied.

#### **Step 2 - Query Default Parameters**

Before using the device in calibrated mode, query to obtain the minimum and maximum absolute attenuation. Use this data to ensure that commands sent are always within range. The commands to gather the device information are:

- Query Minimum Attenuation 82h

- Query Maximum Attenuation 83h

#### Step 3 - Actuate the Device

Use the appropriate Set commands and actuate the device. For verification purposes, pick a large change first to ensure proper operation of the device. Very small changes can be requested, however, they can be misleading for test purposes since they are practically undetectable. The command to actuate the device is:

• Set Attenuation - 80h

# **SECTION 4**

## **PROGRAMMING**

#### **REGISTER ACCESS**

The SMIP *II* optical modules are VXIbus register-based devices. Register-based programming is a series of **reads** and **writes** directly to the switch module registers. This eliminates the time for command parsing thus increasing speed.

#### **ADDRESSING**

The VTI switching modules utilize either the A24 or A32 space of the shared-memory architecture. To read or write to a module register, a register address needs to be specified. This is done by using the offset value (assigned by the resource manager) and multiplying it by 256 or 64 k to get the base address in A24 or A32 address space, respectively

A24 Base Address = Offset value \* 0x00FF (or 256)

A32 Base Address = Offset value \* 0xFFFF (or 65,535)

The A24 or A32 offset value, assigned by the resource manager, can also be accessed by reading the A16 Offset Register. To address the A16 Offset Register use the following formula:

A16 Base Address = (Logical Address \* 64) + 0xC000 (or 49,152)

then

A16 Offset Register Address = A16 Base Address + 6

See following for the A16 Memory Map and the A24/A32 address space allocation.

TABLE 4-1: SMIP II REGISTER MAP - A16

| OFFSET | WRITE FUNCTION                   | READ FUNCTION            |

|--------|----------------------------------|--------------------------|

| 3E     | Trace Advance                    | Board Busy               |

| 3C     | Busy Trigger Control             | Busy Trigger Control     |

| 3A     | Trace RAM Control                | Trace RAM Control        |

| 38     | TTL Trigger Polarity             | Reserved                 |

| 36     | Open Trigger Select              | Reserved                 |

| 34     | Trace ADV Trigger Select         | Reserved                 |

| 32     | Trace RAM Address LOW            | Trace RAM Address LOW    |

| 30     | Trace RAM Address HIGH           | Trace RAM Address HIGH   |

| 2E     | Trace RAM End LOW                | Trace RAM End LOW        |

| 2C     | Trace RAM End HIGH               | Trace RAM End HIGH       |

| 2A     | Trace RAM Start LOW              | Trace RAM Start LOW      |

| 28     | Trace RAM Start HIGH             | Trace RAM Start HIGH     |

| 26     | Module 5, 4 Used Address         | Module 5, 4 Used Address |

| 24     | Module 3, 2 Used Address         | Module 3, 2 Used Address |

| 22     | Module 1, 0 Used Address         | Module 1, 0 Used Address |

| 20     | NVM Access Register              | NVM Access Register      |

| 1E     | Reserved                         | Subclass Register        |

| 1C     | Interrupt Control                | Interrupt Control        |

| 1A     | Reserved Interrupt Status        |                          |

| 18     | Reserved                         | Reserved                 |

| 16     | Reserved                         | Reserved                 |

| 14     | Reserved                         | Reserved                 |

| 12     | Reserved                         | Reserved                 |

| 10     | Reserved                         | Reserved                 |

| Е      | Reserved                         | Version Number           |

| С      | Reserved                         | Serial Number LOW        |

| A      | Reserved                         | Serial Number HIGH       |

| 8      | Reserved                         | Reserved                 |

| 6      | Offset Register Offset Register  |                          |

| 4      | Control Register Status Register |                          |

| 2      | Reserved                         | Device Type Register     |

| 0      | LA Register                      | ID Register              |

### **SMIP II REGISTERS - A16**

The following describes the registers shown in the SMIP II Register Map for A16 address space.

| ID Register – Read Only |                   |                                                        |  |

|-------------------------|-------------------|--------------------------------------------------------|--|

| ADDR                    | Plug-In LA+0x00   |                                                        |  |

| D11-D0                  | Manufacturer's ID | VXI Technology, Inc., set to F4B <sub>16</sub>         |  |

| D13-D12                 | Address Space     | $A16/A24 = 00_2$ $A16/A32 = 01_2$                      |  |

| D15-D14                 | Device Class      | Extended register based device, set to 01 <sub>2</sub> |  |

| Logical Address Register – Write Only |                 |                                                                                                                                                                                                                                                  |

|---------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADDR                                  | Plug-In LA+0x00 |                                                                                                                                                                                                                                                  |

| D7-D0                                 | Logical Address | Sets the new logical address in a dynamically configured module. When set for dynamic configuration (set to $FF_{16}$ ) a soft reset will not alter the configured logical address, while a hard reset will set the register back to $FF_{16}$ . |

| D15-D8                                | Reserved        | Writing to this range has no effect.                                                                                                                                                                                                             |

| Device Type Register – Read Only |                 |                                                                                          |  |

|----------------------------------|-----------------|------------------------------------------------------------------------------------------|--|

| ADDR                             | Plug-In LA+0x02 |                                                                                          |  |

| D11-D0                           | Model Code      | Model 277, set to 115 <sub>16</sub>                                                      |  |

| D15-D12                          | Required Memory | 2 Mbytes, set to 2 <sub>16</sub> , for A24<br>2 Mbytes, set to A <sub>16</sub> , for A32 |  |

| Status Register – Read Only |                 |                                                                                                                                |

|-----------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------|

| ADDR                        | Plug-In LA+0x04 |                                                                                                                                |

| D15                         | A24/A32 Active  | 1 = indicates that A24/A32 memory space access is enabled<br>0 = indicates that A24/A32 memory space access is locked out      |

| D14                         | MODID*          | 1 = indicates that the module is not selected by the MODID line<br>0 = indicates that the module is selected by the MODID line |

| D13-D4                      | Reserved        | These bits always read as 11,1111,1111 <sub>2</sub>                                                                            |

| D3                          | Ready           | This bit always reads as 1 <sub>2</sub>                                                                                        |

| D2                          | Passed          | This bit always reads as 1 <sub>2</sub>                                                                                        |

| D1-D0                       | Reserved        | These bits always read as 11 <sub>2</sub>                                                                                      |

| Control Register – Write Only |                 |                                                                                                              |  |

|-------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------|--|

| ADDR                          | Plug-In LA+0x04 |                                                                                                              |  |

| D15                           | A24/A32 Enable  | 1 = write a 1 to this bit to enable A24/A32 memory access<br>0 = to disable access                           |  |

| D14-D2                        | Reserved        | Writes to these bits have no effect.                                                                         |  |

| D1                            | Sysfail Inhibit | Write a 1 to this bit to prevent the module from asserting the SYSFAIL* line.                                |  |

| D0                            | Reset           | 1 = write a 1 to this bit to force the module into a reset state<br>0 = write a 0 to release the reset state |  |

| Offset Register – Read and Write |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|----------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ADDR                             | Plug-In LA+0x06          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| D15-D0                           | A24/A32 Memory<br>Offset | The value written to this 16-bit register, times 256, sets the base address of the A24 memory space used by the module. The value written to this 16-bit register, times 65,536, sets the base address of the A32 memory space used by the module. A read from this register reflects the previously written value. Because of the required memory size, bits D4-D0 are disregarded on writes and always read back as 0s. Upon receiving a hard reset, all bits in this register are set to 0s. A soft reset does not effect the value in this register. The resource manager sets this register. |  |

| Serial Number High Register – Read Only |                 |                                        |  |

|-----------------------------------------|-----------------|----------------------------------------|--|

| ADDR                                    | Plug-In LA+0x0A |                                        |  |

| D15-D0                                  | Not Implemented | Always read back as FFFF <sub>16</sub> |  |

| Serial Number Low Register – Read Only |                 |                                        |  |

|----------------------------------------|-----------------|----------------------------------------|--|

| ADDR                                   | Plug-In LA+0x0C |                                        |  |

| D15-D0                                 | Not Implemented | Always read back as FFFF <sub>16</sub> |  |

| Version Number Register – Read Only |                                  |                                                                                  |  |

|-------------------------------------|----------------------------------|----------------------------------------------------------------------------------|--|

| ADDR                                | Plug-In LA+0x0E                  |                                                                                  |  |

| D15-D8                              | Firmware Version Number          | Not applicable, reads back as FF <sub>16</sub>                                   |  |

| D7-D4                               | Major Hardware<br>Version Number | Depends on the specific hardware revision of the SMIP <i>II</i> interface board. |  |

| D3-D0                               | Minor Hardware<br>Version Number | Depends on the specific hardware revision of the SMIP <i>II</i> interface board. |  |

| Interrupt Status Register – Read Only |                              |                                                                                                                                                                                                                  |

|---------------------------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADDR                                  | Plug-In LA+0x1A              |                                                                                                                                                                                                                  |

| D15                                   | Scan Function done           | The latest scan list update is complete.                                                                                                                                                                         |

| D14                                   | Openbus Active<br>Event true | The Openbus was activated by one or more programmed inputs.  See description of the Openbus in the module register section.                                                                                      |

| D13-D8                                | Modules 0-5 Busy complete    | D13 = Module 5, and D8 = Module 0.  The programmed Busy signal from one of the modules has timed out. This indicates that the relays actuated for that BUSY cycle have settled and a measurement may take place. |

| D7-D0                                 | Reserved                     | Always reads back as FFFF <sub>16</sub>                                                                                                                                                                          |

Note: This status register may be used in a polled fashion rather than allowing the events above to generate an Interrupt. A read of this register will clear any active bits. Bits that are not set, or are about to be set, are not affected by a read of this register.

| Interrupt Control Register – Read and Write                                                     |                                       |                                                                                                                                                                                                                                                                               |

|-------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADDR                                                                                            | Plug-In LA+0x1C                       |                                                                                                                                                                                                                                                                               |

| D15                                                                                             | Scan Function done mask bit           | 0 = enabled<br>1 = disabled                                                                                                                                                                                                                                                   |

| D14                                                                                             | Openbus Active<br>Event true mask bit | 0 = enabled<br>1 = disabled                                                                                                                                                                                                                                                   |

| D13-D8                                                                                          | Module 0-5 Busy complete              | 0 = enabled<br>1 = disabled<br>D13 = Module 5 and D8 = Module 0.                                                                                                                                                                                                              |

| D7                                                                                              | IR ENA*                               | 0 = writing a 0 to this bit enables interrupter capabilities<br>1 = writing a 1 to this bit disables interrupter capabilities                                                                                                                                                 |

| D6                                                                                              | IH ENA*                               | The module has no interrupt handler capability, therefore writing a 1 or 0 has no effect. A 1 is always read back for this bit.                                                                                                                                               |

| D5-D3                                                                                           | Interrupter IRQ<br>Line               | The complement of the value programmed into these three bits reflects the selected IRQ line used by the module. A value of 011 <sub>2</sub> would select IRQ4, a value of 000 <sub>2</sub> would select IRQ7, and a value of 111 <sub>2</sub> would disconnect the IRQ lines. |

| D2-D0                                                                                           | Handler IRQ Line                      | The module has no interrupt handler capability; therefore writing to these bits has no effect. A 111 <sub>2</sub> is always read back for these bits.                                                                                                                         |

| <b>Note:</b> That all bits in this register are set to 1s upon receipt of a hard or soft reset. |                                       |                                                                                                                                                                                                                                                                               |