## **Nios Embedded Processor**

Programmer's Reference Manual July 2001 Version 1.1.1

101 Innovation Drive San Jose, CA 95134 (408) 544-7000 http://www.altera.com

A-MNL-NIOSPROG-01.1

Copyright © 2001 Altera Corporation. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. ModelSim is a registered trademark of Mentor Graphics Corporation. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. All rights reserved.

## **About this Manual**

This manual provides comprehensive information about the  $\mathsf{Nios}^{\mathsf{TM}}$  embedded processor.

The terms Nios processor or Nios embedded processor are used when referring to the Altera soft core microprocessor in a general or abstract context.

The term Nios CPU is used when referring to the specific block of logic, in whole or part, that implements the Nios processor architecture.

Table 1 below shows the programmer's reference manual revision history.

| Table 1. Revision History |            |                                                                    |  |  |  |  |  |  |

|---------------------------|------------|--------------------------------------------------------------------|--|--|--|--|--|--|

| Revision                  | Date       | Description                                                        |  |  |  |  |  |  |

| Version 1.1               | March 2001 | Nios Embedded Processor Programmer's<br>Reference Manual - printed |  |  |  |  |  |  |

| Version 1.1.1             | July 2001  | PDF format                                                         |  |  |  |  |  |  |

Altera Corporation iii

## How to Contact Altera

For the most up-to-date information about Altera products, go to the Altera world-wide web site at http://www.altera.com.

For additional information about Altera products, consult the sources shown in Table 2.

| Information Type               | Access              | USA & Canada                                               | All Other Locations                                            |

|--------------------------------|---------------------|------------------------------------------------------------|----------------------------------------------------------------|

| Altera Literature<br>Services  | Electronic mail     | lit_req@altera.com (1)                                     | lit_req@altera.com (1)                                         |

| Non-technical customer service | Telephone hotline   | (800) SOS-EPLD                                             | (408) 544-7000<br>(7:30 a.m. to 5:30 p.m.<br>Pacific Time)     |

|                                | Fax                 | (408) 544-7606                                             | (408) 544-7606                                                 |

| Technical support              | Telephone hotline   | (800) 800-EPLD<br>(6:00 a.m. to 6:00 p.m.<br>Pacific Time) | (408) 544-7000 (1)<br>(7:30 a.m. to 5:30 p.m.<br>Pacific Time) |

|                                | Fax                 | (408) 544-6401                                             | (408) 544-6401 (1)                                             |

|                                | Electronic mail     | support@altera.com                                         | support@altera.com                                             |

|                                | FTP site            | ftp.altera.com                                             | ftp.altera.com                                                 |

| General product                | Telephone           | (408) 544-7104                                             | (408) 544-7104 (1)                                             |

| information                    | World-wide web site | http://www.altera.com                                      | http://www.altera.com                                          |

#### Note:

$<sup>(1) \</sup>quad \mbox{You can also contact your local Altera sales office or sales representative}.$

# Typographic Conventions

The *Nios Embedded Processor Programmer's Reference Manual* uses the typographic conventions shown in Table 3.

| Table 3. Conventions                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Visual Cue                                  | Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Bold Type with Initial<br>Capital Letters   | Command names, dialog box titles, checkbox options, and dialog box options are shown in bold, initial capital letters. Example: Save As dialog box.                                                                                                                                                                                                                                                                                                                          |

| bold type                                   | External timing parameters, directory names, project names, disk drive names, filenames, filename extensions, and software utility names are shown in bold type. Examples: f <sub>MAX</sub> , \maxplus2 directory, d: drive, chiptrip.gdf file.                                                                                                                                                                                                                              |

| Bold italic type                            | Book titles are shown in bold italic type with initial capital letters. Example: 1999 Device Data Book.                                                                                                                                                                                                                                                                                                                                                                      |

| Italic Type with Initial<br>Capital Letters | Document titles are shown in italic type with initial capital letters. Example: AN 75 (High-Speed Board Design).                                                                                                                                                                                                                                                                                                                                                             |

| Italic type                                 | Internal timing parameters and variables are shown in italic type. Examples: <i>tPIA</i> , <i>n</i> + 1.  Variable names are enclosed in angle brackets (<>) and shown in italic type. Example: <i><file name=""></file></i> , <i><pre>cfile name&gt;</pre></i> , <i><pre>cfile name&gt;</pre></i> , <i>copiect name&gt;</i> .pof file.                                                                                                                                      |

| Initial Capital Letters                     | Keyboard keys and menu names are shown with initial capital letters. Examples: Delete key, the Options menu.                                                                                                                                                                                                                                                                                                                                                                 |

| "Subheading Title"                          | References to sections within a document and titles of Quartus II and MAX+PLUS II Help topics are shown in quotation marks. Example: "Configuring a FLEX 10K or FLEX 8000 Device with the BitBlaster™ Download Cable."                                                                                                                                                                                                                                                       |

| Courier type                                | Signal and port names are shown in lowercase Courier type. Examples: data1, tdi, input. Active-low signals are denoted by suffix _n, e.g., reset_n.  Anything that must be typed exactly as it appears is shown in Courier type. For example: c:\max2work\tutorial\chiptrip.gdf. Also, sections of an actual file, such as a Report File, references to parts of files (e.g., the AHDL keyword SUBDESIGN), as well as logic function names (e.g., TRI) are shown in Courier. |

| 1., 2., 3., and a., b., c.,                 | Numbered steps are used in a list of items when the sequence of the items is important, such as the steps listed in a procedure.                                                                                                                                                                                                                                                                                                                                             |

|                                             | Bullets are used in a list of items when the sequence of the items is not important.                                                                                                                                                                                                                                                                                                                                                                                         |

| <b>→</b>                                    | The checkmark indicates a procedure that consists of one step only.                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                             | The hand points to information that requires special attention.                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4                                           | The angled arrow indicates you should press the Enter key.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| •••                                         | The feet direct you to more information on a particular topic.                                                                                                                                                                                                                                                                                                                                                                                                               |

## **Contents**

| How to Contact Altera                          | iv |

|------------------------------------------------|----|

| Typographic Conventions                        |    |

| Overview                                       |    |

| Introduction                                   |    |

| Audience                                       |    |

| Nios CPU Overview                              |    |

| Instruction Set                                |    |

| Register Overview                              |    |

| General-Purpose Registers                      |    |

| The K Register                                 |    |

| The Program Counter                            |    |

| Control Registers                              |    |

| Memory Access Overview                         |    |

| Reading from Memory (or Peripherals)           |    |

| Writing to Memory (or Peripherals)             |    |

| Addressing Modes                               |    |

| 5/16-bit Immediate Value                       |    |

| Full Width Register-Indirect                   |    |

| Partial Width Register-Indirect                |    |

| Full Width Register-Indirect with Offset       |    |

| Partial Width Register-Indirect with Offset    | 13 |

| Program-Flow Control                           |    |

| Relative-Branch Instructions                   | 14 |

| Absolute-Jump Instructions                     |    |

| Trap Instructions                              |    |

| Conditional Instructions                       | 15 |

| Exceptions                                     | 16 |

| Exception Handling Overview                    |    |

| Exception Vector Table                         | 16 |

| External Hardware Interrupt Sources            |    |

| Internal Exception Sources                     |    |

| Register Window Underflow                      | 17 |

| Register Window Overflow                       | 18 |

| Direct Software Exceptions (TRAP Instructions) |    |

| Exception Processing Sequence                  | 19 |

| Register Window Usage                          |    |

| Status Preservation: ISTATUS Register          |    |

| Return-Address                                 |    |

| Simple and Complex Exception Handlers          | 21 |

#### Contents

| 32-Bit Instruction Set |    |

|------------------------|----|

| ABS                    | 34 |

| ADD                    |    |

| ADDI                   | 36 |

| AND                    | 37 |

| ANDN                   | 38 |

| ASR                    | 39 |

| ASRI                   |    |

| BGEN                   | 41 |

| BR                     | 42 |

| BSR                    | 43 |

| CALL                   | 44 |

| CMP                    | 45 |

| CMPI                   | 46 |

| EXT16d                 | 47 |

| EXT16s                 | 48 |

| EXT8d                  | 49 |

| EXT8s                  | 50 |

| FILL16                 | 51 |

| FILL8                  | 52 |

| IF0                    | 53 |

| IF1                    | 54 |

| IFRnz                  | 55 |

| IFRz                   | 56 |

| IFS                    | 57 |

| JMP                    | 58 |

| LD                     | 59 |

| LDP                    | 60 |

| LDS                    | 61 |

| LRET                   | 62 |

| LSL                    | 63 |

| LSLI                   | 64 |

| LSR                    | 65 |

| LSRI                   | 66 |

| MOV                    | 67 |

| MOVHI                  | 68 |

| MOVI                   | 69 |

| MSTEP                  | 70 |

| MUL                    | 71 |

| NEG                    | 72 |

| NOP                    | 73 |

| NOT                    | 74 |

| OR                     | 75 |

| PFX                    | 76 |

| RDCTL                  | 77 |

| RESTORE                | 78 |

|         | RET    | 79  |

|---------|--------|-----|

|         | RLC    | 80  |

|         | RRC    | 81  |

|         | SAVE   | 82  |

|         | SEXT16 | 83  |

|         | SEXT8  | 84  |

|         | SKP0   | 85  |

|         | SKP1   | 86  |

|         | SKPRnz | 87  |

|         | SKPRz  | 88  |

|         | SKPS   | 89  |

|         | ST     | 90  |

|         | ST16d  | 91  |

|         | ST16s  | 92  |

|         | ST8d   | 93  |

|         | ST8s   | 94  |

|         | STP    | 95  |

|         | STS    | 96  |

|         | STS16s | 97  |

|         | STS8s  | 98  |

|         | SUB    | 99  |

|         | SUBI   | 100 |

|         | SWAP   | 101 |

|         | TRAP   | 102 |

|         | TRET   | 103 |

|         | WRCTL  | 104 |

|         | XOR    | 105 |

| Index . |        | 107 |

## **List of Tables**

| Table 1.  | Revision History                                                          | iii |

|-----------|---------------------------------------------------------------------------|-----|

|           | How to Contact Altera                                                     |     |

| Table 3.  | Conventions                                                               | v   |

| Table 4.  | Nios CPU Architecture                                                     | 1   |

| Table 5.  | Register Groups                                                           | 2   |

| Table 6.  | Programmer's Model                                                        | 3   |

| Table 7.  | Condition Code Flags                                                      | 6   |

|           | Typical 32-bit Nios CPU Program/Data Memory at Address 0x0100             |     |

| Table 9.  | N-bit-wide Peripheral at Address 0x0100 (32-bit Nios CPU)                 | 7   |

| Table 10. | Instructions Using 5/16-bit Immediate Values                              | 11  |

| Table 11. | Instructions Using Full Width Register-indirect Addressing                | 12  |

| Table 12. | Instructions Using Partial Width Register-indirect Addressing             | 12  |

| Table 13. | Instructions Using Full Width Register-indirect with Offset Addressing    | 13  |

| Table 14. | Instructions Using Partial Width Register-indirect with Offset Addressing | 14  |

| Table 15. | BR Branch Delay Slot Example                                              | 23  |

| Table 16. | Notation Details                                                          | 25  |

| Table 17. | 32-bit Major Opcode Table                                                 | 28  |

| Table 18. | GNU Compiler/Assembler Pseudo-instructions                                | 31  |

xii Altera Corporation

### **Overview**

Uverview

#### Introduction

The Nios<sup>TM</sup> embedded processor is a soft core CPU optimized for programmable logic and system-on-a-programmable chip (SOPC) integration. It is a configurable, general-purpose RISC processor that can be combined with user logic and programmed into an Altera programmable logic device (PLD). The Nios CPU can be configured for a wide range of applications. A 16-bit Nios CPU core running a small program out of an on-chip ROM makes an effective sequencer or controller, taking the place of a hard-coded state machine. A 32-bit Nios CPU core with external FLASH program storage and large external main memory is a powerful 32-bit embedded processor system.

#### **Audience**

This reference manual is for software and hardware engineers creating system design modules using the Excalibur Development Kit, featuring the Nios embedded processor. This manual assumes you are familiar with electronics, microprocessors, and assembly language programming. To become familiar with the conventions used with the Nios CPU, see Table 16 on page 25.

### Nios CPU Overview

The Nios CPU is a pipelined, single-issue RISC processor in which most instructions run in a single clock cycle. The Nios instruction set is targeted for compiled embedded applications. The 16-bit and 32-bit Nios CPU have native-word sizes of 16 bits and 32 bits, respectively, meaning the 16-bit Nios CPU has a native-word size of a half-word, while the 32-bit Nios CPU has a native-word size of a word. In Nios, byte refers to an 8-bit quantity, half-word refers to a 16-bit quantity, and word refers to a 32-bit quantity. The Nios family of soft core processors includes 32-bit and 16-bit architecture variants.

| Table 4. Nios CPU Architecture  |                 |                 |

|---------------------------------|-----------------|-----------------|

| Nios CPU Details                | 32-bit Nios CPU | 16-bit Nios CPU |

| Data bus size (bits)            | 32              | 16              |

| ALU width (bits)                | 32              | 16              |

| Internal register width (bits)  | 32              | 16              |

| Address bus size (bits)         | 33              | 17              |

| Instruction size (bits)         | 16              | 16              |

| Logic cells (typical)           | 1700            | 1100            |

| f <sub>max</sub> (EP20K200E -1) | Up to 50MHz     | Up to 50MHz     |

The Nios CPU ships with the GNUPro compiler and debugger from Cygnus, an industry-standard open-source C/C++ compiler, linker and debugger toolkit. The GNUPro toolkit includes a C/C++ compiler, macro-assembler, linker, debugger, binary utilities, and libraries.

#### Instruction Set

The Nios instruction set is tailored to support programs compiled from C and C++. It includes a standard set of arithmetic and logical operations, and instruction support for bit operations, byte extraction, data movement, control flow modification, and conditionally executed instructions, which can be useful in eliminating short conditional branches.

### Register Overview

This section describes the organization of the Nios CPU general-purpose registers and control registers. The Nios CPU architecture has a large general-purpose register file, several machine-control registers, a program counter, and the K register used for instruction prefixing.

#### **General-Purpose Registers**

The general-purpose registers are 32 bits wide in the 32-bit Nios CPU and 16 bits wide in the 16-bit Nios CPU. The register file size is configurable and contains a total of either 128, 256, or 512 registers. The software can access the registers using a 32-register-long sliding window that moves with a 16-register granularity. This sliding window can traverse the entire register file. This sliding window provides access to a subset of the register file.

The register window is divided into four even sections as shown in Table 5. The lowest eight registers (%r0-%r7) are *global* registers, also known as %g0-%g7. These global registers do not change with the movement or position of the window, but remain accessible as (%g0-%g7). The top 24 registers (%r8-%r31) in the register file are accessible through the current window.

| Table 5. Register Groups |           |    |         |

|--------------------------|-----------|----|---------|

| In registers             | %r24-%r31 | or | %i0-%i7 |

| Local registers          | %r16-%r23 | or | %L0-%L7 |

| Out registers            | %r8-%r15  | or | %00-%07 |

| Global registers         | %r0-%r7   | or | %g0-%g7 |

The top eight registers (%i0-%i7) are known as *in* registers, the next eight (%L0-%L7) as *local* registers, and the other eight (%o0-%o7) are known as *out* registers. When a register window moves down 16-registers (as it does for a SAVE instruction), the out registers become the in registers of the new window position. Also, the local and in registers of the last window position become inaccessible. See Table 6 for more detailed information.

| 7    | able | e 6. Pro         | grammer's Model       |                                                                     |          |     |      |     |            |

|------|------|------------------|-----------------------|---------------------------------------------------------------------|----------|-----|------|-----|------------|

|      |      |                  | 31                    | 16 15                                                               |          |     |      |     | 0          |

|      | %i7  | ′ %r31           |                       | SAVED return-address                                                |          |     |      |     |            |

|      | %i6  | %r30             |                       | %fp—frame pointer                                                   |          |     |      |     |            |

|      | %i5  | %r29             |                       | ' '                                                                 |          |     |      |     |            |

| ı    | %i4  | %r28             |                       |                                                                     |          |     |      |     |            |

| Ν    | %i3  |                  |                       |                                                                     |          |     |      |     |            |

|      | %i2  |                  |                       |                                                                     |          |     |      |     |            |

|      | %i1  |                  |                       |                                                                     |          |     |      |     |            |

|      | %iC  |                  |                       |                                                                     |          |     |      |     |            |

|      | %L   |                  |                       |                                                                     |          |     |      |     |            |

| ١.   |      | 6 %r22           |                       |                                                                     |          |     |      |     |            |

| L    |      | 5 %r21<br>4 %r20 |                       |                                                                     |          |     |      |     |            |

| 0    |      | 4 %r20<br>3 %r19 |                       | Page pointer 2 for CTD/LDD (or general purpose legal)               |          |     |      |     |            |

| Α    |      | 3 %119<br>2 %r18 |                       | Base-pointer 3 for STP/LDP (or general-purpose local)               |          |     |      |     |            |

| L    | %L   |                  |                       | Base-pointer 2 for STP/LDP (or general-purpose local)               |          |     |      |     |            |

|      |      | 0 %r16           |                       | Base-pointer 1 for STP/LDP (or general-purpose local)               |          |     |      |     |            |

|      |      |                  |                       | Base-pointer 0 for STP/LDP (or general-purpose local)               |          |     |      |     |            |

|      | %0   | 7 %r15<br>6 %r14 |                       | current return-address                                              |          |     |      |     |            |

|      |      |                  |                       | %sp-Stack Pointer                                                   |          |     |      |     |            |

| 0    |      | 5 %r13<br>4 %r12 |                       |                                                                     |          |     |      |     |            |

| U    | %0   |                  |                       |                                                                     |          |     |      |     |            |

| Т    |      | 2 %r10           |                       |                                                                     |          |     |      |     |            |

|      | %0   |                  |                       |                                                                     |          |     |      |     |            |

|      |      | 0 %r8            |                       |                                                                     |          |     |      |     |            |

|      | %g   | 7 %r7            |                       |                                                                     |          |     |      |     |            |

| G    | %g   | 6 %r6            |                       |                                                                     |          |     |      |     |            |

| L    | %g   | 5 %r5            |                       |                                                                     |          |     |      |     |            |

| 0    | %g   |                  |                       |                                                                     |          |     |      |     |            |

| В    | %g   |                  |                       |                                                                     |          |     |      |     |            |

| A    | %g   |                  |                       |                                                                     |          |     |      |     |            |

| L    | %g   |                  |                       |                                                                     |          |     |      |     |            |

|      | %g   | 0 %r0            |                       |                                                                     |          |     |      |     |            |

|      |      |                  |                       | 10 9 8 7                                                            | 6 5      | 1   | 2    | 2   | 1 0        |

|      |      |                  |                       |                                                                     |          |     | 0 .  |     |            |

|      |      |                  | 32 31                 | K REGISTER 10 9 8 7                                                 | <u> </u> | 1   | 2    | 2   | 1 0        |

|      |      | PC               | 02 01                 | 1015 10 9 6 7                                                       | 5 5      | 4   | 3 .  |     | 1 0        |

| 0/ 0 |      |                  | Amussiita (MDCTI ) am | evention to this register cots CTATLIC(15) (IF) O Decult of only    |          |     | tion | /D/ | TI \       |

| %C   | เมษ  | CLR_IE           | is undefined.         | eration to this register sets STATUS[15] (IE)=0. Result of any re-  | ;au-op   | era | แบก  | (HC | /IL)       |

| %.   | tl8  | SET_IE           |                       | eration to this register sets STATUS[15] (IE)=1. Result of any re   | ad-or    | ora | tion | (RC | CIT:       |

| /00  |      | OL 1_1L          | is undefined.         | oration to the register dots of the office (12)=1. Hosait or any to | au op    | oiu |      | (   | <i>,</i> , |

| %0   | tl7  | _                |                       | — reserved —                                                        |          |     |      |     |            |

|      | tl6  | _                |                       | — reserved —                                                        |          |     |      |     |            |

| %0   | tl5  | _                |                       | — reserved —                                                        |          |     |      |     |            |

|      | tl4  | _                |                       | — reserved —                                                        |          |     |      |     |            |

| %0   | tl3  | _                |                       | — reserved —                                                        |          | _   |      |     |            |

| %0   | tl2  | WVALID           |                       | HI_LIM                                                              | IT       |     | _0_  | LIM | ΙΙΤ        |

| %0   | tl1  | ISTATUS          | ;                     | Saved Stat                                                          | us       |     |      |     |            |

| %0   | tlO  | STATUS           |                       | IE IPRI C'                                                          | WP       |     | N    | V Z | z c        |

|      |      |                  |                       | • •                                                                 |          |     |      | -   |            |

#### The K Register

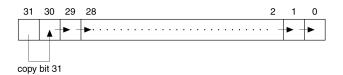

The K register is an 11-bit prefix value and is always set to 0 by every instruction except PFX. A PFX instruction sets K directly from the IMM11 instruction field. Register K contains a non-zero value only for an instruction immediately following PFX.

A PFX instruction disables interrupts for one cycle, so the two-instruction PFX sequence is an atomic CPU operation. Also, PFX sequence instruction pairs are skipped together by SKP-type conditional instructions.

The K register is not directly accessed by software, but is used indirectly. A MOVI instruction, for example, transfers all 11 bits of K into bits 15..5 of the destination register. This K-reading operation will only yield a non-zero result when the previous instruction is PFX.

#### **The Program Counter**

The program counter (PC) register contains the byte-address of the currently executing instruction. Since all instructions must be half-word-aligned, the least-significant bit of the PC value is always 0.

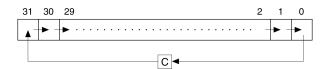

The PC increments by two (PC  $\leftarrow$  PC + 2) after every instruction unless the PC is explicitly set. The following instructions modify PC directly: BR, BSR, CALL, JMP, LRET, RET and TRET. The PC is 33-bits wide in a 32-bit Nios CPU and 17-bits wide in a 16-bit Nios CPU.

#### **Control Registers**

There are five defined control registers that are addressed independently from the general-purpose registers. The RDCTL and WRCTL instructions are the only instructions that can read or write to these control registers (meaning %ctl0 is unrelated to %g0).

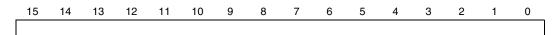

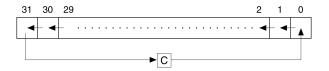

#### STATUS (%ctl0)

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|---|---|---|-----|---|---|---|---|---|---|

| IE |    |    | ΙP |    |    |   |   |   | CWP |   |   | N | V | Z | С |

#### Interrrupt Enable (IE)

IE is the interrupt enable bit. When IE=1, it enables external interrupts and internal exceptions. IE=0 disables external interrupts and exceptions. Software TRAP instructions will still execute normally even when IE=0. Note that IE can be set directly without affecting the rest of the STATUS register by writing to the SET\_IE (%ctl9) and CLR\_IE (%ctl8) control registers. When the CPU is reset, IE is set to 0 (interrupts disabled).

#### **Interrupt Priority (IPRI)**

IPRI contains the current running interrupt priority. When an exception is processed, the IPRI value is set to the exception number. See "Exceptions" on page 16 for more information. For external hardware interrupts, the IPRI value is set directly from the 6-bit hardware interrupt number. For TRAP instructions, the IPRI field is set directly from the IMM6 field of the instruction. For internal exceptions, the IPRI field is set from the pre-defined 6-bit exception number.

A hardware interrupt is not processed if its internal number is greater than or equal to IPRI or IE=0. A TRAP instruction is processed unconditionally. When the CPU is reset, IPRI is set to 63 (lowest-priority). IPRI disables interrupts above a certain number. For example, if IPRI is 3, then interrupts 0, 1 and 2 will be processed, but all others (interrupts 3-63) are disabled.

#### **Current Window Pointer (CWP)**

CWP points to the base of the sliding register window in the general-purpose register file. Incrementing CWP moves the register window up 16 registers. Decrementing CWP moves the register window down 16 registers. CWP is decremented by SAVE instructions and incremented by RESTORE instructions.

Only specialized system software such as register window-management facilities should directly write values to CWP through WRCTL. Software will normally modify CWP by using SAVE and RESTORE instructions. When the CPU is reset, CWP is set to the largest valid value, HI\_LIMIT. This means in a 256 register file size, there will be 16 register windows. After reset, the WVALID register (%ct12) is set to 0x01C1, i.e., LO\_LIMIT = 1 and HI\_LIMIT = 14. See "WVALID (%ctl2)" on page 6 for more information.

#### **Condition Code Flags**

Some instructions modify the condition code flags. These flags are the four least significant bits of the status register as shown in Table 7.

| Table 7. Condition Code Flags |                                                                      |  |  |  |  |  |

|-------------------------------|----------------------------------------------------------------------|--|--|--|--|--|

| N                             | Sign of result, or most significant bit                              |  |  |  |  |  |

| V                             | Arithmetic overflow—set if bit 31 of 32-bit result is different from |  |  |  |  |  |

|                               | sign of result computed with unlimited precision.                    |  |  |  |  |  |

| Z                             | Result is 0                                                          |  |  |  |  |  |

| С                             | Carry-out of addition, borrow-out of subtraction                     |  |  |  |  |  |

#### ISTATUS (%ctl1)

ISTATUS is the saved copy of the STATUS register. When an exception is processed, the value of the STATUS register is copied into the ISTATUS register. This action allows the pre-exception value of the STATUS register to be restored before control returns to the interrupted program. See "Exceptions" on page 16 for more information. A return-from-trap (TRET) instruction automatically copies the ISTATUS register into the STATUS register. Interrupts are disabled (IE=0) when an exception is processed. Before re-enabling interrupts, an exception handler must preserve the value of the ISTATUS register. When the CPU is reset, ISTATUS is set to 0.

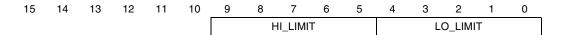

#### WVALID (%ctl2)

WVALID contains two values, HI\_LIMIT and LOW\_LIMIT. When a SAVE instruction decrements CWP from LOW\_LIMIT to LOW\_LIMIT –1 a register window underflow (exception #1) is generated. When a RESTORE instruction increments CWP from HI\_LIMIT to HI\_LIMIT +1, a register window overflow (exception #2) is generated. WVALID is configurable and may be read-only or read/write. When the CPU is reset, LO\_LIMIT is set to 1 and HI\_LIMIT is set to the highest valid window pointer ((register file size / 16) – 2).

#### CLR\_IE(%ctl8)

Any WRCTL operation to the CLR\_IE register clears the IE bit in the STATUS register (IE  $\leftarrow$  0) and the WRCTL value is ignored. A RDCTL operation from CLR\_IE produces an undefined result.

#### SET\_IE (%ctl9)

Any WRCTL operation to the SET\_IE register sets the IE bit in the STATUS register (IE  $\leftarrow$  1) and the WRCTL value is ignored. A RDCTL operation from SET\_IE produces an undefined result.

## Memory Access Overview

The Nios processor is little-endian. Data memory must occupy contiguous native-words. If the physical memory device is narrower than the native-word size, then the data bus should implement dynamic-bus sizing to simulate full-width data to the Nios CPU. Peripherals present their registers as native-word widths, padded by 0s in the most significant bits if the registers happen to be smaller than native-words. Table 8 and Table 9 show examples of the 32-bit Nios CPU native-word widths.

| Table 8. Typical 32-bit Nios CPU Program/Data Memory at Address 0x0100 |         |          |         |         |

|------------------------------------------------------------------------|---------|----------|---------|---------|

| Address                                                                |         | Contents |         |         |

|                                                                        | 31 24   | 23 16    | 15 8    | 7 0     |

| 0x0100                                                                 | byte 3  | byte 2   | byte 1  | byte 0  |

| 0x0104                                                                 | byte 7  | byte 6   | byte 5  | byte 4  |

| 0x0108                                                                 | byte 11 | byte 10  | byte 9  | byte 8  |

| 0x010c                                                                 | byte 15 | byte 14  | byte 13 | byte 12 |

| Table 9. N-bit-wide Peripheral at Address 0x0100 (32-bit Nios CPU) |                |            |  |  |

|--------------------------------------------------------------------|----------------|------------|--|--|

| Address                                                            | Con            | tents      |  |  |

|                                                                    | 31             | N N-1 0    |  |  |

| 0x0100                                                             | (zero padding) | register 0 |  |  |

| 0x0104                                                             | (zero padding) | register 1 |  |  |

| 0x0108                                                             | (zero padding) | register 2 |  |  |

| 0x010c                                                             | (zero padding) | register 3 |  |  |

#### Reading from Memory (or Peripherals)

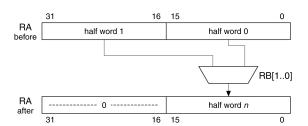

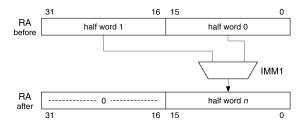

The Nios CPU can only perform aligned memory accesses. A 32-bit read operation can only read a full word starting at a byte address that is a multiple of 4. A 16-bit read operation can only read a half-word starting at a byte address that is a multiple of 2. Instructions which read from memory always treat the low bit (16-bit Nios CPU) or low two bits (32-bit Nios CPU) of the address as 0. Instructions are provided for extracting particular bytes and half-words from words.

The simplest instruction that reads data from memory is the LD instruction. A typical example of this instruction is LD \$g3, [\$o4]. The first register operand, \$g3, is the destination register, where data will be loaded. The second register operand specifies a register containing an address to read from. This address will be aligned to the nearest half-word (16-bit Nios CPU) or word (32-bit Nios CPU) meaning the lowest bit (16-bit Nios CPU) or two bits (32-bit Nios CPU) will be treated as if they are 0.

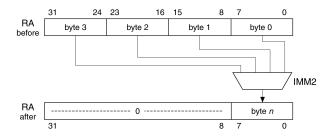

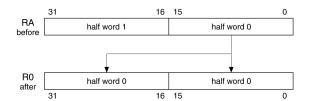

Quite often, however, software must read data smaller than the native data size. The Nios CPU provides instructions for extracting individual bytes (16-bit and 32-bit Nios CPU) and half-words (32-bit Nios CPU) from native-words. The EXT8d instruction is used for extracting a byte, and the EXT16d instruction is used for extracting a word. A typical example of the EXT8d instruction is EXT8d %g3,%o4. The EXT8d instruction uses the lowest bit (on 16-bit Nios CPU) or two bits (on 32-bit Nios CPU) of the second register operand to extract a byte from the first register operand, and replace the entire contents of the first register operand with that byte.

The assembly-language example in Code Example 1 shows how to read a single byte from memory, even if the address of the byte is not native-word-aligned.

#### Code Example 1: Reading a Single Byte from Memory

#### Writing to Memory (or Peripherals)

The Nios CPU can perform aligned writes to memory in widths of byte, half-word, or word (only the 32-bit Nios CPU can write a word). A word (32-bit Nios CPU) can be written to any address that is a multiple of 4 in one instruction. A half-word can be written to any address that is a multiple of 2 in one instruction (16-bit Nios CPU) or two instructions (32-bit Nios CPU). A byte can be written to any address in two instructions.

On the 32-bit Nios CPU, the lowest byte of a register can be written only to an address that is a multiple of 4; the middle-low byte of a register can be written only as an address that is a multiple of 4, plus 1, and so on. Similarly, on the 16-bit Nios CPU, the low byte of a register can be written only to an even address and the high byte of a register can only be written to an odd address.

The 32-bit Nios CPU can also write the low half-word of a register to an address that is a multiple of four, and the high half-word of a register to an address which is a multiple of 4, plus 2.

The ST instruction writes a full native-word to a native-word aligned memory address from any register; the ST8d and ST16d (32-bit Nios CPU only) instructions write a byte and half-word, respectively, with the alignment constraints described above, from register %r0.

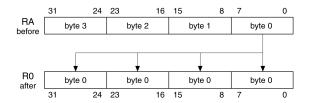

Often it is necessary for software to write a particular byte or half-word to an arbitrary location in memory. The position within the source register may not happen to correspond with the location in memory to be written. The FILL8 and FILL16 (32-bit Nios CPU only) instructions will take the lowest byte or half-word, respectively, of a register and replicate it across register %r0.

Code Example 2 shows how to write a single byte to memory, even if the address of the byte is not native-word-aligned.

#### Code Example 2: Single Byte Written to Memory—Address is not Native-word-aligned

```

Instructions executed on a 32-bit Nios CPU

; Let's assume %o4 contains the address 0x00001203

; and that %g3 contains the value 0x00000054

FILL8 %r0, %g3 ; (First operand can only be %r0)

; replicate low byte of %g3 across %r0

; so %r0 contains 0x54545454

ST8d [%o4], %r0; (Second operand can only be %r0)

; Stores the 3rd byte of %r0 to address 0x1203

Contents of memory after:

2

1

3

0x00001200

0x46

0x54

0x49

0x53

```

## Addressing Modes

The topics in this section includes a description of the following addressing modes:

- 5/16-bit immediate

- Full width register-indirect

- Partial width register-indirect

- Full width register-indirect with offset

- Partial width register-indirect with offset

#### 5/16-bit Immediate Value

Many arithmetic and logical instructions take a 5-bit immediate value as an operand. The ADDI instruction, for example, has two operands: a register and a 5-bit immediate value. A 5-bit immediate value represents a constant from 0 to 31. To specify a constant value that requires from 6 to 16 bits (a number from 32 to 65535), the 11-bit K register can be set using the PFX instruction, This value is concatenated with the 5-bit immediate value. The PFX instruction must be used directly before the instruction it modifies.

To support breaking 16-bit immediate constants into a PFX value and a 5-bit immediate value, the assembler provides the operators %hi() and %lo(). %hi(x) extracts the 11 bits from bit 5 to bit 15 from constant x, and %lo(x) extracts the 5 bits from bit 0 to bit 4 from constant x.

The following example shows an ADDI instruction being used both with and without a PFX.

#### Code Example 3: The ADDI Instruction Used with/without a PFX

```

; Assume %g3 contains the value 0x0041

ADDI %g3,5

; Add 5 to %g3

; so %g3 now contains 0x0046

PFX %hi(0x1234)

; Load K with upper 11 bits of 0x1234

ADDI %g3,%lo(0x1234); Add low 5 bits of 0x1234 to %g3

; so the K register contained 0x0091

; and the immediate operand of the ADDI

; instruction contained 0x0011, which

; concatenated together make 0x1234

```

Besides arithmetic and logical instructions, several other instructions use immediate-mode constants of various widths, and the constant is not modified by the K register. See the description of each instruction in the "32-Bit Instruction Set" for a precise explanation of its operation. Table 10 shows instructions using 5/16-bit immediate values.

| Table 10. Instructions Using 5/16-bit Immediate Values |      |       |      |

|--------------------------------------------------------|------|-------|------|

| ADDI                                                   | AND* | ANDN* | ASRI |

| CMPI                                                   | LSLI | LSRI  | MOVI |

| MOVHI                                                  | OR*  | SUBI  | XOR* |

<sup>\*</sup> AND, ANDN, OR, and XOR can only use PFX'd 16-bit immediate values. These instructions act on two register operands if not preceded by a PFX instruction.

#### **Full Width Register-Indirect**

The LD and ST instructions can load and store, respectively, a full native-word to or from a register using another register to specify the address. The address is first aligned downward to a native-word aligned address, as described in the "Memory Access Overview" section. The K register is treated as a signed offset, in native words, from the native-word aligned value of the address register.

| Table 11. Instructions Using Full Width Register-indirect Addressing |     |     |  |

|----------------------------------------------------------------------|-----|-----|--|

| Instruction Address Register Data Regi                               |     |     |  |

| LD                                                                   | Any | Any |  |

| ST                                                                   | Any | Any |  |

#### Partial Width Register-Indirect

There are no instructions that read a partial word. To read a partial word, you must combine a full width register-indirect read instruction with an extraction instruction, EXT8d, EXT8s, EXT16d (32-bit Nios CPU only) or EXT16s (32-bit Nios CPU only).

Several instructions can write a partial word. Each of these instructions has a static and a dynamic variant. The position within both the source register and the native-word of memory is determined by the low bits of an addressing register. In the case of a static variant, the position within both the source register and the native-word of memory is determined by a 1- or 2-bit immediate operand to the instruction. As with full width register-indirect addressing, the K register is treated as a signed offset in native words from the native-word aligned value of the address register.

The partial width register-indirect instructions all use %r0 as the source of data to write. These instructions are convenient to use in conjunction with the FILL8 or FILL16 (32-bit Nios CPU only) instructions.

| Table 12. Instructions Using Partial Width Register-indirect Addressing |                  |               |                              |

|-------------------------------------------------------------------------|------------------|---------------|------------------------------|

| Instruction                                                             | Address Register | Data Register | Byte/Half-word Selection     |

| ST8s                                                                    | Any              | %r0           | Immediate                    |

| ST16s*                                                                  | Any              | %r0           | Immediate                    |

| ST8d                                                                    | Any              | %r0           | Low bits of address register |

| ST16d*                                                                  | Any              | %r0           | Low bits of address register |

<sup>\* 32-</sup>bit Nios CPU only

#### **Full Width Register-Indirect with Offset**

The LDP, LDS, STP and STS instructions can load or store a full native-word to or from a register using another register to specify an address, and an immediate value to specify an offset, in native words, from that address.

Unlike the LD and ST instructions, which can use any register to specify a memory address, these instructions may each only use particular registers for their address. The LDP and STP instructions may each only use the register %L0, %L1, %L2, or %L3 for their address registers. The LDS and STS instructions may only use the stack pointer, register %sp (equivalent to %o6), as their address register. These instructions each take a signed immediate index value that specifies an offset in native words from the aligned address pointed in the address register.

| Table 13. Instructions Using Full Width Register-indirect with Offset Addressing |                    |               |                          |  |

|----------------------------------------------------------------------------------|--------------------|---------------|--------------------------|--|

| Instruction                                                                      | Address Register   | Data Register | Offset Range without PFX |  |

| LDP                                                                              | %L0, %L1, %L2, %L3 | Any           | -1615 native-words       |  |

| LDS                                                                              | %sp                | Any           | 0255 native-words        |  |

| STP                                                                              | %L0, %L1, %L2, %L3 | Any           | -1615 native-words       |  |

| STS                                                                              | %sp                | Any           | 0255 native-words        |  |

#### Partial Width Register-Indirect with Offset

There are no instructions that read a partial word from memory. To read a partial word, you must combine a full width indexed register-indirect read instruction with an extraction instruction, EXT8d, EXT8s, EXT16d (32-bit Nios CPU only) or EXT16s (32-bit Nios CPU only). The STS8s and STS16s (Nios 32 only) use an immediate constant to specify a byte or halfword offset, respectively, from the stack pointer to write the correspondingly aligned partial width of the source register %r0.

These instructions may each only use the stack pointer, register %sp (equivalent to %o6), as their address register, and may only use register %r0 (equivalent to %g0, but must be called %r0 in the assembly instruction) as the data register. These instructions are convenient to use with the FILL8 or FILL16 (32-bit Nios CPU only) instructions.

| Table 14. Instructions Using Partial Width Register-indirect with Offset Addressing |                     |               |                             |                 |

|-------------------------------------------------------------------------------------|---------------------|---------------|-----------------------------|-----------------|

| Instruction                                                                         | Address<br>Register | Data Register | Byte/Half-word<br>Selection | Index Range     |

| STS8s                                                                               | %sp                 | %r0           | Immediate                   | 01023 bytes     |

| STS16s*                                                                             | %sp                 | %r0           | Immediate                   | 0511 half-words |

\*32-bit Nios CPU only

## Program-Flow Control

The topics in this section includes a description of the following:

- Two relative-branch instructions (BR and BSR)

- Two absolute-jump instructions (JMP and CALL)

- Two trap instructions (TRET and TRAP)

- Five conditional instructions (SKP, SKP0, SKP1, SKPRz and SKPRnz)

#### **Relative-Branch Instructions**

There are two relative-branch instructions: BR and BSR. The branch target address is computed from the current program-counter (i.e. the address of the BR instruction itself) and the IMM11 instruction field. Details of the branch-offset computation are provided in the description of the BR and BSR instructions. See "BR" on page 42 and "BSR" on page 43. BSR is identical to BR except that the return-address is saved in %07. Details of the return-address computation are provided in the description of the BSR instruction. Both BR and BSR are unconditional. Conditional branches are implemented by preceding BR or BSR with a SKP-type instruction.

Both BR and BSR instructions have branch delay slot behavior: The instruction immediately following a BR or BSR is executed after BR or BSR, but before the instruction at the branch-target. See "Branch Delay Slots" on page 23 for more information. The branch range of the BR and BSR instructions is forward by 2048 bytes, or backwards by 2046 bytes relative to the address of the BR or BSR instruction.

#### **Absolute-Jump Instructions**

There are two absolute (computed) jump instructions: JMP and CALL. The jump-target address is given by the contents of a general-purpose register. The register contents are left-shifted by one and transferred into the PC. CALL is identical to JMP except that the return-address is saved in %o7. Details of the return-address computation are provided in the description of the CALL instruction. Both JMP and CALL are unconditional. Conditional jumps are implemented by preceding JMP or CALL with a SKP-type instruction.

Both JMP and CALL instructions have branch delay slot behavior: The instruction immediately following a JMP or CALL is executed after JMP or CALL, but before the instruction at the jump-target. The LRET pseudo-instruction, which is an assembler alias for JMP %07, is conventionally used to return from subroutines.

#### **Trap Instructions**

The Nios processor implements two instructions for software exception processing: TRAP and TRET. See "TRAP" on page 102 and "TRET" on page 103 for detailed descriptions of both these instructions. Unlike JMP and CALL, neither TRAP nor TRET has a branch delay-slot: The instruction immediately following TRAP is not executed until the exception-handler returns. The instruction immediately following TRET is not executed at all as part of TRET's operation.

#### Conditional Instructions

There are five conditional instructions (SKPs, SKP0, SKP1, SKPRz, and SKPRnz). Each of these instructions has a converse assembler-alias pseudo-instruction (IFs, IF0, IF1, IFRz, and IFRnz, respectively). Each of these instructions tests a CPU-internal condition and then executes the next instruction or not, depending on the outcome. The operation of all five SKP-type instructions (and their pseudo-instruction aliases), are identical except for the particular test performed. In each case, the subsequent (conditionalized) instruction is fetched from memory regardless of the test outcome. Depending on the outcome of the test, the subsequent instruction is either executed or cancelled.

While SKP and IF type conditional instructions are often used to conditionalize jump (JMP, CALL) and branch (BR, BSR) instructions, they can be used to conditionalize any instruction. Conditionalized PFX instructions (PFX immediately after a SKPx or IFx instruction) present a special case; the next two instructions are either both cancelled or both executed. PFX instruction pairs are conditionalized as an atomic unit.

#### **Exceptions**

The topics in this section include a description of the following:

- Exception vector table

- How external hardware interrupts, internal exceptions, register window underflow, register window overflow and TRAP instructions are handled

- Direct software exceptions (TRAP) and exception processing sequence

#### **Exception Handling Overview**

The Nios processor allows up to 64 vectored exceptions. Exceptions can be enabled or disabled globally by the IE control-bit in the STATUS register, or selectively enabled on a priority basis by the IPRI field in the STATUS register. Exceptions can be generated from any of three sources: external hardware interrupts, internal exceptions or explicit software TRAP instructions.

The Nios exception-processing model allows precise handling of all internally generated exceptions. That is, the exception-transfer mechanism leaves the exception-handling subroutine with enough information to restore the status of the interrupted program as if nothing had happened. Internal exceptions are generated if a SAVE or RESTORE instruction causes a register-window underflow or overflow, respectively.

Exception-handling subroutines always execute in a newly opened register window, allowing very low interrupt latency. The exception handler does not need to manually preserve the interruptee's register contents.

#### **Exception Vector Table**

The exception vector table is a set of 64 exception-handler addresses. On a 32-bit Nios CPU each entry is 4 bytes and on a 16-bit Nios CPU each entry is 2 bytes. The base-address of the exception vector table is configurable. When the Nios CPU processes exception number n, it fetches the nth entry from the exception vector table, doubles the fetched value and then loads the results into the PC.

The exception vector table can physically reside in RAM or ROM, depending on the hardware memory map of the target system. A ROM exception vector table will not require run-time initialization.

#### **External Hardware Interrupt Sources**

An external source can request a hardware interrupt by driving a 6-bit interrupt number on the Nios CPU irq\_number inputs while simultaneously asserting true (1) the Nios CPU irq input pin. The Nios CPU will process the indicated exception if the IE bit is true (1) and the requested interrupt number is smaller than (higher priority than) the current value in the IPRI field of the STATUS register. Control is transferred to the exception handler whose number is given by the irq\_number inputs.

External logic for producing the irq\_number input and for driving the irq input pin is automatically generated by the Nios SOPC builder software and included in the peripheral bus module PBM outside the CPU. An interrupt-capable peripheral need only generate one or more interrupt-request signals that are combined within the PBM to produce the Nios irq\_number and irq inputs.

The Nios irq input is level sensitive. The irq and irq\_number inputs are sampled at the rising edge of each clock. External sources that generate interrupts should assert their irq output signals until the interrupt is acknowledged by software (e.g. by writing a register inside the interrupting peripheral to 0). Interrupts that are asserted and then deasserted before the Nios CPU core can begin processing the exception are ignored.

#### **Internal Exception Sources**

There are two sources of internal exceptions: register window-overflow and register window-underflow. The Nios processor architecture allows precise exception handling for all internally generated exceptions. In each case, it is possible for the exception handler to fix the exceptional condition and make it behave as if the exception-generating instruction had succeeded.

#### Register Window Underflow

A register window underflow exception occurs whenever the lowest valid register window is in use (CWP = LO\_LIMIT) and a SAVE instruction is issued. The SAVE instruction moves CWP below LO\_LIMIT and %sp is set per the normal operation of SAVE. A register window underflow exception is generated, which transfers control to an exception-handling subroutine before the instruction following SAVE is executed.

When a SAVE instruction causes a register window underflow exception, CWP is decremented only once before control is passed to the exception-handling subroutine. The underflow exception handler will see CWP =  $LO_LIMIT - 1$ . The register window underflow exception is exception number 1. The CPU will not process a register window underflow exception if interrupts are disabled (IE=0) or the current value in IPRI is less than or equal to 1.

The action taken by the underflow exception-handler subroutine depends upon the requirements of the system. For systems running larger or more complex code, the underflow (and overflow) handlers can implement a virtual register file that extends beyond the limits of the physical register file. When an underflow occurs, the underflow handler might (for example) save the current contents of the entire register file to memory and re-start CWP back at HI\_LIMIT, allowing room for code to continue opening register windows. Many embedded systems, on the other hand, might wish to tightly control stack usage and subroutine call-depth. Such systems might implement an underflow handler that prints an error message and exits the program.

The programmer determines the nature of and actions taken by the register window underflow exception handler. The Nios software development kit (SDK) includes, and automatically installs by default, a register window underflow handler that virtualizes the register file using the stack as temporary storage.

A register window underflow exception can only be generated by a SAVE instruction. Directly writing CWP (via a WRCTL instruction) to a value less than LO\_LIMIT will not cause a register window underflow exception. Executing a SAVE instruction when CWP is already below LO\_LIMIT will not generate a register window underflow exception.

#### Register Window Overflow

A register window overflow exception occurs whenever the highest valid register window is in use (CWP = HI\_LIMIT) and a RESTORE instruction is issued. Control is transferred to an exception-handling subroutine before the instruction following RESTORE is executed.

When a register window overflow exception is taken, the exception handler will see CWP at HI\_LIMIT. You can think of CWP being incremented by the RESTORE instruction, but then immediately decremented as a consequence of normal exception processing. The register window overflow exception is exception number 2.

Overview

The action taken by the overflow exception handler subroutine depends upon the requirements of the system. For systems running larger or more complex code, the overflow and underflow handlers can implement a virtual register file that extends beyond the limits of the physical register file. When an overflow occurs, such an overflow handler might (for example) reload the entire contents of the physical register file from the stack and restart CWP back at LO\_LIMIT. Many embedded systems, on the other hand, might wish to tightly control stack usage and subroutine call depth. Such systems might implement an overflow handler that prints an error message and exits the program.

The programmer determines the nature of and actions taken by the register window overflow exception handler. The Nios SDK automatically installs by default a register window overflow handler which virtualizes the register file using the stack.

A register window overflow exception can only be generated by a RESTORE instruction. Directly writing CWP (via a WRCTL instruction) to a value greater than HI\_LIMIT will not cause a register window overflow exception. Executing a RESTORE instruction when CWP is already above HI\_LIMIT will not generate a register window overflow exception.

#### **Direct Software Exceptions (TRAP Instructions)**

Software can directly request that control be transferred to an exception handler by issuing a TRAP instruction. The IMM6 field of the instruction gives the exception number. TRAP instructions are always processed, regardless of the setting of the IE or IPRI bits. TRAP instructions do not have a delay slot. The instruction immediately following a TRAP is not executed before control is transferred to the indicated exception-handler. A reference to the instruction following TRAP will be saved in %07, so that a TRET instruction will transfer control back to the instruction following TRAP at the conclusion of exception processing.

#### **Exception Processing Sequence**

When an exception is processed from any of the sources mentioned above, the following sequence occurs:

- The contents of the STATUS register are copied into the ISTATUS register.

- 2. CWP is decremented, opening a new window for use by the exception-handler routine (This is not the case for register window underflow exceptions, where CWP was already decremented by the SAVE instruction that caused the exception).

- 3. IE is set to 0, disabling interrupts.

- 4. IPRI is set with the 6-bit number of the exception.

- 5. The address of the next non-executed instruction in the interrupted program is transferred into %o7.

- 6. The start-address of the exception handler is fetched from the exception vector table and written into the PC.

- 7. After the exception handler finishes a TRET instruction is issued to return control to the interrupted program.

#### Register Window Usage

All exception processing starts in a newly opened register window. This process decreases the complexity and latency of exception handlers because they are not responsible for maintaining the interruptee's register contents. An exception handler can freely use registers %00..%L7 in the newly opened window. An exception handler should not execute a SAVE instruction upon entry. The use of SAVE and RESTORE from within exception handlers is discussed later.

Because the transfer to exception handling always opens a new register window, programs must always leave one register window available for exceptions. Setting LO-LIMIT to 1 guarantees that one window is available for exceptions (The reset value of LO\_LIMIT is 1). Whenever a program executes a SAVE instruction that would then use up the last register window (CWP = 0), a register-underflow trap is generated. The register-underflow handler itself will execute in the final window (with CWP = 0).

Correctly written software will never process an exception when CWP is 0. CWP will only be 0 when an exception is being processed, and exception handlers must take certain well-defined precautions before re-enabling interrupts. See "Simple and Complex Exception Handlers" on page 21 for more information.

#### Status Preservation: ISTATUS Register

When an exception occurs, the interruptee's STATUS register is copied into the ISTATUS register. The STATUS register is then modified (IE set to 0, IPRI set, CWP decremented). The original contents of the STATUS register are preserved in the ISTATUS register. When exception processing returns control to the interruptee, the original program's STATUS register contents are restored from ISTATUS by the TRET instruction.

Interrupts are automatically disabled upon entry to an exception handler, so there is no danger of ISTATUS being overwritten by a subsequent interrupt or exception. The case of nested exception handlers (exception handlers that use or re-enable exceptions) is discussed in detail below. Nested exception handlers must explicitly preserve, maintain, and restore the contents of the ISTATUS register before and after enabling subsequent interrupts.

#### **Return-Address**

When an exception occurs, execution of the interrupted program is temporarily suspended. The instruction in the interrupted program that was preempted (i.e., the instruction that would have executed, but did not yet execute) is taken as the return-location for exception processing.

The return-location is saved in %o7 (in the exception handler's newly opened register window) before control is transferred to the exception handler. The value stored in %o7 is the byte-address of the returninstruction right-shifted by one place. This value is suitable directly for use as the target of a TRET instruction without modification. Exception handlers will usually execute a TRET %o7 instruction to return control to the interrupted program.

#### **Simple and Complex Exception Handlers**

The Nios processor architecture permits efficient, simple exception handlers. The hardware itself accomplishes much of the status- and register-preservation overhead required by an exception handler. Simple exception handlers can substantially ignore all automatic aspects of exception handling. Complex exception handlers (for example, nested exception handlers) must follow additional precautions.

#### Simple Exception Handlers

An exception handler is considered simple if it obeys the following rules:

- It does not re-enable interrupts.

- It does not use SAVE or RESTORE (either directly or by calling subroutines that use SAVE or RESTORE).

- It does not use any TRAP instructions (or call any subroutines that use TRAP instructions).

- It does not alter the contents of registers %g0..%g7, or %i0..%i7.

Any exception handler that obeys these rules need not take special precautions with ISTATUS or the return address in %07. A simple exception handler need not be concerned with CWP or register-window management.

#### Complex Exception Handlers

An exception handler is considered complex if it violates any of the requirements of a simple exception handler, listed above. Complex exception handlers allow nested exception handling and the execution of more complex code (e.g. subroutines that SAVE and RESTORE). A complex exception handler has the following additional responsibilities:

- It must preserve the contents of ISTATUS before re-enabling interrupts. For example, ISTATUS could be saved on the stack.

- It must check CWP before re-enabling interrupts to be sure CWP is at or above LO\_LIMIT. If CWP is below LO\_LIMIT, it must take an action to open up more available register windows (e.g., save the register file contents to RAM), or it must signal an error.

- It must re-enable interrupts subject to the above two conditions before executing any SAVE or RESTORE instructions or calling any subroutines that execute any SAVE or RESTORE instructions.

- Prior to returning control to the interruptee, it must restore the contents of the ISTATUS register, including any adjustments to CWP if the register-window has been deliberately shifted.

- Prior to returning control to the interruptee, it must restore the contents of the interruptee's register window.

## Pipeline Implementation

This topics in this section include a description of the following:

- Nios CPU pipeline

- Exposed pipeline branch delay and direct CWP manipulation

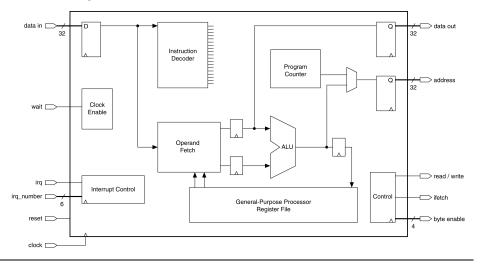

Figure 4. Nios CPU Block Diagram

#### **Pipeline Operation**

The Nios CPU is pipelined RISC architecture. The pipeline implementation is hidden from software except for branch delay slots and when CWP is modified by a WRCTL direct write. The pipeline stages include:

- Instruction Fetch—the Nios CPU issues an address, and the memory subsystem then returns the instruction stored at the issued address.

- Instruction Decode / Operand Fetch—the fetched instruction is decoded. If there are register operands, they are read from the register file. A dedicated branch-target adder computes the destination address for BR and BSR instructions.

- Execute—the operands and control bits are presented to the ALU. The ALU then computes a result.

- Write-back—the ALU result is written back into the destination register when applicable.

#### **Branch Delay Slots**

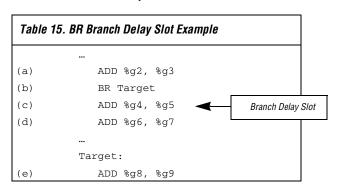

A branch delay slot is defined as the instruction immediately after a BR, BSR, CALL, or JMP instruction. A branch delay slot is executed after the branch instruction but before the branch-target instruction. Table 15 illustrates a branch delay-slot for a BR instruction.

After branch instruction (b) is taken, instruction (c) is executed before control is transferred to the branch target (e). The execution sequence of the above code fragment would be (a), (b), (c), and (e). Instruction (c) is instruction (b)'s branch delay slot. Instruction (d) is not executed. Most instructions can be used as a branch delay slot except for those listed below:

- BR

- BSR

- CALL

- IF1

- IF0

- IFRnz

- IFRz

- IFS

- JMP

- LRET

- PFX

- RET