# ML310 User Guide

## Virtex-II Pro Embedded Development Platform

UG068 (v1.01) August 25, 2004

"Xilinx" and the Xilinx logo shown above are registered trademarks of Xilinx, Inc. Any rights not expressly granted herein are reserved. CoolRunner, RocketChips, Rocket IP, Spartan, StateBENCH, StateCAD, Virtex, XACT, XC2064, XC3090, XC4005, and XC5210 are registered trademarks of Xilinx, Inc.

The shadow X shown above is a trademark of Xilinx, Inc.

ACE Controller, ACE Flash, A.K.A. Speed, Alliance Series, AllianceCORE, Bencher, ChipScope, Configurable Logic Cell, CORE Generator, CoreLINX, Dual Block, EZTag, Fast CLK, Fast CONNECT, Fast FLASH, FastMap, Fast Zero Power, Foundation, Gigabit Speeds...and Beyond!, HardWire, HDL Bencher, IRL, J Drive, JBits, LCA, LogiBLOX, Logic Cell, LogicORE, LogicProfessor, MicroBlaze, MicroVia, MultiLINX, NanoBlaze, PicoBlaze, PLUSASM, PowerGuide, PowerMaze, QPro, Real-PCI, RocketlO, SelectIO, SelectRAM+, Silicon Xpresso, Smartguide, Smart-IP, SmartSearch, SMARTswitch, System ACE, Testbench In A Minute, TrueMap, UIM, VectorMaze, VersaBlock, VersaRing, Virtex-II Pro, Virtex-II EasyPath, Wave Table, WebFITTER, WebPACK, WebPOWERED, XABEL, XACT-Floorplanner, XACT-Performance, XACTstep Advanced, XACTstep Foundry, XAM, XAPP, X-BLOX +, XC designated products, XChecker, XDM, XEPLD, Xilinx Foundation Series, Xilinx XDTV, Xinfo, XSI, XtremeDSP and ZERO+ are trademarks of Xilinx, Inc.

The Programmable Logic Company is a service mark of Xilinx, Inc.

All other trademarks are the property of their respective owners.

Xilinx, Inc. does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx, Inc. reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, Inc. will not assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx provides any design, code, or information shown or described herein "as is." By providing the design, code, or information as one possible implementation of a feature, application, or standard, Xilinx makes no representation that such implementation is free from any claims of infringement. You are responsible for obtaining any rights you may require for your implementation. Xilinx expressly disclaims any warranty whatsoever with respect to the adequacy of any such implementation, including but not limited to any warranties or representations that the implementation is free from claims of infringement, as well as any implied warranties of merchantability or fitness for a particular purpose. Xilinx, Inc. devices and products are protected under U.S. Patents. Other U.S. and foreign patents pending. Xilinx, Inc. does not represent that devices shown or products described herein are free from patent infringement or from any other third party right. Xilinx, Inc. assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx, Inc. will not assume any liability for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

The contents of this manual are owned and copyrighted by Xilinx. Copyright 1994-2004 Xilinx, Inc. All Rights Reserved. Except as stated herein, none of the material may be copied, reproduced, distributed, republished, downloaded, displayed, posted, or transmitted in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Any unauthorized use of any material contained in this manual may violate copyright laws, trademark laws, the laws of privacy and publicity, and communications regulations and statutes.

#### ML310 User Guide UG068 (v1.01) August 25, 2004

The following table shows the revision history for this document..

|          | Version | Revision                      |

|----------|---------|-------------------------------|

| 08/15/04 | 1.0     | Initial Xilinx release.       |

| 08/25/04 | 1.01    | Added SysACE CFGADDR details. |

|          |         |                               |

|          |         |                               |

## Table of Contents

Preface: About This Manual

Chapter 1: Introduction to Virtex-II Pro, ISE, and EDK **Chapter 2: ML310 Embedded Development Platform** Board Hardware 20

System ACE JTAG Configuration Interface

30

GPIO LEDs and LCD

30

GPIO

30

GPIO LED Interface

32

GPIO LCD Interface

32

CPU Debug and CPU Trace

33

CPU Debug Description

33

CPU Debug Connector Pinout

35

CPU Debug Connection to XC2VP30

35

|     | PCI Bus                                                   | 35 |

|-----|-----------------------------------------------------------|----|

|     | ALi South Bridge Interface, M1535D+, U15                  | 40 |

|     | Parallel Port Interface, connector assembly P1            |    |

|     | Serial Port Interface, connector assembly P1              | 42 |

|     | USB, connector assembly J3                                |    |

|     | IDE, connectors J15 and J16.                              |    |

|     | GPIO, connector J5                                        | 45 |

|     | System Management Bus (SMBus)                             |    |

|     | AC97 Audio                                                |    |

|     | PS/2 Keyboard/Mouse Interface, connector P2               | 47 |

|     | Flash ROM, U4                                             | 47 |

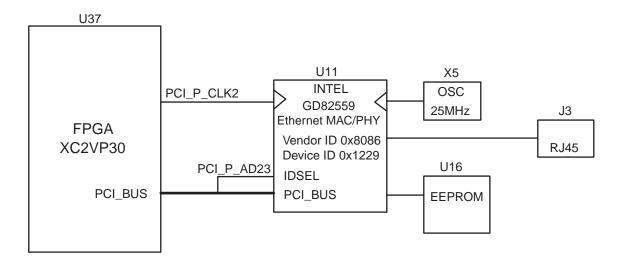

|     | Intel GD82559, U11, 10/100 Ethernet Controller            | 48 |

|     | Intel GD82559 Ethernet Controller                         | 48 |

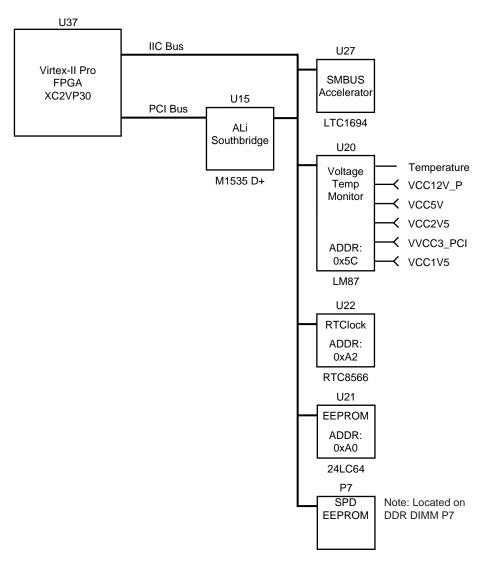

|     | IIC/SMBus Interface                                       | 49 |

|     | Introduction to IIC/SMBus                                 | 49 |

|     | IIC/SMBus Signaling                                       | 49 |

|     | IIC/SMBus on ML310 Board                                  | 49 |

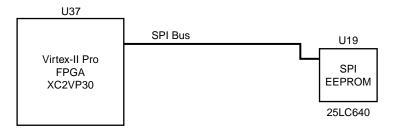

|     | Serial Peripheral Interface (SPI)                         | 52 |

|     | SPI Signaling                                             | 52 |

|     | SPI Addressing                                            |    |

|     | Push Buttons, Switches, Front Panel Interface and Jumpers | 53 |

|     | Push Buttons                                              | 53 |

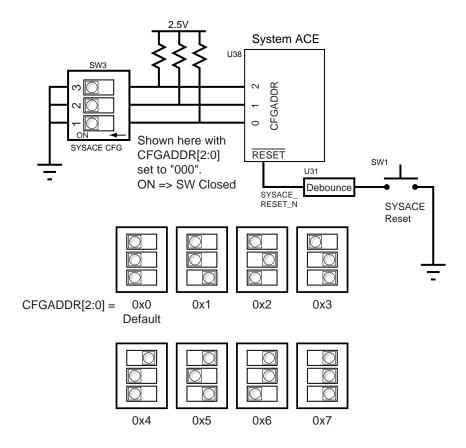

|     | System ACE Configuration Dipswitch, SW3                   | 54 |

|     | Front Panel Interface Connector, J23                      | 55 |

|     | Jumpers                                                   | 57 |

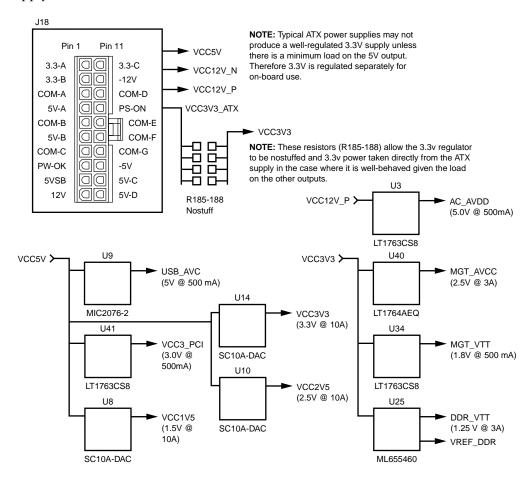

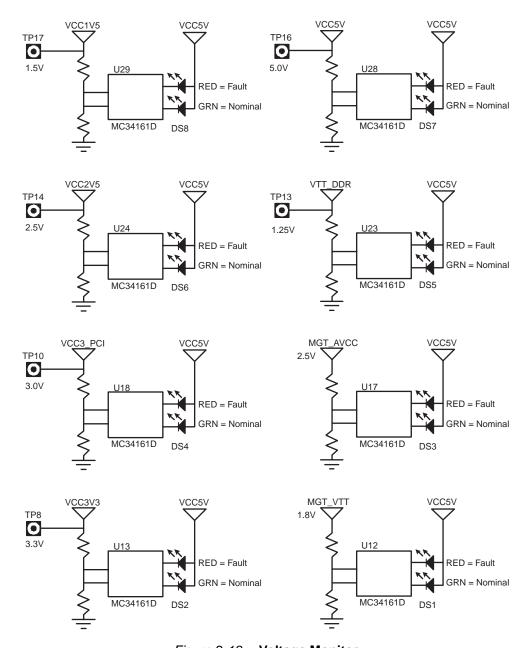

|     | ATX Power Distribution and Voltage Regulation             | 58 |

| Hig | h-Speed I/O                                               | 61 |

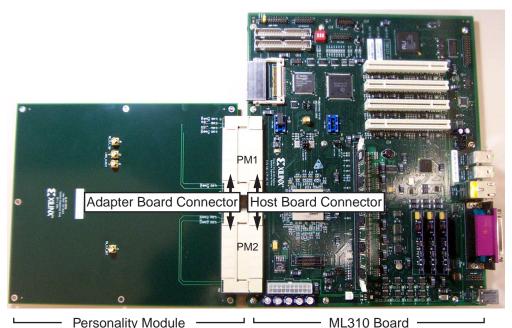

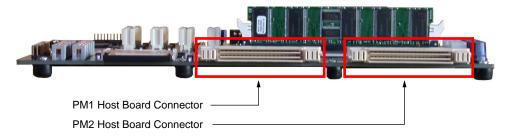

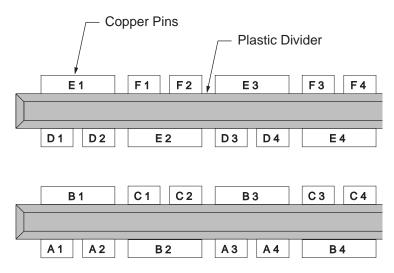

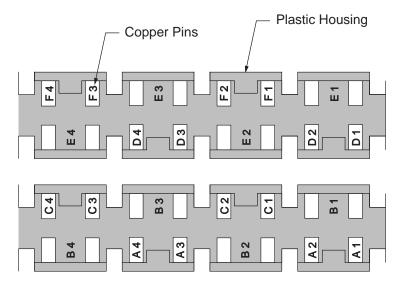

| O   | ML310 PM Connectors                                       |    |

|     | PM1 Connector                                             | 63 |

|     | PM2 Connector                                             | 63 |

|     | Adapter Board PM Connectors                               | 64 |

|     | ML310 PM Utility Pins                                     |    |

|     | Contact Order                                             |    |

|     | PM1 Power and Ground                                      | 65 |

|     | PM2 Power and Ground                                      | 65 |

|     | ML310 PM User I/O Pins                                    |    |

|     | PM1 User I/O                                              | 65 |

|     | ML310 PM2 User I/O                                        | 68 |

### About This Manual

This manual accompanies the ML310 Embedded Development System and contains information about the ML310 Hardware Platform and software tools.

#### **Manual Contents**

This manual contains the following chapters:

- Chapter 1, "Introduction to Virtex-II Pro, ISE, and EDK," provides an overview of the hardware and software features.

- Chapter 2, "ML310 Embedded Development Platform," provides an overview of the embedded development platform and details the components and features of the ML310 board.

#### **Additional Resources**

For additional information, go to <a href="http://support.xilinx.com">http://support.xilinx.com</a>. The following table lists some of the resources you can access from this website. You can also directly access these resources using the provided URLs.

| Resource          | Description/URL                                                                                                                                                      |  |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Tutorials         | Tutorials covering Xilinx design flows, from design entry to verification and debugging                                                                              |  |  |  |

|                   | http://support.xilinx.com/support/techsup/tutorials/index.htm                                                                                                        |  |  |  |

| Answer Browser    | Database of Xilinx solution records                                                                                                                                  |  |  |  |

|                   | http://support.xilinx.com/xlnx/xil_ans_browser.jsp                                                                                                                   |  |  |  |

| Application Notes | Descriptions of device-specific design techniques and approaches <a href="http://support.xilinx.com/apps/appsweb.htm">http://support.xilinx.com/apps/appsweb.htm</a> |  |  |  |

| Data Sheets       | Device-specific information on Xilinx device characteristics, including readback, boundary scan, configuration, length count, and debugging                          |  |  |  |

|                   | http://support.xilinx.com/xlnx/xweb/xil_publications_index.jsp                                                                                                       |  |  |  |

| Resource        | Description/URL                                                                   |  |

|-----------------|-----------------------------------------------------------------------------------|--|

| Problem Solvers | Interactive tools that allow you to troubleshoot your design issues               |  |

|                 | http://support.xilinx.com/support/troubleshoot/psolvers.htm                       |  |

| Tech Tips       | Latest news, design tips, and patch information for the Xilinx design environment |  |

|                 | http://www.support.xilinx.com/xlnx/xil_tt_home.jsp                                |  |

#### **Conventions**

This document uses the following conventions. An example illustrates each convention.

#### Typographical

The following typographical conventions are used in this document:

| Convention         | Meaning or Use                                                                                       | Example                                                                                            |  |

|--------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--|

| Courier font       | Messages, prompts, and program files that the system displays                                        | speed grade: - 100                                                                                 |  |

| Courier bold       | Literal commands that you enter in a syntactical statement                                           | ngdbuild design_name                                                                               |  |

| Helvetica bold     | Commands that you select from a menu                                                                 | File → Open                                                                                        |  |

|                    | Keyboard shortcuts                                                                                   | Ctrl+C                                                                                             |  |

|                    | Variables in a syntax<br>statement for which you must<br>supply values                               | ngdbuild design_name                                                                               |  |

| Italic font        | References to other manuals                                                                          | See the <i>Development System Reference Guide</i> for more information.                            |  |

|                    | Emphasis in text                                                                                     | If a wire is drawn so that it overlaps the pin of a symbol, the two nets are <i>not</i> connected. |  |

| Square brackets [] | An optional entry or parameter. However, in bus specifications, such as bus[7:0], they are required. | ngdbuild [option_name] design_name                                                                 |  |

| Braces { }         | A list of items from which you must choose one or more                                               | lowpwr ={on off}                                                                                   |  |

| Vertical bar       | Separates items in a list of choices                                                                 | lowpwr ={on off}                                                                                   |  |

| Convention          | Meaning or Use                            | Example                                    |  |

|---------------------|-------------------------------------------|--------------------------------------------|--|

| Vertical ellipsis   | Repetitive material that has been omitted | IOB #1: Name = QOUT' IOB #2: Name = CLKIN' |  |

| Horizontal ellipsis | Repetitive material that has been omitted | allow block block_name loc1 loc2 locn;     |  |

#### **Online Document**

The following conventions are used in this document:

| Convention            | Meaning or Use                                            | Example                                                                                     |  |

|-----------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------|--|

| Blue text             | Cross-reference link to a location in the current file or | See the section "Additional Resources" for details.                                         |  |

| blue text             | in another file in the current document                   | Refer to "Title Formats" in Chapter 1 for details.                                          |  |

| Red text              | Cross-reference link to a location in another document    | See Figure 2-5 in the <i>Virtex-II Handbook.</i>                                            |  |

| Blue, underlined text | Hyperlink to a website (URL)                              | Go to <a href="http://www.xilinx.com">http://www.xilinx.com</a> for the latest speed files. |  |

## Introduction to Virtex-II Pro, ISE, and EDK

#### Virtex-II Pro

The Virtex-II Pro Platform FPGA solution is the most technically sophisticated silicon and software product development in the history of the programmable logic industry. The goal was to revolutionize system architecture "from the ground up." To achieve that objective, the best circuit engineers and system architects from IBM, Mindspeed, and Xilinx codeveloped the world's most advanced Platform FPGA silicon product. Leading teams from top embedded systems companies worked together with Xilinx software teams to develop the systems software and IP solutions that enabled new system architecture paradigm.

The result is the first Platform FPGA solution capable of implementing high performance system-on-a-chip designs previously the exclusive domain of custom ASICs, yet with the flexibility and low development cost of programmable logic. The Virtex-II Pro family marks the first paradigm change from programmable logic to programmable systems, with profound implications for leading-edge system architectures in networking applications, deeply embedded systems, and digital signal processing systems. It allows custom user-defined system architectures to be synthesized, next-generation connectivity standards to be seamlessly bridged, and complex hardware and software systems to be codeveloped rapidly with in-system debug at system speeds. Together, these capabilities usher in the next programmable logic revolution.

#### Summary of Virtex-II Pro Features

The Virtex-II Pro has an impressive collection of both programmable logic and hard IP that has historically been the domain of the ASICs.

- High-performance Platform FPGA solution including

- ◆ Up to twenty-four RocketIO<sup>™</sup> embedded multi-gigabit transceiver blocks (based on Mindspeed's SkyRail<sup>™</sup> technology)

- ◆ Up to four IBM® PowerPC™ RISC processor blocks

- Based on Virtex<sup>TM</sup>-II Platform FPGA technology

- Flexible logic resources, up to 125,136 Logic Cells

- SRAM-based in-system configuration

- ◆ Active Interconnect<sup>™</sup> technology

- SelectRAM<sup>TM</sup> memory hierarchy

- Up to 556 Dedicated 18-bit x 18-bit multiplier blocks

- High-performance clock management circuitry

- ♦ SelectIO<sup>TM</sup>-Ultra technology

- Digitally Controlled Impedance (DCI) I/O

| Table 1-1: Virtex-II Pro Family Members | Table 1-1: | Virtex-II | Pro Family | Members |

|-----------------------------------------|------------|-----------|------------|---------|

|-----------------------------------------|------------|-----------|------------|---------|

| Device                | 2VP2  | 2VP4  | 2VP7   | 2VP20  | 2VP30  | 2VP40  | 2VP50  | 2VP70  | 2VP100 | 2VP125  |

|-----------------------|-------|-------|--------|--------|--------|--------|--------|--------|--------|---------|

| Logic Cells           | 3,168 | 6,768 | 11,088 | 20,880 | 30,816 | 43,632 | 53,136 | 74,448 | 99,216 | 125,136 |

| PPC405                | 0     | 1     | 1      | 2      | 2      | 2      | 2      | 2      | 2      | 4       |

| MGTs                  | 4     | 4     | 8      | 8      | 8      | 12     | 16     | 20     | 20     | 24      |

| BRAM<br>(Kbits)       | 216   | 504   | 792    | 1,584  | 2,448  | 3,456  | 4,176  | 5,904  | 7,992  | 10,008  |

| Xtreme<br>Multipliers | 12    | 28    | 44     | 88     | 136    | 192    | 232    | 328    | 444    | 556     |

#### PowerPC™ 405 Core

- Embedded 300+ MHz Harvard architecture core

- Low power consumption: 0.9 mW/MHz

- Five-stage data path pipeline

- Hardware multiply/divide unit

- Thirty-two 32-bit general purpose registers

- 16 KB two-way set-associative instruction cache

- 16 KB two-way set-associative data cache

- Memory Management Unit (MMU)

- 64-entry unified Translation Look-aside Buffers (TLB)

- Variable page sizes (1 KB to 16 MB)

- Dedicated on-chip memory (OCM) interface

- Supports IBM CoreConnect<sup>TM</sup> bus architecture

- Debug and trace support

- Timer facilities

#### RocketIO 3.125 Gb/s Transceivers

- Full-duplex serial transceiver (SERDES) capable of baud rates from 622 Mb/s to 3.125 Gb/s

- 80 Gb/s duplex data rate (16 channels)

- Monolithic clock synthesis and clock recovery (CDR)

- Fibre Channel, Gigabit Ethernet, 10 Gb Attachment Unit Interface (XAUI), and Infiniband-compliant transceivers

- 8-, 16-, or 32-bit selectable internal FPGA interface

- 8B /10B encoder and decoder

- $50\Omega/75\Omega$  on-chip selectable transmit and receive terminations

- Programmable comma detection

- Channel bonding support (two to sixteen channels)

- Rate matching via insertion/deletion characters

- Four levels of selectable pre-emphasis

- Five levels of output differential voltage

- Per-channel internal loopback modes

- 2.5V transceiver supply voltage

#### Virtex-II FPGA Fabric

Description of the Virtex-II Family fabric follows:

- SelectRAM memory hierarchy

- ◆ Up to 10 Mb of True Dual-Port RAM in 18 Kb block SelectRAM resources

- Up to 1.7 Mb of distributed SelectRAM resources

- High-performance interfaces to external memory

- Arithmetic functions

- Dedicated 18-bit x 18-bit multiplier blocks

- Fast look-ahead carry logic chains

- Flexible logic resources

- Up to 111,232 internal registers/latches with Clock Enable

- Up to 111,232 look-up tables (LUTs) or cascadable variable (1 to 16 bits) shift registers

- Wide multiplexers and wide-input function support

- Horizontal cascade chain and Sum-of-Products support

- ♦ Internal 3-state busing

- High-performance clock management circuitry

- Up to eight Digital Clock Manager (DCM) modules

- Precise clock de-skew

- Flexible frequency synthesis

- High-resolution phase shifting

- ♦ 16 global clock multiplexer buffers in all parts

- Active Interconnect technology

- Fourth-generation segmented routing structure

- Fast, predictable routing delay, independent of fanout

- Deep sub-micron noise immunity benefits

- Select I/O-Ultra technology

- ♦ Up to 852 user I/Os

- Twenty two single-ended standards and five differential standards

- Programmable LVTTL and LVCMOS sink/source current (2 mA to 24 mA) per I/O

- Digitally Controlled Impedance (DCI) I/O: on-chip termination resistors for single-ended I/O standards

- ◆ PCI support(1)

- Differential signaling

- 840 Mb/s Low-Voltage Differential Signaling I/O (LVDS) with current mode drivers

- Bus LVDS I/O

- HyperTransport<sup>™</sup> (LDT) I/O with current driver buffers

- Built-in DDR input and output registers

- Proprietary high-performance SelectLink technology for communications between Xilinx devices

- High-bandwidth data path

- Double Data Rate (DDR) link

- Web-based HDL generation methodology

- SRAM-based in-system configuration

- ◆ Fast SelectMAP™ configuration

- Triple Data Encryption Standard (DES) security option (bitstream encryption)

- ♦ IEEE1532 support

- Partial reconfiguration

- Unlimited reprogrammability

- Readback capability

- Supported by Xilinx Foundation<sup>TM</sup> and Alliance<sup>TM</sup> series development systems

- Integrated VHDL and Verilog design flows

- ◆ ChipScope™ Pro Integrated Logic Analyzer

- 0.13-µm, nine-layer copper process with 90 nm high-speed transistors

- 1.5V (VCCINT) core power supply, dedicated 2.5V VCCAUX auxiliary and VCCO I/O power supplies

- IEEE 1149.1 compatible boundary-scan logic support

- Flip-Chip and Wire-Bond Ball Grid Array (BGA) packages in standard 1.00 mm pitch

- Each device 100% factory tested

#### **Foundation ISE**

ISE Foundation is the industry's most complete programmable logic design environment. ISE Foundation includes the industry's most advanced timing driven implementation tools available for programmable logic design, along with design entry, synthesis and verification capabilities. With its ultra-fast runtimes, ProActive Timing Closure technologies, and seamless integration with the industry's most advanced verification products, ISE Foundation offers a great design environment for anyone looking for a complete programmable logic design solution.

#### Foundation Features

#### Design Entry

ISE greatly improves your "Time-to-Market", productivity, and design quality with robust design entry features.

ISE provides support for today's most popular methods for design capture including HDL and schematic entry, integration of IP cores as well as robust support for reuse of your own

IP. ISE even includes technology called IP Builder, which allows you to capture your own IP and reuse it in other designs.

ISE's Architecture Wizards allow easy access to device features like the Digital Clock Manager and Multi-Gigabit I/O technology.

ISE also includes a tool called PACE (Pinout Area Constraint Editor) which includes a front-end pin assignment editor, a design hierarchy browser, and an area constraint editor. By using PACE, designers are able to observe and describe information regarding the connectivity and resource requirements of a design, resource layout of a target FPGA, and the mapping of the design onto the FPGA via location/area.

This rich mixture of design entry capabilities provides the easiest to use design environment available today for your logic design.

#### **Synthesis**

Synthesis is one of the most essential steps in your design methodology. It takes your conceptual Hardware Description Language (HDL) design definition and generates the logical or physical representation for the targeted silicon device.

A state of the art synthesis engine is required to produce highly optimized results with a fast compile and turnaround time. To meet this requirement, the synthesis engine needs to be tightly integrated with the physical implementation tool and have the ability to proactively meet the design timing requirements by driving the placement in the physical device. In addition, cross probing between the physical design report and the HDL design code will further enhance the turnaround time.

Xilinx ISE provides the seamless integration with the leading synthesis engines from Mentor Graphics, Synopsys, and Synplicity. You can use the synthesis engine of our choice. In addition, ISE includes Xilinx proprietary synthesis technology, XST. You have options to use multiple synthesis engines to obtain the best-optimized result of your programmable logic design.

#### Implementation and Configuration

Programmable logic design implementation assigns the logic created during design entry and synthesis into specific physical resources of the target device.

The term "place and route" has historically been used to describe the implementation process for FPGA devices and "fitting" has been used for CPLDs. Implementation is followed by device configuration, where a bitstream is generated from the physical place and route information and downloaded into the target programmable logic device.

To ensure designers get their product to market quickly, Xilinx ISE software provides several key technologies required for design implementation:

- Ultra-fast runtimes enable multiple "turns" per day

- ProActive<sup>™</sup> Timing Closure drives high-performance results

- Timing-driven place and route combined with "push-button" ease

- Incremental Design

- Macro Builder

#### **Board Level Integration**

Xilinx understands the critical issues such as complex board layout, signal integrity, high-speed bus interface, high-performance I/O bandwidth, and electromagnetic interference for system level designers.

To ease the system level designers' challenge, ISE provides support to all Xilinx leading FPGA technologies:

- System IO

- XCITE

- Digital clock management for system timing

- EMI control management for electromagnetic interference

To really help you ensure your programmable logic design works in context of your entire system, Xilinx provides complete pin configurations, packaging information, tips on signal integration, and various simulation models for your board level verification including:

- IBIS models

- HSPICE models

- STAMP models

#### **Embedded Development Kit**

The Embedded Development Kit (EDK) is Xilinx's solution for embedded programmable systems design and supports designs using the Virtex-II Pro. EDK hardware and software development tools, combined with the advanced features of Virtex-II Pro FPGA provide you with a new level of system design.

The system design process can be loosely divided into the following tasks:

- Build the software application

- Simulate the hardware description

- Simulate the hardware with the software application

- Simulate the hardware into the FPGA using the software application in on-chip memory

- Run timing simulation

- Configure the bitstream for the FPGA

## ML310 Embedded Development Platform

#### Overview

The ML310 Embedded Development Platform offers designers a versatile Virtex-II Pro XC2VP30-FF896 based platform for rapid prototyping and system verification. In addition to the more than 30,000 logic cells, over 2,400 Kb of BRAM, dual PowerPC™ 405 processors and RocketIO transceivers available in the FPGA, the ML310 provides an onboard Ethernet MAC/PHY, DDR memory, multiple PCI bus slots, and standard PC I/O ports within an ATX form factor board. An integrated System ACE CF controller is deployed to perform board bring-up and to load applications from the included 512 MB CompactFlash card.

The ML310 CDROM contains documentation and tutorials, along with reference designs and data sheets. The most recent ML310 material can be found on the Xilinx web site at <a href="http://www.xilinx.com/ml310">http://www.xilinx.com/ml310</a>.

The setup and quickstart documentation highlights the functionality of the ML310 using the applications shipped on the included CompactFlash card. The reference designs were produced using the Xilinx Embedded Development Kit (EDK), ISE and Answer Database solution records. Tutorials in coordination with Xilinx documentation for EDK, ISE, and the Answer Database, describe how the reference designs and applications were produced. These tutorials may be used to re-create the applications provided and also as a basis for the development of new designs. Xilinx EDK provides for the development of basic board specific systems beginning with Base System Builder (BSB) to highly customized systems leveraging the flexibility of Xilinx Platform Studio (XPS) and the EDK IP.

Documentation for Xilinx tools and solutions can be found at:

- EDK: http://www.xilinx.com/edk

- ISE: http://www.xilinx.com/ise

- Answer Database: <a href="http://www.xilinx.com/support">http://www.xilinx.com/support</a>

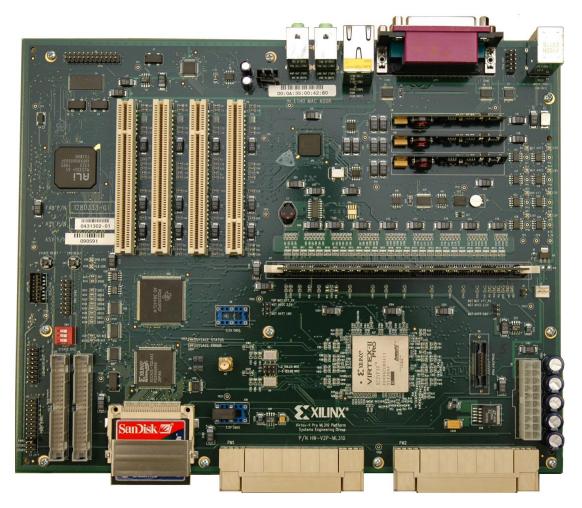

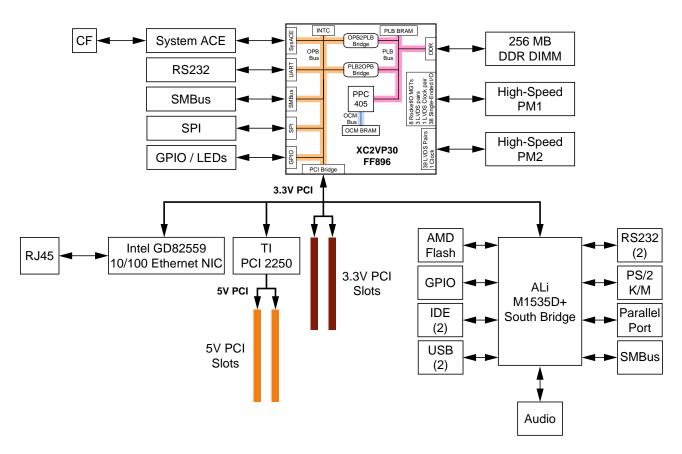

An image of the ML310 board and its corresponding block diagram are shown in, Figure 2-1 and Figure 2-2 respectively.

Figure 2-1: ML310 Board

Figure 2-2 shows a high-level block diagram of the ML310 and its peripherals.

Figure 2-2: ML310 High-Level Block Diagram

#### **Features**

In addition to the Virtex-II Pro™ FPGA with the embedded PPC405, the ML310 board features the following:

- ATX Motherboard formfactor

- 256 MB DDR DIMM

- System ACE<sup>TM</sup> CF Controller

- 512 MB CompactFlash card

- Onboard 10/100 Ethernet NIC

- 4 PCI slots (3.3V and 5V)

- LCD character display and cable

- FPGA serial port connection

- RS-232 mini-cable

- Personality module interface for RocketIO and LVDS access

- Standard JTAG connectivity

- ALi Super I/O

- 1 parallel and 2 serial ports

- ♦ 2 USB ports

- ♦ 2 IDE connectors

- ◆ GPIO

- SMBus Interface

- ♦ AC97 Audio CODEC

- ♦ PS/2 keyboard and mouse ports

- ATX power supply

#### **Board Hardware**

The ML310 Virtex-II Pro FPGA is connected to several peripherals listed below. The peripherals are either directly connected to the FPGA or in directly accessible via the PCI Bus. The following sections describe the main features of each of the peripherals and how they interface with the Xilinx Virtex-II Pro. The EDK *Processor IP Reference Guide* should be reviewed as well as each of the data sheets corresponding to the devices listed. All device data sheets are located on the ML310 CDROM.

- DDR DIMM Memory, compatible with EDK supported IP and SW drivers

- FPGA UART, compatible with EDK supported IP and SW drivers

- System ACE, compatible with EDK supported IP and SW drivers

- GPIO- LEDs / LCD, compatible with EDK supported IP and SW drivers

- PCI Bus Interface, compatible with EDK supported IP and SW drivers

- ♦ ALi M1535D+ PCI Device

- ♦ Intel Ethernet/NIC PCI Device

- SMBus/IIC, multiple devices available, compatible with EDK supported IP and SW drivers

- ♦ LTC1694 SMBUS accelerator

- ◆ RTC8566 Real time clock

- ◆ 24LC64 EEPROM 64k bits

- LM87 voltage/temp monitor

- DDR DIMM SPD EEPROM

- SPI EEPROM, compatible with EDK supported IP and SW drivers

- High speed IO through RocketIO Transceivers

#### Clock Generation

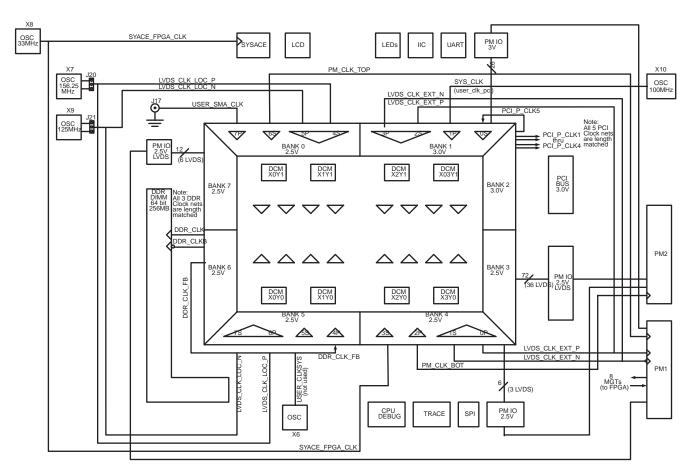

The ML310 board employs a Xilinx XC2VP30-FF896 FPGA. Several clocks are distributed throughout the ML310 as can be seen in Figure 2-3. The main system clock is a 100 MHz oscillator, X10. The system clock is typically used to generate multiple clocks with varying frequency and phases within the FPGA fabric by using the Virtex-II Pro DMCs. The FPGA also generates and drives clocks required by the DDR DIMM memory and PCI bus interfaces.

The FPGA requires different banking voltages that are set based on the I/O voltage interface requirements of each device connected directly to the FPGA. All but two of the banks are set to 2.5V while banks 1 and 2 are set to 3.0V as shown in Figure 2-3. The Virtex-

II Pro FPGA I/O can be configured to use different IO standards such as SSTL2 as required on the DDR DIMM interface. Please review the ML310 Virtex-II Pro data sheet for more information regarding I/O standards.

Figure 2-3 shows the top-level clocking for the ML310 board.

Figure 2-3: Top-Level Clocking

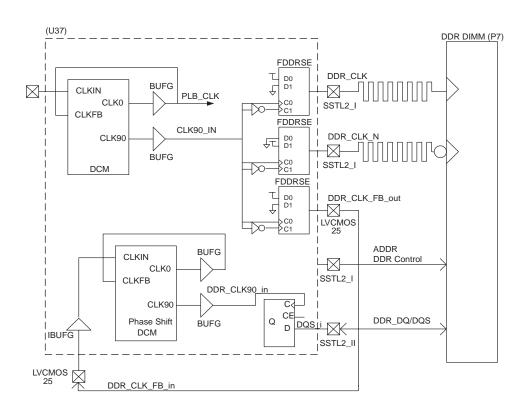

#### **DDR Memory**

#### **DDR DIMM**

The ML310 includes a registered 256MB PC3200 Double Data Rate (DDR) Dual Inline Memory Module (DIMM) with an industry standard 184-pin count. The DDR DIMM is commercially available from Wintec Industries as part number W4F232726HA-5Q. The associated datasheet is provided on the ML310 CDROM. The DDR DIMM is manufactured using nine Infineon HYB25D256800BT-5, 32Mx8 DDR SDRAM devices with 13-row address lines, 10-column address lines, and 4 bank select lines. Read and write access to the Infineon devices is programmable in burst lengths of 2, 4, or 8 column locations. The memory module inputs and outputs are compatible with SSTL2 signaling. Serial Presence Detect (SPD) using an SMBus interface to the DDR DIMM is also supported. Please refer to section "IIC/SMBus Interface" for more details on accessing the DIMM module's SPD EEPROM.

#### **DDR Signaling**

The FPGA DDR DIMM interface supports SSTL2 signaling. All DDR signals are controlled impedance and are SSTL2 terminated.

#### **DDR Memory Expansion**

The FPGA is capable of replicating up to three differential clock output pairs to the DIMM in order to support either registered or unbuffered DIMMs. The ML310 DDR interface is very flexible in the event different DDR memory is desired such as an unbuffered DIMM or increased memory size. The DDR interface core delivered with EDK supports both registered and unbuffered DRR Memory interfaces. Please review the EDK *Processor IP Reference Guide* when migrating to a different DDR DIMM.

Figure 2-4: DDR DIMM Interface Block Diagram

Table 2-1 lists the connections from the FPGA to the DDR DIMM interface. Please note that the DDR\_DQ signal names do not correlate as the FPGA uses IBM notation, Big Endian, while the DDR DIMMs use Intel notation, Little Endian.

Table 2-1: Connections from FPGA to DIMM Interface, P7

| UCF Signal Name | XC2VP30 Pin<br>(U37) | Schem Signal Name | DIMM<br>(P7) |

|-----------------|----------------------|-------------------|--------------|

| ddr_ad[0]       | AE23                 | DDR_A0            | 48           |

| ddr_ad[1]       | AJ23                 | DDR_A1            | 43           |

Table 2-1: Connections from FPGA to DIMM Interface, P7

| UCF Signal Name XC2VP30 Pi<br>(U37) |      | Schem Signal Name | DIMM<br>(P7) |  |

|-------------------------------------|------|-------------------|--------------|--|

| ddr_ad[2]                           | AG20 | DDR_A2            | 41           |  |

| ddr_ad[3]                           | AF23 | DDR_A3            | 130          |  |

| ddr_ad[4]                           | AH22 | DDR_A4            | 37           |  |

| ddr_ad[5]                           | AF22 | DDR_A5            | 32           |  |

| ddr_ad[6]                           | AF21 | DDR_A6            | 125          |  |

| ddr_ad[7]                           | AH21 | DDR_A7            | 29           |  |

| ddr_ad[8]                           | AG21 | DDR_A8            | 122          |  |

| ddr_ad[9]                           | AJ21 | DDR_A9            | 27           |  |

| ddr_ad[10]                          | AK21 | DDR_A10           | 141          |  |

| ddr_ad[11]                          | AH20 | DDR_A11           | 118          |  |

| ddr_ad[12]                          | AF20 | DDR_A12           | 115          |  |

| ddr_ba[0]                           | AG18 | DDR_BA0           | 59           |  |

| ddr_ba[1]                           | AF19 | DDR_BA1           | 62           |  |

| ddr_casb                            | AF17 | DDR_CAS_N         | 65           |  |

| ddr_cke                             | AG24 | DDR_CKE0          | 21           |  |

| ddr_csb                             | AE17 | DDR_S0_N          | 157          |  |

| ddr_rasb                            | AE16 | DDR_RAS_N         | 154          |  |

| ddr_web                             | AD16 | DDR_WE_N          | 63           |  |

| ddr_clk                             | V30  | DDR_CK0           | 137          |  |

| ddr_clkb                            | U30  | DDR_CK0_N         | 138          |  |

| ddr_clk_fb                          | AF16 | DDR_CLK_FB        | N/A          |  |

| ddr_clk_fb_out                      | AG25 | DDR_CLK_FB        | N/A          |  |

| ddr_dm[0]                           | AH29 | DDR_DQM07         | 177          |  |

| ddr_dm[1]                           | AE29 | DDR_DQM06         | 169          |  |

| ddr_dm[2]                           | AA24 | DDR_DQM05         | 159          |  |

| ddr_dm[3]                           | AB30 | DDR_DQM04         | 149          |  |

| ddr_dm[4]                           | P30  | DDR_DQM03         | 129          |  |

| ddr_dm[5]                           | M30  | DDR_DQM02         | 119          |  |

| ddr_dm[6]                           | K24  | DDR_DQM01         | 107          |  |

| ddr_dm[7]                           | E30  | DDR_DQM00         | 97           |  |

| ddr_dqs[0]                          | AG30 | DDR_DQS07         | 86           |  |

| ddr_dqs[1]                          | AF30 | DDR_DQS06         | 78           |  |

| ddr_dqs[2]                          | AA28 | DDR_DQS05         | 67           |  |

| ddr_dqs[3]                          | Y29  | DDR_DQS04         | 56           |  |

| ddr_dqs[4]                          | P28  | DDR_DQS03         | 36           |  |

Table 2-1: Connections from FPGA to DIMM Interface, P7

| UCF Signal Name | XC2VP30 Pin<br>(U37) | Schem Signal Name | DIMM<br>(P7) |  |

|-----------------|----------------------|-------------------|--------------|--|

| ddr_dqs[5]      | M29                  | DDR_DQS02         | 25           |  |

| ddr_dqs[6]      | H29                  | DDR_DQS01         | 14           |  |

| ddr_dqs[7]      | F29                  | DDR_DQS00         | 5            |  |

| ddr_dq[0]       | AG28                 | DDR_DQ63          | 179          |  |

| ddr_dq[1]       | AG26                 | DDR_DQ62          | 178          |  |

| ddr_dq[2]       | AE26                 | DDR_DQ61          | 175          |  |

| ddr_dq[3]       | AD26                 | DDR_DQ60          | 174          |  |

| ddr_dq[4]       | AH27                 | DDR_DQ59          | 88           |  |

| ddr_dq[5]       | AH26                 | DDR_DQ58          | 87           |  |

| ddr_dq[6]       | AF25                 | DDR_DQ57          | 84           |  |

| ddr_dq[7]       | AD25                 | DDR_DQ56          | 83           |  |

| ddr_dq[8]       | AF28                 | DDR_DQ55          | 171          |  |

| ddr_dq[9]       | AD28                 | DDR_DQ54          | 170          |  |

| ddr_dq[10]      | AB25                 | DDR_DQ53          | 166          |  |

| ddr_dq[11]      | AB26                 | DDR_DQ52          | 165          |  |

| ddr_dq[12]      | AF27                 | DDR_DQ51          | 80           |  |

| ddr_dq[13]      | AD27                 | DDR_DQ50          | 79           |  |

| ddr_dq[14]      | AC25                 | DDR_DQ49          | 73           |  |

| ddr_dq[15]      | AC26                 | DDR_DQ48          | 72           |  |

| ddr_dq[16]      | AC27                 | DDR_DQ47          | 162          |  |

| ddr_dq[17]      | AC28                 | DDR_DQ46          | 161          |  |

| ddr_dq[18]      | AA26                 | DDR_DQ45          | 155          |  |

| ddr_dq[19]      | Y26                  | DDR_DQ44          | 153          |  |

| ddr_dq[20]      | AB27                 | DDR_DQ43          | 69           |  |

| ddr_dq[21]      | AB28                 | DDR_DQ42          | 68           |  |

| ddr_dq[22]      | AA25                 | DDR_DQ41          | 64           |  |

| ddr_dq[23]      | Y27                  | DDR_DQ40          | 61           |  |

| ddr_dq[24]      | W28                  | DDR_DQ39          | 151          |  |

| ddr_dq[25]      | W25                  | DDR_DQ38          | 150          |  |

| ddr_dq[26]      | V27                  | DDR_DQ37          | 147          |  |

| ddr_dq[27]      | V25                  | DDR_DQ36          | 146          |  |

| ddr_dq[28]      | W27                  | DDR_DQ35          | 60           |  |

| ddr_dq[29]      | W26                  | DDR_DQ34          | 57           |  |

| ddr_dq[30]      | V28                  | DDR_DQ33          | 55           |  |

| ddr_dq[31]      | V26                  | DDR_DQ32          | 53           |  |

Table 2-1: Connections from FPGA to DIMM Interface, P7

| UCF Signal Name | XC2VP30 Pin<br>(U37) | Schem Signal Name | DIMM<br>(P7) |

|-----------------|----------------------|-------------------|--------------|

| ddr_dq[32]      | N27                  | DDR_DQ31          | 133          |

| ddr_dq[33]      | P26                  | DDR_DQ30          | 131          |

| ddr_dq[34]      | R25                  | DDR_DQ29          | 127          |

| ddr_dq[35]      | R27                  | DDR_DQ28          | 126          |

| ddr_dq[36]      | N28                  | DDR_DQ27          | 40           |

| ddr_dq[37]      | P27                  | DDR_DQ26          | 39           |

| ddr_dq[38]      | R26                  | DDR_DQ25          | 35           |

| ddr_dq[39]      | R28                  | DDR_DQ24          | 33           |

| ddr_dq[40]      | K27                  | DDR_DQ23          | 123          |

| ddr_dq[41]      | L26                  | DDR_DQ22          | 121          |

| ddr_dq[42]      | M27                  | DDR_DQ21          | 117          |

| ddr_dq[43]      | N26                  | DDR_DQ20          | 114          |

| ddr_dq[44]      | K28                  | DDR_DQ19          | 31           |

| ddr_dq[45]      | L27                  | DDR_DQ18          | 28           |

| ddr_dq[46]      | M28                  | DDR_DQ17          | 24           |

| ddr_dq[47]      | N25                  | DDR_DQ16          | 23           |

| ddr_dq[48]      | K25                  | DDR_DQ15          | 110          |

| ddr_dq[49]      | K26                  | DDR_DQ14          | 109          |

| ddr_dq[50]      | J27                  | DDR_DQ13          | 106          |

| ddr_dq[51]      | J28                  | DDR_DQ12          | 105          |

| ddr_dq[52]      | M25                  | DDR_DQ11          | 20           |

| ddr_dq[53]      | M26                  | DDR_DQ10          | 19           |

| ddr_dq[54]      | J25                  | DDR_DQ09          | 13           |

| ddr_dq[55]      | J26                  | DDR_DQ08          | 12           |

| ddr_dq[56]      | H28                  | DDR_DQ07          | 99           |

| ddr_dq[57]      | G27                  | DDR_DQ06          | 98           |

| ddr_dq[58]      | F28                  | DDR_DQ05          | 95           |

| ddr_dq[59]      | E27                  | DDR_DQ04          | 94           |

| ddr_dq[60]      | H27                  | DDR_DQ03          | 8            |

| ddr_dq[61]      | G28                  | DDR_DQ02          | 6            |

| ddr_dq[62]      | F27                  | DDR_DQ01          | 4            |

| ddr_dq[63]      | E28                  | DDR_DQ00          | 2            |

The connections from the FPGA to the DDR DIMM support either a registered or an unbuffered DIMM. The only difference from a connectivity perspective is that the

unbuffered DIMM requires more than one clock input pair versus a single clock input pair for a registered DIMM.

Table 2-2 shows optional clocking connections that are required for interfacing the FPGA to unbuffered DDR DIMMs.

Table 2-2: Optional DDR DIMM Clocks for use with Unbuffered DIMMs

| Schem Signal | XC2VP30 (U37) | DIMM (P7) |

|--------------|---------------|-----------|

| DDR_CK1      | K29           | 16        |

| DDR_CK1_N    | L29           | 17        |

| DDR_CK2      | AD30          | 76        |

| DDR_CK2_N    | AD25          | 75        |

Note: All 3 DDR differential clock pairs are length matched and controlled impedance.

#### Serial Port FPGA UART

#### Introduction to Serial Ports

Serial ports are useful as simple, low-speed interfaces between Data Terminal Equipment (DTE) such as PCs or terminals and Data Communication Equipment (DCE) such as modems. A DTE to DCE connection uses a "straight-through" type of cable in which the transmit (TX) and receive (RX) lines of one end of the cable directly connect to the corresponding TX and RX wires on the other end of the cable. In a DTE to DTE connection a "null-modem" type of cable which cross-wires the TX and RX signals from one end of the cable to the RX and TX signals on the other end is used. Since the ML310 is a DTE, use a "null modem" cable when connecting to another DTE such as a PC.

#### Signaling Standards of RS-232

The RS-232 standard specifies output voltage levels between -5 to -15 Volts for logical 1 and +5 to +15 Volts for logical 0. Inputs must be compatible with voltages in the range of -3V to -15V for logical 1 and +3V to +15V for logical 0. This ensures data bits are read correctly at the maximum cable length of 50 feet between two RS-232 connected devices.

Note: A negative voltage represents a logic level 1 while a positive voltage represents a logic level 0. As these signaling levels are quite high compared to current signaling levels, transceivers are often used to convert to more manageable levels.

#### RS-232 on the ML310

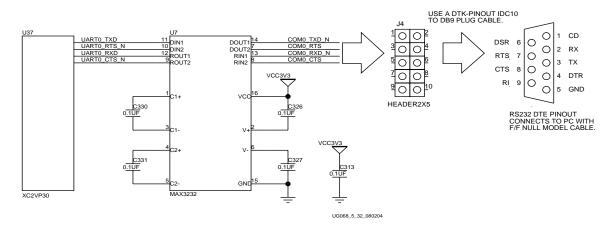

Three RS-232 ports are available on the ML310; two ports (P1) are connected to the ALi M1535D+ South Bridge (U15) and the third (J4) is connected to the XC2VP30 FPGA (U37) through a MAX3232 Transceiver (U7).

The two RS-232 ports connected to the ALi South Bridge(U15) are wired such that the ML310 is a DTE device. These two ports on connector P1 are only accessible by the FPGA through the PCI Bus. Please review section "ALi South Bridge Interface, M1535D+, U15" for more information as well as the M1535D+ data sheet

The third RS-232 port is connected directly to the XC2VP30 FPGA and can be accessed by simply implementing a UART in the FPGA fabric. EDK provides many IP cores, including

a UART usable with any member of the Virtex-II Pro device family. Please review the EDK *Processor IP Reference Guide* for more details.

The RS-232 port directly connected to the XC2VP30 is accessible by a 10 pin header(J4). An RS-232 mini-cable adapter included with the ML310 converts J4, 10 pin header, to a DB9 male connector. The adapter is a standard DTK/Intel IDC-10 to DB9 Male. The FPGA RS-232 port on the ML310 is wired as a DTE and meets the *EIA/TIA-574* standard

Figure 2-5 shows the RS-232 connectivity from the XC2VP30 to the DTK adapter.

.

Figure 2-5: FPGA UART and RS-232 Connectivity

Table 2-3 shows the RS-232 connections to the XCV2VP30 FPGA.

Table 2-3: FPGA RS-232 Connections

| UCF Signal<br>Name | XC2VP30 Pin<br>(U37) | Schem Signal<br>Name | 10 pin Header<br>(J4) | DTK Adapter<br>(DB9) |

|--------------------|----------------------|----------------------|-----------------------|----------------------|

| uart1_ctsn         | B10                  | UART0_CTS            | 6                     | 8                    |

| uart1_rtsn         | G14                  | UART0_RTS            | 4                     | 7                    |

| uart1_sin          | F14                  | UART0_RXD            | 3                     | 2                    |

| uart1_sout         | F12                  | UART0_TXD            | 5                     | 3                    |

#### System ACE CF Controller

#### **Board Bring-Up**

System ACE is the primary means of configuring the XC2VP30 on the ML310 board. Configuration of XC2VP30 is accomplished using the JTAG interface. System ACE sits between the JTAG connector and the XC2VP30, and passes the JTAG signals back and forth between the two. However, when System ACE is configuring the XC2VP30, it takes control of the JTAG signals in order to configure the XC2VP30.

#### Non-Volatile Storage

In addition to programming the FPGA and storing bitstreams, System ACE can be used for general use non-volatile storage. System ACE provides an MPU interface for allowing a microprocessor to access the CompactFlash, allowing the use of the CompactFlash as a file system.

#### XC2VP30 Connectivity

System ACE is connected to the XC2VP30 through both the JTAG chain, for configuration, and through the MPU port of the System ACE, for allowing the XC2VP30 to control System ACE and access the CompactFlash. Table 2-4 shows the connection between the System ACE and the XC2VP30. It shows the signal names with associated pins on System ACE and the XC2VP30 for both the MPU interface.

Table 2-4: System ACE MPU Connection from FPGA to Controller

| UCF Signal Name | XC2VP30 Pin<br>(U37) | Schem Signal<br>Name | System ACE<br>(U38) |

|-----------------|----------------------|----------------------|---------------------|

| sysace_clk_in   | AF15                 | sysace_clk_in        | 93                  |

| sysace_clk_oe   | C22                  | sysace_clk_oe        | 77                  |

| sysace_mpa[0]   | B22                  | sysace_mpa[0]        | 70                  |

| sysace_mpa[1]   | E19                  | sysace_mpa[1]        | 69                  |

| sysace_mpa[2]   | E18                  | sysace_mpa[2]        | 68                  |

| sysace_mpa[3]   | H19                  | sysace_mpa[3]        | 67                  |

| sysace_mpa[4]   | G19                  | sysace_mpa[4]        | 45                  |

| sysace_mpa[5]   | B23                  | sysace_mpa[5]        | 44                  |

| sysace_mpa[6]   | A23                  | sysace_mpa[6]        | 43                  |

| sysace_mpd[0]   | E20                  | sysace_mpd[0]        | 66                  |

| sysace_mpd[1]   | D20                  | sysace_mpd[1]        | 65                  |

| sysace_mpd[2]   | H20                  | sysace_mpd[2]        | 63                  |

| sysace_mpd[3]   | G20                  | sysace_mpd[3]        | 62                  |

| sysace_mpd[4]   | D23                  | sysace_mpd[4]        | 61                  |

| sysace_mpd[5]   | C23                  | sysace_mpd[5]        | 60                  |

| sysace_mpd[6]   | E21                  | sysace_mpd[6]        | 59                  |

| sysace_mpd[7]   | D21                  | sysace_mpd[7]        | 58                  |

| sysace_mpoe     | E23                  | sysace_mpoe          | 77                  |

| sysace_mpce     | E22                  | sysace_mpce          | 42                  |

| sysace_mpwe     | G23                  | sysace_mpwe          | 76                  |

| sysace_mpirq    | F23                  | sysace_mpirq         | 41                  |

#### **JTAG**

JTAG is a simple interface that provides for many uses. On the ML310 Hardware Platform, the primary uses include configuration of the XC2VP30, debugging software (similar to the CPU debug interface), and debugging hardware using the ChipScope<sup>TM</sup> Integrated Logic Analyzer (ILA).

The Virtex-II Pro family is fully compliant with the IEEE Standard 1149.1 Test Access Port and Boundary-Scan Architecture. The architecture includes all mandatory elements defined in the IEEE 1149.1 Standard. These elements include the Test Access Port (TAP), the TAP controller, the instruction register, the instruction decoder, the boundary-scan register, and the bypass register. The Virtex-II Pro family also supports some optional instructions; the 32-bit identification register, and a configuration register in full compliance with the standard.

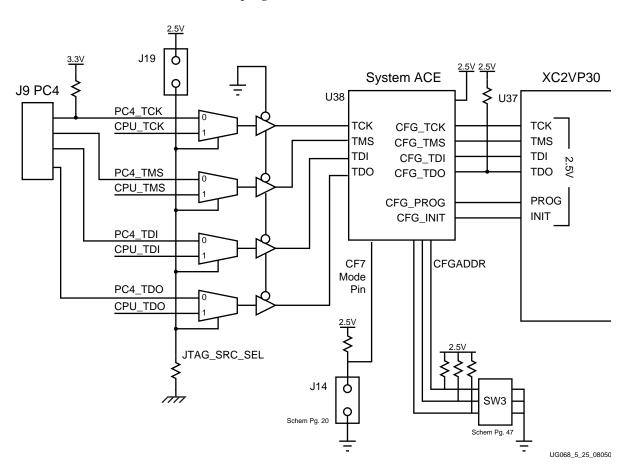

#### JTAG Connection to XC2VP30

The JTAG connector initially connects to the System ACE chip, which passes the JTAG connections through to the XC2VP30. Figure 2-6 is a block diagram showing the connections between the JTAG connector, System ACE, and the XC2VP30. This diagram also shows the logic that allows the CPU JTAG debug connector (J12) to be used to access the JTAG interface to program the XC2VP30.

Figure 2-6: JTAG Connections to the XC2VP30 and System ACE

#### Parallel Cable IV Interface

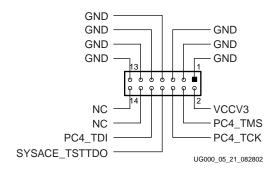

The Parallel Cable IV (PC IV) download cable can also be used to program the XC2VP30. The pinout provided in Figure 2-7 is compatible with the PC IV JTAG programming solution.

Figure 2-7 shows the pinout of the PC IV JTAG connector.

Figure 2-7: PC4 IV JTAG Connector Pinout

#### System ACE JTAG Configuration Interface

The JTAG Configuration port on the System ACE device is connected directly to the JTAG interface of the XC2VP30 device. Table 2-5 shows the JTAG connections from System ACE to the XC2VP30.

Table 2-5: JTAG Connection from System ACE to XC2VP30

| Pin Name | System ACE (U38) | XC2VP30 (U37) |

|----------|------------------|---------------|

| FPGA_TCK | 80               | G7            |

| FPGA_TDO | 81               | F5            |

| FPGA_TDI | 82               | F26           |

| FPGA_TMS | 85               | Н8            |

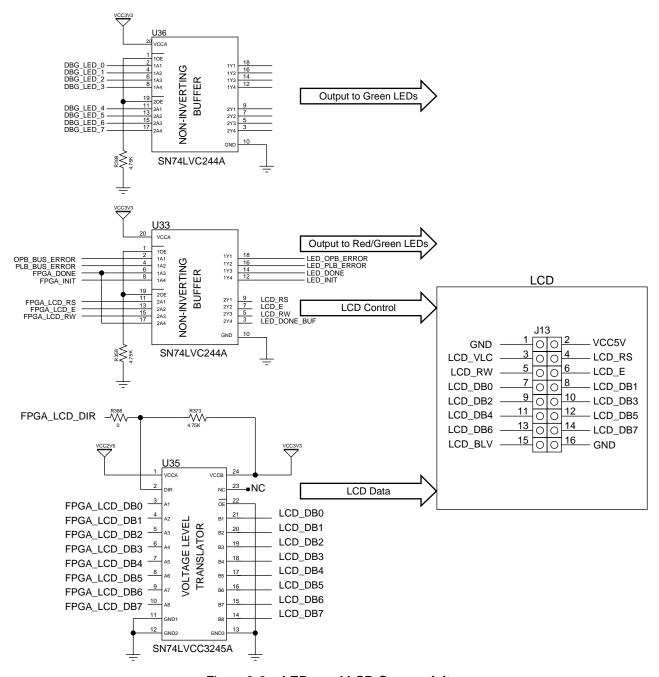

#### GPIO LEDs and LCD

#### **GPIO**

The ML310 Hardware Platform provides direct GPIO access to eight LEDs for general purpose use and provides indirect access to a 16 pin connector (J13) used to interface the ML310 with a 2 Line by 16 character LCD Display, AND491GST. Access to the GPIO lines is handled by a simple register interface that is connected XC2VP30 GPIO signals. Figure 2-8 shows the connectivity of the ML310 LEDs and LCD.

The user also has an indirect access path to more GPIO capability via PCI Bus accesses when controlling the GPIO header (J5) connected to the ALi M1535D+ South Bridge. Please refer to section "ALi South Bridge Interface, M1535D+, U15" for more details on programming and controlling the ALi M1535D+ GPIO port.

Figure 2-8: LEDs and LCD Connectivity

#### **GPIO LED Interface**

All LEDs connected to the GPIO lines illuminate Green when driven with a logic zero and extinguish with a logic one. Table 2-6 shows the connections for the GPIO LEDs from the FPGA to the non-inverting buffer (U36).

Table 2-6: GPIO LED Connection from FPGA to U36

| UCF Signal Name | XC2VP30 Pin<br>(U37) | Schem Signal<br>Name | LVC244 Buffer<br>(U36) | LED  |

|-----------------|----------------------|----------------------|------------------------|------|

| DBG_LED_0       | H13                  | DBG_LED_0            | 2                      | DBG0 |

| DBG_LED_1       | G13                  | DBG_LED_1            | 4                      | DBG1 |

| DBG_LED_2       | C10                  | DBG_LED_2            | 6                      | DBG2 |

| DBG_LED_3       | C11                  | DBG_LED_3            | 8                      | DBG3 |

| DBG_LED_4       | J14                  | DBG_LED_4            | 11                     | DBG4 |

| DBG_LED_5       | H14                  | DBG_LED_5            | 13                     | DBG5 |

| DBG_LED_6       | E14                  | DBG_LED_6            | 15                     | DBG6 |

| DBG_LED_7       | D14                  | DBG_LED_7            | 17                     | DBG7 |

#### **GPIO LCD Interface**

The GPIO signals used to connect to the 16 pin LCD header (J13) are organized into two types of I/O, output only and input/output. There are three output only signals and eight input/output signals. The eight input/outputs are controlled by the logic level of the FPGA\_LCD\_DIR signal. Driving FPGA\_LCD\_DIR to a logic one configures the LVCC3245 to drive the J13 connector while a logic zero configures the LVCC3245 to drive the XC2VP30.

Table 2-7 shows the data bus signals on the GPIO LCD interface from the FPGA to U35.

Table 2-7: GPIO LCD Data Bus Connection from FPGA to U35

| UCF Signal Name | XC2VP30 Pin<br>(U37) | Schem Signal<br>Name | LVCC3245<br>Translator<br>(U35) | LCD I/F<br>(J13) |

|-----------------|----------------------|----------------------|---------------------------------|------------------|

| FPGA_LCD_DB0    | F19                  | FPGA_LCD_DB0         | 3                               | 7                |

| FPGA_LCD_DB1    | F20                  | FPGA_LCD_DB1         | 4                               | 8                |

| FPGA_LCD_DB2    | F17                  | FPGA_LCD_DB2         | 5                               | 9                |

| FPGA_LCD_DB3    | G17                  | FPGA_LCD_DB3         | 6                               | 10               |

| FPGA_LCD_DB4    | B21                  | FPGA_LCD_DB4         | 7                               | 11               |

| FPGA_LCD_DB5    | A21                  | FPGA_LCD_DB5         | 8                               | 12               |

| FPGA_LCD_DB6    | G18                  | FPGA_LCD_DB6         | 9                               | 13               |

| FPGA_LCD_DB7    | H18                  | FPGA_LCD_DB7         | 10                              | 14               |

| FPGA_LCD_DIR    | C20                  | FPGA_LCD_DIR         | 2                               | -                |

The three GPIO signals configured as outputs only are used as control signals that allows the user to read/write the LCD character display in conjunction with the eight LCD data signals defined earlier in Table 2-7. Please review the AND491GST LCD display data sheet located on the ML310 CDROM for more detailed information.

Table 2-8 shows the control signal connections for the GPIO LCD from the FPGA to U33.

Table 2-8: GPIO LCD Control Signal Connections from FPGA to U33

| UCF Signal Name | XC2VP30 Pin<br>(U37) | Schem Signal<br>Name | LVC244<br>Buffer (U33) | LCD I/F<br>(J13) |

|-----------------|----------------------|----------------------|------------------------|------------------|

| FPGA_LCD_E      | C21                  | FPGA_LCD_E           | 13                     | 6                |

| FPGA_LCD_RS     | J17                  | FPGA_LCD_RS          | 11                     | 4                |

| FPGA_LCD_RW     | H17                  | FPGA_LCD_RW          | 15                     | 5                |

#### CPU Debug and CPU Trace

The ML310 board includes two CPU debugging interfaces, the CPU Debug (J12 header) and the Combined CPU Trace and Debug (P8 mictor) connector.

These connectors can be used in conjunction with third party tools, or in some cases the Xilinx Parallel Cable IV, to debug software as it runs on the processor. The PowerPC<sup>TM</sup> 405 CPU core includes dedicated debug resources that support a variety of debug modes for debugging during hardware and software development. These debug resources include:

- Internal debug mode for use by ROM monitors and software debuggers

- External debug mode for use by JTAG debuggers

- Debug wait mode, which allows the servicing of interrupts while the processor appears to be stopped

- Real-time trace mode, which supports event triggering for real-time tracing

Debug modes and events are controlled using debug registers in the processor. The debug registers are accessed either through software running on the processor or through the JTAG port. The debug modes, events, controls, and interfaces provide a powerful combination of debug resources for hardware and software development tools. The JTAG port interface supports the attachment of external debug tools, such as the ChipScope<sup>TM</sup> Integrated Logic Analyzer, a powerful tool providing logic analyzer capabilities for signals inside an FPGA, without the need for expensive external instrumentation. Using the JTAG test access port, a debug tool can single-step the processor and examine the internal processor state to facilitate software debugging. This capability complies with the IEEE 1149.1 specification for vendor-specific extensions and is, therefore, compatible with standard JTAG hardware for boundary-scan system testing. (1)

#### **CPU Debug Description**

External-debug mode can be used to alter normal program execution. It provides the ability to debug system hardware as well as software. The mode supports multiple setting breakpoints, as well as monitoring processor status. Access to processor resources is provided through the CPU Debug port. (2)

<sup>1.</sup> http://www.support.xilinx.com/ PowerPC Architecture - Debug (JTAG, Trace), Sept. 12, 2002

<sup>2.</sup> Virtex-II Pro Platform FPGA Documentation - Volume 2(a): PPC405 User Manual, March 2002 Release, p. 537.

The PPC405 JTAG (Joint Test Action Group) Debug port complies with IEEE standard 1149.1-1990, IEEE Standard Test Access Port and Boundary Scan Architecture. This standard describes a method for accessing internal chip resources using a four-signal or five-signal interface. The PPC405 JTAG Debug port supports scan-based board testing and is further enhanced to support the attachment of debug tools. These enhancements comply with the IEEE 1149.1 specifications for vendor-specific extensions and are compatible with standard JTAG hardware for boundary-scan system testing.

The PPC405 JTAG debug port supports the four required JTAG signals: TCK, TMS, TDI, and TDO. It also implements the optional TRST signal. The frequency of the JTAG clock signal can range from 0 MHz (DC) to one-half of the processor clock frequency. The JTAG debug port logic is reset at the same time the system is reset, using TRST. When TRST is asserted, the JTAG TAP controller returns to the test-logic reset state.

Refer to the PPC405 Processor Block Manual for more information on the JTAG debug-port signals. Information on JTAG is found in the IEEE standard 1149.1-1990.<sup>(3)(3)</sup>

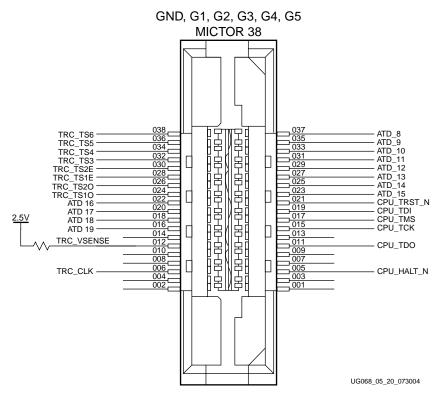

Figure 2-9 shows a 38-pin Mictor connector that combines the CPU Trace and the CPU Debug interfaces for high-speed, controlled-impedance signaling. For more information functions: starting and stopping the processor, single-stepping instruction execution on the trace-debug capabilities, how trace-debug works, and how to connect an external trace tool, see the *RISCWatch Debugger User's Guide*.

Figure 2-9: Combined Trace/Debug Connector Pinout

<sup>3.</sup> Virtex-II Pro Platform FPGA Documentation - Volume 2(a): PPC405 User Manual, March 2002 Release, p. 557.

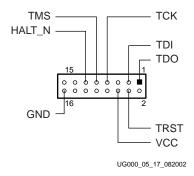

#### **CPU Debug Connector Pinout**

Figure 2-10 shows J12, the 16 pin header used to debug the operation of software in the CPU. This is done using debug tools such as Parallel Cable IV or third party tools. Refer to the *PPC405 Processor Block Manual* for more information on the JTAG debug-port signals.

Figure 2-10: CPU Debug Connector (J12)

#### CPU Debug Connection to XC2VP30

The connection between the CPU debug connector and the XC2VP30 are shown in Table 2-9. These are attached to the PowerPC<sup>TM</sup> 405 JTAG debug resources using normal FPGA routing resources. The JTAG debug resources are not hard-wired to particular pins, and are available for attachment in the FPGA fabric, making it possible to route these signals to whichever FPGA pins the user prefers.

| Pin Name | XC2VP30 Pin (U37) | Connector Pin (J12) |

|----------|-------------------|---------------------|

| TDO      | AH19              | 1                   |

| TDI      | AJ9               | 3                   |

| TRST_N   | AE12              | 4                   |

| TCK      | AC13              | 7                   |

| TMS      | AD13              | 9                   |

| HALT_N   | AE11              | 11                  |

Table 2-9: CPU Debug Connection to XC2VP30

#### **PCI** Bus

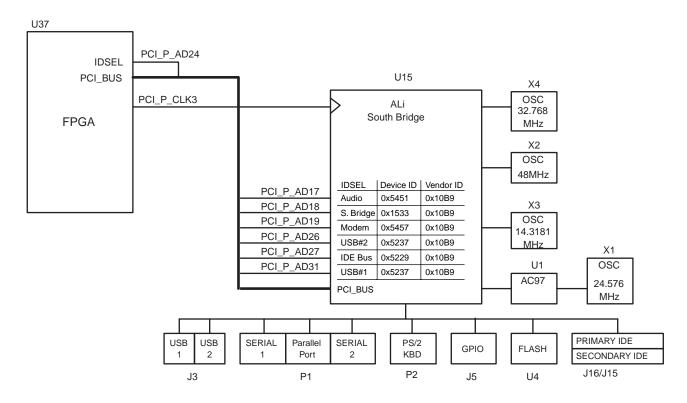

The ML310 board design provides the Xilinx Virtex-II Pro access to two 33MHz/32bit PCI buses, Primary 3.3V PCI Bus and a Secondary 5.0V PCI Bus. The FPGA is directly connected to the Primary 3.3V PCI bus while the 5.0V PCI Bus is connected to the Primary PCI Bus via a PCI-to-PCI Bridge. There are several PCI devices available on the PCI Buses as well as 4 PCI add-in card Slots. All PCI Bus signals driven by the XC2VP30 comply with the IO requirements specified in the PCI Local Bus Specification, Revision 2.2.

The majority of the ML310 features are accessed over the 33MHz/32 bit PCI Bus. The Virtex-II Pro Power PC405 Processors can gain access to the Primary PCI Bus through the EDK PCI Host Bridge IP. All PCI configuration and control can be performed via a PCI Host Bridge implemented in the FPAG fabric. The Primary PCI Bus is wired so that the FPGA fabric must used to provide PCI Bus arbitration logic. The EDK kit also provides PCI

Arbiter IP. Please see the EDK *Processor IP Reference Guide* for more information about the EDK IP mentioned in this section.

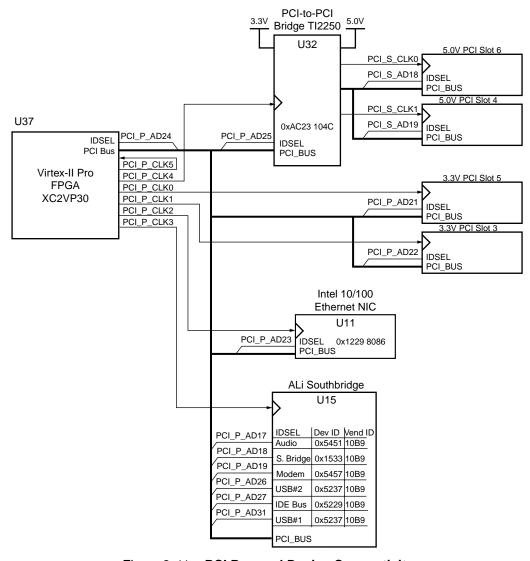

The FPGA is responsible generating the PCI RST signal as well as the PCI CLK signal. The FPGA fabric is used to generate six PCI Clocks that drive each of the PCI devices/slots shown in the Figure 2-11. All six PCI Clock outputs are length matched. Since the FPGA generates all PCI Clocks, the downstream PCI devices have no clock input prior to or during FPGA configuration therefore, PCI Reset should be de-asserted after the PCI CLK has stabilized. Please review the *PCI Local Bus Specification*, *Revision 2.2* for more detailed information.

The on-board 33MHz/32 bit PCI Bus is connected to three fixed PCI devices that are part of the ML310 board. These devices are listed below and more information on the devices can be found in the following sections as well their data sheets on the ML310 CDROM

- Texas Instruments, TI2250, PCI-to-PCI Bridge

- Intel, GD82559, 10/100 PCI Ethernet NIC.

- ♦ Ali, M1535D+, PCI South Bridge

In addition to the three fixed PCI devices, there are a total of four 33MHz/32 Bit PCI slots available for use. For more information on the PCI slot pinouts, refer to the PCI Local Bus Specification, Revision 2.2 and the ML310 schematics.

- ◆ 2 3.3V Keyed PCI Add In Card Slots (P5 and P3)

- ◆ 2 5.0V Keyed PCI Add In Card Slots (P6 and P4)

**Note:** The 5.0V PCI slots differ from the 3.3V slots. See the Important Instructions sheet (PN 0402263) packaged with the ML310 kit before using Universal PCI add-in cards with the ML310 board.

Figure 2-11 shows the connectivity of the PCI bus and PCI devices. For more information on the PCI slot pinouts, refer to the PCI 2.2 Specification or review the ML310 schematics. The 5.0V PCI slots differ from the 3.3V slots. See the **Important Instructions** sheet (PN 0402263) packaged with the ML310 kit before using Universal PCI add-in cards with the ML310 board.

Figure 2-11: PCI Bus and Device Connectivity

Table 2-10 shows the connections for the PCI controller.

Table 2-10: PCI Controller Connections

| UCF Signal Name | XC2VP30 Pin (U37) | Description |

|-----------------|-------------------|-------------|

| PCI_CLK0        | T2                | PCI_P_CLK0  |

| PCI_CLK1        | R2                | PCI_P_CLK1  |

| PCI_CLK2        | R5                | PCI_P_CLK2  |

| PCI_CLK3        | R6                | PCI_P_CLK3  |

| PCI_CLK4        | R3                | PCI_P_CLK4  |

| PCI_CLK5        | R4                | PCI_P_CLK5  |

| PCI_CLK5_FB     | C15               | PCI_P_CLK5  |

Table 2-10: PCI Controller Connections (Continued)

| UCF Signal Name | XC2VP30 Pin (U37) | Description               |  |

|-----------------|-------------------|---------------------------|--|

| PCI_INTA        | L5                |                           |  |

| PCI_INTB        | N2                |                           |  |

| PCI_INTC        | M2                | DCI Interment Cinnels     |  |

| PCI_INTD        | R9                | - PCI Interrupt Signals   |  |

| PCI_INTE        | P9                | _                         |  |

| PCI_INTF        | M3                |                           |  |

| PCI_REQ0_N      | P1                |                           |  |

| PCI_REQ1_N      | N1                | _                         |  |

| PCI_REQ2_N      | P7                | PCI Request Signals       |  |

| PCI_REQ3_N      | P8                |                           |  |

| PCI_REQ4_N      | N3                | _                         |  |

| PCI_GNT0_N      | P2                |                           |  |

| PCI_GNT1_N      | P3                | _                         |  |

| PCI_GNT2_N      | R7                | PCI Grant Signals         |  |

| PCI_GNT3_N      | R8                |                           |  |

| PCI_GNT4_N      | P4                |                           |  |

| PCI_CBE[0]      | J2                |                           |  |

| PCI_CBE[1]      | H2                | DCI Posto Escablo Cincolo |  |

| PCI_CBE[2]      | M7                | PCI Byte Enable Signals   |  |

| PCI_CBE[3]      | M8                |                           |  |

| PCI_FRAME_N     | K6                |                           |  |

| PCI_IRDY_N      | K1                | _                         |  |

| PCI_TRDY_N      | J1                |                           |  |

| PCI_STOP_N      | M5                |                           |  |

| PCI_DEVSEL_N    | M6                | PCI Control Signals       |  |

| PCI_PERR_N      | J3                |                           |  |

| PCI_SERR_N      | J4                |                           |  |

| PCI_LOCK        | L2                |                           |  |

| PCI_IDSEL       | K2                |                           |  |

| PCI_REQ64_N*    | F8                | # PM_IO_3V_1              |  |

| PCI_ACK64_N*    | E8                | # PM_IO_3V_2              |  |

Table 2-10: PCI Controller Connections (Continued)

| UCF Signal Name | XC2VP30 Pin (U37) | Description               |

|-----------------|-------------------|---------------------------|

| PCI_AD[0]       | G5                |                           |

| PCI_AD[1]       | G6                |                           |

| PCI_AD[2]       | D5                |                           |

| PCI_AD[3]       | C5                |                           |

| PCI_AD[4]       | C1                |                           |

| PCI_AD[5]       | C2                |                           |

| PCI_AD[6]       | J7                |                           |

| PCI_AD[7]       | J8                |                           |

| PCI_AD[8]       | D3                |                           |

| PCI_AD[9]       | C4                |                           |

| PCI_AD[10]      | D1                |                           |

| PCI_AD[11]      | D2                |                           |

| PCI_AD[12]      | H5                |                           |

| PCI_AD[13]      | Н6                |                           |

| PCI_AD[14]      | E3                |                           |

| PCI_AD[15]      | E4                | PCI Address/Data Lines    |

| PCI_AD[16]      | E1                | — TCI Address/ Data Lines |

| PCI_AD[17]      | E2                |                           |

| PCI_AD[18]      | K7                |                           |

| PCI_AD[19]      | K8                |                           |

| PCI_AD[20]      | F3                |                           |

| PCI_AD[21]      | F4                |                           |

| PCI_AD[22]      | F1                |                           |

| PCI_AD[23]      | F2                |                           |

| PCI_AD[24]      | J5                |                           |

| PCI_AD[25]      | J6                |                           |

| PCI_AD[26]      | G3                |                           |

| PCI_AD[27]      | G4                |                           |

| PCI_AD[28]      | G1                |                           |

| PCI_AD[29]      | G2                |                           |

| PCI_AD[30]      | L7                |                           |

| PCI_AD[31]      | L8                |                           |

| PCI_PAR         | H3                | PCI_P_PAR                 |

| PCI_RST_N       | N8                | PCI_P_RST_N               |

<sup>\*</sup> Note: These signals are connected, but are not required for 32 bit only PCI systems.

Table 2-11 describes how the Primary PCI Bus interrupts are connected on the ML310 board along with each devices IDSEL, REQ/GNT, PCI Clocks and DeviceID/Vendor ID information.

Table 2-11: 3.3V Primary PCI Bus Information

| Device Name      | Device<br>ID | Vendor<br>ID | Bus | DEV | IDSEL | REQ  | FPGA<br>PCI<br>CLK | INTR    |

|------------------|--------------|--------------|-----|-----|-------|------|--------------------|---------|

| PCI Slot 5       | N/A          | N/A          | 0   | 5   | AD21  | 0    | 0                  | A,B,C,D |

| PCI Slot 3       | N/A          | N/A          | 0   | 6   | AD22  | 1    | 1                  | B,C,D,A |

| U11, Enet Mac    | 0x1229       | 0x8086       | 0   | 7   | AD23  | 2    | 2                  | С       |

| U15, ALI SB      | 0x1533       | 0x10B9       | 0   | 2   | AD18  | 3    | 3                  | INT,NMI |

| U15, ALi Pwr Mgt | 0x7101       | 0x10B9       | 0   | 12  | AD28  | 3    | 3                  | INT,NMI |

| U15, ALI IDE     | 0x5299       | 0x10B9       | 0   | 11  | AD27  | 3    | 3                  | INT,NMI |

| U15, ALi Audio   | 0x5451       | 0x10B9       | 0   | 1   | AD17  | 3    | 3                  | INT,NMI |

| U15, Ali Modem   | 0x5457       | 0x10B9       | 0   | 3   | AD19  | 3    | 3                  | INT,NMI |

| U15, ALi USB#1   | 0x5237       | 0x10B9       | 0   | 15  | AD31  | 3    | 3                  | INT,NMI |

| U15, ALi USB#2   | 0x5237       | 0x10B9       | 0   | 10  | AD26  | 3    | 3                  | INT,NMI |

| U32, PCI-PCI Brg | 0xAC23       | 0x104C       | 0   | 9   | AD25  | 4    | 4                  | N/A     |

| U37, XC2VP30     | 0x0300       | 0x10EE       | 0   | 8   | AD24  | Int. | 5                  | N/A     |

Table 2-12 describes how the Secondary PCI Bus interrupts are connected on the ML310 board along with each devices IDSEL, REQ/GNT, PCI Clocks and DeviceID/Vendor ID information.

Table 2-12: 5.0V Secondary PCI Bus Information

| Device Name      | Device<br>ID | Vendor<br>ID | Bus | DEV | IDSEL | REQ  | Bridge<br>CLK | INTR    |

|------------------|--------------|--------------|-----|-----|-------|------|---------------|---------|

| PCI Slot 6       | N/A          | N/A          | 1   | 2   | AD18  | 0    | 0             | A,B,C,D |

| PCI Slot 4       | N/A          | N/A          | 1   | 3   | AD19  | 1    | 1             | B,C,D,A |

| U32, PCI-PCI Brg | N/A          | N/A          | N/A | 7   | N/A   | Int. | 4             | N/A     |