# Intel® PXA27x Processor Family Power Requirements

**Application Note**

Order Number: 280005-002

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel® PXA27x processor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

This document and the software described in it are furnished under license and may only be used or copied in accordance with the terms of the license. The information in this document is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by Intel Corporation. Intel Corporation assumes no responsibility or liability for any errors or inaccuracies that may appear in this document or any software that may be provided in association with this document. Except as permitted by such license, no part of this document may be reproduced, stored in a retrieval system, or transmitted in any form or by any means without the express written consent of Intel Corporation.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2004

AlertVIEW, i960, AnyPoint, AppChoice, BoardWatch, BunnyPeople, CablePort, Celeron, Chips, Commerce Cart, CT Connect, CT Media, Dialogic, DM3, EtherExpress, ETOX, FlashFile, GatherRound, i386, i486, iCat, iCOMP, Insight960, InstantIP, Intel Jogo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel ChatPad, Intel Create&Share, Intel Dct. Station, Intel GigaBlade, Intel Insuisness, Intel Inside, Intel Inside, Intel Play, Intel Play logo, Intel Pocket Concert, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel TeamStation, Intel WebOutfitter, Intel Xeon, Intel XScale, Itanium, JobAnalyst, LANDesk, LanRover, MCS, MMX, MMX logo, NetPort, NetportExpress, Optimizer logo, OverDrive, Paragon, PC Dads, PC Parents, Pentium, Pentium II Xeon, Pentium III Xeon, Performance at Your Command, ProShare, RemoteExpress, Screamline, Shiva, SmartDie, Solutions960, Sound Mark, StorageExpress, The Computer Inside, The Journey Inside, This Way In, TokenExpress, Trillium, Vivonic, and VTune are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

| 1.0 | Intro                                  | oduction                                                                                                                                                                                                                                                                                                                                                                                                                      | 5                    |

|-----|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|     | 1.1                                    | Naming Conventions                                                                                                                                                                                                                                                                                                                                                                                                            | 5                    |

| 2.0 | Intel                                  | ® PXA27x Processor Power Supply Domains                                                                                                                                                                                                                                                                                                                                                                                       | 5                    |

|     | 2.1                                    | Power Domains and System Voltage/Current Requirements                                                                                                                                                                                                                                                                                                                                                                         |                      |

|     |                                        | 2.2.3 Battery Chargers and Main Power                                                                                                                                                                                                                                                                                                                                                                                         | 15                   |

| 3.0 | Intel                                  | ® PXA27x Processor Low Power Operating Modes                                                                                                                                                                                                                                                                                                                                                                                  | 17                   |

| 4.0 | Pow                                    | er Controller Interface Signals                                                                                                                                                                                                                                                                                                                                                                                               | 18                   |

|     | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6 | Power Enable (PWR_EN)  System Power Enable (SYS_EN) / GPIO<2>  Power Manager I2C Clock (PWR_SCL) / GPIO<3>  Power Manager I2C Data (PWR_SDA) / GPIO<4>)  System-Level Considerations for I2C  On, Off, and RESET  4.6.1 On and Off Control  4.6.2 User-Initiated Hard Reset Input  4.6.3 nRESET Output from PMIC to the Intel® PXA27x Processor  Universal Subscriber Identity Module (USIM)  Power Manager Capacitor Signals |                      |

| 5.0 | Pow                                    | er Mode Sequencing                                                                                                                                                                                                                                                                                                                                                                                                            | 22                   |

|     | 5.1                                    | Power-On                                                                                                                                                                                                                                                                                                                                                                                                                      | 22<br>23<br>24<br>27 |

| 6.0 | Dyna                                   | amic Voltage Management (DVM)                                                                                                                                                                                                                                                                                                                                                                                                 | 29                   |

|     | 6.1<br>6.2<br>6.3<br>6.4               | VCC_CORE Regulator and Dynamic Voltage Management Intel® PXA27x Processor Voltage Manager Power Manager I2C Interface DVM Sequencing                                                                                                                                                                                                                                                                                          | 30<br>31             |

| 7.0 | Fault                                  | t Management                                                                                                                                                                                                                                                                                                                                                                                                                  | 31                   |

|     | 7.1                                    | nVDD_FAULT                                                                                                                                                                                                                                                                                                                                                                                                                    | 31                   |

# Intel® PXA27x Processor Family Power Requirements Contents

|            | 7.2 nBA1                | TT_FAULT                                               | 32 |

|------------|-------------------------|--------------------------------------------------------|----|

| 8.0        | Power Man               | nagement Integrated Circuit Requirements               | 32 |

|            | 8.1 Gene                | eral PMIC Characteristics                              | 32 |

|            |                         | ures of a PMIC                                         |    |

|            |                         | rammable Voltage Control                               |    |

|            | 8.3.1                   |                                                        |    |

|            | 8.3.2                   |                                                        |    |

|            | 8.3.3                   | <u> </u>                                               |    |

|            | 8.3.4                   | Other Aspects of an Integrated Power Controller        | 35 |

| 9.0        | Summary                 |                                                        | 35 |

| <b>Fig</b> | <b>JUPES</b> Intel® PXA | A27x Processor Internal and External Power Domains     | 7  |

| 2          | Typical Ba              | attery and External Regulator Configuration            | 16 |

| 3          | Overview                | of Power Management Operating Modes                    | 18 |

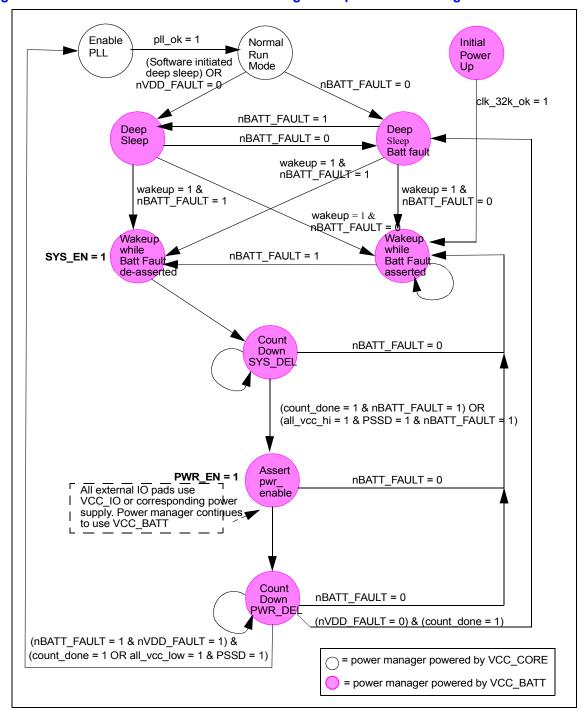

| 4          | Intel® PX/              | A27x Processor Power Manager Sleep Reset State Diagram | 26 |

| Ta         | bles                    |                                                        |    |

| 1          | External F              | Power Supply Descriptions                              | 6  |

| 2          | Intel® PX               | A27x Processor Voltage Domains                         | 9  |

| 3          |                         | rs Required to Power the Intel® PXA27x Processor       |    |

| 4          |                         | A27x Processor Supply Current For Each Power Domain    |    |

| 5          |                         | A27x Processor VCC_CORE Supply Current                 |    |

| 6          |                         | Backup Battery Configurations                          |    |

| 7          | Intel® PX               | A27x Processor Operating Modes                         | 17 |

| 8          |                         | ontroller Interface Signals                            |    |

| 9          | General P               | PMIC Characteristics                                   | 33 |

### 1.0 Introduction

The Intel® PXA27x Processor Family (PXA27x processor) is a highly integrated system-on-chip optimized for handheld battery-powered devices such as PDAs and 2.5G or 3G cell phones. The PXA27x processor is ideal for products requiring substantial computing and multimedia capability with very low power consumption.

The PXA27x processor combines a high-performance CPU with a variety of integrated peripheral functions. The processor has separate power supply domains for the processor core, memory, and peripherals to enable low-power system design. The PXA27x processor provides several dedicated control signals as well as an I<sup>2</sup>C interface to connect to an external power management integrated circuit.

Other system components, such as SDRAM and flash memory, audio codecs, touchscreen controllers, and specialized companion chips, have with their own unique power requirements. In many designs, a highly integrated power controller supplies power for these other components, particularly those that interface directly to the PXA27x processor. An advanced power controller can contain circuitry for charging batteries, powering the display panel, and include other analog functions required by the system.

In any system design, factors such as operating conditions, application workload, environmental considerations and the sophistication of the device's power management software all play a role in determining the amount of power consumed. When designing a system, manufacturers need to take into account where the device is intended to be used (such as high temperature environments) and what it is expected to do for an end user (such as play a game, a video or do simple email transactions).

The Intel® PXA27x Processor Family EMTS provides manufacturers with a typical system power consumption specification for all frequencies of the processor family. The purpose of this application note is to provide guidance on how power consumption, in a typical environment can change, based on different software workloads. In addition, this application note provides further details on the requirements for providing power to the processor and for interfacing to its power control signals, including behavioral requirements and typical system design examples under these workloads.

The power numbers generated utilized Intel development platforms in lab conditions and the information provided should be used as a guideline only.

# 1.1 Naming Conventions

In this document, active low items are prefixed with a lowercase "n".

nRESET

Bits within a signal name are enclosed in angle brackets:

EXTERNAL\_ADDRESS<31:0> nCS<1>

Bits within a register bit field are enclosed in square brackets:

REGISTER\_BITFIELD[3:0]

REGISTER\_BIT[0]

The terms *run mode* and *normal mode* are used interchangeably, although normal mode comprises both the run-mode and turbo-mode settings.

# 2.0 Intel® PXA27x Processor Power Supply Domains

Viewed externally, the main or backup battery powers ten power-supply domains. Additional supply domains are present internally, but power for these is derived from the external supply inputs.

All functional units within a power domain connect to the same power supply and are powered up and down together. The PXA27x processor architecture, with its multiple power-supply domains, provides flexibility in system configuration (including selection of I/O voltages for different memory and peripherals) and efficient power management (for instance, flexibility in selecting which peripherals are powered at the same time). Together, these let system designers make power/complexity trade-offs and optimize a product for intended markets.

Product designers can also choose to strap certain supplies together (to power several domains from a common regulator) to reduce complexity, cost, and the number of regulators in the system. Guidelines showing which supplies can be combined are provided in this document.

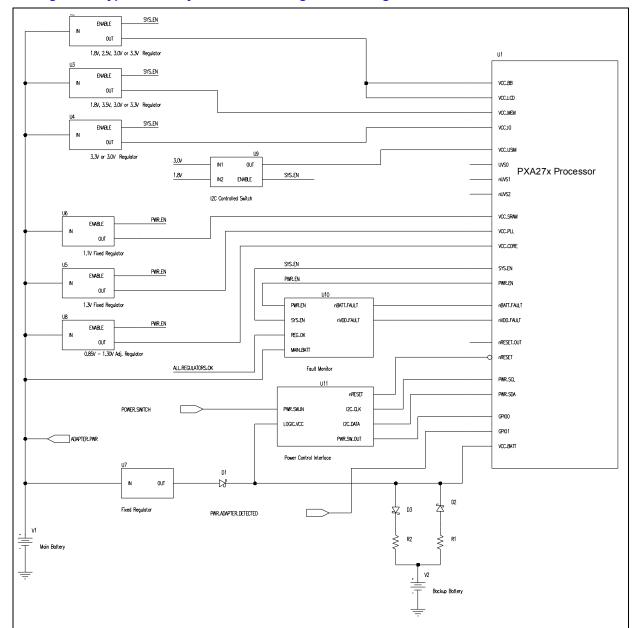

A summary of the voltage and tolerance requirements for each external supply input is shown in Table 1. Figure 1 shows the PXA27x processor internal and external power domains and their connections.

**Table 1. External Power Supply Descriptions**

| Power Domain                                 | Enable <sup>1</sup> | Units                                                    | Specified Levels<br>(Volts)       | Tolerance<br>(%)                  |

|----------------------------------------------|---------------------|----------------------------------------------------------|-----------------------------------|-----------------------------------|

| VCC_BATT                                     | None                | Sleep-control subsystem, oscillators and real-time clock | 3.0                               | ± 25                              |

| VCC_IO                                       | SYS_EN              | Peripheral input/output                                  | 3.0, 3.3                          | ±10 (@ 3.0 V<br>=10%, -10.3%)     |

| VCC_LCD                                      | SYS_EN              | LCD input/output                                         | 1.8, 2.5, 3.0, 3.3                | +20,-5 (@ 1.8 V)<br>otherwise ±10 |

| VCC_MEM                                      | SYS_EN              | Memory controller input/output                           | 1.8, 2.5, 3.0, 3.3                | +20,-5 (@ 1.8 V)<br>otherwise ±10 |

| VCC_BB                                       | SYS_EN              | Baseband interface                                       | 1.8, 2.5, 3.0, 3.3                | +20,-5 (@ 1.8 V)<br>otherwise ±10 |

| VCC_USIM                                     | SYS_EN              | USIM interface                                           | 1.8, 3.0                          | +20,-5 (@ 1.8 V)<br>otherwise ±10 |

| VCC_USB                                      | SYS_EN              | Differential USB input/output                            | 3.0, 3.3                          | ±10                               |

| VCC_PLL                                      | PWR_EN              | Phase-locked loops                                       | 1.3                               | ±10                               |

| VCC_SRAM                                     | PWR_EN              | Internal SRAM units                                      | 1.1                               | ±10                               |

| VCC_CORE PWR_EN CPU and other internal units |                     | CPU and other internal units                             | variable 0.85 – 1.55 <sup>1</sup> | -5 +10                            |

NOTE: SYS\_EN and PWR\_EN are PXA27x processor output control signals.

<sup>1.</sup> PXA27x processors have different maximum frequencies and VCC\_CORE voltages. Refer to both of the Intel® PXA27x Processor Family EMTSs for details.

VCC\_PLL VCC\_CORE VCC\_SRAM VCC\_PLL VCC\_CPU CPU C-PLL Intr prg. frq. Control vcc\_osc VCC\_MEM MEM Control P-PLL 312 M VCC\_PER LCD vcc\_osc Control **PXTAL** SRAM 13 M Control **TXTAL** USB-H 32.768 k 48.000 M VCC\_USB DMA/ Bridge USB-C DC-DC 48.000 M VCC\_R3 Lin-Reg SRAM ICP 48.000 M VCC\_RTC CPM 32.768 k VCC R2 I<sup>2</sup>S SRAM prg. frq. VCC\_REG RTC 32.768 k MMC VCC\_R1 19.500 M SRAM VCC\_PI PWR\_I<sup>2</sup>C VCC\_BB 13 M ВВ 48.000 N VCC\_R0 Timer **SRAM** 13 M 0 VCC\_USIM USIM 48.000 M JTAG KYBD SSPs **PWMs** I<sup>2</sup>C **UARTs** AC MSHC 19.500 M **TCK** 32.768 k 13 M 13 M 32.842 M 14.857 M (ext clk) VCC\_10 VCC\_BATT

Figure 1. Intel® PXA27x Processor Internal and External Power Domains

# 2.1 Power Domains and System Voltage/Current Requirements

The following sections document the power requirements for the PXA27x processor, but do not include external support, memory, or other peripheral components.

The power consumption values shown in Table 5 are all worst-case numbers. These numbers give the worst-case system power-supply requirements and do not reflect typical system power consumption.

#### 2.1.1 Intel® PXA27x Processor Power Supplies

Viewed externally, the processor can require up to nine independent voltages provided by regulated supplies. In some cases, multiple voltage domains might be strapped together, reducing the number of separate regulators to as few as four. Internally, there are more domains, but these are powered from the externally supplied domains by on-chip regulators. The internal domains are documented for informational purposes only; the external power controller does not have to consider them in its design.

Table 2 shows the PXA27x processor voltage domains.

Table 2. Intel® PXA27x Processor Voltage Domains (Sheet 1 of 2)

| Voltage  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCC_BATT | BATTERY VOLTAGE:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          | Voltage-limited power from the main battery, or directly from a backup battery, at nominal 3.0 V (±25%). VCC_BATT must be supplied to start the power manager. When the main battery is installed, VCC_BATT powers the real-time clock and power management circuitry during initial power-on, sleep, deep sleep and sleep wake-up, so it remains powered from the backup battery when the main power source has been discharged or removed. See Section 2.2, "Batteries" on page 14 for information about directly connecting VCC_BATT to the backup battery or main battery.                                                                                                                                                                                                                         |

|          | NOTE: The power management integrated circuit (PMIC) output drivers for logic signals nRESET, nVDD_FAULT, nBATT_FAULT, PWR_SDA, GPIO0 and GPIO1 must be powered from the VCC_BATT supply. This also applies to all other digital outputs such as the JTAG signals driving PXA27x processor inputs on the VCC_REG domain. Any devices that have a digital input driven by a PXA27x processor digital output powered from the VCC_REG domain must tolerate output high drive levels between 2.25 V and 3.75 V.                                                                                                                                                                                                                                                                                           |

|          | NOTE: VCC_BATT must be driven by a regulator whose output is matched to the VCC_IO regulator so that VCC_IO and VCC_BATT remain within 200 mV of each other when the VCC_IO regulator is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VCC_CORE | CORE VOLTAGE:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|          | Dynamically variable core voltage of 0.85 V to 1.55 V. VCC_CORE also powers internal peripheral logic blocks such as the memory controller, LCD controller, digital audio, and serial ports. It does not power the internal SRAM. In a full featured system, this supply is software controllable as described in Section 6.1, "VCC_CORE Regulator and Dynamic Voltage Management" on page 29. In a simple system, this supply might be a fixed voltage chosen to meet the minimum voltage requirement for the highest frequency at which the PXA27x processor operates. In systems that use standby mode, there must also be a provision to set VCC_CORE to 1.10 V (±10%) prior to entry into standby mode. VCC_CORE must be enabled when PWR_EN is asserted and disabled when PWR_EN is de-asserted. |

| VCC_PLL  | PHASE-LOCK LOOP VOLTAGE:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|          | 1.3 V (±10%) for internal PLL circuits, fixed. VCC_PLL must not be connected to VCC_CORE, even though they both may be at the same voltage: 1.3 V. A separate low-noise voltage source is recommended to keep the PLL supply clean. This supply must be enabled when PWR_EN is asserted and disabled when PWR_EN is de-asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| VCC_SRAM | Power for the internal SRAM during operation in run or turbo modes. This supply is fixed at 1.1 V (±10%). If the core supply (VCC_CORE) is also fixed at 1.1V (no dynamic voltage changes are used and the maximum core clock frequency is not supported), these two supplies are connected together and powered by a common regulator. In sleep and deep-sleep modes, VCC_SRAM is powered down and the internal SRAM banks, under program control, are powered from an internal regulator connected to VCC_BATT. Doing so retains their contents although no accesses are allowed. VCC_SRAM must be enabled when PWR_EN is asserted and disabled when PWR_EN is de-asserted.                                                                                                                          |

Table 2. Intel® PXA27x Processor Voltage Domains (Sheet 2 of 2)

| Voltage  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| VCC_IO   | Fixed 3.0 V or 3.3 V (±10%) for standard CMOS I/Os interfacing to external components, which are also supplied from fixed 3.0 V or 3.3 V. The I/Os for external components connected to the corresponding signals on the PXA27x processor must be supplied from the same regulator. Driving VCC_BATT in this manner prevents forward biasing of protection diodes and inadvertent charging of the backup battery through inputs on the PXA27x processor VCC_REG domain. The VCC_IO supply must be the highest potential in the system (excluding VCC_BATT and VCC_USB) and must be sequenced on at the same time or before the other supplies enabled by SYS_EN. VCC_IO are connected to any of the VCC_LCD, VCC_MEM, VCC_BB or VCC_USIN supplies as long as none of these supplies are driven at a voltage higher than VCC_IO VCC_IO must be enabled when SYS_EN is asserted and disabled when SYS_EN is de-asserted.  NOTE: When the main battery is installed, VCC_BATT must be driven by a regulator. |  |  |  |

|          | whose output is matched to the VCC_IO regulator so that VCC_IO and VCC_BATT remain within 200 mV of each other when the VCC_IO regulator is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| VCC_LCD  | Power for output drivers to LCD panel, 1.8 V (+20%, -5%), 2.5 V, 3.0V or 3.3 V (± 10%). Optionally, these are strapped to one of the existing I/O supplies at 3.3 V, 2.5 V, or 1.8 V if appropriate for the panel used. This supply must be enabled when SYS_EN is asserted and disabled when SYS_EN is de-asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| VCC_MEM  | Power for memory/system bus I/O at 1.8 V (+20%, -5%), 2.5 V, 3.0V or 3.3 V (±10%); fixed, strappable by input signals on the power controller to one of these voltages. The power controller automatically powers up VCC_MEM to the voltage specified by its input control signals when this regulator is enabled. Corresponding I/Os of the memory components or companion chips must be powered from the same regulator. This supply must be enabled when SYS_EN is asserted and disabled when SYS_EN is de-asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| VCC_BB   | Power for I/Os to an external baseband module or device, at 1.8 V (+20%, -5%), 2.5 V, 3.0V, or 3.3 V (±10%). Corresponding I/Os of the baseband device must be powered from the same regulator. In systems that use PCMCIA or Compact flash and the baseband interface, VCC_BB must be tied to VCC_MEM because some of the card interface signals are multiplexed with baseband interface signals. This supply must be enabled when SYS_EN is asserted and disabled when SYS_EN is de-asserted if any of these GPIOs are used (as either a GPIO or as an alternate function): GPIO<48>, GPIO<57:50>, GPIO<85:81>.                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| VCC_USIM | Power for I/Os to an external Universal Subscriber Identity Module (USIM) card. The VCC_USIM voltage generated by the PMIC is software configurable at settings of 1.8 V (+20%, -5%) or 3.0 V (± 10%) or disabled (0 V). The software voltage control is implemented using I <sup>2</sup> C commands or the PMIC decodes the PXA27x processor UVS0, nUVS1, and nUVS2 outputs. Refer to Section 4.7, "Universal Subscriber Identity Module (USIM)" on page 21 for more information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| VCC_USB  | Power for USB at 3.0 V or 3.3V (±10%) for standard differential USB I/Os interfacing to external components, which are also supplied from fixed 3.0 V or 3.3 V.  NOTE: VCC_USB powers the I/O for the USB interfaces, the USB differential signals D+. D- is out of compliance with the USB specification if VCC_USB is below 2.8 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|          | NOTE: The +5 V VBUS source from USB host controller, which must be available for bus-powered peripherals, must be supplied from an external source, but it is not part of the PXA27x processor silicon.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

# 2.1.2 Power Supply Configuration in a Minimal System

For minimal systems, only five (four if VCC\_USIM is disabled) regulators are required to power the PXA27x processor and its input/output interfaces, as shown in Table 3.

| Table 3. Red | ıulators Red | auired to F | ower the | Intel® PXA27x | <b>Processor</b> |

|--------------|--------------|-------------|----------|---------------|------------------|

|--------------|--------------|-------------|----------|---------------|------------------|

| Regulator | Description                                                                                                                                                                              |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1         | Regulated main battery voltage, nominally 3.0 V (limited to a maximum of 3.75 V) to power VCC_BATT and charge the optional backup battery also connected to VCC_BATT.                    |

| 2         | VCC_IO, VCC_LCD, VCC_MEM, VCC_BB, VCC_USB connected together (can be powered at 3.0V or 3.3 V (±10%)).                                                                                   |

| 3         | VCC_USIM at 1.8V and 3.0 V (±10%)                                                                                                                                                        |

| 4         | VCC_CORE and VCC_SRAM may be connected together, fixed at 1.1 V. Dynamic voltage management cannot be used and the maximum core clock frequency is not supported using this arrangement. |

| 5         | VCC_PLL at 1.3 V.                                                                                                                                                                        |

More complex systems might require further separation of supply domains and additional regulators. Independent PXA27x power domains provide flexibility when supporting peripherals with different I/O voltages, which makes it possible to reduce overall system power by supporting 1.8 V low-power memory with 3.0 V peripherals.

#### 2.1.3 Modeling Intel PXA27x processor power consumption

This section provides guidelines for the power consumption required for the processor by varying the software workload. In this analysis, the information is divided into two groups:

- Core (modeled as VCC CORE) Section 2.1.3.1

- All other power domains (such as memory controller, LCD, etc.) Section 2.1.3.2

The core model section contains power consumption data with differing workloads. The model for the remaining domains shows power consumption data for each domain.

Use the guidelines detailed in Section 2.1.3.1 and Section 2.1.3.2 in conjunction with the Power Consumption Specifications listed in the *Intel® PXA27x Processor Family EMTS*.

# 2.1.3.1 Intel® PXA27x Processor VCC\_CORE Supply Current

This section specifies the power consumption expected for VCC\_CORE power supply domain across differing workloads.

Table 4 shows the typical current consumption for the VCC\_CORE power domain at room temperature, at nominal voltage levels but with differing workloads. All data is taken using the Intel PXA270 Processor Development Kit processor card running low level boot code, no operating system (unless specified).

- Dhrystones 2.1 Dhrystones workload. Configured to run 20,000,000 cycles with LCD disabled.

- MPEG4 Decode Frame rate unlimited, Intel® IPP Performance Suite v4.0 for the Intel PXA270 processor for Linux, QVGA LCD with frame buffer in SRAM.

- Power Stress Test Code Low level code executing a repetitive test case of back to back 64bit MAC instructions in an infinite loop. This stress code is written specifically to exercise the core power domain to yield data at the higher end of usage. It does not represent a real application.

**Note:** The figures in Table 4 where taken from a system with no enhanced power management optimization such as Intel Wireless Speedstep (which allows control over the PXA27x processors low power modes and dynamically selectable frequency and voltage change capability).

Table 4. Intel® PXA27x Processor VCC\_CORE Supply Current

| Frequency<br>Point @<br>voltage V                                                     | Dhrystones 2.1<br>Current (mA) | Power<br>(mW) | MPEG4 Decode current (mA) | Power<br>(mW) | Power Stress<br>Test<br>Current (mA) | Power<br>(mW) |

|---------------------------------------------------------------------------------------|--------------------------------|---------------|---------------------------|---------------|--------------------------------------|---------------|

| 624 MHz<br>1.55 V                                                                     | 658                            | 1019          | 622                       | 964           | 1006                                 | 1559          |

| 520 Mhz<br>1.45V                                                                      | 503                            | 729           | 475                       | 689           | 767                                  | 1112          |

| 416 MHz<br>1.35V                                                                      | 395                            | 533           | 420                       | 567           | 594                                  | 802           |

| 312 MHz<br>1.25V                                                                      | 297                            | 371           | 333                       | 416           | 436                                  | 545           |

| 208 MHz<br>1.15V                                                                      | 208                            | 239           | 263                       | 303           | 295                                  | 339           |

| NOTE: Core Frequency shown above/Internal bus = 208MHz/Memclk = 208MHz/SDCLK = 104MHz |                                |               |                           |               |                                      |               |

**Note:** Use these specifications as a guideline for power supply capacity. These typical guidelines will vary across different platforms and software applications.

#### 2.1.3.2 Supply Current For Each Power Domain

This section provides guidelines for the power consumption that could be seen for each power supply domain when running a heavily loaded system. Focused workloads were used to exercise each power supply domain separately. It is important to note that the workloads were designed to push the power consumption **on each domain** to a higher than normal level given a typical environment in order to show what the overall power envelope for these domains could look like. In a real system, each domain will see varying amounts of power consumption based on the type of workload run. For instance, an MPEG-4 decoder is going to utilize the memory controller much more than performing simple email transactions would.

Guidance on the power consumption for each domain in order to show Table 5 lists power-supply current for each PXA27x processor power domain except for VCC\_CORE (Table 4 shows data for VCC\_CORE). The environment test conditions are at room temperature and the voltage levels are specified below.

Note that the I/O domain regulator(s) (VCC\_IO, VCC\_LCD, VCC\_MEM, VCC\_BB, VCC\_USIM, VCC\_USB) have additional loading from external devices attached to the PXA27x processor. For example, when flash memory or SDRAM is connected to the system bus. These loads must be added to those of PXA27x processor I/Os (if they are powered by the same regulator) when specifying the total load to be provided by a given regulator.

| Table 5. | Intel® PXA27x | Processor S | Supply | Current I | For Each I | Power Domain |

|----------|---------------|-------------|--------|-----------|------------|--------------|

|----------|---------------|-------------|--------|-----------|------------|--------------|

| Name                           | Functional Units                                                                 | Current (mA) @ voltage V  | Power<br>(mW)    |

|--------------------------------|----------------------------------------------------------------------------------|---------------------------|------------------|

| VCC_BATT                       | VCC_BATT Power manager and real-time clock max. during power-on and sleep wakeup |                           | 37.5             |

|                                | Power manager and real-time clock typical during deep sleep                      | 6 μA @ 3.0 V              | 20 μW            |

| ACC_IO                         | Peripheral input/output                                                          | 25 @ 3.3 V                | 82.5             |

| VCC_LCD                        | LCD input/output                                                                 | 11 @ 3.3 V                | 33               |

| VCC_MEM<br>(3.3V)              | Memory controller input/output                                                   | 300 @ 3.3 V               | 1080             |

| VCC_MEM <sup>1</sup><br>(1.8V) | Memory controller input/output                                                   | 150 @ 1.80 V <sup>1</sup> | 297 <sup>1</sup> |

| VCC_BB                         | Baseband interface                                                               | 9 @ 3.3 V                 | 30               |

| VCC_USB                        | Differential USB interface                                                       | 25 @ 3.3 V                | 82.5             |

| VCC_USIM                       | USIM interface                                                                   | 0.3 @ 3.0 V               | 1                |

| VCC_PLL                        | Phase-locked loops                                                               | 40 @ 1.3 V                | 52               |

| VCC_SRAM                       | Internal SRAM                                                                    | 50 @ 1.1 V                | 55               |

#### NOTE:

For each I/O domain, maximum current draw and power use is highest at the 3.3 V supply as shown. For lower voltages (2.5 V, or 1.8 V) maximum current draw and power use is reduced following the  $P=CV^2F$  relationship.

**Note:** Use these specifications as a guideline for power supply capacity. These typical guidelines will vary across different platforms and software applications.

#### 2.1.4 Default Reset Values

Of the nine power domains besides VCC\_BATT, two (VCC\_SRAM and VCC\_PLL) are fixed. Five domains (VCC\_MEM, VCC\_IO, VCC\_LCD, VCC\_BB, and VCC\_USB) can take one of several possible values, but once powered up, remain fixed. VCC\_CORE and VCC\_USIM are dynamically variable.

On power up, VCC\_BATT is the first voltage supplied to the PXA27x processor; limit VCC\_BATT to a maximum of 3.75 V. Other voltages/power domains power up following a predefined sequence as set by the control signals, PWR\_EN and SYS\_EN. Refer to the *Intel® PXA27x Processor Family Electrical, Mechanical, and Thermal Specification* for a description of the power-on sequence.

VCC\_SRAM must power up and remain at 1.1 V. VCC\_PLL must power up to and remain at 1.3 V. VCC\_CORE must power up to any user-selected voltage between 0.85 and 1.55 V. VCC\_USIM must default to 0 V at power up.

The five supplies that individually take one of several values are: VCC\_IO, VCC\_LCD, VCC\_MEM, VCC\_BB, and VCC\_USB. The voltages required for these domains are determined by other components in the system and the I/O voltages they use. When the system powers up,

<sup>1.</sup> This data does not include the Intel® PXA27x Processor Family with Intel StrataFlash® memory power requirements. Refer to the appropriate top package data sheet for power requirements and include this data when sizing power regulators that will support the PXA27x processors with Intel StrataFlash® memory

these supplies must come up at the required voltage to operate reliably and to avoid damage to the external components. VCC\_IO must be the highest potential of the system I/O supplies<sup>1</sup>. VCC\_IO can be connected to any of VCC\_LCD, VCC\_MEM, VCC\_USIM, VCC\_USB and VCC\_BB, but none of these supplies can exceed VCC\_IO.

The power-up voltage requirement must be communicated by some input strapping mechanism on the PMIC if a PMIC can provide more than one voltage level for any of these domains. This ensures that each regulator powers up to its designated voltage without processor intervention. Software must read this configuration information using an I<sup>2</sup>C command.

#### 2.2 Batteries

The PXA27x processor supports a variety of system battery configurations with both a main battery and backup battery, and a main battery alone.

In systems with only a main battery, the main battery must drive VCC\_BATT directly or use a regulator. In systems with a backup battery, the backup battery connects directly to VCC\_BATT or the backup battery can be connected to a power controller, which in turn drives the PXA27x processor VCC\_BATT.

#### 2.2.1 Main Battery

The main battery is a rechargeable single cell (or multiple cells in parallel) using lithium-ion or lithium-polymer technology. These batteries typically present a voltage as high as 4.2 V when fully charged, declining to under 3.0 V as they discharge. A main battery capacity of 500 to 1200 mAh is typical for most applications.

#### 2.2.2 Backup Battery

The backup battery is a lithium or lithium-manganese coin cell with an output voltage of approximately 3.0 V. The backup battery is a small rechargeable coin cell permanently mounted to the printed circuit board (PCB) in many handset applications. The PMIC must include a regulator and associated circuitry for recharging this type of backup battery. The two backup battery configurations are shown in Table 6.

<sup>1.</sup> excluding VCC\_BATT and VCC\_USB

**Table 6. Possible Backup Battery Configurations**

| Backup Battery<br>Connection | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCC_BATT and PMIC            | The backup battery connects to both the VCC_BATT input and PMIC charging regulator (driven from the main battery or AC adaptor supply). Powering VCC_BATT from a battery directly eliminates the inefficiency of an external regulator in the PMIC, maximizing the battery life in sleep and deep sleep. In such a configuration, ensure that the requirements for limiting current to the backup battery are observed, regardless of whether it is a rechargeable or non-rechargeable type. Information on battery current limits is available from the battery manufacturer. Series resistors and diodes might be needed to limit intentional charging current, to prevent the backup battery from being drained by a discharged main battery, and to prevent unintentional backup battery charging by the PXA27x processor. These components may be internal or external to the PMIC. |

| PMIC only                    | There is more flexibility in the number of cells and allowable charging voltage when the backup battery is connected only to the PMIC and the PMIC drives VCC_BATT. In this configuration, the PMIC must ensure that requirements for limiting current into the backup battery are observed, regardless of whether it is a rechargeable or non-rechargeable type.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

The system schematic in Figure 2 shows one recommended configuration for connecting the PXA27x processor directly to the backup battery. In such a configuration, the regulated main battery powers VCC\_BATT through regulator U7, and the backup battery powers VCC\_BATT when the main battery discharges. Regulator U7 also charges the backup battery and its output voltage must be chosen to ensure that VCC\_BATT remains between 2.25 V and 3.75 V when VCC\_IO is disabled and within 200 mV of VCC\_IO when VCC\_IO is enabled. D1 protects regulator U7 from back current when the backup battery drives VCC\_BATT to a higher potential than the output of U7. D3 and R2 are chosen to limit intentional charging current to the backup battery. D2 and R1 prevent the PXA27x processor from driving unintended charging current into the backup battery if an input signal on the VCC\_REG domain is driven above the backup battery voltage while the processor is powering the VCC\_REG domain from VCC\_BATT.

Signals from the PMIC to the processor on the VCC\_REG domain must be powered from the VCC\_BATT supply voltage when SYS\_EN de-asserts in deep-sleep mode. Doing so prevents forward-biasing the PXA27x processor input protection diodes.

#### 2.2.3 Battery Chargers and Main Power

The PMIC includes as an option a way of charging the main battery when the system is plugged into an AC power outlet or through the USB port. An external power brick is often used to convert the main voltage (90 VAC to 240 VAC) to a low DC voltage suitable for powering the regulators and charging the batteries.

The PMIC must have an input (voltage detect) that can sense when AC power is supplied to the system to manage main power. An output from the PMIC must make this information available to a PXA27x processor GPIO at a suitable voltage (normally, 3.3 V CMOS logic levels). For GPIO<0> or GPIO<1> to generate deep sleep wake-up events, the PMIC must make the input (voltage detect) information available as an output to one of these GPIO signals.

Figure 2. Typical Battery and External Regulator Configuration

# 3.0 Intel® PXA27x Processor Low Power Operating Modes

The PXA27x processor provides several low-power operating modes that temporarily suspend or power down the core or peripherals to reduce power consumption. The external power supplies are disabled in some modes. Transitions between certain domains require a sequence of events and handshakes between the PXA27x processor and the external power management integrated circuit (PMIC) that are detailed in this section.

The PXA27x processor supports six operating modes, shown in Table 7.

Table 7. Intel® PXA27x Processor Operating Modes

| Operating Modes                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Normal mode<br>(Run/Turbo mode) | All external power supplies are enabled and all internal domains are powered. The CPU core and peripherals are fully functional.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Idle mode                       | The clocks to the CPU are disabled but context is retained. The peripherals continue normal operation. All power supplies are enabled. An interrupt assertion causes the transition back to normal mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| Deep Idle mode                  | The core frequency is at 13 MHz (CCCR[CDPIS] is set) and the processor is in idle mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| Standby mode                    | The clocks to the CPU are disabled and the CPU is placed in a low leakage state but context is retained. All external power supplies are enabled. Each internal SRAM bank can be independently placed in a low-power mode where the state is retained but no activity is allowed under program control. The PLLs are disabled and peripheral operation is suspended. An interrupt assertion causes the transition back to normal mode.                                                                                                                                                                                                                                  |  |  |  |  |

| Sleep mode                      | All internal power domains except VCC_RTC and VCC_OSC are optionally powered down. All clock sources except the real-time clock (RTC) and power manager are disabled, and all external low-voltage power supplies (VCC_CORE, VCC_PLL, and VCC_SRAM) controlled by PWR_EN are disabled. Recovery is initiated by external wake-up events or select internal wake-up events. A system reboot is required because the program counter is invalid.                                                                                                                                                                                                                          |  |  |  |  |

| Deep sleep mode                 | All internal power domains except VCC_RTC and VCC_OSC are powered down. All clock sources except the real-time clock (RTC) and power manager are disabled, and the external low-voltage supplies (VCC_CORE, VCC_PLL, and VCC_SRAM) controlled by PWR_EN are disabled. The high-voltage power supplies (VCC_IO, VCC_MEM, VCC_LCD, VCC_BB and VCC_USIM) controlled by SYS_EN are disabled. The active internal power domains are powered from one of three internal regulators driven from the backup battery signal, VCC_BATT. Recovery is initiated by external or select internal wake-up events and requires a system reboot, because the program counter is invalid. |  |  |  |  |

|                                 | NOTE: Refer to the Intel® PXA27x Processor Family Developers Manual, "Clocks and Power" section for more information on low power modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

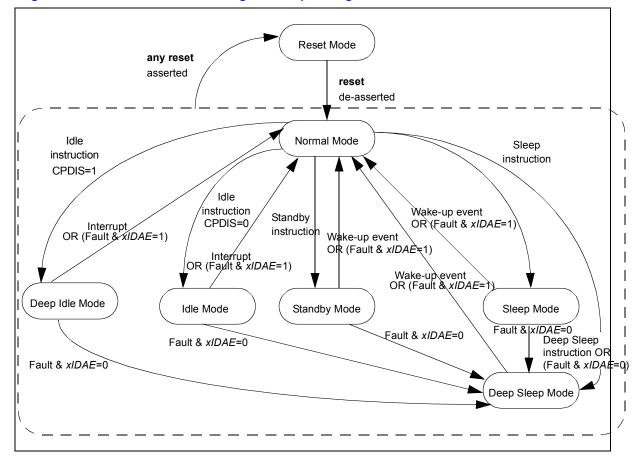

The state diagram in Figure 3 shows the transitions between operating modes and the events and conditions that cause or enable transitions.

Figure 3. Overview of Power Management Operating Modes

# 4.0 Power Controller Interface Signals

The PXA27x processor has an internal power manager unit (PMU) and a set of I/O signals for communicating with an external power management integrated circuit (PMIC). These signals are active for initial power up, certain reset events, device on/off events, and transitions between some operating modes. In addition, two fault signals are required from the PMIC to communicate the onset of power supply problems to the processor. These signals and their function are described fully in Section 7.0.

The PXA27x processor communicates to the power controller using the signals defined in Table 8.

| Signal      | Definition                                           | Active State | Signal Direction <sup>1</sup> |

|-------------|------------------------------------------------------|--------------|-------------------------------|

| PWR_EN      | Power enable                                         | high         | Output                        |

| SYS_EN      | System enable                                        | high         | Output                        |

| PWR_SCL     | I <sup>2</sup> C bus clock                           | Clock        | Output                        |

| PWR_SDA     | I <sup>2</sup> C bus data                            | _            | Bidirectional                 |

| nRESET      | Forces an unconditional hardware reset               | low          | Input                         |

| nBATT_FAULT | Indicates main battery removed or discharged         | low          | Input                         |

| nVDD_FAULT  | Indicates one or more supplies are out of regulation | low          | Input                         |

NOTE: 1. Input and output refers to the signal direction from the standpoint of the PXA27x processor

# 4.1 Power Enable (PWR\_EN)

PWR\_EN is an active-high output from the PXA27x processor (input to the PMIC) that enables the external core power supplies (VCC\_CORE, VCC\_SRAM, and VCC\_PLL). De-asserting PWR\_EN informs the external regulator that the processor is going into sleep mode, and that the low-voltage core power supplies are to be shut down.

The PMIC turns on the core (low-voltage) supplies in response to PWR\_EN assertion to resume normal operation. The power controller must preserve, during sleep or deep sleep, the previous state of its regulators including the voltage for the core, so that on resumption of core power, the regulators return to their last known voltage levels.

# 4.2 System Power Enable (SYS\_EN) / GPIO<2>

SYS\_EN is an active-high output from the PXA27x processor (input to the PMIC) that enables the external system power supplies. De-asserting SYS\_EN informs the power supply that the processor is going into deep-sleep mode, and that the high-voltage system power supplies (VCC\_IO, VCC\_LCD, VCC\_MEM, VCC\_USIM, VCC\_BB, and VCC\_USB) are to be shut down. Assertion and de-assertion of SYS\_EN occurs in the correct sequence with PWR\_EN to ensure the correct sequencing of power supplies when powering on and off the various voltage domains.

To resume normal operation, the PMIC first turns on the system I/O (high-voltage) supplies in response to SYS\_EN assertion and then turns on the core (low-voltage) supplies in response to PWR\_EN assertion. The power controller must return all system I/O voltages to their pre-deep sleep mode levels.

# 4.3 Power Manager I<sup>2</sup>C Clock (PWR\_SCL) / GPIO<3>

The PWR\_SCL signal is the power manager I<sup>2</sup>C clock in to the external PMIC. The I<sup>2</sup>C serial bus must operate at a minimum 40 kHz and (optionally) be able to operate at a 160 kHz clock rate.

# 4.4 Power Manager I<sup>2</sup>C Data (PWR\_SDA) / GPIO<4>)

The PWR\_SDA signal is the power manager I<sup>2</sup>C data signal to the external PMIC. It functions like an open-drain signal so either component can pull it down to a logic-low level.

# 4.5 System-Level Considerations for I<sup>2</sup>C

Both  $I^2C$  signals have an alternate function on the PXA27x processor as GPIO signals. Following cold-start power-on or a hard reset, both signals default to the GPIO mode of operation and are configured as inputs. An internal (nominally 50 K $\Omega$ ) pull-down resistor on each signal prevents them from floating during reset or power-on events. To use the  $I^2C$  capabilities after power-up or reset, the PXA27x processor must, while under software control, configure these signals as  $I^2C$  signals and disconnect the internal pull-down resistor.

These  $I^2C$  signals behave functionally like open-drain outputs and require an external pull-up resistor on the system module in the 2 K $\Omega$  to 20 K $\Omega$  range I. A typical system uses approximately a 5 K $\Omega$  resistor connected to 3.3 V.

The I<sup>2</sup>C signals from the PXA27x processor are pulled low after power-up or reset events. The PMIC must ignore those signals (logic low is the asserted or ON state for I<sup>2</sup>C bus) after either type of event until the PXA27x processor has asserted PWR\_EN and SYS\_EN, and the system is operating normally.

The I<sup>2</sup>C interface does not support the hardware general call, 10-bit addressing, high-speed mode (Hs-mode, 3.4 Mbits/s), or CBUS compatibility. Although other compatible protocols, such as SMBus, can be used with the PXA27x processor I<sup>2</sup>C interface, they have not been tested for compatibility.

Refer to the I<sup>2</sup>C Bus Interface Unit section of the *Intel*® *PXA27x Processor Family Developer's Manual* for more information.

# 4.6 On, Off, and RESET

#### 4.6.1 On and Off Control

User-initiated ON and OFF events are accomplished using a push button or similar type of system power switch. The system power switch is a momentary-contact type; making contact shorts the normally high input to GND.

The switch signal can be connected directly to a PXA27x processor GPIO input or, preferably, to the PMIC, which debounces the input and forwards the clean signal to a PXA27x processor GPIO. This process requires two signals on the PMIC; one input and one output. GPIO<0> or GPIO<1> are recommended for this purpose because they can generate deep-sleep wake-up events.

#### 4.6.2 User-Initiated Hard Reset Input

This signal from a momentary-contact push button switch connects to a power controller input for user-initiated hard reset. Detection of hard reset forces assertion of the nRESET output from the power controller IC to the PXA27x processor. The input must be debounced to cause clean

<sup>1.</sup> See 1<sup>2</sup>C-Bus Specification 2.1, dated January 2000, by Phillips Semiconductors, order #9398 358 10011, pp. 39-42.

assertion of nRESET for a minimum of 50 ms. This type of reset would be used only for a severe and otherwise unrecoverable hardware or software problem, because it completely resets the state of the processor and may result in lost data. Refer to the *Intel® PXA27x Processor Family Electrical, Mechanical, and Thermal Specification* for the hardware reset timing specification.

#### 4.6.3 nRESET Output from PMIC to the Intel® PXA27x Processor

nRESET is an active-low signal from the PMIC to the PXA27x processor that tells the processor to enter the hardware-reset state. The assertion of nRESET cannot be gated and causes the PXA27x processor to enter a complete and unconditional reset state. The nRESET signal contains an internal resistive pull-up that is always active (no pull-up required on the system module or in the PMIC).

nRESET is a hard reset that can cause the system to lose state or data when asserted. It is asserted for a cold start power-on event, or if for any reason the user pushes the system reset button. The power controller must assert nRESET for both events.

nRESET must remain asserted for at least 50 ms when asserted. When not asserted, nRESET is pulled up internally to VCC\_REG. VCC\_REG is normally powered from VCC\_IO, except when in deep-sleep mode, where VCC\_REG is powered from VCC\_BATT.

All PXA27x processor internal registers and processes are held at their defined reset conditions during hardware reset. While the nRESET signal is asserted, the only activity inside the PXA27x processor is the stabilization of the 13.000 MHz oscillator and phase-locked loops. The remaining internal clocks are stopped and the processor is fully static. Additionally, all signals assume their reset conditions, and the nBATT\_FAULT and nVDD\_FAULT signals are ignored. The nRESET\_OUT signal from the PXA27x processor is asserted when the nRESET input signal is asserted.

# 4.7 Universal Subscriber Identity Module (USIM)

The PXA27x processor provides signals to control an external regulator that powers the USIM card interface used in many digital cell phones. The VCC\_USIM regulator output voltage is set to 1.8 V or 3.0 V or disabled (0 V) under software control. The software voltage control is implemented either by using  $I^2C$  commands or by decoding the PXA27x processor UVS0, nUVS1, and nUVS2 outputs in the PMIC.

The regulator must drive VCC\_USIM to ground when UVS0 is driven high. The regulator must drive VCC\_USIM to 1.8 V when nUVS1 is driven low. The regulator must drive VCC\_USIM to 3.0 V when nUVS2 is driven low. The PXA27x processor USIM interface asserts only one of these signals at a time such that they can be used to control the gate of simple FET switches directly.

e: The regulator that generates VCC\_USIM must be disabled using SYS\_EN or an I<sup>2</sup>C command when the PXA27x processor enters deep-sleep mode. During deep sleep, the UVS0, nUVS1, and nUVS2 outputs are not driven and cannot control the VCC\_USIM regulator.

# 4.8 Power Manager Capacitor Signals

This section describes connection of external capacitors to PXA27x processor signals. These capacitors do not have a direct design impact on a PMIC but are included here for completeness.

The PXA27x processor has a low-power DC-to-DC converter that is enabled by software while in sleep or deep-sleep mode. Enabling the low-power DC-to-DC converter further reduces power consumption by shutting off the high-power regulators on the PMIC, eliminating losses in the external power supply subsystem. Use of the sleep mode DC-to-DC converter requires three external capacitors connected to the PXA27x processor PWR\_CAP signals.

These capacitors are required for the DC-to-DC converter:

- A 0.1 µF capacitor connected between the PWR CAP<0> and PWR CAP<1> signals

- A 0.1 µF capacitor connected between the PWR CAP<2> and PWR CAP<3> signals