Technical Reference Manual Rev. 3.00

P/N: 46157\_sb600\_bdg\_pub\_3.00 ©2008 Advanced Micro Devices, Inc.

### **Trademarks**

AMD, the AMD Arrow, ATI, the ATI logo, Radeon, Mobility Radeon, AMD Athlon, Sempron, Turion and combinations thereof are trademarks of Advanced Micro Devices, Inc.

HyperTransport is a licensed trademark of the HyperTransport Technology Consortium.

Microsoft and Windows are registered trademarks of Microsoft Corporation.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

#### Disclaimer

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel, or otherwise, to any intellectual property rights are granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

.

# **Table of Contents**

| 1 | Introduction                                               | 7  |

|---|------------------------------------------------------------|----|

|   | 1.1 About This Manual                                      |    |

|   | 1.2 Overview                                               | 7  |

|   | 1.3 PCI Internal Devices                                   | 10 |

| 2 | SB600 Programming Architecture                             | 12 |

|   | 2.1 PCI Devices and Functions                              | 12 |

|   | 2.2 I/O Map                                                | 13 |

|   | 2.2.1 Fixed I/O Address Ranges                             | 13 |

|   | 2.2.1.1 Fixed I/O Address Ranges – SB600 Proprietary Ports | 13 |

|   | 2.2.2 Variable I/O Decode Ranges                           | 13 |

|   | 2.3 Memory Map                                             | 14 |

| 3 | SB600 Early-POST Initialization                            | 15 |

|   | 3.1 512K/1M ROM Enable                                     |    |

|   | 3.1.1 PCI ROM                                              |    |

|   | 3.1.2 LPC ROM                                              |    |

|   | 3.1.3 LPC ROM Read/Write Protect                           |    |

|   | 3.1.4 SPI ROM controller                                   |    |

|   | 3.2 Real Time Clock (RTC)                                  |    |

|   | 3.2.1 RTC Access                                           |    |

|   | 3.2.1.1 Special Locked Area in CMOS                        |    |

|   | 3.2.1.3 Date Alarm                                         |    |

|   | 3.3 BIOS RAM                                               |    |

|   | 3.4 Serial IRQ                                             |    |

|   |                                                            |    |

|   | ·                                                          |    |

|   | 3.6 AMD Athlon <sup>TM</sup> Processor Registers           |    |

|   | 3.7 System Restart after Power Fail                        |    |

|   | 3.7.1 Power Fail and Alarm Setup                           | 20 |

| 4 | PCI IRQ Routing                                            |    |

|   | 4.1 PCI IRQ Routing Registers                              |    |

|   | 4.2 PCI IRQ BIOS Programming                               |    |

|   | 4.3 Integrated PCI Devices IRQ Routing                     |    |

|   | 4.3.1 IRQ Routing for HD Audio                             |    |

|   | 4.4 PCI IRQ Routing for APIC Mode                          | 23 |

| 5 | SMBus Programming                                          |    |

|   | 5.1 SMBus I/O Base Address                                 | 24 |

|   | 5.2 SMBus Timing                                           | 24 |

|   | 5.3 SMBus Host Controller Programming                      | 25 |

| 6 | IDE Controller                                             | 27 |

|   |                                                            |    |

|    | 6.1 IDE Channel Enable/Disable              | 27 |

|----|---------------------------------------------|----|

|    | 6.1.1 IDE Channel Enable                    | 27 |

|    | 6.1.2 IDE Channel Disable                   | 27 |

|    | 6.2 PIO Modes                               | 28 |

|    | 6.2.1 PIO Mode                              |    |

|    | 6.2.2 PIO Timing                            |    |

|    | 6.3 DMA Modes                               |    |

|    | 6.3.1 Legacy (Multi-Words) DMA mode         |    |

|    | 6.3.2 Ultra-DMA Mode                        | 29 |

| 7  | Serial ATA (SATA)                           | 30 |

|    | 7.1 SATA Hot Plug                           | 30 |

|    | 7.1.1 Sample Code                           | 30 |

| 8  | Power Management                            | 31 |

|    | 8.1 SMI Handling – EOS (PM IO Reg10h[Bit0]) |    |

|    | 8.2 Programmable I/Os                       |    |

|    | 8.3 Power Management Timers                 |    |

|    | 8.3.1 PM Timer 1 (Inactivity Timer)         |    |

|    | 8.3.2 PM Timer 2 (Activity Timer)           |    |

|    | 8.4 SMI Events                              |    |

|    | 8.4.1 Power Button                          |    |

|    | 8.5 C-State Break Events                    |    |

|    | 8.5.2 Break Events for C3 and C4 States     |    |

|    | 8.6 Save/Restore Sequence for S3 State      |    |

|    | 8.6.1 Register Save Sequence for S3 State   |    |

|    | 8.7 Wake on Events                          |    |

|    | 8.8 Sleep SMI Events                        |    |

|    | 8.8.1 Sleep SMI Control Register            |    |

|    | 8.8.2 Sleep SMI Programming Sequence        |    |

|    | 8.8.2.1 Set Sleep SMI Control Register      | 35 |

|    | 8.8.2.2 Enter Sleep SMI# Routine            | 35 |

| 9  | APIC Programming                            | 37 |

|    | 9.1 Northbridge APIC Enable                 |    |

|    | 9.2 Southbridge APIC Enable                 |    |

|    | 9.3 IOAPIC Base Address                     |    |

|    | 9.4 APIC IRQ Assignment                     |    |

|    | 9.5 APIC IRQ Routing                        |    |

| 10 | Watchdog Timer                              | 39 |

| 11 | A-Link Bridge                               | 41 |

|    | 11.1 A-Link Registers                       |    |

|    | 11.2 Programming Procedure                  | 42 |

| <b>12</b> | High Precision Event Timer (HPET)                                   | 44 |

|-----------|---------------------------------------------------------------------|----|

|           | 12.1 Initialization                                                 |    |

|           | 12.1.1 Sample Initialization Code                                   | 44 |

|           | 12.2 ACPI HPET Description Table                                    |    |

|           | 12.3 HPET Support for Longhorn                                      | 45 |

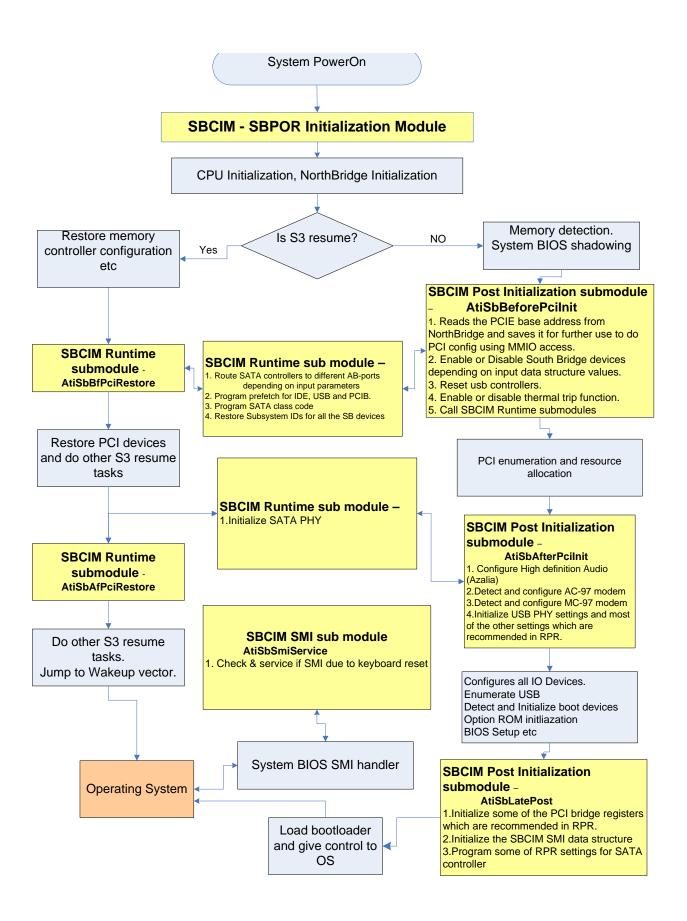

| 13        | Common Interface Module – CIM-SB600                                 | 46 |

|           | 13.1 CIM-SB600 Architecture                                         | 46 |

|           | 13.2 CIM-SB600 Build Configuration                                  | 48 |

|           | 13.3 CIM-SB600 Setup Input Data Structure                           |    |

|           | 13.4 CIM-SB600 SBPOR Sub-Module                                     |    |

|           | 13.4.1 SBPOR Interface                                              |    |

|           | 13.5 CIM-SB600 SB POST Initialize Sub-Module                        |    |

|           | 13.5.1 Requirements                                                 |    |

|           | 13.5.2 SB POST Interface                                            |    |

|           | 13.6 CIM-SB600 SB Runtime Interface Sub-Module                      | 53 |

|           | 13.6.1 Requirements                                                 | 53 |

|           | 13.6.2 SB Runtime Interface                                         | 53 |

|           | 13.7 CIM-SB600 SB SMI Interface Sub-Module                          |    |

|           | 13.7.1 Requirements                                                 |    |

|           | 13.8 CIM-SB600 SPI Interface Sub-Module                             | 54 |

| 14        | Sample Programs                                                     | 55 |

|           | 14.1 SB600 Register Initialization on Power-Up                      | 55 |

|           | 14.1.1 Initialization of PCI IRQ Routing Before Resource Allocation | 55 |

|           | 14.2 Setup Options                                                  | 56 |

|           | 14.2.1 64 Bytes DMA                                                 |    |

|           | 14.2.2 USB Overcurrent Detection Disable                            |    |

|           | 14.2.3 C3 Support                                                   |    |

|           | 14.2.4 Subtractive Decoding for P2P Bridge.                         |    |

|           | 14.2.5 Enable/Disable On-Chip SATA                                  |    |

|           | 14.2.7 Disable AC97 Audio or MC97 Modem.                            |    |

|           | 14.2.8 Enable EHCI Controller                                       |    |

|           | 14.2.9 Enable OHCI Controller                                       |    |

|           | 14.3 IDE Settings                                                   |    |

|           | 14.3.1 PIO Mode Settings                                            |    |

|           | 14.3.2 Multiword DMA Settings                                       | 65 |

|           | 14.3.3 UDMA Mode Settings                                           |    |

|           | 14.3.4 IDE Channel Disable                                          |    |

|           | 14.3.5 IDE Channel Enable                                           |    |

|           | 14.4 USB Controller Reset at Hard Reset                             |    |

|           | 14.5 Clock Throttling                                               |    |

|           | 14.6 Lid Switch                                                     |    |

|           | 14.6.1 Lid Switch Hardware Connection                               |    |

|           | 14.6.2 Associated Registers                                         |    |

|           | 14.6.3 BIOS Initialization.                                         | /1 |

| 14.6.4 ACPI Programming                          | 72 |

|--------------------------------------------------|----|

| 14.7 SATA Hot Plug Sample Program                | 74 |

| 14.8 Temperature Limit Shutdown through SMI#     | 80 |

| 14.8.1 Setting Up ITE 8712 Super I/O Registers   |    |

| 14.8.2 Initialize Southbridge Registers for SMI# |    |

| 14.8.3 SMI Programming to Shut Down the System   |    |

| 14.9 Sleep Trap through SMI#                     | 87 |

| 14.9.1 Enable Sleep SMI# in ACPI ASL code        | 87 |

| 14.9.2 Sleep Trap SMI Routine                    | 88 |

| 14.10 HD Audio – Detection and Configuration     | 89 |

| Appendix: Revision History                       | 98 |

# 1 Introduction

### 1.1 About This Manual

This manual provides guidelines for BIOS developers working with the AMD SB600. It describes the BIOS and software modifications required to fully support the device.

**Note:** To help the reader to readily identify changes/updates in this document, changes/updates over the previous revision are highlighted in red. Refer to *Appendix: Revision History* at the end of this document for a detailed revision history.

### 1.2 Overview

The SB600 is an I/O Communication Processor designed to work with AMD's ATI Radeon<sup>TM</sup> and Mobility Radeon<sup>TM</sup> Integrated Graphics Processors (IGPs). The functions and capabilities of the SB600 are as follows:

#### **CPU Interface**

- Supports both Single and Dual core AMD CPUs

- Desktop: AMD Athlon<sup>TM</sup> 64, Athlon 64 FX, Athlon 64 X2, Sempron<sup>TM</sup>, Opteron<sup>TM</sup>, dual-core Opteron

- Mobile: Athlon XP-M, Mobile Athlon 64, Turion 64, Mobile Sempron

### **PCI Host Bus Controller**

- Supports PCI Rev. 2.3 specification

- Supports PCI bus at 33MHz

- Supports up to 6 bus master devices

- Supports 40-bit addressing

- Supports interrupt steering for plug-n-play devices

- Supports concurrent PCI operations

- Supports hiding of PCI devices by BIOS/hardware

- Supports spread spectrum on PCI clocks

### **USB Controllers**

5 OHCI and 1 EHCI Host controllers to support 10 USB ports

- All 10 ports are USB 1.1 ("Low Speed", "Full Speed") and 2.0 ("High Speed") compatible

- Supports ACPI S1~S5

- Supports legacy keyboard/mouse

- Supports USB debug port

- Supports port disable with individual control

### **SMBus Controller**

- SMBus Rev. 2.0 compliant

- Support SMBALERT # signal / GPIO

### **Interrupt Controller**

- Supports IOAPIC/X-IO APIC mode for 24 channels of interrupts

- Supports 8259 legacy mode for 15 interrupts

- Supports programmable level/edge triggering on each channels

- Supports serial interrupt on quiet and continuous modes

## **DMA Controller**

- Two cascaded 8237 DMA controllers

- Supports PC/PCI DMA

- Supports LPC DMA

- Supports type F DMA

### LPC host bus controller

- Supports LPC based super I/O and flash devices

- Supports two master/DMA devices

- Supports TPM version 1.1/1.2 devices for enhanced security

- Supports SPI devices

### **SATA II AHCI Controller**

- Supports four SATA ports, complying with the SATA 2.0 specification

- Supports SATA II 3.0GHz PHY, with backward compatibility with 1.5GHz

- Supports RAID striping (RAID 0) across all 4 ports

- Supports RAID mirroring (RAID 1) across all 4 ports

- Supports RAID 10 (4 ports needed)

- Supports both AHCI mode and IDE mode

- Supports advanced power management with ACHI mode

### **IDE Controller**

- Single PATA channel support

- Supports PIO, Multi-word DMA, and Ultra DMA 33/66/100/133 modes

- 32x32byte buffers on each channel for buffering

- Swap bay support by tri-state IDE signals

- Supports Message Signaled Interrupt (MSI)

- Integrated IDE series resistors

### **AC Link interface**

- Supports for both audio and modem codecs

- Compliant with AC-97 codec Rev. 2.3

- 6/8 channel support on audio codec

- Multiple functions for audio and modem Codec operations

- Bus master logic

- Supports up to 3 codecs simultaneously

- Supports SPDIF output

- Separate bus from the HD audio

### **HD** Audio

- 4 Independent output streams (DMA)

- 4 Independent input streams (DMA)

- Up to 16 channels of audio output per stream

- Supports up to 4 codecs

- Up to 192kHz sample rate

- Up to 32-bit per sample

- Message Signaled Interrupt (MSI) capability

- 64-bit addressing capability for MSI

- 64-bit addressing capability for DMA bus master

- Unified Audio Architecture (UAA) compatible

- HD Audio registers can be located anywhere in the 64-bit address space

### Timers

- 8254-compatible timer

- Microsoft High Precision Event Timer (HPET)

- ACPI power management timer

## RTC (Real Time Clock)

- 256-byte battery-backed CMOS RAM

- Hardware supported century rollover

- RTC battery monitoring feature

### **Power Management**

- ACPI specification 2.0 compliant power management schemes

- Supports C2, C3, C4, ACPI states

- Supports C1e and C3 pop-up

- Supports S0, S1, S2, S3, S4, and S5

- Wakeup events for S1, S2, S3, S4/S5 generated by:

- Any GEVENT pin

- Any GPM pin

- USB

- Power button

- Internal RTC wakeup

- SMI# event

- Full support for On-Now<sup>TM</sup>

- Supports CPU SMM, generating SMI# signal upon power management events

- GPIO supports on external wake up events

- Supports CLKRUN# on PCI power management

- Provides clock generator and CPU STPCLK# control

- Support for ASF

### **Hardware Monitor**

- Supports 3 Independent FAN Control outputs

- Supports 1 AMDSI function

**Note:** SB600 does not support thermal diode temperature sensing function.

### 1.3 PCI Internal Devices

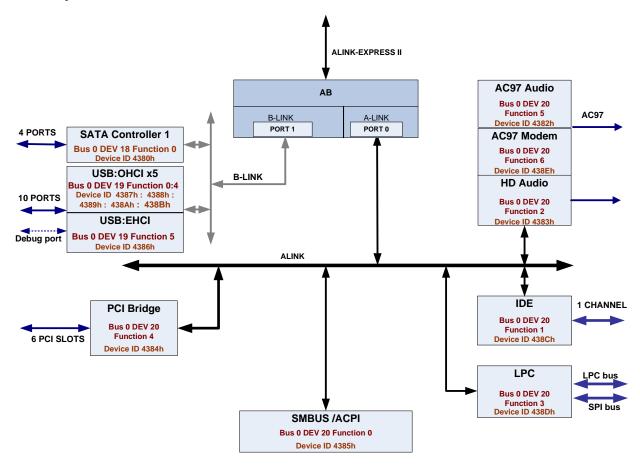

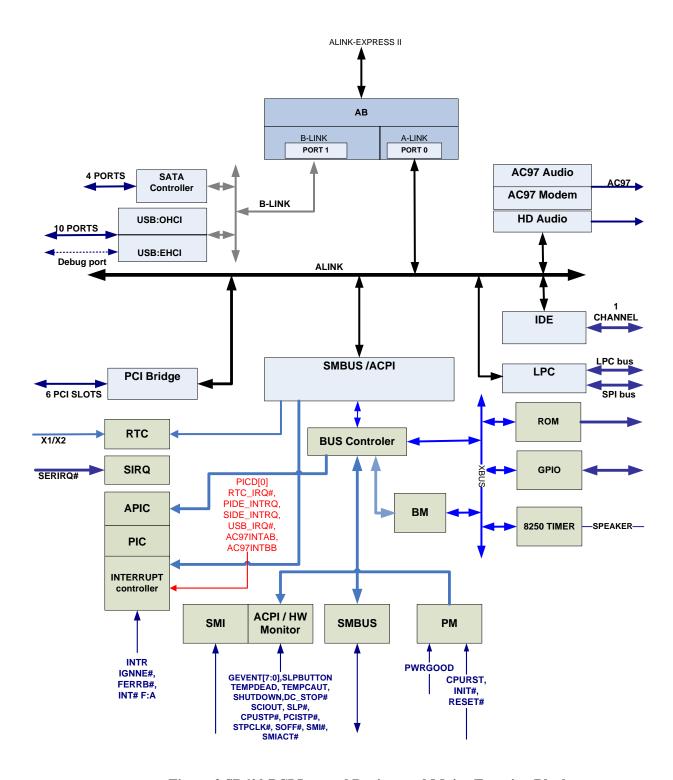

This section contains two block diagrams for the SB600. *Figure 1* shows the SB600 internal PCI devices with their assigned bus, device, and function numbers. *Figure 2* shows the SB600 internal PCI devices and the major function blocks.

Figure 1 SB600 PCI Internal Devices

Figure 2 SB600 PCI Internal Devices and Major Function Blocks

# 2 SB600 Programming Architecture

# 2.1 PCI Devices and Functions

| <b>Bus:Device:Function</b>                                                                                                                              | <b>Function Description</b>                                                                                        | Dev ID                                             | Enable/Disable                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bus 0:Device 14h:Function 0                                                                                                                             | SMBus Controller                                                                                                   | 4385h                                              | Always enabled                                                                                                                                                            |

| Bus 0:Device 14h:Function 1                                                                                                                             | IDE Controller                                                                                                     | 438Ch                                              | Always enabled                                                                                                                                                            |

| Bus 0:Device 14h:Function 2                                                                                                                             | HD Audio Controller                                                                                                | 4383h                                              | PM IO Reg59h[Bit3] 0: Disables HD Audio 1: Enables HD Audio                                                                                                               |

| Bus 0:Device 14h:Function 3                                                                                                                             | LPC Controller                                                                                                     | 438Dh                                              | SMBus PCI Reg64h[Bit20] 0: Disables LPC controller 1: Enables LPC controller                                                                                              |

| Bus 0:Device 14h:Function 4                                                                                                                             | PCI to PCI Bridge                                                                                                  | 4384h                                              | Always enabled                                                                                                                                                            |

| Bus 0:Device 14h:Function 5                                                                                                                             | AC'97 Audio Controller                                                                                             | 4382h                                              | PM IO Reg59h[Bit0] 0: Enables AC97 1: Disables AC97                                                                                                                       |

| Bus 0:Device 14h:Function 6                                                                                                                             | AC'97 Modem Controller                                                                                             | 438Eh                                              | PM IO Reg59h[Bit1] 0: Enables MC97 1: Disables MC97                                                                                                                       |

| Bus 0:Device 13h:Function 5                                                                                                                             | EHCI USB Controller                                                                                                | 4386h                                              | SMBus PCI Reg68h[Bit0] 0: Enables EHCI controller 1: Disables EHCI controller                                                                                             |

| Bus 0:Device 13h:Function 0<br>Bus 0:Device 13h:Function 1<br>Bus 0:Device 13h:Function 2<br>Bus 0:Device 13h:Function 3<br>Bus 0:Device 13h:Function 4 | OHCI USB Controller #0 OHCI USB Controller #1 OHCI USB Controller #2 OHCI USB Controller #3 OHCI USB Controller #4 | 4387h<br>4388h<br>4389h<br>438Ah<br>438Bh<br>438Ch | SMBus PCI Reg68h[Bit1] SMBus PCI Reg68h[Bit2] SMBus PCI Reg68h[Bit3] SMBus PCI Reg68h[Bit4] SMBus PCI Reg68h[Bit5] 0: Disables OHCI controller 1: Enables OHCI controller |

| Bus 0:Device 12h:Function 0                                                                                                                             | Raid-5 Serial ATA Controller Non-Raid-5 Serial ATA Controller                                                      | 4381h<br>4380h                                     | SMBus PCI Reg ADh[bit 0]                                                                                                                                                  |

# 2.2 I/O Map

The I/O map is divided into Fixed and Variable address ranges. Fixed ranges cannot be moved, but can be disabled in some cases. Variable ranges are configurable.

# 2.2.1 Fixed I/O Address Ranges

## 2.2.1.1 Fixed I/O Address Ranges – SB600 Proprietary Ports

| I/O Address | Description                                       | Enable Bit                            |

|-------------|---------------------------------------------------|---------------------------------------|

| C00h-C01h   | IRQ Routing Index/Data register                   | SMBus PCI Reg64h[Bit0]                |

| C14h        | PCI Error Control register SMBus PCI Reg78h[Bit4] |                                       |

| C50h-C51h   | Client Management Index /Data registers           | SMBus PCI Reg 79h[Bit3]               |

| C52h        | GPM Port                                          | SMBus PCI Reg78h[Bit6]                |

| C6Fh        | Flash Rom Program Enable                          | SMBus PCI Reg78h[Bit8]                |

| CD0h-CD1h   | PM2 Index/Data                                    |                                       |

| CD4h-CD5h   | BIOS RAM Index/Data                               |                                       |

| CD6h-CD7h   | Power Management I/O register                     | SMBus PCI Reg64h[Bit2] & Reg78h[Bit9] |

# 2.2.2 Variable I/O Decode Ranges

| I/O Name                                              | Description                                   | Configure Register                 | Range Size<br>(Bytes) |

|-------------------------------------------------------|-----------------------------------------------|------------------------------------|-----------------------|

| PIO0                                                  | Programmable I/O Range 0                      | PM IO Reg14h & Reg15h              | <=16                  |

| PIO1                                                  | Programmable I/O Range 1                      | PM IO Reg16H & Reg17H              | <=16                  |

| PIO2                                                  | Programmable I/O Range 2                      | PM IO Reg18h & Reg19h              | <=16                  |

| PIO3                                                  | Programmable I/O Range 3                      | PM IO Reg1Ah & Reg1Bh              | <=16                  |

| PIO4                                                  | Programmable I/O Range 4                      | PM IO Reg A0h & Reg A1h            | <=16                  |

| PIO5                                                  | Programmable I/O Range 5                      | PM IO Reg A2h & Reg A3h            | <=16                  |

| PIO6                                                  | Programmable I/O Range 6                      | PM IO Reg A4h & Reg A5h            | <=16                  |

| PIO7 Programmable I/O Range 7 PM IO Reg A6h & Reg A7h |                                               | <=16                               |                       |

| PM1_EVT                                               | 1_EVT ACPI PM1a_EVT_BLK PM IO Reg20h & Reg21h |                                    | 4                     |

| PM1_CNT                                               | ACPI PM1a_CNT_BLK                             | PM IO Reg22h & Reg23h              | 2                     |

|                                                       |                                               | PM IO Reg24h & Reg25h              | 4                     |

| P_BLK ACPI P_BLK PM IO Reg26h & Reg27h                |                                               | 6                                  |                       |

| GPE0_EVT                                              | GPE0_EVT ACPI GPE0_EVT_BLK PM IO Reg28h & Reg |                                    | 8                     |

| SMI CMD Block * SMI Command Block PM IO               |                                               | PM IO Reg2Ah & Reg2Bh              | 2                     |

| Pma Cnt Block PMa Control Block PM IO Reg20           |                                               | PM IO Reg2Ch & Reg2Dh              | 1                     |

| Reserved Reserved PM IO Reg2Eh                        |                                               | PM IO Reg2Eh & Reg2Fh              | 1                     |

| SMBus                                                 | SMBus IO Space                                | SMBus PCI Reg90h &<br>RegD2h[Bit0] | 16                    |

### \* Note:

- The SMI CMD Block must be defined on the 16-bit boundary, i.e., the least significant nibble of the address must be zero (for example, B0h, C0h etc.)

- The SMI CMD Block consists of two ports the SMI Command Port at base address, and the SMI Status Port at base address+1.

- The writes to SMI Status Port will not generate an SMI. The writes to the SMI Command Port will generate an SMI.

- The SMI Command and SMI Status ports may be written individually as 8 bit ports, or together as a 16-bit port.

# 2.3 Memory Map

| Memory Range          | Description           | Enable Bit                           |

|-----------------------|-----------------------|--------------------------------------|

| 0000 0000h-000D FFFFh | Main System Memory    |                                      |

| 0010 0000h- TOM       |                       |                                      |

| 000E 0000h-000F FFFFh | Either PCI ROM or LPC | PCI ROM : SMBus PCI Reg41h[Bit4]     |

|                       | ROM                   | LPC ROM : LPC Reg68h & LPC_Rom strap |

| FFC0 0000h-FFC7 FFFFh | FWH                   | LPC Reg70h[3:0]                      |

| FF80 0000h-FF87 FFFFh |                       |                                      |

| FFC8 0000h-FFCF FFFFh | FWH                   | LPC Reg70h[7:4]                      |

| FF88 0000h-FF8F FFFFh |                       |                                      |

| FFD0 0000h-FFD7 FFFFh | FWH                   | LPC Reg70h[11:8]                     |

| FF90 0000h-FF97 FFFFh |                       |                                      |

| FFD8 0000h-FFDF FFFFh | FWH                   | LPC Reg70h[15:12]                    |

| FF98 0000h-FF9F FFFFh |                       |                                      |

| FFE0 0000h-FFE7 FFFFh | FWH                   | LPC Reg70h[19:16]                    |

| FFA0 0000h-FFA7 FFFFh |                       |                                      |

| FFE8 0000h-FFEF FFFFh | FWH                   | LPC Reg70H[23:20]                    |

| FFA8 0000h-FFAF FFFFh |                       |                                      |

| FFF0 0000h-FFF7 FFFFh | FWH                   | LPC Reg70h[27:24]                    |

| FFB0 0000h-FFB7 FFFFh |                       |                                      |

| FFF8 0000h-FFFF FFFFh | FWH                   | LPC Reg70h[31:28]                    |

| FFB8 0000h-FFBF FFFFh |                       |                                      |

# 3 SB600 Early-POST Initialization

The system BIOS needs to configure the SB600 at the very beginning of POST. Some of the settings will change depending on the OEM design, or on the newer revision chipset.

## **3.1 512K/1M ROM Enable**

With the SB600 design, there can be two possible ROM sources: PCI ROM and LPC ROM. Two pin straps (UseLpcRom, FWHDisable) decide where the ROM is (see the SB600 databook). Upon system power on, the SB600 enables 256K ROM by default. The BIOS needs to enable 512K ROM or up to 1M for LPC ROM, if required.

#### 3.1.1 **PCI ROM**

| Control Bit            | Description                                                                                          | 256K ROM<br>(Default) | 512K ROM<br>Setting |

|------------------------|------------------------------------------------------------------------------------------------------|-----------------------|---------------------|

| SMBus PCI Reg41h[Bit1] | When set to 1, the address between FFF80000h to FFFDFFFFh will be directed to the PCI ROM interface. | 0                     | 1                   |

| SMBus PCI Reg41h[Bit4] | When set to 1, the address between 0E0000h to 0EFFFh will be directed to the PCI ROM interface.      | 0                     | 1                   |

### **3.1.2 LPC ROM**

To use the LPC ROM, the pin straps UseLpcRom, FWHDisable must be set accordingly.

| Control Bit(s)  | Description                           | Default    | 512K ROM<br>Setting | 1 M ROM<br>Setting |  |

|-----------------|---------------------------------------|------------|---------------------|--------------------|--|

| LPC PCI         | 16-bit starting & end address of the  | 000E0000h  | 000E0000h           | 000E0000h          |  |

| Reg68h          | LPC ROM memory address range 1.       | OOOLOOOOII | OOOEOOOOII          | UUUEUUUUN          |  |

| LPC PCI Reg6Ch  | 16-bit starting & end address of the  | FFFE0000   | FFF80000h           | FFF00000h          |  |

|                 | LPC ROM memory address range 2.       | h          | rrr80000011         | rrruuuuui          |  |

| LPC PCI         | Enable bits for LPC ROM memory        | 00b        | 11b 11b             |                    |  |

| Reg48Hh[Bits4:3 | address range 1 & 2.                  |            |                     |                    |  |

| ]               | Note: with pins straps set to LPC     |            |                     |                    |  |

|                 | ROM, these two bits have no effect on |            |                     |                    |  |

|                 | Reg68 & Reg6C.                        |            |                     |                    |  |

### 3.1.3 LPC ROM Read/Write Protect

The SB600 allows all or a portion of the LPC ROM addressed by the firmware hub to be read protected, write protected, or both read and write protected. Four dword registers are provided to select up to 4 LPC ROM ranges for read or write protection. The ROM protection range is defined by the base address and the length. The base address is aligned at a 2K boundary. The address length can be from 1K to 256K in increments of 1K.

### Register 50h, 54h, 58h, 5ch of Device 14h, Function 3

| Field Name    | Bits  | Description                                                                  |  |

|---------------|-------|------------------------------------------------------------------------------|--|

| Base Address  | 31:11 | ROM Base address. The most significant 21 bits of the base address are       |  |

|               |       | defined in this field. Bits 10:0 of the base address are assumed to be zero. |  |

|               |       | Base address, therefore, is aligned at a 2K boundary.                        |  |

| Length        | 10:2  | These 9 bits (0-511) define the length from 1K to 512K in increments of      |  |

|               |       | 1K.                                                                          |  |

| Read Protect  | 1     | When set, the memory range defined by this register is read protected.       |  |

|               |       | Reading any location in the range returns FFh.                               |  |

| Write Protect | 0     | When set, the memory range defined by this register is write protected.      |  |

|               |       | Writing to the range has no effect.                                          |  |

## **Example:**

Protect 32K LPC ROM starting with base address FFF80000.

Base address bits 31:11 1111 1111 1111 1000 0000 0 b

Length 32K bit  $10:2 = 31h = 000 \ 0111 \ 11 \ b$

Read protect bit 1 = 1

Write protect bit 0 = 1

Register 50h = 1111 1111 1111 1000 0000 0000 0111 1111 b = FFF8007F h

#### Note:

- 1. Registers 50h ~ 5Fh can be written once after the hardware reset. Subsequent writes to them have no effect.

- 2. Setting sections of the LPC ROM to either read or write protect will not allow the ROM to be updated by a flash programming utility. Most flash utilities write and verify ROM sectors, and will terminate programming if verification fails due to read protect.

### 3.1.4 SPI ROM controller

The SPI ROM interface is a new feature added to the SB600. Refer to the *AMD SB600 Register Reference Guide* for more information on this feature.

Note: The LPC ROM Read/Write Protect mentioned in the previous paragraph also applies to SPI. Two strap pins, PCICLK0 and PCICLK1, determine the SB600 boot up from LPC ROM or SPI ROM. There is no register status to reflect whether the current ROM interface is LPC or SPI.

## 3.2 Real Time Clock (RTC)

### 3.2.1 RTC Access

The internal RTC is divided into two sections: the clock and alarm function (registers 0 to 0Dh), and CMOS memory (registers 0Eh to FFh). The clock and alarm functions must be accessed through I/O ports 70h/71h. The CMOS memory (registers 0Eh to FFh) should be accessed through I/O ports 72h/73h.

## 3.2.1.1 Special Locked Area in CMOS

Some CMOS memory locations may be disabled for read/write. Register 6Ah of SMBus (Bus 0, Device 14h, Function 0) has bits to disable these CMOS memory locations. These bits can be written only once after each power up reset or PCI reset.

| RTCProtect- RW - 8 bits - [PCI_Reg: 6Ah] |     |         |                                                     |  |

|------------------------------------------|-----|---------|-----------------------------------------------------|--|

| Field Name Bits Default                  |     | Default | Description                                         |  |

| RTCProtect                               | 0   | 0h      | When set, RTC RAM index 38h:3Fh will be locked from |  |

|                                          |     |         | read/write. This bit can only be written once.      |  |

| RTCProtect                               | 1   | 0h      | When set, RTC RAM index F0h:FFh will be locked from |  |

|                                          |     |         | read/write. This bit can only be written once.      |  |

| RTCProtect                               | 2   | 0h      | When set, RTC RAM index E0h:EFh will be locked from |  |

|                                          |     |         | read/write. This bit can only be written once.      |  |

| RTCProtect 3 0h                          |     | 0h      | When set, RTC RAM index D0h:DFh will be locked from |  |

|                                          |     |         | read/write. This bit can only be written once.      |  |

| RTCProtect 4 0h                          |     | 0h      | When set, RTC RAM index C0h:CFh will be locked from |  |

|                                          |     |         | read/write. This bit can only be written once.      |  |

| Reserved                                 | 7:5 | 0h      |                                                     |  |

### 3.2.1.2 Century Byte

The RTC has a century byte at CMOS location 32h. Century is stored in a single byte and the BCD format is used for the century (for example, 20h for the year 20xx). This byte is accessed using I/O ports 70h and 71h. (The BIOS must set PMIO register 7Ch bit 4 to 1 to use this century byte at CMOS location 32h

### 3.2.1.3 Date Alarm

The RTC has a date alarm byte. This byte is accessed as follows:

- 1. Set to 1 the RTC register 0Ah, bit 4, using I/O ports 70h and 71h.

- 2. Write Date Alarm in BCD to register 0Dh using I/O ports 70h and 71h.

- 3. Clear to 0 the RTC register 0Ah bit 4 using I/O ports 70h and 71h.

Note: It is important to clear RTC register 0Ah bit 4 to zero; otherwise, the CMOS memory may not be accessed correctly from this point onward.

### 3.3 BIOS RAM

The SB600 has 256 bytes of BIOS RAM. Data in this RAM is preserved until RSMRST# or S5 is asserted, or until power is lost.

This RAM is accessed using index and data registers at CD4h/CD5h.

# 3.4 Serial IRQ

The SB600 supports serial IRQ, which allows one single signal to report multiple interrupt requests. The SB600 supports a message for 21 serial interrupts, which include 15 IRQs, SMI#, IOCHK#, and 4 PCI interrupts.

SMBus PCI Reg69h is used for setting serial IRQ.

| Bits in SMBus<br>PCI Reg69 | Description                          | Power-on<br>Default | Recommended<br>Value |

|----------------------------|--------------------------------------|---------------------|----------------------|

| 7                          | 1 – Enables the serial IRQ function  | 0                   | 1                    |

|                            | 0 – Disables the serial IRQ function |                     |                      |

| 6                          | 1 – Active (quiet) mode              | 0                   | 0                    |

|                            | 0 – Continuous mode                  |                     |                      |

| 5:2                        | Total number of serial IRQs = 17 +   | 0                   | 0100b                |

|                            | NumSerIrqBits                        |                     |                      |

|                            | 0 – 17 serial IRQs (15 IRQs, SMI#,   |                     |                      |

|                            | IOCHK#)                              |                     |                      |

|                            | 1 – 18 serial IRQs (15 IRQs, SMI#,   |                     |                      |

|                            | IOCHK#, INTA#)                       |                     |                      |

|                            |                                      |                     |                      |

|                            | 15 - 32 serial IRQ's                 |                     |                      |

|                            | The SB600 serial IRQ can support 15  |                     |                      |

|                            | IRQs, SMI#, IOCHK#, INTA#,           |                     |                      |

|                            | INTB#, INTC#, and INTD#.             |                     |                      |

| 1:0                        | Number of clocks in the start frame  | 0                   | 00b                  |

Note: The BIOS should enter the continuous mode first when enabling the serial IRQ protocol, so that the SB600 can generate the start frame.

#### 3.5 SubSystemID and SubSystem Vendor ID

SubSytem ID and SubSystem Vendor ID can be programmed in various functions of SB600 register 2Ch. These registers are write-once registers. For example, to program a SubSystem vendor ID of 1002h and SubSystem ID of 4341h in AC97 device 14h, function 5, use the following assembly language sample code:

eax,8000A52Ch mov

mov dx,0CF8h

out dx,eax

dx,0CFCh mov

mov eax,43411002h

out dx,eax

# 3.6 AMD Athlon<sup>TM</sup> Processor Registers

The SB600 is set for the AMD Athlon processor by hardware strap. The following registers in the PM IO space (accessed through index/data registers at CD6h/CD7h) are specific for the AMD Athlon processor. For the early post initialization these registers may be left at default values.

SMAFx in the table below are sent with STPCLK messages down the HyperTransport<sup>TM</sup> link.

| Register  | Name             | Default | Description                                     |

|-----------|------------------|---------|-------------------------------------------------|

| PM IO 80h | SMAF0            | 06h     | System Management Action for C2 and S4/S5       |

| PM IO 81h | SMAF1            | 21h     | System Management Action for VFID and C3        |

| PM IO 82h | SMAF2            | 43h     | System Management Action for S3 and S1          |

| PM IO 83h | SMAF3            | 55h     | System Management Action for thermal and normal |

|           |                  |         | throttling.                                     |

| PM IO 85h | CF9Rst           | 00h     | Full reset/INIT                                 |

| PM IO 86h | Thermal Throttle | 00h     | Enables time control for thermal throttling.    |

|           | Control          |         |                                                 |

| PM IO 87h | LdtStpCmd        | 00h     | Write bit[0] = 1 to generate C3                 |

| PM IO 88h | LdtStartTime     | 00h     | LDTSTP# assertion delay in microseconds         |

| PM IO 8Ah | LdtAgpTimeCntl   | 00h     | LDTSTP# de-assertion delay select               |

| PM IO 8Bh | StutterTime      | 00h     | Stutter LDTSTP# duration in microseconds        |

| PM IO 8Ch | StpClkDlyTime    | 00h     | STPCLK# assertion in microseconds               |

| PM IO 8Dh | AbPmeCntl        | 0Eh     | Fake A-link bridge PME                          |

# 3.7 System Restart after Power Fail

The way the system restarts following the power-fail/power-restore cycle depends both on the PMIO register 74h [bits 1:0], and the hardware jumper on the SB600 pin ACPWR\_Strap.

| PMIO         | Description                                                                                                                                                            |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Register 74h |                                                                                                                                                                        |

| bits[1:0]    |                                                                                                                                                                        |

| 00b          | The system restart will depend on the ACPWR_Strap pin pull up/down state.                                                                                              |

|              | Pin = 0: The system will restart without pressing the power button                                                                                                     |

|              | Pin = 1: The system will remain off until the power button in pressed.                                                                                                 |

| 01b          | The system will always restart after the power is restored.                                                                                                            |

| 10b          | The system will remain off until the power button is pressed.                                                                                                          |

| 11b          | At power-up the system will either restart or remain off depending on the state of the                                                                                 |

|              | system at power failure. If the system was on when the power failed, the system will restart at power-up. If the system was off when the power failed, the system will |

|              | remain off after the power is restored. Pressing the power button is required to restart                                                                               |

|              | the system.                                                                                                                                                            |

Notes on programming the PMIO register 74h:

- 1. PMIO register bits[3:0] should be used for programming. Bits[7:4] are read-only bits and reflect the same values as bits[3:0].

- 2. Bit2 is used by the hardware to save the power on/off status. This bit should not be modified during Software/BIOS programming. The BIOS programmer should always read the PMIO register 74h, modify bit3 and bits[1:0] as required, and write back the PMIO register 74h.

## 3.7.1 Power Fail and Alarm Setup

The state of the machine after the power-fail/power-restore cycle is controlled by PMIO register 74h bits[1:0] as described above. This programming can be over-ridden for the special case when the alarm is set. When both the alarm and the PMIO register 74h bit3 are set, the system will restart after the power is restored, regardless of how register 74h bits [1:0] are defined.

# 4 PCI IRQ Routing

# 4.1 PCI IRQ Routing Registers

The SB600 uses one pair of I/O ports to do the PCI IRQ routing. The ports are at C00h/C01h.

| Address | Register Name  | Description                 |

|---------|----------------|-----------------------------|

| C00h    | PCI_Intr_Index | PCI IRQ Routing Index       |

|         |                | 0 – INTA#                   |

|         |                | 1 – INTB#                   |

|         |                | 2 – INTC#                   |

|         |                | 3 – INTD#                   |

|         |                | 4 – SCI                     |

|         |                | 5 – SMBus interrupt         |

|         |                | 9 – INTE#                   |

|         |                | 0Ah – INTF#                 |

|         |                | 0Bh – INTG#                 |

|         |                | 0Ch – INTH#                 |

| C01h    | PCI_Intr_Data  | 0 ~ 15 : IRQ0 to IRQ15      |

|         |                | IRQ0, 2, 8, 13 are reserved |

# 4.2 PCI IRQ BIOS Programming

PCI IRQs are assigned to interrupt lines using I/O ports at C00h and C01h in index/data format. The register C00h is used for index as written with index number 0 through 0Ch as described in section 4.1 above. Register C01h is written with the interrupt number as data.

The following assembly language example assigns INTB# line to interrupt 10 (0Ah).

| mov | dx,0C00h | ; To write to IO port C00h                          |

|-----|----------|-----------------------------------------------------|

| mov | al,02h   | ; Index for PCI IRQ INTB# as defined in section 4.1 |

| out | dx,al    | ; Index is now set for INTB#                        |

| mov | dx,0C01h | ; To write interrupt number 10 (0Ah)                |

| mov | al,0Ah   | ; Data is interrupt number 10 (0Ah)                 |

| out | dx,al    | ; Assign IRQB# to interrupt 10                      |

## 4.3 Integrated PCI Devices IRQ Routing

In the SB600, the AC'97 and USB need PCI IRQ. Internally, they are routed to different PCI INT#s.

| Device                       | Reg3Dh of<br>PCI Device | PCI INT#        | Description            |

|------------------------------|-------------------------|-----------------|------------------------|

| Bus 0:Device 14h:Function 1  | 01                      | INTA#           | IDE Controller*        |

| Bus 0:Device 14h: Function 2 | 01                      | Programmable*** | High Definition Audio  |

| Bus 0:Device 14h:Function 5  | 02                      | INTB#           | AC'97 Audio Controller |

| Bus 0:Device 14h:Function 6  | 02                      | INTB#           | AC'97 Modem Controller |

| Bus 0:Device 13h:Function 0  | 01                      | INTA#           | OHCI USB Controller #1 |

| Bus 0:Device 13h:Function 1  | 02                      | INTB#           | OHCI USB Controller #2 |

| Bus 0:Device 13h:Function 2  | 03                      | INTC#           | EHCI USB Controller    |

| Bus 0:Device 13h: Function 3 | 02                      | INTB#           | OHCI USB Controller #3 |

| Bus 0:Device 13h: Function 4 | 03                      | INTC#           | OHCI USB Controller #4 |

| Bus 0:Device 13h: Function5  | 04                      | INTD#           | EHCI USB Controller    |

| Bus 0:Device 12h:Function 0  | 01                      | Programmable**  | SATA Controller #1     |

| Bus 0:Device 11h:Function 0  | 01                      | Programmable**  | SATA Controller #2     |

#### Notes:

## 4.3.1 IRQ Routing for HD Audio

Interrupt routing for device 14h, function 2 HD Audio is done through PCI SMBUS (device 14h, function 0) register 63h. Values from INTA# to INTH# can be set in this register.

**Sample Code**: Set High Definition Audio interrupt routing to INTA#:

mov eax,8000A060h; Device 14h, function 0, registers 60h-63h

mov dx,0CF8h ; PCI configuration Index register

out dx,eax; Set to read/write registers 60h-63h

mov dx,0CFFh ; PCI configuration Data register for 63h

mov al,0 ; Set to INTA#

out dx,al ; Write to PCI register 63h

Note: The SB600 has provisions to modify the interrupt pin register (PCI register 3Dh) for special conditions. This pin is modified through device 14h, function 2, register 44h. Under normal circumstances do not modify this register. The default is Pin 1.

<sup>\*</sup> IDE controller needs PCI IRQ only if it is set to the native mode.

<sup>\*\*</sup> Smbus\_pci\_config 0xAF [4:2] for SATA1 Smbus\_pci\_config 0xAF [7:5] for SATA2

<sup>\*\*\*</sup> Refer to section 4.3.1 for details.

# 4.4 PCI IRQ Routing for APIC Mode

| PCI IRQ | APIC Assignment |

|---------|-----------------|

| INTA#   | 16              |

| INTB#   | 17              |

| INTC#   | 18              |

| INTD#   | 19              |

| INTE#   | 20              |

| INTF#   | 21              |

| INTG#   | 22              |

| INTH#   | 23              |

# **5** SMBus Programming

The SB600 SMBus (System Management Bus) complies with SMBus Specification Version 2.0.

### 5.1 SMBus I/O Base Address

The BIOS needs to set a valid SMBus I/O base address before enabling the SMBus Controller. There are two places at which the BIOS is able to set the SMBus I/O base addresses: one is at PCI Reg10h, another is at PCI Reg90h, and both are on the SMBus Controller (Bus 0, Device 14h, Function 0).

Before the BAR register, Reg10h, is assigned automatically during PCI bus enumeration, the BIOS needs to give a temporary SMBus I/O base address for accessing devices on the SMBus.

The SMBus controller enable bit is bit 0, register D2h, of the SMBus device (Bus 0, Device 14h, Function 0).

The following is a sample code to enable the SMBus with a temporary I/O base address:

SMB\_IO EQU 8040h

; Set SMBus I/O base address

mov dx, 0CF8h ; PCI Index Register

mov eax, 8000A090h ; Reg90h on SMBus PCI Controller

out dx, eax

mov dx, 0CFCh ; PCI Data Register

mov eax, SMB\_IO ; temp SMBus I/O base address

out dx, eax

; Enable the SMBus controller

mov dx, 0CF8h ; PCI Index Register

mov eax, 8000A0D0h ; RegD0 on SMBus PCI Controller

out dx, eax

mov dx, 0CFEh ; PCI Data Register

in al, dx ; read back from RegD2h

or al, 01 ; bit0 for enabling SMBus Controller interface

out dx, al

# 5.2 SMBus Timing

The SMBus frequency can be adjusted using different values in an 8-bit I/O register at the SMBus base + 0Eh location.

The SMBus frequency is set as follows:

SMBus Frequency = (Primary A-Link Clock)/(Count in index 0Eh \* 4)

The power-up default value in register 0Eh is A0h, therefore the default frequency is (66MHz)/(160 \* 4), or approximately 103 KHz.

The minimum SMBus frequency can be set with the value FFh in the register at index 0Eh, which yields:

(66MHz)/(255\*4) = 64.7 KHz.

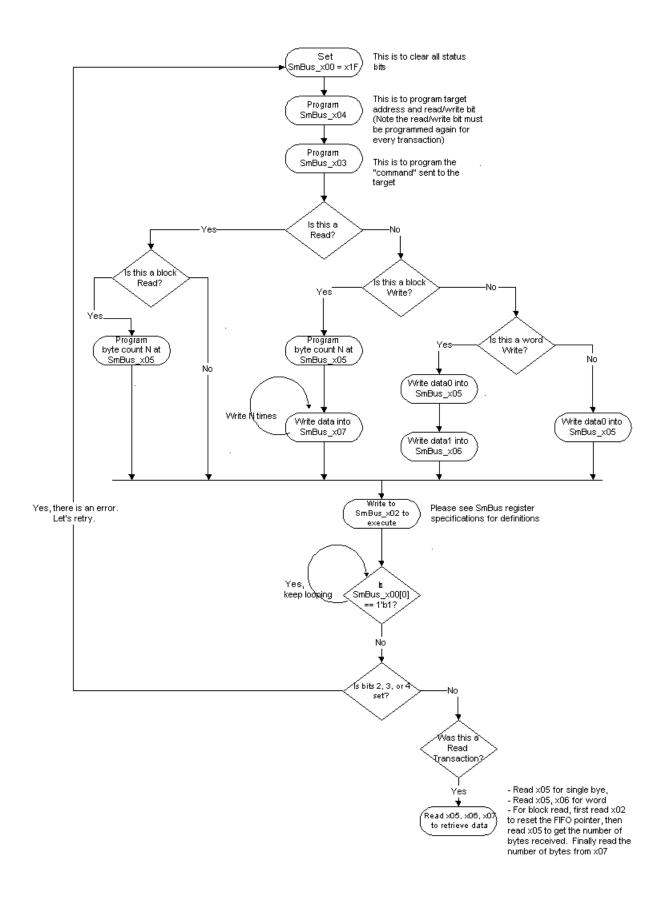

# 5.3 SMBus Host Controller Programming

| Step | Descriptions                                                                               | Register in<br>SMBus I/O<br>Space | Comments                                                                                                                           |

|------|--------------------------------------------------------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Wait until SMBus is idle.                                                                  | Reg00h[Bit0]                      | 0 – Idle<br>1 – Busy                                                                                                               |

| 2    | Clear SMBus status.                                                                        | Reg00h[Bit4:1]                    | Write all 1's to clear                                                                                                             |

| 3    | Set SMBus command.                                                                         | Reg03h                            | The command will go to SMBus device.                                                                                               |

| 4    | Set SMBus device address with read/write protocol                                          | Reg04h                            | Bit7:1 – address<br>Bit0 – 1 for read, 0 for write                                                                                 |

| 5    | Select SMBus protocol                                                                      | Reg02h[Bit4:2]                    |                                                                                                                                    |

| 6    | Do a read from Reg02 to reset the counter if it's going to be a block read/write operation | Reg02h                            |                                                                                                                                    |

| 7    | Set low byte when write command                                                            | Reg05h                            | Byte command – It is the written data Word command – It is the low byte data Block command – It is block count Others – Don't care |

| 8    | Set high byte when write command                                                           | Reg06h                            | Word command – It is the high byte data<br>Others – Don't care                                                                     |

| 9    | Write the data when block write                                                            | Reg07h                            | Block write – write data one by one to it<br>Others – Don't care                                                                   |

| 10   | Start SMBus command execution                                                              | Reg02h[Bit6]                      | Write 1 to start the command                                                                                                       |

| 11   | Wait for host not busy                                                                     | Reg00h[Bit0]                      |                                                                                                                                    |

| 12   | Check status to see if there is any error                                                  | Reg00h[Bit4:2]                    | With 1 in the bit, there is error                                                                                                  |

| 13   | Read data                                                                                  | Reg05h                            | Byte command – It is the read data Word command – It is the low byte data Block command – It is block count Others – Don't care    |

| 14   | Read data                                                                                  | Reg06h                            | Word command – It is the high byte data<br>Others – Don't care                                                                     |

| 15   | Read the data when block write                                                             | Reg07h                            | Block read – read data one by one.<br>Others – Don't care                                                                          |

The following flow chart illustrates the steps in programming the SMBus host controller.

## 6 IDE Controller

The SB600 IDE controller supports Ultra ATA 33/66/100/133 modes. The IDE controller can be configured into either the compatible mode or the native mode. Under the compatible mode, the IDE controller will use the legacy resources.

The SB600 allows programming of the IDE timing and mode for each drive independently on each channel.

### 6.1 IDE Channel Enable/Disable

| <b>Register on IDE Controller</b> | Bit                                         | Description                                    |

|-----------------------------------|---------------------------------------------|------------------------------------------------|

| Reg09h                            | 1                                           | Primary IDE channel programmable logic enable. |

| Reg48h                            | 0 Set 1 to disable the primary IDE channel. |                                                |

| Reg48h                            | 8                                           | Set 1 to disable the secondary IDE channel.    |

With the SB600, the BIOS must follow particular sequences to enable or disable the IDE channels (see section 6.1.1 and 6.1.2 below for further information).

#### **6.1.1 IDE Channel Enable**

Both of the IDE channels are enabled as power-on default. To enable an IDE channel, the BIOS must be set as follows:

- 1. Set the IDE channel programmable logic enable bit in Reg09h.

- 2. Clear the IDE channel disable bit in Reg48h to enable the IDE channel.

Note: No IDE I/O port access is allowed in between step (1) and step (2). It is recommended that the BIOS execute step (2) immediately after step (1).

Refer to section 14.3.5 for a programming sample.

### **6.1.2 IDE** Channel Disable

To disable an IDE channel, the BIOS must:

- 1. Set IDE channel programmable logic enable bit in Reg09h.

- 2. Set IDE channel disable bit in Reg48h to disable IDE channel.

**Note:** No IDE I/O port access is allowed in between step (1) and (2). It's recommended that the BIOS execute step (2) immediately after step (1).

**Note:** Secondary IDE channel should always be disabled for there is no pin out for secondary IDE.

After the IDE disable sequence, the IDE channel programmable logic enable bit will be cleared automatically.

Refer to section 14.3.4 for a programming sample.

### 6.2 PIO Modes

The SB600 supports IDE PIO mode 0, 1, 2, 3, and 4. For PIO mode selection, the BIOS needs to program not only the PIO mode register, but also the PIO timing register.

#### **6.2.1 PIO** Mode

The BIOS can simply give the PIO mode number through Reg4Ah on the IDE controller.

## 6.2.2 PIO Timing

Two parameters determine the PIO bus-cycle timing: the command width and the recovery width.

CT (bus-cycle timing) =

$$30 \text{ns} * ((\text{command width} + 1) + (\text{recovery width} + 1))$$

For each PIO mode, the command width and the recovery width must be set by the BIOS accordingly:

| PIO Mode | Command Width<br>(In Reg40h) | Recovery Width<br>(In Reg40h) | CT                             |

|----------|------------------------------|-------------------------------|--------------------------------|

| 0        | 9                            | 9                             | 600ns = 30 * ((9+1) + (9+1))   |

| 1        | 4                            | 7                             | 390ns = 30 * ((4+1) + (7+1))   |

| 2        | 3                            | 4                             | 270ns = 30 * ((3+1) + (4+1))   |

| 3        | 2                            | 2                             | 180ns = $30 * ((2+1) + (2+1))$ |

| 4        | 2                            | 0                             | 120ns = 30 * ((2+1) + (0+1))   |

### 6.3 DMA Modes

The SB600 IDE controller can run at either the legacy (Multi-Words) DMA mode, or the Ultra-DMA mode.

### 6.3.1 Legacy (Multi-Words) DMA mode

The SB600 IDE controller will run at the legacy DMA mode only when the Ultra-DMA mode is disabled.

Two parameters determine the DMA bus-cycle timing: the command width and the recovery width.

CT (bus-cycle timing) =

$$30 \text{ns} * ((\text{command width} + 1) + (\text{recovery width} + 1))$$

For each legacy DMA mode, the command width and recovery width must be set by the BIOS accordingly:

| Legacy DMA<br>Mode | Command Width<br>(In Reg44h) | Recovery Width<br>(In Reg44h) | CT                            |

|--------------------|------------------------------|-------------------------------|-------------------------------|

| 0                  | 7                            | 7                             | 480ns = 30 * ((7+1) + (7+1))  |

| 1                  | 2                            | 1                             | 150 ns = 30 * ((2+1) + (1+1)) |

| 2                  | 2                            | 0                             | 120ns = 30 * ((2+1) + (0+1))  |

## 6.3.2 Ultra-DMA Mode

The SB600 IDE controller supports UDMA mode 0, 1, 2, 3, 4, 5, and 6.

It only takes two simple steps to program the SB600 IDE controller into the UDMA mode:

- 1. Set the mode number in UDMA mode register (Reg56h).

- 2. Enable the UDMA mode through the UDMA control register (Reg54h). The UDMA buscycle timing is fixed after the UDMA mode is selected.

| UDMA Mode | <b>Bus-Cycle Timing (ns)</b> |

|-----------|------------------------------|

| 0         | 120                          |

| 1         | 90                           |

| 2         | 60                           |

| 3         | 45                           |

| 4         | 30                           |

| 5         | 20                           |

| 6         | 15                           |

# 7 Serial ATA (SATA)

The SB600 has two SATA devices. For ASIC revision A21, they are at Bus 0, Device 12h, Function 0 and Bus 0, Device 11h, Function 0. For revisions A11 and A12, they are at Bus 0, Device 13h, Function 3 and Function 4. The SATA devices are enabled/disabled through a register at ADh in the SMBus controller (Device 14h, function 0).

| MiscSata - RW - 8 bits - [PCI_Reg: ADh] |      |         |                                                        |  |

|-----------------------------------------|------|---------|--------------------------------------------------------|--|

| Field Name                              | Bits | Default | Description                                            |  |

| SATA Enable                             | 0    | 1       | SATA enable                                            |  |

| SataSmbusEn                             | 1    | 0       | SATA SMBus enable                                      |  |

| SataSmbusMode                           | 2    | 0       | SATA SMBus mode, set to 1 to put SATA I2C on GPIO pins |  |

| SataPsvEn                               | 5    | 1       | SATA power saving enable                               |  |

| Enable                                  |      |         |                                                        |  |

MiscSata register

The SATA option ROM initial load size is 64KB, and the run time size is 2KB.

A SATA controller enable/disable sample code is found in section 14.2.5.

A SATA class ID change sample code is found in section 14.2.6.

# 7.1 SATA Hot Plug

The SATA hot plug feature is implemented through the following registers:

- 1. ACPI GPE0 Block status register bit 31 for SCI status.

- 2. ACPI GPE0 Block enable register bit 31 for SCI enable.

- 3. PMIO register 37h bit 2 to trigger SATA hot plug SCI.

- 1 = Rising edge.

- 0 =Falling edge trigger.

- 4. The SATA internal status is set whenever a SATA hard drive is plugged in, unplugged, powered up, or powered down. The status registers are:

Register BAR 5 + 10Ah, bit 0, for primary channel.

Register BAR 5 + 18Ah, bit 0, for secondary channel.

### 7.1.1 Sample Code

See section 14.7 for the SATA Hot Plug sample code.

# **8** Power Management

On the SB600, PM registers can be accessed through I/O ports CD6h/CD7h. Before initiating any power management functions in the SB600, the BIOS needs to set the I/O base addresses for the ACPI I/O register, the SMI Command Port, etc.

| I/O Name        | Description       | Configure Register    | Range Size<br>(Bytes) |

|-----------------|-------------------|-----------------------|-----------------------|

| PM1_EVT         | ACPI PM1a_EVT_BLK | PM IO Reg20h & Reg21h | 4                     |

| PM1_CNT         | ACPI PM1a_CNT_BLK | PM IO Reg22h & Reg23h | 2                     |

| PM_TMR          | ACPI PM_TMR_BLK   | PM IO Reg24h & Reg25h | 4                     |

| P_BLK           | ACPI P_BLK        | PM IO Reg26h & Reg27h | 6                     |

| GPE0_EVT        | ACPI GPE0_EVT_BLK | PM IO Reg28h & Reg29h | 8                     |

| SMI CMD Block * | SMI Command Block | PM IO Reg2Ah & Reg2Bh | 2                     |

<sup>\*</sup> Notes:

- The SMI CMD Block must be dword aligned, i.e., the least significant two bits of the address must be zero (address[1:0] must be 00). For example, B0h, B4h, B8h, BCh, etc.

- The SMI CMD Block consists of two ports the SMI Command Port at base address, and the SMI Status Port at base address+1.

- The writes to the SMI Status Port will not generate an SMI. The writes to the SMI Command Port will generate an SMI.

- The SMI Command and SMI Status ports may be written individually as 8 bit ports, or together as a 16 bit port.

# 8.1 SMI Handling – EOS (PM IO Reg10h[Bit0])

Upon each SMI generation, the SB600 will clear the EOS bit automatically. At the end of the SMI service, the BIOS needs to clear the status bit of the SMI event and re-enable the EOS; otherwise, the SB600 will not be able to generate SMI, even if SMI events arrive.

# 8.2 Programmable I/Os

There are eight sets of programmable I/Os available on the SB600. The BIOS can use them for I/O trapping, which means that an SMI will be generated if any access falls into the PIO range.

The PIO address range can be set to 2, 4, 8, and 16.

| I/O Name | Description              | Configure Register    | Enable             | Status             |

|----------|--------------------------|-----------------------|--------------------|--------------------|

| PIO0     | Programmable I/O Range 0 | PM IO Reg14h & Reg15h | PM IO Reg1Ch[Bit7] | PM IO Reg1Dh[Bit7] |

| PIO1     | Programmable I/O Range 1 | PM IO Reg16h & Reg17h | PM IO Reg1Ch[Bit6] | PM IO Reg1Dh[Bit6] |

| PIO2     | Programmable I/O Range 2 | PM IO Reg18h & Reg19h | PM IO Reg1Ch[Bit5] | PM IO Reg1Dh[Bit5] |

| PIO3     | Programmable I/O Range 3 | PM IO Reg1Ah & Reg1Bh | PM IO Reg1Ch[Bit4] | PM IO Reg1Dh[Bit4] |

| I/O Name | Description              | Configure Register   | Enable              | Status             |

|----------|--------------------------|----------------------|---------------------|--------------------|

| PIO4     | Programmable I/O Range 4 | PM IO RegA0 & RegA1h | PM IO Reg A8h[Bit0] | PM IO RegA9h[Bit0] |

| PIO5     | Programmable I/O Range 5 | PM IO RegA2 & RegA3h | PM IO Reg A8h[Bit1] | PM IO RegA9h[Bit1] |

| PIO6     | Programmable I/O Range 6 | PM IO RegA4 & RegA5h | PM IO Reg A8h[Bit2] | PM IO RegA9h[Bit2] |

| PIO7     | Programmable I/O Range 7 | PM IO RegA6 & RegA7h | PM IO Reg A8h[Bit3] | PM IO RegA9h[Bit3] |

Note: PM IO Reg04h[Bit7] is the overall control bit for enabling all the PIOs. The BIOS must set it before using any PIO.

## **8.3 Power Management Timers**

There are two PM timers available on the SB600 – PM Timer 1 and PM Timer 2. The PM Timer 1 (Inactivity Timer) can be programmed to reload on some activities, but not the PM Timer 2 (Activity Timer).

## **8.3.1** PM Timer 1 (Inactivity Timer)

The PM Timer 1 is a 6-bit timer with a granularity of 1 minute. The BIOS can set the initial value of the PM Timer 1 through PM IO Reg0Bh. PM IO Reg0Ch will return the current value of the decrementing counter.

The PM Timer 1 is typically used as a stand-by timer under the APM mode.

| PM Timer1 Reloading On      | Description                          | Enable               |

|-----------------------------|--------------------------------------|----------------------|

| IRQ[15:8]                   | IRQ[15:8] activity.                  | PM IO Reg08h[Bit7:0] |

| IRQ[7:3], NMI, and IRQ[1:0] | IRQ[7:3], NMI, and IRQ[1:0] activity | PM IO Reg09h[Bit7:0] |

| Programmable IO             | Any access to PIO ports.             | PM IO Reg0Ah[Bit7]   |

| Parallel Port               | Parallel ports activity              | PM IO Reg0Ah[Bit6]   |

| Serial Port                 | Serial Ports activity                | PM IO Reg0Ah[Bit5]   |

| IDE Port                    | IDE port activity                    | PM IO Reg0Ah[Bit4]   |

| Floppy Port                 | Floppy port activity                 | PM IO Reg0Ah[Bit3]   |

| Game Port                   | Game port (201H) activity            | PM IO Reg0Ah[Bit2]   |

| ExtEvent1                   | Assert ExtEvent1 pin                 | PM IO Reg0Ah[Bit1]   |

| ExtEvent0                   | Assert ExtEvent0 pin                 | PM IO Reg0Ah[Bit0]   |

## 8.3.2 PM Timer 2 (Activity Timer)

The PM Timer 2 is an 8-bit timer with a granularity of  $500 \, \mu s$ . The BIOS can set the initial value of the PM Timer 2 through PM IO Reg12h. PM IO Reg13h will return the current value of the decrementing counter.

Note: The PM Timer 2 cannot be configured to reload on any system activities.

### 8.4 SMI Events

The following is a list of all the SMI events available on the SB600. The events can only generate SMI, not SCI or wakeup events.

The global SMI disable bit is PM IO register 53h, bit [3].

PM IO register 53h bit [3] = 0 SMI# enabled (default)

PM IO register 53h bit [3] = 1 SMI# disabled (all events disabled)

| SMI Source                  | Description                          | Enable                  | Status                  |

|-----------------------------|--------------------------------------|-------------------------|-------------------------|

| Software SMI                | Set SmiReq (PM IO                    | Always                  | PM IO Reg01h[Bit4]      |

| (obsolete way)              | Reg00h[Bit4]) to generate SMI.       |                         |                         |

| Software SMI                | Any writing to SMI Command           | PM IO Reg0Eh[Bit2]      | PM IO Reg0Fh[Bit2]      |

|                             | port.                                |                         |                         |

| PM Timer 1                  | Timeout on PM Timer 1.               | PM IO Reg00h[Bit1]      | PM IO Reg01h[Bit1]      |

|                             | Activity on PM IO register 08h,      |                         |                         |

| DM (TE) O                   | 09h, 0Ah will retrigger timer        | DM IO D 001 [D': 2]     | DM IO D 011 [D'/2]      |

| PM Timer 2                  | Timeout on PM Timer 2.               | PM IO Reg00h[Bit2]      | PM IO Reg01h[Bit2]      |

| IDO[15.0]                   | (See section 9.3.2)                  | DM IO D = =021-[D:47.0] | DM 10 D = =051-[D:47.0] |

| IRQ[15:8]                   | IRQ[15:8] activity.                  | PM IO Reg02h[Bit7:0]    | PM IO Reg05h[Bit7:0]    |

| IRQ[7:3], NMI, and IRQ[1:0] | IRQ[7:3], NMI, and IRQ[1:0] activity | PM IO Reg03h[Bit7:0]    | PM IO Reg06h[Bit7:0]    |

| Programmable I/O            | Any access to PIO ports              | PM IO Reg04h[Bit7]      | PM IO Reg1Dh[Bit7:4]    |

| r Togrammable 1/O           | Any access to FIO ports              | AND                     | r w to Region[bit/.4]   |

|                             |                                      | PM IO Reg1Ch[Bit7:4]    |                         |

| Parallel Port               | Parallel ports activity              | PM IO Reg04h[Bit6]      | PM IO Reg07h[Bit6]      |

| Serial Port                 | Serial Ports activity                | PM IO Reg04h[Bit5]      | PM IO Reg07h[Bit5]      |

| IDE Port                    | IDE port activity                    | PM IO Reg04h[Bit4]      | PM IO Reg07h[Bit4]      |

| Floppy Port                 | Floppy port activity                 | PM IO Reg04h[Bit3]      | PM IO Reg07h[Bit3]      |

| Game Port                   | Game port (201h) activity            | PM IO Reg04h[Bit2]      | PM IO Reg07h[Bit2]      |

| ExtEvent1                   | Assert ExtEvent1 pin                 | PM IO Reg04h[Bit1]      | PM IO Reg07h[Bit1]      |

| ExtEvent0                   | Assert ExtEvent0 pin                 | PM IO Reg04h[Bit0]      | PM IO Reg07h[Bit0]      |

| Mouse/Keyboard              | Mouse/Keyboard port activity         | PM IO Reg1Ch[Bit3]      | PM IO Reg1Dh[Bit3]      |