### **Arch Meter Corporation**

Rm.807, Bldg.53,195 Sec. 4 Chung Hsing Rd., Chutung, Hsinchu, Taiwan 310, R.O.C. Tel: 886-3-591-0234 Fax: 886-3-591-0342 E-mail : <u>sales@archmeter.com.tw</u> http:// www.archmeter.com

# PS1000 User Guide V1.2

Preliminary datasheet

# Index

| 1. System Architecture        |

|-------------------------------|

| 2. Mode Control               |

| 3. Clock Setting              |

| 3.1 MCU Clock Setting         |

| 3.2 ADC Clock Setting9        |

| 3.3 DSP Clock Setting11       |

| 4. SFR Mapping13              |

| 5. I/O Mapping                |

| 6. DSP                        |

| 6.1 DSP Program               |

| 6.2 AGC                       |

| 6.3 DSP Status                |

| 7. MCU                        |

| 7.1 32-bit ALU                |

| 7.2 MODE Control              |

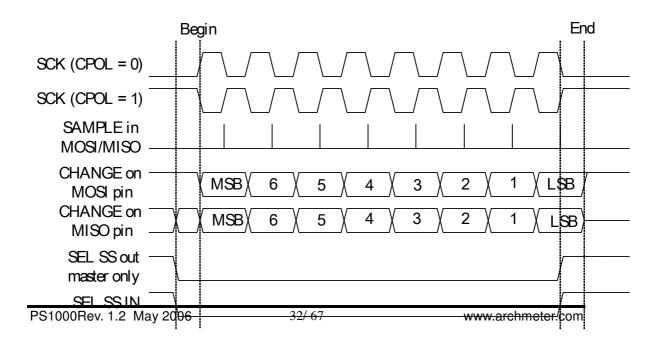

| 8. SPI                        |

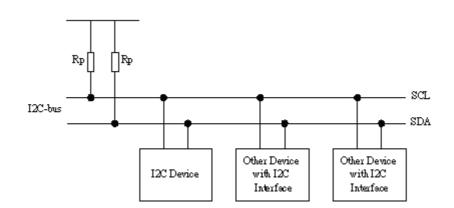

| 9. I <sup>2</sup> C           |

| 9.1 Registers                 |

| 9.2 Operation Modes           |

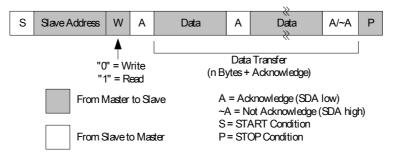

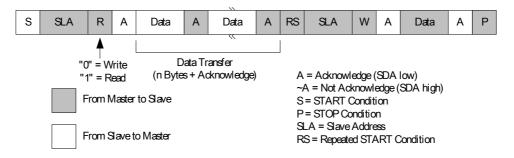

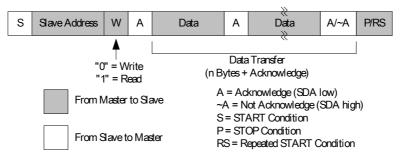

| 9.2.1 Master Transmitter Mode |

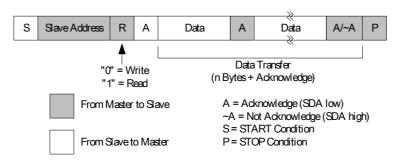

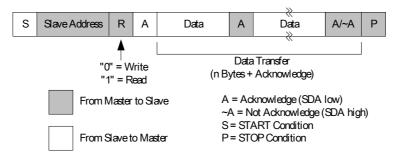

| 9.2.2 Master Receiver Mode    |

| 9.2.3 Slave Receiver Mode     |

| 9.2.4 Slave Transmitter Mode  |

| 9.3 Status Codes              |

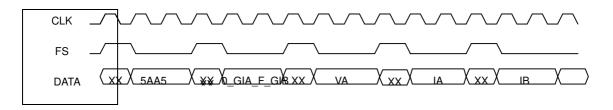

| 10. SSP                       |

| 11. RTC                       |

| 12. LCD                       |

| 13. Interrupt                 |

|                               |

| 14. Power Management          |

| 14. Power Management          |

PS1000Rev. 1.2 May 2006

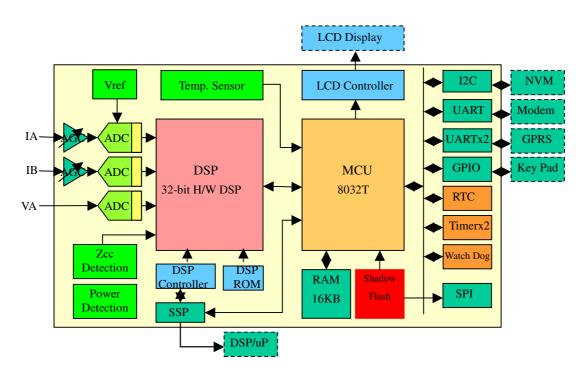

# **1. System Architecture**

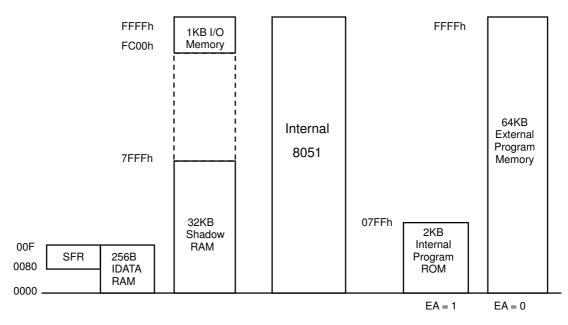

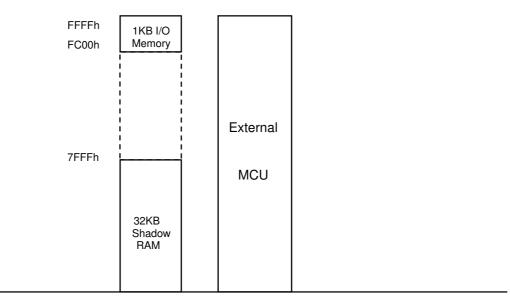

The PS1000 is an ASIC for the 1P3W (One-Phase, Three-Wire) Power Meter (Energy Meter) application. The PS1000 integrated all the function needs for energy meter application. The system architecture is shown in figure 1.

Figure 1. PS1000 System Architecture

PS1000 contains the following major subsystems

- 2 CH 16-bit ADC with AGC for current input(1x/2x/4x/8x)

- 1 CH 16-bit ADC for voltage input

- Built-in internal temperature sensor with 10-bit ADC

- Built-in 32-bit hardware DSP core (256x32 program space)

- 8032T high performance MCU

- 256B internal data memory space

- 16KB external data memory space

- 64KB program space

- Timer x 3 (including a Watch Dog Timer)

- UART x 3 (UART2/UART3 mapped to same timer)

- I2C interface

- TI DSP SSP interface

- SPI EEPROM interface

- 16 GPIO

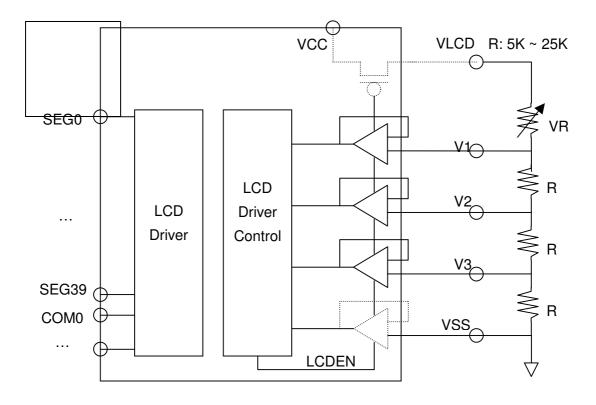

- 40x4 LCD Controller/Driver

- 1/4 LCD Bias

The detail description for each block is described in each section.

PS1000 has several different package types. For the detail pin assignment, please reference the Section 14. The detail PIN description is shown in below.

| Name   | Туре         | Description                  |

|--------|--------------|------------------------------|

| VCC3A  | Power (3.3V) | 3.3V Analog power supply     |

| VCCIO  | Power (3.3V) | 3.3V I/O Power supply        |

| VCCK   | Power(2.5V)  | 2.5V Core power              |

| VREG25 | 0            | Regulator 2.5V output        |

| VSSA   | Ground       | Analog Ground                |

| GND    | Ground       | I/O, Digital Ground          |

|        |              |                              |

| VCCRTC | Power(2.5V)  | RTC power supply (2.5V)      |

| RTCXI  | Ι            | RTC crystal input (32.768K)  |

| RTCXO  | 0            | RTC crystal output           |

| RTCGND | Ground       | RTC Crystal ground           |

| OSCVCC | Power(2.5V)  | Crystal power supply (2.5V)  |

| XTLI   | Ι            | System Crystal input (24MHz) |

| SPICSSPIC SSPICSOSPI CS control signal, active lowSOOSPI SO outputSIISPI SI inputFSXI/OSSP transmit draw signalDXI/OSSP transmit draw signalDXI/OSSP transmit and received clock. The maximum clock rate isSYSCLK/4OSSP receive data signalFSROSSP receive frame sync signalSCLI/OI2C clockSDAI/OI2C clockSDAI/OCurrent input(-)IAMIPhase B Current input(-)IAMIPhase A Current input(-)VAMIVoltage input(+)VCD2OLCD bias input 3CCD2OLCD bias input 3CCD3OLCD CoM output (maximum driving current 20uA)SEC0-39OLCD Segment output (maximum driving current 20uA)SEC0-39OLCD Segment output                                                                                                                                                                                                                                                                                                                                                                                                          | XTLO    | 0          | System Crystal output                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|------------------------------------------------------------------------|

| in master or slave mode, in the master mode, the maximum clock rate is<br>SYSCLK/4           SPICS         O         SPI SO output           SO         O         SPI SO output           SI         I         SPI SO output           SNELK/A         SSP transmit data signal         CLK           DX         I/O         SSP transmit data signal         CLK           CLK         O         SSP receive data signal         SSP scieve data signal           FSR         O         SSP receive frame sync signal         SSP cluck/A           SDA         I/O         I2C clock         SDA           SDA         I/O         I2C clock         SDA           VCM1         O         Current Phase A/B ADC reference output(VCC3A/2)         IIBM           I         Phase B Current input(+)         IAM         I         Phase A Current input(+)           IAM         I         Phase A Current input(+)         IAM         I         Voltage input(-)           VAM         I         Voltage input(-)         VAM         I         Voltage input(+)                           |         |            |                                                                        |

| SPICS       O       SPI CS control signal, active low         SO       O       SPI SO output         SI       I       SPI SI put         FSX       I/O       SSP transmit frame sync signal         DX       I/O       SSP transmit data signal         CLK       O       SSP Teck. (he transmit and received clock. The maximum clock rate is SYSCLK/4         DR       O       SSP receive data signal         FSR       O       SSP receive frame sync signal         CLL       I/O       12C clock         SDA       I/O       12C clock         VCM1       O       Current input(-)         VCM2       Voltage input(-)                                                                                                                                                                        | SCLK    | I/O        | in master or slave mode. In the master mode, the maximum clock rate is |

| SO       O       SPI SO output         SI       I       SPI SI input         SS       I/O       SSP transmit frame sync signal         DX       I/O       SSP transmit data signal         CLK       O       SSP CLK, the transmit and received clock. The maximum clock rate is SYSCLK/4         DR       O       SSP receive data signal         FSR       O       SSP receive data signal         SCL       I/O       I2C clock         SDA       I/O       I2C Address/Data         VCM1       O       Current Phase A/B ADC reference output(VCC3A/2)         IBM       I       Phase B Current input(-)         IBP       I       Phase A Current input(+)         IAM       I       Phase A Current input(-)         VAM       I       Voltage input(-)         VAM       I       Voltage input(-)         VCM2       O       Voltage input(-)         VCM2       O       Voltage input(-)         VCM2       O       Voltage input 2         V1       I       LCD bias input 1         V2       I       LCD bias input 2         V3       I       LCD bias input 3         COM3-0       LCD COM output (maximum d                                                                                                             |         |            |                                                                        |

| SI     I     SPI SI input       FSX     I/O     SSP transmit frame sync signal       DX     I/O     SSP transmit data signal       CLK     O     SSP transmit data signal       CLK     O     SSP receive data signal       FSR     O     SSP receive frame sync signal       FSR     O     SSP receive frame sync signal       SCL     I/O     I2C clock       SDA     I/O     I2C clock       SDA     I/O     I2C clock       SDA     I/O     Current Phase A/B ADC reference output(VCC3A/2)       IBM     I     Phase B Current input(-)       IBM     I     Phase B Current input(+)       IAM     I     Phase A Current input(-)       VAM     I     Voltage input(-)       VAM     I     Voltage input(-)       VAM     I     Voltage input(-)       VAP     O     LCD bias input 1       V1CD     O     LCD bias input 2       V2     I     LCD bias input 2       V3     I     LCD bias input 2       V3     I     LCD bias input 2       V3     I     CDS genent output (maximum driving current 20uA)       SEG0-39     O     LCD Segment output (maximum driving current 20uA)       SEG0-39                                                                                                                              |         |            |                                                                        |

| FSX         I/O         SSP transmit frame sync signal           DX         I/O         SSP transmit data signal           CLK         O         SSP CLK, the transmit and received clock. The maximum clock rate is SYSCLK/4           DR         O         SSP receive data signal           FSR         O         SSP receive frame sync signal           SCL         I/O         I2C clock           SDA         I/O         I2C Address/Data           VCM1         O         Current Phase A/B ADC reference output(VCC3A/2)           IBM         I         Phase B Current input(+)           IAP         I         Phase B Current input(+)           IAP         I         Phase A Current input(+)           IAM         I         Phase A Current input(-)           VAM         Voltage input(-)         VAM           VCM2         O         Voltage input(-)           VAP         I         Voltage input(-)           VAP         I         Voltage input(-)           VAM         I         Voltage input(-)           VAM         I         Voltage input(-)           VAM         I         Voltage input(-)           VCM2         O         LCD bias input 2                                                    |         | 0          |                                                                        |

| DX     I/O     SSP transmit data signal       CLK     O     SSP CLK, the transmit and received clock. The maximum clock rate is<br>SYSCLK/4       DR     O     SSP receive data signal       FSR     O     SSP receive frame sync signal       SCL     I/O     I2C clock       SDA     I/O     I2C clock       SDA     I/O     I2C clock       SDA     I/O     Current Phase A/B ADC reference output(VCC3A/2)       IBM     I     Phase B Current input(-)       IBM     I     Phase B Current input(-)       IAM     I     Phase A Current input(-)       VAM     I     Voltage input(-)       VAM     I     Voltage input(-)       VAP     I     Voltage input(-)       VAP     I     Voltage input(-)       VAP     I     Voltage input(-)       VAP     I     Voltage input(-)       VAM     I     Ucb bias input 1       VCD     C     LCD bias input 1       V2     I     LCD bias input 2       V3     I     LCD bias input 2       V3     I     LCD bias input 3       COM3-0     LCD COM output (maximum driving current 200A)       SEG0-39     O     LCD Segment output (maximum driving current 200A)                                                                                                                    | SI      | I          | SPI SI input                                                           |

| DX     I/O     SSP transmit data signal       CLK     O     SSP CLK, the transmit and received clock. The maximum clock rate is<br>SYSCLK/4       DR     O     SSP receive data signal       FSR     O     SSP receive frame sync signal       SCL     I/O     I2C clock       SDA     I/O     I2C clock       SDA     I/O     I2C clock       SDA     I/O     Current Phase A/B ADC reference output(VCC3A/2)       IBM     I     Phase B Current input(-)       IBM     I     Phase B Current input(-)       IAM     I     Phase A Current input(-)       VAM     I     Voltage input(-)       VAM     I     Voltage input(-)       VAP     I     Voltage input(-)       VAP     I     Voltage input(-)       VAP     I     Voltage input(-)       VAP     I     Voltage input(-)       VAM     I     Ucb bias input 1       VCD     C     LCD bias input 1       V2     I     LCD bias input 2       V3     I     LCD bias input 2       V3     I     LCD bias input 3       COM3-0     LCD COM output (maximum driving current 200A)       SEG0-39     O     LCD Segment output (maximum driving current 200A)                                                                                                                    | FSX     | 1/0        | SSP transmit frame sync signal                                         |

| CLK       O       SSP CLK, the transmit and received clock. The maximum clock rate is SYSCLK/4         DR       O       SSP receive data signal         FSR       O       SSP receive frame sync signal         SCL       I/O       I2C clock         SDA       I/O       I2C clock         SDA       I/O       I2C clock         SDA       I/O       Current Phase A/B ADC reference output(VCC3A/2)         IBM       I       Phase B Current input(-)         IBP       I       Phase A Current input(-)         IAM       I       Phase A Current input(-)         VAM       I       Voltage input(-)         VAM       I       Voltage input(-)         VAP       Voltage input(-)       VAP         VLCD       O       Voltage input(-)         VLCD       O       LCD bias input 1         V2       I       LCD bias input 3         COM3-0       LCD COM output (maximum driving current 200uA)         SEG0-39       O       LCD Segment output (maximum driving current 200uA)         SEG1-39       O       LCD Segment output (maximum driving current 200uA)         SEG0-39       O       LCD Segment output (maximum driving current 200uA)         SEG1-39 <t< td=""><td></td><td></td><td></td></t<>                 |         |            |                                                                        |

| DR       O       SSP receive data signal         FSR       O       SSP receive frame sync signal         SCL       I/O       I2C clock         SDA       I/O       I2C Address/Data         VCM1       O       Current Phase A/B ADC reference output(VCC3A/2)         IBM       I       Phase B Current input(-)         IBP       I       Phase A Current input(+)         IAP       I       Phase A Current input(-)         VAM       I       Voltage input(-)         VAM       I       Voltage input(-)         VAP       I       Voltage input(-)         VAP       I       Voltage input(-)         VLCD       O       LCD bias input 1         V1       I       LCD bias input 2         V2       I       LCD bias input 3         COM3-0       O       LCD Segment output (maximum driving current 200uA)         SEG0-39       O       LCD Segment output (maximum driving current 200uA)         SEG0-39       O       LCD Segment output (maximum driving current 200uA)         CEXternal ROM       0: External ROM         0: External ROM       0: External ROM         0: External S1 Mode (1)       001 ICP Mode         010                                                                                        |         |            | SSP CLK, the transmit and received clock. The maximum clock rate is    |

| FSR       O       SSP receive frame sync signal         SCL       I/O       I2C clock         SDA       I/O       I2C Address/Data         VCM1       O       Current Phase A/B ADC reference output(VCC3A/2)         IBM       I       Phase B Current input(-)         IBP       I       Phase A Current input(-)         IAP       I       Phase A Current input(-)         VAM       I       Voltage input(-)         VCM2       O       Voltage input(-)         VCM2       O       Voltage input(-)         VCM2       O       Voltage input(-)         VCM2       O       Voltage input -)         VCM2       O       LCD bias input 1         V2       I       LCD bias input 1         V2       I       LCD bias input 2         V3       I       LCD Segment output (maximum driving current 200A)         SEG0-39       O       LCD Segment output (maximum driving current 20uA)         EA       I       8051 MCU EA                                                                                                                     | DR      | 0          |                                                                        |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         | -          |                                                                        |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |                                                                        |

| VCM1OCurrent Phase A/B ADC reference output(VCC3A/2)IBMIPhase B Current input(-)IBPIPhase B Current input(+)IAPIPhase A Current input(-)VAMIVoltage input(-)VAMIVoltage input(-)VAPIVoltage input(-)VCD2OVoltage ADC reference output(VCC3A/2)VLCDOLCD bias input 1V2ILCD bias input 2V2ILCD bias input 3COM3-0OLCD COM output (maximum driving current 200uA)SEG0-39OLCD Segment output (maximum driving current 20uA)RSTIChip Reset, active highEAI8051 MCU EA control signal1: Internal ROM0: External ROMPSENI/O8051 PSEN control signalMODE2-0IOperation Mode selection000Normal Operation (1)001ICP Mode010Kexternal S1 Mode (1)011Normal Operation (2)100Memory Test Mode (2)111Memory BIST Mode (Reserved)111Memory BIST PO I/O port bit 0 (mapped to the AD1)P0.4I/O8051 PO I/O port bit 3 (mapped to the AD1)P0.4I/O8051 PO                                                                                                                                                                                                             | SCL     | I/O        | I2C clock                                                              |

| IBM       I       Phase B Current input(-)         IBP       I       Phase A Current input(+)         IAP       I       Phase A Current input(-)         VAM       I       Phase A Current input(-)         VAM       I       Voltage input(-)         VAP       I       Voltage input(-)         VAP       I       Voltage input(-)         VCD2       O       Voltage input(-)         VLCD       O       LCD bias input 1         VLCD       I       LCD bias input 2         V2       I       LCD bias input 3         COM3-0       O       LCD COM output (maximum driving current 200uA)         SEG0-39       O       LCD Segment output (maximum driving current 20uA)         RST       I       Chip Reset, active high         EA       I       8051 MCU EA control signal         1: Internal ROM       0: External ROM         0: External ROM       0: External ROM         0: EXternal S1 Mode (1)       001 ICP Mode         010       Normal Operation (1)         001       Normal Operation (2)         100       Momeny Test Mode (10)         011       Normal S1 Mode (2)         110       Analog Test Mode (Reserved)<                                                                                         | SDA     | I/O        | I2C Address/Data                                                       |

| IBM       I       Phase B Current input(-)         IBP       I       Phase A Current input(+)         IAP       I       Phase A Current input(-)         VAM       I       Phase A Current input(-)         VAM       I       Voltage input(-)         VAP       I       Voltage input(-)         VAP       I       Voltage input(-)         VCD2       O       Voltage input(-)         VLCD       O       LCD bias input 1         VLCD       I       LCD bias input 2         V2       I       LCD bias input 3         COM3-0       O       LCD COM output (maximum driving current 200uA)         SEG0-39       O       LCD Segment output (maximum driving current 20uA)         RST       I       Chip Reset, active high         EA       I       8051 MCU EA control signal         1: Internal ROM       0: External ROM         0: External ROM       0: External ROM         0: EXternal S1 Mode (1)       001 ICP Mode         010       Normal Operation (1)         001       Normal Operation (2)         100       Momeny Test Mode (10)         011       Normal S1 Mode (2)         110       Analog Test Mode (Reserved)<                                                                                         |         |            |                                                                        |

| IBPIPhase B Current input(+)IAPIPhase A Current input(+)IAMIPhase A Current input(-)VAMIVoltage input(-)VAPIVoltage input(-)VAPIVoltage input(-)VCM2OVoltage aDC reference output(VCC3A/2)VLCDOLCD bias power supply outputV1ILCD bias input 1V2ILCD bias input 2V3ILCD bias input 3COM3-0OLCD COM output (maximum driving current 200A)SEG0-39OLCD Segment output (maximum driving current 20uA)EAI8051 MCU EA control signal<br>1 : Internal ROM<br>0: External ROM<br>0: External ROM<br>000 Normal Operation (1)<br>0001 ICP ModeMODE2-0IOperation Mode selection<br>000 Normal Operation (1)<br>001 ICP Mode<br>101 External 51 Mode (2)<br>110 Analog Test Mode<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         | 0          |                                                                        |

| IAPIPhase A Current input(+)IAMIPhase A Current input(-)VAMIVoltage input(-)VAPIVoltage input(+)VCM2OVoltage ADC reference output(VCC3A/2)VLCDOLCD bias input 1V2ILCD bias input 2V3ILCD bias input 3COM3-0OLCD COM output (maximum driving current 200uA)SEG0-39OLCD Segment output (maximum driving current 200uA)SEG0-39OLCD Segment output (maximum driving current 200uA)RSTIChip Reset, active highEAI8051 MCU EA control signal<br>1 : Internal ROM<br>0: External ROMMODE2-0IOperation Mode selection<br>000 Normal Operation (1)<br>001 ICP Mode<br>101 External 51 Mode (1)<br>101 Normal Operation (2)<br>100 Memory Test Mode<br>101 External 51 Mode (2)<br>110 Analog Test Mode (Reserved)P0.0I/O8051 P0 I/O port bit 0 (mapped to the AD0)<br>P0.1P0.2I/O8051 P0 I/O port bit 2 (mapped to the AD1)<br>P0.2P0.4I/O8051 P0 I/O port bit 3 (mapped to the AD3)<br>P0.4P0.4I/O8051 P0 I/O port bit 3 (mapped to the AD4)                                                                                                                                                                                                                                                                                                  |         | I          |                                                                        |

| IAM       I       Phase A Current input(-)         VAM       I       Voltage input(-)         VAP       I       Voltage input(+)         VCM2       O       Voltage ADC reference output(VCC3A/2)         VLCD       O       LCD bias power supply output         V1       I       LCD bias input 1         V2       I       LCD bias input 3         COM3-0       O       LCD COM output (maximum driving current 200uA)         SEG0-39       O       LCD Segment output (maximum driving current 20uA)         SEG0-39       O       LCD Segment output (maximum driving current 20uA)         RST       I       Chip Reset, active high         EA       I       8051 MCU EA control signal         1: Internal ROM       0: External ROM         0: External ROM       0: External Signal         MODE2-0       I       Operation Mode selection         000       Normal Operation (1)       001 ICP Mode         010       External 51 Mode (1)       101 External 51 Mode (2)         100       Monalog Test Mode (Reserved)       111 Memory BIST Mode (Reserved)         111       Memory BIST Mode (Reserved)       111 Memory BIST Mode (Reserved)         111       Memory BIST Mode (Reserved)       111 Memo           |         | Ι          |                                                                        |

| VAM       I       Voltage input(-)         VAP       I       Voltage input(+)         VCM2       O       Voltage ADC reference output(VCC3A/2)         VLCD       O       LCD bias power supply output         V1       I       LCD bias input 1         V2       I       LCD bias input 3         COM3~0       O       LCD COM output (maximum driving current 200uA)         SEG0~39       O       LCD Segment output (maximum driving current 20uA)         RST       I       Chip Reset, active high         EA       I       8051 MCU EA control signal         1: Internal ROM       0: External ROM         0: External ROM       0: External ROM         000       Normal Operation (1)         001       ICP Mode         010       External 51 Mode (1)         011       Normal Operation (2)         100       Memory Test Mode         101       External 51 Mode (2)         110       Analog Test Mode (Reserved)         111       Memory BIST                                                                                |         | Ι          | /                                                                      |

| VAPIVoltage input(+)VCM2OVoltage ADC reference output(VCC3A/2)VLCDOLCD bias power supply outputV1ILCD bias input 1V2ILCD bias input 2V3ILCD COM output (maximum driving current 200uA)SEG0-39OLCD CoM output (maximum driving current 200uA)SEG0-39OLCD Segment output (maximum driving current 200uA)RSTIChip Reset, active highEAI8051 MCU EA control signal<br>1: Internal ROM<br>0: External ROM<br>0: External ROMPSENI/O8051 PSEN control pinALEI/O8051 ALE control signalMODE2-0IOperation Mode selection<br>000 Normal Operation (1)<br>001 ICP Mode<br>010 External 51 Mode (1)<br>011 Normal Operation (2)<br>100 Memory Test Mode<br>101 External 51 Mode (2)<br>110 Analog Test Mode (Reserved)<br>111 Memory BIST Mode (Reserved)P0.0I/O8051 P0 I/O port bit 0 (mapped to the AD0)<br>P0.1P0.2I/O8051 P0 I/O port bit 1 (mapped to the AD1)<br>P0.3P0.4I/O8051 P0 I/O port bit 4 (mapped to the AD4)                                                                                                                                                                                                                                                                                                                     |         | Ι          |                                                                        |

| VCM2       O       Voltage ADC reference output(VCC3A/2)         VLCD       O       LCD bias power supply output         V1       I       LCD bias input 1         V2       I       LCD bias input 2         V3       I       LCD bias input 3         COM3~0       O       LCD COM output (maximum driving current 200uA)         SEG0~39       O       LCD Segment output (maximum driving current 20uA)         RST       I       Chip Reset, active high         EA       I       8051 MCU EA control signal         1:       Internal ROM       0: External ROM         0:       External ROM       0: External ROM         0:       External ROM       0: External ROM         0:       B051 PSEN control signal       1         MODE2-0       I       Operation Mode selection         000       Normal Operation (1)       001       100         010       External 51 Mode (1)       011       101         011       Normal Operation (2)       100       Memory Test Mode         101       External 51 Mode (2)       110       Analog Test Mode (Reserved)         111       Memory BIST Mode (Reserved)       111       Memory BIST Mode (Reserved)         101 </td <td></td> <td>Ι</td> <td>0 1 ()</td>                |         | Ι          | 0 1 ()                                                                 |

| VLCD       O       LCD bias power supply output         V1       I       LCD bias input 1         V2       I       LCD bias input 2         V3       I       LCD COM output (maximum driving current 200uA)         SEG0-39       O       LCD Segment output (maximum driving current 20uA)         RST       I       Chip Reset, active high         EA       I       8051 MCU EA control signal         1: Internal ROM       0: External ROM         0: External ROM       0: External ROM         0: External ROM       00: Normal Operation (1)         000       Normal Operation (1)         001       ICP Mode         010       External 51 Mode (1)         011       Normal Operation (2)         100       Memory Test Mode         101       External 51 Mode (2)         111       Memory BIST Mode (Reserved)         111       Memory BIST Mode (Reserved)         111       Memory BIST PO I/O port bit 0 (mapped to the AD0)         P0.0       I/O       8051 PO I/O port bit 3 (mapped to the AD1)         P0.2       I/O       8051 PO I/O port bit 3 (mapped to the AD2)         P0.4       I/O       8051 PO I/O port bit 4 (mapped to the AD4)                                                                |         | Ι          |                                                                        |

| V1       I       LCD bias input 1         V2       I       LCD bias input 2         V3       I       LCD bias input 3         COM3~0       O       LCD COM output (maximum driving current 200uA)         SEG0~39       O       LCD Segment output (maximum driving current 20uA)         SEG0~39       O       LCD Segment output (maximum driving current 20uA)         RST       I       Chip Reset, active high         EA       I       8051 MCU EA control signal         1:       Internal ROM       0: External ROM         PSEN       I/O       8051 PSEN control pin         ALE       I/O       8051 ALE control signal         MODE2-0       I       Operation Mode selection         000       Normal Operation (1)       001         010       External 51 Mode (1)       011         011       Normal Operation (2)       100         100       Memory Test Mode       101         101       External 51 Mode (2)       110         111       Memory BIST Mode (Reserved)       111         111       Memory BIST Mode (Reserved)       111         111       Memory BIST PO I/O port bit 0 (mapped to the AD0)       P0.1         P0.1       I/O                                                                      | VCM2    | 0          | Voltage ADC reference output(VCC3A/2)                                  |

| V1       I       LCD bias input 1         V2       I       LCD bias input 2         V3       I       LCD bias input 3         COM3~0       O       LCD COM output (maximum driving current 200uA)         SEG0~39       O       LCD Segment output (maximum driving current 20uA)         SEG0~39       O       LCD Segment output (maximum driving current 20uA)         RST       I       Chip Reset, active high         EA       I       8051 MCU EA control signal         1:       Internal ROM       0: External ROM         PSEN       I/O       8051 PSEN control pin         ALE       I/O       8051 ALE control signal         MODE2-0       I       Operation Mode selection         000       Normal Operation (1)       001         010       External 51 Mode (1)       011         011       Normal Operation (2)       100         100       Memory Test Mode       101         101       External 51 Mode (2)       110         111       Memory BIST Mode (Reserved)       111         111       Memory BIST Mode (Reserved)       111         111       Memory BIST PO I/O port bit 0 (mapped to the AD0)       P0.1         P0.1       I/O                                                                      | VICD    | 0          | I CD bias power supply output                                          |

| V2       I       LCD bias input 2         V3       I       LCD bias input 3         COM3~0       O       LCD COM output (maximum driving current 2004A)         SEG0~39       O       LCD Segment output (maximum driving current 20uA)         RST       I       Chip Reset, active high         EA       I       8051 MCU EA control signal         1: Internal ROM       0: External ROM         0: External ROM       0: External ROM         MODE2-0       I       Operation Mode selection         000       Normal Operation (1)       001 ICP Mode         010       External 51 Mode (1)         011       Normal Operation (2)         100       Memory Test Mode         101       External 51 Mode (2)         110       Analog Test Mode (Reserved)         111       Memory BIST Mode (Reserved)         111       Memory BIST Mode (Reserved)         111       Memory BIST Mode (Teserved)         111       Memory BIST PO I/O port bit 0 (mapped to the AD0)         P0.0       I/O       8051 P0 I/O port bit 3 (mapped to the AD1)         P0.2       I/O       8051 P0 I/O port bit 3 (mapped to the AD3)         P0.4       I/O       8051 P0 I/O port bit 4 (mapped to the AD4) <td></td> <td>-</td> <td></td> |         | -          |                                                                        |

| V3       I       LCD bias input 3         COM3~0       O       LCD COM output (maximum driving current 200A)         SEG0~39       O       LCD Segment output (maximum driving current 20uA)         RST       I       Chip Reset, active high         EA       I       8051 MCU EA control signal         1: Internal ROM       0: External ROM         0: External ROM       0: External ROM         MODE2-0       I       Operation Mode selection         000       Normal Operation (1)       001 ICP Mode         010       External 51 Mode (1)       011 Normal Operation (2)         100       Memory Test Mode       101         111       Memory Test Mode       111         102       K051 P0 I/O port bit 0 (mapped to the AD0)       111         113       Memory BIST Mode (Reserved)       111         114       Memory BIST P0 I/O port bit 1 (mapped to the AD1)       111         115       P0.1       I/O       8051 P0 I/O port bit 2 (mapped to the AD1)         114       I/O       8051 P0 I/O port bit 3 (mapped to the AD3)         115       P0.4       I/O       8051 P0 I/O port bit 4 (mapped to the AD4)                                                                                               |         | 1<br>T     |                                                                        |

| COM3-0       O       LCD COM output (maximum driving current 200uA)         SEG0~39       O       LCD Segment output (maximum driving current 20uA)         RST       I       Chip Reset, active high         EA       I       8051 MCU EA control signal         1: Internal ROM       0: External ROM         PSEN       I/O       8051 PSEN control pin         ALE       I/O       8051 ALE control signal         MODE2-0       I       Operation Mode selection         000       Normal Operation (1)         001       ICP Mode         010       External 51 Mode (1)         011       Normal Operation (2)         100       Memory Test Mode         101       External 51 Mode (2)         110       Analog Test Mode (Reserved)         111       Memory BIST PO I/O port bit 0 (mapped to the AD0)         P0.0       I/O       8051 PO I/O port bit 2 (mapped to the AD1)         P0.2       I/O       8051 PO I/O port bit 3 (mapped to the AD2)         P0.3       I/O       805                                            |         | I          |                                                                        |

| SEG0~39       O       LCD Segment output (maximum driving current 20uA)         RST       I       Chip Reset, active high         EA       I       8051 MCU EA control signal         1: Internal ROM       0: External ROM         PSEN       I/O       8051 PSEN control pin         ALE       I/O       8051 ALE control signal         MODE2-0       I       Operation Mode selection         000       Normal Operation (1)         001       ICP Mode         010       External 51 Mode (1)         011       Normal Operation (2)         100       Memory Test Mode         111       Memory BIST Mode (Reserved)         111       Memory BIST Mode (Reserved)         111       Memory BIST Mode to the AD0)         P0.0       I/O       8051 P0 I/O port bit 0 (mapped to the AD1)         P0.2       I/O       8051 P0 I/O port bit 3 (mapped to the AD2)         P0.3       I/O       8051 P0 I/O port bit 3 (mapped to the AD3)         P0.4       I/O       8051 P0 I/O port bit 4 (mapped to the AD4)                                                                                                                                                                                                               |         |            | 1                                                                      |

| EAI8051 MCU EA control signal<br>1: Internal ROM<br>0: External ROMPSENI/O8051 PSEN control pinALEI/O8051 ALE control signalMODE2-0IOperation Mode selection<br>000 Normal Operation (1)<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         | -          |                                                                        |

| EAI8051 MCU EA control signal<br>1: Internal ROM<br>0: External ROMPSENI/O8051 PSEN control pinALEI/O8051 ALE control signalMODE2-0IOperation Mode selection<br>000 Normal Operation (1)<br>001 ICP Mode<br>010 External 51 Mode (1)<br>011 Normal Operation (2)<br>100 Memory Test Mode<br>101 External 51 Mode (2)<br>110 Analog Test Mode (Reserved)<br>111 Memory BIST Mode (Reserved)P0.0I/O8051 P0 I/O port bit 0 (mapped to the AD0)<br>P0.1P0.2I/O8051 P0 I/O port bit 2 (mapped to the AD1)<br>P0.3P0.4I/O8051 P0 I/O port bit 3 (mapped to the AD4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |                                                                        |

| 1: Internal ROM<br>0: External ROMPSENI/O8051 PSEN control pinALEI/O8051 ALE control signalMODE2-0IOperation Mode selection<br>000 Normal Operation (1)<br>001 ICP Mode<br>010 External 51 Mode (1)<br>011 Normal Operation (2)<br>100 Memory Test Mode<br>101 External 51 Mode (2)<br>110 Analog Test Mode (Reserved)<br>111 Memory BIST Mode (Reserved)P0.0I/O8051 P0 I/O port bit 0 (mapped to the AD0)<br>P0.1P0.2I/O8051 P0 I/O port bit 2 (mapped to the AD2)<br>P0.3P0.4I/O8051 P0 I/O port bit 3 (mapped to the AD4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RST     | Ι          |                                                                        |

| 0: External ROMPSENI/O8051 PSEN control pinALEI/O8051 ALE control signalMODE2-0IOperation Mode selection<br>000 Normal Operation (1)<br>001 ICP Mode<br>010 External 51 Mode (1)<br>011 Normal Operation (2)<br>100 Memory Test Mode<br>101 External 51 Mode (2)<br>110 Analog Test Mode (Reserved)<br>111 Memory BIST Mode (Reserved)P0.0I/O8051 P0 I/O port bit 0 (mapped to the AD0)<br>P0.1P0.2I/O8051 P0 I/O port bit 2 (mapped to the AD2)<br>P0.3P0.4I/O8051 P0 I/O port bit 4 (mapped to the AD4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | EA      | Ι          | 8051 MCU EA control signal                                             |

| PSENI/O8051 PSEN control pinALEI/O8051 ALE control signalMODE2-0IOperation Mode selection<br>000 Normal Operation (1)<br>001 ICP Mode<br>010 External 51 Mode (1)<br>011 Normal Operation (2)<br>100 Memory Test Mode<br>101 External 51 Mode (2)<br>110 Analog Test Mode (Reserved)<br>111 Memory BIST Mode (Reserved)P0.0I/O8051 P0 I/O port bit 0 (mapped to the AD0)<br>P0.1P0.2I/O8051 P0 I/O port bit 2 (mapped to the AD2)<br>P0.3P0.4I/O8051 P0 I/O port bit 3 (mapped to the AD4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |                                                                        |

| ALEI/O8051 ALE control signalMODE2-0IOperation Mode selection<br>000 Normal Operation (1)<br>001 ICP Mode<br>010 External 51 Mode (1)<br>011 Normal Operation (2)<br>100 Memory Test Mode<br>101 External 51 Mode (2)<br>110 Analog Test Mode (Reserved)<br>111 Memory BIST Mode (Reserved)P0.0I/O8051 P0 I/O port bit 0 (mapped to the AD0)<br>P0.1P0.2I/O8051 P0 I/O port bit 2 (mapped to the AD1)<br>P0.3P0.4I/O8051 P0 I/O port bit 3 (mapped to the AD4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |                                                                        |

| MODE2-0IOperation Mode selection<br>000000Normal Operation (1)<br>001ICP Mode<br>010010External 51 Mode (1)<br>011011Normal Operation (2)<br>100100Memory Test Mode<br>101101External 51 Mode (2)<br>110110Analog Test Mode (Reserved)<br>111111Memory BIST Mode (Reserved)P0.0I/O8051 P0 I/O port bit 0 (mapped to the AD0)<br>P0.1P0.2I/OP0.3I/O8051 P0 I/O port bit 3 (mapped to the AD3)<br>P0.4P0.4I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            | *                                                                      |

| 000Normal Operation (1)001ICP Mode010External 51 Mode (1)011Normal Operation (2)100Memory Test Mode101External 51 Mode (2)110Analog Test Mode (Reserved)111Memory BIST Mode (Reserved)111Memory BIST Mode (Reserved)P0.0I/O8051 P0 I/O port bit 0 (mapped to the AD0)P0.1I/O8051 P0 I/O port bit 1 (mapped to the AD1)P0.2I/O8051 P0 I/O port bit 2 (mapped to the AD2)P0.3I/O8051 P0 I/O port bit 3 (mapped to the AD3)P0.4I/O8051 P0 I/O port bit 4 (mapped to the AD4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         | I/O        |                                                                        |

| 001ICP Mode010External 51 Mode (1)011Normal Operation (2)100Memory Test Mode101External 51 Mode (2)110Analog Test Mode (Reserved)111Memory BIST Mode (Reserved)111Memory BIST Mode (Reserved)P0.0I/O8051 P0 I/O port bit 0 (mapped to the AD0)P0.1I/O8051 P0 I/O port bit 1 (mapped to the AD1)P0.2I/O8051 P0 I/O port bit 2 (mapped to the AD2)P0.3I/O8051 P0 I/O port bit 3 (mapped to the AD3)P0.4I/O8051 P0 I/O port bit 4 (mapped to the AD4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | MODE2-0 | Ι          | -                                                                      |

| 010External 51 Mode (1)011Normal Operation (2)100Memory Test Mode101External 51 Mode (2)110Analog Test Mode (Reserved)111Memory BIST Mode (Reserved)111Memory BIST Mode (Reserved)P0.0I/O8051 P0 I/O port bit 0 (mapped to the AD0)P0.1I/O8051 P0 I/O port bit 1 (mapped to the AD1)P0.2I/O8051 P0 I/O port bit 2 (mapped to the AD2)P0.3I/O8051 P0 I/O port bit 3 (mapped to the AD3)P0.4I/O8051 P0 I/O port bit 4 (mapped to the AD4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |                                                                        |

| 011Normal Operation (2)100Memory Test Mode101External 51 Mode (2)110Analog Test Mode (Reserved)111Memory BIST Mode (Reserved)111Memory BIST Mode (Reserved)P0.0I/O8051 P0 I/O port bit 0 (mapped to the AD0)P0.1I/O8051 P0 I/O port bit 1 (mapped to the AD1)P0.2I/O8051 P0 I/O port bit 2 (mapped to the AD2)P0.3I/O8051 P0 I/O port bit 3 (mapped to the AD3)P0.4I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |                                                                        |

| 100Memory Test Mode101External 51 Mode (2)110Analog Test Mode (Reserved)111Memory BIST Mode (Reserved)111Memory BIST Mode (Reserved)P0.0I/O8051 P0 I/O port bit 0 (mapped to the AD0)P0.1I/O8051 P0 I/O port bit 1 (mapped to the AD1)P0.2I/O8051 P0 I/O port bit 2 (mapped to the AD2)P0.3I/O8051 P0 I/O port bit 3 (mapped to the AD3)P0.4I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |                                                                        |

| 101External 51 Mode (2)110Analog Test Mode (Reserved)111Memory BIST Mode (Reserved)P0.0I/O8051 P0 I/O port bit 0 (mapped to the AD0)P0.1I/O8051 P0 I/O port bit 1 (mapped to the AD1)P0.2I/O8051 P0 I/O port bit 2 (mapped to the AD2)P0.3I/O8051 P0 I/O port bit 3 (mapped to the AD3)P0.4I/O8051 P0 I/O port bit 4 (mapped to the AD4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |                                                                        |

| 110Analog Test Mode (Reserved)<br>111111Memory BIST Mode (Reserved)P0.0I/O8051 P0 I/O port bit 0 (mapped to the AD0)P0.1I/O8051 P0 I/O port bit 1 (mapped to the AD1)P0.2I/O8051 P0 I/O port bit 2 (mapped to the AD2)P0.3I/O8051 P0 I/O port bit 3 (mapped to the AD3)P0.4I/O8051 P0 I/O port bit 4 (mapped to the AD4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |                                                                        |

| III         Memory BIST Mode (Reserved)           P0.0         I/O         8051 P0 I/O port bit 0 (mapped to the AD0)           P0.1         I/O         8051 P0 I/O port bit 1 (mapped to the AD1)           P0.2         I/O         8051 P0 I/O port bit 2 (mapped to the AD2)           P0.3         I/O         8051 P0 I/O port bit 3 (mapped to the AD3)           P0.4         I/O         8051 P0 I/O port bit 4 (mapped to the AD4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |                                                                        |

| P0.0         I/O         8051 P0 I/O port bit 0 (mapped to the AD0)           P0.1         I/O         8051 P0 I/O port bit 1 (mapped to the AD1)           P0.2         I/O         8051 P0 I/O port bit 2 (mapped to the AD2)           P0.3         I/O         8051 P0 I/O port bit 3 (mapped to the AD3)           P0.4         I/O         8051 P0 I/O port bit 4 (mapped to the AD4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |                                                                        |

| P0.1         I/O         8051 P0 I/O port bit 1 (mapped to the AD1)           P0.2         I/O         8051 P0 I/O port bit 2 (mapped to the AD2)           P0.3         I/O         8051 P0 I/O port bit 3 (mapped to the AD3)           P0.4         I/O         8051 P0 I/O port bit 4 (mapped to the AD4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            | 111 Memory BIS1 Mode (Reserved)                                        |

| P0.1         I/O         8051 P0 I/O port bit 1 (mapped to the AD1)           P0.2         I/O         8051 P0 I/O port bit 2 (mapped to the AD2)           P0.3         I/O         8051 P0 I/O port bit 3 (mapped to the AD3)           P0.4         I/O         8051 P0 I/O port bit 4 (mapped to the AD4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | P0.0    | I/O        | 8051 P0 I/O port bit 0 (mapped to the AD0)                             |

| P0.2         I/O         8051 P0 I/O port bit 2 (mapped to the AD2)           P0.3         I/O         8051 P0 I/O port bit 3 (mapped to the AD3)           P0.4         I/O         8051 P0 I/O port bit 4 (mapped to the AD4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |                                                                        |

| P0.3         I/O         8051 P0 I/O port bit 3 (mapped to the AD3)           P0.4         I/O         8051 P0 I/O port bit 4 (mapped to the AD4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |                                                                        |

| P0.4 I/O 8051 P0 I/O port bit 4 (mapped to the AD4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | P0.5    | I/O<br>I/O | 8051 P0 I/O port bit 5 (mapped to the AD5)                             |

Arch Meter Corporation

| P0.6           | I/O | 8051 P0 I/O port bit 6 (mapped to the AD6)                   |

|----------------|-----|--------------------------------------------------------------|

| P0.7           | I/O | 8051 P0 I/O port bit 7 (mapped to the AD7)                   |

| P1.0(optional) | I/O | 8051 P1 I/O port bit 0 (mapped to T2 interrupt input)        |

| P1.1           | I/O | 8051 P1 I/O port bit 1 (mapped to T2EX interrupt input)      |

| P1.2           | I/O | 8051 P1 I/O port bit 2 (mapped to RS-232 RxD1)               |

| P1.3           | I/O | 8051 P1 I/O port bit 3 (mapped to RS-232 TxD1)               |

| P1.4           | I/O | 8051 P1 I/O port bit 4 (mapped to RS-232 RxD2)               |

| P1.5           | I/O | 8051 P1 I/O port bit 5 (mapped to RS-232 TxD2)               |

| P1.6           | I/O | 8051 P1 I/O port bit 6 (mapped to ExtInt0 interrupt)         |

| P1.7           | I/O | 8051 P1 I/O port bit 7 (mapped to ExtInt1 interrupt)         |

| P2.0           | I/O | 8051 P2 I/O port bit 0 (mapped to the A8)                    |

| P2.1           | I/O | 8051 P2 I/O port bit 1 (mapped to the A9)                    |

| P2.2           | I/O | 8051 P2 I/O port bit 2 (mapped to the A10)                   |

| P2.3           | I/O | 8051 P2 I/O port bit 3 (mapped to the A11)                   |

| P2.4           | I/O | 8051 P2 I/O port bit 4 (mapped to the A12)                   |

| P2.5           | I/O | 8051 P2 I/O port bit 5 (mapped to the A13)                   |

| P2.6           | I/O | 8051 P2 I/O port bit 6 (mapped to the A14)                   |

| P2.7           | I/O | 8051 P2 I/O port bit 7 (mapped to the A15)                   |

| P3.0           | I/O | 8051 P3 I/O port bit 0 (mapped to RS-232 RxD0)               |

| P3.1           | I/O | 8051 P3 I/O port bit 1 (mapped to RS-232 TxD2)               |

| P3.2           | I/O | 8051 P3 I/O port bit 2 (mapped to INT0 interrupt input)      |

| P3.3           | I/O | 8051 P3 I/O port bit 3 (mapped to INT1 interrupt input)      |

| P3.4(optional) | I/O | 8051 P3 I/O port bit 4 (mapped to T0 interrupt input)        |

| P3.5(optional) | I/O | 8051 P3 I/O port bit 5 (mapped to T1 interrupt input)        |

| P3.6           | I/O | 8051 P3 I/O port bit 6 (mapped to memory WR_ control signal) |

| P3.7           | I/O | 8051 P3 I/O port bit 7 (mapped to memory RD_ control signal) |

# 2. Mode Control

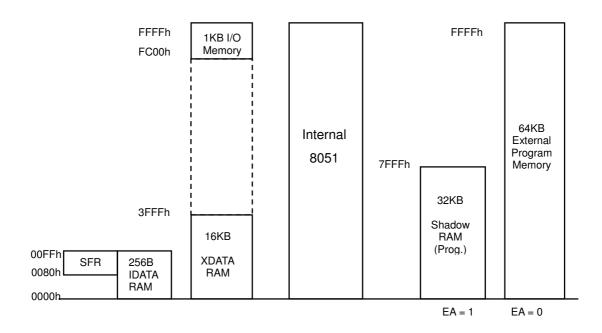

The PS1000 has several modes for different operation. The mode is controlled by the MODE and EA setting. Here is the configuration list.

| Mode | EA | MCU      | ROM             | RAM                         | Notes              |

|------|----|----------|-----------------|-----------------------------|--------------------|

| 000  | 0  | Internal | External Flash  | XDATA+ I/O Memory           | Normal Operation 1 |

| 000  | 1  | Internal | Shadow RAM      | XDATA+ I/O Memory           | Normal Operation 1 |

|      |    |          | (Power On)      |                             |                    |

| 001  | 0  | Internal | External Flash  | Shadow RAM + I/O Memory     | ICP Mode           |

| 001  | 1  | Internal | Internal 2K ROM | Shadow RAM + I/O Memory     | ICP Mode           |

| 010  | х  | External |                 | Shadow RAM + I/O Memory     | External 51 Mode 1 |

| 011  | 0  | Internal | External Flash  | XDATA+ I/O Memory           | Normal Operation 2 |

| 011  | 1  | Internal | Shadow RAM      | XDATA+ I/O Memory           | Normal Operation 2 |

| 100  | х  | External |                 | Shadow + XData + I/O Memory | Memory Test Mode   |

| 101  | Х  | External |                 | I/O Memory                  | External 51 Mode 2 |

| 110  | 0  | Non      |                 |                             | Analog Test Mode 1 |

| 110  | 1  | Non      |                 |                             | Analog Test Mode 2 |

| 111  | Х  | Non      |                 |                             | Memory BIST        |

For the detail description for each mode, please reference the section 7 MCU.

# 3. Clock Setting

The operation frequency of some PS1000 internal function blocks, like the ADC, MCU, DSP and LCD can be adjusted depends on operation condition. It can be configured with some internal register. The next section will describe how to program these registers. When change these registers setting, please make sure that is matched with the system requirement.

### 3.1 MCU Clock Setting

The PS1000 can set the different MCU operation clock during the different operation condition. It also can help to save the power.

| MCUCFG (0xFE29)                       |                                                                                 |  |  |  |  |  |  |  |

|---------------------------------------|---------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| B7                                    | B7         B6         B5         B4         B3         B2         B1         B0 |  |  |  |  |  |  |  |

| PORTCFG DSPTM[1:0] DSPROM MCUDIV[3:0] |                                                                                 |  |  |  |  |  |  |  |

PORTCFG

- 0: P0/P2 normal operation

- 1: P0/P2 mapped to the P4/P5

DSPTM [1:0]

- 00: DSP normal operation

- 01: DSP Test Mode 1 (reserved)

- 10: DSP Test Mode 2 (reserved)

- 11: DSP Test Mode 3 (reserved)

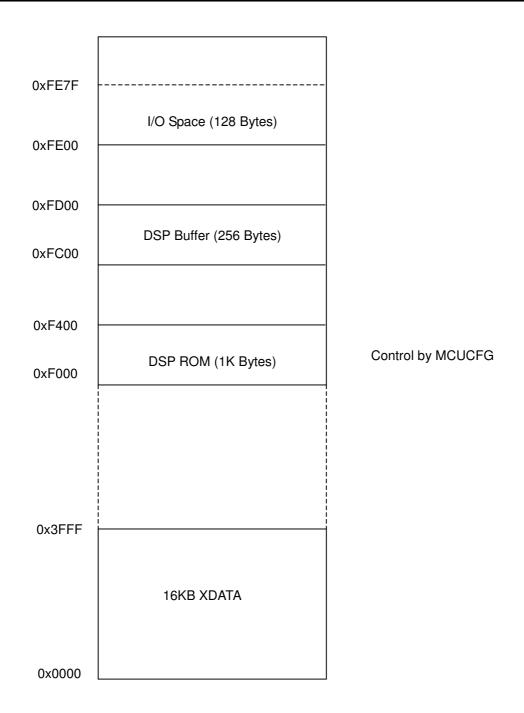

#### DSPROM:

- 0: DSP Normal operation

- 1: Mapping DSPROM to the I/O memory space (0xF000 ~ 0xF3FF, 1KB)

| MCUDIV[3:0] |        | 22MHz | 24MHz |

|-------------|--------|-------|-------|

| 0000        | SCLK/1 | 22.00 | 24.00 |

| 0001        | SCLK/2 | 11.00 | 12.00 |

| 0010        | SCLK/3 | 7.33  | 8.00  |

| 0011        | SCLK/4 | 5.50  | 6.00  |

#### MCUDIV: MCU clock Divider

Ver1.2

| 0100 | SCLK / 5  | 4.40 | 4.80 |

|------|-----------|------|------|

| 0101 | SCLK/6    | 3.67 | 4.00 |

| 0110 | SCLK / 7  | 3.14 | 3.43 |

| 0111 | SCLK / 8  | 2.75 | 3.00 |

| 1000 | SCLK/9    | 2.44 | 2.67 |

| 1001 | SCLK / 10 | 2.20 | 2.40 |

| 1010 | SCLK / 11 | 2.00 | 2.18 |

| 1011 | SCLK / 12 | 1.83 | 2.00 |

| 1100 | SCLK / 13 | 1.69 | 1.85 |

| 1101 | SCLK / 14 | 1.57 | 1.71 |

| 1110 | SCLK / 15 | 1.47 | 1.60 |

| 1111 | SCLK / 16 | 1.38 | 1.50 |

PS1000

### 3.2 ADC Clock Setting

The IA/IB/VA input ADC clock will be set as 1/2 system clock. For the ADC sampling rate, The PS1000 can set the different ADC sampling rate for different application. This setting is controlled by the ADCCFG register. The ADCCFG configuration is

| ADCCFG (0xFE21)             |    |    |    |    |    |    |    |  |

|-----------------------------|----|----|----|----|----|----|----|--|

| B7                          | B6 | B5 | B4 | B3 | B2 | B1 | B0 |  |

| EN ADCMODE Half-Rate ADCDIV |    |    |    |    |    |    |    |  |

#### ADC mode: ADC format selection

- 0x: Unsigned

- 10: Signed 2's complement

- 11: Signed 1's complement

Half-Rate

- 0: Normal ADC data rate

- 1: Half ADC data rate

#### ADCDIV: ADC sampling rate selection

|      |                | SYSCLK(24M) | SYSCLK(22M) |

|------|----------------|-------------|-------------|

| 0000 | ADC_CLK / 375  | 32.00K      | 29.33K      |

| 0001 | ADC_CLK / 750  | 16.00K      | 14.67K      |

| 0010 | ADC_CLK / 768  | 15.63K      | 14.32K      |

| 0011 | ADC_CLK / 1536 | 7.81K       | 7.16K       |

| 0100 | ADC_CLK / 1500 | 8.00K       | 7.33K       |

| 0101 | ADC_CLK / 500  | 24.00K      | 22.00K      |

| 0110 | ADC_CLK / 250  | 48.00K      | 44.00K      |

| Arch Meter Co | orporation   | PS1000 | Ver1.2 |                  |

|---------------|--------------|--------|--------|------------------|

| 0111          | ADC_CLK/38   | 24     | 31.25K | 28.65K           |

| 1000          | ADC_CLK / 54 |        | 22.06K | 28.03K<br>20.22K |

| 1000          | ADC_CLK/ 34  |        | 11.03K | 10.11K           |

| 1010          | ADC CLK / 51 |        | 23.44K | 21.48K           |

| 1011          | ADC_CLK / 10 | 024    | 11.72K | 10.74K           |

| 1100          | ADC_CLK / 13 | 6      | 88.24K | 80.88K           |

| 1101          | ADC_CLK / 27 | 2      | 44.12K | 40.44K           |

| 1110          | ADC_CLK / 12 |        | 93.75K | 85.94K           |

| 1111          | ADC_CLK / 25 | 6      | 46.88K | 42.97K           |

In the PS1000, it still has one ADC for temperature measurement. This ADC can be controlled by the SARCFG.

| SARCFG             | (0xFE22) |    |    |    |    |    |    |