**User Manual**

**PCI-7020**

PCI Half-sized Intel<sup>®</sup> LGA775 Processor Card with VGA/Single Gigabit LAN

Trusted ePlatform Services

# Copyright

The documentation and the software included with this product are copyright 2009 by Advantech Co., Ltd. All rights are reserved. Advantech Co., Ltd. reserves the right to make improvements in the products described in this manual at any time without notice. No part of this manual may be reproduced, copied, translated or transmitted in any form or by any means without the prior written permission of Advantech Co., Ltd. Information provided in this manual is intended to be accurate and reliable. However, Advantech Co., Ltd. assumes no responsibility for its use, nor for any infringements of the rights of third parties, which may result from its use.

# **Acknowledgements**

AWARD is a trademark of Phoenix Technologies Ltd.

IBM and PC are trademarks of International Business Machines Corporation.

Intel<sup>®</sup>, Core<sup>™</sup> 2 Duo, Pentium<sup>®</sup> D, Pentium<sup>®</sup> 4, and Celeron<sup>®</sup> D are trademarks of Intel Corporation.

WinBond is a trademark of Winbond Corporation.

All other product names or trademarks are the properties of their respective owners.

Part No. 2002702000 Printed in China Edition 1 July 2009

## A Message to the Customer

#### **Advantech Customer Services**

Each and every Advantech product is built to the most exacting specifications to ensure reliable performance in the harsh and demanding conditions typical of industrial environments. Whether your new Advantech equipment is destined for the laboratory or the factory floor, you can be assured that your product will provide the reliability and ease of operation for which the name Advantech has come to be known.

Your satisfaction is our primary concern. Here is a guide to Advantech's customer services. To ensure you get the full benefit of our services, please follow the instructions below carefully.

#### **Technical Support**

We want you to get the maximum performance from your products. So if you run into technical difficulties, we are here to help. For the most frequently asked questions, you can easily find answers in your product documentation. These answers are normally a lot more detailed than the ones we can give over the phone.

So please consult this manual first. If you still cannot find the answer, gather all the information or questions that apply to your problem, and with the product close at hand, call your dealer. Our dealers are well trained and ready to give you the support you need to get the most from your Advantech products. In fact, most problems reported are minor and are able to be easily solved over the phone.

In addition, free technical support is available from Advantech engineers every business day. We are always ready to give advice on application requirements or specific information on the installation and operation of any of our products.

# **Declaration of Conformity**

#### **FCC Class A**

Note: This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference in which case the user will be required to correct the interference at his own expense.

Caution! There is a danger of a new battery exploding if it is incorrectly installed. Do not attempt to recharge, force open, or heat the battery. Replace the battery only with the same or equivalent type recommended by the manufacturer. Discard used batteries according to the manufacturer's instructions.

# **Memory Compatibility**

| Brand           | Size   | Speed    | Type | Memory                                         |  |

|-----------------|--------|----------|------|------------------------------------------------|--|

|                 | 512 MB | DDR2 533 | DDR2 | ELPIDA E5108AG-5C-E (64x8)                     |  |

|                 | 512 MB | DDR2 667 | DDR2 | ELPIDA E5108AG-6E-E (64x8)                     |  |

| Apacer(RoHS)    | 1 GB   | DDR2 533 | DDR2 | SAMSUNG K4T51083QB-ZKD5<br>(128x4)             |  |

|                 | 1 GB   | DDR2 533 | DDR2 | ELPIDA E5108AGBG-6E-E (64x8)                   |  |

|                 | 1 GB   | DDR2 667 | DDR2 | ELPIDA E5108AGBG-6E-E (64x8)                   |  |

|                 | 2 GB   | DDR2 667 | DDR2 | SEC K4T1G08400 (128x8)                         |  |

|                 | 512 MB | DDR2 533 | DDR2 | infineon HYB18T512 800AF37<br>FSS43331 (64x8)  |  |

| DSL             | 1 GB   | DDR2 533 | DDR2 | ELPIDA E5108AE-5C-E (64x8)                     |  |

|                 | 1 GB   | DDR2 667 | DDR2 | ELPIDA E5108AGBG-6E-E (64x8)                   |  |

|                 | 2 GB   | DDR2 667 | DDR2 | ELPIDA E1108ACSE-6E-E(128x8)                   |  |

| Kingston(RoHS)  | 2 GB   | DDR2 667 | DDR2 | Micron 7KE12 D9HNL (128x8)                     |  |

|                 | 256 MB | DDR2 533 | DDR2 | infineon HYB18T512160AF3.7<br>3VV21710 (32x16) |  |

|                 | 256 MB | DDR2 533 | DDR2 | SAMSUNG 443 K4T56083QF-GCD5 (32x8)             |  |

|                 | 512 MB | DDR2 533 | DDR2 | SEC K4T51083QC ZCD5 (64X8)                     |  |

| Transcend(RoHS) | 512 MB | DDR2 667 | DDR2 | SAMSUNG K4T51083QC ZCE6 (64x8)                 |  |

|                 | 1 GB   | DDR2 667 | DDR2 | SEC K4T51083QE ZCE6 (64x8)                     |  |

|                 | 1 GB   | DDR2 667 | DDR2 | SEC K4T51083QG HCE6 (64x8)                     |  |

|                 | 2 GB   | DDR2 667 | DDR2 | SAMSUNG K4T1G084QD-ZCE6<br>(128x8)             |  |

|                 | 2 GB   | DDR2 667 | DDR2 | Micron 7HE12 D9HNL (128x8)                     |  |

|                 | 2 GB   | DDR2 667 | DDR2 | SAMSUNG K4T1G084QA-ZCE6<br>(128x8)             |  |

# **Network Feature Comparison**

| LAN/Model           | PCI-7020F | PCI-7020VG | PCI-7020LV |

|---------------------|-----------|------------|------------|

| LAN1: Intel® 82574L | Yes       | Yes        | No         |

## **Processor Support**

Intel Core™ 2 Duo Desktop Processor Intel® Pentium® Dual-Core Desktop Processor Intel Celeron® Processor 400

Long-term supported P/N: E7400, E6400, E4300, E2160, Celeron 440

Intel Pentium D Processor Intel Pentium 4 Processor Intel Celeron D Processor

Note!

PCI-7020 CPU cooler (p/n:1960035861N000), It must use the CPU thermal design power lower than 65 Watt.

## **Product Warranty (2 years)**

Advantech warrants to you, the original purchaser, that each of its products will be free from defects in materials and workmanship for two years from the date of purchase.

This warranty does not apply to any products which have been repaired or altered by persons other than repair personnel authorized by Advantech, or which have been subject to misuse, abuse, accident or improper installation. Advantech assumes no liability under the terms of this warranty as a consequence of such events.

Because of Advantech's high quality-control standards and rigorous testing, most of our customers never need to use our repair service. If an Advantech product is defective, it will be repaired or replaced at no charge during the warranty period. For out-of-warranty repairs, you will be billed according to the cost of replacement materials, service time and freight. Please consult your dealer for more details.

If you think you have a defective product, follow these steps:

- Collect all the information about the problem encountered. (For example, CPU speed, Advantech products used, other hardware and software used, etc.) Note anything abnormal and list any onscreen messages you get when the problem occurs.

- 2. Call your dealer and describe the problem. Please have your manual, product, and any helpful information readily available.

- If your product is diagnosed as defective, obtain an RMA (return merchandise authorization) number from your dealer. This allows us to process your return more quickly.

- 4. Carefully pack the defective product, a fully-completed Repair and Replacement Order Card and a photocopy proof of purchase date (such as your sales receipt) in a shippable container. A product returned without proof of the purchase date is not eligible for warranty service.

- 5. Write the RMA number visibly on the outside of the package and ship it prepaid to your dealer.

# **Initial Inspection**

Before you begin installing your single board computer, please make sure that the following materials have been shipped:

PCI-7020 Intel® LGA775 processor-based single board computer

■ 1 PCI-7020 user manual

■ 1 CD with driver utility and manual (in PDF format)

2 Power cable 12P / Big 4P P/N: 1700006196 1 Dual COM cable 2.0 mm pitch P/N: 1700008762 1 Serial ATA HDD data cable P/N: 1700003194 1 Serial ATA HDD power cable P/N: 1703150102 P/N: 1700002223 1 Printer port cable 2.0 mm pitch 1 Y cable for PS/2 keyboard and PS/2 mouse P/N: 1700060202 1 USB cable with 4 ports P/N: 1700014398 ATX feature cable P/N: 1700002343 P/N: 9689000002 1 Jumper pack CPU cooler P/N: 1960035861N000

1 warranty card

If any of these items are missing or damaged, contact your distributor or sales representative immediately. We have carefully inspected the PCI-7020 mechanically and electrically before shipment. It should be free of marks and scratches and in perfect working order upon receipt. As you unpack the PCI-7020, check it for signs of shipping damage. (For example, damaged box, scratches, dents, etc.) If it is damaged or it fails to meet the specifications, notify our service department or your local sales representative immediately. Also notify the carrier. Retain the shipping carton and packing material for inspection by the carrier. After inspection, we will make arrangements to repair or replace the unit.

Note!

PCI-7020 CPU cooler (p/n:1960035861N000), It must use the CPU thermal design power lower than 65 Watt.

# **Contens**

| Chapter | 1    | Hardware Configuration                                                | 1  |

|---------|------|-----------------------------------------------------------------------|----|

|         | 1.1  | Introduction                                                          | 2  |

|         | 1.2  | Features                                                              | 2  |

|         | 1.3  | Specifications                                                        | 3  |

|         |      | 1.3.1 System                                                          |    |

|         |      | 1.3.2 Memory                                                          |    |

|         |      | 1.3.3 Input/Output                                                    |    |

|         |      | 1.3.4 Ethernet LAN                                                    |    |

|         |      | 1.3.5 Industrial Features                                             |    |

|         |      | 1.3.6 Mechanical and Environmental Specifications                     |    |

|         | 1.4  | Jumpers and Connectors                                                |    |

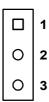

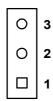

|         |      | Table 1.1: Jumpers                                                    |    |

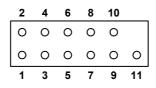

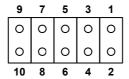

|         | 4.5  | Table 1.2: Connectors                                                 |    |

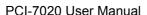

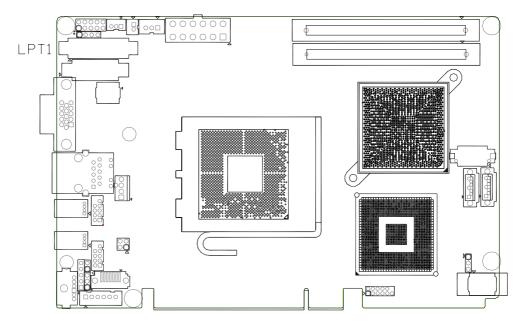

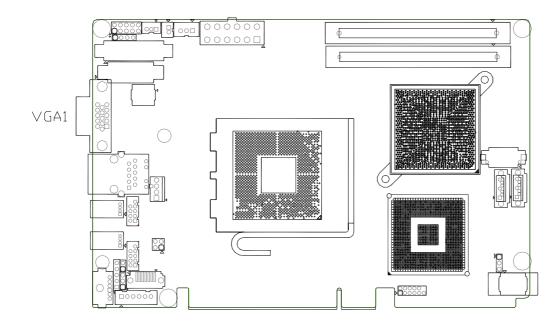

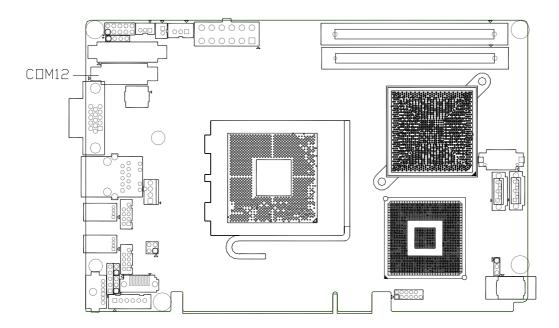

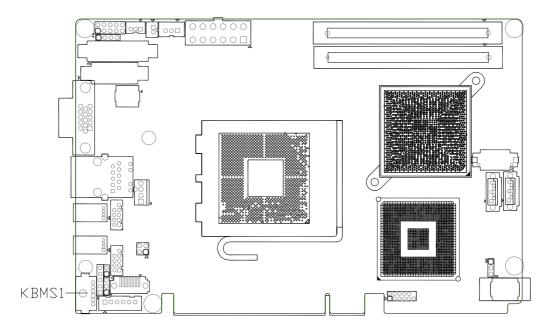

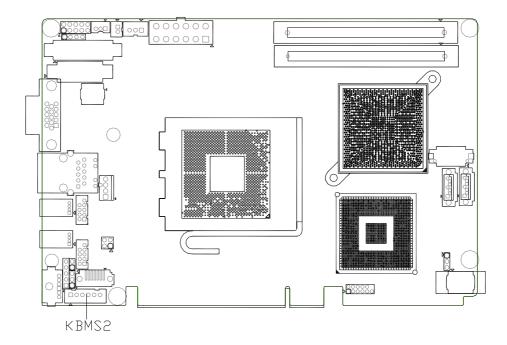

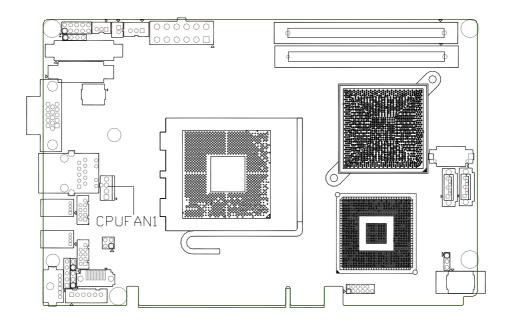

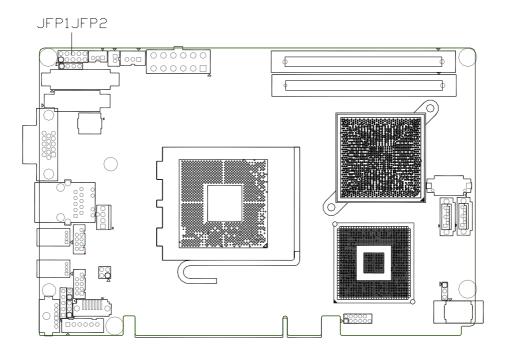

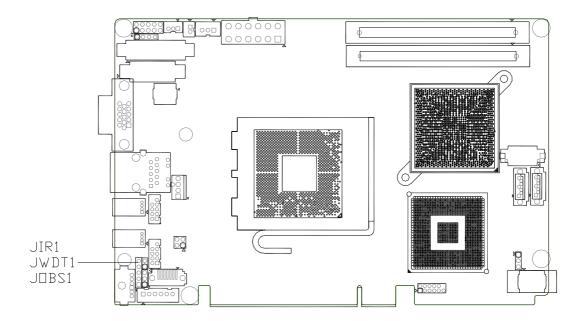

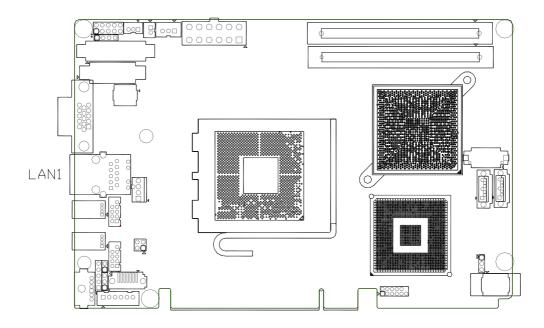

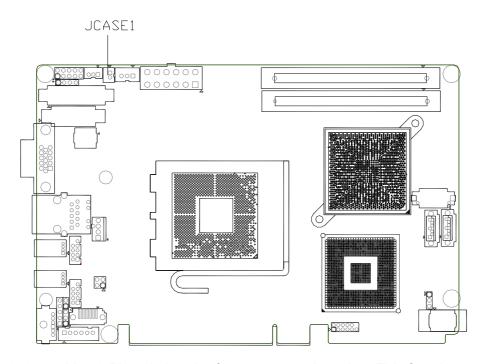

|         | 1.5  | Board Layout: Jumper and Connector                                    |    |

|         |      | Figure 1.1 Jumper and connector location (top)                        |    |

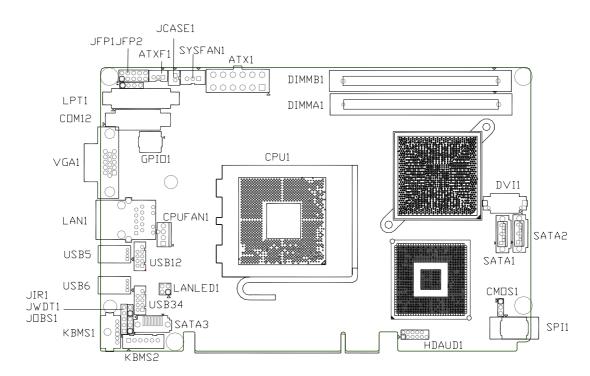

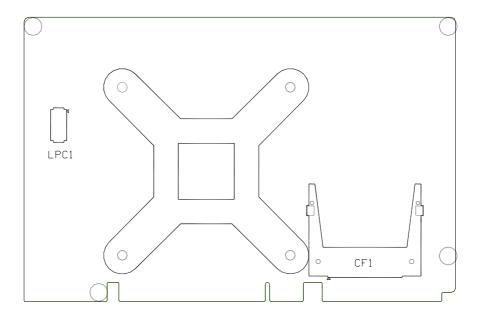

|         | 1.6  | Figure 1.2 Jumper and connector location (bot) PCI-7020 Block Diagram |    |

|         | 1.0  | Figure 1.3 PCI-7020 block diagram                                     |    |

|         | 1.7  | Safety Precautions                                                    |    |

|         | 1.7  | Jumper Settings                                                       |    |

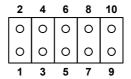

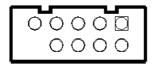

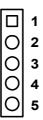

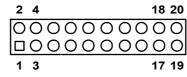

|         | 1.0  | 1.8.1 How to Set Jumpers                                              |    |

|         |      | 1.8.2 CMOS Clear (CMOS1)                                              |    |

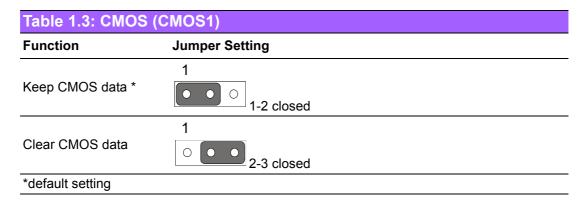

|         |      | Table 1.3: CMOS (CMOS1)                                               |    |

|         |      | 1.8.3 Watchdog Timer Output (JWDT1)                                   |    |

|         |      | Table 1.4: Watchdog Timer Output (JWDT1)                              |    |

|         | 1.9  | System Memory                                                         |    |

|         |      | 1.9.1 CPU FSB and Memory Speed                                        |    |

|         | 1.10 | Memory Installation Procedures                                        |    |

|         | 1.11 | Cache Memory                                                          | 9  |

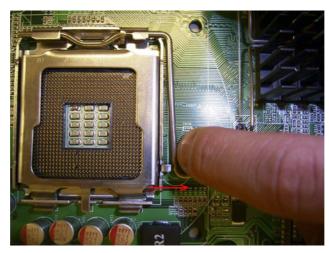

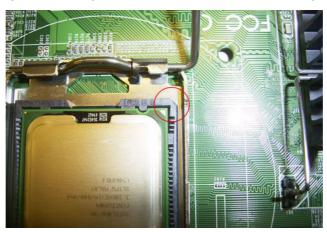

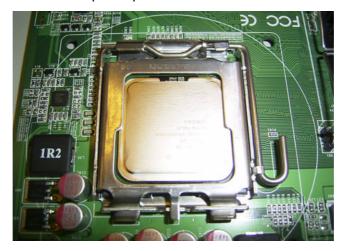

|         | 1.12 | Processor Installation                                                | 9  |

|         | 1.13 | Power Model Setting and Installation                                  | 10 |

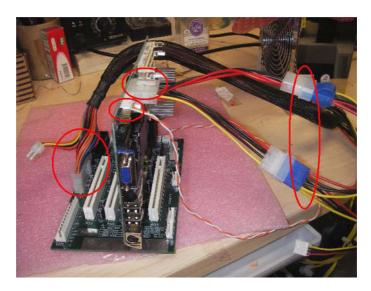

|         |      | Figure 1.4 ATX power setting of PCI-7020 with backplane               | 10 |

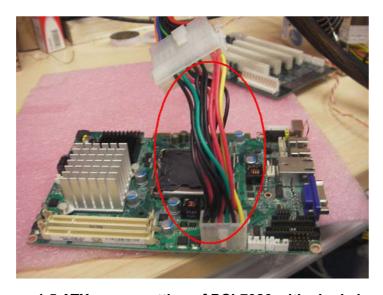

|         |      | Figure 1.5 ATX power setting of PCI-7020 with single board            |    |

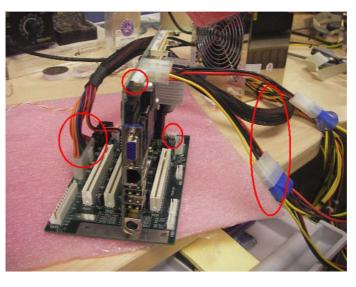

|         |      | Figure 1.6 AT power setting of PCI-7020 with backplane                |    |

|         |      | Figure 1.7 AT power setting of PCI-7020 with single board             | 11 |

| Chapter | 2    | Connecting Peripherals                                                | 13 |

|         | 2.1  | Introduction                                                          |    |

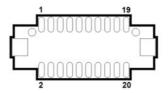

|         | 2.2  | Parallel Port (LPT1)                                                  |    |

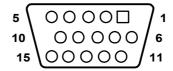

|         | 2.3  | VGA Connector (VGA1)                                                  | 15 |

|         | 2.4  | Serial Ports (COM1, COM2)                                             | 15 |

|         | 2.5  | PS/2 Keyboard and Mouse Connector (KBMS1)                             |    |

|         | 2.6  | External Keyboard & Mouse (KBMS2)                                     |    |

|         | 2.7  | CPU Fan Connector (CPUFAN1)                                           |    |

|         | 2.8  | Front Panel Connectors (JFP1, JFP2)                                   |    |

|         | 2.9  | H/W Monitor Alarm (JOBS1)                                             |    |

|         |      | Table 2.1: Hardware Monitor Alarm Setting                             |    |

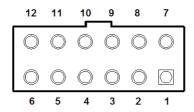

|         | 2.10 | LAN RJ45 Connector (LAN1)                                             |    |

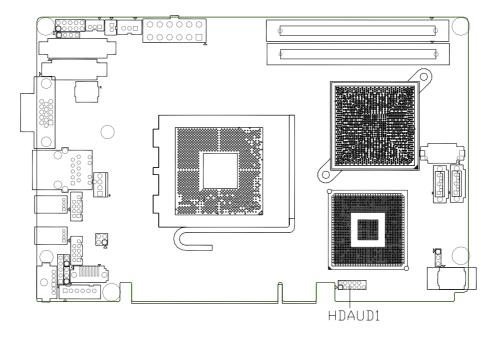

|         | 2.11 | HD Link Connector (HDAUD1)                                            |    |

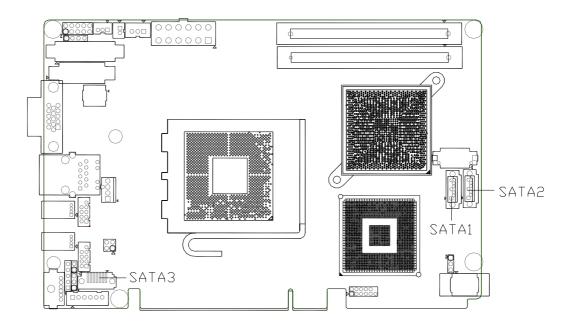

|         | 2.12 | Serial ATA2 Interface (SATA1 ~ SATA3)                                 |    |

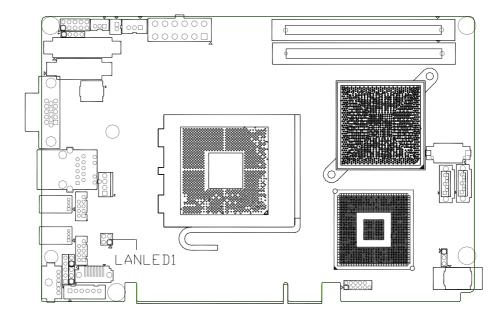

|         | 2.13 | LAN LED Connector (LAN LED1)                                          |    |

|         | 0.44 | Table 2.2: Front Panel LAN Indicator Connector                        |    |

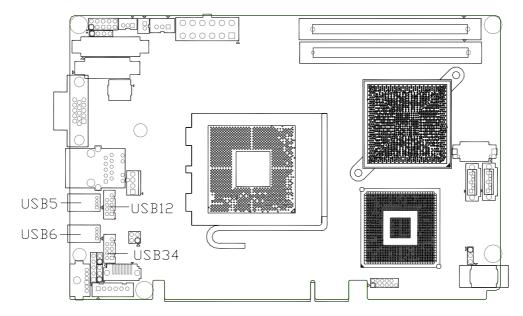

|         | 2.14 | USB (USB12, USB34, USB56)                                             | 21 |

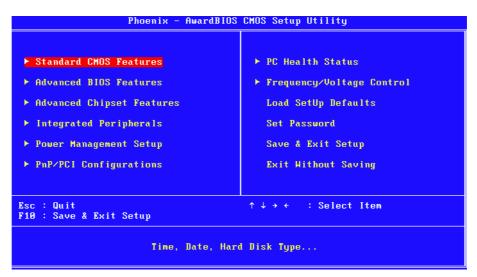

| Chapter 3 Award BIOS Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 24        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 3.1.1 CMOS RAM Auto-backup and Restore  Figure 3.1 Award BIOS setup initial screen  3.3 Standard CMOS Setup  Figure 3.2 Standard CMOS features screen  3.4 Advanced BIOS Features  Figure 3.3 Advanced BIOS features screen  3.5 Advanced Chipset Features  Figure 3.4 Advanced chipset features screen  3.6 Integrated Peripherals  Figure 3.5 Integrated peripherals  Figure 3.6 On-Chip IDE device  Figure 3.7 Onboard device  Figure 3.8 Super I/O device.  3.7 Power Management Setup  Figure 3.10Power management setup screen (Conn.)  Table 3.1: Power Saving  3.8 PnP/PCI Configurations  Figure 3.11PnP/PCI configurations screen  3.9 PC Health Status  Figure 3.12PC health status screen  3.10 Frequency / Voltage Control  Figure 3.13Spread spectrum control screen  3.11 Password Setting  Figure 3.14Enter password  3.12 Load Setup Defaults  Figure 3.15 Load setup defaults screen  Figure 3.15 Load setup defaults screen  Figure 3.15 Load setup defaults screen  Figure 3.16Save to CMOS and Exit  Exit Without Saving                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |

| 3.1.1 CMOS RAM Auto-backup and Restore  Figure 3.1 Award BIOS setup initial screen  3.3 Standard CMOS Setup  Figure 3.2 Standard CMOS features screen  3.4 Advanced BIOS Features  Figure 3.3 Advanced BIOS features screen  3.5 Advanced Chipset Features  Figure 3.4 Advanced chipset features screen  3.6 Integrated Peripherals  Figure 3.5 Integrated peripherals  Figure 3.6 On-Chip IDE device  Figure 3.7 Onboard device  Figure 3.8 Super I/O device.  3.7 Power Management Setup  Figure 3.10Power management setup screen (Conn.)  Table 3.1: Power Saving  3.8 PnP/PCI Configurations  Figure 3.11PnP/PCI configurations screen  3.9 PC Health Status  Figure 3.12PC health status screen  3.10 Frequency / Voltage Control  Figure 3.13Spread spectrum control screen  3.11 Password Setting  Figure 3.14Enter password  3.12 Load Setup Defaults  Figure 3.15 Load setup defaults screen  Figure 3.15 Load setup defaults screen  Figure 3.15 Load setup defaults screen  Figure 3.16Save to CMOS and Exit  Exit Without Saving                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |

| Standard CMOS Setup   Figure 3.1 Award BIOS setup initial screen.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 24        |

| Figure 3.1 Award BIOS setup initial screen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |

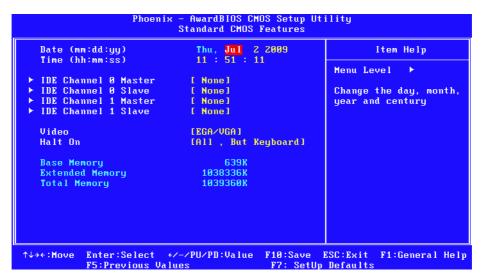

| Standard CMOS Setup Figure 3.2 Standard CMOS features screen  3.4 Advanced BIOS Features Figure 3.3 Advanced BIOS features screen  3.5 Advanced Chipset Features Figure 3.4 Advanced chipset features screen  3.6 Integrated Peripherals. Figure 3.5 Integrated peripherals Figure 3.6 On-Chip IDE device Figure 3.7 Onboard device Figure 3.8 Super I/O device  3.7 Power Management Setup Figure 3.9 Power management setup screen Figure 3.10 Power management setup screen Figure 3.11 Power Saving  3.8 PnP/PCI Configurations Figure 3.11PnP/PCI configurations screen  3.9 PC Health Status Figure 3.11PnP/PCI configurations screen  3.10 Frequency / Voltage Control Figure 3.13Spread spectrum control screen  3.11 Password Setting Figure 3.14Enter password  3.12 Load Setup Defaults Figure 3.15 Load setup defaults screen  5ave & Exit Setup Figure 3.16Save to CMOS and Exit  5axe & Exit Setup Figure 3.16Save to CMOS and Exit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |

| Figure 3.2 Standard CMOS features screen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |

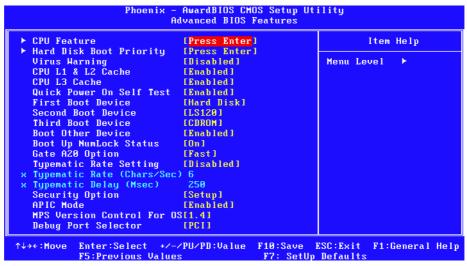

| 3.4   Advanced BIOS Features   Figure 3.3   Advanced BIOS features screen   3.5   Advanced Chipset Features   Figure 3.4   Advanced chipset features screen   3.6   Integrated Peripherals   Figure 3.5   Integrated peripherals   Figure 3.6   On-Chip IDE device   Figure 3.7   Onboard device   Figure 3.8   Super I/O device   Figure 3.8   Super I/O device   Super I/O device   Figure 3.9   Power Management Setup   Figure 3.10   Power management setup screen   Figure 3.11   Power Saving   Super I/O device   Figure 3.11   Power Saving   Super I/O device   Figure 3.12   Power Saving   Super I/O device   Figure 3.12   Power Saving   Super I/O device   Figure 3.12   Power Saving   Figure 3.11   Power Saving   Figure 3.11   Power Saving   Figure 3.12   Power Saving   Figure 3.12   Power Saving   Figure 3.13   Power Saving   Figure 3.13   Power Saving   Figure 3.14   Figure 3.14   Enter password   Super I/O device   Figure 3.15   Figure 3.15   Figure 3.16   Figure 3.16   Figure 3.16   Figure 3.16   Figure 3.16   Figure 3.14   Exit Without Saving   Figure 3.14   Exit Without Saving   Figure 3.14   Exit Without Saving   Figure 3.14   Figure 3.16   Figure 3.16 |           |

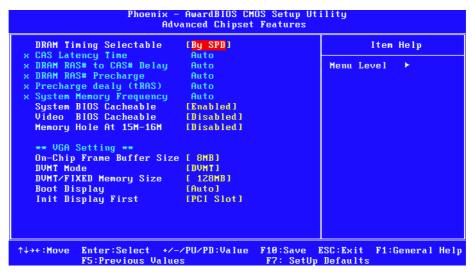

| 3.5 Advanced Chipset Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |

| Figure 3.4 Advanced chipset features screen  3.6 Integrated Peripherals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 26        |

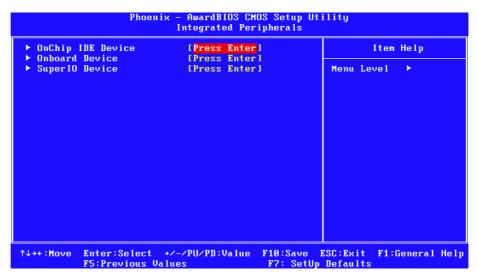

| Figure 3.5 Integrated peripherals  Figure 3.5 Integrated peripherals  Figure 3.6 On-Chip IDE device  Figure 3.7 Onboard device  Figure 3.8 Super I/O device  3.7 Power Management Setup  Figure 3.9 Power management setup screen  Figure 3.10Power management setup screen (Conn.)  Table 3.1: Power Saving  3.8 PnP/PCI Configurations  Figure 3.11PnP/PCI configurations screen  3.9 PC Health Status  Figure 3.12PC health status screen  3.10 Frequency / Voltage Control  Figure 3.13Spread spectrum control screen  3.11 Password Setting  Figure 3.14Enter password  3.12 Load Setup Defaults  Figure 3.15 Load setup defaults screen  3.13 Save & Exit Setup  Figure 3.16Save to CMOS and Exit  3.14 Exit Without Saving                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 28        |

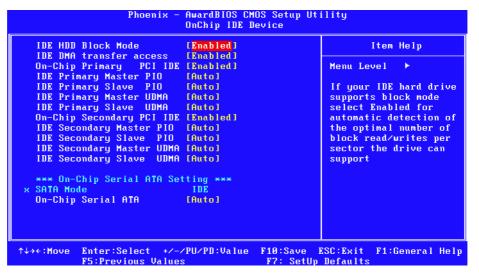

| Figure 3.5 Integrated peripherals Figure 3.6 On-Chip IDE device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 28        |

| Figure 3.6 On-Chip IDE device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |

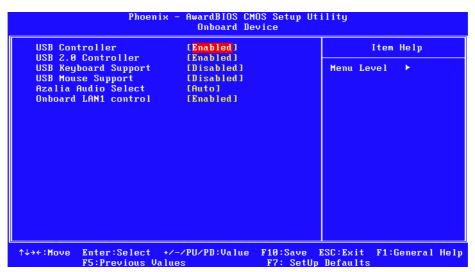

| Figure 3.7 Onboard device Figure 3.8 Super I/O device  3.7 Power Management Setup Figure 3.9 Power management setup screen Figure 3.10Power management setup screen (Conn.) Table 3.1: Power Saving  3.8 PnP/PCI Configurations Figure 3.11PnP/PCI configurations screen  3.9 PC Health Status Figure 3.12PC health status screen  3.10 Frequency / Voltage Control Figure 3.13Spread spectrum control screen  3.11 Password Setting Figure 3.14Enter password  3.12 Load Setup Defaults Figure 3.15 Load setup defaults screen  3.13 Save & Exit Setup Figure 3.16Save to CMOS and Exit  3.14 Exit Without Saving                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |

| Figure 3.8 Super I/O device  3.7 Power Management Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |

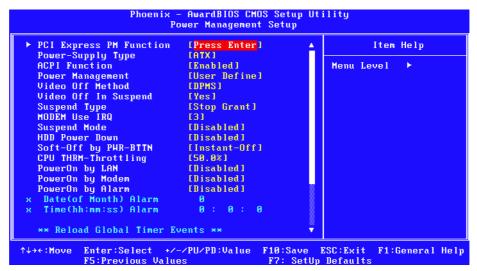

| 3.7 Power Management Setup  Figure 3.9 Power management setup screen  Figure 3.10Power management setup screen (Conn.)  Table 3.1: Power Saving  3.8 PnP/PCI Configurations  Figure 3.11PnP/PCI configurations screen  3.9 PC Health Status  Figure 3.12PC health status screen  3.10 Frequency / Voltage Control  Figure 3.13Spread spectrum control screen  3.11 Password Setting  Figure 3.14Enter password  3.12 Load Setup Defaults  Figure 3.15 Load setup defaults screen  3.13 Save & Exit Setup  Figure 3.16Save to CMOS and Exit  3.14 Exit Without Saving                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |

| Figure 3.9 Power management setup screen Figure 3.10Power management setup screen (Conn.) Table 3.1: Power Saving  3.8 PnP/PCI Configurations Figure 3.11PnP/PCI configurations screen  3.9 PC Health Status Figure 3.12PC health status screen  3.10 Frequency / Voltage Control Figure 3.13Spread spectrum control screen  3.11 Password Setting Figure 3.14Enter password  3.12 Load Setup Defaults Figure 3.15 Load setup defaults screen  3.13 Save & Exit Setup Figure 3.16Save to CMOS and Exit  3.14 Exit Without Saving                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 32        |

| Figure 3.10 Power management setup screen (Conn.) Table 3.1: Power Saving  3.8 PnP/PCI Configurations Figure 3.11 PnP/PCI configurations screen  3.9 PC Health Status Figure 3.12 PC health status screen  3.10 Frequency / Voltage Control Figure 3.13 Spread spectrum control screen  3.11 Password Setting Figure 3.14 Enter password  3.12 Load Setup Defaults Figure 3.15 Load setup defaults screen  3.13 Save & Exit Setup Figure 3.16 Save to CMOS and Exit  3.14 Exit Without Saving                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 34        |

| Table 3.1: Power Saving  3.8 PnP/PCI Configurations Figure 3.11PnP/PCI configurations screen  3.9 PC Health Status Figure 3.12PC health status screen  3.10 Frequency / Voltage Control Figure 3.13Spread spectrum control screen  3.11 Password Setting Figure 3.14Enter password  3.12 Load Setup Defaults Figure 3.15 Load setup defaults screen  3.13 Save & Exit Setup Figure 3.16Save to CMOS and Exit  3.14 Exit Without Saving                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |

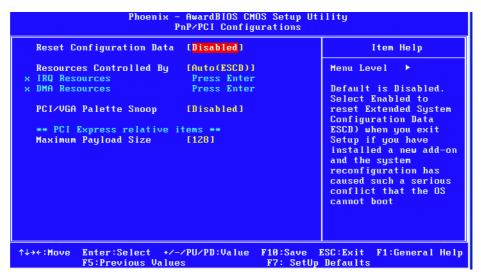

| 3.8 PnP/PCI Configurations Figure 3.11PnP/PCI configurations screen  3.9 PC Health Status Figure 3.12PC health status screen  3.10 Frequency / Voltage Control Figure 3.13Spread spectrum control screen  3.11 Password Setting Figure 3.14Enter password  3.12 Load Setup Defaults Figure 3.15 Load setup defaults screen  3.13 Save & Exit Setup Figure 3.16Save to CMOS and Exit  3.14 Exit Without Saving                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |

| Figure 3.11PnP/PCI configurations screen  3.9 PC Health Status Figure 3.12PC health status screen  3.10 Frequency / Voltage Control Figure 3.13Spread spectrum control screen  3.11 Password Setting Figure 3.14Enter password  3.12 Load Setup Defaults Figure 3.15 Load setup defaults screen  3.13 Save & Exit Setup Figure 3.16Save to CMOS and Exit  3.14 Exit Without Saving                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |

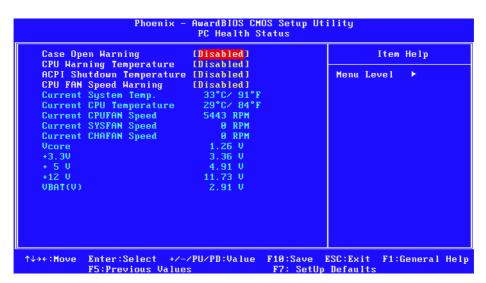

| 3.9 PC Health Status Figure 3.12PC health status screen  3.10 Frequency / Voltage Control Figure 3.13Spread spectrum control screen  3.11 Password Setting Figure 3.14Enter password  3.12 Load Setup Defaults Figure 3.15 Load setup defaults screen  3.13 Save & Exit Setup Figure 3.16Save to CMOS and Exit  3.14 Exit Without Saving                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 36        |

| Figure 3.12PC health status screen  3.10 Frequency / Voltage Control Figure 3.13Spread spectrum control screen  3.11 Password Setting Figure 3.14Enter password  3.12 Load Setup Defaults Figure 3.15 Load setup defaults screen  3.13 Save & Exit Setup Figure 3.16Save to CMOS and Exit  3.14 Exit Without Saving                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 36        |

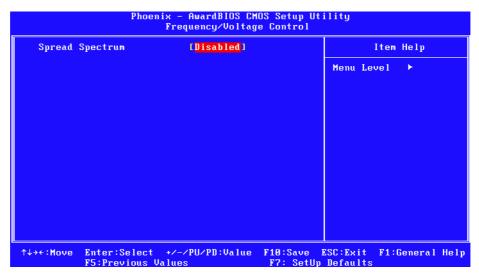

| 3.10 Frequency / Voltage Control Figure 3.13Spread spectrum control screen 3.11 Password Setting Figure 3.14Enter password 3.12 Load Setup Defaults Figure 3.15 Load setup defaults screen 3.13 Save & Exit Setup Figure 3.16Save to CMOS and Exit 3.14 Exit Without Saving                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           |

| Figure 3.13Spread spectrum control screen  3.11 Password Setting Figure 3.14Enter password  3.12 Load Setup Defaults Figure 3.15 Load setup defaults screen  3.13 Save & Exit Setup Figure 3.16Save to CMOS and Exit  3.14 Exit Without Saving                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |

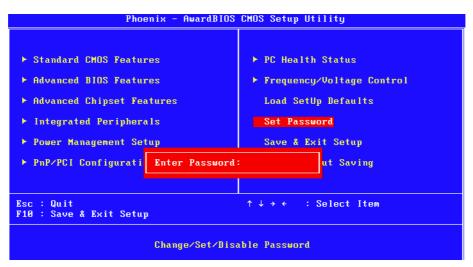

| 3.11 Password Setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |

| Figure 3.14Enter password  3.12 Load Setup Defaults  Figure 3.15 Load setup defaults screen  3.13 Save & Exit Setup  Figure 3.16Save to CMOS and Exit  3.14 Exit Without Saving                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |

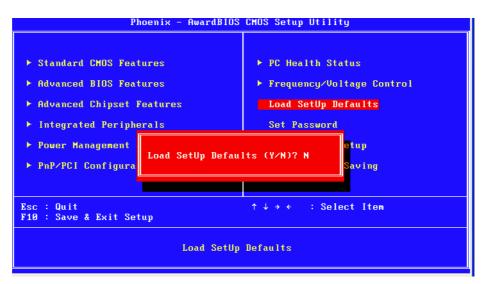

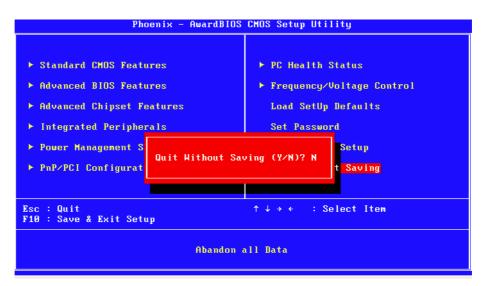

| 3.12 Load Setup Defaults  Figure 3.15 Load setup defaults screen  3.13 Save & Exit Setup  Figure 3.16Save to CMOS and Exit  3.14 Exit Without Saving                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |

| Figure 3.15 Load setup defaults screen  3.13 Save & Exit Setup  Figure 3.16Save to CMOS and Exit  3.14 Exit Without Saving                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 39        |

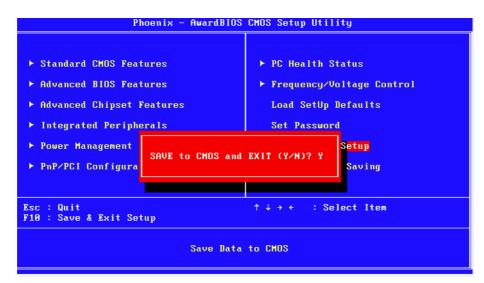

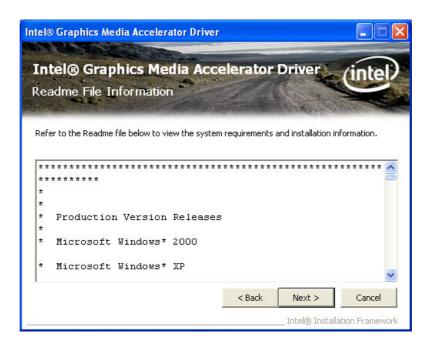

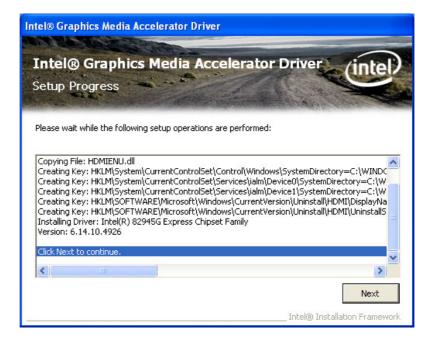

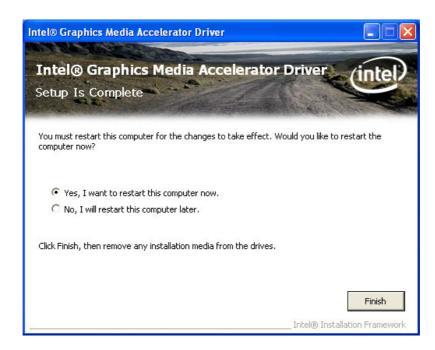

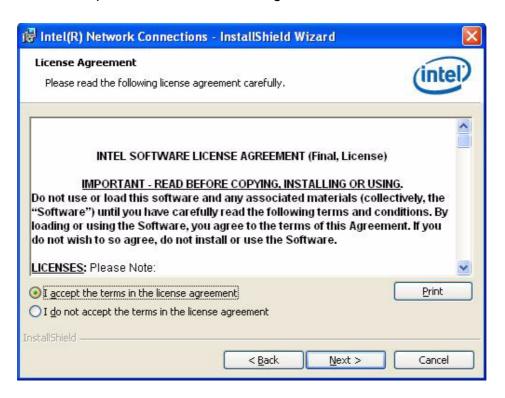

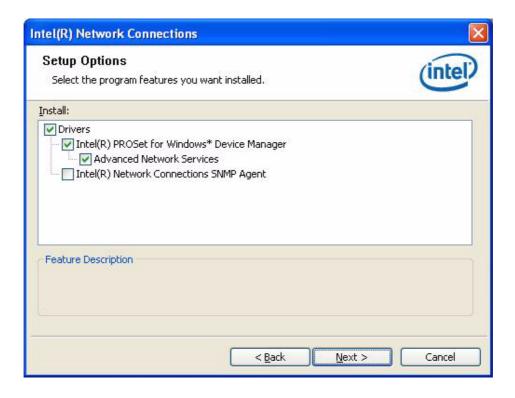

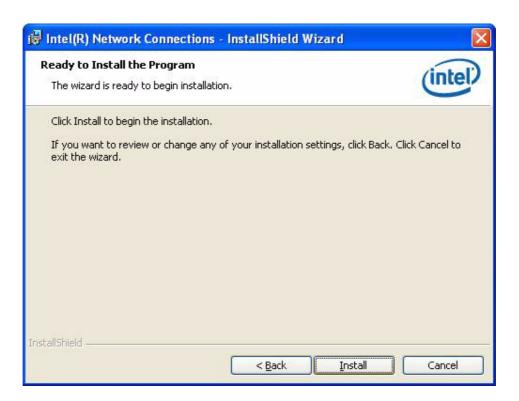

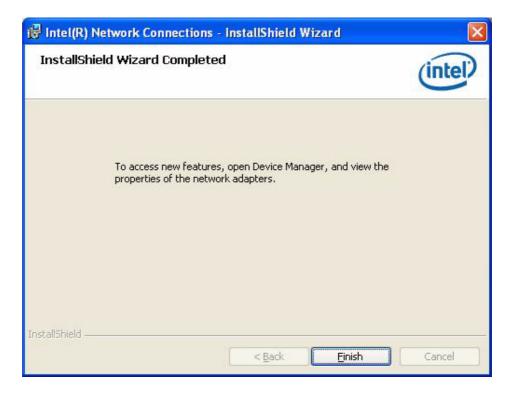

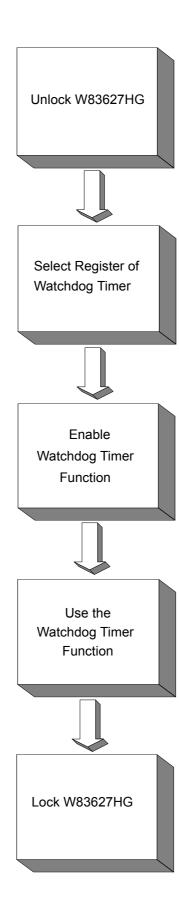

| 3.13 Save & Exit Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |