## ZT 8808A/8809A V20 Single Board Computers

**OPERATING MANUAL**

FOR

ZT 8808A/8809A REVISION A ZT 88CT08A/88CT09A REVISION A

May 1, 1993

1050 Southwood Drive San Luis Obispo, CA 93401 USA FAX (805) 541-5088 Telephone (805) 541-0488

# ZIATECH WARRANTY

**Ziatech Hardware:** Within two years of shipping date, Ziatech will repair or replace products which prove to be defective in materials and/or workmanship, provided they are promptly returned to Ziatech at customer's expense and have not been repaired, altered, or damaged by non-Ziatech personnel. Service after warranty is available at a predesignated service charge. Batteries are not covered by this warranty. No other warranty is expressed or implied.

**Ziatech Software:** Within 90 days of shipping date, Ziatech will replace software (PROM or diskette) should it prove defective.

**Products not manufactured by Ziatech:** Limited to the warranty provided by the original manufacturer.

**Notice:** Contact Ziatech for a Return Materials Authorization (RMA) number before returning any product to Ziatech for repair.

**Life Support Policy:** Ziatech products are not authorized for use as critical components in life support devices or systems without the express written approval of the president of Ziatech Corporation. As used herein:

- 1. Life support devices or systems are devices or systems that support or sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### ©1993 Ziatech Corporation

IBM PC, PC/AT, and PC/XT are registered trademarks of International Business Machines, Inc. MS-DOS is a registered trademark of Microsoft Corp.

#### **CUSTOMER SUPPORT**

If you have a technical question, please call Ziatech's Customer Support Service at one of the following numbers.

Corporate Headquarters: (805) 541-0488 (805) 541-5088 (FAX)

You can also use a modem to leave a message on the 24-hour Ziatech Bulletin Board Service (BBS) by calling (805) 541-8218. The BBS will provide you with current Ziatech product revision and upgrade information.

## PREFACE

The ZT 8808A and ZT 8809A are single board computers designed primarily for DOS applications on the STD bus. The combination of the 8088-compatible V20 microprocessor with RAM, EPROM, serial ports, a printer port, timers, and a real-time clock makes a hardwarecompatible PC viable for compact industrial applications.

This manual describes the operation and use of the ZT 8808A/8809A. The only difference between the ZT 8808A and ZT 8809A is the processor clock speed; the ZT 8808A runs at 5 MHz and the ZT 8809A runs at 8 MHz. The ZT 88CT08A and ZT 88CT09A are extended temperature CMOS versions of the ZT 8808A and ZT 8809A.

Except where otherwise specifically stated, all references in this manual to the ZT 8809A also apply to the ZT 8808A and ZT 88CT08A/88CT09A.

The following organizational outline describes the focus of each chapter. Section headings enclosed in boxes indicate the locations of labeled tabs, provided for quick access to the appropriate information.

**Chapter 1, "Introduction,"** is an overview of the ZT 8809A. It includes a product definition, a listing of product features, a functional block diagram, and a brief description of each block. If you are evaluating the ZT 8809A to determine whether it fits your needs, this chapter is especially useful to you.

**Chapter 2, "Getting Started,"**summarizes the information you need to get your ZT 8809A up and running. Refer to the remaining chapters in this manual for further explanation of the material covered here.

**Chapter 3, "Theory Of Operation,"** presents a detailed description of ZT 8809A system level operation. Some of the topics discussed include microprocessor performance compared to the IBM PC®,

STD bus compatibility, serial communications, interrupts, direct memory access, power-fail protection, and battery backup.

**Chapter 4, "Application Examples,"** provides specific examples of the ZT 8809A in operation, including code to implement these applications. The examples demonstrate the use of interrupts, timers, and the real-time clock.

**Chapter 5, "Memory and I/O Capability,"** focuses on the memory and input/output organization of the V20 microprocessor relative to the ZT 8809A.

**Chapter 6, "CPU Description (V20),"** describes the basic components of the V20 microprocessor, its enhancements over 8088 architecture, its ability to operate in both native mode and 8080 emulation mode, its operation with DMA, and the wait state generator.

**Chapter 7, ''Numeric Data Processor (8087),''** explains the installation and operation of the optional 8087 Numeric Data Processor for numerically intensive applications.

**Chapter 8, "Serial Communications (16C452),"** describes the two RS-232-C serial ports on the ZT 8809A, serial port signals, and register addresses.

Chapter 9, "Centronics Printer Interface," details the Centronics printer port interface.

**Chapter 10, ''Real-Time Clock (DS 1215),''** explains the organization of the real-time clock, including method of access and register organization.

**Chapter 11, "Counter/Timers (8254),"** describes the main components of the three programmable 16-bit counter/timers implemented in an Intel 8254 chip on the ZT 8809A. This chapter describes the method used to program the counter/timers and their use by STD DOS and STD ROM.

**Chapter 12, ''Interrupt Controller (8259A),''** describes the features and operation of the Intel 8259A Programmable Interrupt Controller (PIC).

**Chapter 13, ''ZT 88CT08A/88CT09A CMOS Boards,''** describes the functional, electrical, and environmental characteristics of the CMOS versions of the ZT 8808A and ZT 8809A that differ from the non-CMOS versions.

**Appendix A, "Jumper Configurations,"** describes the ZT 8809A jumper selectable options in detail.

**Appendix B, "Specifications,"** contains the electrical, mechanical, and environmental specifications for the ZT 8809A. It also contains STD-80 bus timing diagrams, cable drawings, and tables showing connector pin assignments.

**Appendix C, "Customer Support,"** offers technical assistance for ZT 8809A users. A revision history, and warranty and service information are also included.

## CONTENTS

#### I. INTRODUCTION

| Chapter 1. INTRODUCTION 1                           | -1 |

|-----------------------------------------------------|----|

| OVERVIEW                                            | -1 |

| ZT 88CT08A and ZT 88CT09A 1                         | -3 |

| FEATURES OF THE ZT 8809A 1                          | -4 |

| FUNCTIONAL BLOCKS 1                                 | -6 |

| V20 (uPD70108) Processor                            | -6 |

| Memory and I/O Addressing 1                         | -6 |

| Wait-State Generator 1                              | -7 |

| Direct Memory Access (DMA) 1                        | -7 |

| Optional Battery Backup 1                           | -7 |

| AC/DC Power-Fail Detection 1                        | -8 |

| Real-Time Clock 1                                   | -9 |

| Serial Communications 1                             | -9 |

| Counter/Timers 1-1                                  | 10 |

| Interrupts 1-1                                      | 11 |

| Centronics Printer/General Purpose I/O Port 1-1     | 12 |

| Optional Numeric Data Coprocessor (8087) 1-1        | 12 |

| Clock Slowdown & Halt Restart (CMOS boards only) 1- | 13 |

|                                                     |    |

### II. GETTING STARTED

| Chapter 2. GETTING STARTED | 2-1 |

|----------------------------|-----|

| OVERVIEW                   | 2-2 |

| UNPACKING                  | 2-2 |

| WHAT'S IN THE BOX?         | 2-3 |

| SYSTEM REQUIREMENTS        | 2-4 |

| Physical Requirements                | 2-4  |

|--------------------------------------|------|

| Power Requirements                   | 2-4  |

| Environmental Requirements           | 2-6  |

| INSTALLING THE ZT 8809A              | 2-7  |

| Configuring the ZT 8809A for STD ROM | 2-9  |

| Configuring the ZT 8809A for STD DOS | 2-13 |

| MEMORY ADDRESSING                    | 2-19 |

| I/O ADDRESSING                       | 2-22 |

| UPGRADING FROM ZT 8806/8807 SYSTEMS  | 2-24 |

## III. USER'S REFERENCE

| Chapter 3. THEORY OF OPERATION      | 3-1  |

|-------------------------------------|------|

| OVERVIEW                            | 3-2  |

| RELATIVE MICROPROCESSOR PERFORMANCE | 3-3  |

| STD BUS COMPATIBILITY               | 3-4  |

| MEMORY AND I/O                      |      |

| SERIAL COMMUNICATIONS               | 3-4  |

| Serial Port 1 (COM1)                | 3-5  |

| Serial Port 2 (COM2)                | 3-6  |

| INTERRUPTS                          | 3-8  |

| Interrupt Request Assignments       | 3-8  |

| Polled Interrupts on the STD Bus    |      |

| STD Bus Vectored Interrupts         |      |

| STD Bus Cascaded Interrupts         |      |

| Non-Maskable Interrupts             |      |

| DIRECT MEMORY ACCESS (DMA)          |      |

| Advantages of DMA                   |      |

| DMA Operation                       | 3-16 |

| POWER-FAIL PROTECTION               |      |

| DC Power-Fail                       | 3-18 |

| AC Power-Fail                       | 3-19 |

| System Battery Fail                 | 3-22 |

| BATTERY                             | 3-23 |

| STATUS INDICATOR (LED)              |      |

| RESET                               | 3-26 |

| CMOS VERSIONS OF THE ZT 8808A/8809A | 3-27 |

| Added Features                      | 3-27 |

| Functional Differences              | 3-29 |

| Chapter 4. APPLICATION EXAMPLES          | 4-1 |

|------------------------------------------|-----|

| OVERVIEW                                 | 4-2 |

| EXAMPLE 1-A: USING SIMPLE INTERRUPTS     |     |

| Objectives                               | 4-3 |

| System Configuration                     |     |

| Software Outline                         | 4-4 |

| Program Code                             | 4-6 |

| EXAMPLE 1-B: HANDLING SLAVE INTERRUPTS 4 | -13 |

| Objectives                               | -13 |

| System Configuration 4                   | -14 |

| Software Outline 4                       | -14 |

|                                          | -17 |

| EXAMPLE 2: POWER-FAIL/WATCHDOG TIMER 4   | -28 |

| Objectives                               | -28 |

| System Level Issues 4                    |     |

| System Requirements 4                    | -29 |

|                                          | -31 |

|                                          | -34 |

| EXAMPLE 3: REAL-TIME CLOCK DRIVERS 4     |     |

| Objectives                               |     |

| System Configuration 4                   |     |

| Software Outline                         | -40 |

| Chapter 5. MEMORY AND I/O CAPABILITY     | 5-1 |

| OVERVIEW                                 | 5-1 |

| MEMORY ADDRESSING                        |     |

| Memory Expansion (MEMEX)                 |     |

| On-Board Memory Capacity                 |     |

| Write Protection                         |     |

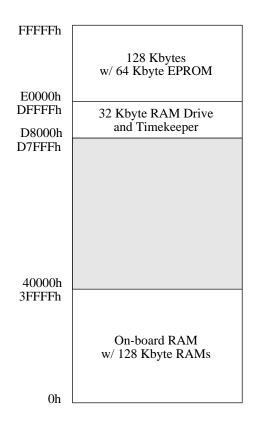

| MEMORY MAPS                              | 5-4 |

| BATTERY BACKUP 5                         | -10 |

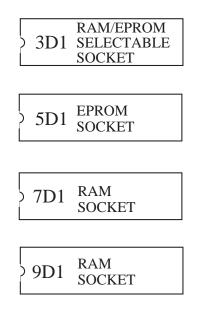

| MEMORY DEVICE LOCATIONS                  | -11 |

| Sockets 3D1 and 5D1 5                    | -12 |

| Sockets 7D1 and 9D1 5                    | -13 |

| DEVICE ACCESS TIMES                      | -14 |

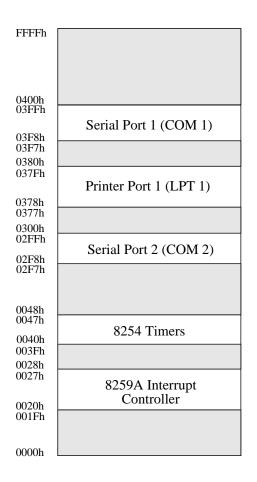

| INPUT/OUTPUT ADDRESSING                  | -15 |

| Chapter 6. CPU DESCRIPTION (V20)         | 6-1 |

| V20 OVERVIEW                             | 6-2 |

| Segment Registers                        | ~ - |

| Program Counter (PC) [IP]                |     |

| Prefetch Pointer (PFP)                                                                                                                                                                                                                                                                                                                                                                                                                         | 6-6                                                                                                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General Purpose Registers                                                                                                                                                                                                                                                                                                                                                                                                                      | . 6-6                                                                                                                                                                                                                            |

| Pointers and Index Registers                                                                                                                                                                                                                                                                                                                                                                                                                   | . 6-7                                                                                                                                                                                                                            |

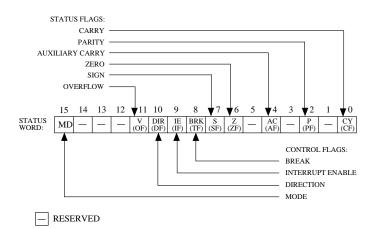

| Program Status Word (PSW) [FL]                                                                                                                                                                                                                                                                                                                                                                                                                 | . 6-8                                                                                                                                                                                                                            |

| V20 ARCHITECTURAL ENHANCEMENTS                                                                                                                                                                                                                                                                                                                                                                                                                 | . 6-9                                                                                                                                                                                                                            |

| Dual Data Bus                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6-9                                                                                                                                                                                                                              |

| Effective Address Generator                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                  |

| 16/32-Bit Temporary Shift Registers (TA,TB)                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                  |

| Loop Counter (LC)                                                                                                                                                                                                                                                                                                                                                                                                                              | 6-10                                                                                                                                                                                                                             |

| Program Counter (PC) and Prefetch Pointer (PFP)                                                                                                                                                                                                                                                                                                                                                                                                | 6-10                                                                                                                                                                                                                             |

| Enhanced and Unique Instructions                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                  |

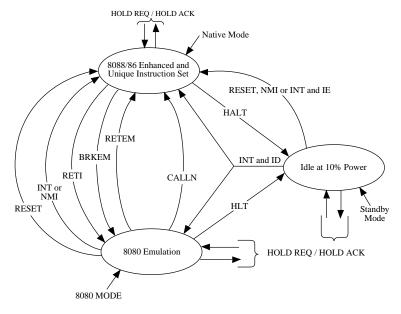

| MODE OPERATIONS - 8080 EMULATION MODE                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                  |

| Break for Emulation (BRKEM)                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                  |

| Return From Emulation (RETEM)                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                  |

| Call Native Routine (CALLN)                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                  |

| Return from Interrupt (RETI)                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                  |

| Register Use in Emulation Mode                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                  |

| DMA SUPPORT                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                  |

| RESET STATE                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                  |

| WAIT-STATE GENERATOR                                                                                                                                                                                                                                                                                                                                                                                                                           | 6-21                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                  |

| Chapter 7. NUMERIC DATA PROCESSOR (8087)                                                                                                                                                                                                                                                                                                                                                                                                       | 7-1                                                                                                                                                                                                                              |

| Chapter 7. NUMERIC DATA PROCESSOR (8087) OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 7-1                                                                                                                                                                                                                            |

| OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 7-1<br>7-3                                                                                                                                                                                                                     |

| OVERVIEW<br>zSBC 337 PIGGYBACK PROCESSOR                                                                                                                                                                                                                                                                                                                                                                                                       | . 7-1<br>7-3<br>. 7-4                                                                                                                                                                                                            |

| OVERVIEW<br>zSBC 337 PIGGYBACK PROCESSOR<br>INSTALLING THE zSBC 337<br>COPROCESSOR INTERFACE<br>MEMORY ADDRESSING                                                                                                                                                                                                                                                                                                                              | . 7-1<br>7-3<br>. 7-4<br>. 7-7<br>. 7-8                                                                                                                                                                                          |

| OVERVIEW<br>zSBC 337 PIGGYBACK PROCESSOR<br>INSTALLING THE zSBC 337<br>COPROCESSOR INTERFACE                                                                                                                                                                                                                                                                                                                                                   | . 7-1<br>7-3<br>. 7-4<br>. 7-7<br>. 7-8                                                                                                                                                                                          |

| OVERVIEW<br>zSBC 337 PIGGYBACK PROCESSOR<br>INSTALLING THE zSBC 337<br>COPROCESSOR INTERFACE<br>MEMORY ADDRESSING                                                                                                                                                                                                                                                                                                                              | . 7-1<br>7-3<br>. 7-4<br>. 7-7<br>. 7-8<br>. 7-9                                                                                                                                                                                 |

| OVERVIEW<br>zSBC 337 PIGGYBACK PROCESSOR<br>INSTALLING THE zSBC 337<br>COPROCESSOR INTERFACE<br>MEMORY ADDRESSING<br>INTERRUPT/NUMERIC ERRORS                                                                                                                                                                                                                                                                                                  | . 7-1<br>7-3<br>. 7-4<br>. 7-7<br>. 7-8<br>. 7-9                                                                                                                                                                                 |

| OVERVIEW .<br>zSBC 337 PIGGYBACK PROCESSOR .<br>INSTALLING THE zSBC 337 .<br>COPROCESSOR INTERFACE .<br>MEMORY ADDRESSING .<br>INTERRUPT/NUMERIC ERRORS .<br>REFERENCES .<br>Chapter 8. SERIAL COMMUNICATIONS (16C452)                                                                                                                                                                                                                         | . 7-1<br>7-3<br>. 7-4<br>. 7-7<br>. 7-8<br>. 7-9<br>7-13<br><b>8-1</b>                                                                                                                                                           |

| OVERVIEW .<br>zSBC 337 PIGGYBACK PROCESSOR .<br>INSTALLING THE zSBC 337 .<br>COPROCESSOR INTERFACE .<br>MEMORY ADDRESSING .<br>INTERRUPT/NUMERIC ERRORS .<br>REFERENCES .<br>Chapter 8. SERIAL COMMUNICATIONS (16C452)<br>OVERVIEW .                                                                                                                                                                                                           | . 7-1<br>7-3<br>. 7-4<br>. 7-7<br>. 7-8<br>. 7-9<br>7-13<br><b>8-1</b><br>. 8-2                                                                                                                                                  |

| OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                       | <ul> <li>7-1</li> <li>7-3</li> <li>7-4</li> <li>7-7</li> <li>7-8</li> <li>7-9</li> <li>7-13</li> <li>8-1</li> <li>8-2</li> <li>8-3</li> </ul>                                                                                    |

| OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 7-1<br>7-3<br>. 7-4<br>. 7-7<br>. 7-8<br>. 7-9<br>7-13<br><b>8-1</b><br>. 8-2<br>. 8-3<br>. 8-8                                                                                                                                |

| OVERVIEW .<br>zSBC 337 PIGGYBACK PROCESSOR .<br>INSTALLING THE zSBC 337 .<br>COPROCESSOR INTERFACE .<br>MEMORY ADDRESSING .<br>INTERRUPT/NUMERIC ERRORS .<br>REFERENCES .<br><b>Chapter 8. SERIAL COMMUNICATIONS (16C452)</b><br>OVERVIEW .<br>SERIAL COMMUNICATIONS PROTOCOL .<br>SERIAL INTERFACE (RS-232-C/422/485) .<br>RS-232-C vs. RS-422/485 .                                                                                          | . 7-1<br>7-3<br>. 7-4<br>. 7-7<br>. 7-8<br>. 7-9<br>7-13<br><b>8-1</b><br>. 8-2<br>. 8-3<br>. 8-8<br>8-10                                                                                                                        |

| OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 7-1<br>7-3<br>. 7-4<br>. 7-7<br>. 7-8<br>. 7-9<br>7-13<br><b>8-1</b><br>. 8-2<br>. 8-3<br>. 8-8<br>8-10<br>8-11                                                                                                                |

| OVERVIEW .<br>zSBC 337 PIGGYBACK PROCESSOR .<br>INSTALLING THE zSBC 337 .<br>COPROCESSOR INTERFACE .<br>MEMORY ADDRESSING .<br>INTERRUPT/NUMERIC ERRORS .<br>REFERENCES .<br><b>Chapter 8. SERIAL COMMUNICATIONS (16C452)</b><br>OVERVIEW .<br>SERIAL COMMUNICATIONS PROTOCOL .<br>SERIAL INTERFACE (RS-232-C/422/485) .<br>RS-232-C vs. RS-422/485 .<br>Signal Definitions .                                                                  | . 7-1<br>7-3<br>. 7-4<br>. 7-7<br>. 7-8<br>. 7-9<br>7-13<br><b>8-1</b><br>. 8-2<br>. 8-3<br>. 8-8<br>8-10<br>8-11                                                                                                                |

| OVERVIEW .<br>zSBC 337 PIGGYBACK PROCESSOR .<br>INSTALLING THE zSBC 337 .<br>COPROCESSOR INTERFACE .<br>MEMORY ADDRESSING .<br>INTERRUPT/NUMERIC ERRORS .<br>REFERENCES .<br><b>Chapter 8. SERIAL COMMUNICATIONS (16C452)</b><br>OVERVIEW .<br>SERIAL COMMUNICATIONS PROTOCOL .<br>SERIAL INTERFACE (RS-232-C/422/485) .<br>RS-232-C vs. RS-422/485 .<br>Signal Definitions .<br>SERIAL REGISTERS .                                            | <ul> <li>7-1</li> <li>7-3</li> <li>7-4</li> <li>7-7</li> <li>7-8</li> <li>7-9</li> <li>7-13</li> <li>8-1</li> <li>8-2</li> <li>8-8</li> <li>8-10</li> <li>8-11</li> <li>8-16</li> <li>8-20</li> </ul>                            |

| OVERVIEW .<br>zSBC 337 PIGGYBACK PROCESSOR .<br>INSTALLING THE zSBC 337 .<br>COPROCESSOR INTERFACE .<br>MEMORY ADDRESSING .<br>INTERRUPT/NUMERIC ERRORS .<br>REFERENCES .<br><b>Chapter 8. SERIAL COMMUNICATIONS (16C452)</b><br>OVERVIEW .<br>SERIAL COMMUNICATIONS PROTOCOL .<br>SERIAL INTERFACE (RS-232-C/422/485) .<br>RS-232-C vs. RS-422/485 .<br>Signal Definitions .<br>SERIAL REGISTERS .<br>Transmit and Receive Buffer Registers . | <ul> <li>7-1</li> <li>7-3</li> <li>7-4</li> <li>7-7</li> <li>7-8</li> <li>7-9</li> <li>7-13</li> <li>8-1</li> <li>8-2</li> <li>8-3</li> <li>8-8</li> <li>8-10</li> <li>8-11</li> <li>8-16</li> <li>8-20</li> <li>8-20</li> </ul> |

| Line Status Register                      | 8-26  |

|-------------------------------------------|-------|

| Interrupt ID Register                     | 8-28  |

| Interrupt Enable Register                 | 8-30  |

| Modem Control Register                    | 8-31  |

| Modem Status Register                     | 8-33  |

| Chapter 9. CENTRONICS PRINTER INTERFACE   | 9-1   |

| OVERVIEW                                  |       |

| PRINTER PORT OUTPUT CHARACTERISTICS       | . 9-3 |

| USING THE PRINTER PORT                    |       |

| REGISTER DEFINITIONS/ADDRESSES            |       |

| Data Port                                 |       |

| Status Port                               |       |

| Control Port                              |       |

| DISABLING SHARING OF PRINTER PORT SIGNALS |       |

| OPTIONAL PRINTER CABLE PINOUT             |       |

| PRINTER PORT RESET STATE                  | 9-15  |

| Chapter 10. REAL-TIME CLOCK (DS 1215)     | 10-1  |

| OVERVIEW                                  | 10-1  |

| OPERATION                                 | 10-3  |

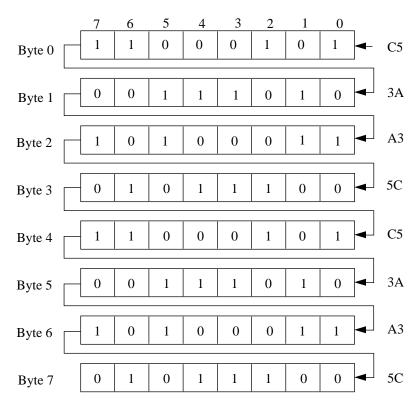

| TIMECHIP COMPARISON REGISTER DEFINITION   | 10-5  |

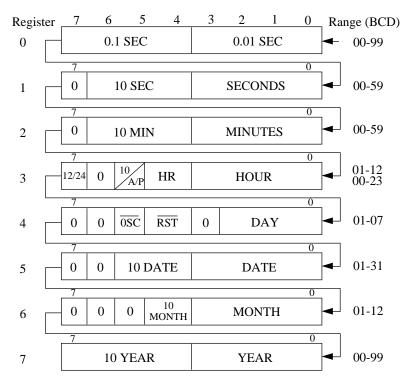

| TIMEKEEPER REGISTER INFORMATION           | 10-6  |

| TIMECHIP REGISTER DEFINITION              | 10-7  |

| AM/PM 12/24-Hour Mode                     | 10-8  |

| Oscillator and Reset Bits                 | 10-8  |

| Zero Bits                                 | 10-8  |

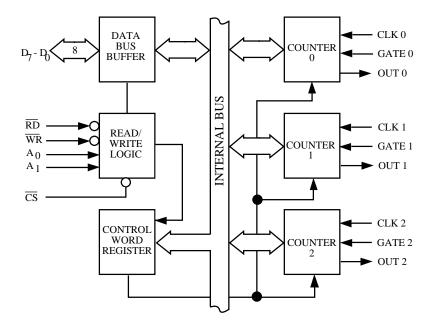

| Chapter 11. COUNTER/TIMERS (8254)         | 11-1  |

| OVERVIEW                                  | 11-2  |

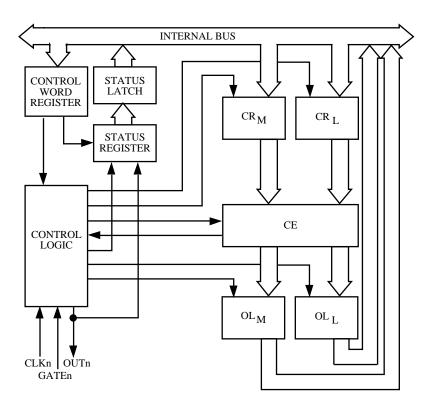

| BLOCK DIAGRAM                             | 11-3  |

| COUNTER/TIMER ARCHITECTURE                | 11-4  |

| OPERATION                                 | 11-6  |

| Reset State                               | 11-6  |

| Programming                               | 11-6  |

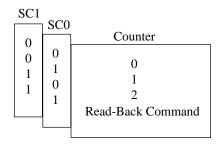

| Read Operations                           |       |

| Mode Definitions                          |       |

| Operation Common to All Modes             |       |

| Counter Use by STD DOS and STD ROM        | 11-25 |

| Chapter 12. INTERRUPT CONTROLLER (8259A)   | 12-1    |

|--------------------------------------------|---------|

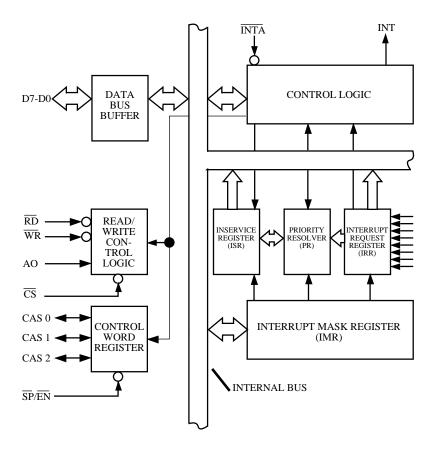

| OVERVIEW                                   | 12-3    |

| I/O PORT ADDRESSES                         |         |

| OPERATION OVERVIEW                         |         |

| FUNCTIONAL DESCRIPTION                     |         |

| Interrupt Request Register (IRR)           |         |

| Interrupt Mask Register (IMR)              | 12-8    |

| Priority Resolver (PR)                     | 12-9    |

| Interrupt In-Service Register (ISR)        |         |

| Control Logic                              | 12-9    |

| Read/Write Control Logic                   | . 12-10 |

| Initialization and Operation Registers     | . 12-10 |

| Cascade Buffer/Comparator                  |         |

| PROGRAMMABLE REGISTERS                     |         |

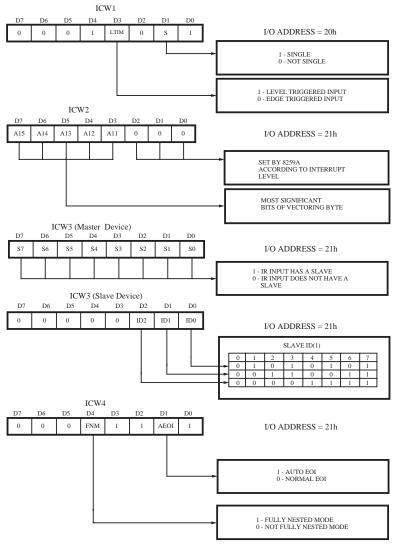

| Initialization Control Words (ICW1-4)      | . 12-12 |

| Operation Control Words (OCW1-3)           | 12-16   |

| 8259A I/O PORT ADDRESSES                   | . 12-21 |

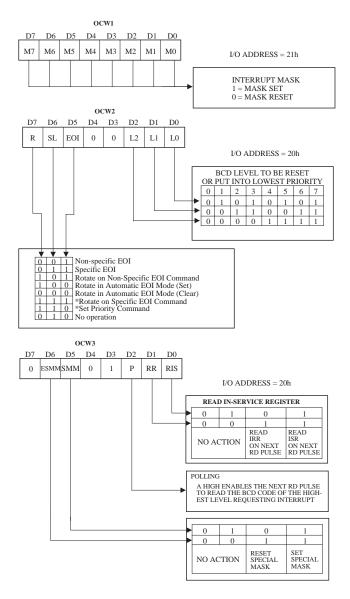

| INTERRUPT ASSIGNMENTS ON THE ZT 8809A      | . 12-22 |

| OPERATION OF THE INTERRUPT CONTROLLER      | . 12-24 |

| Priorities                                 | . 12-24 |

| Interrupt Triggering                       | 12-27   |

| Interrupt Status                           |         |

| EOI COMMANDS                               | . 12-31 |

| Nonspecific EOI Commands                   | 12-31   |

| Specific EOI Commands                      |         |

| Automatic EOI Mode                         |         |

| RESET                                      |         |

| Chapter 13. ZT 88CT08A/88CT09A CMOS BOARDS | 13-1    |

| OVERVIEW                                   |         |

| FUNCTIONAL DIFFERENCES                     |         |

| Logic Family (CT vs. C)                    |         |

| Use of 80C88 Processor                     |         |

| Addition of Optional 8087(-2)              |         |

| Clock Slowdown Mode                        |         |

|                                            |         |

| Halt With Restart Via Interrupt            |         |

| ELECTRICAL/ENVIRONMENTAL DIFFERENCES       |         |

| Increased Temperature Range                |         |

| Reduced Power Consumption                  |         |

| Bus Loading                                | 13-9    |

### IV. APPENDICES

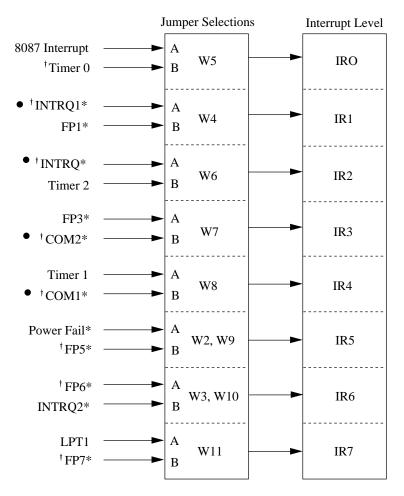

| Appendix A. JUMPER CONFIGURATIONS                                                                                                                                                                                                                                             | A-1                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| OVERVIEW                                                                                                                                                                                                                                                                      | A-1                                                                               |

| JUMPER DESCRIPTIONS                                                                                                                                                                                                                                                           | A-3                                                                               |

| Appendix B. SPECIFICATIONS                                                                                                                                                                                                                                                    | B-1                                                                               |

| OVERVIEW                                                                                                                                                                                                                                                                      |                                                                                   |

| ELECTRICAL AND ENVIRONMENTAL                                                                                                                                                                                                                                                  | B-2                                                                               |

| Absolute Maximum Ratings                                                                                                                                                                                                                                                      | <b>B-2</b>                                                                        |

| DC Operating Characteristics                                                                                                                                                                                                                                                  |                                                                                   |

| Battery Backup Characteristics                                                                                                                                                                                                                                                |                                                                                   |

| STD Bus Loading Characteristics                                                                                                                                                                                                                                               | B-3                                                                               |

| MECHANICAL                                                                                                                                                                                                                                                                    |                                                                                   |

| CONNECTORS                                                                                                                                                                                                                                                                    |                                                                                   |

| CABLES                                                                                                                                                                                                                                                                        |                                                                                   |

| TIMINC                                                                                                                                                                                                                                                                        | D 02                                                                              |

| TIMING                                                                                                                                                                                                                                                                        | B-23                                                                              |

| Appendix C. CUSTOMER SUPPORT                                                                                                                                                                                                                                                  | в-23<br>С-1                                                                       |

|                                                                                                                                                                                                                                                                               | C-1                                                                               |

| Appendix C. CUSTOMER SUPPORT                                                                                                                                                                                                                                                  | <b>C-1</b><br>C-1                                                                 |

| Appendix C. CUSTOMER SUPPORT<br>OVERVIEW                                                                                                                                                                                                                                      | <b>C-1</b><br>C-1<br>C-2                                                          |

| Appendix C. CUSTOMER SUPPORT<br>OVERVIEW                                                                                                                                                                                                                                      | C-1<br>C-1<br>C-2<br>C-2                                                          |

| Appendix C. CUSTOMER SUPPORT<br>OVERVIEW<br>TROUBLESHOOTING<br>Powering Up STD ROM<br>Powering Up STD DOS<br>ZT 8808A/8809A REVISION HISTORY                                                                                                                                  | C-1<br>C-2<br>C-2<br>C-2<br>C-4<br>C-8                                            |

| Appendix C. CUSTOMER SUPPORT<br>OVERVIEW                                                                                                                                                                                                                                      | C-1<br>C-2<br>C-2<br>C-4<br>C-8<br>C-8                                            |

| Appendix C. CUSTOMER SUPPORT<br>OVERVIEW                                                                                                                                                                                                                                      | C-1<br>C-2<br>C-2<br>C-4<br>C-8<br>C-8<br>C-8<br>C-8                              |

| Appendix C. CUSTOMER SUPPORT<br>OVERVIEW .<br>TROUBLESHOOTING .<br>Powering Up STD ROM .<br>Powering Up STD DOS .<br>ZT 8808A/8809A REVISION HISTORY .<br>Revision 0 - Original Release of Board, 12/17/91 .<br>Revision A - 8/19/92 .<br>ZT 88CT08A/88CT09A REVISION HISTORY | C-1<br>C-2<br>C-2<br>C-4<br>C-8<br>C-8<br>C-8<br>C-8<br>C-8                       |

| Appendix C. CUSTOMER SUPPORT<br>OVERVIEW                                                                                                                                                                                                                                      | C-1<br>C-2<br>C-2<br>C-4<br>C-8<br>C-8<br>C-8<br>C-8<br>C-8<br>C-8<br>C-8         |

| Appendix C. CUSTOMER SUPPORT<br>OVERVIEW                                                                                                                                                                                                                                      | C-1<br>C-2<br>C-2<br>C-4<br>C-8<br>C-8<br>C-8<br>C-8<br>C-8<br>C-8<br>C-9<br>C-10 |

| Appendix C. CUSTOMER SUPPORT<br>OVERVIEW                                                                                                                                                                                                                                      | C-1<br>C-2<br>C-2<br>C-4<br>C-8<br>C-8<br>C-8<br>C-8<br>C-8<br>C-8<br>C-8         |

## **TABLES**

| Table 3–1  | Processor Speed Comparison.                | 3-3          |

|------------|--------------------------------------------|--------------|

| Table 3–2  | Serial Communications Standards.           | 3-7          |

| Table 5–1  | Memory Configurations, 3D1/5D1/BRAM        | 5-12         |

| Table 5–2  | Memory Configurations, 7D1/9D1             | 5-13         |

| Table 5–3  | Device Access Times.                       | 5-14         |

| Table 6–1  | Segment Registers.                         | 6-4          |

| Table 6–2  | 8080 Emulation Register Use.               | 6-16         |

| Table 6–3  | Memory Access Times.                       |              |

| Table 7–1  | Queue-Status Line Functions.               | 7-7          |

| Table 8–1  | 16C452 Reset State.                        | 8-14         |

| Table 8–2  | ZT 8809A I/O Port Assignments.             | 8-17         |

| Table 8–3  | 16C452 Addressable Registers Summary.      | 8-18         |

| Table 8–4  | Baud Rate Table.                           | 8-25         |

| Table 8–5  | 16C452 Interrupt Control Functions.        | 8-28         |

| Table 9–1  | 16C452 Printer Port Output Characteristics | 9-3          |

| Table 9–2  | Parallel Port Register Definitions.        | 9-5          |

| Table 9–3  | Parallel Port Register Addresses.          | 9-5          |

| Table 9–4  | Shared Printer Signals.                    | 9-13         |

| Table 9–5  | ZT 90039 Cable Pinout.                     | 9-14         |

| Table 11–1 | Read-Back Command Example.                 | 11-15        |

| Table 11–2 | Gate Pin Operations Summary.               | 11-22        |

| Table 11–3 | Minimum and Maximum Initial Counts         | 11-24        |

| Table 12–1 | PIC Registers.                             | 12-11        |

| Table A-1  | Jumper Descriptions                        | A-3          |

| Table A–2  | Memory Addressing, W55-W59                 | A-42         |

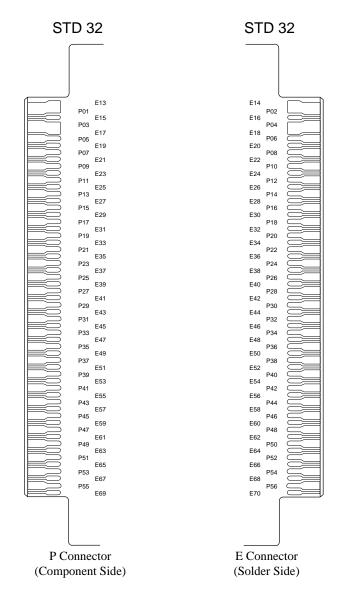

| Table B-1  | STD Bus Signal Loading, P Connector.       | <b>B-</b> 4  |

| Table B–2  | STD Bus Signal Loading, E Connector.       | B-5          |

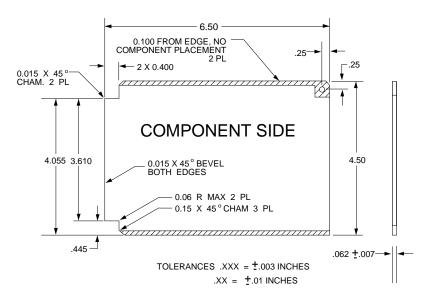

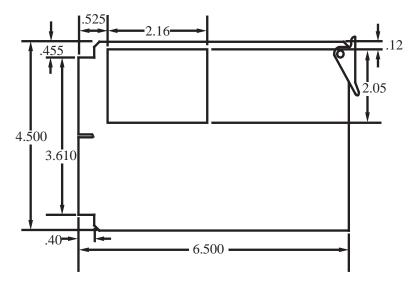

| Table B–3  | Mechanical Specifications.                 | B-7          |

| Table B–4  | J1 Pin Assignments (RS-232-C).             |              |

| Table B–5  | J2 Pin Assignments (RS-232-C).             | <b>B-</b> 14 |

| Table B–6  | J2 Pin Assignments (RS-422/485)            | B-15         |

| Table B–7  | J3 Pin Assignments.                        | B-16         |

| Table B–8  | J4 Pin Assignments.                        | B-17         |

|            |                                            |              |

| Table B–9  | J5 Pin Assignments. | B-17 |

|------------|---------------------|------|

| Table B–10 | J6 Pin Assignments. | B-18 |

| Table B–11 | J7 Pin Assignments. | B-19 |

## ILLUSTRATIONS

| Figure 1–1  | ZT 8809A Functional Block Diagram.            | 1-5  |

|-------------|-----------------------------------------------|------|

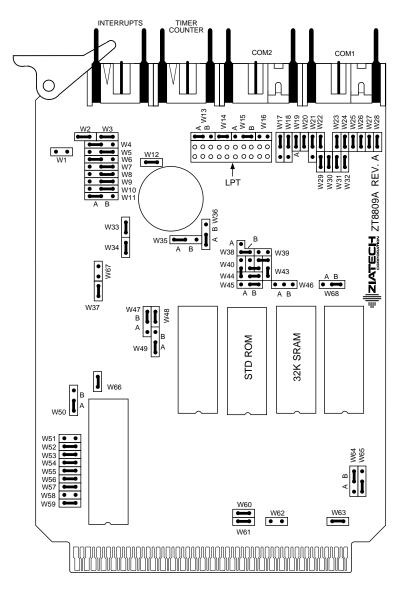

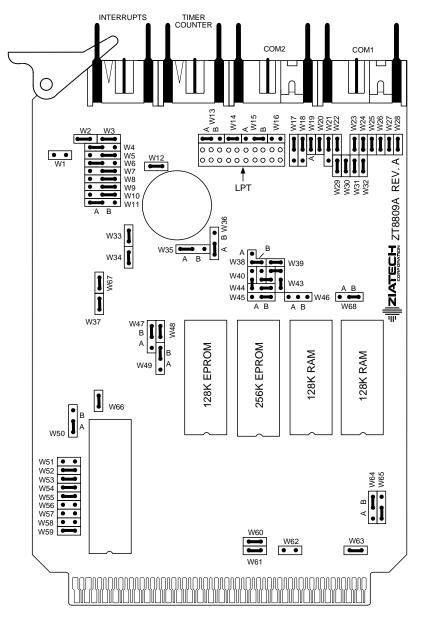

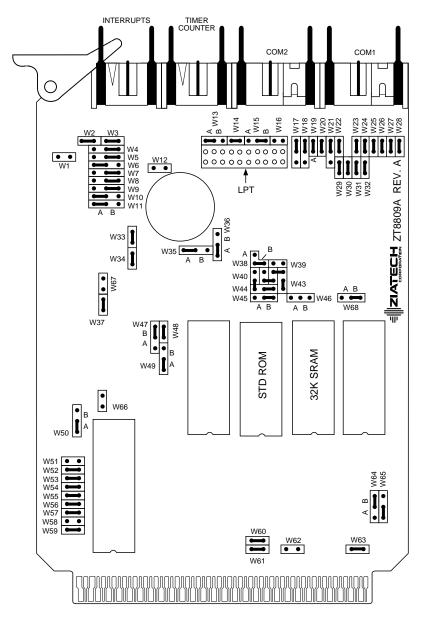

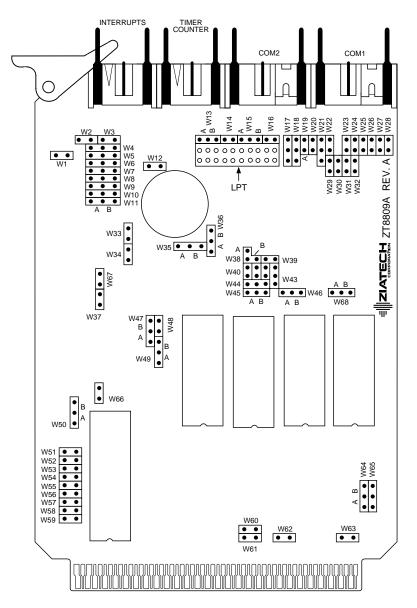

| Figure 2–1  | Non-DOS Factory Default Jumper Configuration  | 2-8  |

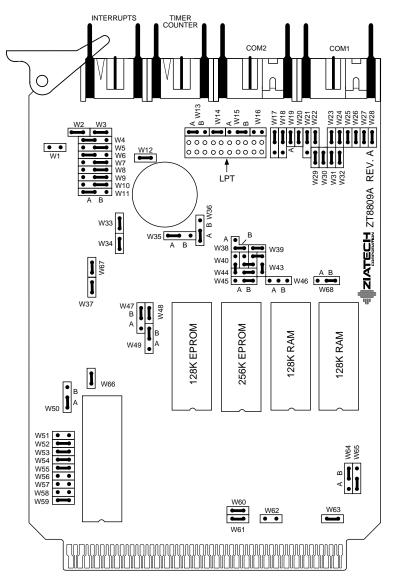

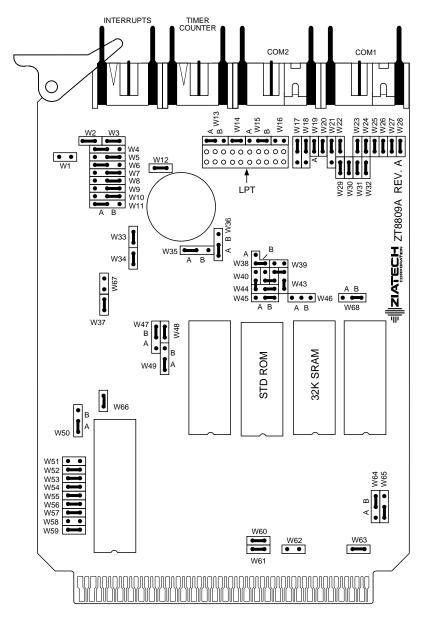

| Figure 2–2  | ZT 8809A Configured For STD DOS.              | 2-14 |

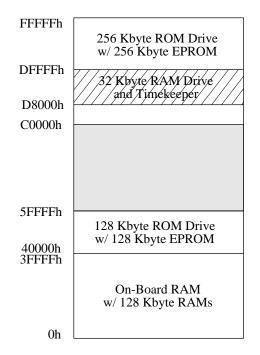

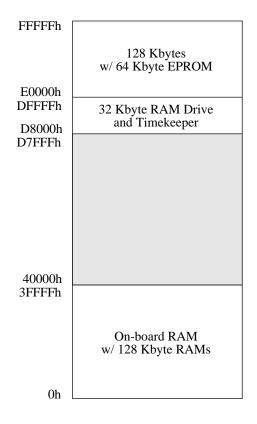

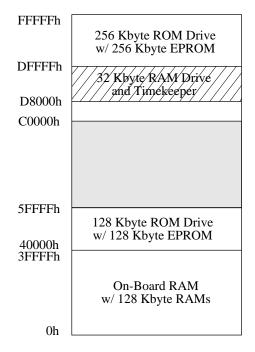

| Figure 2–3  | STD DOS Factory Default Memory Map.           | 2-20 |

| Figure 2–4  | STD ROM Factory Default Memory Map            | 2-21 |

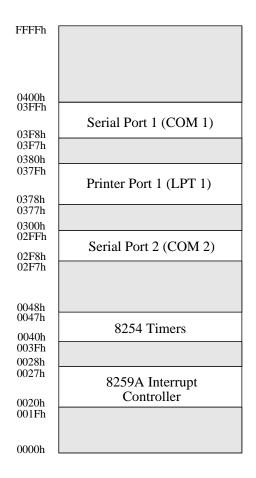

| Figure 2–5  | I/O Map, STD DOS / STD ROM Systems            | 2-23 |

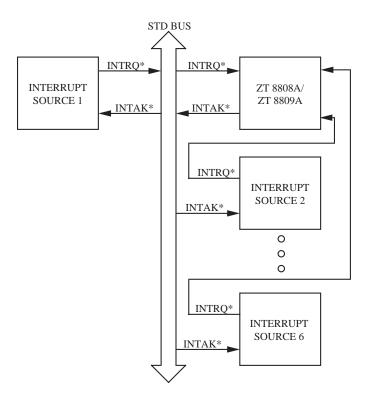

| Figure 3–1  | PIC Interrupt Input Requests.                 | 3-9  |

| Figure 3–2  | Polled Interrupt Structure.                   | 3-11 |

| Figure 3–3  | Small Scale Vectored Structure.               | 3-12 |

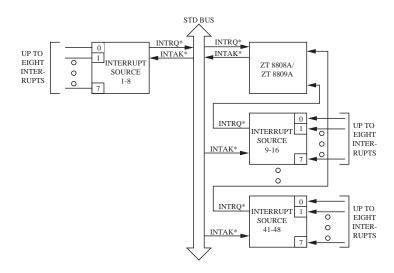

| Figure 3–4  | Large Scale Vectored Structure.               | 3-13 |

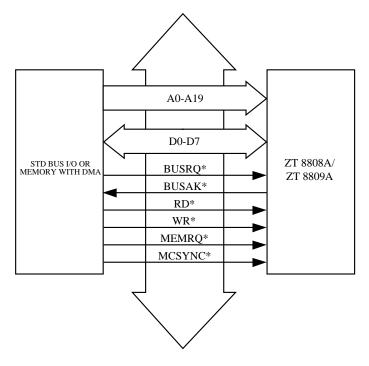

| Figure 3–5  | DMA With STD Bus Controller.                  | 3-17 |

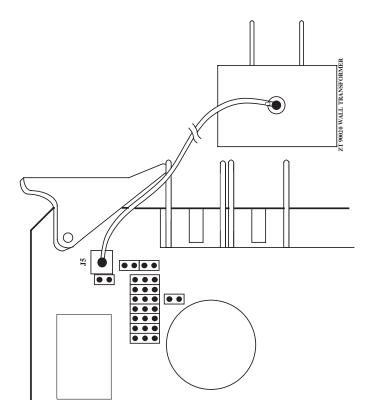

| Figure 3–6  | AC Transformer Connection.                    | 3-19 |

| Figure 5–1  | STD DOS Factory Default Memory Map.           | 5-4  |

| Figure 5–2  | STD DOS Factory Default Jumper Configuration. | 5-5  |

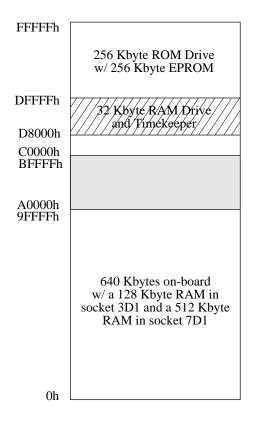

| Figure 5–3  | STD DOS Map with 640K On-Board RAM            | 5-6  |

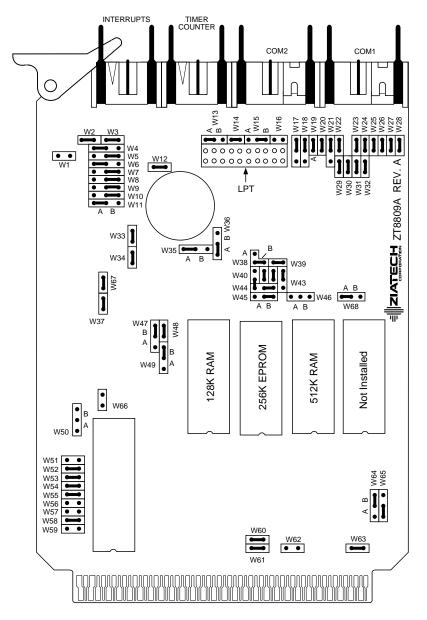

| Figure 5–4  | STD DOS With 640K RAM Jumper Configuration.   | 5-7  |

| Figure 5–5  | Non-DOS Factory Default Memory Map            | 5-8  |

| Figure 5–6  | Non-DOS Factory Default Jumper Configuration  | 5-9  |

| Figure 5–7  | Memory Chip Locations.                        | 5-11 |

| Figure 5–8  | ZT 8809A I/O Map                              | 5-16 |

| Figure 6–1  | Program Status Word.                          |      |

| Figure 6–2  | V20 Modes                                     | 6-13 |

| Figure 6–3  | DMA With STD Bus Controller.                  | 6-19 |

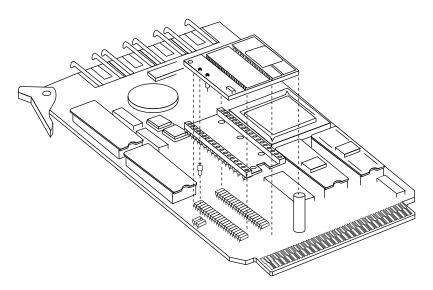

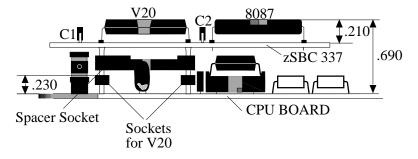

| Figure 7–1  | zSBC 337 Piggyback Processor Installation     | 7-6  |

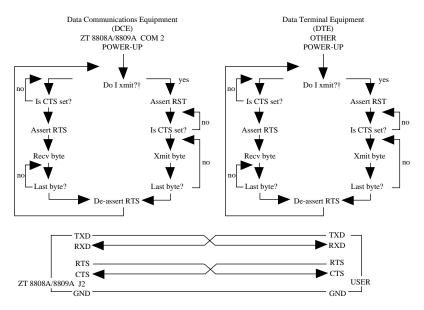

| Figure 8–1  | Establishing Serial Communications.           | 8-5  |

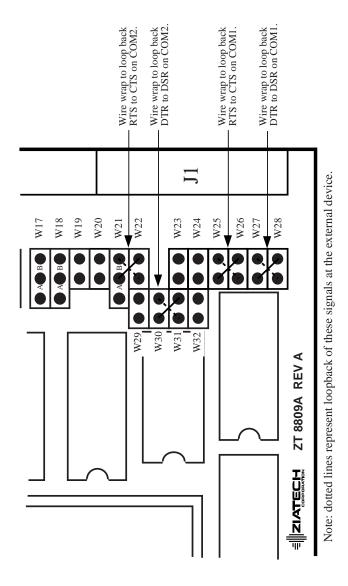

| Figure 8–2  | Loopback of RTS/CTS, DTR/DSR                  | 8-7  |

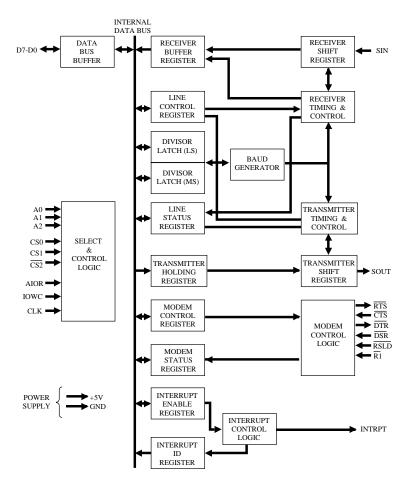

| Figure 8–3  | 16C452 Serial Port Block Diagram.             | 8-9  |

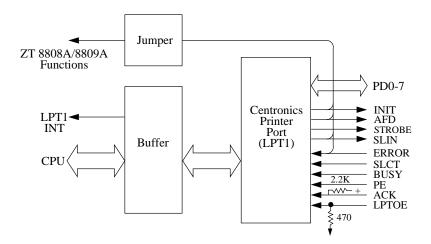

| Figure 9–1  | Printer Interface Block Diagram.              | 9-2  |

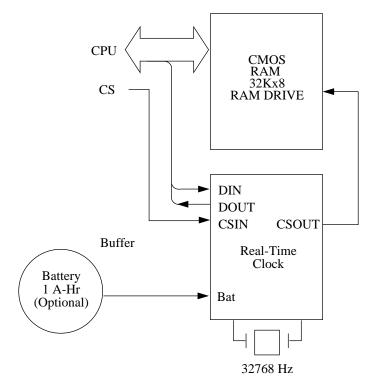

| Figure 10–1 | Real-Time Clock Block Diagram.                | 10-2 |

| Figure 10–2 | Timechip Comparison Register.                 | 10-5 |

| Figure 10–3 | Timechip Register.                            |      |

| Figure 11–1 | Intel 8254 Timers Block Diagram.              |      |

| Figure 11–2 | Internal Block Diagram of a Counter.          | 11-4 |

| Figure 11–3 | Control Word Format.                         | 11-7  |

|-------------|----------------------------------------------|-------|

| Figure 11–4 | Counter Latch Command Format.                | 11-9  |

| Figure 11–5 | Counter Status Format.                       | 11-12 |

| Figure 11–6 | Null Count Operation.                        | 11-13 |

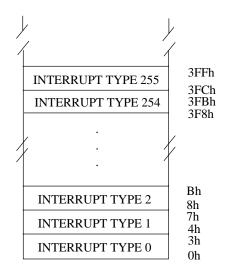

| Figure 12–1 | V20 Interrupt Vector Table.                  | 12-5  |

| Figure 12–2 | 8259A Block Diagram.                         | 12-7  |

| Figure 12–3 | 8259A ICW Formats.                           | 12-13 |

| Figure 12–4 | 8259A Operation Control Word Formats.        | 12-17 |

| Figure 12–5 | 8259A Interrupts.                            | 12-23 |

| Figure A–1  | W1 - W12 Jumper Block.                       | . A-2 |

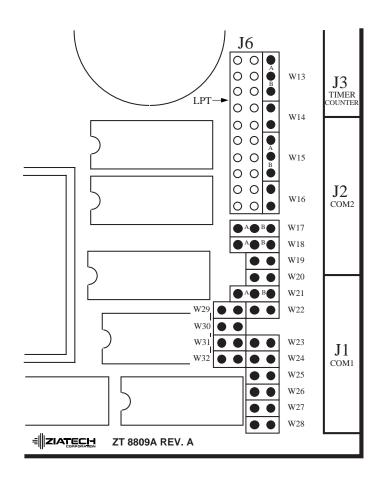

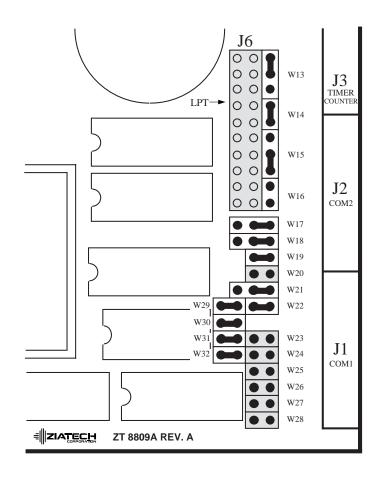

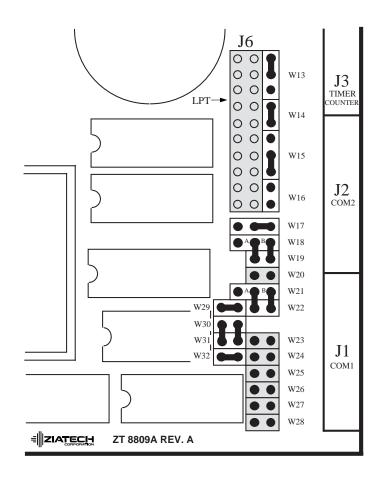

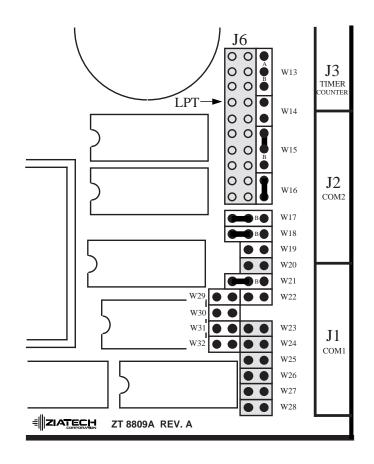

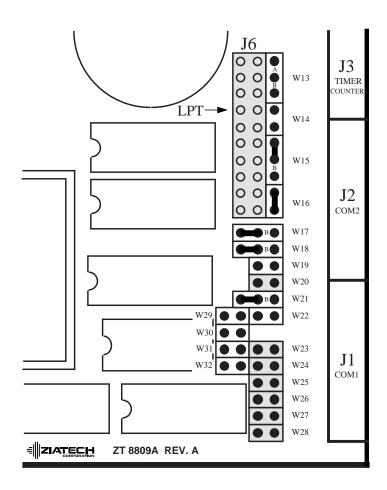

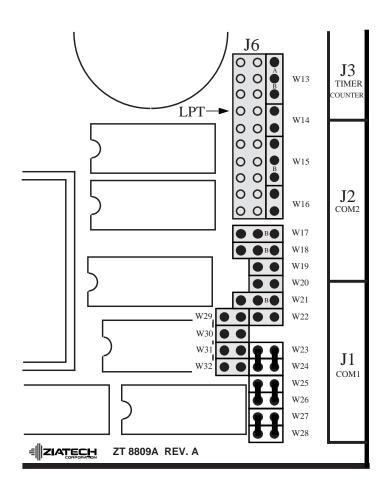

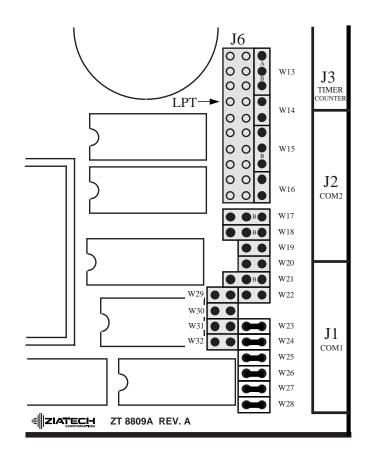

| Figure A–2  | W13 - W32 Jumper Block.                      | A-11  |

| Figure A–3  | COM2 Configured as RS-232-C DCE.             | A-18  |

| Figure A–4  | COM2 Configured as RS-232-C DTE.             | A-19  |

| Figure A–5  | COM2 Configured as RS-422 DCE.               | A-20  |

| Figure A–6  | COM2 Configured for RS-485 Operation.        | A-21  |

| Figure A–7  | COM1 Configured for DTE Operation.           | A-23  |

| Figure A–8  | COM1 Configured for DCE Operation.           | A-24  |

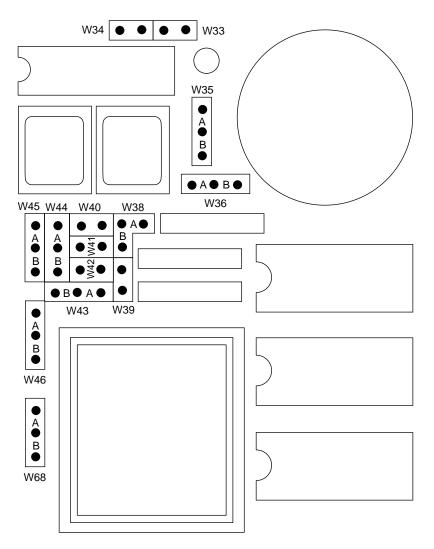

| Figure A–9  | W33-W36, W38-W46, W68 Jumper Blocks          | A-26  |

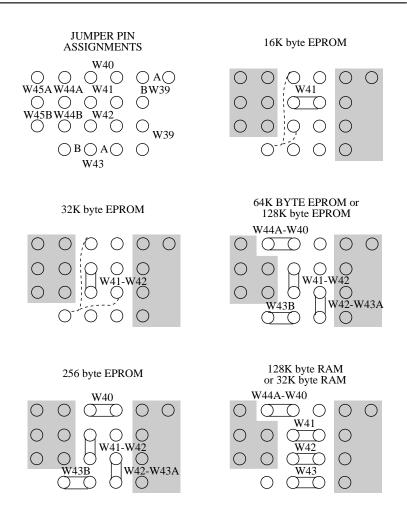

| Figure A–10 | Socket 3D1 Configuration.                    |       |

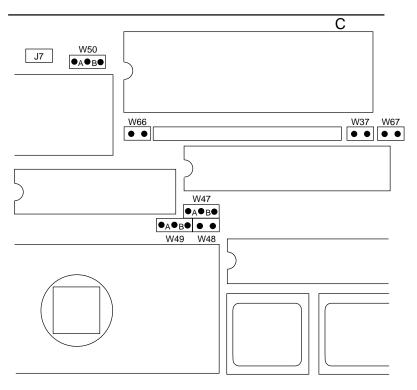

| Figure A–11 | W37, W47-50, W66-W67 Jumper Blocks           | A-34  |

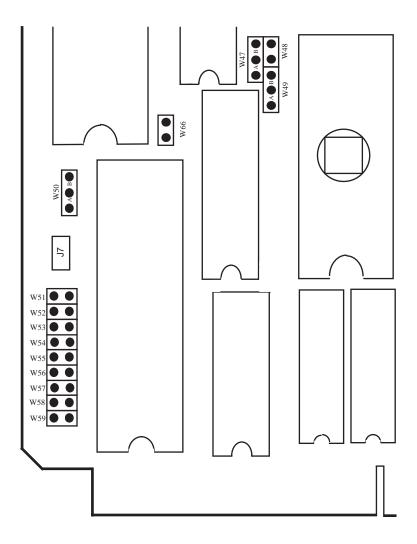

| Figure A–12 | W51 - W59 Jumper Block.                      | A-37  |

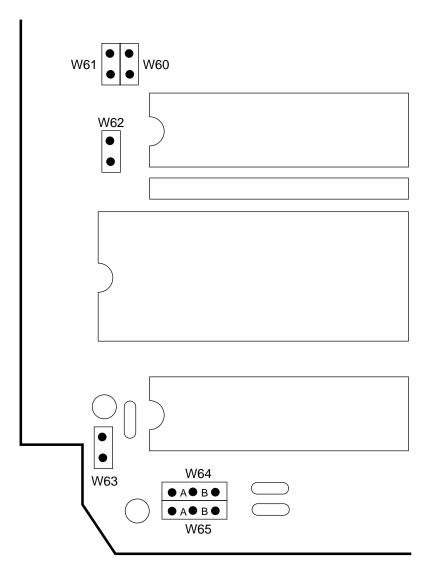

| Figure A–13 | W60 - W65 Jumper Block.                      | A-46  |

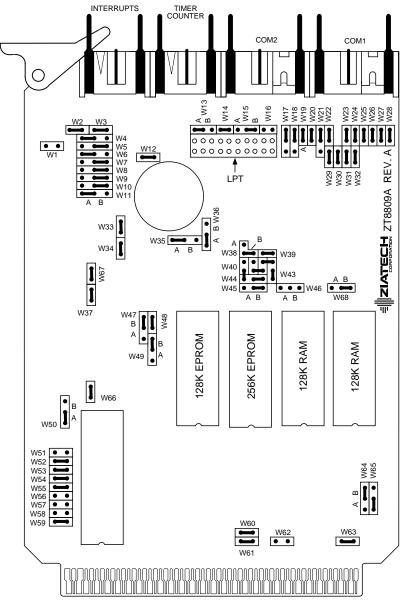

| Figure A–14 | ZT 8809A User Configuration.                 | A-54  |

| Figure A–15 | Non-DOS Factory Default Jumper Configuration | A-55  |

| Figure A–16 | ZT 8809A Configured for STD DOS.             | A-56  |

| Figure B–1  | Board Dimensions Without zSBC 337            | . B-7 |

| Figure B–2  | Board Dimensions With zSBC 337               | . B-8 |

| Figure B–3  | P/E Connector Pinout.                        | B-11  |

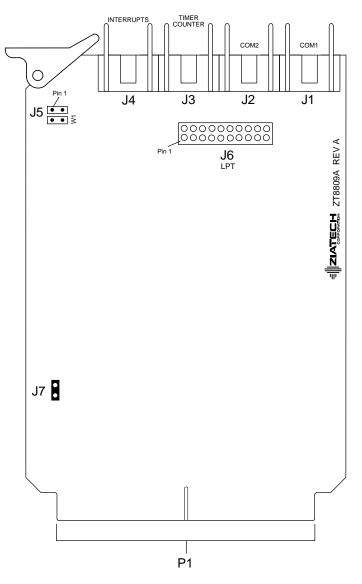

| Figure B–4  | ZT 8809A Connector Locations.                | B-12  |

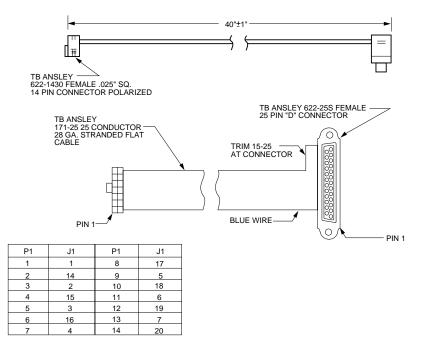

| Figure B–5  | ZT 90014 Cable Drawing.                      | B-20  |

| Figure B–6  | ZT 90027 Cable Drawing.                      | B-21  |

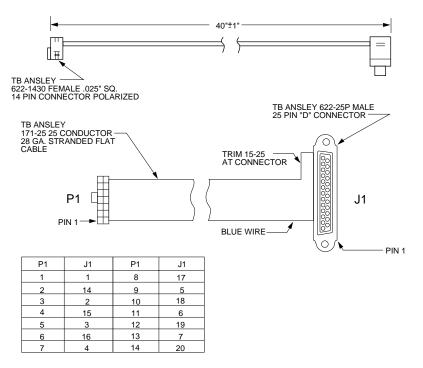

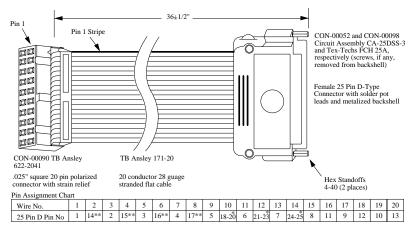

| Figure B–7  | ZT 90039 Cable Drawing.                      | B-22  |

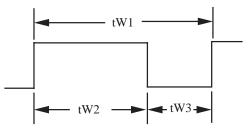

| Figure B–8  | ZT 8809A CLOCK* Timing.                      | B-23  |

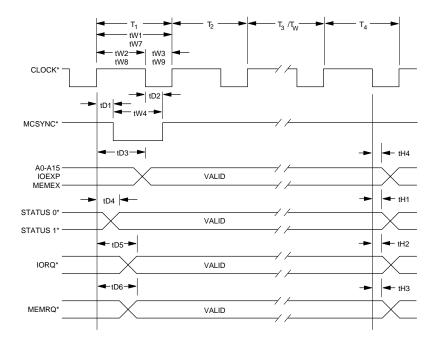

| Figure B–9  | ZT 8809A Status Timing.                      | B-24  |

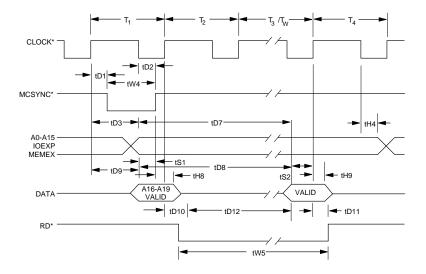

| Figure B–10 | ZT 8809A Read Timing.                        | B-25  |

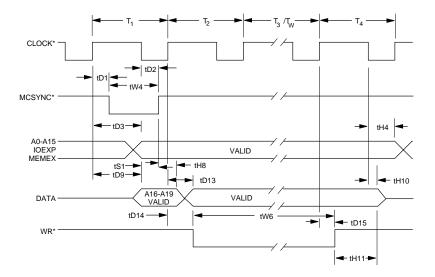

| Figure B–11 | ZT 8809A Write Timing.                       | B-26  |

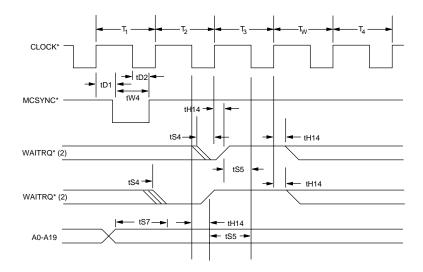

| Figure B–12 | ZT 8809A Wait Request Timing.                | B-27  |

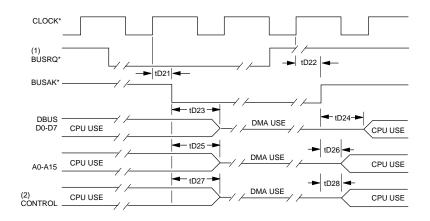

| Figure B–13 | ZT 8809A Bus Exchange Timing.                | B-28  |

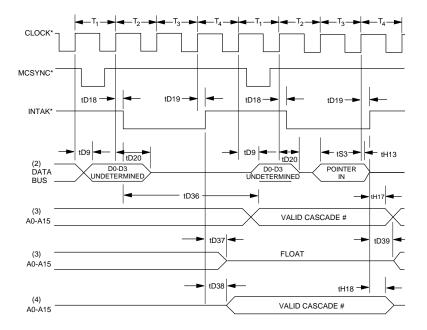

| Figure B–14 | ZT 8809A Interrupt Timing.                   | B-29  |

|             |                                              |       |

#### Chapter 1

## **INTRODUCTION**

#### **Contents** Page ZT 88CT08A and ZT 88CT09A ..... 1-3 FEATURES OF THE ZT 8809A 1-4FUNCTIONAL BLOCKS 1-6Memory and I/O Addressing ..... 1-6 Direct Memory Access (DMA) 1 - 7Optional Battery Backup ..... 1-7 AC/DC Power-Fail Detection 1-8 Real-Time Clock 1-9 Serial Communications 1-9 Counter/Timers ..... 1 - 10Interrupts 1-11 Centronics Printer/General Purpose I/O Port ..... 1-12 Optional Numeric Data Coprocessor (8087)..... 1 - 12Clock Slowdown & Halt Restart (CMOS boards only)..... 1-13

### **OVERVIEW**

The 5 MHz ZT 8808A and 8 MHz ZT 8809A are 16-bit single board computers (SBCs) designed with DOS applications on the STD bus in mind. The high level of integration allows for a complete STD DOS system on one board. All peripherals are located at the same I/O addresses as on the IBM PC®, allowing for a greater degree of software compatibility.

A performance increase over 8088-based STD CPU boards is achieved in part by the use of the NEC V20 microprocessor. This is an 8088 compatible processor with a superset of the 8088 instruction set. The V20 is a CMOS device with a standby mode, which results in lower power consumption.

The ZT 8808A/8809A and 88CT08A/88CT09A boards also provide an increase in memory capacity over the earlier non-"A" versions (ZT 8808/8809 and 88CT08/88CT09). The "A" versions allow up to 640 bytes of static RAM directly on the processor board, thus eliminating the need to use an additional memory board. Increased memory capacity is accomplished by adding support for a 512 Kbyte RAM device in socket 7D1 and placing a 128 Kbyte RAM in socket 3D1 (this configuration assumes no EPROM in socket 3D1). If you have been using an additional memory board (ZT 8824, ZT 8820B, ZT 8825, or other) to achieve 640 Kbytes of system RAM, you may be able to eliminate that memory board from your system by putting more system RAM on the "A" version processor board. However, systems with large RAM and PROM disks on the ZT 8825 will probably still require the ZT 8825.

Peripherals on the ZT 8808A and ZT 8809A include three counter/timers, an interrupt controller, a real-time clock, two RS-232-C serial ports (one of which may be configured to be RS-485), a Centronics printer interface or general purpose parallel I/O port, and four 32-pin memory sockets. The memory sockets may include one EPROM, two RAM, and one additional RAM or EPROM (the last socket is configurable). An additional 32 Kbytes of on-board RAM and a general purpose LED indicator are also provided.

All RAM and the real-time clock may be optionally battery-backed by a 1 Amp-hour lithium battery. DC power failure detection is provided to switch to the battery backup mode during +5 VDC failure. AC power failure detection is possible with the use of an optional AC/DC converter. Detection of AC power failure provides time for the processor to save critical data in battery-backed RAM before impending +5 VDC failure.

#### ZT 88CT08A and ZT 88CT09A

The ZT 88CT08A and ZT 88CT09A are CMOS versions of the ZT 8808A and ZT 8809A, respectively. They are designed for extended temperature and low power applications. All references in this manual to the ZT 8808A and ZT 8809A are also appropriate for the ZT 88CT08A and ZT 88CT09A. Refer to Chapter 13 for information pertaining specifically to the ZT 88CT08A and ZT 88CT09A. Features provided with the CMOS version boards in addition to the standard ZT 8808A/8809A include slow-down and sleep modes.

Software support is provided by Ziatech's STD DOS option and by the STD ROM option. STD DOS includes the MS-DOS operating system for the ZT 8809A. STD ROM provides software debugging capabilities when used in conjunction with an IBM PC. The STD ROM option is useful for applications where no operating system is required for the target system. Contact Ziatech for further information on these development systems.

### FEATURES OF THE ZT 8809A

- STD-80 and STD 32 bus compatible

- Optional CMOS versions available

- 8088/8086 code compatible

- Four 32-pin memory sockets, configurable for

- 1 EPROM and 3 RAMs or

- 2 EPROMs and 2 RAMs

- Acceptable RAM sizes are 32 Kbytes to 512 Kbytes

- Acceptable EPROM sizes 16 Kbytes through 256 Kbytes

- One 32 Kbyte static RAM

- Real-time clock (DS 1215)

- Optional battery backup for all RAM and real-time clock

- AC/DC power-fail protection

- Latching frontplane connectors

- Optional Numeric Data Processor (8087) via zSBC 337

- Wait-state generator

- Interrupt Controller (8259A-2)

- Two RS-232-C serial channels (VL 16C452), one RS-422/485 selectable

- Three Counter/Timers (8254)

- Centronics printer interface or general purpose parallel I/O port (VL 16C452)

- Optional STD DOS operating system software

- Optional STD ROM development/debug software

- Optional cables for Centronics printer interface and serial ports

- Fully tested while cycling temperature from ambient to +55° Celsius to guarantee reliability (to +80° Celsius for ZT 88CT08A/88CT09A)

- Slow-down and sleep modes provided with the ZT 88CT08A/88CT09A

- Two-year warranty on all boards

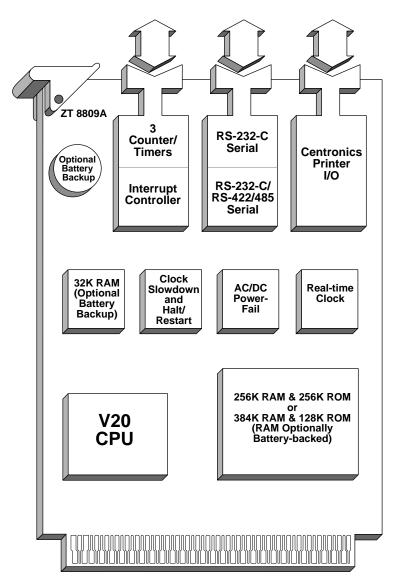

Figure 1–1. ZT 8809A Functional Block Diagram.

## **FUNCTIONAL BLOCKS**

Figure 1-1 illustrates the ZT 8809A's functional blocks. A brief description of each block follows.

#### V20 (uPD70108) Processor

The NEC V20 is an 8088-compatible microprocessor with a 16-bit internal data bus and an 8-bit external data bus. The V20 executes all code written for the 8088/8086 family of microprocessors and includes a superset of their instruction set. Performance enhancements are provided by way of such architectural features as a dual 16-bit internal data bus, high-speed effective address generation, and additional hidden temporary registers. The added instructions include shift and rotate by immediate value, move string, stack manipulations, and 8080 emulation mode. The 8080 emulation mode enables existing 8-bit 8080 software to run on new 16-bit hardware with few or no software modifications.

#### Memory and I/O Addressing

The ZT 8809A comes populated with one 32 Kbyte static RAM and four 32-pin JEDEC compatible byte-wide sockets. Two of the sockets accept 16K through 256 Kbyte EPROMs; the other two accept 32K through 512 Kbyte RAMs. One of the EPROM sockets can also be configured to accept a 32K or 128 Kbyte RAM.

The full 20-bit address is used for both on-board and off-board memory accesses, giving the system 1 Mbyte of direct address space. I/O accesses are accomplished with a 16-bit address, providing 64 Kbytes of I/O space for 16-bit I/O boards or 256 bytes for 8-bit boards.

#### Wait-State Generator

To accommodate I/O and memory boards needing more time for access, the ZT 8809A contains a one wait-state generator. If enabled, it inserts one wait-state (clock cycle) within the normal four-clock bus cycle to increase it to five clocks. This gives memory and I/O boards additional time between address valid time and the end of the bus cycle to complete an access.

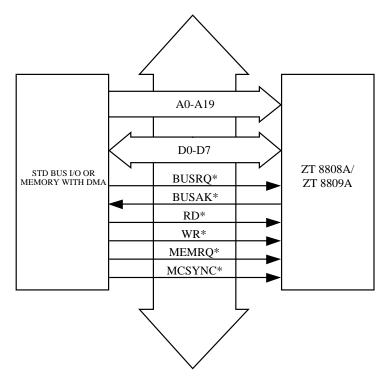

#### **Direct Memory Access (DMA)**

External DMA controllers are supported by the ZT 8809A via the BUSRQ\* (pin 42) and BUSAK\* (pin 41) STD bus control signals. A request for the bus is made to the ZT 8809A via BUSRQ\* pin 42, and the ZT 8809A responds with BUSAK\* once the microprocessor has signaled its release of the bus. When the DMA transfer is complete, the DMA device releases BUSRQ\* and the ZT 8809A then responds by releasing BUSAK\*. DMA is supported on the ZT 8809A for all on-board EPROM and RAM, with the exception of the 32 Kbyte static RAM.

#### **Optional Battery Backup**

All RAM and the real-time clock may be selectively battery-backed with a 3.9 V, 1 Amp-hour lithium battery, which is shipped as a standard option with the ZT 8809A STD DOS systems. When DC power falls below 4.75 V, the battery power is switched in and remains until power is again at that level. At the same time, the DCPWRDWN\* STD bus signal (pin 6) is driven active (low) to warn other boards in the system of low DC voltage.

Jumpers are provided to select whether the following three groups of devices, either individually or as a whole, are to be battery-backed:

- Real-time clock and 32 Kbyte RAM

- Two RAM sockets

- ROM/RAM socket when RAM is present

This conserves battery power exclusively for those devices that require backup.

#### AC/DC Power-Fail Detection

DC power-fail detection senses when DC voltage drops below 4.75 V. This signals the board to switch into battery backup mode, as described above. AC power-fail detection is also available for early warning of impending low DC voltage, to give the processor time to store critical data while DC voltage is still above 4.75 V.

An optional 24 V transformer is available from Ziatech (ZT 90020) to monitor the same AC source supplying the STD bus card cage, and may be attached to the ZT 8809A via the frontplane. Upon detection of AC voltage falling below 90 VAC, a non-maskable interrupt (NMIRQ\*) is sent to the CPU to prepare for the power down. Approximately 2 ms after a DC power failure, the battery is switched in and simultaneously the DCPWRDWN\* STD bus signal (pin 6) is driven active low.

#### **Real-Time Clock**

The real-time clock on the ZT 8809A is a Dallas Semiconductor DS 1215. It keeps track of hundredths of seconds, seconds, minutes, hours, days, date of the month, months, and years. The clock automatically corrects for leap years, and adjusts for months with fewer than 31 days. It may be battery-backed by the optional battery.

The real-time clock shares its address space with the 32 Kbyte static RAM. To communicate with the DS 1215, a 64-bit signature must be written to the device, which then switches out the 32 Kbyte static RAM and switches in the timekeeper function.

#### Serial Communications

The ZT 8809A contains two asynchronous RS-232-C communications channels, one of which is selectable for RS-422/485. Both use the same type of UART chip (16C450 equivalent), which is functionally equivalent to the serial communications channels found in the IBM family of personal computers or their compatibles.

Each channel has a programmable baud rate generator, loopback diagnostic capability, maskable interrupt generation, and jumper selectable DCE or DTE configuration. The two channels become the COM1 and COM2 serial ports in an STD DOS system. All drivers for both the RS-232-C and RS-422/485 are on board the ZT 8809A. COM2 may be disabled to allow an external board, such as a modem board, to provide COM1.

#### **Counter/Timers**

The ZT 8809A has three independent 16-bit counter/timers, each of which can be used as a timer or event counter. The clock frequency driving each of these timers is a 1.19318 MHz oscillator. For timers 1 and 2, the clock input may be jumpered to receive the frontplane connector J4 signal, which may be an external frequency or event input.

The six programmable counter/timer modes are as follows:

- 1. Interrupt on end of count

- 2. Frequency divider

- 3. Square wave generator

- 4. Software triggered strobe

- 5. Retriggerable hardware triggered strobe

- 6. Retriggerable one-shot

Each timer output may be jumper-selected to drive one of the interrupt controller inputs, and is also available at connector J4. The "gate" or enable input to each timer is pulled up active by a 10 k $\Omega$  resistor and may be controlled by a source on frontplane connector J4.

#### **Interrupts**

The programmable interrupt controller (PIC) on the ZT 8809A is an Intel 8259A-2 or equivalent. It has eight interrupt inputs that can be prioritized in software. Its output drives the CPU interrupt input. All PIC interrupt inputs may be jumper selected between various onboard sources and the five frontplane and three backplane sources. Factory default assigns the STD DOS compatible interrupt selections as described by jumper descriptions W2-11 in Appendix A.

The interrupt structure follows Revision 2.3 and later of the STD-80 Series Bus Specification, which allows for the RESERVED and CNTRL\* STD bus pins 37 and 50, respectively, to be interrupt sources as well as INTRQ\* pin 44. These signals are now referred to as INTRQ1\*, INTRQ2\*, and INTRQ\*, respectively. This provides for more backplane interrupts and may eliminate frontplane cabling for added interrupts.

Also supported is the 8088 STD bus protocol for PIC cascading, allowing for 8259A interrupt controller expansion. The PIC may handle up to 50 prioritized interrupts by combining six off-board sources, each of which may support eight interrupt inputs via a separate "slave" interrupt controller, plus two direct on-board sources.

#### Centronics Printer/General Purpose I/O Port

A Centronics printer interface is included on the ZT 8809A. It may drive a Centronics-compatible printer directly. The printer interface can also be used for general purpose I/O. It consists of eight I/O lines for data, four open collector I/O lines for control, and five input lines for status. The open collector lines have internal 2.5 k $\Omega$  pullups to Vcc.

One of the status lines, ACK, activates the interrupt request LPT1 from the printer interface to the interrupt controller. An enable bit for this interrupt is within the printer interface chip, the VL 16C452. (This chip also contains the two 16C450 equivalent serial ports.) All lines have corresponding register bits within the 16C452.

#### **Optional Numeric Data Coprocessor (8087)**

An Intel 8087 or equivalent Numeric Data Coprocessor is available for the ZT 8809A. It adds performance by contributing arithmetic, trigonometric, exponential, and logarithmic instructions to the standard 8088/8086 instruction set.

The 8087 may be mounted on the ZT 8809A with the aid of Ziatech's zSBC 337 module. This module mounts onto the microprocessor socket and accepts both the microprocessor and 8087. This configuration requires two slots in a standard STD bus card cage unless mounted in the end slot.

#### Clock Slowdown & Halt Restart (CMOS boards only)

For power conservation, the ZT 88CT08A and ZT 88CT09A contain two features to slow down or stop processor execution programmatically. These are the clock slowdown and halt with interrupt restart features, provided by a special Harris Semiconductor 82C85 clock chip that replaces the 82C84A normally shipped on the ZT 8809A board.

Clock slowdown divides the existing clock frequency by 256, allowing a selection between 5 MHz and 19.5 kHz for the ZT 88CT08A, and between 8 MHz and 31.25 kHz for the ZT 88CT09A. Writing to a bit at the printer port allows programmatic control of the slowdown feature. If the printer requires this bit for proper control (most do not), a jumper selection is also provided to allow hardware selection of this feature.

Interrupt restart allows the processor to stop processing via a software halt instruction and remain dormant until a time interval has passed or until the processor is needed by an external device. This conserves the ZT 88CT08A/88CT09A power until processing is actually needed. To use this feature, the software programs the on-board 8259A interrupt controller to enable the proper interrupt level. This interrupt may be from the on-board timers with their independent oscillator or from an external source. The program then halts the microprocessor with the HLT instruction until the interrupt arrives to restart it.

### Chapter 2

## **GETTING STARTED**

| Contents                             | Page |

|--------------------------------------|------|

| OVERVIEW                             | 2-2  |

| UNPACKING                            |      |

| WHAT'S IN THE BOX?                   | 2-3  |

| SYSTEM REQUIREMENTS                  | 2-4  |

| Physical Requirements                | 2-4  |

| Power Requirements                   |      |

| Environmental Requirements           |      |

| INSTALLING THE ZT 8809A              | 2-7  |

| Configuring the ZT 8809A for STD ROM | 2-9  |

| STD ROM Memory Requirements          | 2-9  |

| STD ROM Cable Requirements           |      |

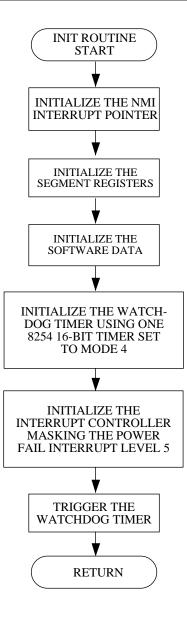

| STD ROM Jumper Configuration         |      |