# TFT-LCD TV/MONITOR

Chassis Model

NK15N\* LTM1575W NK17N\* LTM1775W

# Training

# Manual

# TFT-LCD TV/MONITOR

# SAMSUNO

#### CONTENTS

- 1. Introduction of TFT-LCD

- 2. Specifications

- 3. Alignment & Adjustments

- 4. Block Diagram

- 5. Troubleshooting

- 6. IC Specifications

- 7. Samsung LCD TV's sales points

- 8. General Informations of LCD

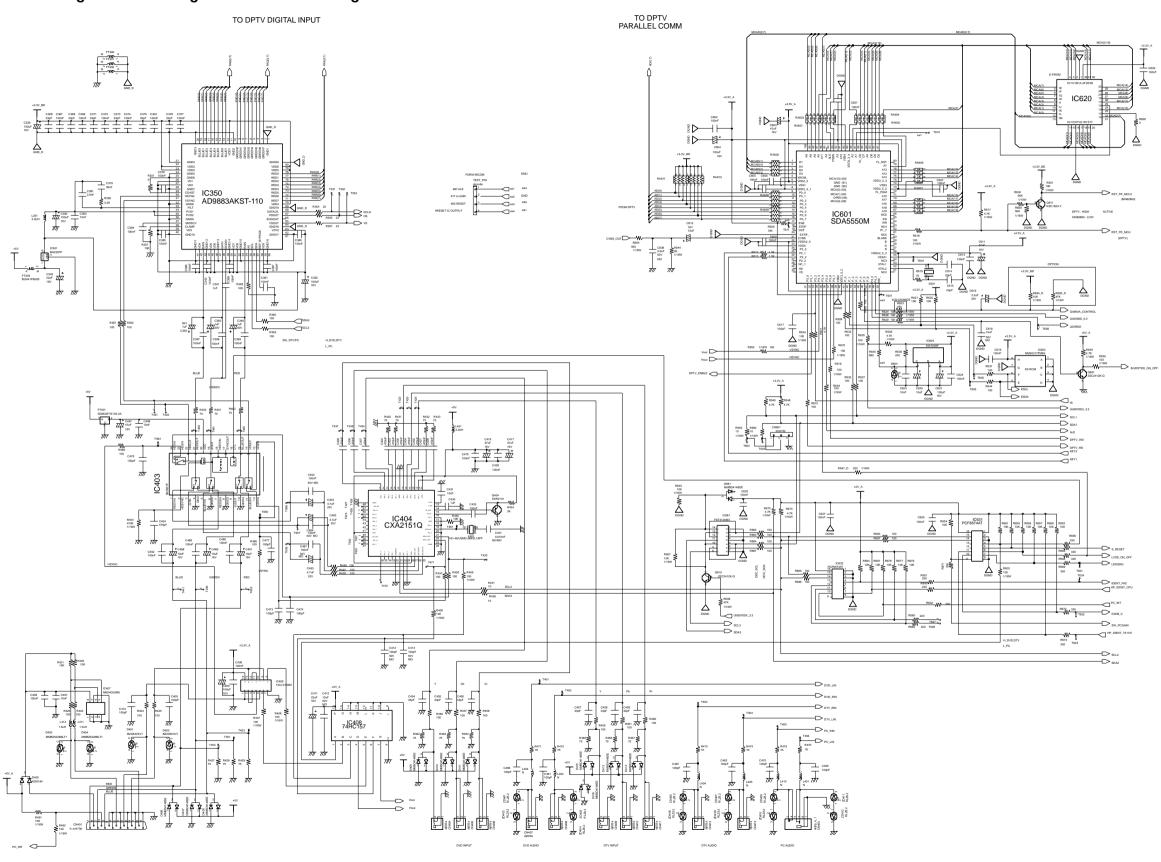

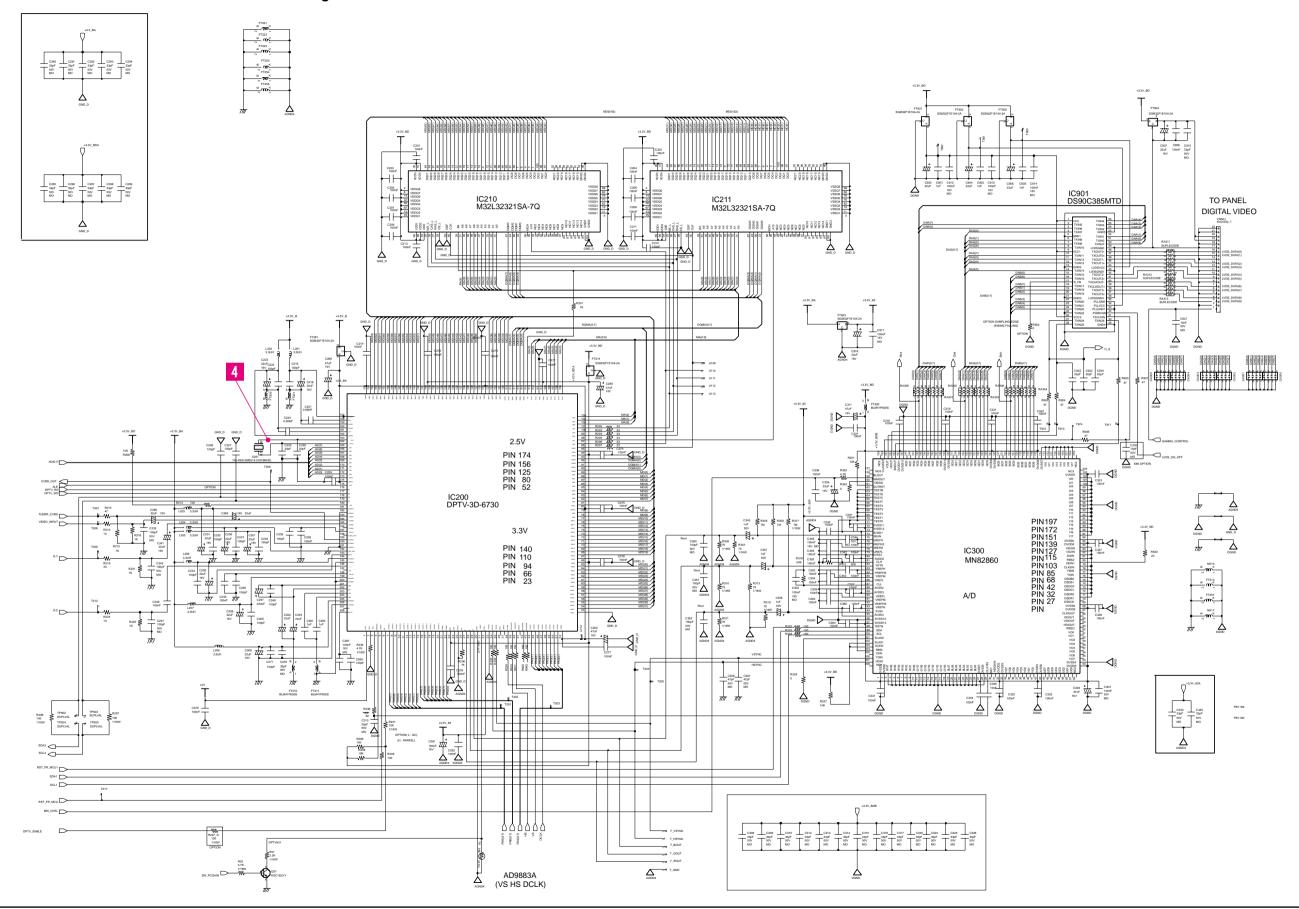

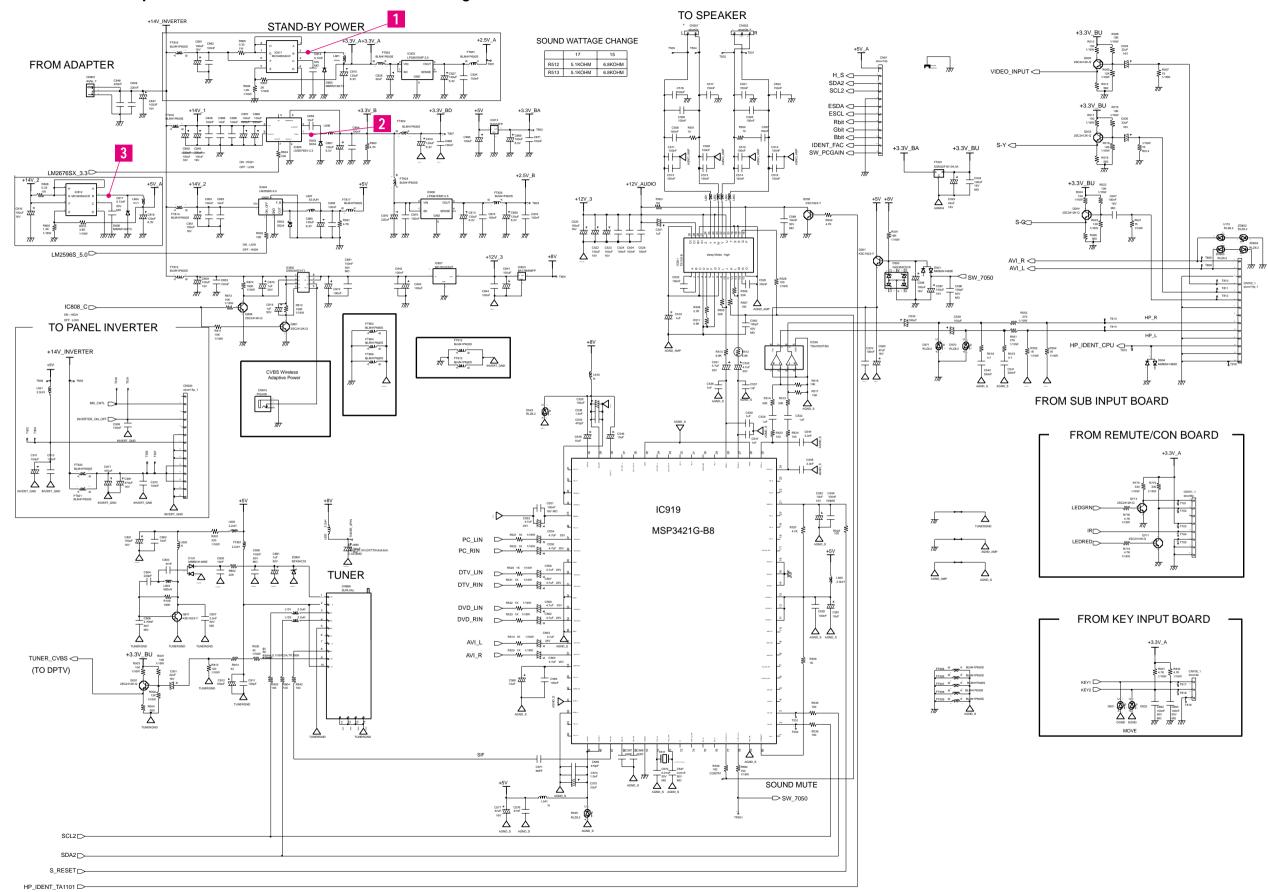

- 9. Schematic Diagrams

Visual Media Division Global CS Team Quality Assurance Group

**Samsung Electronics Co.,Ltd.** 416, Maetan-3Dong, Paldal-Gu, Suwon City, Kyungki-Do, Korea. Printed in Korea

Published by S.K.Yang / Manager of VD Division May 2002

# 2. Product Specifications

# 1 Specifications

| Item                                           | Description                                                                                                                                                                                                                             |                          |                                                                                                   |  |  |  |  |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------------------------------------------------------------------------------------------|--|--|--|--|

| Item                                           | LTM1575W                                                                                                                                                                                                                                |                          | LTM1775W                                                                                          |  |  |  |  |

| LCD Panel                                      | TFT-LCD panel, RGB vertical str<br>white, 15-Inch viewable, 0.2895 i                                                                                                                                                                    |                          | TFT-LCD panel, RGB vertical stripe, normaly white, 17-Inch viewable, 0.2895 mm pixel pitch        |  |  |  |  |

| Scanning Frequency                             | Horizontal : 30 kHz ~ 61 kHz (A<br>Vertical : 56 Hz ~ 75 Hz (Aut                                                                                                                                                                        |                          |                                                                                                   |  |  |  |  |

| Display Colors                                 | 16.2 Million colors                                                                                                                                                                                                                     |                          |                                                                                                   |  |  |  |  |

| Maximum Resolution                             | Horizontal : 1280 Pixels<br>Vertical : 768 Pixels                                                                                                                                                                                       |                          |                                                                                                   |  |  |  |  |

| Input Video Signal                             | Analog 0.7 Vp-p ± 5% positive                                                                                                                                                                                                           | at 75 $\Omega$ , interna | Illy terminated                                                                                   |  |  |  |  |

| Input Sync Signal                              | Type : Seperate H/V<br>Level : TTL level                                                                                                                                                                                                |                          |                                                                                                   |  |  |  |  |

| Maximum Pixel Clock rate                       | 80 MHz                                                                                                                                                                                                                                  |                          | 80 MHz                                                                                            |  |  |  |  |

| Active Display<br>Horizontal/Vertical          | 368.0 mm / 236.0 mm                                                                                                                                                                                                                     |                          | 370.560 mm / 222.336 mm                                                                           |  |  |  |  |

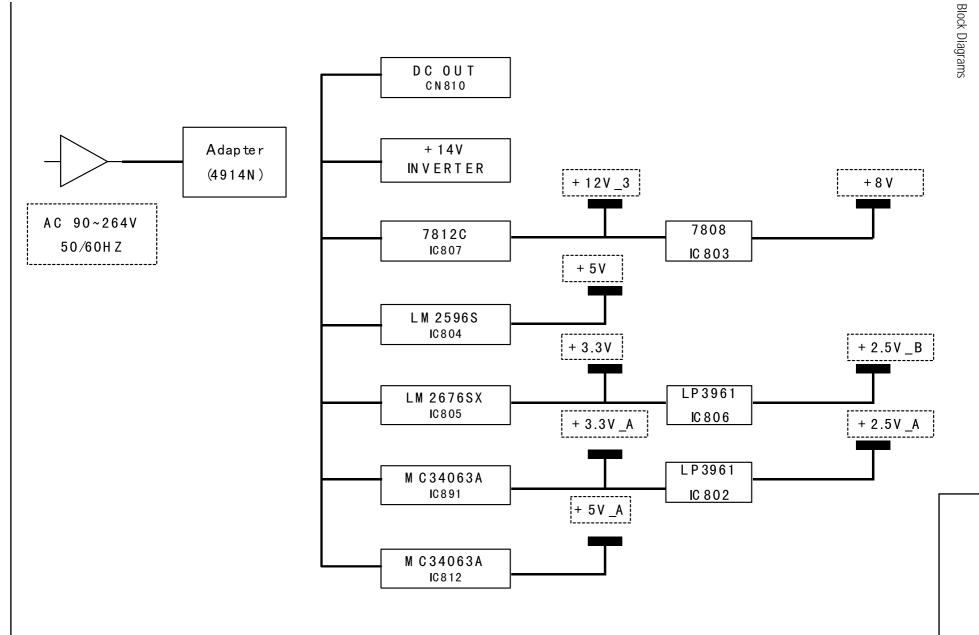

| AC power voltage & Frequency                   | AC 90 ~ 264 Volts, 60 / 50 Hz ±                                                                                                                                                                                                         | 3 Hz                     |                                                                                                   |  |  |  |  |

| Power Consumption                              | 50 W (Max)                                                                                                                                                                                                                              |                          | 53 W (Max)                                                                                        |  |  |  |  |

| Dimensions Unit (W x D x H) Carton (W x D x H) | 19.6 x 8.0 x 14.7 Inches (498 x 2<br>22.5 x 17.4 x 10.6 Inches (571 x                                                                                                                                                                   |                          | 21.1 x 8.0 x 15.8 Inches (536 x 204.5 x 402 mm)<br>24.0 x 18.3 x 10.6 Inches (609 x 465 x 269 mm) |  |  |  |  |

| Weight                                         | 3.95 Kg (8.7 lbs)                                                                                                                                                                                                                       |                          | 4.8 Kg (10.6 lbs)                                                                                 |  |  |  |  |

| Environmental Considerations                   | Operating Temperature: 50 °F ~ 104 °F (10 °C ~ 40 °C)  Humidity: 10 % ~ 80 %  Storage Temperature: -4 °F ~ 113 °F (-20 °C ~ 45 °C)  Humidity: 5 % ~ 95 %                                                                                |                          |                                                                                                   |  |  |  |  |

|                                                | Tunning                                                                                                                                                                                                                                 |                          | Frequency Synthesize                                                                              |  |  |  |  |

| TV System                                      | System                                                                                                                                                                                                                                  |                          | NTSC-M                                                                                            |  |  |  |  |

|                                                | Sound                                                                                                                                                                                                                                   |                          | STEREO                                                                                            |  |  |  |  |

| Antena Input                                   | 75 <b>Ω</b> , Coaxial Cable                                                                                                                                                                                                             |                          |                                                                                                   |  |  |  |  |

|                                                | - MAX Internal speaker Out: Right => 3W Right => 5W Left => 5W                                                                                                                                                                          |                          |                                                                                                   |  |  |  |  |

| Sound Characteristic                           | <ul> <li>BASS Control Range: -12 dB~ + 12 dB</li> <li>TREBLE Control Range: -12 dB~ + 12 dB</li> <li>Headphone Out: 5mW max (400m Vrms)</li> <li>Output Frequency: RF =&gt; 80 Hz ~ 15 kHz</li> <li>A/V =&gt; 80 Hz ~ 15 kHz</li> </ul> |                          |                                                                                                   |  |  |  |  |

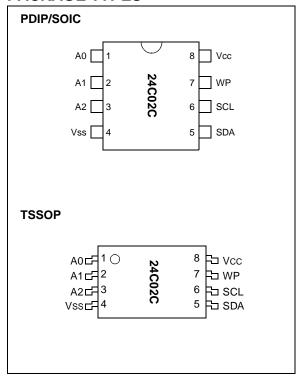

# 2 Pin Assignments

# 2-1 D-SUB

| Pin | Separate            |

|-----|---------------------|

| 1   | Red                 |

| 2   | Green               |

| 3   | Blue                |

| 4   | GND                 |

| 5   | GND (DDC Return)    |

| 6   | GND-Red             |

| 7   | GND-Green           |

| 8   | GND-Blue            |

| 9   | No Connection       |

| 10  | GND-Sync./Self Test |

| 11  | GND                 |

| 12  | DDC Data            |

| 13  | H-Sync.             |

| 14  | V-Sync.             |

| 15  | DDC Clock           |

# 2-2 DVD, DTV

| RCA Green  | Υ       |  |  |  |  |

|------------|---------|--|--|--|--|

| NOA GICCII | GND     |  |  |  |  |

| RCA Blue   | Pb (Cb) |  |  |  |  |

| Non Blue   | GND     |  |  |  |  |

| RCA Red    | Pr (Cr) |  |  |  |  |

| No/ Neu    | GND     |  |  |  |  |

| RCA White  | Audio L |  |  |  |  |

| NOA WIIIC  | GND     |  |  |  |  |

| RCA Red    | Audio R |  |  |  |  |

| KCA KEU    | GND     |  |  |  |  |

# 2-3 S-Video

| Pin | Separate |

|-----|----------|

| 1   | GND      |

| 2   | Υ        |

| 3   | С        |

| 4   | GND      |

| 5   | GND      |

# 2-4 A/V

| RCA Yellow | CVBS    |

|------------|---------|

| DCA Mhito  | Audio L |

| RCA White  | GND     |

| RCA Red    | Audio R |

|            | GND     |

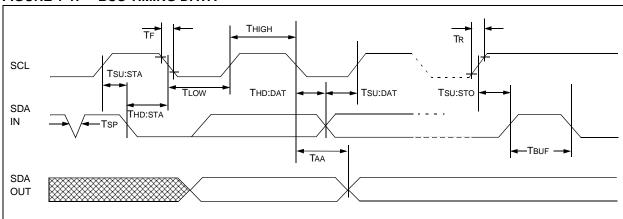

# 3 Timing Chart

This section of the service manual describes the timing that the computer industry recognizes as standard for computer-generated video signals.

# 3-1 LCD Panel Mode: 1 mode

| Timing No.                     |                      |

|--------------------------------|----------------------|

| Originator                     | 4 000 /001 1         |

| Mode Name                      | 1280/60Hz            |

| Resolution (HxV)               | 1280x768             |

| HORIZONTAL                     |                      |

| Frequency                      | 47.700kHz            |

| Total time                     | 20.964μs             |

| Active time                    | 15.973µs             |

| Blank time<br>  Border (L / R) | 4.992μs<br>0.000μs   |

| Data time                      | 15.964μs             |

| Front porch                    | 0.799µs              |

| Sync. width                    | 1.697µs              |

| Back porch                     | 2 496μs              |

| Sync. polarity                 | Negative             |

| VERTICAL                       |                      |

| Frequency                      | 60Hz                 |

| Total time Active time         | 16.667ms<br>16.101ms |

| Blank time                     | 0.566ms              |

| Border (T / B)                 | 0.000ms              |

| Data time                      | 16.101ms             |

| Front porch                    | 20.964ms             |

| Sync width                     | 62.893ms             |

| Back porch                     | 482.180              |

| Sync. polarity                 | Positive             |

| Dot Clock                      | 80.136MHz            |

| Sync. Type                     | Separate             |

| Scan Type                      | N/I                  |

# 3-2 Supported Modes (1)

| Timing No.                                                                                                                      | 2                                                                                                               | 3                                                                                                               | 11                                                                                                              | 17                                                                                                              | 32                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Originator                                                                                                                      | IBM                                                                                                             | IBM                                                                                                             | VESA                                                                                                            | VESA                                                                                                            | MAC                                                                                                             |

| Mode Name                                                                                                                       | VGA2                                                                                                            | VGA3                                                                                                            | 640/72Hz                                                                                                        | 640/75Hz                                                                                                        | 640/67Hz                                                                                                        |

| Resolution (HxV)                                                                                                                | 720x400                                                                                                         | 640x480                                                                                                         | 640x480                                                                                                         | 640x480                                                                                                         | 640x480                                                                                                         |

| HORIZONTAL Frequency Total time Active time Blank time Border (L / R) Data time Front porch Sync. width Back porch              | 31.469kHz<br>31.777µs<br>26.058µs<br>5.720µs<br>0.318µs<br>25.422µs<br>0.318µs<br>3.813µs<br>1.589µs            | 31.469kHz<br>31.778µs<br>26.058µs<br>5.720µs<br>0.318µs<br>25.422µs<br>0.318µs<br>3.813µs<br>1.589µs            | 37.861kHz<br>26.413µs<br>20.825µs<br>5.588µs<br>0.254µs<br>20.317µs<br>0.508µs<br>1.270µs<br>3.810µs            | 37.500kHz<br>26.667µs<br>20.317µs<br>6.350µs<br>0.000µs<br>20.317µs<br>0.508µs<br>2.032µs<br>3.810µs            | 35.000kHz<br>28.571 µs<br>21.164 µs<br>7.407 µs<br>0.000 µs<br>21.164 µs<br>2.116 µs<br>2.116 µs<br>3.175 µs    |

| Sync. polarity                                                                                                                  | Negative                                                                                                        | Negative                                                                                                        | Negative                                                                                                        | Negative                                                                                                        | Negative                                                                                                        |

| VERTICAL Frequency Total time Active time Blank time Border (T / B) Data time Front porch Sync. width Back porch Sync. polarity | 70.087Hz<br>14.268ms<br>13.155ms<br>1.113ms<br>0.222ms<br>12.711ms<br>0.191ms<br>0.064ms<br>0.858ms<br>Positive | 59.940Hz<br>16.683ms<br>15.761ms<br>0.922ms<br>0.254ms<br>15.253ms<br>0.064ms<br>0.064ms<br>0.794ms<br>Negative | 72.809Hz<br>13.735ms<br>13.100ms<br>0.635ms<br>0.211ms<br>12.678ms<br>0.026ms<br>0.079ms<br>0.528ms<br>Negative | 75.000Hz<br>13.333ms<br>12.800ms<br>0.533ms<br>0.000ms<br>12.800ms<br>0.027ms<br>0.080ms<br>0.427ms<br>Negative | 66.667Hz<br>15.000ms<br>13.714ms<br>1.286ms<br>0.000ms<br>13.714ms<br>0.086ms<br>0.086ms<br>1.114ms<br>Negative |

| Dot Clock                                                                                                                       | 28.322MHz                                                                                                       | 25.175MHz                                                                                                       | 31.500MHz                                                                                                       | 31.500MHz                                                                                                       | 30.240MHz                                                                                                       |

| Sync. Type                                                                                                                      | Separate                                                                                                        | Separate                                                                                                        | Separate                                                                                                        | Separate                                                                                                        | Separate                                                                                                        |

| Scan Type <sup>*</sup>                                                                                                          | N/I                                                                                                             | N/I                                                                                                             | N/I                                                                                                             | N/I                                                                                                             | N/I                                                                                                             |

# 3-2 Supported Modes (2)

| Timing No.                                                                                                                        | 13                                                                                                                       | 14                                                                                                               | 18                                                                                                                    | 33                                                                                                               | 15                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| Originator                                                                                                                        | VESA                                                                                                                     | VESA                                                                                                             | VESA                                                                                                                  | MAC                                                                                                              | VESA                                                                                                                     |

| Mode Name                                                                                                                         | 800/60Hz                                                                                                                 | 800/72Hz                                                                                                         | 800/75Hz                                                                                                              | 832/75Hz                                                                                                         | 1024/60Hz                                                                                                                |

| Resolution (HxV)                                                                                                                  | 800x600                                                                                                                  | 800x600                                                                                                          | 800x600                                                                                                               | 832x624                                                                                                          | 1024x768                                                                                                                 |

| HORIZONTAL Frequency Total time Active time Blank time Border (L / R) Data time Front porch Sync. width Back porch Sync. polarity | 37.879kHz<br>26.400 μs<br>20.000 μs<br>6.400 μs<br>0.000 μs<br>20.000 μs<br>1.000 μs<br>3.200 μs<br>2.200 μs<br>Positive | 48.077kHz<br>20.800µs<br>16.000µs<br>4.800µs<br>0.000µs<br>16.000µs<br>1.120µs<br>2.400µs<br>1.280µs<br>Positive | 46.875kHz<br>21.333µs<br>16.162µs<br>5.171 µs<br>0.000 µs<br>16.162µs<br>0.323 µs<br>1.616 µs<br>3.232 µs<br>Positive | 49.726kHz<br>20.110µs<br>14.524µs<br>5.171µs<br>0.000µs<br>14.524µs<br>0.559µs<br>1.117µs<br>3.910µs<br>Positive | 48.363kHz<br>20.677 μs<br>15.754 μs<br>4.923 μs<br>0.000 μs<br>15.754 μs<br>0.369 μs<br>2.092 μs<br>2.462 μs<br>Negative |

| VERTICAL Frequency Total time Active time Blank time Border (T / B) Data time Front porch Sync. width Back porch Sync. polarity   | 60.317Hz<br>16.579ms<br>15.840ms<br>0.739ms<br>0.000ms<br>15.840ms<br>0.026ms<br>0.106ms<br>0.607ms<br>Positive          | 72.188Hz<br>13.853ms<br>12.480ms<br>1.373ms<br>0.000ms<br>12.480ms<br>0.770ms<br>0.125ms<br>0.478ms<br>Positive  | 75.000Hz<br>13.333ms<br>12.800ms<br>0.533ms<br>0.000ms<br>12.800ms<br>0.021ms<br>0.064ms<br>0.448ms<br>Positive       | 74.551Hz<br>13.414ms<br>12.549ms<br>0.864ms<br>0.000ms<br>12.549ms<br>0.020ms<br>0.060ms<br>0.784ms<br>Positive  | 60.004Hz<br>16.666ms<br>15.880ms<br>0.786ms<br>0.000ms<br>15.880ms<br>0.062ms<br>0.124ms<br>0.600ms<br>Negative          |

| Dot Clock                                                                                                                         | 40.000MHz                                                                                                                | 50.000MHz                                                                                                        | 49.500MHz                                                                                                             | 49.500MHz                                                                                                        | 65.000MHz                                                                                                                |

| Sync. Type                                                                                                                        | Separate                                                                                                                 | Separate                                                                                                         | Separate                                                                                                              | Separate                                                                                                         | Separate                                                                                                                 |

| Scan Type                                                                                                                         | N/I                                                                                                                      | N/I                                                                                                              | N/I                                                                                                                   | N/I                                                                                                              | N/I                                                                                                                      |

# 3-2 Supported Modes (3)

| Timing No.                                                                                                                        | 16                                                                                                               | 19                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| Originator                                                                                                                        | VESA                                                                                                             | VESA                                                                                                                     |

| Mode Name                                                                                                                         | 1024/70Hz                                                                                                        | 1024/75Hz                                                                                                                |

| Resolution (HxV)                                                                                                                  | 1024x768                                                                                                         | 1024x768                                                                                                                 |

| HORIZONTAL Frequency Total time Active time Blank time Border (L / R) Data time Front porch Sync. width Back porch Sync. polarity | 56.476kHz<br>17.707µs<br>13.653µs<br>4.053µs<br>0.000µs<br>13.653µs<br>0.320µs<br>1.813µs<br>1.920µs<br>Negative | 60.023kHz<br>16.660 µs<br>13.003 µs<br>3.777 µs<br>0.000 µs<br>13.003 µs<br>0.323 µs<br>1.219 µs<br>2.235 µs<br>Positive |

| VERTICAL Frequency Total time Active time Blank time Border (T / B) Data time Front porch Sync. width Back porch Sync. polarity   | 70.069Hz<br>14.272ms<br>13.599ms<br>0.672ms<br>0.000ms<br>13.599ms<br>0.053ms<br>0.106ms<br>0.513ms<br>Negative  | 75.029Hz<br>13.328ms<br>12.795ms<br>0.533ms<br>0.000ms<br>12.795ms<br>0.017ms<br>0.050ms<br>0.466ms<br>Positive          |

| Dot Clock                                                                                                                         | 75.000MHz                                                                                                        | 78.750MHz                                                                                                                |

| Sync. Type                                                                                                                        | Separate                                                                                                         | Separate                                                                                                                 |

| Scan Type                                                                                                                         | N/I                                                                                                              | N/I                                                                                                                      |

# 3. Factory Mode Adjustments

# 1 Entering Factory Mode

- 1. To enter "Service Mode" Press the remote -control keys in this sequence :

- If you do not have Factory remote control

- If you have Factory remote - control

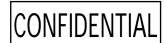

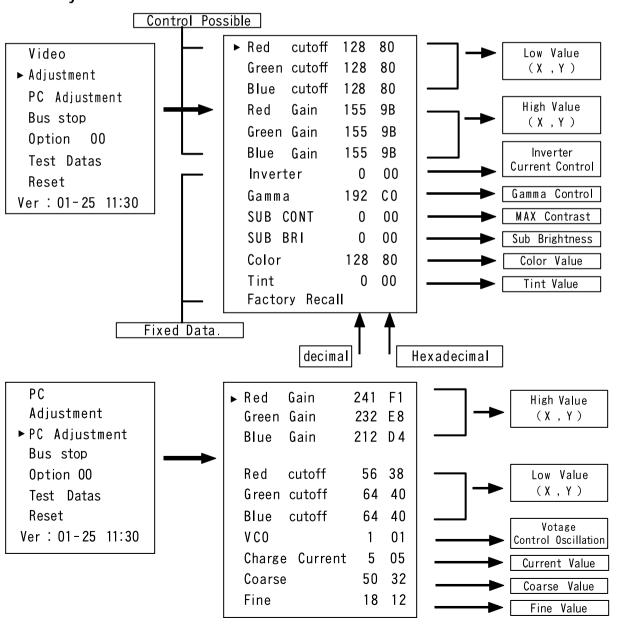

# 2 Factory Mode Tree

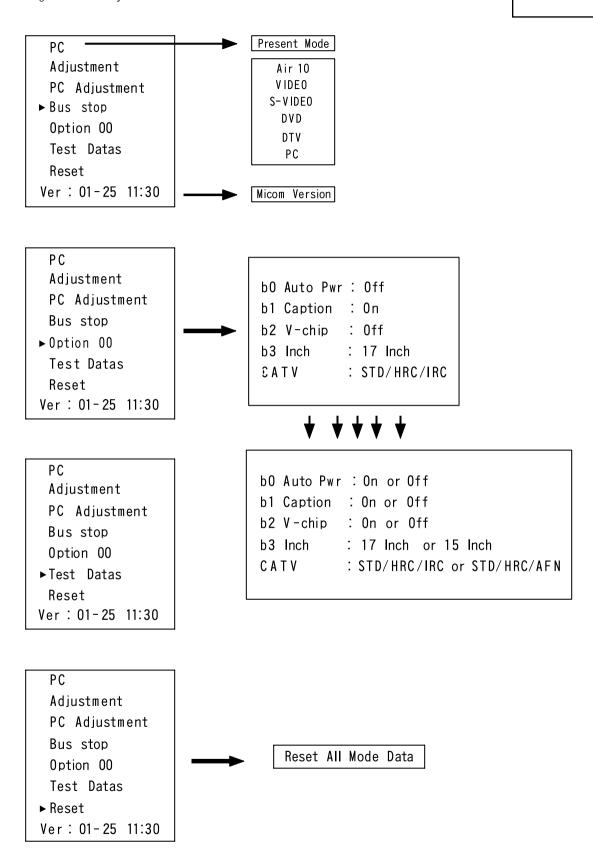

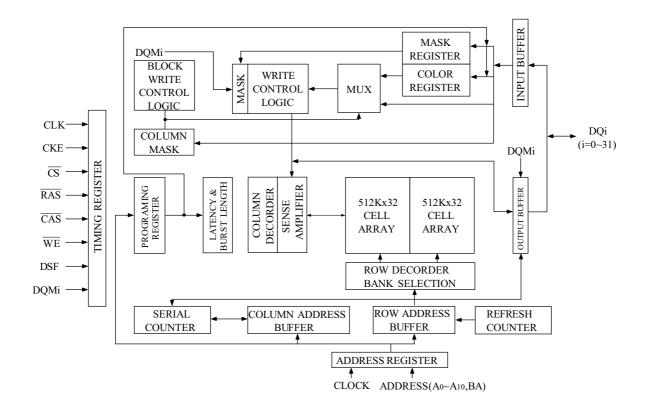

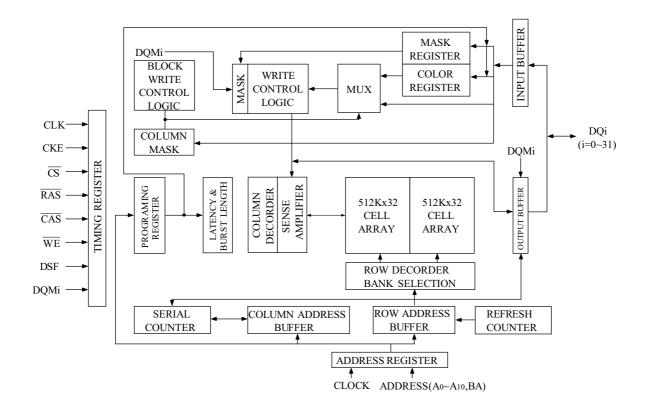

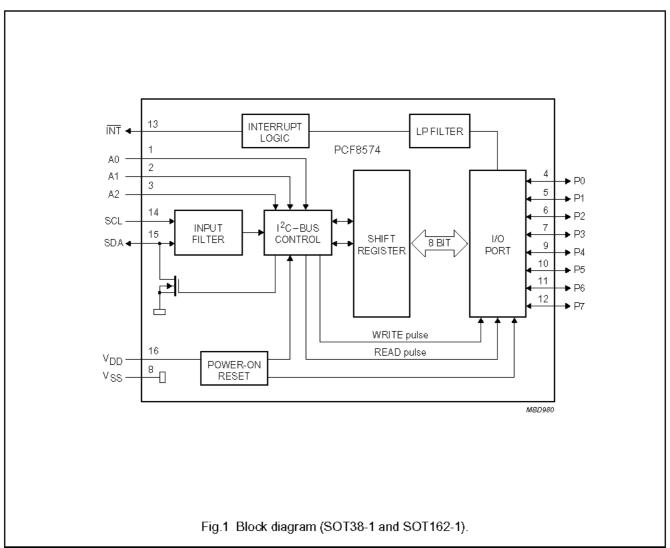

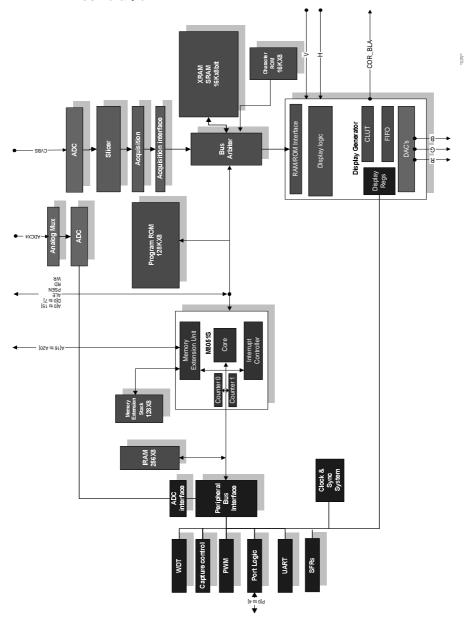

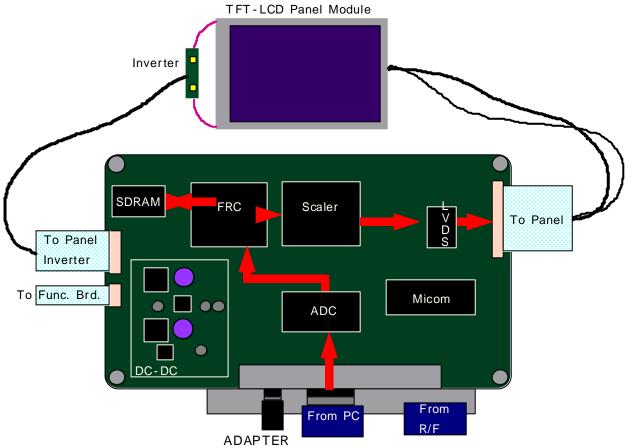

# The Block diagram of TFT-LCD Monitor Main Board

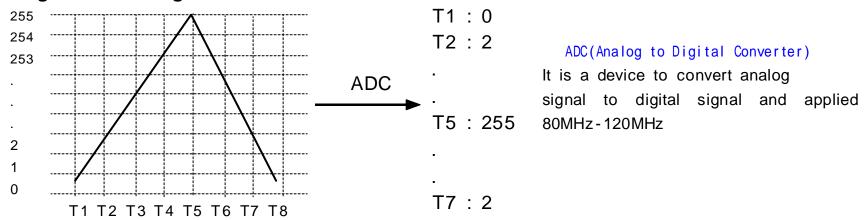

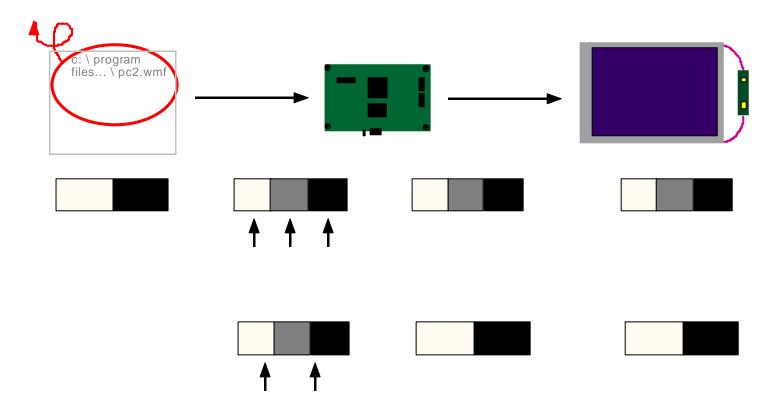

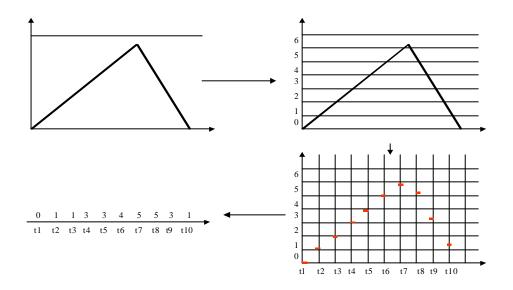

# **Analog To Digital Converting**

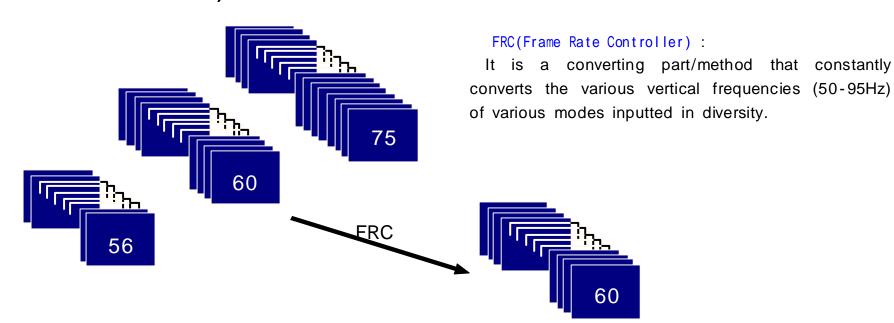

# FRC(Frame Rate Conversion):

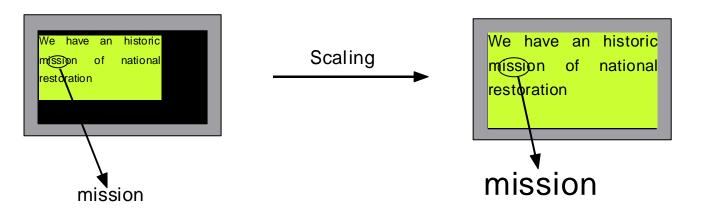

# Scaling concept: It converts the resolution signal inputted in various forms to WXGA 1280x768

#### Image Scaler:

A technique to change the inputted resolution to the other resolution.

(EX. 640x480 1024x768)

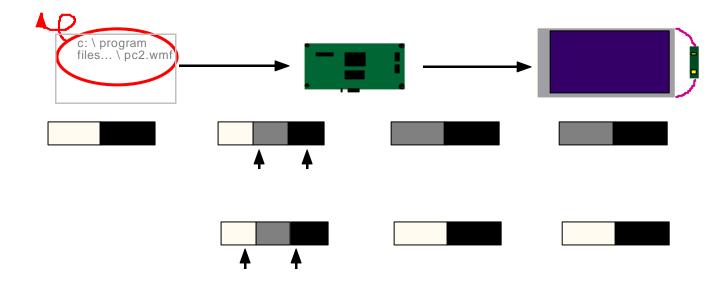

#### Fine adjustment

#### FINE:

Adjustment of the monitor's distinction by adjusting the positional difference between video signal and video clock.

# **Adjustment of Coarse**

# COARSE:

(Fine adjustment of a video clock for matching video clocks occurred between inputted video band and PLL)

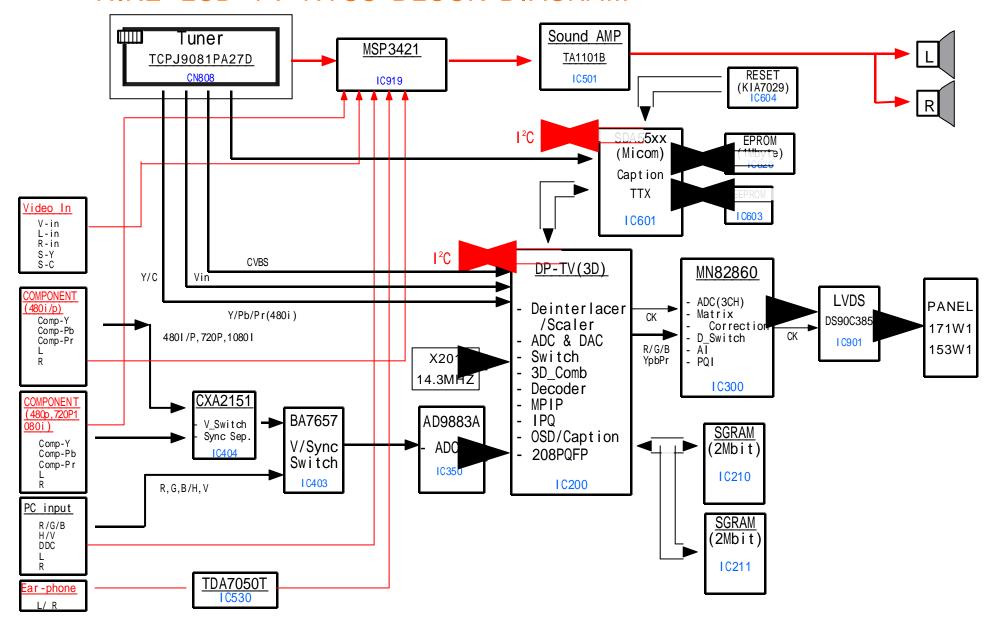

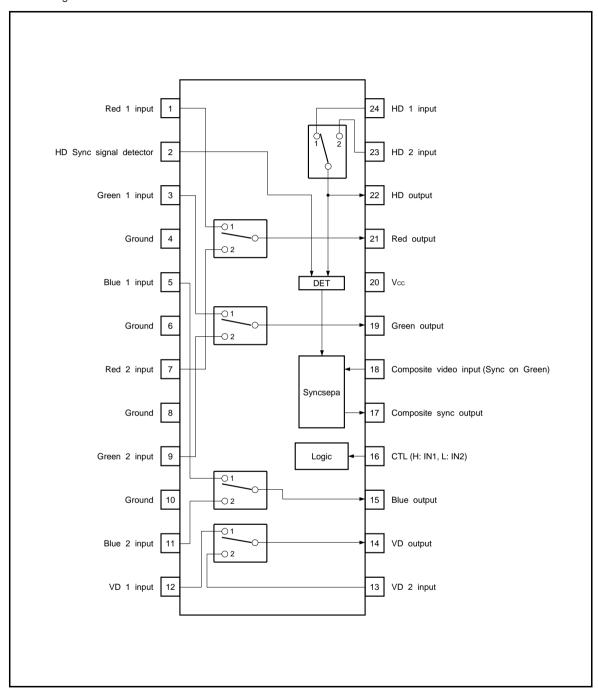

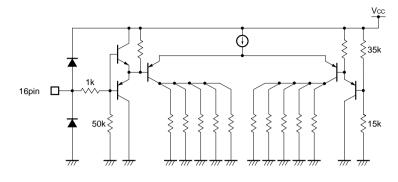

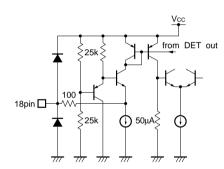

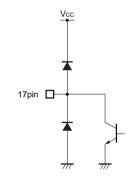

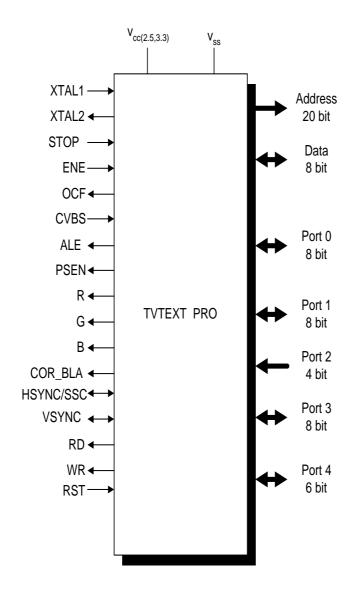

# NIKE-LCD TV NTSC BLOCK DIAGRAM

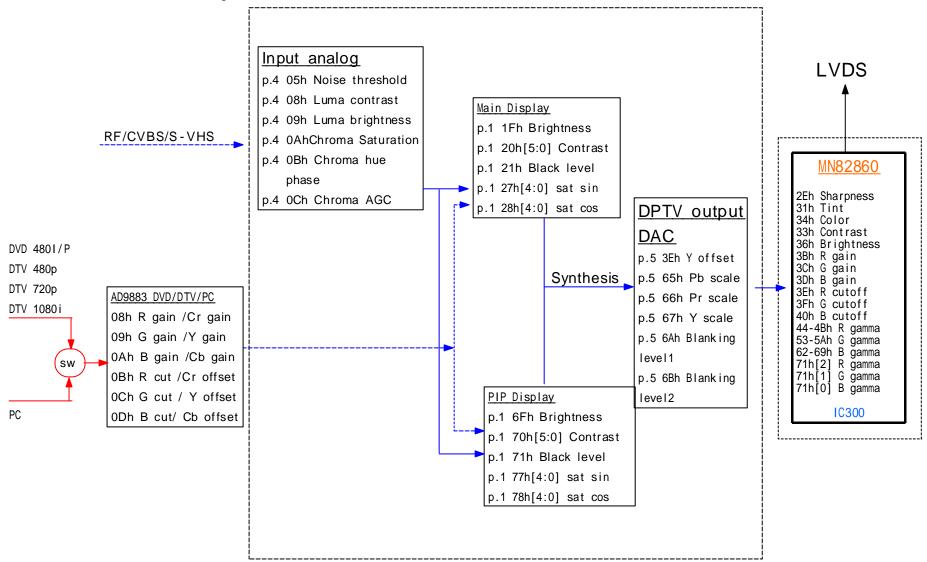

# NIKE LCD-TV NTSC adjustment RESISTOR

- 1. Full white level setting

- 1) Pattern in use: full white (100% IRE)

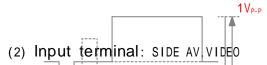

- (1) CVBS (Measured at AV JECK)

(3) Controlled by measuring Instrument: video gain 140%(100%IRE)

-When video gain is 100%, it is 70%IRE.

#### (TOCHIBA PATTERN)

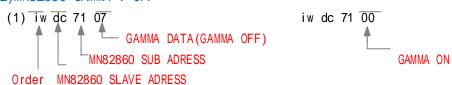

#### 2)MN82860 GAMMA : OFF

- 3) Highlight adjustment (x:282 y:283 T:10,000K)

- (1) Pattern adjustment : FULL WHITE PATTERN (VIDEO GAIN 140%)

- After it is inputted at chassis to panel with RGB Full Gain, it can be adjusted to the coordinates where you wish by using CA110.

- (2)Adjustment address and adjustment

iw dc 3e ?? -->RED GAIN (X value adjustment)

iw dc 3f ?? -->GREEN GAIN (Y value adjustment)

iw dc 40 FF -->BLUE GAIN (Y value adjustment) -->FIX

- -. The ratio of input/output is outputted 1:1 at MN82860 when RGB gain value is FF.

- -. Among characters of the RGB reproduction, a character of blue reproduction is the lowest. If you want to have white coordinates, you must output the blue higher at chassis.

- (3) The reason why gamma has to be off at 2)

- -The RGB Gain has to be adjusted in the state of gamma-Off because the MN82860 gamma correction is located at the end of column after adjustment of RGB cut-off and gain.

- After the gamma correction is set finally, the RGB Gain has to be adjusted in the state of gamma-On for production.

#### 2. Set the low light level

- 1) Pattern in use: Toshiba ABL pattern Low Light Area

- (1)Turn On the gamma correction of NM82860. (iw dc 71 00)

- -There was a trial and error. In the state of gamma-off, the Toshiba pattern's cut-off is broken down because the gray pattern touches the gamma.

Therefore, it is necessary to align the Cut-off of the Toshiba pattern to the first/second row of the gray pattern. However, do not touch the data of cut-off when you adjust the gray pattern. (Please, refer to the previous page for data address of cut-off)

Therefore, for the adjustment, turn on the gamma.

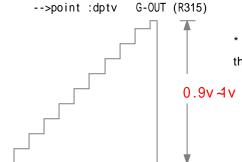

(2)Adjustment of Low-light(x:282 y:283 Y: about 4.5 (10.000k)-->

Until the 6<sup>th</sup> row of the Toshiba pattern can be seen)

iw dc 3b ?? -->RED CUT-OFF (x value adjustment)

iw dc 3c ?? -->GREEN CUT-OFF (y value adjustment)

iw dc 3d 80 -->BLUE CUT-OFF (Y value adjustment) -->FIX

-Set the blue to maximum due to its low reproduction.

- (3) Adjustment with ignoring the highlight data

- The maximum luminance is determined with IRE 100% full white pattern.

- The highlight luminance of the Toshiba ABL pattern cannot be maximum luminance due to its luminance is IRE 70%.

- 3. Final Adjustment Method

- 1)Repeat the adjustment of 1 and 2 till it is matched with adjustment spec. Nevertheless, the output voltage [1V~0.9V] has to be measured with scope when moving to the full white, and then adjust the gain. (Refer to the 1.)

- \*Method of the panel gamma setting\*

- 1)Set the maximum value not to occur the white saturation in panel by using out sources such as DVD, etc.

(1)17": A0 (2)15": D0

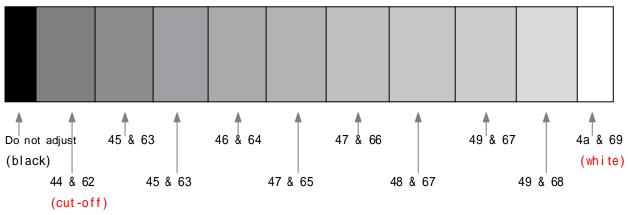

- 4. Method of the RGB gamma setting

- 1)Pattern in use: 100%IRE GREY-SCALE PATTERN

- 2)Adjustment of sub address: MN82860 (1)GREEN GAMMA GAIN FIX: ALL 40

- (2) R, G, and B data about the sub address (Green is fixed, so adjust read and blue)

| SUB ADDRESS | RED | SUB ADDRESS | BLUE | SUB ADDRESS | GREEN |

|-------------|-----|-------------|------|-------------|-------|

| 44          |     | 62          |      | 53          | 40    |

| 45          |     | 63          |      | 54          | 40    |

| 46          |     | 64          |      | 55          | 40    |

| 47          |     | 65          |      | 56          | 40    |

| 48          |     | 66          |      | 57          | 40    |

| 49          |     | 67          |      | 58          | 40    |

| 4A          |     | 68          |      | 59          | 40    |

| 4B          |     | 69          |      | 5A          | 40    |

FIX ♠

- 3) The adjustment sequence of the gray scale

- (1) Drive the 11 gray patterns

- (2) Measured the input/output gain voltage (Adjust the video gain to 100%)

- $^{\ast}$  As mentioned above, check the gain voltage when you change the pattern, then adjust.  $^{\ast}$

- (3)After perform the factory mode, spread the gamma data. (iw dc 71 00) (4) Adjust the each steps to match with the adjustment spec (x:282, y:283)

- -Adjust by using the sub address in the above.

-When you adjust the each step, do not affect to the next steps.

(Example: When adjusting the cut-off row, the flowing rows get effects. You may know when you give ff to the data.)

- (5) Confirm whether the cut-off is matched or not in Toshiba pattern.

- It has to be confirmed because the cut-off is a little bit twisted when adjusting the gray scale. If it is not matched to the adjustment spec, repeat the step (2) of 2. After adjustment, return to the gray scale and perform the fine adjustment for each step.

(The values are already adjusted, so there will not be big differences.)

- -Adjust the Toshiba pattern and gray scale pattern repeatedly.

- -After finished the adjustment, check it in the Full-white pattern.

(Do not forget to measure the gain voltage.)

If white is twisted, repeat the above. (Gamma off in full white)

3. FACTORY MODE MICOM SETTING

|          |          | 1)     | MN828 | 360 G | amma |      | ectio |      |       |          |                           |                                                                       |

|----------|----------|--------|-------|-------|------|------|-------|------|-------|----------|---------------------------|-----------------------------------------------------------------------|

| Sub-     |          | mma Co |       |       |      |      |       |      | on (1 | <u> </u> |                           | Remarks                                                               |

| add ress | SpI1     | SpI2   | SpI3  | SpI4  | SpI5 | SpI1 | SpI2  | SpI3 | SpI4  | SpI5     |                           | Nona Tho                                                              |

| 33h '    | 95       |        |       |       |      | A0   |       |      |       |          |                           | Contrast control                                                      |

| 36h '    | 1C       |        |       |       |      | 10   |       |      |       |          |                           | Brightness Control                                                    |

| 3Bh '    | E1       |        |       |       |      | DD   |       |      |       |          |                           | Red Gain                                                              |

| 3Ch '    | C7       |        |       |       |      | C8   |       |      |       |          | RGB Gain                  | Green Gain                                                            |

| 3Dh'     | FF       |        |       |       |      | FF   |       |      |       |          | Cont rol                  | Blue Gain                                                             |

| / cd/m2  | 98.1     |        |       |       |      |      |       |      |       |          |                           | Condition of the full white gamma off                                 |

| 3Eh '    | 7E       |        |       |       |      | 86   |       |      |       |          |                           | Red Cut-off                                                           |

| 3Fh'     | 75       |        |       |       |      | 77   |       |      |       |          | RGB Cut-off               | Green Cut-off                                                         |

| 40h '    | 80       |        |       |       |      | 80   |       |      |       |          | Cont rol                  | Blue Cut-off                                                          |

| Y cd/m   | 2.0      |        |       |       |      | 3.5  |       |      |       |          |                           | Low light condition of Toshiba ABL patter                             |

| 44h '    | 44       |        |       |       |      | 44   |       |      |       |          |                           | Bit[7-0] RTANA R static Gamma gradient setting 1 (=40h' for 1x)       |

| 45h '    | 45       |        |       |       |      | 47   |       |      |       |          | Red Gamma<br>Correction   | Bit[7-0] RTANB<br>R static Gamma gradient setting 2<br>(=40h' for 1x) |

| 46h '    | 44       |        |       |       |      | 41   |       |      |       |          |                           | Bit[7-0] RTANC<br>R static Gamma gradient setting 3<br>(=40h' for 1x) |

| 47h '    | 33       |        |       |       |      | 37   |       |      |       |          |                           | Bit[7-0] RTAND<br>R static Gamma gradient setting 4<br>(=40h' for 1x) |

| 48h '    | 40       |        |       |       |      | 4D   |       |      |       |          |                           | Bit[7-0] RTANE R static Gamma gradient setting 5 (=40h' for 1x)       |

| 49h '    | 3B       |        |       |       |      | 2E   |       |      |       |          |                           | Bit[7-0] RTANF<br>R static Gamma gradient setting 6<br>(=40h' for 1x) |

| 4Ah'     | 3D       |        |       |       |      | 25   |       |      |       |          |                           | Bit[7-0] RTANG<br>R static Gamma gradient setting 7<br>(=40h' for 1x) |

| 4Bh '    | 40       |        |       |       |      | 40   |       |      |       |          |                           | Bit[7-0] RTANH<br>R static Gamma gradient setting 8<br>(=40h' for 1x) |

| 53h '    | 40       |        |       |       |      | 40   |       |      |       |          |                           |                                                                       |

| 54h '    | 40       |        |       |       |      | 40   |       |      |       |          |                           |                                                                       |

| 55h '    | 40       |        |       |       |      | 40   |       |      |       |          |                           |                                                                       |

| 56h '    | 40       |        |       |       |      | 40   |       |      |       |          | Green Gamma<br>Correction |                                                                       |

| 57h '    | 40       |        |       |       |      | 40   |       |      |       |          |                           |                                                                       |

| 58h '    | 40       |        |       |       |      | 40   |       |      |       |          |                           |                                                                       |

| 59h '    | 40       |        |       |       |      | 40   |       |      |       |          |                           |                                                                       |

| 62h '    | 37       |        |       |       |      | 3F   |       |      |       |          |                           |                                                                       |

| 63h '    | 3A       |        |       |       |      | 3F   |       |      |       |          |                           |                                                                       |

| 64h '    | 40       |        |       |       |      | 39   |       |      |       |          |                           |                                                                       |

| 65h '    | 33       |        |       |       |      | 34   |       |      |       |          | Pluo Comma                |                                                                       |

| 66h '    | 42       |        |       |       |      | 42   |       |      |       |          | Blue Gamma<br>Correction  |                                                                       |

| 67h '    | 48       |        |       |       |      | 44   |       |      |       |          |                           |                                                                       |

| Orli     | 46<br>4F |        |       |       |      | 5F   |       |      |       |          |                           |                                                                       |

| 68h '    | /1⊨      |        |       |       |      | JI"  |       |      |       |          |                           |                                                                       |

# 5. Troubleshooting

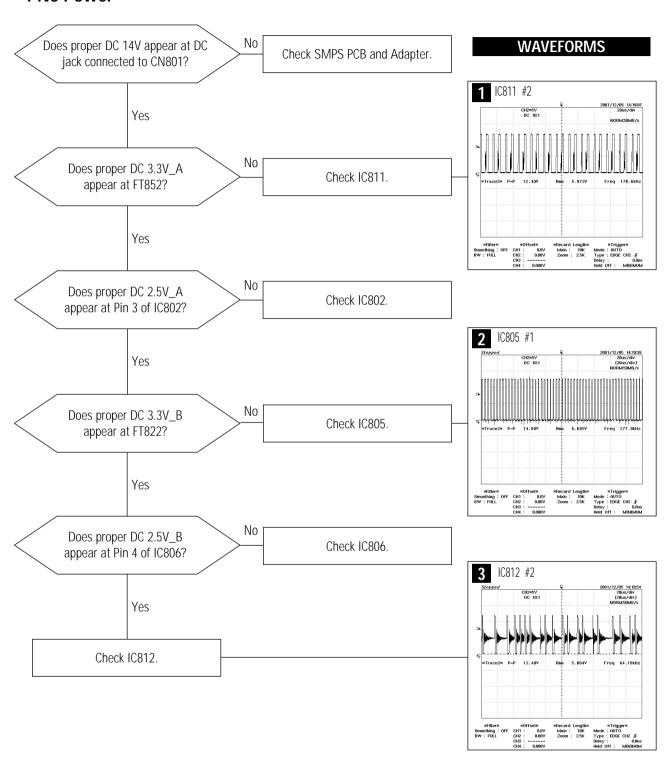

#### 1 No Power

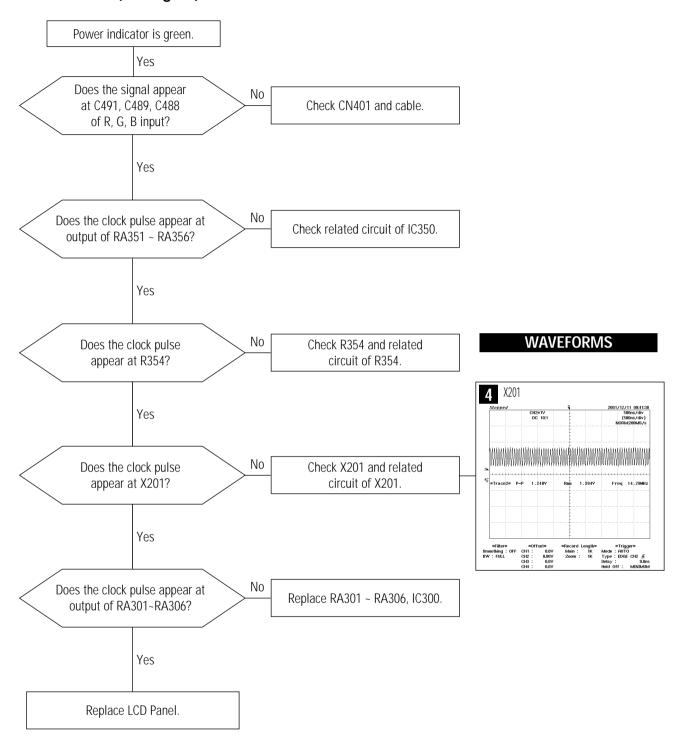

# 2 No Video (PC Signal)

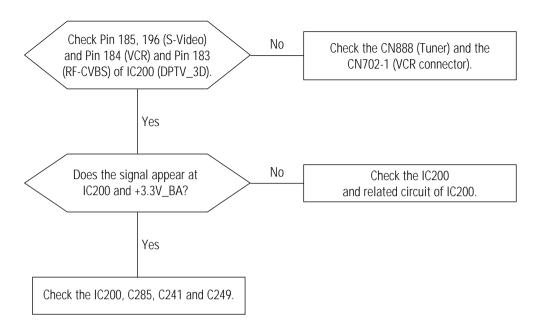

# 3 No Picture (TV, Video, S-Video, DVD, DTV)

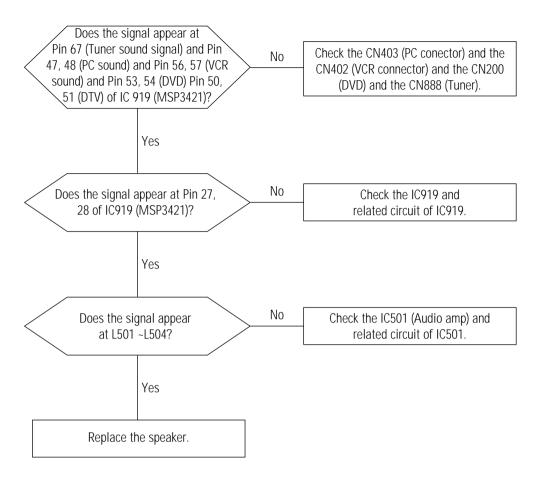

# 4 No Sound

# Extra

# Troubleshooting

If the TV seems to have a problem, first try this list of possible problems and solutions. If none of these troubleshooting tips apply, call your nearest service center.

# **Identifying Problems**

| Problem                      | Possible Solution                                           |

|------------------------------|-------------------------------------------------------------|

| Poor picture                 | Try another channel.                                        |

|                              | Adjust the antenna.                                         |

|                              | Check all wire connections.                                 |

| Poor sound quality.          | Try another channel.                                        |

|                              | Adjust the antenna.                                         |

| No picture or sound.         | Try another channel.                                        |

|                              | Press the TV/VIDEO button.                                  |

|                              | Make sure the TV is plugged in.                             |

|                              | Check the antenna connections.                              |

| No color, wrong colors or    | Make sure the program is broadcast in color.                |

| tints.                       | Adjust the picture settings.                                |

|                              | If the set is moved or turned in a different direction, the |

|                              | power should be OFF for at least 30 minutes.                |

|                              | Adjust the antenna.                                         |

| Picture rolls vertically.    | Check all wire connections.                                 |

| The TV operates erratically. | Unplug the TV for 30 seconds, then try operating it         |

|                              | again.                                                      |

| The TV won't turn on.        | Make sure the wall outlet is working.                       |

| Blurred or snowy picture,    | Check the direction, location and connections of your       |

| distorted sound              | aerial.                                                     |

|                              | This interference is often due to the use of an indoor      |

|                              | aerial.                                                     |

| Remote control malfunctions  | Replace the remote control batteries.                       |

|                              | Clean the upper edge of the remote control                  |

|                              | (transmission window).                                      |

|                              | Check the battery terminals.                                |

| "Check Signal Cable"         | Ensure that the signal cable is firmly connected to the     |

| message.                     | PC or video sources.                                        |

|                              | Ensure that the PC or video sources are turned on.          |

# Troubleshooting

| Problem                          | Possible Solution                                        |                    |

|----------------------------------|----------------------------------------------------------|--------------------|

| "Not Supported Mode!" mes-       | Check the maximum resolution and the frequency of        |                    |

| sage.                            | the video Adapter.                                       |                    |

|                                  | Compare these values with the data in the Display        |                    |

|                                  | Modes Timing Chart.                                      |                    |

| The image is too light or too    | Adjust the Brightness and Contrast.                      |                    |

| dark.                            | Adjust the Fine function.                                |                    |

| Horizontal bars appear to        | Adjust the Coarse function and then adjust the Fine      |                    |

| flicker, jitter or shimmer on    | function.                                                |                    |

| the image.                       |                                                          |                    |

| Vertical bars appear to flicker, | The TV is using its power management system.             |                    |

| jitter or shimmer on the         | Move the computer's mouse or press a key on the          |                    |

| image.                           | keyboard.                                                |                    |

| Screen is black and power        | Check that the display resolution and frequency from     |                    |

| indicator light blinks steadily. | your PC or video board is an available mode for your     |                    |

|                                  | TV. On your computer check: Control Panel, Display,      |                    |

|                                  | Settings.                                                |                    |

| Image is not stable and may      | If the setting is not correct, use your computer utility |                    |

| appear to vibrate.               | program to change the display settings.                  |                    |

|                                  | NOTE: Your TV supports multiscan display functions       |                    |

|                                  | within the following frequency domain:                   |                    |

|                                  | <ul> <li>Horizontal frequency:</li> </ul>                | 30 kHz ~ 61 kHz    |

|                                  | <ul> <li>Vertical frequency:</li> </ul>                  | 56 Hz ~ 75 Hz      |

|                                  | • Maximum refresh rate:                                  | 1280 x 768 @ 60 Hz |

| Image is not centered on the     | Adjust the horizontal and vertical position.             |                    |

| screen.                          |                                                          |                    |

| You need the Monitor driver      | Download the driver from WWW pages:                      |                    |

| software.                        | http://www.samsungusa.com/monitor                        |                    |

|                                  |                                                          |                    |

# 8. General Informations of LCD

#### 1. History of the LCD (Liquid Crystal Display)

LCD, a display device, has been started to adapt for a calculator, display part of watch, and electronic note-book, and nowadays, it is adapted for a PC, Workstation, Liquid crystal color TV, monitor, game device, and so on with a tendency of larger size, larger capacity, and colorization.

Liquid crystal has been starting to use as a display device since R. Williams at RCA co. in 1963 stated that the liquid crystal has the electro-optics effect in the science magazine, "Nature".

After the G. H Heilmeier group of the Sharp presented the first possibility of LCD's practical use in 1968, the first segment type of the DSM style LCD electronic calculator, 'EL-805', was commercialized in 1973. But, it has several problems such as black-and-white display, responding speed, narrow viewing angle, high power consumption for portability, and so on.

Responding speed: It is taking time that LCD element becomes On

or Off. When voltage signal from external changes it On to Off or Off to On, a LCD is changed due to the signal. But, it cannot be changed immediately because of the viscosity of the liquid crystal, so time delay for reaching the liquid crystal to equilibrium state is occurred. Such transformational characteristic shows up as an optical characteristic, and the delay time for the optic is called responding time. responding time is proportional to the viscosity of the liquid crystal and inversely proportional to the cell spacing. When the electronic signal is converted to On/Off, the responding time can be measured from the transmission characteristic in contrast with the time.

Viewing angle:

The LCD has a characteristic that the contrast ratio is changed by angle of the viewing point. The changing degree is shown by the viewing angle. The viewing angle is expressed as an angle over than certain value of the contrast ratio according to top, bottom, right, and left position. In a LCD cell, the transmissivity is sharply changed due to the angle of the incoming light. Therefore, in the driving process for turning it On/Off, the contrast ratio is changed because of such change of the transmissivity.

The measuring method of the viewing angle is that determine 0° where eye and a screen become a front view, and measure the gray level (gray1~gray16) at every 25° while rotate a panel to top, bottom,  $(-60\degree, +60\degree)$  left, and right  $(-60\degree, +60\degree)$ . If you draw the luminance curve due to the viewing angle, the angle from an inversion of the gray scale can be found. The viewing angle range is settled when the C/R value is over 10:1. Generally, the points to decide the picture quality of the LCD are not only the viewing angle, but also the angel of the inverted gray scale.

\* LCD electronic calculator of the segment type \*

Enterprises of the display market acknowledge the unlimited potential power of the LCD and have needed to develop better LCD with dot matrix display for informational device, which can obtain letter, figure, and various information.

\* Segment display and Dot matrix display \*

Afterward, TN (Twisted Nematic) style LCD is developed for reducing consumption power. It has weaknesses of contrast, viewing angle, and display grade. Especially, it is not proper for the larger

screen. Therefore, the STN (Super TN) LCD is developed. STN LCD has several merits compare to TN such as higher productive efficiency, suitable for lager screen, wider viewing angle, and higher contrast. The Sharp presented the word processor "WD-250" with STN LCD in 1986. It was the beginning to rapidly distribute the LCD and to develop the word processor and PC.

Nevertheless, the STN LCD uses two display colors, yellow and blue, to get enough luminosity for high contrast. The LCD needs clean white-and-black display color to be regularly substituted for CRT instead of OA. With the reason, DSTN (Double STN) style LCD, displays beautiful black-and-white, is developed in 1987, and it is commercialized.

\* STN Color Word processor and DSTN color LCD notebook \*

The materialization of the black and white display is opened the way of the gray scale and color display period, and it helps to access to PC following word processor. Afterward, LCD is developed for better conditions such as lighter weight, thinner thickness, higher resolution for larger screen, higher contrast, and wider viewing angle.

The gray scale:

It is a display method that the different state exists except On/Off state. The huge amount of information such as color display cannot be displayed with only On/Off drive. In the gray scale display, several middle states exist between an On and Off state. For example, there is gray state between black and white to display information. The gray scale is made by applying middle power between On and Off power in LCD. There are several methods to get a middle value: control the strength of the power, adjust the rage of the power pulse, and so on. The color display is determined by the degree of

the gray scale. With the only On and Off state, just 8 colors can be displayed, but with the gray scale, more colors can be displayed.

The capacity of it is still not as good as CRT.

Because LCD has passive matrix construction, it is not suitable for moving pictures in fact of high quality picture, high contrast, and high-speed response.

Development of the high capacity color LCD is needed for emulating the existing screen. With the reason, TFT (Thin film transistor) LCD of the Active matrix drive method, which is totally different to the passive matrix drive method, is developed.

The new method puts a switch element (TFT) into a picture element to control each picture element. As a result, the TFT LCD has been gotten excellent construction to develop the display quality, contrast, and viewing angle.

After 3" color TV with the TFT\_LCD is developed in 1986, LCD has been larger, and technique suitable for the larger size has been developed. At the present, 40" LCD is developed.

Through the continuous efforts for developing LCD for 4 and half centuries, the flat display is made at present.

The strong parts of TFT\_LCD compared to CRT are lighter weight, thinner style, and lower power consumption. In the efficiency aspect, the viewing angle, luminance, and contrast are near or even better than CRT. But, price and responding speed is still not so good as the CRT. In case of the viewing angle, if it is 15", left and right is 110° ~160°, top and bottom is 90°~160° which is no problem to watch. The luminance is maximum 200~250cd, and the contrast ratio is 200:1~300:1 which is better than CRT. The responding speed for TFT\_LCD is several tens ms (15": 30ms~50ms) and for the STN\_LCD is several hundreds ms. For display a moving picture, the frequency of the frame is 60Hz, so it must be 16ms. But, the frequency of

TFT\_LCD has to be twice more than STN\_LCD to make differences between the signals (On/Off), so it must be under 8ms. Nevertheless, it is a just theoretical numerical value. For driving moving picture, actually it has to be 2 or 3 times faster than that.

Contrast ratio:

The contrast ratio(C/R) is the scale to decide whether the image is clearly appeared or not. It will be clearer when the difference of the luminance is bigger. It is defined by dividing the luminance with all pixels white by luminance with all pixels black in the middle front view.

C/R = (Luminance with all pixels white) / (Luminance with all pixels black)

Luminance with all pixels black has lower value than luminance with all pixels white. The value of the contrast ratio has mainly affected by luminance of the black pixels.

In the fact of the industrial economic (another fact to rise the price), the investment efficiency and productivity problem have to be overcome. By developing responding speed of TFT\_LCD and productivity, the cost competitive power can be gotten, which makes possibility to outdo the CRT market easily.

#### 2. Principle of the driving LCD monitor

#### \* Principle outline\*

Among display parts such as LED, PDP, EL and so on, TFT\_LCD has been the most widely used together with LED. The configuration of the LC cell is as follow. Liquid crystal is located in between two tipenclosed glass plates, and electrodes exist inside of each glass plate to display an image. These electrodes are electrically contacted to external terminal.

LC cell:

It consists of two glass plates, and it is a construction part of LCD element inserted between Inside of the plates, transparent the plates. electrodes exist to construct picture element, and above it, an alignment film plate exists for aligning LC molecule in one direction. The procession LCD is formed at the lower substrate. and the active elements (diode and transistor) are formed at the side of the picture element. Color LCD is formed at the upper substrate, and a color filter is mounted for displaying colors. The color filter is located between transparent electrode and glass substrate, and it is made by pigment dispersion method, staining techniques, and etc. on the glass substrate.

space between the grass substrates maintained for inserting the liquid crystal, and the spacer maintains the space for the wider display element. In the space, the liquid crystal is inserted and aligned. At the side of the cell, electrode pattern connected to the transparent electrode exists, and external voltage reaches to the liquid crystal through the pattern. In the procession LCD, pattern for driving active element is formed. The active element is driven by patterns, and external voltage is applied to the liquid crystal through the patterns.

#### \* Why TFT LCD\*

Display is requested the display efficiencies such as high contrast ratio, high luminance, high revolution (display capacity on the dialogue screen), gradation display ability, color display ability, high-speed response ability, wide angle of visual field, and so on. Picture, letter, or figure information can be displayed by single passive matrix type, but the characteristics are in the relation of trade-off. In other

words, making one characteristic better would make other characteristic worth. Therefore, there is a limit to make all characteristics highly efficient. The worst weakness is a problem of cross-talking, but active matrix can enhance the ability of display by adding a switch element into each picture element.

Cross Talk:

It is a signal interruption between elements. For example, the display signal is distorted in the unselected picture element row, and it makes low C/R value. Active matrix method has low cross talk value contrast with simple matrix. But, the active matrix method still occurs the cross talk because the TFT element cannot drive the switch well. Also, the simple matrix method occurs the cross talk because of the signal delay due to the resistance of the electrode. Therefore, it is needed making a low resistance of ITO or driving it by given a same signal from the both side of the electrodes.

#### ? Liquid Crystal

Liquid crystal seems like a liquid at a glance, but it is in a unique state showing anisotropy like a crystal. It is an organic compound called "Thermotropic liquid crystal" becomes a liquid crystal in certain temperature range.

There are reflection type and backlit type of LCD. The reflective LCD reflects the incoming light from the front side of the LCD panel to the reflection board mounted to the backside of the panel. The backlit LCD expresses an image by taking surrounding light or fluorescence from rear side.

#### ? Driving principle

The liquid crystal is contacted to the aligned surface for inducting the direction of the liquid crystal, and the liquid crystal molecules are arranged in parallel with the alignment film hollow. All liquid crystal

molecules are arranged in parallel near to the both substrate surfaces, and both substrates are twisted 90 degree against each other (called 'twisted molecule arrangement'). Therefore, the liquid crystal molecules are twisted 90 degree between both substrates in succession, and the light advances in the same direction with the molecules. As shown in the figure, if the molecules are twisted 90 degrees, the light takes same direction with the molecules in twisted 90 degrees.

Liquid crystal: There is a mesophase exists in the natural world with three common states, solid, liquid, and gas.

The mesophase is called liquid crystal phase. It has characteristics, fluidity of liquid and positional system of crystal, in the certain temperature range.

The liquid crystal phase is divided into Nematic, Smectic, and columnar phase. The phase of is changed by temperature, and phase of is changed by density.

[Liquid crystal molecules are arranged in parallel to the aligned film hollow.]

[Liquid crystal molecules are twisted 90 degree between both substrates.]

By adding voltage or external force with TFT, the direction of the liquid crystal is coming undone from the state of twisted in 90 degree. The direction is arranged in one direction to the panel surface vertically, and the light goes straight.

Consequently, the matter of passing the incoming light is depending on the conditions (twisted or untwisted) of liquid crystal. By adding the polarizing to the both glass boards, the light passed through the liquid crystal is collected in one direction again, and it is entered into the picture element to be appeared on the screen finally.

Polarizing film: Light is vibrated by electromagnetic wave, and the electronic field and magnetic field are vibrated vertically to the operating direction. The vibrating direction of the light from the backlight of the LCD module has same probability to the all direction. The polarizing film transmits the light vibrated same direction of the polarizing axis, and it absorbs with proper medium or reflects the rest of the light vibrated to other directions to make the light in specific direction. While it is passing the liquid cell, the strength of transmitting light is controlled by rotation of the polarizing axis, and it makes the expression of gray in between black and white. In the LCD application, it is important not only polarizing degree but also management of the low reflected surface. When using the LCD in brightening place, the contrast becomes low, and the acknowledgment is reduced as a result. Therefore, the technique to reduce the reflecting ratio for the surface of the polarizing film is needed for developing picture quality.

[Shows how liquid crystal molecules are arranged when voltage is given.]

[Shows how liquid crystal molecules are arranged when voltage is off.]

[Shows how light go through when voltage is on or off.]

# ? Principle of expressing colors

In the beginning, LCD supports only black color. Nevertheless, as the application range of LCD is getting wider, and the display market is getting changed toward to the color, the LCD has developed to support colors.

LCD uses the color filter, which has three primary colors of red,

green and blue, to express colors. The RGB color filters are arranged closely to each other, and each color signal is applied to the color filter for controlling the brightness to express colors. The voltage applied to the element is controlled for managing the brightness to express various colors.

If the liquid crystal has only two functions such as cutting off light and passing light completely (red, green, blue = 1bit respectively), 8 colors (2 to the third power) can be expressed. In other words, if filter has a function to open and close, each of three colors can be controlled with 1 bit data. If each color is controlled by 2 bits, 64 colors (2 to the sixth power) can be expressed. It is expressed in equation as below.

Consequently, the quantity of colors to be expressed by LCD is depending on the bits of image data.

In other words, the quantity of light passing through the color filter is controlled by liquid crystal. The voltage for operating the liquid crystal is output from the source driver IC and supplied through the pixel TFT. The voltage supplied to the liquid crystal changes the permeability of liquid crystal. The possible quantity of colors to be expressed is determined by number of steps for controlling the liquid crystal. For example, if the liquid crystal is twisted, the color will be black, and if the liquid crystal is released, the color will be white. The combination of medium gray scales expresses other various colors.

#### ? Resolution

The resolution is another primary characteristic of display. The resolution is a measurement to express an image in detail. As resolution is higher, the quantities of picture elements are getting more. It means that the amount of data treated by drive IC during unit of time is larger; therefore, the processing speed reaches near to

the limit.

Due to the fact, there are more possibilities of creating signal distortion and EMI. In addition, as vertical resolution is getting higher, time allowed for one horizontal line becomes shorter. Time for charging data voltage into picture element is the same as time for one horizontal line. If the time gets shorter than a certain level, charging process cannot be achieved completely which leads to bad picture quality. Study and research to solve the problems has been processed in many aspects, and technology has made much advance.

EMI: Electro-magnetic interference. It is an electronic interruption by a mutual induction of electromagnetic It is not proved its harmfulness, but its frequency. harmfulness is proved in statistics and dynamic research indirectly. It drops off immunity and outbreaks of VDT Therefore, every country has standard for symptom. limitation of EMI emission. For preventing serious interference problem, electromagnetic basically standardized not to interrupt other machine's operation such as instrument or communication facility of airplane, pulse generator of hospital, etc. Recently, government also processes to establish the restriction low due to the studies.

#### ? Construction of color TFT\_LCD module

Color TFT\_LCD is divided into a-Si (amorphous silicon) TFT and p-Si (polysilicon) TFT. The direct view TFT\_LCD using a-Si TFT is the most widely used.

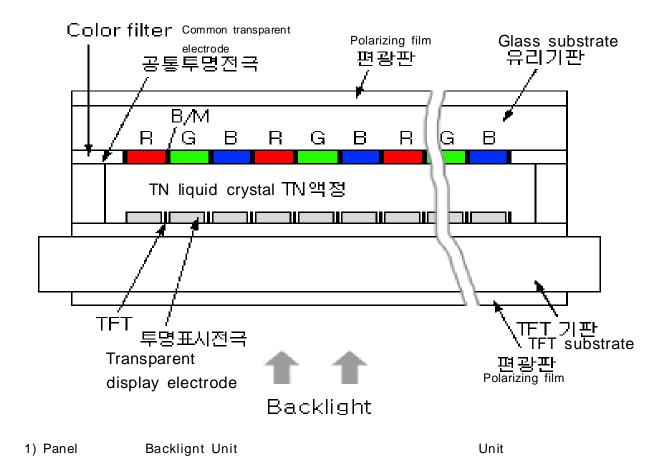

TFT\_LCD is roughly divided into the following 3 units.

First, panel with liquid crystal implanted between substrates.

Second, driving circuit includes Driver LSI for driving panel and PCB (printed circuit board) with circuit element.

Third, chassis structure with backlight.

Assembly composed of these units is called TFT\_LCD module.

Backlight:

Light is sent from backside. Liquid crystal cannot make light itself, so it controls the amount of light from backlight to display various colors. Therefore, the backlight function has deep relation with luminance. As backlight is better, luminance is higher.

Two tubes looks like fluorescent lamp are installed horizontally, and send light over the screen evenly. The light is controlled light to display liquid crystal and display various color.

The backlight of a surface light source type, which maintains even luminosity of whole screen, is needed because liquid crystal cannot make light itself and just modulates the amount of transmitted light. The requesting performance of the backlight for LCD is having even luminance of whole display surface, and maintaining enough luminance in considering transmissivity of panel, less than 10%. In case of portable LCD, it has to be lighter, thinner, and has low consumption power. CCFL (cold cathode fluorescent lamp) used as light source of backlight unit is consisted of fluorescent lamp (heat cathode shape), light guide panel, prism sheet, diffusion plate, reflection sheet, etc.

The fluorescent substance of the CCFL is mainly the rare earth (Y, Ce, Tb, etc), which has high efficiency. For LCD, fluorescent substance is consisted of 3 frequency types of white system, which is mixture of red, green, and blue fluorescent. The light guide plate takes the light from the side of acrylic plate. The light processes to the inside of the acrylic plate, and it is coming out to the front of panel by reflection plate. The reflection plate, dot type gradation pattern, controls the amount of reflection to make the backlight to have even luminance over its surface by applying less light in where close to the lamp or more light in where far from the lamp.

TFT\_LCD module has display function, and it is a subsystem of the systems such as a notebook PC, TV, or monitor.

[Construction of the TFT-LCD module]

\* Principle of LCD drive\*

1)

- a) Black Matrix: It cuts off the light from the R,G, and B element. It is formed in among pixels of color filters and absorbs the light coming from the outside to prevent the reflection.

- b) Color Filter: It is a resin film containing dyeing stuff or pigments of primary colors (red, green, and blue). Eventually, it makes the passed light through liquid crystal to have colors.

- c) Over Coat Film: It is used for making a flat surface of the color filter. It is also used for improving adhesiveness with ITO (Indium Tin Oxide), which is a material of transparent electrode due to its great transmissivity, conductivity, and chemical/thermal stability.

- d) Common Electrode: It is an electrode made of ITO, the transparent electric conductor, and adds voltage to liquid crystal cell.

- e) Alignment Film: It is a thin organic film consists of Polimide, and is formed for aligning liquid crystal.

- f) Liquid Crystal: Its thickness is normally about 5μm, and it has arrangement of twisted Nematic letters.

- g) Sealant: It is located on the edge of panel and works as an adhesive to fix TFT array substrate and color filter substrate. It makes active cell area.

- h) Picture element electrode: It is transparent and made of electric-conductive ITO. It adds the signal voltage given by TFT to liquid crystal cells.

- i) TFT: It is a switching element to give or cut off the signal voltage to liquid crystal.

- j) Storage Capacitor: It maintains the signal voltage given to pixel ITO more than a certain time.

#### 2) Backlight unit

It makes a plane light with even luminosity from a fluorescent lamp used as the light resource. The thickness of module and consumption of electricity are depending on making thinner thickness of the unit and improving coefficient of utilization of light. The light from backlight gradually decreases in brightness immediately after penetrating the display module unit. Only 5% of light coming into the backlight penetrates the front Polarizer.

#### 3) Driving circuit and Chassis unit

The TFT LCD panel consists of TFT array and color filter substrates. The drive circuit including driver IC must be installed in the peripheral part. The drive circuit takes multi layer PCB type. For the circuit part, SMT (surface mounting technology) is used for having a thinness and high density. Driver IC is made in the form of TCP (Tape carrier package) and connected between PCB and panel.

The drive circuits, TFT LCD panel, and backlight unit made as above are completed with chassis unit, and become assembled parts. It is called TFT module.

Manufacturing processes for TFT LCD panel is briefly described as

follows.

- 1) TFT array process to make switch elements, which give pixel unit signal.

- 2) Color filter process to make color array of red, green, and blue for expression of colors.

- 3) Liquid crystal process to make liquid crystal cells in between TFT substrate and color filter substrates.

The STN LCD is adopted for the LC cellular phone or car navigation, monitors, and so on, and the TFT LCD is adopted for Note PC monitor, desktop monitor, and so on. The 15" and 18" LC desktop monitors are the most popular in the world. For increasing the market share in the display field, the technique for larger size screen has to be developed.

In the technical aspect, it is difficult to maintain the LC space equally because the LC weight gets together into the middle if it is larger size. The picture quality becomes low due to the distribution of the unequal space.

Due to the weakness, PDP is developed for the 20", but its market share is small because of its expensiveness. Therefore, it is expected the lots of technical developments of the LCD for the flat display device with its high market share.

#### 3. CRT monitor and LCD monitor

The weakness of the LCD compare to the CRT

Viewing angle, after image, quantity of display color, responding speed

The strong point of the LCD

Consumption power, electromagnetic wave, size (saving space), picture quality (focus, GD, CG)

Equivalence (no problem to use and possible compensation):

Maximum luminance, contrast, flicker

Viewing angle: It is one of LCD's weakness. It is no problem to watch the 120 ° of right and left and 110 ° of top and bottom. But, if many people watch one screen, the color is turning over due to the changing viewing point with moving a head little bit to the top, bottom, right, or left. Especially, as size is larger, the viewing angle must be bigger; therefore, the technical development is necessary for larger screen.