### **OPERATING MANUAL**

### **PENTEK MODEL 6526**

32–Channel Digital Receiver VMEbus Board with RACEway

Pentek, Inc. One Park Way Upper Saddle River, NJ 07458 (201) 818–5900 http://www.pentek.com/

Copyright © 2000

Manual Part No: 800.65260

#### Manual Revision History

| Date     | <u>Manual Rev</u> | <u>Applicable Serial #'s</u> | <u>Comments</u>                                         |

|----------|-------------------|------------------------------|---------------------------------------------------------|

| 06/18/99 | Preliminary       | 9908001 – Forward            | Initial release. – Adapted from Preliminary Engineering |

| 9/20/00  | А                 |                              | Spec & Manual.<br>Updated for relase                    |

|          |                   |                              |                                                         |

|          |                   |                              |                                                         |

|          |                   |                              |                                                         |

|          |                   |                              |                                                         |

|          |                   |                              |                                                         |

#### <u>Warranty</u>

Pentek warrants that all products manufactured by Pentek conform to published Pentek specifications and are free from defects in materials and workmanship for a period of one year from the date of delivery when used under normal operating conditions and within the service conditions for which they were furnished.

The obligation of Pentek arising from a warranty claim shall be limited to repairing or at its option, replacing without charge, any product which in Pentek's sole opinion proves to be defective within the scope of the warranty.

Pentek must be notified in writing of the defect or nonconformity within the warranty period and the affected product returned to Pentek within thirty days after discovery of such defect or nonconformity.

Buyer shall prepay shipping charges, taxes, duties, and insurance for products returned to Pentek for warranty service. Pentek shall pay for the return of products to buyer except for products returned from another country.

Pentek shall have no responsibility for any defect or damage caused by improper installation, unauthorized modification, misuse, neglect, inadequate maintenance, or accident, or for any product which has been repaired or altered by anyone other than Pentek or its authorized representatives.

The warranty described above is buyer's sole and exclusive remedy and no other warranty, whether written or oral, is expressed or implied. Pentek specifically disclaims fitness for a particular purpose. Under no circumstances shall Pentek be liable for any direct, indirect, special, incidental, or consequential damages, expenses, losses or delays (including loss of profits) based on contract, tort, or any other legal theory.

#### **Copyrights**

With the exception of those items listed below, the contents of this publication are copyright © 2000, Pentek, Inc. All Rights Reserved. Contents of this publication may not be reproduced in any form without written permission.

Appendix C, Graychip 4014 Datasheet, is the copyrighted property of Graychip, Inc., Palo Alto CA. Appendix D, PitCrewJr. Datasheet, is the copyrighted property of Cypress Semiconductor Corporation, San Jose, CA.

#### <u>Trademarks</u>

RACE and RACEway are registered trademarks or trademarks of Mercury Computer Systems, Inc.

#### Page

#### Chapter 1: Overview

| 1.1  | Introduction                         | 11 |

|------|--------------------------------------|----|

| 1.2  | Digital Receiver                     | 11 |

| 1.3  | Synchronization                      | 11 |

| 1.4  | Time Stamp Counter                   | 12 |

| 1.5  | Command Controller / DSP             |    |

| 1.6  | Channel Formatters                   | 12 |

| 1.7  | VMEbus Interface                     | 13 |

| 1.8  | RACEway Interface                    | 13 |

| 1.9  | Digital Interfaces                   | 13 |

| 1.10 | Model 6526 Block Diagram             | 14 |

|      | Figure 1–1: Model 6526 Block Diagram | 14 |

| 1.11 | Specifications                       | 15 |

#### Chapter 2: Installation and Connections

| 2.1 | Inspect | ion                                      |                                                                    | 17 |  |  |

|-----|---------|------------------------------------------|--------------------------------------------------------------------|----|--|--|

| 2.2 | VMEb    | us A16 Base                              | e Address Switches                                                 | 17 |  |  |

|     | Figure  | Figure 2–1: Model 6526 – Rotary Switches |                                                                    |    |  |  |

|     | Figure  | 2–2: Mode                                | 1 6526 VME Board – Component Side Assembly Drawing                 | 18 |  |  |

|     | Figure  | 2–3: Mode                                | 1 6526 VME Board – Solder Side Assembly Drawing                    | 19 |  |  |

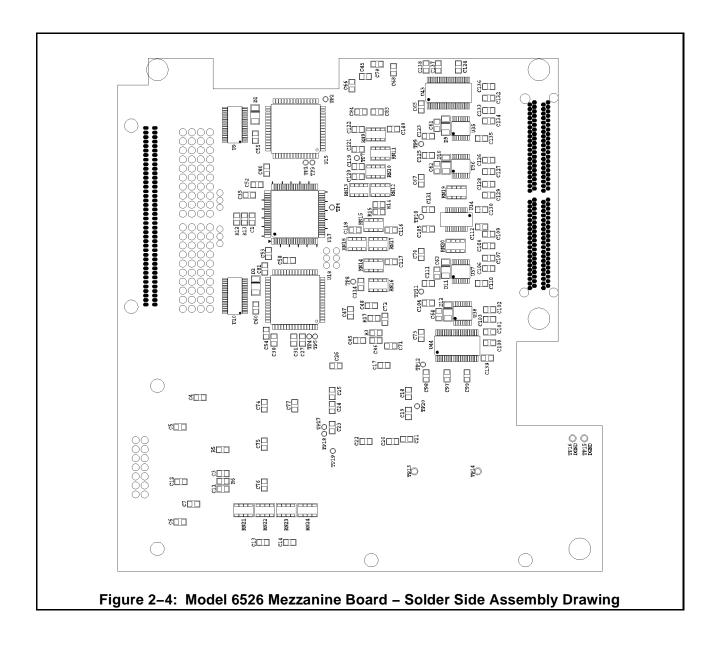

|     | Figure  | 2–4: Mode                                | l 6526 Mezzanine Board – Solder Side Assembly Drawing              | 20 |  |  |

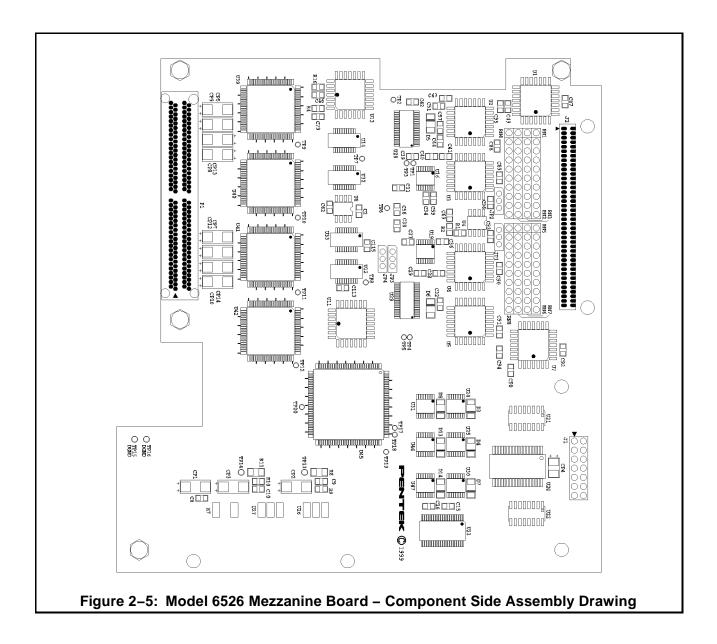

|     | Figure  | 2–5: Mode                                | 1 6526 Mezzanine Board – Component Side Assembly Drawing           | 21 |  |  |

| 2.3 | -       |                                          | ings on the Model 6526                                             |    |  |  |

|     | Table   | 2–1: RACE                                | way RESET Enable Jumper JP3                                        | 22 |  |  |

| 2.4 |         |                                          | Panel                                                              |    |  |  |

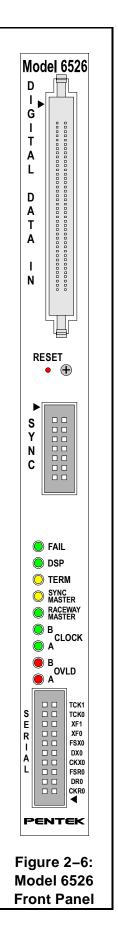

|     | Figure  | Figure 2–6: Model 6526 Front Panel       |                                                                    |    |  |  |

|     | 2.4.1   | Digital D                                | Data Input Connector                                               | 23 |  |  |

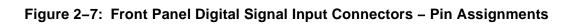

|     |         |                                          | -7: Front Panel Digital Signal Input Connectors – Pin Assignments. |    |  |  |

|     |         | 2.4.1.1                                  | Connecting a Watkins-Johnson Model WJ-9107 to Model 6526           | 25 |  |  |

|     |         |                                          | Table 2–2: Input Connections – Watkins–Johnson Model 9107          |    |  |  |

|     |         |                                          | to Pentek Model 6526 with Pentek Model 2126 Cable                  |    |  |  |

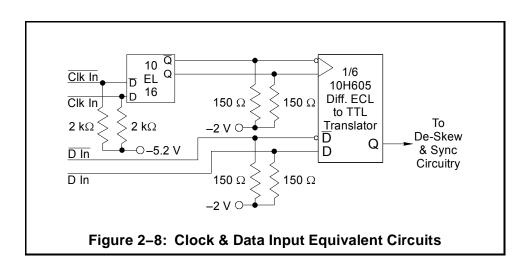

|     |         | 2.4.1.2                                  | Input Equivalent Circuits – Option 002                             |    |  |  |

|     |         |                                          | Figure 2–8: Clock & Data Input Equivalent Circuits                 |    |  |  |

|     | 2.4.2   |                                          | 5                                                                  |    |  |  |

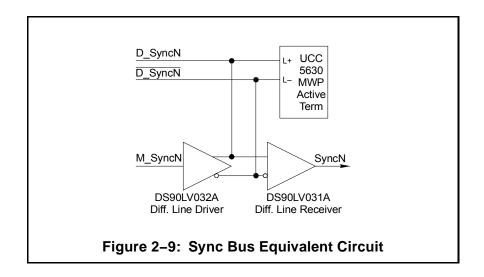

|     |         | 2.4.2.1                                  | Sync Bus Connector                                                 |    |  |  |

|     |         |                                          | Table 2–3: Front Panel Sync Bus Connector Pinout                   |    |  |  |

|     |         | 2.4.2.2                                  | Sync Bus / Receiver Assignments                                    |    |  |  |

|     |         | 2.4.2.3                                  | Sync Bus Signal Characteristics                                    |    |  |  |

|     |         |                                          | Table 2–4: Sync Bus Signals and their Associated Receivers         |    |  |  |

|     |         | 2.4.2.4                                  | Sync Bus Equivalent Circuit                                        |    |  |  |

|     |         |                                          | Figure 2–9: Sync Bus Equivalent Circuit                            | 30 |  |  |

2.5

### Table of Contents (continued)

#### Page

#### Chapter 2: Installation and Connections (continued)

| 2.4.3    | TMS320                              | C31 Serial Port                                                                                                                                                                                                                                                                                |                                              |

|----------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|          | Table 2-                            | -5: Front Panel Serial Port Connector                                                                                                                                                                                                                                                          |                                              |

| 2.4.4    | Reset Bu                            | ıtton                                                                                                                                                                                                                                                                                          |                                              |

| 2.4.5    | LED Ind                             | licators                                                                                                                                                                                                                                                                                       |                                              |

|          | 2.4.5.1                             | Overload Indicator LEDs (OVLD A & B)                                                                                                                                                                                                                                                           |                                              |

|          | 2.4.5.2                             | Clock Signal Present LEDs (CLOCK A & B)                                                                                                                                                                                                                                                        |                                              |

|          | 2.4.5.3                             |                                                                                                                                                                                                                                                                                                |                                              |

|          | 2.4.5.4                             | Sync Bus Master LED (SYNC MASTER)                                                                                                                                                                                                                                                              |                                              |

|          | 2.4.5.5                             | Sync Bus Terminator LED (TERM)                                                                                                                                                                                                                                                                 |                                              |

|          | 2.4.5.6                             |                                                                                                                                                                                                                                                                                                |                                              |

|          | 2.4.5.7                             | FAIL LED                                                                                                                                                                                                                                                                                       |                                              |

| Insertin | g and Ren                           | noving the Model 6526 in the VMEbus Card Cage                                                                                                                                                                                                                                                  |                                              |

| 2.5.1    | Inserting                           | g the Unit                                                                                                                                                                                                                                                                                     |                                              |

| 2.5.2    |                                     |                                                                                                                                                                                                                                                                                                |                                              |

|          | 2.4.4<br>2.4.5<br>Insertin<br>2.5.1 | Table 2-           2.4.4         Reset Bu           2.4.5         LED Inc.           2.4.5         2.4.5.1           2.4.5.2         2.4.5.2           2.4.5.3         2.4.5.4           2.4.5.5         2.4.5.6           2.4.5.7         Inserting and Ren           2.5.1         Inserting | Table 2–5: Front Panel Serial Port Connector |

#### Chapter 3: Memory Maps and Register Descriptions

| 3.1 | Program | mming Ove    | erview                             |    |

|-----|---------|--------------|------------------------------------|----|

| 3.2 |         |              | Modifier Codes                     |    |

| 3.3 | VMEbu   | ıs Access    |                                    |    |

|     | Table 3 | 3–1: VMEb    | ous Address Modifier Codes         |    |

| 3.4 | VMEbı   | us A16 Slave | e Memory                           |    |

|     | Table 3 | 3–2: VMEb    | us A16 Slave Memory Map            |    |

|     | 3.4.1   | VMEbus       | Board Control Register             |    |

|     |         |              | 3: VMEbus Board Control Register   |    |

|     |         | 3.4.1.1      | General Hardware Reset             |    |

|     |         | 3.4.1.2      | DSP Reset                          |    |

|     |         | 3.4.1.3      | Special Hardware Reset             |    |

|     |         | 3.4.1.4      | A24 Unique Address Space Enable    |    |

|     |         | 3.4.1.5      | A32 Unique Address Space Enable    |    |

|     |         | 3.4.1.6      | A24 Broadcast Address Space Enable |    |

|     |         | 3.4.1.7      | A32 Broadcast Address Space Enable |    |

|     |         | 3.4.1.8      | VMEbus Access                      |    |

|     |         | 3.4.1.9      | Word Swap                          |    |

|     |         | 3.4.1.10     | General Reset Done                 |    |

|     | 3.4.2   | Sync Bus     | Gontrol Register                   | 41 |

|     |         | Table 3–     | 4: Sync Bus Control Register       |    |

|     |         | 3.4.2.1      | Sync Bus Master                    |    |

|     |         | 3.4.2.2      | Sync Bus Termination               |    |

|     | 3.4.3   | VMEbus       | Interrupt to 'C31 DSP              |    |

|     |         |              |                                    |    |

# Table of Contents (continued)

|     | 3.4.4   | VMEbus     | Unique A24/A32 Base Address Register               |    |

|-----|---------|------------|----------------------------------------------------|----|

|     |         | Table 3–   | -5: VMEbus Unique A24/A32 Base Address Register    | 42 |

|     |         | 3.4.4.1    | VMEbus Unique A32 Base Address                     |    |

|     |         | 3.4.4.2    | VMEbus Unique A24 Base Address                     |    |

|     | 3.4.5   | VMEbus     | Broadcast A24/A32 Base Address Register            | 44 |

|     |         |            | -6: VMEbus Broadcast A24/A32 Base Address Register |    |

|     |         | 3.4.5.1    | VMEbus Broadcast A32 Base Address                  |    |

|     |         | 3.4.5.2    | VMEbus Broadcast A24 Base Address                  | 45 |

|     | 3.4.6   | Built–In   | Self-Test (BIST) Control Register                  | 46 |

|     |         | Table 3–   | -7: Built–In Self–Test Control Register            | 46 |

|     |         | 3.4.6.1    | BIST Enable                                        |    |

|     |         | 3.4.6.2    | BIST Active                                        | 46 |

|     |         | 3.4.6.3    | BIST Results                                       | 46 |

| 3.5 | VMEbu   | is A24/A32 | 2 Global Slave Register Memory                     | 47 |

|     | Table 3 | -8: VMEb   | us A24/A32 Global Slave Register Memory Map        | 48 |

|     | 3.5.1   |            | Board Control Register                             |    |

|     |         |            | -9: VMEbus Board Control Register                  |    |

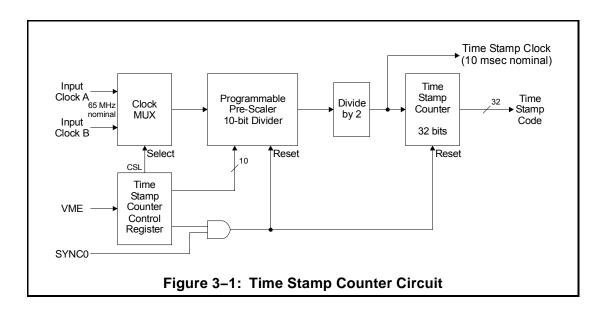

|     | 3.5.2   |            | mp Counter Control Register                        |    |

|     |         |            | -1: Time Stamp Counter Circuit                     |    |

|     |         |            | -10: Time Stamp Counter Control Register           |    |

|     |         | 3.5.2.1    | Synchronous Reset Enable                           | 50 |

|     |         | 3.5.2.2    | Pre-Scaler Clock Source Select                     | 50 |

|     |         | 3.5.2.3    | Pre-Scaler Divisor                                 | 50 |

|     | 3.5.3   | Time Sta   | mp Counter Output Register                         | 50 |

|     |         | Table 3–   | -11: Time Stamp Counter Output Register            | 50 |

|     | 3.5.4   |            | nerator Mask Register                              |    |

|     |         | Table 3–   | -12: Sync Generator Mask Register                  | 51 |

|     | 3.5.5   | Channel    | Formatter Reset Control Register                   | 51 |

|     |         | Table 3–   | -13: Channel Formatter Reset Control Register      | 51 |

|     | 3.5.6   | RACEwa     | ay Status Register                                 | 52 |

|     |         | Table 3–   | -14: RACEway Status Register                       | 52 |

|     |         | 3.5.6.1    | Active Channel                                     |    |

|     |         | 3.5.6.2    | Sending                                            | 53 |

|     |         | 3.5.6.3    | Suspended                                          |    |

|     |         | 3.5.6.4    | Master                                             | 53 |

|     |         | 3.5.6.5    | Slave                                              | 53 |

|     |         | 3.5.6.6    | Master Go                                          | 53 |

|     |         | 3.5.6.7    | Master Error                                       | 54 |

|     |         | 3.5.6.8    | Diagnostics                                        | 54 |

|     |         | 3.5.6.9    | Channel Request                                    | 54 |

|     |         |            |                                                    |    |

Page

| 3.5.7  | Sync Gen  | erator Execute Register                                         | 55  |

|--------|-----------|-----------------------------------------------------------------|-----|

|        | Table 3–2 | 15: Sync Generator Execute Register                             | 55  |

|        | 3.5.7.1   | Sync Generate Command                                           |     |

|        | 3.5.7.2   | Clock A Readback                                                |     |

|        | 3.5.7.3   | Clock B Readback                                                | 55  |

| 3.5.8  | Output F  | IFO Status Register                                             | 56  |

|        |           | 16: Output FIFO Status Register                                 |     |

|        | 3.5.8.1   | FIFO Empty Flags                                                |     |

|        | 3.5.8.2   | FIFO Full Flags                                                 |     |

| 3.5.9  | Clock Sta | tus Register                                                    | 57  |

|        | Table 3–1 | 17: Clock Status Register                                       | 57  |

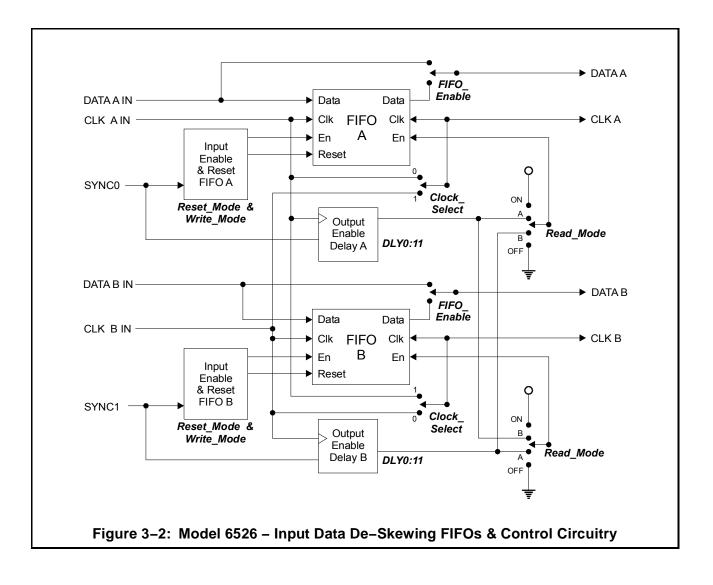

| 3.5.10 | Input Dat | ta De–Skewing FIFOs                                             | 57  |

|        | Figure 3- | 2: Model 6526 – Input Data De–Skewing FIFOs & Control Circuitry | .58 |

| 3.5.11 |           | O A Delay Control Register                                      |     |

|        | Table 3–1 | 18: Input FIFO A Delay Control Register                         | 60  |

| 3.5.12 |           | O B Delay Control Register                                      |     |

|        |           | 19: Input FIFO B Delay Control Register                         |     |

| 3.5.13 |           | O A Control Register                                            |     |

|        | Table 3-2 | 20: Input FIFO A Control Register                               | 61  |

|        | 3.5.13.1  | Reset Mode                                                      | 61  |

|        |           | Table 3–21: Input FIFO A Reset Mode                             | 61  |

|        | 3.5.13.2  | Write Mode                                                      | 62  |

|        |           | Table 3–22: Input FIFO A Write Mode                             | 62  |

|        | 3.5.13.3  | Read Mode                                                       | 62  |

|        |           | Table 3–23: Input FIFO A Read Mode                              | 62  |

|        | 3.5.13.4  | Clock Select                                                    | 63  |

|        | 3.5.13.5  | FIFO Enable                                                     | 63  |

|        | 3.5.13.6  | Input Word Length                                               | 63  |

|        | 3.5.13.7  | Front Panel Sync Enable                                         | 63  |

| 3.5.14 | Input FIF | O B Control Register                                            | 65  |

|        | Table 3-2 | 24: Input FIFO B Control Register                               | 65  |

|        | 3.5.14.1  | Reset Mode                                                      | 65  |

|        |           | Table 3–25: Input FIFO B Reset Mode                             | 65  |

|        | 3.5.14.2  | Write Mode                                                      |     |

|        |           | Table 3–26: Input FIFO B Write Mode                             | 66  |

|        | 3.5.14.3  | Read Mode                                                       |     |

|        |           | Table 3–27: Input FIFO B Read Mode                              | 66  |

|        | 3.5.14.4  | Clock Select                                                    | 67  |

|        | 3.5.14.5  | FIFO Enable                                                     |     |

|        | 3.5.14.6  | Input Word Length                                               | 67  |

|        | 3.5.14.7  | Front Panel Sync Enable                                         | 67  |

#### Page

| 3.6 | VMEbu   | s A24/A32                                                                   | 2 Channel Formatter Register Memory               | 68 |  |  |

|-----|---------|-----------------------------------------------------------------------------|---------------------------------------------------|----|--|--|

|     | Table 3 | Table 3–28: VMEbus A24/A32 Channel Formatter Register Memory Map            |                                                   |    |  |  |

|     |         |                                                                             | Address Ranges for Channel Formatter Registers    |    |  |  |

|     | 3.6.1   |                                                                             | ay Data Packet Structure                          |    |  |  |

|     |         |                                                                             | -30: RACEway Data Packet Structure                |    |  |  |

|     | 3.6.2   |                                                                             | tart Code Register                                |    |  |  |

|     |         |                                                                             | -31: Packet Start Code Register                   |    |  |  |

|     | 3.6.3   |                                                                             | n ID Tag Registers                                |    |  |  |

|     |         |                                                                             | -32: Channel n ID Tag Registers                   |    |  |  |

|     |         | 3.6.3.1                                                                     | Destination Processor ID                          |    |  |  |

|     |         | 3.6.3.2                                                                     | Destination Board ID                              | 72 |  |  |

|     |         | 3.6.3.3                                                                     | Source DDR Channel ID                             | 72 |  |  |

|     |         | 3.6.3.4                                                                     | Source DDR Board ID                               | 72 |  |  |

|     | 3.6.4   | Channel                                                                     | n Block Counter Output Register                   | 73 |  |  |

|     |         | Table 3–                                                                    | -33: Channel n Block Counter Output Register      | 73 |  |  |

|     | 3.6.5   | Time Sta                                                                    | mp Counter Output Register                        | 73 |  |  |

|     |         | Table 3–                                                                    | -34: Time Stamp Counter Output Register           | 73 |  |  |

|     | 3.6.6   | Channel                                                                     | n DDR Complex Output Data Register                | 74 |  |  |

|     |         | Table 3–                                                                    | -35: Channel n DDR Complex Data Output Register   | 74 |  |  |

|     |         | 3.6.6.1                                                                     | DDR Output Data: In-Phase (Real) Component        |    |  |  |

|     |         | 3.6.6.2                                                                     | DDR Output Data: Quadrature (Imaginary) Component | 74 |  |  |

|     | 3.6.7   |                                                                             | top Code Register                                 |    |  |  |

|     |         |                                                                             | -36: Packet Stop Code Register                    |    |  |  |

|     | 3.6.8   |                                                                             | n Formatter Status Register                       |    |  |  |

|     |         |                                                                             | -37: Channel n Formatter Status Register          |    |  |  |

|     |         | 3.6.8.1                                                                     | RACEway FIFO Full                                 |    |  |  |

|     |         | 3.6.8.2                                                                     | Packet Send Request                               |    |  |  |

|     |         | 3.6.8.3                                                                     | Sync Word Substitution Armed                      |    |  |  |

|     |         | 3.6.8.4                                                                     | Block Counter Synchronous Reset Armed             |    |  |  |

|     | 3.6.9   |                                                                             | n Formatter Control Register                      |    |  |  |

|     |         |                                                                             | -38: Channel n Formatter Control Register         |    |  |  |

|     |         | 3.6.9.1                                                                     | Sync Word Substitution Enable                     |    |  |  |

|     |         | 3.6.9.2                                                                     | Block Counter Synchronous Reset Enable            |    |  |  |

|     |         | 3.6.9.3                                                                     | Packet Output Enable                              |    |  |  |

|     |         | 3.6.9.4                                                                     | Channel Formatter Enable                          |    |  |  |

|     |         | 3.6.9.5                                                                     | Mode Selection                                    |    |  |  |

|     |         | 3.6.9.6                                                                     | Packet Start Delay                                |    |  |  |

|     |         | 3.6.9.7                                                                     | Number of Packets per Trigger                     |    |  |  |

|     | 3.6.10  |                                                                             | n RACEway Packet Size Register                    |    |  |  |

|     |         |                                                                             | -39: Channel n RACEway Packet Size Register       |    |  |  |

|     |         | Table 3–40: Channel n RACEway Packet Size Register – Packet Size Settings81 |                                                   |    |  |  |

|     | 3.6.11  |                                                                             | n Sync Code Word Register                         |    |  |  |

|     |         | Table 3–                                                                    | -41: Channel n Sync Code Word Register            | 82 |  |  |

Page

#### Chapter 3: Memory Maps and Register Descriptions (continued)

| 3.6.12  | Channel           | n RACEway Routing Register                                    | 83 |

|---------|-------------------|---------------------------------------------------------------|----|

|         | Table 3–          | 42: Channel n RACEway Routing Register                        | 83 |

|         | 3.6.12.1          | Mode Selection                                                |    |

|         | 3.6.12.2          | Routing Priority Code                                         | 83 |

|         |                   | Table 3-43: RACEway Routing Register - Priority Codes         | 84 |

|         | 3.6.12.3          | Broadcast Accept Code                                         | 84 |

|         | 3.6.12.4          | RACEway Route Fields                                          | 85 |

|         |                   | Table 3-44: RACEway Routing Register – Route Field Exit Codes | 85 |

| 3.6.13  | Channel           | n RACEway Start Address Register                              | 86 |

|         | Table 3–          | 45: Channel n RACEway Start Address Register                  | 86 |

|         | 3.6.13.1          | Lock Flag                                                     | 86 |

|         | 3.6.13.2          | Read Flag                                                     | 86 |

|         | 3.6.13.3          | Start Address Fiel                                            |    |

|         | 3.6.13.4          | Width/Alignment Field                                         | 87 |

| 3.6.14  | Channel           | n RACEway End Address Register                                | 88 |

|         | Table 3–          | 46: Channel n RACEway End Address Register                    | 88 |

|         | 3.6.14.1          | • •                                                           |    |

|         | 3.6.14.2          | RACEway Address Mod                                           | 90 |

| Dual Po | ort Memory        | and Command Tables                                            |    |

| Table 3 | <b>3–47: Dual</b> | Port SRAM Usage Memory Map                                    | 91 |

|         |                   | nand Table Header Words Memory Map                            |    |

|         |                   | nand Table Start Addresses                                    |    |

| 3.7.1   |                   | nd Table Header Word #1: Command Control                      |    |

| 0       |                   | -50: Command Table Header Word #1: Command Control            |    |

|         | 3.7.1.1           | Single Load                                                   |    |

|         | 3.7.1.2           | Schedule Command                                              |    |

|         | 3.7.1.3           | Command Table Length                                          |    |

|         | 3.7.1.4           | Data Format                                                   |    |

|         | 01111             | Table 3–51: Command Table Header Word 1 – Data Format         |    |

| 3.7.2   | Comman            | nd Table Header Word #2: Channel Mask                         |    |

| 0.,     |                   | -52: Command Table Header Word #2: Channel Mask               |    |

| 3.7.3   |                   | nd Table Header Word #3: Timestamp                            |    |

| 011.10  |                   | -53: Command Table Header Word #3: Timestamp                  |    |

| 3.7.4   |                   | nd Table Header Word #4: Command Status                       |    |

| 0.7.1   |                   | -54: Command Table Header Word #4: Command Status             |    |

|         | 3.7.4.1           | Command Complete                                              |    |

|         | 3.7.4.2           | Command Error                                                 |    |

|         | 3.7.4.3           | Command Parameter Error                                       |    |

|         | 3.7.4.4           | Command Error Location                                        |    |

| 3.7.5   |                   | nd Set                                                        |    |

| 3.7.6   |                   | ble Library Functions                                         |    |

| 5.7.0   | C Callai          | or Library runcholis                                          | 70 |

3.7

#### Page

| 3.8 | ′C31 DS                                                                   | SP Memory  | Maps and Registers                                        | 99  |  |  |  |

|-----|---------------------------------------------------------------------------|------------|-----------------------------------------------------------|-----|--|--|--|

|     |                                                                           |            | /lemory Map – Local SRAM, Dual–Port SRAM, VMEbus Register |     |  |  |  |

|     |                                                                           |            | Aemory Map – Channel Formatter Registers                  |     |  |  |  |

|     |                                                                           |            | Address Ranges for Channel Formatter Registers            |     |  |  |  |

|     | Table 3–58: 'C31 Memory Map – VME port DPSRAM, Boot Flash, 'C31, Graychip |            |                                                           |     |  |  |  |

|     |                                                                           |            | Aemory Map – Internal, Time Stamp, Overload, Interrupts   |     |  |  |  |

|     | 3.8.1                                                                     |            | O Control Register                                        |     |  |  |  |

|     | 0.0.1                                                                     |            | 60: 'C31 LED Control Register                             |     |  |  |  |

|     |                                                                           | 3.8.1.1    | BIST Fail                                                 |     |  |  |  |

|     |                                                                           | 3.8.1.2    | DSP LED                                                   |     |  |  |  |

|     | 3.8.2                                                                     |            | c Arm Register                                            |     |  |  |  |

|     |                                                                           |            | 61: 'C31 Sync Arm Register                                |     |  |  |  |

|     |                                                                           | 3.8.2.1    | Local Sync Arm                                            |     |  |  |  |

|     |                                                                           | 3.8.2.2    | Time Stamp Counter Reset Arm                              |     |  |  |  |

|     | 3.8.3                                                                     | 'C31 Syne  | c Word Substitution Register                              |     |  |  |  |

|     |                                                                           |            | 62: 'C31 Sync Word Substitution Register                  |     |  |  |  |

|     | 3.8.4                                                                     |            | c Block Counter Reset Register                            |     |  |  |  |

|     |                                                                           | Table 3–   | 63: 'C31 Sync Block Counter Reset Register                | 105 |  |  |  |

|     | 3.8.5                                                                     |            | trol Register                                             |     |  |  |  |

|     |                                                                           | Table 3–   | 64: 'C31 Control Register                                 | 106 |  |  |  |

|     |                                                                           | 3.8.5.1    | Clock Source                                              |     |  |  |  |

|     |                                                                           |            | Table 3–65: Clock Source / Channel Association            | 106 |  |  |  |

|     |                                                                           | 3.8.5.2    | Sync Source                                               |     |  |  |  |

|     |                                                                           |            | Table 3–66: Sync Source / Signal Association              |     |  |  |  |

|     |                                                                           | 3.8.5.3    | Test Clock                                                |     |  |  |  |

|     |                                                                           | 3.8.5.4    | VME Interrupt                                             |     |  |  |  |

|     |                                                                           | 3.8.5.5    | Local General Hardware Reset                              |     |  |  |  |

|     | 3.8.6                                                                     |            | mp Counter Output Register                                |     |  |  |  |

|     |                                                                           |            | 67: Time Stamp Counter Output Register                    |     |  |  |  |

|     | 3.8.7                                                                     |            | l Detection Control Registers                             |     |  |  |  |

|     |                                                                           |            | 68: 'C31 Overload Detection Control Registers             |     |  |  |  |

|     |                                                                           | 3.8.7.1    | Crossing Count                                            |     |  |  |  |

|     |                                                                           |            | Table 3–69: Crossing Count Codes                          |     |  |  |  |

|     |                                                                           | 3.8.7.2    | Threshold Level                                           |     |  |  |  |

|     |                                                                           |            | Table 3–70: Threshold Level Codes                         |     |  |  |  |

|     | <b>a</b> o o                                                              | 3.8.7.3    | Overload Detector Enable                                  |     |  |  |  |

|     | 3.8.8                                                                     | -          | Vector Register                                           |     |  |  |  |

|     | 200                                                                       |            | 71: Interrupt Vector Register                             |     |  |  |  |

|     | 3.8.9                                                                     | Interrupt  | Mask Register                                             | 110 |  |  |  |

|     |                                                                           | Table $3-$ | 72: Interrupt Mask Register                               | 110 |  |  |  |

|     |                                                                           | Table 3–   | 73: Interrupt Bit Conditions                              | 110 |  |  |  |

Page

#### Chapter 3: Memory Maps and Register Descriptions (continued)

| 3.8.10 | Interrupt Status Register #0                                                | 111 |

|--------|-----------------------------------------------------------------------------|-----|

|        | Table 3–74: Interrupt Status Register #0                                    |     |

| 3.8.11 | Interrupt Status Register #1: VME Interrupt                                 |     |

|        | Table 3–75: Interrupt Status Register #1                                    | 111 |

| 3.8.12 | Interrupt Status Register #2: Channel Formatter Error / FIFO Full Interrupt |     |

|        | Table 3–76: Interrupt Status Register #2                                    | 112 |

| 3.8.13 | Interrupt Status Register #3: Time Stamp Interrupt                          | 112 |

|        | Table 3–77: Interrupt Status Register #3                                    | 112 |

| 3.8.14 | Built–In Self–Test (BIST) Register                                          |     |

|        | Table 3–78: Built–In Self–Test Register                                     |     |

#### Appendix A: Boot EEPROM Source Code Listing

| A.1 | Boot EPROM Source Code Listing | A–1 |  |

|-----|--------------------------------|-----|--|

|     |                                |     |  |

#### Appendix B: RACEway Interlink Modules

| B.1 | Overview                                             | B–1 |

|-----|------------------------------------------------------|-----|

| B.2 | RACEway ILK1                                         | B–1 |

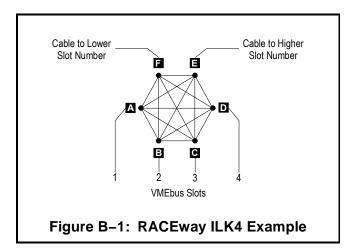

| B.3 | RACEway ILK 4 Example                                | B–1 |

|     | Figure B–1: RACEway ILK4 Example                     |     |

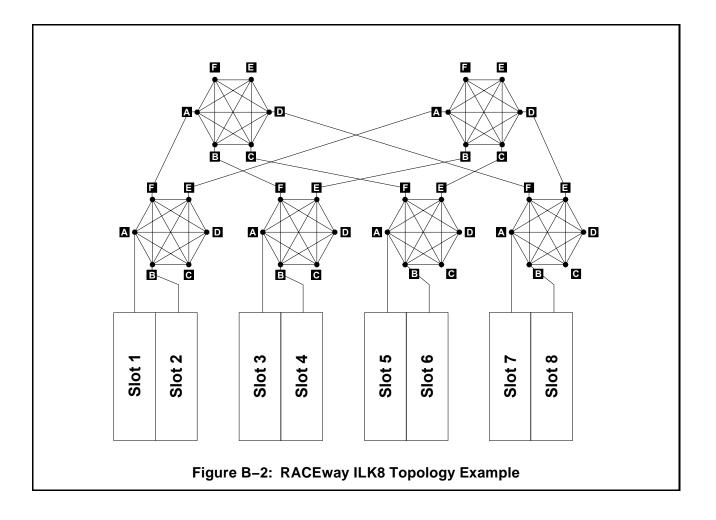

| B.4 | RACEway ILK 8 Example                                |     |

|     | Figure B-2: RACEway ILK8 Topology Example            |     |

|     | B.4.1 ILK8 Example RACEway Transaction Routing Codes | В–3 |

|     | Table B-1: ILK8 Routing Code Examples                |     |

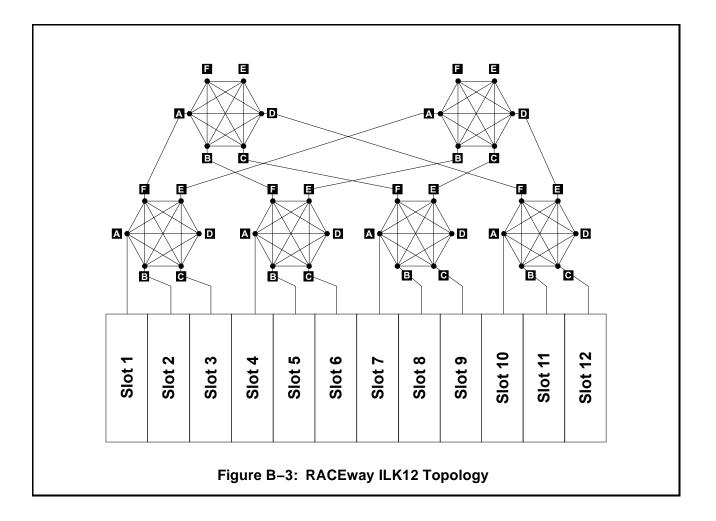

| B.5 | RACEway ILK12 Example                                |     |

|     | Figure B-3: RACEway ILK12 Topology                   |     |

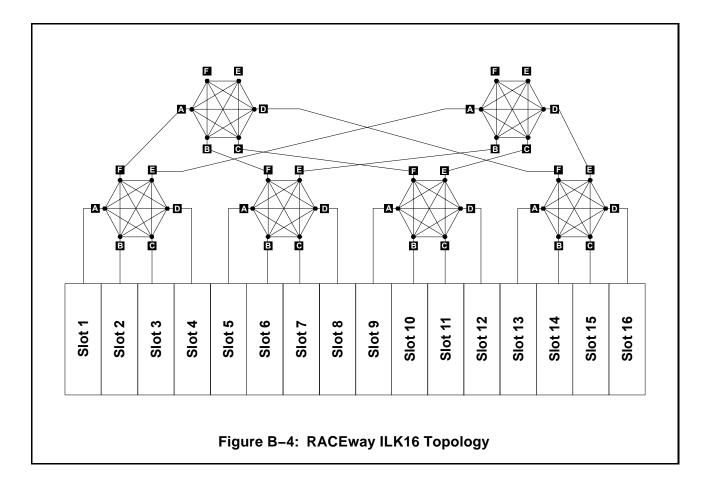

| B.6 | RACEway ILK16 Example                                |     |

|     | Figure B-4: RACEway ILK16 Topology                   |     |

|     | 0 7 1 07                                             |     |

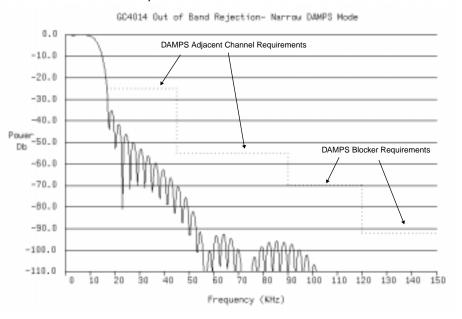

#### Appendix C: Graychip 4014

| C.1 Intro | ductionC | ]— | 1 |

|-----------|----------|----|---|

|-----------|----------|----|---|

#### Appendix D: PitCREWjr

### Chapter 1: Overview

#### 1.1 Introduction

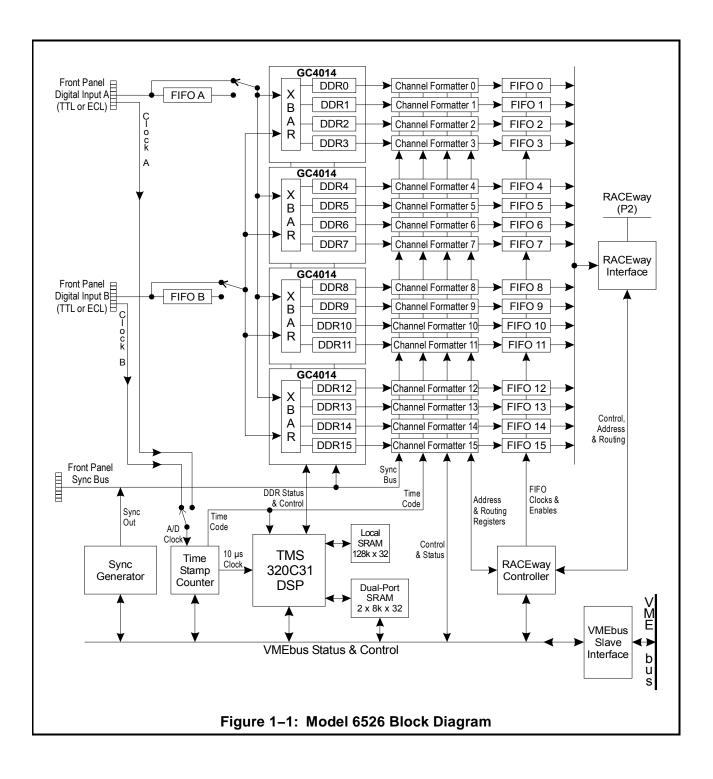

The Model 6526 is a 16–Channel, two input, Narrowband Digital Receiver for the VMEbus. It features a RACEway<sup>™</sup> interface for output data, and several on–board control sections for supporting input switching, multi–board synchronization, and time code stamping of data. The Model 6526 is a single–slot, 6U VME board with front panel connections for input clock, input data, and synchronization signals. It includes a 32–bit VMEbus slave interface for control and status.

The RACEway interface allows packets of data from each receiver channel to be directed to different RACEway–equipped VME boards, including memory and DSP functions. RACEway is a high–speed, synchronous backplane bus capable of deliver–ing 32–bit word transfers between VME boards at a peak rate of 160 MB/sec. It offers significant advantages for VMEbus systems by providing a high–speed data channel completely independent of the VMEbus. The interface utilizes the 64 user–defined pins of the VME P2 connector, which are usually unconnected pins in most backplanes.

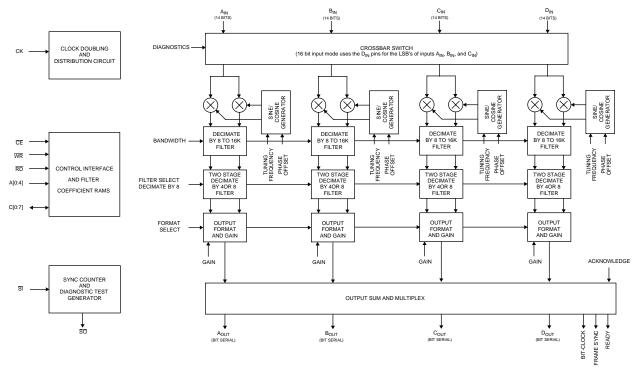

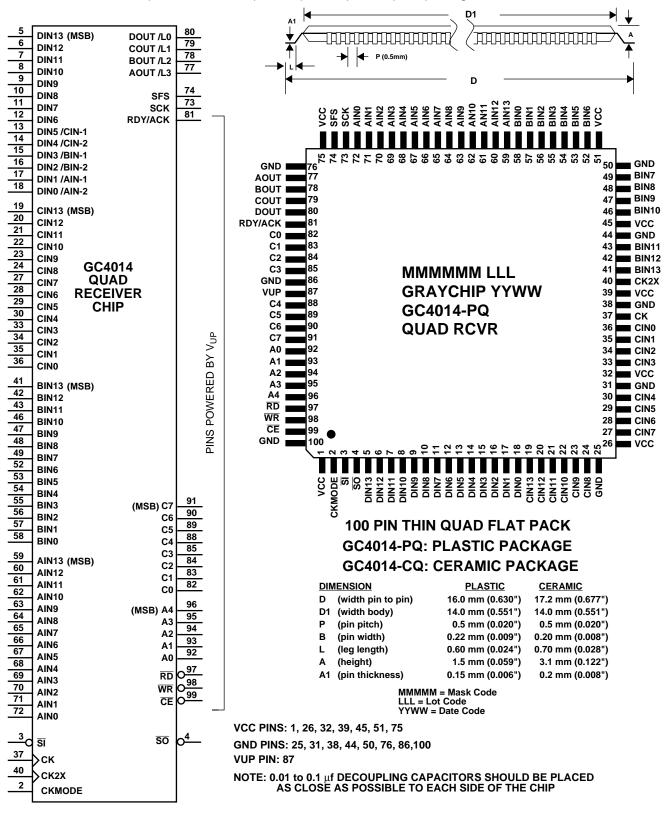

#### 1.2 Digital Receiver

The Model 6526 uses four Graychip GC4014 Quad Narrowband Digital Drop Receivers (DDRs) to provide a total of 16 receiver channels. Two front panel parallel digital data inputs operate at either TTL or differential ECL logic levels, and support up to 16 bits of data and one clock at sampling rates up to 62.5 MHz for ECL and 50 MHz for TTL. The clock for the two inputs must be the same to meet the timing requirements of the GC4014's. The front panel inputs are directly compatible with the digital output of Pentek's Series 64xx A/D Converters.

The two parallel input signals are connected to two 16–bit inputs of each GC4014. Within the GC4014, input crossbar switches allow any DDR channel to independently select either of the two input signals. The GC4014's are controlled by commands from the VMEbus and by an on–board TMS320C31 DSP (Digital Signal Processor) for setting all operational parameters of the receiver channels.

#### 1.3 Synchronization

The front panel of the Model 6526 has a Sync bus that can be bridged across all Model 6526's in a system. It is used to distribute four synchronization signals to all connected boards for synchronizing each of the of the same-channel DDR sections on each board. An on-board Sync Generator controlled by VMEbus commands can generate any number of sync signals (1 to 4) for output to the Sync bus.

#### **1.4** Time Stamp Counter

The Time Stamp Counter is a 32–bit digital counter which acts as a master time code reference for the board. It is used for time stamping data packets from the receivers, and for determining when input switching commands are performed. It advances its code using a nominal 10 µsec clock derived by dividing (pre–scaling) the input clock from either parallel digital input.

#### 1.5 Command Controller / DSP

The TMS320C31 Digital Signal Processor controls the receivers by using a list of input switching times for each of the 16 channels. This list is written through the VMEbus interface into a table, and then examined once every 10 µsec to determine if any DDR channel should change its input switch setting for the current 32–bit time stamp.

#### **1.6 Channel Formatters**

Sixteen identical Channel Formatter sections accept serial output data from the GC4014 DDRs, convert the data to 32–bit parallel words, and then form data packets (blocks) containing channel identification, the block number, the time stamp value, and a pro–grammable number of complex DRR data samples. The channel identification and block counter values are programmable over the VMEbus interface.

Optionally, the Channel Formatter also inserts a special Sync Code pattern into the data sequence, replacing two consecutive DDR samples following the receipt of the Sync bus signal for that channel.

Additionally, the Channel Formatter stores the RACEway routing code and the RACEway address for each channel into VME-programmable registers. This allows each channel's data packet to be directed to any RACEway board and then steered to any resource on that board.

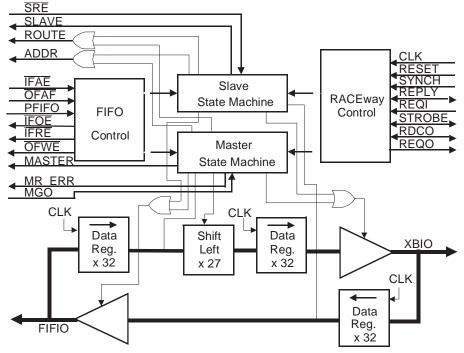

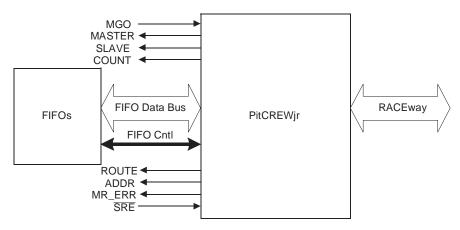

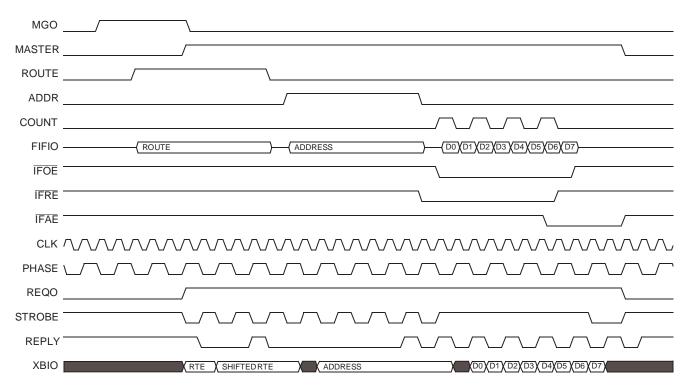

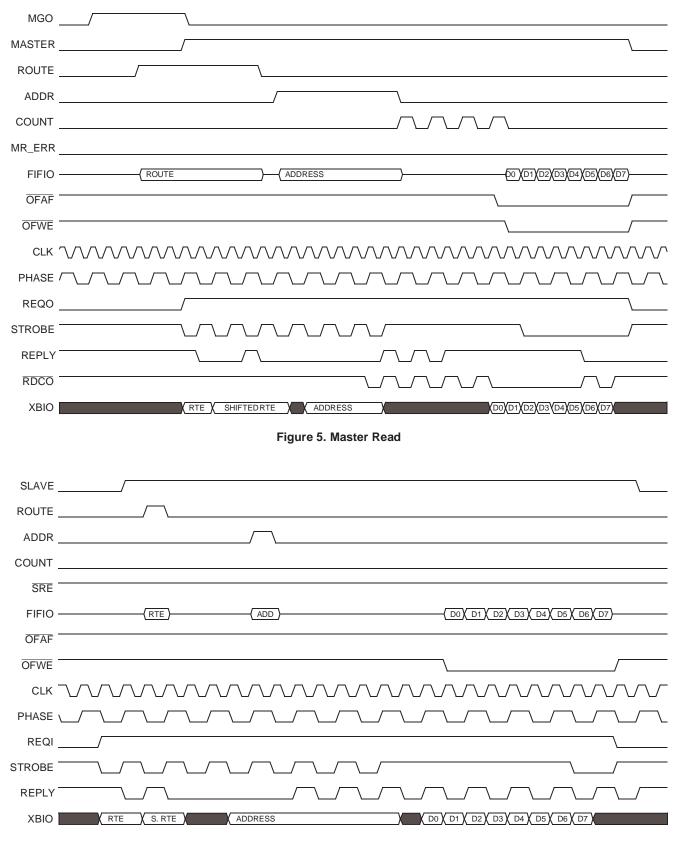

Data packets from the Channel Formatter are delivered to 4k x 32 synchronous Output FIFOs, one for each of the 16 channels. Once a data packet is delivered to a FIFO, a signal is sent to the RACEway Controller. The RACEway Controller then retrieves the RACEway routing code and address from the Channel Formatter, and starts a RACE-way bus transfer using the packet stored in the FIFO.

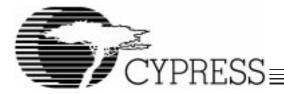

#### 1.7 RACEway Interface

The Model 6526's RACEway interface is implemented using the Cypress PitCREWjr chip set. The RACEway interface circuitry creates separate RACEway packets for each DDR on the board and sends them to the desired destination processors. Each DDR's output can be sent to one or more independent processors on another VME board in the same VME chassis via RACEway Interlink Modules. For more information about RACEway Interlinks, see Appendix B, and refer to the Pentek RACEway Handbook, Pentek part number 800.00003.

The Model 6526 is directly compatible with all of Pentek's RACEway–compatible DSP processors, including the Models 4290 and 4291 (equipped with a Model 6219 or 6220 RACEway Interface VIM module) and the Model 4285 (equipped with the Option 034 RACEway interface). The Model 6526 supports local RACEway packet steering to any of the processors on these boards, as determined by the RACEway address.

#### **1.8 Digital Interfaces**

Model 6526 Option 002 accepts two 16-bit differential ECL-level input signals, at a maximum data rate of 62.5 MSPS. This input option is compatible with Pentek A/D Converter Models 6402 Option 002, 6410 Option 002, 6425 Option 001, 6441 Option 002, 6465, 6470, and 6472. Model 6526 Option 019 accepts single-ended TTL-level signals, at a maximum rate of 50 MSPS. This input option is compatible with the standard versions of Pentek A/D Converter Models 6402, 6410, 6420, 6425, and 6441.

Another input data source for the Model 6526 is the Watkins–Johnson WJ–9107 Wide– band Telecom Tuner. The WJ–9107 output is a 36–pin connector delivering differential ECL output levels. Two WJ–9107's may be located in an external VXI chassis, each supplying one digitized data signal to the two data inputs on one Model 6526. A spe– cial cable, available separately from Pentek as Model 2126, provides direct connection for the two input data signals from two WJ–9107's to the Model 6526.

#### **1.9 VMEbus Interface**

The Model 6526 is a single–slot, VME stand–alone board that meets VME C.1 specifications. It provides slave A32/D32 access, A24/D16 access, and A16/D16 access. It does not allow D8 access. It is a VMEbus interrupter but it is not a VMEbus interrupt handler. It passes the Bus Grant and IACK daisy chain signals.

The VMEbus Slave Interface allows read/write control of registers and access to a dual port SRAM used for passing parameters to the DDRs. These resources are memory mapped into a unique A24/A32 VME address space. A second address space, identical to the first, provides write–only access to all the same functions. The base address of each of these two spaces is programmable in A16 address space. This allows multiple boards to share the same write–only space for broadcast commands sent to several boards using a single VMEbus cycle. Commands for individual boards can always be sent through the unique read/write space.

#### 1.10 Model 6526 Block Diagram

The block diagram for the Model 6526 is shown in Figure 1–1, below.

### 1.11 Specifications

| <b>Receiver Chips:</b>                                       | 4 (four) Graychip GC4014s, 16–bit input data<br>(See Appendix C for chip specifications)                                                                                                                                                                                                                                              |

|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Digital Inputs                                               |                                                                                                                                                                                                                                                                                                                                       |

| Input Connectors:                                            | Front panel 80–pin 3M connector for 0.025" pitch cable;<br>accepts two input signals of up to 16 data bits each, using<br>80–conductor cable (3M # 3756/80, Pentek # 378.68000) &<br>80–pin connector (3M # 82080–6006, Pentek # 353.08005)                                                                                           |

| Option 002:                                                  | Differential ECL inputs compatible with Pentek Models<br>6402–002, 6410–002, 6441–002, and 6465 A/D Converters<br>(using Pentek's Model 2117 cable assembly), and Pentek<br>Models 6425–001, 6470, and 6472 A/D Converters (using<br>Pentek's Model 2119 cable assembly); these A/D<br>Converters can provide data rates up to 70 MHz |

| Option 019:                                                  | Single–ended TTL inputs compatible with Pentek Models<br>4261–019, 6402, 6410, 6420, 6421, and 6441 (using Pentek's<br>Model 2117 cable assembly), and Pentek Model 6425 (using<br>Pentek's Model 2119 cable assembly); data rates up to<br>41 MHz can be provided by these units                                                     |

| Input Signals (2):                                           |                                                                                                                                                                                                                                                                                                                                       |

| Data:                                                        | 16 (sixteen) bit lines/input signal<br>(16 differential pairs (32 lines) for Option 002)                                                                                                                                                                                                                                              |

| <u>Clock:</u><br>Clock Rate:                                 | 1 (one) bit line/input signal<br>62.5 MHz, maximum (Option 002)<br>50 MHz, maximum (Option 019)                                                                                                                                                                                                                                       |

| <u>External Sync:</u><br>Data Setup Time:<br>Data Hold Time: | 2 (two) bit lines/input (filter & accumulator syncs)                                                                                                                                                                                                                                                                                  |

| Input Multiplexers:                                          | Each receiver can independently select Input A or Input B                                                                                                                                                                                                                                                                             |

| Input FIFO Memory:                                           | 4k x 32 Synchronous FIFO for each receiver                                                                                                                                                                                                                                                                                            |

| <b>RACEway Interface:</b>                                    | One PitCREWjr chip set; transfers data at 160 MByte/sec<br>peak and 140 MByte/sec sustained throughput<br>(See Appendix D for chip specifications)                                                                                                                                                                                    |

### **1.11 Specifications** (continued)

| VMEbus Interface:                                                  | Slave; A32/D32; I1–7;<br>Power up with no A24/A32 address mapping;<br>Bus Grant daisy chain bussed through;<br>Interrupt daisy chain supported           |

|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| A16 Memory:                                                        | A16 base address set with rotary switch;<br>256–byte address space maximum;<br>A24/A32 base address configuration registers                              |

| A24/32 Memory:                                                     | Mapping disabled on power up, configured with A16<br>memory registers;<br>1 MB address space in A24;<br>4 MB address space in A32                        |

| VMEbus Data Rate:                                                  | 200 nsec DS to DTACK delay max (with no contention for<br>global bus by 'C31);<br>280 nsec bus cycle time max (with 80 nsec master response<br>overhead) |

| Processor:                                                         | One Texas Instruments TMS320C31, 60 MHz;<br>On-board XDS-500 emulator connector (12 pins)                                                                |

| 'C31 Memory:                                                       | 128k x 32 Global SRAM, one wait state, shared with<br>VMEbus;<br>256k x 8 Flash User EEPROM                                                              |

| <u>Dual–Ported SRAM</u><br>Size:<br>'C31 Access:<br>VMEbus access: | 64 kbytes, 1 bank, 16k x 32<br>Yes (controlled by on–board register)<br>Yes, A24/A32 (controlled by on–board register)                                   |

| Power:                                                             | 6.5 A @ +5 VDC maximum                                                                                                                                   |

| <u>Dimensions:</u><br>Depth:<br>Height:<br>Panel Width:            | Standard 6U VMEbus board<br>160.0 mm (6.3")<br>233.5 mm (9.2")<br>20.3 mm (0.8")                                                                         |

### **Chapter 2: Installation and Connections**

#### 2.1 Inspection

After unpacking, inspect the unit carefully for possible damage to connectors or components. If any damage is discovered, contact Pentek at (201) 818–5900. Please save the original shipping container and packing material in case re–shipment is required.

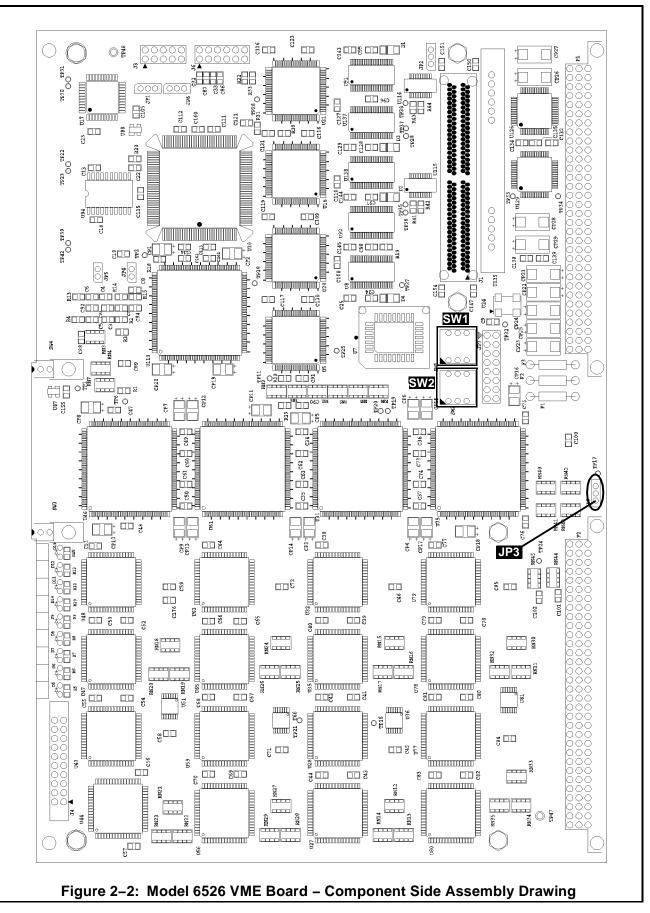

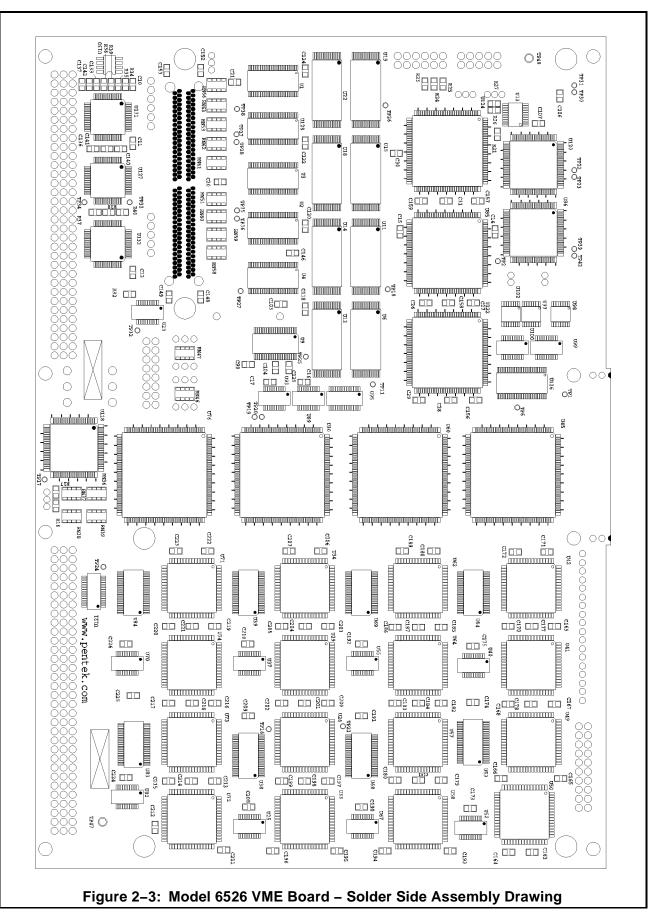

The Model 6526 contains two printed circuit (PC) assemblies. The board with the VME– bus P1 and P2 connectors (the VME board, Pentek part # 004.65260) contains the VME interface, the 'C31 DSP, its associated memory resources, and the FIFOs. The other board (the Mezzanine board, Pentek part # 004.65261), houses the input connectors and the Digital Receiver circuitry. Drawings of the component and solder sides of both PC assemblies are shown in Figures 2–2 through 2–5, on the next four pages.

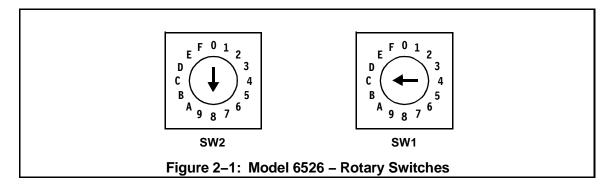

#### 2.2 VMEbus A16 Base Address Switches

Three separate address spaces are defined for the VMEbus environment. These three regions are known as A16, A24, and A32. Each device in your VMEbus card cage must have a unique address in any address space in which it must be accessible. On the Model 6526, the A16\_base address (the lowest address in the A16 region occupied by this device) is set by two rotary switches. These switches, SW1 and SW2, are located on the VME board and are accessible through a notch at the rear of the Mezzanine board. Set these switches for the desired A16\_base address before installing the Model 6526 in the VMEbus card cage. Figure 2–1, below, shows what these switches look like, and Figure 2–2, on the next page, shows the location of these switches on the VME board.

The settings of these 16–position rotary switches each defines four bits of the Model 6526's A16\_base address. Each of the 16 positions on the switches denotes a hex digit (0 to F), whose four–bit binary value is used as part of the device's base address. SW2 defines the four most significant bits (MSBs) of the address (A15 – A12), and SW1 defines the next four bits (A11 – A8). Thus, with 16 settings available on each of two switches, 256 different base addresses may be selected. Figure 2–1, above, illustrates the switches set for an A16\_base address of 0x8C00.

#### 2.3 Jumper Block Settings on the Model 6526

Most of the jumper blocks on the Model 6526 are for factory testing purposes. These are all configured for proper field operation at the conclusion of testing, and should not be changed by the user.

There is, however, one jumper the user might want to set before installing the unit in the card cage. Jumper block JP3 determines whether or not the Model 6526 is capable of generating the RACEway RESET signal. By default, the jumper on this block is placed between pins 1 and 2, which disables the Model 6526 as a RACEway RESET generator (removing this jumper from the block also serves this purpose). To allow the Model 6526 to generate the RACEway RESET signal, place the jumper between pins 2 and 3 of JP3. This is summarized in Table 2–1, below.

| Table 2–1: RACEway RESET Enable Jumper JP3                              |           |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------|-----------|--|--|--|--|--|--|--|

| Jumper Position RACEway RESET Generation                                |           |  |  |  |  |  |  |  |

| Pin 1 – Pin 2*                                                          | Disabled* |  |  |  |  |  |  |  |

| Pin 2 – Pin 3                                                           | Enabled   |  |  |  |  |  |  |  |

| * Factory Default Setting<br>– also Disabled if no jumper is installed. |           |  |  |  |  |  |  |  |

The JP3 jumper block is located just above the P2 VME connector on the Model 6526 main VME board (see Figure 2–2, on page 18).

#### 2.4 Model 6526 Front Panel

The front panel of Pentek's Model 6526 is shown in Figure 2–6, at the right. Available on the front panel are an 80–pin Digital Data In connector, a Reset button, a 14–pin Sync bus connector, several indicator LEDs, and a 20–pin Serial connector for access to the TMS320C31's Serial Port. Each of these is described in a subsection below.

#### 2.4.1 Digital Data Input Connector

The input connector, labeled DIGITAL DATA IN, is an 80–pin flat ribbon cable header manufactured by 3M. The part number for the header is 3M #81080–620203 (Pentek part # 354.08001).

The mating flat cable socket connector is 3M #82080–6006, and the strain relief is 3M #3858–080. Pentek's part number for the connector, with the strain relief, is 353.08005. One of each of these items is supplied with the Model 6526. The recommended 0.025" pitch flat rib–bon cable is 3M #3756/80.

A 68–conductor cable of the same type may also be used for applications requiring only 12 data bits. This cable is type 3M #3756/68. The 68–conductor cable should be crimped into the center of the 80–pin cable connector such that pins 1 through 6 and pins 75 through 80 are left unconnected.

The 80-pin connector is composed of two similar 40-pin groups, one for each input signal. The ribbon cable can be split in half, forming two 40-pin cables. The pin assignment for the connector is shown on the next page, in Figure 2–7, for the two input signal options.

- Model 6526 Option 002 accommodates two 16-bit differential ECL-level input signals, available from such devices as Pentek A/D Converter Models 6402 Option 002, 6410 Option 002, 6425 Option 001, 6441 Option 002, 6465, 6470, and 6472.

- Model 6526 Option 019 accepts single-ended TTLlevel signals, and is compatible with the standard versions of Pentek A/D Converter Models 6402, 6410, 6420, 6425, and 6441.

|          |                              |     |                                     |     |          |                              |          |        | -                                |  |                |                       |

|----------|------------------------------|-----|-------------------------------------|-----|----------|------------------------------|----------|--------|----------------------------------|--|----------------|-----------------------|

|          | ut Connector                 |     |                                     |     |          | ut Connector                 |          |        | 1                                |  | 2              | Model 6               |

|          | del 6526-002 (               |     | ,                                   |     |          | el 6526-019 (                |          | -      | 3                                |  | 4              | D                     |

| Pin      | Signal                       | Pin | Signal                              |     | Pin      | Signal                       | Pin      | Signal | 7                                |  | 8              |                       |

| 1        | Ch B - D1 in                 | 2   | Ch B - D1 in                        |     | 1        | Ch B - D1 in                 | 2        | GND    | 9<br>11                          |  | 10<br>12       | G                     |

| 3        | Ch B - D2 in                 | 4   | Ch B - D2 in                        |     | 3        | Ch B - D2 in                 | 4        | GND    | 13<br>15                         |  | 14<br>16       |                       |

| 5        | Ch B - D3 in                 | 6   | Ch B - D3 in                        |     | 5        | Ch B - D3 in                 | 6        | GND    | 17<br>19                         |  | 18<br>20       | <b>T</b>              |

| 7        | Ch B - D4 in                 | 8   | Ch B - D4 in                        |     | 7        | Ch B - D4 in                 | 8        | GND    | 21                               |  | 22<br>24       | A                     |

| 9        | Ch B - D5 in                 | 10  | Ch B - <u>D5</u> in                 |     | 9        | Ch B - D5 in                 | 10       | GND    | 21<br>23<br>25<br>27<br>29<br>31 |  | 26             |                       |

| 11       | Ch B - D6 in                 | 12  | Ch B - <u>D6</u> in                 |     | 11       | Ch B - D6 in                 | 12       | GND    | 27<br>29                         |  | 28<br>30<br>32 |                       |

| 13       | Ch B - D7 in                 | 14  | Ch B - D7 in                        |     | 13       | Ch B - D7 in                 | 14       | GND    | 33                               |  | 32<br>34       | I<br>T<br>A<br>L<br>D |

| 15       | Ch B - D8 in                 | 16  | Ch B - D8 in                        |     | 15       | Ch B - D8 in                 | 16       | GND    | 35<br>37                         |  | 36<br>38       |                       |

| 17       | Ch B - D9 in                 | 18  | Ch B - D9 in                        |     | 17       | Ch B - D9 in                 | 18       | GND    | 39                               |  | 40             | T                     |

| 19       | Ch B - D10 in                | 20  | Ch B - D10 in                       |     | 19       | Ch B - D10 in                | 20       | GND    | 41<br>43                         |  | 42<br>44       | A .                   |

| 21       | Ch B - D11 in                | 22  | Ch B - D11 in                       |     | 21       | Ch B - D11 in                | 22       | GND    | 45<br>47                         |  | 46<br>48       |                       |

| 23       | Ch B - D12 in                | 24  | Ch B - D12 in                       | 1   | 23       | Ch B - D12 in                | 24       | GND    | 49<br>51                         |  | 50<br>52       | T<br>A<br>I<br>N      |

| 25       | Ch B - D13 in                | 26  | Ch B - D13 in                       | 1   | 25       | Ch B - D13 in                | 26       | GND    | 53<br>55                         |  | 54<br>56       | N                     |

| 27       | Ch B - D14 in                | 28  | Ch B - D14 in                       | 1   | 27       | Ch B - D14 in                | 28       | GND    | 57                               |  | 58             |                       |

| 29       | Ch B - D15 in                | 30  | Ch B - D15 in                       | 1   | 29       | Ch B - D15 in                | 30       | GND    | 59<br>61                         |  | 60<br>62       |                       |

| 31       | Ch B - SS in                 | 32  | Ch B - SS                           | 1   | 31       | Ch B - SS in                 | 32       | GND    | 63<br>65                         |  | 64<br>66       |                       |

| 33       | Reserved                     | 34  | Reserved                            |     | 33       | Reserved                     | 34       | GND    | 67<br>69                         |  | 68<br>70       |                       |

| 35       | Ch B - CK                    | 36  | Ch B - CK                           |     | 35       | Ch B - CK                    | 36       | GND    | 69<br>71<br>73                   |  | 70<br>72<br>74 | RESET                 |

| 37       | Ch B - D0 in                 | 38  | Ch B - D0 in                        |     | 37       | Ch B - D0 in                 | 38       | GND    | 75                               |  | 76             |                       |

| 39<br>39 | GND                          | 40  | GND                                 | 1   | 39       | GND                          | 40       | GND    | . 77<br>79                       |  | 78<br>80       |                       |

| 39<br>41 | Ch A - D4 in                 | 40  | Ch A - D4 in                        | 1   | 41       | Ch A - D4 in                 | 40       | GND    |                                  |  |                |                       |

| 41<br>43 | Ch A - D4 in<br>Ch A - D5 in | 42  | Ch A - D4 in<br>Ch A - D5 in        |     | 41       | Ch A - D4 in<br>Ch A - D5 in | 42       | GND    |                                  |  | _              |                       |

| 43<br>45 | Ch A - D5 in<br>Ch A - D6 in | 44  | Ch A - D5 in<br>Ch A - <u>D6</u> in | ┨╴┠ | 43<br>45 | Ch A - D5 in<br>Ch A - D6 in | 44       | GND    |                                  |  |                | S .                   |

|          |                              |     | Ch A - D6 in<br>Ch A - D7 in        | ▎▕  | -        |                              |          | GND    |                                  |  |                | Y    🗆 🗆              |

| 47       | Ch A - D7 in                 | 48  | Ch A - D7 in<br>Ch A - D8 in        | ┨╴┠ | 47<br>49 | Ch A - D7 in                 | 48<br>50 | GND    |                                  |  |                | N B                   |

| 49<br>51 | Ch A - D8 in                 | 50  |                                     |     |          | Ch A - D8 in                 |          |        |                                  |  |                | C    🗆 🗆              |

| 51<br>52 | Ch A - D9 in                 | 52  | Ch A - <u>D9</u> in                 | ▎▕  | 51       | Ch A - D9 in                 | 52       | GND    |                                  |  |                |                       |

| 53       | Ch A - D10 in                | 54  | Ch A - D10 in                       |     | 53       | Ch A - D10 in                | 54       | GND    |                                  |  |                |                       |

| 55       | Ch A - D11 in                | 56  | Ch A - D11 in                       |     | 55       | Ch A - D11 in                | 56       | GND    |                                  |  |                |                       |

| 57       | Ch A - D12 in                | 58  | Ch A - D12 in                       |     | 57       | Ch A - D12 in                | 58       | GND    |                                  |  |                |                       |

| 59       | Ch A - D13 in                | 60  | Ch A - D13 in                       |     | 59       | Ch A - D13 in                | 60       | GND    |                                  |  |                | S FAIL                |

| 61       | Ch A - D14 in                | 62  | Ch A - D14 in                       |     | 61       | Ch A - D14 in                | 62       | GND    |                                  |  |                |                       |

| 63<br>05 | Ch A - D15 in                | 64  | Ch A - D15 in                       |     | 63       | Ch A - D15 in                | 64       | GND    |                                  |  |                | O DSP                 |

| 65<br>07 | Ch A - SS in                 | 66  | Ch A - SS in                        |     | 65       | Ch A - SS in                 | 66       | GND    |                                  |  |                | 🔘 TERN                |

| 67       | Reserved                     | 68  | Reserved                            |     | 67       | Reserved                     | 68       | GND    |                                  |  |                |                       |

| 69       | Ch A - CK                    | 70  | Ch A - CK                           |     | 69       | Ch A - CK                    | 70       | GND    |                                  |  |                |                       |

| 71       | Ch A - D0                    | 72  | Ch A - D0                           |     | 71       | Ch A - D0                    | 72       | GND    |                                  |  |                | — В                   |

| 73       | GND                          | 74  | GND                                 |     | 73       | GND                          | 74       | GND    |                                  |  |                |                       |

| 75       | Ch A - D1                    | 76  | Ch A - D1                           |     | 75       | Ch A - D1                    | 76       | GND    |                                  |  |                |                       |

| 77       | Ch A - D2                    | 78  | Ch A - D2                           |     | 77       | Ch A - D2                    | 78       | GND    |                                  |  |                |                       |

| 79       | Ch A - D3                    | 80  | Ch A - D3                           |     | 79       | Ch A - D3                    | 80       | GND    | ]                                |  |                | <b>A</b>              |

The recommended 0.025" pitch flat ribbon cable is 3M # 3756/080.

DR0 CKR0

PENTEK

#### 2.4.1 Digital Data Input Connector (continued)

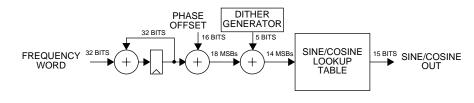

#### 2.4.1.1 Connecting a Watkins–Johnson Model WJ–9107 to Model 6526