## SSRAM\_FLASH user guide

| Target                      |                                   |                     | -Clock Setting | yo .                                 |              |                |            |            |           |          |

|-----------------------------|-----------------------------------|---------------------|----------------|--------------------------------------|--------------|----------------|------------|------------|-----------|----------|

| Device Family: Stratix IV ▼ |                                   |                     |                | Name                                 | Source       |                |            |            | MHz       |          |

|                             | ,                                 |                     | clk_50         |                                      | External     |                |            |            | 50.0      |          |

|                             |                                   |                     | system_cl      | lk                                   | pll_0.c0     |                |            |            | 83.333333 |          |

| ssram_clk                   |                                   |                     | ssram_clk      | •                                    | pli_0.c1     |                |            |            | 83.333333 |          |

|                             |                                   |                     |                |                                      |              |                |            |            | '         |          |

| Jse                         | Connections                       | Module              | Name           | Description                          | Clock        | Т              | Base       | End        | Tags      |          |

| <del>-</del>                |                                   | ⊟ cpu_0             |                | Nios II Processor                    |              |                |            |            |           |          |

|                             |                                   | instruction         | master         | Avalon Memory Mapped Master          | system clk   |                |            |            |           |          |

|                             |                                   | data_mast           | _              | Avalon Memory Mapped Master          | o y o com_om |                | IRQ O      | IRQ 3      | ,         | ←        |

|                             |                                   | jtag_debu           |                | Avalon Memory Mapped Slave           |              |                | 0x00001000 | _          | 1         | ľ        |

| ⊽                           |                                   |                     |                | On-Chip Memory (RAM or ROM)          |              |                | 0×00001000 | 0x00001711 |           |          |

| •                           |                                   |                     | enioryz_u      |                                      |              | ١.             |            |            |           |          |

| _                           |                                   | s1                  |                | Avalon Memory Mapped Slave           | system_clk   | 100            | 0×00800000 | 0x008f9fff |           |          |

| ₹                           |                                   | ⊟ sc_inf_inst       | ı              | sc_inf                               |              |                |            |            |           |          |

|                             |                                   | nios                |                | Avalon Memory Mapped Slave           | system_clk   | •              | 0x00000000 | 0x000003ff |           | -        |

| ~                           | 1 1 1                             | ☐ jtag_avalor       | n_master_0     | JTAG to Avalon Master Bridge         |              |                |            |            |           |          |

|                             | $\square \succeq $                | master              |                | Avalon Memory Mapped Master          | system_clk   |                |            |            |           |          |

| ⊽                           |                                   | □ pll_0             |                | PLL                                  |              |                |            |            |           |          |

|                             | $\rightarrow$                     | s1                  |                | Avalon Memory Mapped Slave           | clk_50       | m <sup>2</sup> | 0x00000420 | 0x0000043f |           |          |

| 7                           |                                   | ☐ led_out           |                | PIO (Parallel I/O)                   |              |                |            |            |           |          |

|                             | $\longrightarrow$                 | s1                  |                | Avalon Memory Mapped Slave           | system_clk   | 0              | 0x00000490 | 0x0000049f |           |          |

| 7                           |                                   | ☐ dipsw in          |                | PIO (Parallel I/O)                   |              |                |            |            |           |          |

|                             |                                   | s1                  |                | Avalon Memory Mapped Slave           | system_clk   | -              | 0x000004a0 | 0x000004af |           |          |

| V                           |                                   | □ pb_in             |                | PIO (Parallel I/O)                   | o, atom_ork  |                | ~~00000x40 | 52500004AI |           |          |

| 14                          |                                   | <b>□ po_m</b><br>s1 |                | Avalon Memory Mapped Slave           | system_clk   | L              | 0x000004c0 | 0x000004cf |           |          |

| ⊽                           |                                   |                     |                |                                      | system_cik   |                | 0×000004C0 | 0x000004CI |           |          |

| ~                           |                                   | □ lcd_0             |                | Character LCD                        |              |                |            |            |           |          |

| _                           | 1                                 | control_sk          |                | Avaion Memory Mapped Slave           | system_clk   | 100            | 0x000004b0 | 0x000004bf |           |          |

| 굣                           |                                   | ☐ jtag_uart_(       |                | JTAG UART                            |              |                |            |            |           |          |

|                             | $\downarrow \uparrow \rightarrow$ | avalon_jta          |                | Avalon Memory Mapped Slave           | system_clk   | =0             | 0x000004d0 | 0x000004d7 |           | <b>►</b> |

| 굣                           |                                   | ☐ time_stam         | p_timer        | Interval Timer                       |              |                |            |            |           |          |

|                             | $\downarrow$                      | s1                  |                | Avalon Memory Mapped Slave           | system_clk   | =0             | 0x00000440 | 0x0000045f |           | <b>-</b> |

| 굣                           |                                   |                     | k_timer        | Interval Timer                       |              |                |            |            |           |          |

|                             | $\downarrow$                      | s1                  |                | Avalon Memory Mapped Slave           | system_clk   | er.            | 0x00000460 | 0x0000047f |           | <b>├</b> |

| 굣                           |                                   | ☐ tri_state_b       | ridge_0        | Avalon-MM Tristate Bridge            |              |                |            |            |           |          |

|                             |                                   | avalon sla          |                | Avalon Memory Mapped Slave           | system_clk   |                |            |            |           |          |

|                             |                                   | tristate ma         |                | Avalon Memory Mapped Tristate Master | ,            |                |            |            |           |          |

| ~                           |                                   | ☐ cfi_flash_0       |                | Flash Memory Interface (CFI)         |              |                |            |            |           |          |

| -                           |                                   | s1                  |                | Avalon Memory Mapped Tristate Slave  | system_clk   | L              | 0×04000000 | 0x07ffffff |           |          |

| V                           | $-111^{-7}$                       |                     |                |                                      | ayatem_cik   |                | 0.04000000 | 020/111111 |           |          |

| *                           |                                   | □ ssram_0           |                | Cypress CY7C1380C SSRAM              |              |                | 0.004000   | 00054444   |           |          |

|                             |                                   | s1<br>s1            |                | Avalon Memory Mapped Tristate Slave  | ssram_clk    | 100            | 0x00400000 | 0x005fffff |           |          |

| ~                           |                                   | ☐ max2_inf          |                | Cypress CY7C1380C SSRAM              |              |                |            |            |           |          |

|                             | $    \rightarrow$                 | s1                  |                | Avalon Memory Mapped Tristate Slave  | ssram_clk    | 100            | 0x00600000 | 0x006fffff |           |          |

| ゼ                           |                                   | ⊟ temp              |                | PIO (Parallel I/O)                   |              |                |            |            |           |          |

|                             | $\rightarrow$                     | s1                  |                | Avalon Memory Mapped Slave           | clk_50       | =0             | 0x00000400 | 0x0000040f |           |          |

| 굣                           |                                   | □ volt              |                | PIO (Parallel I/O)                   |              |                |            |            |           |          |

| - 1                         |                                   | s1                  |                | Avalon Memory Mapped Slave           | clk_50       | 100            |            | 0x0000041f |           |          |

This project is just a connection to a lot of components. There are 2 Avalon masters, CPU and JTAG-Avalon-Memory mapped Master. Bellow them, there are

| instance      |                                                                                        |                                                                                                                                                                                      |  |

|---------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| name          | Start address                                                                          | End address                                                                                                                                                                          |  |

|               | 0x00800000                                                                             | 0x008f9fff                                                                                                                                                                           |  |

| (sc_inf_inst) | 0x00000000                                                                             | 0x000003ff                                                                                                                                                                           |  |

| (pll_0)       | 0x420                                                                                  | 0x43f                                                                                                                                                                                |  |

| (led_out)     | 0x490                                                                                  | 0x49f                                                                                                                                                                                |  |

| (dipsw_in)    | 0x4a0                                                                                  | 0x4af                                                                                                                                                                                |  |

| (pb_in)       | 0x4c0                                                                                  | 0x4cf                                                                                                                                                                                |  |

| (lcd_0)       | 0x4b0                                                                                  | 0x4bf                                                                                                                                                                                |  |

| (temp)        | 0x400                                                                                  | 0x40f                                                                                                                                                                                |  |

| (volt)        | 0x410                                                                                  | 0x41f                                                                                                                                                                                |  |

| (cfi_flash_0) | 0x04000000                                                                             | 0x07ffffff                                                                                                                                                                           |  |

| (ssram_0)     | 0x00400000                                                                             | 0x005fffff                                                                                                                                                                           |  |

|               | (sc_inf_inst) (pll_0) (led_out) (dipsw_in) (pb_in) (lcd_0) (temp) (volt) (cfi_flash_0) | name Start address 0x00800000 (sc_inf_inst) 0x00000000 (pll_0) 0x420 (led_out) 0x490 (dipsw_in) 0x4a0 (pb_in) 0x4c0 (lcd_0) 0x4b0 (temp) 0x400 (volt) 0x410 (cfi_flash_0) 0x04000000 |  |

## MAX-II register interface (max2\_inf) 0x00600000 0x006fffff

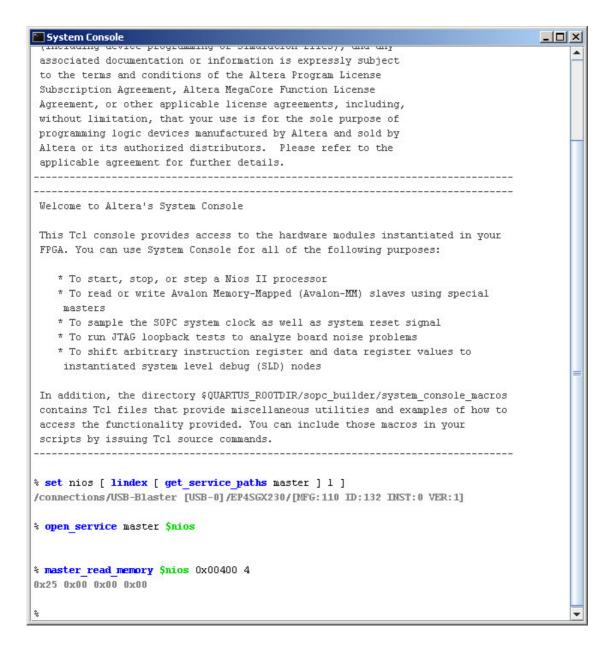

I recommend to use System Console.

The system console can be called from SOPC Builder or command line.

Here are the sample commands to use

- 1. set nios [ lindex [ get\_service\_paths master ] 1 ]

- 2. open\_service master \$nios

- 3. master\_read\_memory \$nios 0x00400 4

- 4. master\_write\_memory \$nios 0x0040C [ list 0x54 ]

3 and 4 is accessing the component.

Master\_read\_memory \$nios [target\_read\_address] [byte\_to\_read] So, the example is reading address 0x400 for 4 bytes.

master\_write\_memory \$nios [target\_write\_address] [list write\_data] write data is the hex data to write.

If you want to write 32 bits data, it will be [list 0x00 0x01 0x02 0x03]

For more information about the system console, please check online document for the system console.