# Xilinx Timing Constraints User Guide

UG612 (v1.0.0) December 9, 2008

Xilinx is disclosing this user guide, manual, release note, and/or specification (the "Documentation") to you solely for use in the development of designs to operate with Xilinx hardware devices. You may not reproduce, distribute, republish, download, display, post, or transmit the Documentation in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Xilinx expressly disclaims any liability arising out of your use of the Documentation. Xilinx reserves the right, at its sole discretion, to change the Documentation without notice at any time. Xilinx assumes no obligation to correct any errors contained in the Documentation, or to advise you of any corrections or updates. Xilinx expressly disclaims any liability in connection with technical support or assistance that may be provided to you in connection with the Information.

THE DOCUMENTATION IS DISCLOSED TO YOU "AS-IS" WITH NO WARRANTY OF ANY KIND. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DOCUMENTATION, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NONINFRINGEMENT OF THIRD-PARTY RIGHTS. IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOSS OF DATA OR LOST PROFITS, ARISING FROM YOUR USE OF THE DOCUMENTATION.

© 2002–2008 Xilinx, Inc. All rights reserved.

XILINX, the Xilinx logo, the Brand Window, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners

## Preface: About the Xilinx Timing Constraints User Guide

| Xilinx Timing Constraints User Guide Contents | . 3 |

|-----------------------------------------------|-----|

| Additional Resources                          | . 3 |

| Conventions                                   |     |

| TypographicalOnline Document                  |     |

## Chapter 1: Introduction to the Xilinx Timing Constraints User Guide

## Chapter 2: Timing Constraint Methodology

| About Timing Constraint Methodology                                                                                                                                                                                                                                                         | 9           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Basic Constraints Methodology 1                                                                                                                                                                                                                                                             | 0           |

| Input Timing Constraints       1         About Input Timing Constraints       1                                                                                                                                                                                                             | 1           |

| System Synchronous Inputs    1      Source Synchronous Inputs    1                                                                                                                                                                                                                          | 2           |

| Register-To-Register Timing Constraints       1         About Register-To-Register Timing Constraints       1         Automatically Related Synchronous DCM/PLL Clock Domains       1         Manually Related Synchronous Clock Domains       1         Asynchronous Clock Domains       1 | 4<br>5<br>5 |

| Output Timing Constraints.       1         System Synchronous Output       1         Source Synchronous Outputs.       2                                                                                                                                                                    | 8           |

| Timing Exceptions       2         False Paths       2         Multi-Cycle Paths       2                                                                                                                                                                                                     | 2           |

## **Chapter 3: Timing Constraint Principles**

| Constraint Priorities 43                      |

|-----------------------------------------------|

| Timing Constraints                            |

| About Timing Constraints 44                   |

| Timing Constraint Exceptions                  |

| Setting Timing Constraint Requirements        |

| PERIOD Constraints                            |

| About PERIOD Constraints 45                   |

| Related TIMESPEC PERIOD Constraints           |

| Paths Covered by PERIOD Constraints           |

| OFFSET Constraints                            |

| About OFFSET Constraints 51                   |

| Paths Covered by OFFSET Constraints           |

| FROM:TO (Multi-Cycle) Constraints 55          |

| About FROM:TO (Multi-Cycle) Constraints       |

| False Paths or Timing Ignore (TIG) Constraint |

| Paths Covered by FROM:TO Constraints          |

| Timing Constraint Syntax                      |

| Creating Timing Constraints                   |

| Timing Constraint Analysis                    |

| About Timing Constraint Analysis 62           |

| PERIOD Constraints                            |

| About PERIOD Constraints                      |

| Gated Clocks                                  |

| Single Clock Domain                           |

| Two-Phase Clock Domain                        |

| Multiple Clock Domains                        |

| Clocks from DCM outputs                       |

| Clk0 Clock Domain                             |

| Clk90 Clock Domain                            |

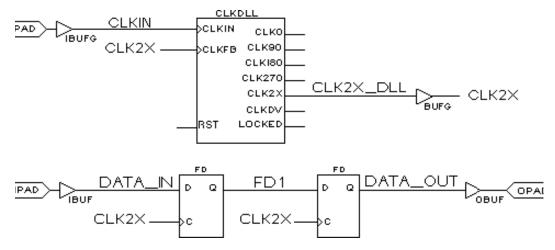

| Clk2x Clock Domain                            |

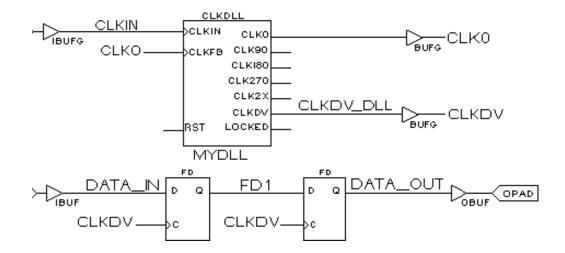

| CLKDV/CLKFX Clock Domain 69                   |

| FROM:TO (Multi-Cycle) Constraints 70          |

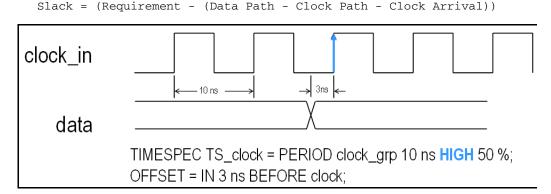

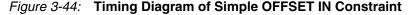

| OFFSET IN Constraints                         |

| About OFFSET IN Constraints                   |

| OFFSET IN BEFORE Constraints                  |

| OFFSET IN AFTER Constraints 80                |

| OFFSET OUT Constraints 80                     |

| About OFFSET OUT Constraints 80               |

| OFFSET OUT AFTER Constraints 81               |

| OFFSET OUT BEFORE Constraints                 |

| Clock Skew                                    |

| Clock Uncertainty                             |

| Asynchronous Reset Paths                      |

# Preface

# About the Xilinx Timing Constraints User Guide

This chapter provides general information about this Guide, and includes:

- "Xilinx Timing Constraints User Guide Contents"

- "Additional Resources"

- "Conventions"

## Xilinx Timing Constraints User Guide Contents

The Xilinx Timing Constraints User Guide contains the following chapters:

- Chapter 1, "Introduction to the Xilinx Timing Constraints User Guide"

- Chapter 2, "Timing Constraint Methodology"

- Chapter 3, "Timing Constraint Principles"

## **Additional Resources**

For additional documentation, see the Xilinx website at:

http://www.xilinx.com/literature.

To search the Answer Database of silicon, software, and IP questions and answers, or to create a technical support WebCase, see the Xilinx website at:

http://www.xilinx.com/support.

## Conventions

This document uses the following conventions. An example illustrates each convention.

- "Typographical"

- "Online Document"

The following typographical conventions are used in this document:

| Convention          | Meaning or Use                                                                                               | Example                                                                                                  |

|---------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| Courier font        | Messages, prompts, and<br>program files that the system<br>displays                                          | speed grade: - 100                                                                                       |

| Courier bold        | Literal commands that you enter in a syntactical statement                                                   | ngdbuild design_name                                                                                     |

| Helvetica bold      | Commands that you select from a menu                                                                         | File > Open                                                                                              |

|                     | Keyboard shortcuts                                                                                           | Ctrl+C                                                                                                   |

| Italic font         | Variables in a syntax statement<br>for which you must supply<br>values                                       | <b>ngdbuild</b> design_name                                                                              |

|                     | References to other manuals                                                                                  | See the <i>Development System</i><br><i>Reference Guide</i> for more<br>information.                     |

|                     | Emphasis in text                                                                                             | If a wire is drawn so that it<br>overlaps the pin of a symbol, the<br>two nets are <i>not</i> connected. |

| Square brackets [ ] | An optional entry or parameter.<br>They are required in bus<br>specifications, such as<br><b>bus [7:0]</b> , | <b>ngdbuild</b> [option_name]<br>design_name                                                             |

| Braces { }          | A list of items from which you must choose one or more                                                       | lowpwr ={on off}                                                                                         |

| Vertical bar        | Separates items in a list of choices                                                                         | lowpwr ={on off}                                                                                         |

| Vertical ellipsis   | Repetitive material that has been omitted                                                                    | <pre>IOB #1: Name = QOUT' IOB #2: Name = CLKIN'</pre>                                                    |

| Horizontal ellipsis | Repetitive material that has been omitted                                                                    | <b>allow block</b> block_name<br>loc1 loc2 locn;                                                         |

### **Online Document**

The following conventions are used in this document:

| Convention | Meaning or Use                                                                                          | Example                                                                                                         |

|------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Blue text  | Cross-reference link to a location<br>in the current file or in another<br>file in the current document | See the section "Additional<br>Resources" for details.<br>Refer to "Title Formats" in<br>Chapter 1 for details. |

XILINX®

| Convention            | Meaning or Use                                         | Example                                                           |

|-----------------------|--------------------------------------------------------|-------------------------------------------------------------------|

| Red text              | Cross-reference link to a location in another document | See Figure 2-5 in the Virtex-II Platform FPGA User Guide.         |

| Blue, underlined text | Hyperlink to a website (URL)                           | Go to <u>http://www.xilinx.com</u><br>for the latest speed files. |

# Chapter 1

## Introduction to the Xilinx Timing Constraints User Guide

The *Xilinx*<sup>®</sup> *Timing Constraints User Guide* is written specifically to address timing closure in high-performance applications. The guide is designed for all FPGA designers, from beginners to advanced. The high performance of today's Xilinx devices can overcome the speed limitations of other technologies and older devices. Designs that formerly only fit or ran at high clock frequencies in an ASIC device are finding their way into Xilinx FPGA devices. In addition, it is imperative that designers have a proven methodology for obtaining their performance objectives.

This Guide discusses:

- The fundamentals of timing constraints, including:

- "PERIOD Constraints"

- "OFFSET IN Constraints"

- "OFFSET OUT Constraints"

- "FROM:TO (Multi-Cycle) Constraints"

- The ability to group elements and provided a better understanding of the constraint system software

- Information about the analysis of the basic constraints, with clock skew and clock uncertainty

# Chapter 2

## **Timing Constraint Methodology**

This chapter discusses Timing Constraint Methodology, and includes:

- "About Timing Constraint Methodology"

- "Basic Constraints Methodology"

- "Input Timing Constraints"

- "Register-To-Register Timing Constraints"

- "Output Timing Constraints"

- "Timing Exceptions"

## **About Timing Constraint Methodology**

You must have a proven methodology in order to meet your design objectives. This chapter outlines the process to:

- Understand the design requirements

- Constrain the design to meet these requirements

Before starting a design, you must understand:

- The performance requirements of the system

- The features of the target device

This knowledge allows you to use proper coding techniques utilizing the features of the device to give the best performance.

The FPGA device requirements depend on the system and the upstream and downstream devices. Once the interfaces to the FPGA device are known, the internal requirements can be outlined. How to meet these requirements depends on the device and its features.

You should understand:

- The device clocking structure

- RAM and DSP blocks

- Any hard IP contained within the device

For more information, see the device User Guide.

Timing constraints communicate all design requirements to the implementation tools. This also implies that all paths are covered by the appropriate constraint. This chapter provides general guidelines that explain the strategy for identifying and constraining the most common timing paths in FPGA devices as efficiently as possible.

## **Basic Constraints Methodology**

Timing requirements fall into into several global categories depending on the type of path to be covered.

The most common types of path categories include:

- Input paths

- Synchronous element to synchronous element paths

- Path specific exceptions

- Output Paths

A Xilinx<sup>®</sup> timing constraint is associated with each of these global constraint types. The most efficient way to specify these constraints is to begin with global constraints and add path specific exceptions as needed. In many cases, only the global constraints are required.

The FPGA device implementation tools are driven by the specified timing requirements. They assign device resources and expend the appropriate amount of effort necessary to ensure the timing requirements are met. However, when a requirement is over-constrained - or specified as a value greater than the design requirement - the effort spent by the tools to meet this constraint increases significantly. This extra effort results in increased memory use and tool runtime.

More importantly, over-constraint can result in loss of performance, not only for the constraint in question, but for other constraints as well. For this reason, Xilinx recommends that you specify the constraint values using the actual design requirements.

Xilinx recommends that you always comment the constraints file. This allows other designers to understand why each constraint is used.

Include in your comments:

- Source of the constraint

- Whether the PERIOD constraint is based on an external clock

This Guide uses UCF constraint syntax examples. This format passes the design requirements to the implementation tools. However, the easiest way to enter design constraints is to use Constraints Editor.

**Constraints Editor:**

- Provides a unified location in which to manage all the timing constraints associated with a design

- Provides assistance in creating timing constraints from the design requirements in UCF syntax

## **Input Timing Constraints**

This section discusses Input Timing Constraints and includes:

- "About Input Timing Constraints"

- "System Synchronous Inputs"

- "Source Synchronous Inputs"

## About Input Timing Constraints

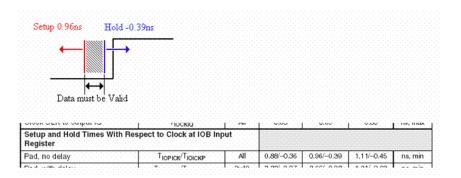

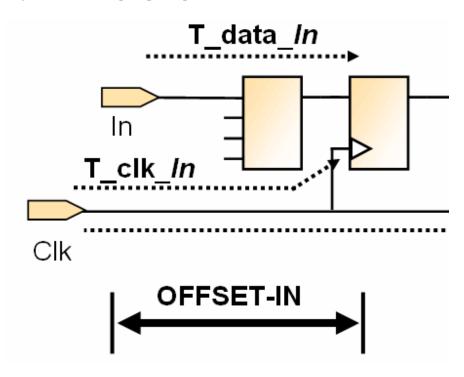

Input timing covers the data path from the external pin of the FPGA device to the internal register that captures that data. The constraint used to specify the input timing is the OFFSET IN constraint. The best way to specify the input timing requirements depends on the type (source/system synchronous) and single data rate (SDR) or double data rate (DDR) of the interface.

The OFFSET IN constraint defines the relationship between the data and the clock edge used to capture that data at the pins of the FPGA device. When analyzing the OFFSET IN constraint, the timing analysis tools automatically take all internal factors affecting the delay of the clock and data into account. These factors include:

- Frequency and phase transformations of the clock

- Clock uncertainties

- Data delay adjustments

In addition to the automatic adjustments, you may also add additional input clock uncertainty to the PERIOD constraint associated with the interface clock.

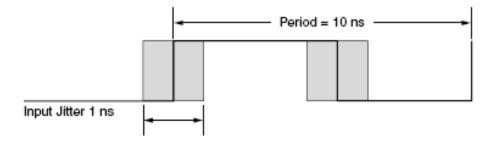

For more information on adding INPUT\_JITTER, see "PERIOD Constraints" in Chapter 3, "Timing Constraint Principles."

The OFFSET IN constraint is associated with a single input clock. By default, the OFFSET IN constraint covers all paths from the input pads of the FPGA device to the internal synchronous elements that capture that data and are triggered by the specified OFFSET IN clock. This application of the OFFSET IN constraint is called the *global* method. It is the most efficient way to specify input timing.

### System Synchronous Inputs

In a system synchronous interface, a common system clock both transfers and captures the data. This interface uses a common system clock. The board trace delays and clock skew limit the operating frequency of the interface. The lower frequency also results in the system synchronous input interface typically being an SDR application.

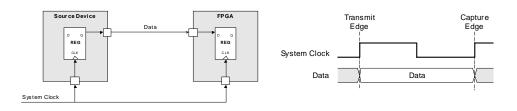

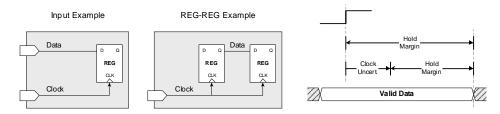

In the system synchronous SDR application example, shown in Figure 2-1, "Simplified System Synchronous interface with associated SDR timing," the data is transmitted from the source device on one rising clock edge and captured in the FPGA device on the next rising clock edge.

#### Figure 2-1: Simplified System Synchronous interface with associated SDR timing

The global OFFSET IN constraint is the most efficient way to specify the input timing for a system synchronous interface. In this method, one OFFSET IN constraint is defined for each system synchronous input interface clock. This single constraint covers the paths of

all input data bits that are captured in synchronous elements triggered by the specified input clock.

To specify the input timing:

- Define the clock PERIOD constraint for the input clock associated with the interface

- Define the global OFFSET IN constraint for the interface

#### Example

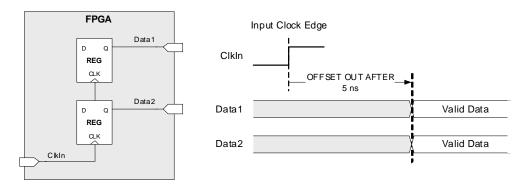

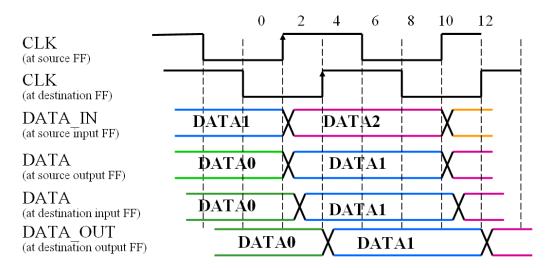

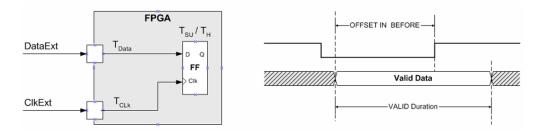

A timing diagram for an ideal System Synchronous SDR interface is shown in Figure 2-2, "Timing diagram for an ideal System Synchronous SDR interface." The interface has a clock period of 5 ns, The data for both bits of the bus remains valid for the entire period.

#### Figure 2-2: Timing diagram for an ideal System Synchronous SDR interface

The global OFFSET IN constraint is:

OFFSET = IN value VALID value BEFORE clock;

In the OFFSET IN constraint, the **OFFSET=IN <value>** determines the time from the capturing clock edge to the time in which data first becomes valid. In this system synchronous example, the data becomes valid 5 ns prior to the capturing clock edge. In the OFFSET IN constraint, the **VALID <value>** determines the duration in which data remains valid. In this example, the data remains valid for 5 ns.

For this example, the complete OFFSET IN specification with associated PERIOD constraint is:

```

NET "SysClk" TNM_NET = "SysClk";

TIMESPEC "TS_SysClk" = PERIOD "SysClk" 5 ns HIGH 50%;

OFFSET = IN 5 ns VALID 5 ns BEFORE "SysClk";

```

This global constraint covers both the data bits of the bus:

- data1

- data2

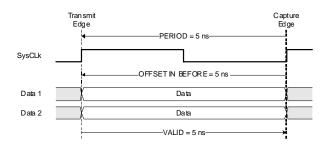

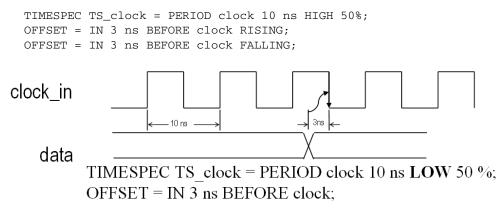

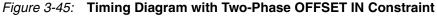

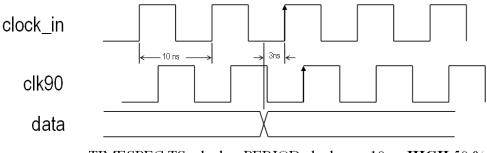

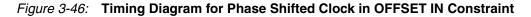

#### Source Synchronous Inputs

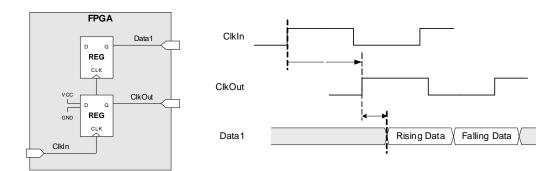

In a source synchronous input interface, a clock is regenerated and transmitted along with the data from the source device along similar board traces. This clock is then used to capture the data in the FPGA device. The board trace delays and board skew no longer limit the operating frequency of the interface. The higher frequency also results in the source synchronous input interface typically being a dual data rate (DDR) application. In this source synchronous DDR application example, shown in Figure 2-3, "Simplified Source Synchronous input interface with associated DDR timing," unique data is

transmitted from the source device on both the rising and falling clock edges and captured in the FPGA device using the regenerated clock.

## Figure 2-3: Simplified Source Synchronous input interface with associated DDR timing

The global OFFSET IN constraint is the most efficient way to specify the input timing for a source synchronous interface. In the DDR interface, one OFFSET IN constraint is defined for each edge of the input interface clock. These constraints cover the paths of all input data bits that are captured in registers triggered by the specified input clock edge.

To specify the input timing:

- Define the clock PERIOD constraint for the input clock associated with the interface

- Define the global OFFSET IN constraint for the rising edge (RISING) of the interface

- Define the global OFFSET IN constraint for the falling edge (FALLING) of the interface

#### Example

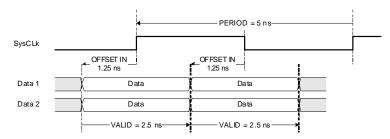

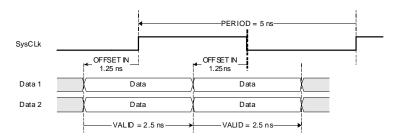

A timing diagram for an ideal Source Synchronous DDR interface is shown in Figure 2-4, "Timing diagram for ideal Source Synchronous DDR." The interface has a clock period of 5 ns with a 50/50 duty cycle. The data for both bits of the bus remains valid for the entire  $\frac{1}{2}$  period.

The global OFFSET IN constraint for the DDR case is:

OFFSET = IN value VALID value BEFORE clock RISING; OFFSET = IN value VALID value BEFORE clock FALLING;

In the OFFSET IN constraint, **OFFSET=IN** *<value>* determines the time from the capturing clock edge in which data first becomes valid. In this source synchronous input example, the rising data becomes valid 1.25 ns prior to the rising clock edge. The falling data also becomes valid 1.25 ns prior to the falling clock edge. In the OFFSET IN constraint,

www.xilinx.com

the **VALID** *<value>* determines the duration in which data remains valid. In this example, both the rising and falling data remains valid for 2.5 ns.

For this example, the complete OFFSET IN specification with associated PERIOD constraint is:

NET "SysClk" TNM\_NET = "SysClk"; TIMESPEC "TS\_SysClk" = PERIOD "SysClk" 5 ns HIGH 50%; OFFSET = IN 1.25 ns VALID 2.5 ns BEFORE "SysClk" RISING; OFFSET = IN 1.25 ns VALID 2.5 ns BEFORE "SysClk" FALLING;

This global constraint covers both the data bits of the bus:

- data1

- data2

### **Register-To-Register Timing Constraints**

This section discusses Register-To-Register Timing Constraints and includes:

- "About Input Timing Constraints"

- "Automatically Related Synchronous DCM/PLL Clock Domains"

- "Manually Related Synchronous Clock Domains"

- "Asynchronous Clock Domains"

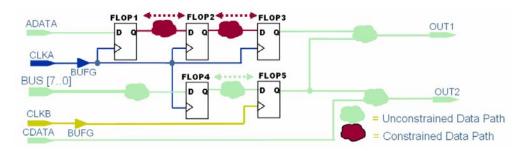

#### About Register-To-Register Timing Constraints

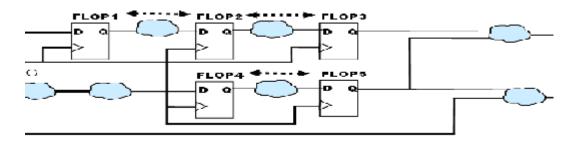

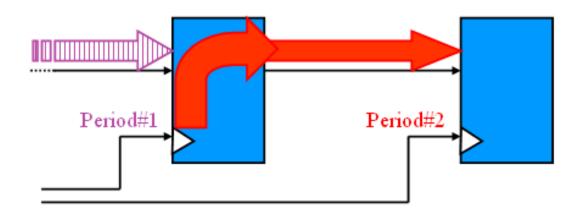

Register-to-register or *synchronous element to synchronous element* path constraints cover the synchronous data paths between internal registers. The PERIOD constraint:

- Defines the timing requirements of the clock domains

- Analyzes the paths within a single clock domain

- Analyzes all paths between related clock domains

- Takes into account all frequency, phase, and uncertainty differences between the clock domains during analysis

For more information, see "PERIOD Constraints" in Chapter 3, "Timing Constraint Principles."

The application and methodology for constraining synchronous clock domains falls under several common cases. These categories include:

- "Automatically Related Synchronous DCM/PLL Clock Domains"

- "Manually Related Synchronous Clock Domains"

- "Asynchronous Clock Domains"

By allowing the tools to automatically create clock relationships for DLL/DCM/PLL output clocks, and manually defining relationships for externally related clocks, all synchronous cross clock domain paths are covered by the appropriate constraints, and properly analyzed. Using PERIOD constraints that follow this methodology eliminates the need for additional cross-clock-domain constraints.

### Automatically Related Synchronous DCM/PLL Clock Domains

The most common type of clock circuit is one in which:

- The input clock is fed into a DLL/DCM/PLL

- The outputs are used to clock the synchronous paths in the device

In this case, the recommended methodology is to define a PERIOD constraint on the input clock to the DLL/DCM/PLL.

By placing the PERIOD constraint on the input clock, the Xilinx tools automatically:

- Derive a new PERIOD constraint for each of the DLL/DCM/PLL output clocks

- Determine the clock relationships between the output clock domains, and automatically perform an analysis for any paths between these clock domains.

#### Example

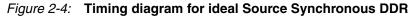

The circuit of an input clock driving a DCM is shown inFigure 2-5, "The input clock of the design goes to a DCM example."

Figure 2-5: The input clock of the design goes to a DCM example

The PERIOD constraint syntax for this example is:

```

NET "ClockName" TNM_NET = "TNM_NET_Name";

TIMESPEC "TS_name" = PERIOD "TNM_NET_Name" PeriodValue HIGH HighValue%;

```

In the PERIOD constraint, the **PeriodValue** defines the duration of the clock period. In this case, the input clock to the DCM has a period of 5 ns. The **HighValue** of the PERIOD constraint defines the percent of the clock waveform that is HIGH. In this example, the waveform has a 50/50 duty cycle resulting in a **HighValue** of 50%.

The syntax for this example is:

NET "ClkIn" TNM\_NET = "ClkIn"; TIMESPEC "TS\_ClkIn" = PERIOD "ClkIn" 5 ns HIGH 50%;

Based on the input clock PERIOD constraint given above, the DCM automatically:

- Creates two output clock constraints for the DCM outputs

- Performs analysis between the two domains

#### Manually Related Synchronous Clock Domains

In some cases the relationship between synchronous clock domains can not be automatically determined by the tools - for example, when related clocks enter the FPGA device on separate pins. In this case, Xilinx recommends that you:

- Define a separate PERIOD constraint for each input clock

- Define a manual relationship between the clocks

Once you define the manual relationship, all paths between the two synchronous domains are automatically analyzed. The analysis takes into account all frequency, phase, and uncertainty information.

The Xilinx constraints system allows you to define complex manual relationships between clock domains using the PERIOD constraint including clock frequency and phase transformations.

To define complex manual relationships between clock domains using the PERIOD constraint:

- Define the PERIOD constraint for the primary clock

- Define the PERIOD constraint for the related clock using the first PERIOD constraint as a reference

For more information on using the PERIOD constraint to define clock relationships, see "PERIOD Constraints" in Chapter 3, "Timing Constraint Principles."

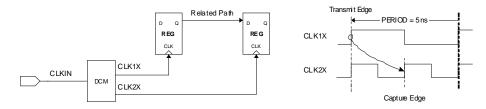

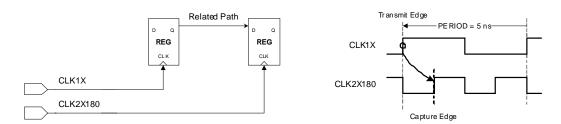

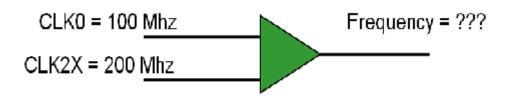

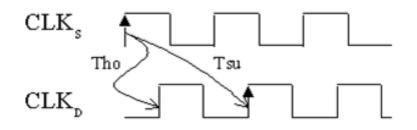

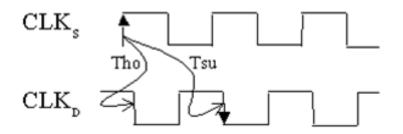

Two related clocks enter the FPGA device through separate external pins, as shown in Figure 2-6, "Two related clocks entering the FPGA device through separate external pins."

- The first clock (CLK1X) is the primary clock

- The second clock (CLK2X180) is the related clock

## Figure 2-6: Two related clocks entering the FPGA device through separate external pins

The PERIOD constraint syntax for this example is:

```

NET "PrimaryClock" TNM_NET = "TNM_Primary";

NET "RelatedClock" TNM_NET = "TNM_Related";

TIMESPEC "TS_primary" = PERIOD "TNM_Primary" PeriodValue HIGH

HighValue%;

TIMESPEC "TS_related" = PERIOD "TNM_Related" TS_Primary_relation PHASE

value;

```

In the related PERIOD definition, the PERIOD value is defined as a time unit (period) relationship to the primary clock. The relationship is expressed in terms of the primary clock TIMESPEC. In this example CLK2X180 operates at twice the frequency of CLK1X which results in a PERIOD relationship of one-half.

In the related PERIOD definition, the PHASE value defines the difference in time between the rising clock edge of the source clock and the related clock. In this example, since the CLK2X180 clock is 180 degrees shifted, the rising edge begins 1.25 ns after the rising edge of the primary clock.

The syntax for this example is:

```

NET "Clk1X" TNM_NET = "Clk1X";

NET "Clk2X180" TNM_NET = "Clk2X180";

TIMESPEC "TS_Clk1X" = PERIOD "Clk1X" 5 ns;

TIMESPEC "TS_Clk2X180" = PERIOD "Clk2X180" TS_Clk1X/2 PHASE + 1.25 ns ;

```

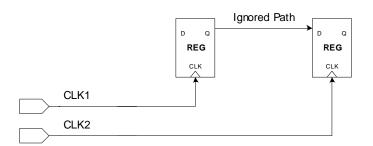

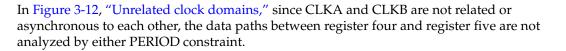

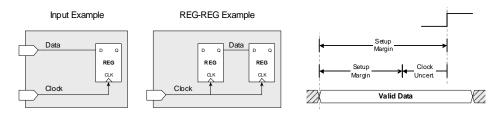

### Asynchronous Clock Domains

Asynchronous clock domains are those in which the source and destination clocks do not have a frequency or phase relationship. Since the clocks are not related, it is not possible to determine the final relationship for setup and hold time analysis. For this reason, Xilinx recommends that you use proper asynchronous design techniques to ensure the successful capture of data. One example of proper asynchronous design technique is to use a FIFO design element to capture and transfer data between asynchronous clock domains. While not required, in some cases you may wish to constrain the maximum data path delay in isolation without regard to clock path frequency or phase relationship.

The Xilinx constraints system allows you to constrain the maximum data path delay without regard to source and destination clock frequency and phase relationship. This requirement is specified using the FROM-TO constraint with the DATAPATHONLY keyword.

To constrain of the maximum data path delay without regard to source and destination clock frequency and phase relationship:

- Define a time group for the source synchronous elements

- Define a time group for the destination synchronous elements

- Define the maximum delay of the data paths using the FROM-TO constraint between the two time groups with DATAPATHONLY keyword.

For more information on using the FROM-TO constraint with the DATAPATHONLY keyword, see "FROM:TO (Multi-Cycle) Constraints" in Chapter 3, "Timing Constraint Principles."

Example

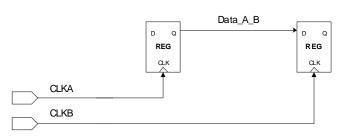

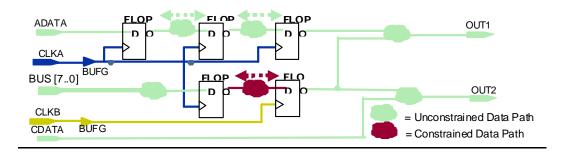

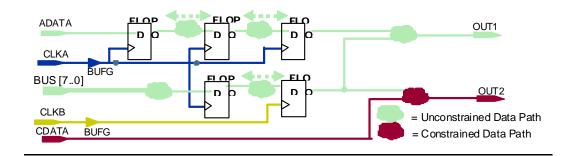

Two unrelated clocks enter the FPGA device through separate external pins as shown in Figure 2-7, "Two unrelated clocks entering the FPGA device through separate external pins."

- The first clock (CLKA) is the source clock

- The second clock (CLKB) is the destination clock

*Figure 2-7:* **Two unrelated clocks entering the FPGA device through separate** external pins

The syntax for this example is:

```

NET "CLKA" TNM_NET = FFS "GRP_A";

NET "CLKB" TNM_NET = FFS "GRP_B";

TIMESPEC TS_Example = FROM "GRP_A" TO "GRP_B" 5 ns DATAPATHONLY;

```

## **Output Timing Constraints**

Output timing covers the data path from a register inside the FPGA device to the external pin of the FPGA device. The OFFSET OUT constraint specifies the output timing. The best way to specify the output timing requirements depends on the type (source/system syncronous) and SDR/DDR of the interface.

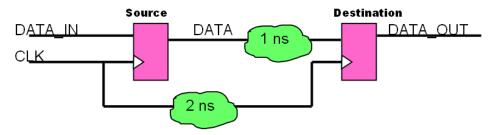

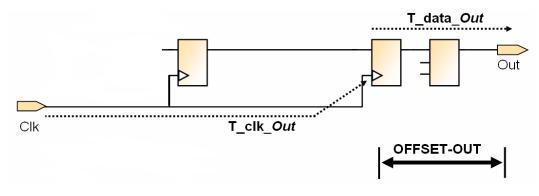

The OFFSET OUT constraint defines the maximum time allowed for data to be transmitted from the FPGA device. The output delay path begins at the input clock pin of the FPGA device and continues through the output register to the data pins of the FPGA device, as shown in Figure 2-8, "Output-timing constraints from input clock pad to the output data pad."

#### Figure 2-8: Output-timing constraints from input clock pad to the output data pad

When analyzing the OFFSET OUT constraint, the timing tools automatically take all internal factors affecting the delay of the clock and data paths into account. These factors include:

- Frequency and phase transformations of the clock

- Clock uncertainties

- Data path delay adjustments

For more information, see "OFFSET OUT Constraints" in Chapter 3, "Timing Constraint Principles."

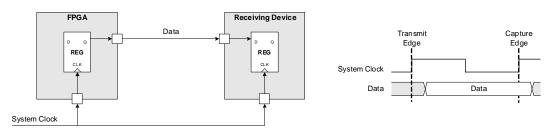

#### System Synchronous Output

The system synchronous output interface is an interface in which a common system clock is used to both transfer and capture the data. Since this interface uses a common system clock, only the data is transmitted from the FPGA device to the receiving device as shown

in Figure 2-9, "Simplified System Synchronous output interface with associated SDR timing."

*Figure 2-9:* Simplified System Synchronous output interface with associated SDR timing

If these paths must be constrained, the global OFFSET OUT constraint is the most efficient way to specify the output timing for the system synchronous interface. In the global method, one OFFSET OUT constraint is defined for each system synchronous output interface clock. This single constraint covers the paths of all output data bits sent from registers triggered by the specified input clock.

To specify the output timing:

- Define a time name (TNM) for the output clock to create a time group, which contains all output registers triggered, by the input clock

- Define the global OFFSET OUT constraint for the interface

#### Example

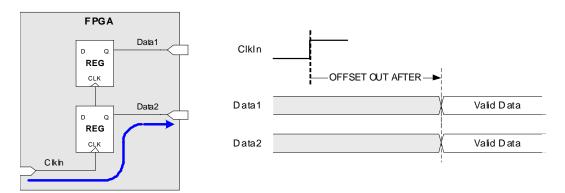

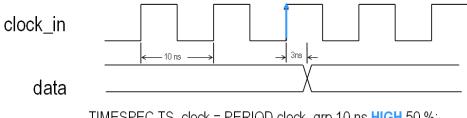

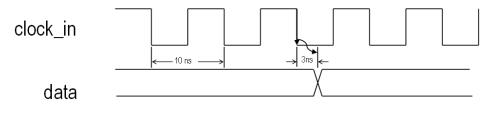

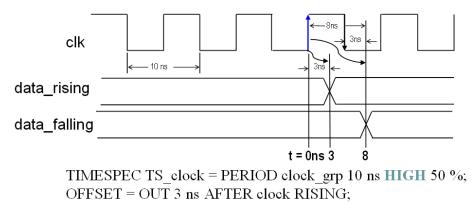

A timing diagram for a System Synchronous SDR output interface is shown in Figure 2-10, "Timing diagram for System Synchronous SDR output interface." The data in this example must become valid at the output pins a maximum of 5 ns after the input clock edge at the pin of the FPGA device.

#### Figure 2-10: Timing diagram for System Synchronous SDR output interface

The global OFFSET OUT constraint for the system synchronous interface is:

OFFSET = OUT value AFTER clock;

In the OFFSET OUT constraint, **OFFSET=OUT <value>** determines the maximum time from the rising clock edge at the input clock port until the data first becomes valid at the data output port of the FPGA device. In this system synchronous example, the output data must become valid at least 5 ns after the input clock edge.

For this example, the complete OFFSET OUT specification is:

NET "ClkIn" TNM\_NET = "ClkIn"; OFFSET = OUT 5 ns AFTER "ClkIn";

This global constraint covers both the data bits of the bus:

- data1

- data2

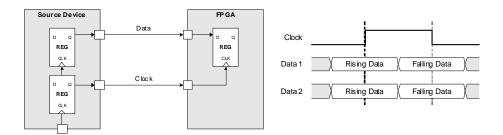

#### Source Synchronous Outputs

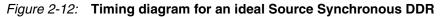

The source synchronous output interface is an interface in which a clock is regenerated and transmitted along with the data from the FPGA device. The regenerated clock is transmitted along with the data. The interface is primarily limited in performance by system noise and the skew between the regenerated clock and the data bits, as shown in Figure 2-11, "Simplified Source Synchronous output interface with associated DDR timing." In this interface, the time from the input clock edge to the output data becoming valid is not as important as the skew between the output data bits. In most cases, it can be left unconstrained.

## Figure 2-11: Simplified Source Synchronous output interface with associated DDR timing

The global OFFSET OUT constraint is the most efficient way to specify the output timing for a source synchronous interface. In the DDR interface, one OFFSET OUT constraint is defined for each edge of the output interface clock. These constraints cover the paths of all output data bits that are transmitted by registers triggered with the specified output clock edge.

To specify the input timing:

- Define a time name (TNM) for the output clock to create a time group which contains all output registers triggered by the output clock

- Define the global OFFSET OUT constraint for the rising edge (RISING) of the interface

- Define the global OFFSET OUT constraint for the falling edge (FALLING) of the interface

#### Example

A timing diagram for an ideal Source Synchronous DDR interface is shown in Figure 2-12, "Timing diagram for an ideal Source Synchronous DDR." The interface has a clock period

of 5 ns with a 50/50 duty cycle. The data for both bits of the bus remains valid for the entire  $\frac{1}{2}$  period.

The global OFFSET IN constraint for the DDR case is:

OFFSET = IN **value** VALID **value** BEFORE **clock** RISING; OFFSET = IN **value** VALID **value** BEFORE **clock** FALLING;

In the OFFSET IN constraint, **OFFSET=IN** *<value>* determines the time from the capturing clock edge in which data first becomes valid. In this source synchronous input example, the rising data becomes valid 1.25 ns prior to the rising clock edge and the falling data also becomes valid 1.25 ns prior to the falling clock edge. In the OFFSET IN constraint, **VALID** *<value>* determines the duration in which data remains valid. In this example, both the rising and falling data remains valid for 2.5 ns.

For this example, the complete OFFSET IN specification with associated PERIOD constraint is:

NET "SysClk" TNM\_NET = "SysClk"; TIMESPEC "TS\_SysClk" = PERIOD "SysClk" 5 ns HIGH 50%; OFFSET = IN 1.25 ns VALID 2.5 ns BEFORE "SysClk" RISING; OFFSET = IN 1.25 ns VALID 2.5 ns BEFORE "SysClk" FALLING;

In the OFFSET OUT constraint, **OFFSET=OUT <value>** determines the maximum time from the rising clock edge at the input clock port until the data first becomes valid at the data output port of the FPGA device. When **<value>** is omitted from the OFFSET OUT constraint, the constraint becomes a report-only specification which reports the skew of the output bus. The REFERENCE\_PIN keyword defines the regenerated output clock as the reference point against which the skew of the output data pins is reported.

For this example, the complete OFFSET OUT specification for both the rising and falling clock edges is :

```

NET "CLkIn" TNM_NET = "ClkIn";

OFFSET = OUT AFTER "ClkIn" REFERENCE_PIN "ClkOut" RISING;

OFFSET = OUT AFTER "ClkIn" REFERENCE PIN "ClkOut" FALLING;

```

## **Timing Exceptions**

Using the global definitions of the input, register-to-register, and output timing constraints, properly constrains the majority of the paths. In certain cases a small number of paths contain exceptions to the global constraint rules. The most common types of exceptions are:

- "False Paths"

- "Multi-Cycle Paths"

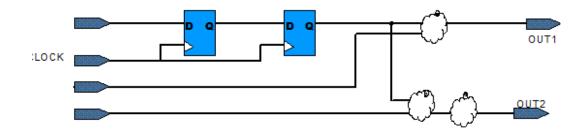

### **False Paths**

In some cases, you may want to remove a set of paths from timing analysis if you are sure that these paths do not affect timing performance.

One common way to specify the set of paths to be removed from timing analysis is to use the FROM-TO constraint with the timing ignore (TIG) keyword. This allows you to:

- Specify a set of registers in a source time group

- Specify a set of registers in a destination time group

- Automatically remove all paths between those time groups from analysis.

To specify the timing ignore (TIG) constraint for this method, define:

- A set of registers for the source time group

- A set of registers for the destination time group

- A FROM-TO constraint with a TIG keyword to remove the paths between the groups

#### Example

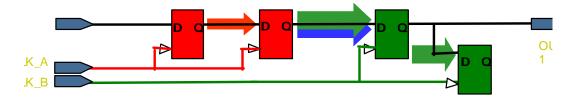

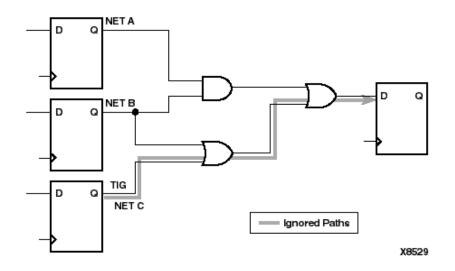

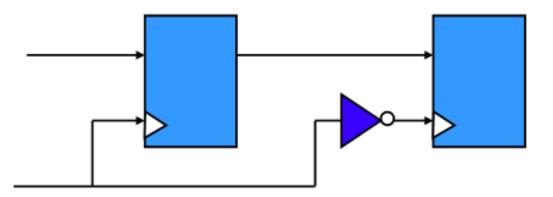

A hypothetical case in which a path between two registers does not affect the timing of the design, and is desired to be removed from analysis, is shown in Figure 2-13, "Path between two registers that does not affect the timing of the design."

## *Figure 2-13:* Path between two registers that does not affect the timing of the design

The generic syntax for defining a timing ignore (TIG) between time groups is:

TIMESPEC "TSid" = FROM "SRC\_GRP" TO "DST\_GRP" TIG;

In the FROM-TO TIG example, the SRC\_GRP defines the set of source registers at which path tracing begins. The DST\_GRP defines the set of destination registers at which the path tracing ends. All paths that begin in the SRC\_GRP and end in the DST\_GRP are ignored.

The specific syntax for this example is:

```

NET "CLK1" TNM_NET = FFS "GRP_1";

NET "CLK2" TNM_NET = FFS "GRP_2";

TIMESPEC TS_Example = FROM "GRP_1" TO "GRP_2" TIG;

```

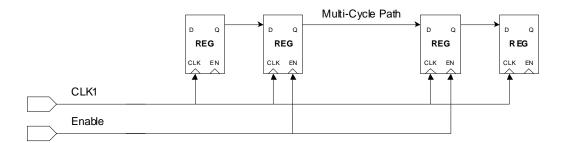

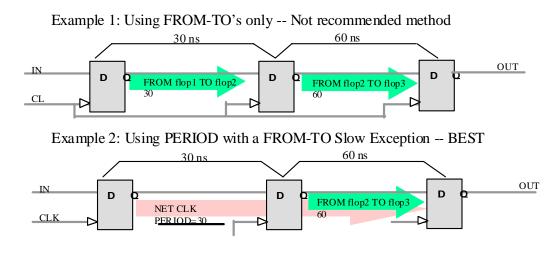

#### Multi-Cycle Paths

In a multi-cycle path, data is transferred from source to destination synchronous elements at a rate less than the clock frequency defined in the PERIOD specification.

This occurs most often when the synchronous elements are gated with a common clock enable signal. By defining a multi-cycle path, the timing constraints for these synchronous

elements are relaxed over the default PERIOD constraint. The implementation tools are then able to appropriately prioritize the implementation of these paths.

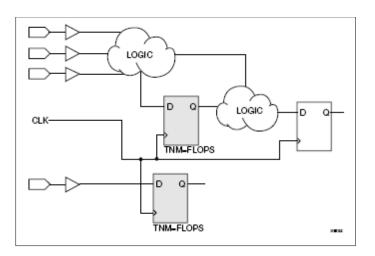

One common way to specify the set of multi-cycle paths is to define a time group using the clock enable signal. This allows you to:

- Define one time group containing both the source and destination synchronous elements using a common clock enable signal

- Automatically apply the multi-cycle constraint to all paths between these synchronous elements

To specify the FROM:TO (multi-cycle) constraint for this method, define:

- A PERIOD constraint for the common clock domain

- A set of registers based on a common clock enable signal

- A FROM:TO (multi-cycle) constraint describing the new timing requirement

#### Example

Figure 2-14, "Path between two registers clocked by a common clock enable signal," shows a hypothetical case in which a path between two registers is clocked by a common clock enable signal. In this example, the clock enable is toggled at a rate that is one-half of the reference clock.

#### *Figure 2-14:* Path between two registers clocked by a common clock enable signal

The generic syntax for defining a multi-cycle path between time groups is:

TIMESPEC "TSid" = FROM "MC\_GRP" TO "MC\_GRP" <value>;

In the FROM:TO (multi-cycle) example, the MC\_GRP defines the set of registers which are driven by a common clock enable signal. All paths that begin in the MC\_GRP and end in the MC\_GRP have the multi-cycle timing requirement applied to them. Paths into and out of the MC\_GRP are analyzed with the appropriate PERIOD specification.

The specific syntax for this example is:

```

NET "CLK1" TNM_NET = "CLK1";

TIMESPEC "TS_CLK1" = PERIOD "CLK1" 5 ns HIGH 50%;

NET "Enable" TNM_NET = FFS "MC_GRP";

TIMESPEC TS_Example = FROM "MC_GRP" TO "MC_GRP" TS_CLK1*2;

```

# Chapter 3

## **Timing Constraint Principles**

This chapter includes:

- "Constraint System"

- "Constraint Priorities"

- "Timing Constraints"

- "Timing Constraint Syntax"

- "Creating Timing Constraints"

- "Timing Constraint Analysis"

- "Clock Skew"

- "Clock Uncertainty"

- "Asynchronous Reset Paths"

This chapter:

- Discusses the fundamentals of timing constraints, including:

- "PERIOD Constraints"

- "OFFSET Constraints"

- "FROM:TO (Multi-Cycle) Constraints"

- Discusses the ability to group elements in order to provide a better understanding of the constraint system subsystem

- Provides more information about the analysis of the basic constraints, with "Clock Skew" and "Clock Uncertainty"

### **Constraint System**

This section discusses the Constraint System and includes:

- "About the Constraint System"

- "DLL/DCM/PLL/BUFR/PMCD Components"

- "Timing Group Creation with TNM/TNM\_NET Attributes"

- "Grouping Constraints"

#### About the Constraint System

The constraint system is that portion of the implementation tools (NGDBUILD) that parses and understands the physical and timing constraints for the design.

The constraint system:

- Parses the constraints from the following files and delivers this information to the other implementation tools:

- NCF

- ♦ UCF

- ◆ EDN/EDF/EDIF

- NGC

- NGO

- Confirms that the constraints are correctly specified for the design

- Applies the necessary attributes to the corresponding elements

- Issues error and warning messages for constraints that do not correlate correctly with the design

#### DLL/DCM/PLL/BUFR/PMCD Components

This section discusses DLL/DCM/PLL/BUFR/PMCD Components and includes:

- "About DLL/DCM/PLL/BUFR/PMCD Components"

- "Transformation Conditions"

- "New PERIOD Constraints on DCM Outputs"

- "The newly created TIMESPEC PERIOD constraints contain all the paths associated with the clock modifying block component. If the PERIOD constraint is not translated and then traces only to the clock modifying block component, the timing report show 0 items analyzed. No other PERIOD constraints are reported."

- "Analysis with NET PERIOD"

- "PHASE Keyword"

- "DLL/DCM/PLL Manipulation with PHASE"

#### About DLL/DCM/PLL/BUFR/PMCD Components

When a TIMESPEC PERIOD specification on the input pad clock net is traced or translated through the DCM/DLL/PLL/BUFR/PMCD component (also known as a clock-modifying block), the derived or output clocks are constrained with new PERIOD constraints.

In order to generate the destination-element-timing group, during transformation each clock output pin of the clock-modifying block is given:

- A new TIMESPEC PERIOD constraint

- A corresponding TNM\_NET constraint

The new TIMESPEC PERIOD constraint is based upon the manipulation of the clock modifying block component. The transformation:

- Takes into account the phase relationship factor of the clock outputs

- Performs the appropriate multiplication or division of the PERIOD requirement value

#### **Transformation Conditions**

The transformation occurs when:

- The TIMESPEC PERIOD constraint is traced into the CLKIN pin of the clock modifying block component, and

- The following conditions are met:

- The group associated with the PERIOD constraint is used in exactly *one* PERIOD constraint

- The group associated with the PERIOD constraint is *not* used in any other timing constraints, including FROM:TO (multicycle) or OFFSET constraints

- The group associated with the PERIOD constraint is *not* referenced or related to any other user group definition

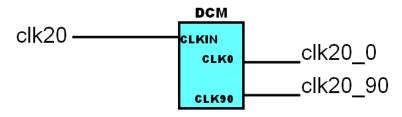

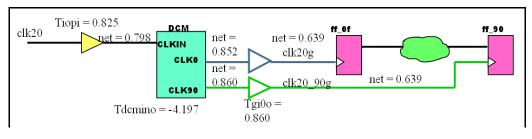

#### New PERIOD Constraints on DCM Outputs

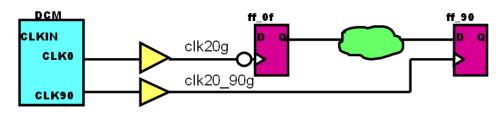

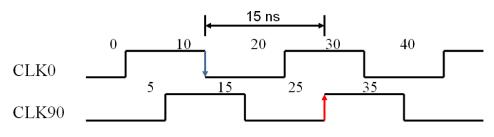

If the "Transformation Conditions" are met, the **TIMESPEC** "**TS\_clk20**" = **PERIOD** "**clk20\_grp**" **20** ns **HIGH 50** %; constraint is translated into the following constraints based upon the clock structure shown in Figure 3-1, "New PERIOD Constraints on DCM Outputs."

CLK0: TS\_clk20\_0=PERIOD clk20\_0 TS\_clk20\*1.000000 HIGH 50.000000% CLK90: TS\_clk20\_90=PERIOD clk20\_90 TS\_clk20\*1.000000 PHASE + 5.000000 nS HIGH 50.000000%

Figure 3-1: New PERIOD Constraints on DCM Outputs

The following message appears in the NGDBuild (design.bld) or MAP (design.mrp) report:

INFO:XdmHelpers:851 - TNM " clk20\_grp ", used in period specification

"TS\_clk20", was traced into DCM instance "my\_dcm". The following new TNM

groups and period specifications were generated at the DCM output(s):

clk0: TS\_clk20\_0=PERIOD clk20\_0 TS\_clk20\*1.000000 HIGH 50.000000% clk90: TS\_clk20\_90=PERIOD clk20\_90 TS\_clk20\*1.000000 PHASE + 5.000000 nS HIGH 50.000000%

If the CLKIN\_DIVIDE\_BY\_2 attribute is set to TRUE for the DCM in Figure 3-1, "New PERIOD Constraints on DCM Outputs," the translated PERIOD constraints are adjusted accordingly. The following constraints are the result of this attribute:

CLK0: TS\_clk20\_0=PERIOD clk20\_0 TS\_clk20\*2.000000 HIGH 50.000000% CLK90: TS\_clk20\_90=PERIOD clk20\_90 TS\_clk20\*2.000000 PHASE + 5.000000 nS HIGH 50.000000%

If the "Transformation Conditions" are not met:

- The PERIOD constraint is *not* placed on the output or derived clocks of the clock modifying block component, and

- An error or warning message is reported in the NGDBuild report

#### Error Message Example

Following is an example of an error message:

"ERROR:NgdHelpers:702 - The TNM "PAD\_CLK" drives the CLKIN pin of CLKDLL "\$I1". This TNM cannot be traced through the CLKDLL because it is not used in exactly one PERIOD specification. This TNM is used in the following user groups and/or specifications:

TS\_PAD\_CLK=PERIOD PAD\_CLK 20000.000000 pS HIGH 50.000000% TS\_01=FROM PAD\_CLK TO PADS 20000.000000 pS"

*Note:* The original TIMESPEC PERIOD constraint is reported in the timing report and shows "0 items analyzed."

The newly created TIMESPEC PERIOD constraints contain all the paths associated with the clock modifying block component. If the PERIOD constraint is not translated and then traces only to the clock modifying block component, the timing report show **0 items analyzed**. No other PERIOD constraints are reported.

If the PERIOD constraint traces to other synchronous elements, the analysis includes only those synchronous elements.

#### Synchronous Elements

Synchronous elements include:

- Flip Flops

- Latches

- Distributed RAM

- Block RAM

- Distributed ROM

- ISERDES

- OSERDES

- PPC405

- PPC440

- MULT18X18

- DSP48

- MGTs (GT, GT10, GT11, GTP)

- SRL16

- EMAC

- FIFO (16, 18, & 36)

- PCIE

- TEMAC

#### Analysis with NET PERIOD

When a NET PERIOD constraint is applied to the input clock pad or net, this constraint is not translated through the clock modifying block component. This can result in zero items or paths analyzed for these constraints.

The NET PERIOD is analyzed only during MAP, PAR, and Timing analysis. When "MAP - timing" and PAR call the timing tools, the timing tools do the clock modifying block manipulation for placement and routing, but not for the timing analysis timing reports.

When a TIMESPEC PERIOD constraint is traced into an input pin on a clock modifying block, NGDBuild or the translate process transforms the original TIMESPEC PERIOD constraint into new TIMESPEC PERIOD constraints based upon the derived output clocks. The NGDBuild report (design.bld) indicates this transformation.

MAP, PAR, and Timing Analyzer use the new derived clock TIMESPEC PERIOD constraints that are propagated to the Physical Constraints File (PCF). The original TIMESPEC PERIOD is unchanged during this transformation. It is used as a reference for the new TIMESPEC PERIOD constraints.

*Note:* Constraints Editor sees only the original PERIOD constraint and not the newly transformed PERIOD constraints.

#### PHASE Keyword

The PHASE keyword is used in the relationship between related clocks. The timing analysis tools use this relationship for the OFFSET constraints and cross-clock domain path analysis. The PHASE keyword can be entered in the UCF/NCF or through the translation of the DCM/DLL/PLL components during NGDBuild.

*Note:* If the phase shifted value of DCM/PLL/DLL component is changed in FPGA Editor, the change is not reflected in the PCF file.

The timing analysis tools use the PHASE keyword value in the PCF to emulate the DLL/DCM/PLL phase shift value. In order to see the change that was made in FPGA Editor, the PCF must also be modified manually with the corresponding change.

#### **DLL/DCM/PLL** Manipulation with PHASE

Table 3-1, "Transformation of PERIOD Constraint Through DCM," displays the new DCM/DLL/PLL component output clock net derived TIMESPEC PERIOD constraints, based upon the original PERIOD (TS\_CLKIN) constraints. TS\_CLKIN is expressed as a time value.

If TS\_CLKIN is expressed as a frequency value, the multiply and divide operations are reversed. If the DCM attributes FIXED\_PHASE\_SHIFT or VARIABLE\_PHASE\_SHIFT are used, the amount of the phase-shifted value is included in the PHASE keyword value.

The DCM attributes FIXED\_PHASE\_SHIFT or VARIABLE\_PHASE\_SHIFT phase shifting amount on the DCM is not reflected in Table 3-1, "Transformation of PERIOD Constraint Through DCM."

| Table 3-1: | Transformation of PERIOD Constraint Through DCM |

|------------|-------------------------------------------------|

|------------|-------------------------------------------------|

| Output Pin | PERIOD Value | PHASE Shift value           |

|------------|--------------|-----------------------------|

| CLK0       | TS_CLKIN * 1 | None                        |

| CLK90      | TS_CLKIN * 1 | PHASE + (clk0_period * 1/4) |

| CLK180     | TS_CLKIN * 1 | PHASE + (clk0_period * ½)   |

| CLK270   | TS_CLKIN * 1                                                                                                                            | PHASE + (clk0_period * 3/4) |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| CLK2x    | TS_CLKIN / 2                                                                                                                            | None                        |

| CLK2x180 | TS_CLKIN / 2                                                                                                                            | PHASE + (clk2x_period * ½)  |

| CLKDV    | TS_CLKIN * clkdv_divide                                                                                                                 | None                        |

|          | (clkdv_divide = value of<br>CLKDV_DIVIDE property<br>(default = 2.0))                                                                   |                             |

| CLKFX    | TS_CLKIN / clkfx_factor                                                                                                                 | None                        |

|          | (clkfx_factor = value of<br>CLKFX_MULTIPLY property (default<br>= 4.0) divided by value of<br>CLKFX_DIVIDE property<br>(default = 1.0)) |                             |

| CLKFX180 | TS_CLKIN / clkfx_factor                                                                                                                 | PHASE + (clkfx_period * ½)  |

|          | (clkfx_factor = value of<br>CLKFX_MULTIPLY property (default<br>= 4.0) divided by value of<br>CLKFX_DIVIDE property<br>(default = 1.0)) |                             |

#### Table 3-1: Transformation of PERIOD Constraint Through DCM (Cont'd)

#### Timing Group Creation with TNM/TNM\_NET Attributes

This section discusses Timing Group Creation with TNM/TNM\_NET Attributes and includes:

- "About Timing Group Creation with TNM/TNM\_NET Attributes"

- "Net Connectivity (NET)"

- "Predefined Time Groups"

- "Propagation Rules for TNM\_NET"

- "Instance or Hierarchy"

- "Instance Pin"

#### About Timing Group Creation with TNM/TNM\_NET Attributes

All design elements with same TNM/TNM\_NET attribute are considered a timing group. A design element may be in multiple timing groups (TNM/TNM\_NET).

The NM/TNM\_NET attributes can be applied to:

- Net Connectivity (NET)

- Instance/Module INST

- Instance Pin PIN

*Note:* To ensure correct timing analysis, Xilinx<sup>®</sup> recommends that you place only one TNM/TNM\_NET on each element, driver pin, or macro driver pin.

#### Net Connectivity (NET)

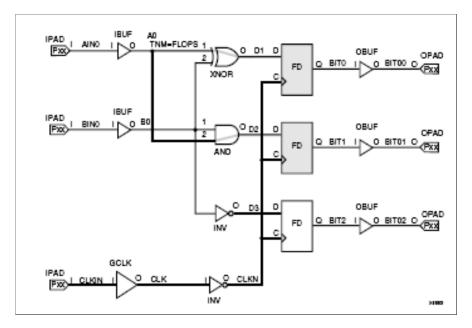

Identifying groups by net connectivity allows the grouping of elements by specifying a net or signal that eventually drives synchronous elements and pads. This method is a good way to identify multi-cycle path elements that are controlled by a clock enable and can be constrained as a FROM:TO (multi-cycle) constraint. This method uses TNM\_NET (timing net) or TNM (timing name) on a net of the design. The timing name attribute is commonly used on HDL port declarations, which are directly connected to pads.

If a timing name attribute is placed on a net or signal, the constraints parser traces the signal or net downstream to the synchronous elements. A timing name is an attribute that can be used to identify the elements that make up a time group that can be then used in a timing constraint. Those synchronous elements are then tagged with the same timing name attribute. The timing name attribute name is then used in a TIMESPEC or Timing Constraint.

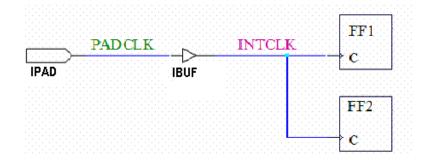

An example is the clock net in following schematic is traced forward to the two flip-flops in Figure 3-2, "TNM on the CLOCK pad or net traces downstream to the Flip-Flops."

Figure 3-2: TNM on the CLOCK pad or net traces downstream to the Flip-Flops

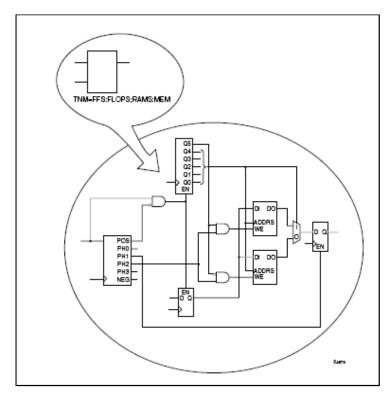

Flagging a common input (typically a clock signal or clock enable signal) can be used to group flip-flops, latches, or other synchronous elements. The TNM is traced forward along the path (through any number of gates, buffers, or combinatorial logic) until it reaches a flip-flop, input latch, or synchronous element. Those elements are added to the specified TNM or time group. Using TNM on a net that traces forward to create a group of flip-flops is shown in Figure 3-3, "TNM on the CLK net traced through combinatorial logic to synchronous elements (flip-flops)."

## *Figure 3-3:* **TNM on the CLK net traced through combinatorial logic to synchronous** elements (flip-flops)

When you place a TNM constraint on a net, use a qualifier to narrow the list of elements in the time group. A qualified TNM is traced forward until it reaches the first synchronous element that matches the qualifier type. The qualifier types are the predefined time groups. If that type of synchronous element matches the qualifier, the synchronous element is given that TNM attribute. Whether or not there is a match, the TNM is not traced through the synchronous element.

#### **Predefined Time Groups**

The following keywords are predefined time groups:

• FFS

All SLICE and IOB edge-triggered flip-flops and shift registers

• PADS

All I/O pads

- DSPS

- ◆ All DSP48 in Virtex<sup>™</sup>-4 devices

- All DSP48E in Virtex-5 devices

- RAMS

All single-port and dual-port SLICE LUT RAMs and block Rams

MULTS

All synchronous and asynchronous multipliers in the following devices:

- ♦ VirtexII-Pro

- ♦ VirtexII-ProX

- Virtex-4

- Virtex-5

- HSIOS

- All GT and GT10 in the following devices:

- VirtexII-Pro

- VirtexII-ProX

- Virtex-4

- All GTP in Virtex-5 devices

- CPUS

- All PPC405 in the following devices:

- VirtexII-Pro

- VirtexII-ProX

- Virtex-4

- All PPC450 in Virtex-5 devices

- LATCHES

All SLICE level-sensitive latches

• BRAMS\_PORTA

Port A of all dual-port block RAMs

• BRAMS\_PORTB

Port B of all dual-port block RAMs

The TNM\_NET is equivalent to TNM on a net, but produces different results on pad nets. The Translate Process or NGDBuild command never transfers a TNM\_NET constraint from the attached net to an input pad, as it does with the TNM constraint. You can use TNM\_NET only with nets. If TNM\_NET is used with any other objects (such as a pin or instance), a warning is generated and TNM\_NET definition is ignored.

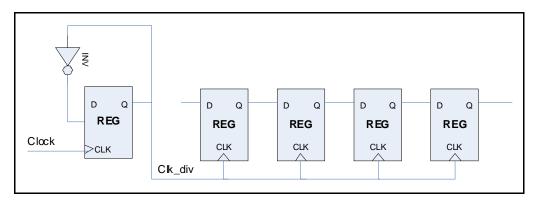

A TNM attribute on a pad net or the net between the IPAD and the IBUF, the constraints parser traces the signal or net upstream to the pad element, as shown in Figure 3-4, "Differences between TNM and TNM\_NET." The TNM\_NET attribute is traced through the buffer to the synchronous elements. In HDL designs, the IBUF output signal is the same as the IPAD or port name, so there are not differences between the TNM\_NET and TNM attributes. In this case, both timing name attributes trace downstream to the synchronous elements.

#### Propagation Rules for TNM\_NET

The propagation rules for TNM\_NET are:

- If applied to a pad net, TNM\_NET propagates forward through the IBUF elements and any other combinatorial logic to synchronous elements or pads.

- If applied to a clock-pad net, TNM\_NET propagates forward through the clock buffer to synchronous elements or pads.

- If applied to an input clock net of a DCM/DLL/PLL/PMCD/BUFR and associated with a PERIOD constraint, TNM\_NET propagates forward through the clock-modifying block to synchronous elements or pads.

Figure 3-4: Differences between TNM and TNM\_NET

In the design shown in Figure 3-4, "Differences between TNM and TNM\_NET," a TNM associated with the IPAD signal includes only the PAD symbol as the member of a time group. A TNM\_NET associated with the IPAD signal includes all the synchronous elements after the IBUF as members of a time group.

Following are examples of different ways to create time groups using the IPAD signal:

NET PADCLK TNM = PAD\_grp;

Use the **padclk** net to define the time group **PAD\_grp**. Contains the IPAD element.

NET PADCLK TNM = FFS "FF\_grp";

Use the **padclk** net to define the time group **FF\_grp**. Contains no flip-flop elements.

NET PADCLK TNM\_NET = FFS FF2\_grp;

Use the **padclk** net to define the time group **FF2\_grp**. Contains all flip-flop elements associated with this net.

In the design shown in Figure 3-4, "Differences between TNM and TNM\_NET," a TNM associated with the IBUF output signal can only include the synchronous elements after the IBUF as members of a time group.

Following are examples of time groups that use only the IBUF output signal:

NET INTCLK TNM = FFS FF1\_grp;

Use the **intclk** net to define the time group **FF1\_grp**. Contains all flip-flop elements associated with this net.

NET INTCLK TNM\_NET = RAMS Ram1\_grp;

Use the **intclk** net to define the time group **Ram1\_grp**. Contains all distributed and block RAM elements associated with this net.

#### Instance or Hierarchy

When a TNM attribute is placed on a module or macro, the constraints parser traces the macro or module down the hierarchy to the synchronous elements and pads. The attribute transverses through all levels of the hierarchy rather than forward along a net or signal. This feature is illustrated in:

- Figure 3-2, "TNM on the CLOCK pad or net traces downstream to the Flip-Flops"

- Figure 3-3, "TNM on the CLK net traced through combinatorial logic to synchronous elements (flip-flops)"

Those synchronous elements are then tagged with the same TNM attribute. The TNM attribute name is then used in a TIMESPEC or timing constraint. This method uses a TNM on a block of the design. Multiple instances of the same TNM attribute are used to identify the time group.

A macro or module is an element that performs some general purpose higher level function. It typically has a lower level design that consists of primitives or elements, other macros or modules, or both, connected together to implement the higher level function.

A TNM constraint attached to a module or macro indicates that all elements inside the macro or module (at all levels of hierarchy below the tagged module or macro) are part of the named time group. Use the **keep\_hierarchy** attribute to ensure that the design hierarchy is maintained. This feature is illustrated in:

- Figure 3-5, "The TNM on the upper left hierarchy is traced down to the lower level element"

- Figure 3-6, "Grouping via Instances"

*Figure 3-5:* The TNM on the upper left hierarchy is traced down to the lower level element

Figure 3-6: Grouping via Instances

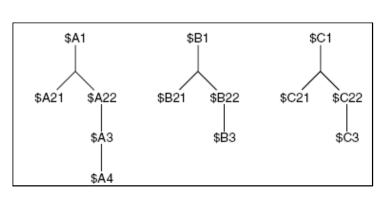

You can use wildcard characters to transverse the hierarchy of a design.

- A question mark (?) represents one character.

- An asterisk (\*) represents multiple characters.

The following example uses a wildcard character to transverse the hierarchy where **Level1** is a top level module:

• Level1/\*

Transverses all blocks in Level1 and below

• Level1/\*/

Transverses all blocks in Level1 but no further

The instances described below are either:

- Symbols on a schematics, or

- A symbol name as it appears in the EDIF netlist

An example of the wildcard transversing the design hierarchy is shown in Figure 3-6, "Grouping via Instances," for the following instances:

• INST \*

All synchronous elements are in this time group

• INST /\*

All synchronous elements are in this time group

• INST /\*/

Top level elements or modules are in this time group:

- ♦ A1

- ♦ B1

- C1

### • INST A1/\*

All elements one or more levels of hierarchy below the A1 hierarchy are in this time group:

- ♦ A21

- ♦ A22

- ♦ A3

- ♦ A4

- INST A1/\*/

All elements one level of hierarchy below the A1 hierarchy are in this time group:

- ♦ A21

- ♦ A22

- INST A1/\*/\*

All elements two or more levels of hierarchy below the A1 hierarchy are in this time group:

- ♦ A3

- ♦ A4

- INST A1/\*/\*/

All elements two levels of hierarchy below the A1 hierarchy are in this time group:

- ♦ A3

- INST A1/\*/\*/\*

All elements three or more levels of hierarchy below the A1 hierarchy are in this time group:

- ♦ A4

- INST A1/\*/\*/\*/

All elements three levels of hierarchy below the A1 hierarchy are in this time group:

- ♦ A4

- INST /\*/\*22/

All elements with instance name of 22 are in this time group:

- ♦ A22

- ♦ B22

- ♦ C22

- INST /\*/\*22

All elements with instance name of 22 and elements one level of hierarchy below are in this time group:

- ♦ A22

- ♦ A3

- ♦ A4

- ♦ B22

- ♦ B3

C22

C3

Figure 3-7: Transversing hierarchy with wildcards

### **Instance** Pin

Identifying groups by pin connectivity allows you to group elements by specifying a pin that eventually drives synchronous elements and pads. This method uses TNM (timing name) on a pin of the design. If a TNM attribute isplaced on a pin, the constraints parser traces the pin downstream to the synchronous elements. A TNM is an attribute that can be used to identify the elements that make up a time group that can be then used in a timing constraint.

An example of this method is shown in Figure 3-8, "TNM placed on Macro Pin traces downstream to synchronous elements."

### Figure 3-8: TNM placed on Macro Pin traces downstream to synchronous elements

When placing a TNM constraint on a pin, a qualifier can be used to narrow the list of elements in the time group. A qualified TNM is traced forward until it reaches the first synchronous element hat matches the qualifier type. The qualifier types are the predefined time groups. If that type of synchronous element matches the qualifier, the synchronous element is given that TNM attribute. Whether or not there is a match, the TNM is not traced through the synchronous element. For more information, see "Predefined Time Groups."

## **Grouping Constraints**

Grouping constraints allow you to group similar elements together for timing analysis. They can be defined in the following files:

- UCF

- NGC

- EDN

- EDIF/EDF

The timing analysis is on timing constraints, which are applied to logical paths. The logic paths typically start and stop at pads and synchronous elements. The grouped elements signify the starting and ending points for timing analysis. These starting and ending points can be based upon predefined groups, user-defined groups, or both. The timing groups are ideal for identifying groups of logic that operate at different speeds, or have different timing requirements.

The time groups are used in the timing analysis of the design. The user-defined and predefined time group informs the timing analysis tools the start and end points for each path being analyzed. The time groups are used in the following constraints:

- PERIOD

- OFFSET IN

- OFFSET OUT

- FROM:TO (Multi-cycle)

- TIG (Timing Ignore)

When using a specific net or instance name, you must use its full hierarchical path name. This allows the implementation tools to find the net or instance. The pattern matching wildcards can be used to specify when creating time groups with predefined time group qualifiers. This is done by using placing a pattern in parenthesis after the time group qualifier.

The predefined groups can reference all the following (among others):

- Flip-flops

- Latches

- Pads

- RAMs

- CPUs

- Multipliers

- High-speed-input/outputs

The predefined group keywords can be used globally, and to create user-defined subgroups. The predefined time groups are considered reserved keywords that define the types of synchronous elements and pads in the FPGA device.

For more information, see "Predefined Time Groups."

The user-defined time group name is case sensitive and can overlap with other userdefined time group and with predefined time groups. An example of design elements being is multiple time groups. In those cases, a register is in the FFS predefined time group, but is also in the **clk** time group, which is associated with the PERIOD constraint. Use the following keywords to define user-defined time groups:

- ♦ TNM

- ◆ TNM\_NET

- ♦ TIMEGRP

If the instance or net associated with the user-defined time group matches internal reserved words, the time group or constraint is rejected. The same is true for the user-defined time group name. In all the constraints files (NCF, UCF, and PCF), instances, or variable names that match internal reserved words, may be rejected unless the names are enclosed in double quotes. If the instance or net name does match an internal reserved word, enclose the name in double quotes. Double quotes are mandatory if the instance or net name contains special characters such as the tilde (~) or dollar sign (\$). Xilinx recommends using double quotes on all net and instances.

All elements with the same TNM or TNM\_NET attributes are considered a timing group. For more information about TNM and TNM\_NET attributes, see "Constraint System."

The TIMEGRP attribute is to combine existing time groups (pre-defined or user-defined) together or remove common elements from existing time groups, and create a new user-defined time group. The TIMEGRP attribute is also a method for creating a new time group by pattern matching (grouping a set of objects that all have output nets that begin with a given string).

Use the following keywords to create subsets of an existing time group:

- Rising edge synchronous elements (RISING)

- Falling edge synchronous elements (FALLING)

- Remove common elements (EXCEPT)

Use the EXCEPT keyword with a TIMEGRP attribute to remove elements from an alreadycreated time group. The overlapping items to be removed from the original time group must be in the excluded or EXCEPT time group. If the excluded time group does not overlap with the original time group, none of the design elements are removed. In that case, the new time group contains the same elements as the original time group.

In addition to using TIMEGRP to include multiple time groups or exclude multiple time groups, it also can be used to create sub-groups using the RISING and FALLING keywords. Use RISING and FALLING to create groups based upon the synchronous element triggered clocking edge (rising or falling edges).

### Pattern Matching

Pattern matching on either net or instance names can define the user-defined time group. Use wildcard characters to define a user-defined time group of symbols whose associated net name or instance name matches a specific pattern. Wildcards are used to generalize the group selection of synchronous elements. Wildcards can also be used to shorten and simplify the full hierarchical path to the synchronous elements.

Pattern matching is as follows:

- Asterisk (\*) Matches any string of zero or more characters

- Question Mark (?)

Matches a single character

Table 3-2: Pattern Matching Examples

| String  | Indicates                                                                            | Examples                                           |

|---------|--------------------------------------------------------------------------------------|----------------------------------------------------|

| DATA*   | any net or instance name that begins with <b>DATA</b>                                | DATA1, DATA22, and DATABASE                        |

| NUMBER? | any net names that begin<br>with <b>NUMBER</b> and ends with<br>one single character | NUMBER1 or NUMBERS, but<br>not NUNMBER or NUMBER12 |

A pattern may contain more than one wildcard character. For example, **\*AT?** specifies any net name that:

- Begins with one or more characters followed by AT, and

- Ends with any one character

Following are examples of net names included in **\*AT?**:

- BAT2

- CAT4

- THAT9

## **Time Group Examples**

Following are time group examples:

- "Time Group Example One (Predefined Group of RAMs)"

- "Time Group Example Two (Predefined Group of FFS)"

- "Time Group Example Three (Predefined Group on a Hierarchical Instance)"

- "Time Group Example Four (Combining Time Groups)"

- "Time Group Example Five (Removing Time Groups)"

- "Time Group Example Six (Clock Edges)"

### Time Group Example One (Predefined Group of RAMs)

Following is an example of a time group created with a search string and a predefined group of RAMs in a multicycle constraint:

INST my\_core TNM = RAMS my\_rams;

This time group (my\_rams) is the RAM components of the hierarchical block my\_core

- TIMSPEC TS01 = FROM FFS TO my\_rams 14.24ns;

- NET clock\_enable TNM\_NET = RAMS(address\*) fast\_rams;

This time group (fast\_rams) is the RAM components driven by net name of **clock\_enable** with an output net name of **address\***

• TIMSPEC TS01 = FROM FFS TO fast\_rams 12.48ns; OR

#### TIMESPEC TS01 = FROM FFS TO RAMS(address\*) 12.48ns;

The Destination time group is based upon RAM components with an output net name of **address\***,

Time Group Example Two (Predefined Group of FFS)

Following is an example of a time group created with a search string and a predefined group of FFS in a multi-cycle constraint:

TIMESPEC TS01 = FROM RAMS TO FFS(macro\_A/Qdata?) 14.25ns;

The Destination time group is based upon Flip Flop components with an output net named macro\_A/Qdata?,

Time Group Example Three (Predefined Group on a Hierarchical Instance)

Following is an example of a time group created with the predefined group on a hierarchical instance:

INST macroA TNM = LATCHES latch\_grp;

This time group (latch\_grp) consists of the latch components of the hierarchical instance macroA,

INST macroB TNM = RAMS memory\_grp;

This time group (**memory\_grp**) consists of the RAM components of the hierarchical instance **macroB**,

INST tester TNM = overall\_grp;

This time group (**overall\_grp**) consists of synchronous components (such as RAMS, FFS, LATCHES, and PADS) of the hierarchical instance **tester**.

Time Group Example Four (Combining Time Groups)

The following example shows how to define a new time group by combining it with other time groups:

• TIMEGRP "larger\_grp" = "small\_grp" "medium\_grp";

Combines **small\_grp** and **medium\_grp** into a larger group called **larger\_grp**

• **TIMEGRP memory\_and\_latch\_grp = latch\_grp memory\_grp;** Combine the elements of **latch\_grp** and **memory\_grp**.

Time Group Example Five (Removing Time Groups)

Following are examples using the EXCEPT keyword with the TIMEGRP attribute:

TIMEGRP new\_time\_group = Original\_time\_group EXCEPT a\_few\_items\_time\_grp;

Removes the elements of **a\_few\_items\_time\_grp** from **Original\_time\_group**.

• TIMEGRP "medium\_grp" = "small\_grp" EXCEPT "smaller\_grp";

Creates a time **group medium\_grp** from the elements of **small\_grp** and removes the elements of **smaller\_grp**.

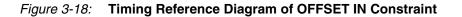

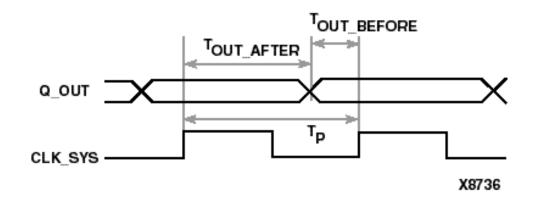

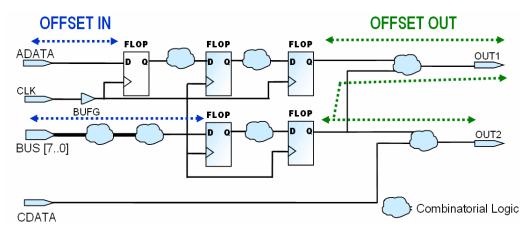

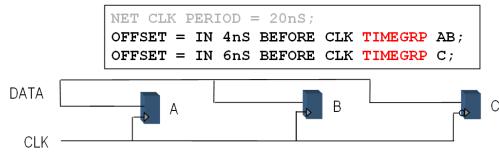

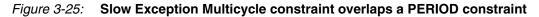

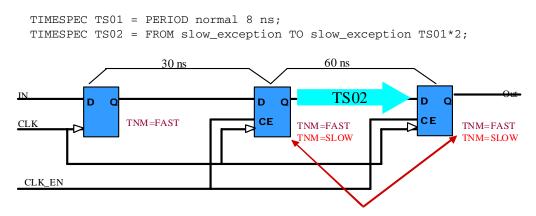

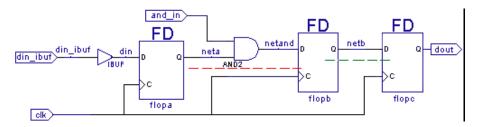

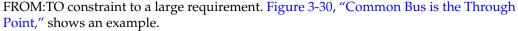

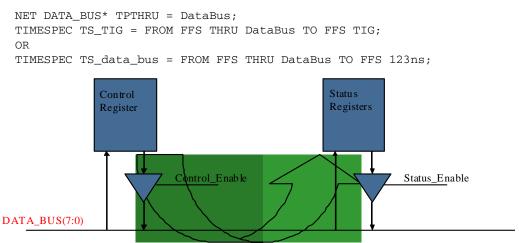

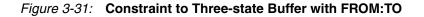

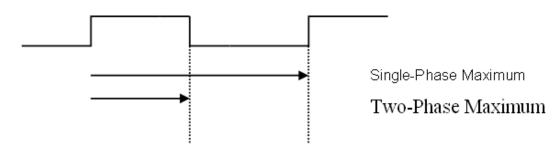

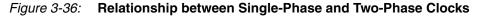

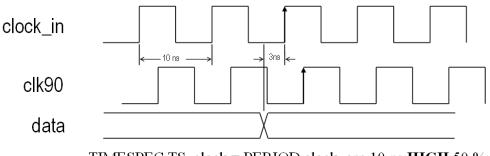

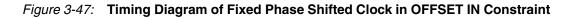

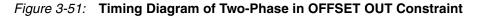

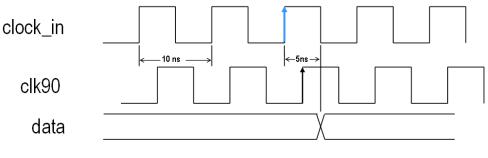

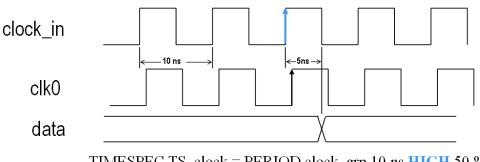

• TIMEGRP all\_except\_mem\_and\_latches\_grp = overall\_grp EXCEPT memory\_and\_latch\_grp;