# I-8084W User Manual

Version 1.0 beta1, June 2009

Service and usage information for LinPAC-8000 Series

## Warranty

All products manufactured by ICP DAS are under warranty regarding defective materials for a period of one year, beginning from the date of delivery to the original purchaser.

## Warning

ICP DAS assumes no liability for any damage resulting from the use of this product.

ICP DAS reserves the right to change this manual at any time without notice. The information furnished by ICP DAS is believed to be accurate and reliable. However, no responsibility is assumed by ICP DAS for its use, no for any infringements of patents or other rights of third parties resulting from its use.

## Copyright

Copyright © 2009 by ICP DAS Co., Ltd. All rights are reserved.

## **Trademarks**

The names used in this manual are for identification purpose only and may be registered trademarks of their respective companies.

# **Table of Contents**

| Table of Contents                   | 3  |

|-------------------------------------|----|

| 1. Introduction to the I8084W       | 5  |

| 1.1. Specification                  | 5  |

| 1.2. Pin Assignment                 | 7  |

| 1.3. I/O Structure                  | 8  |

| 1.4. Wiring Connection              | 12 |

| 2. Hardware Operation Principle     | 14 |

| 2.1. Input Signal Model             | 14 |

| 2.2. Digital Low Pass Filter        | 17 |

| 2.3. Operation Mode                 | 27 |

| 2.3.1. Mode 00: Pulse /Dir Counting | 28 |

| 2.3.2. MODE 01: UP/DOWN COUNTING    | 29 |

| 2.3.3. MODE 02: FREQUENCY MODE      | 30 |

| 2.3.4. MODE 03: UP COUNTING         | 31 |

| 2.3.5. Mode 04: Quadrant Counting   | 32 |

| 3. Usage on the LinPAC              | 33 |

| 3.1. i8084W_GetLibVersion           | 33 |

| 3.2. i8084W_GetLibDate              | 35 |

| 3.3. i8084W_InitDriver              | 36 |

| 3.4. i8084W_SetChannelMode          | 37 |

| 3.5. i8084W_AutoScan                | 38 |

| 3.6. i8084W_ReadCntABPhase          | 39 |

| 3.7. i8084W_ReadCntPulseDir         | 40 |

| 3.8. i8084W_ReadCntUpDown           | 41 |

| 3.9. i8084W_ReadFreq                | 42 |

| 3.10. i8084W_ReadCntUp              | 43 |

| 3.11. i8084W_ClrCnt                 | 44 |

| 3.12. i8084W_RecoverDefaultSetting  | 45 |

| 3.13. i8084W_ReadXorRegister        | 46 |

| 3.14. i8084W_SetXorRegister         | 47 |

| 3.15. i8084W_ReadChannelMode        | 48 |

| 3.16. | i8084W_ReadLowPassFilter_Us     | 49 |

|-------|---------------------------------|----|

| 3.17. | i8084W_SetLowPassFilter_Us      | 50 |

| 3.18. | i8084W_ReadLowPassFilter_Status | 51 |

| 3.19. | i8084W_SetLowPassFilter_Status  | 52 |

| 3.20. | i8084W_ReadFreqMode             | 53 |

| 3.21. | i8084W_SetFreqMode              | 54 |

| 3.22. | i8084W_ReadFreqUpdateTime       | 55 |

| 3.23. | i8084W_SetFreqUpdateTime        | 56 |

| 3.24. | i8084W_ReadDI_Xor               | 57 |

| 3.25. | i8084W_ReadDI_XorLPF            | 58 |

| 3.26. | i8084W_EepWriteEnable           | 59 |

| 3.27. | i8084W_EepWriteDisable          | 60 |

| 3.28. | i8084W_EepWriteWord             | 61 |

| 3.29. | i8084W_EepReadWord              | 62 |

# 1. Introduction to the I8084W

I-8084W is a 4/8-channel Counter/Frequency Module.

# 1.1. Specification

| Digital Input           |                                                     |

|-------------------------|-----------------------------------------------------|

|                         | 4-ch Up/Down Counter (Up/Down)                      |

|                         | 4-ch Dir/Pulse Counter (Bi-direction)               |

|                         | 4-ch Quadrant Counting                              |

| Mode                    | 8-ch Up Counter                                     |

|                         | 8-ch Frequency                                      |

|                         | Programmable Built-in gate time: 0.33 sec (Default) |

|                         | Programmable Digital Noise Filter: 1 ~ 32737 μs     |

| Isolated Input Level    | Logic Level 0: +1 V max                             |

| isolated iliput Level   | Logic Level 1: +4.5 ~ 30 V                          |

| TTL Input Level         | Logic Level 0: 0 ~ 0.8 V                            |

| i i L iliput Level      | Logic Level 1: 2 ~ 5 V                              |

| Input Frequency         | 0 ~ 450 kHz (Frequency Mode)                        |

| input Frequency         | 450 kHz (Counter Mode)                              |

| Minimum Pulse Width     | 1 μs (Frequency Mode)                               |

| Willimiditi Puise Widui | 1 μs (Counter Mode)                                 |

| EEPROM                  | 128 KB                                              |

| Isolated Voltage        | 1000 Vrms                                           |

| ESD Protection          | 2 kV (Contact for each channel)                     |

# LED Display

## 1 LED as Power Indicator

## 8 LEDs as Digital Input Indicators

| Power             |     |

|-------------------|-----|

| Power Consumption | 1 W |

| Environment           |                             |

|-----------------------|-----------------------------|

| Operating Temperature | -25 ~ 75 °C                 |

| Storage Temperature   | -30 ~ 85 °C                 |

| Humidity              | 5 ~ 95 % RH, Non-condensing |

## Dimensions

30 mm x 85 mm x 114 mm (W x L x H)

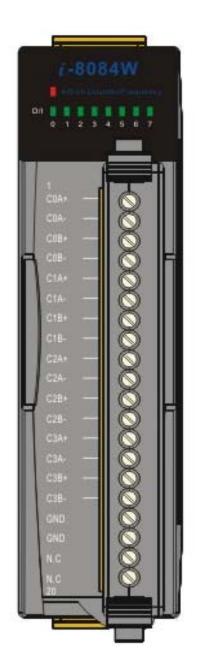

#### 1.2. Pin Assignment

| Terminal No. | Pin Assignment |

|--------------|----------------|

| C = ( 01     | C0A+           |

| C a 02       | C0A-           |

| C = 03       | C0B+           |

| [ n 04       | C0B-           |

| [ D 05       | C1A+           |

| C 06         | C1A-           |

| [ = ( 07     | C1B+           |

| C = 08       | C1B-           |

| C = 09       | C2A+           |

| [ = 10       | C2A-           |

| [ n 11       | C2B+           |

| [ n 12       | C2B-           |

| L = 13       | C3A+           |

| C 0 14       | C3A-           |

| L = 15       | C3B+           |

| C = 16       | C3B-           |

| [ a 17       | GND            |

| 18           | GND            |

| 19           | N.C            |

| 20           | N.C            |

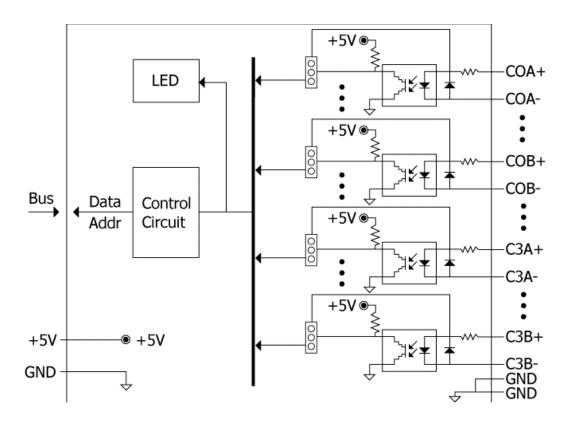

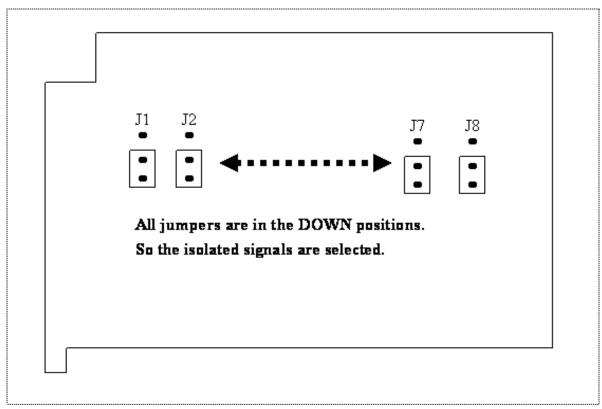

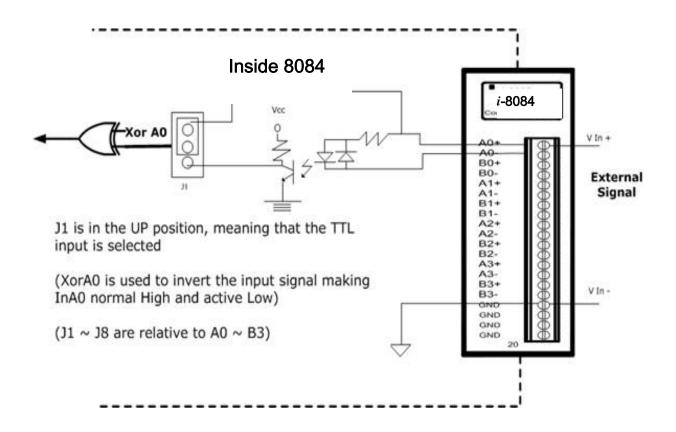

# 1.3. I/O Structure

The default jumper settings are as follows:

# Isolated

Input:

# TTL

Input:

Isolated or TTL input is selected by using JP1 to JP3 as indicated below:

| J1 | Select A0 |

|----|-----------|

| J2 | Select B0 |

| J3 | Select A1 |

| J4 | Select B1 |

| J5 | Select A2 |

| J6 | Select B2 |

| J7 | Select A3 |

| J8 | Select B3 |

| J1/2/3/4/5/6/7/8                    | J1/2/3/4/5/6/7/8 |

|-------------------------------------|------------------|

| +<br>•                              | •                |

| Isolated input<br>(Default Setting) | TTL input        |

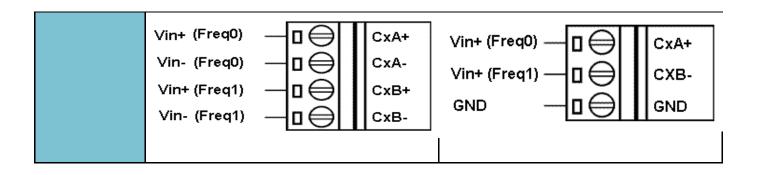

# 1.4. Wiring Connection

| Counter Type |                                                                             |                                                                            |  |

|--------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------|--|

| Mode         | Isolation                                                                   | No-n-Isolation                                                             |  |

| Dir/Pulse    | Vin+ (Pulse) — CxA+ Vin- (Pulse) — CxA- Vin+ (Dir) — CxB+ Vin- (Dir) — CxB- | Vin+ (Pulse) — CxA+ Vin+ (Dir)rol — CXB- Vin- (Pulse) — GND and Vin- (Dir) |  |

| Up/Down      | Vin+ (Up) — CxA+ Vin- (Up) — CxA- Vin+ (Down) — CxB+ Vin- (Down) — CxB-     | Vin+ (Up) CxA+ Vin+ (Down) CXB- Vin- (Up) GND and Vin- (Down)              |  |

| Up           | Vin+ (Up0) —                                                                | Vin+ (Up0) —                                                               |  |

| Quadrant     | Vin+ (A0) —                                                                 | Vin+ (A0) — CxA+ Vin+ (B0) — CXB- GND — GND                                |  |

| Frequenc | у Туре    |                |

|----------|-----------|----------------|

| Mode     | Isolation | No-n-Isolation |

# 2. Hardware Operation Principle

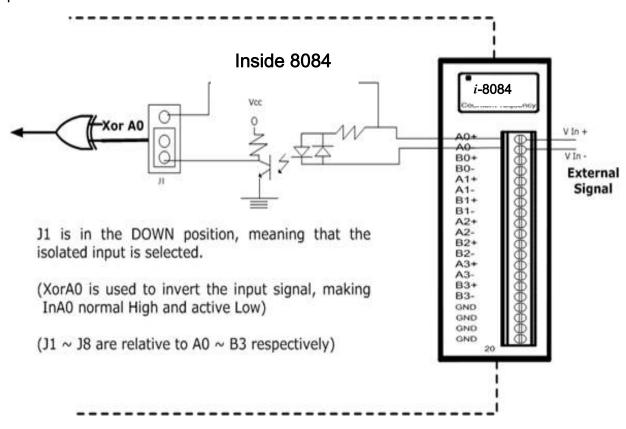

# 2.1. Input Signal Model

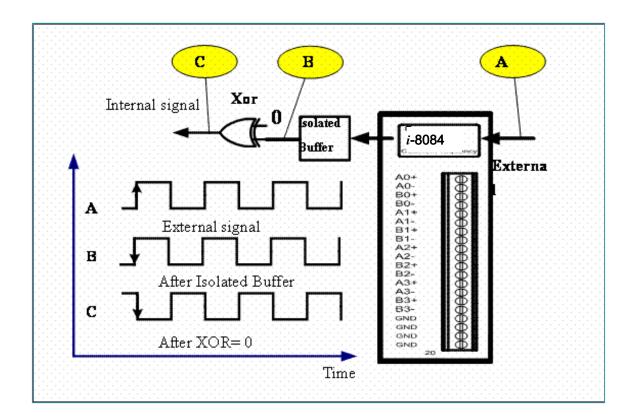

## 1. Isolated Input (XOR=0)

The operational logic applied on the 8084 modules is the falling edge trigger.

(Normal High and Active Low)

The external signal is input into an 8084 module through the isolated mechanism, with the signal being reversed from the external signal.

This internal signal is the suggested waveform, as it doesn't need to execute the XOR operation (XOR=0).

The solution is shown below.

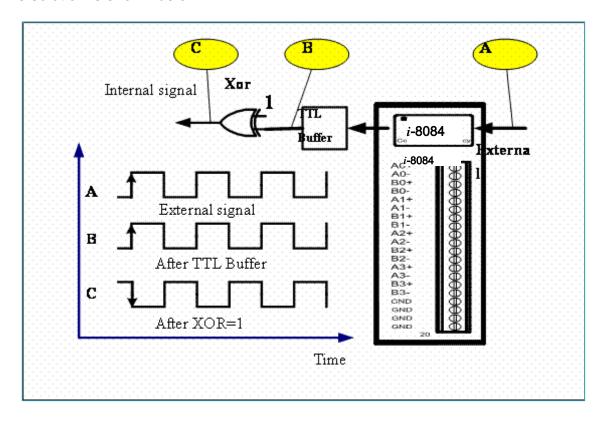

## 2. TTL Input (XOR=1)

When an external TTL signal is input into an 8084 module through the TTL mechanism, the signal will be the same as the external signal. This internal signal isn't the recommended waveform as it must execute the exclusive OR (XOR=1) operation.

The solution is shown below.

## 3. Always XOR=0

Regardless of whether the input signal is TTL or isolated, XOR is always set to 0, and the maximum count error can only be 1. XOR=0 can be used for all cases, if a 1-count error is acceptable.

#### Note:

- When XOR=0 and the 8084 module status is OPEN status (i.e. no signals on the input terminal), regardless of whether you select the TTL or Isolated mode, the signal at the C point will always be 1. Similarly, if XOR=1 and the status is OPEN, then the signal at the C point will always be 0.

- If the input signal is a pulse rather than a 50/50 duty cycle square waveform, then the 1-count error will not occur as the pulse width is shorter..

# 2.2. Digital Low Pass Filter

The 8084 has three independent 2nd-order digital noise filters, LP0, LP1 & LP2, to remove noises as follows:

| Channel | Low Pass Filter   |

|---------|-------------------|

| A0      | Low Pass Filter 0 |

| В0      | Low Pass Filter 0 |

| A1      | Low Pass Filter 1 |

| B1      | Low Pass Filter 1 |

| A2      | Low Pass Filter 2 |

| B2      | Low Pass Filter 2 |

| A3      | Low Pass Filter 2 |

| В3      | Low Pass Filter 2 |

- The Low Pass Filter can be either disabled or programmable from 2 μs to 65535 μs.

- The Low Pass Filter will apply to all working modes, counter or frequency.

- These 3 Low Pass Filters are disabled status in the default shipping. User defined program can be used to issue a command to enable or disable the filters.

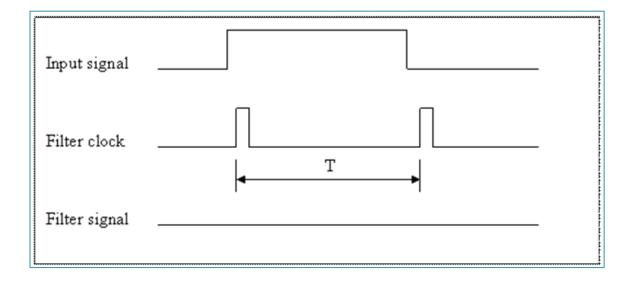

- Assume that the filter clock of the Low Pass Filter is set to T, this clock is used to sample the input signal.

- If one of the adjacent 2 samples is low, then the input signal will be removed as follows:

- If the high width of the input signal is shorter then T, it will be filtered.

- If the adjacent 2 samples are all HIGH, the input signal can pass as indicated below:

Note: the filter signal is shorter than the original input signal.

١

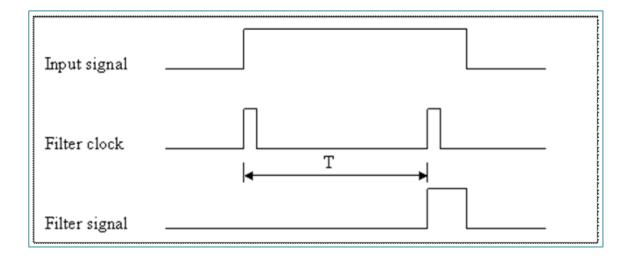

• If the input signal is shorter than 2T, it may be filtered in the following manner:

- The relationship between the input signal and the filter signal is as follows:

if (2T signal), it will pass

- if (2T<input signal), it will pass

- if (T<=input signal<=2T), it may be filtered or passed

- if (input signal <T), it will be filtered

- The software driver, i8084\_SetLowPassUs (int Slot, int Channel, unsigned int Us), provides an parameter, Us which can be used to set the Low Pass Filter as follows: if Us=1 and 2T =1μs then T = 0.5μs and signal<=0.5μs will be removed if Us=2 and 2T= 2μs then T = 1 μs and signal<=1μs will be removed if Us=N, N from 1 to 0x7fff and 2T = N μs then signal<=(N/2) μs will be removed</p>

- The Low Pass Filter range can be configured from 1µs to 32767µs. The high width of the signal < (Us/2) will be removed.</li>

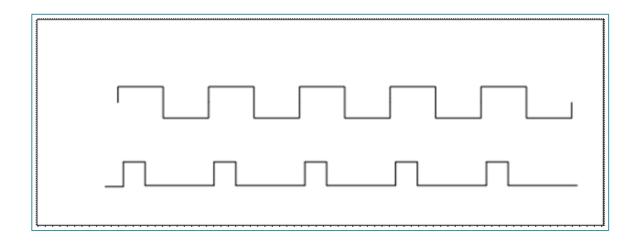

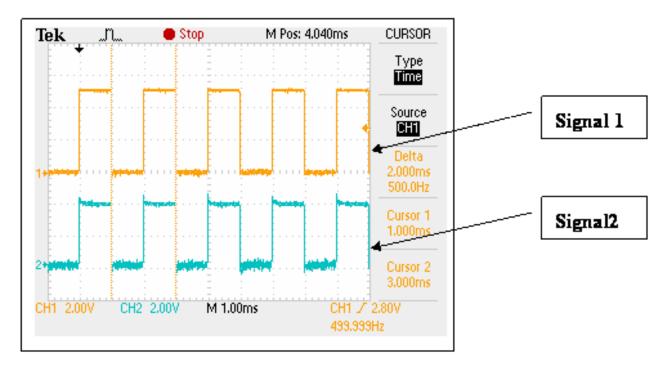

For example, if you use a function generator as signal source, the 500Hz signal & 50/50 duty cycle will generate a 1000 µs high & 1000 µs low as follows:

Input signal=500Hz & Low Pass Filter Disable

Signal 1 =

input signal=500Hz, 50/50 duty cycle

## Signal 2 =

input signal after Xor and Low Pass Filter, now Xor=0 and Low Pass Filter is disable.

If the Low Pass Filter is disabled, signal 2 will be the same as signal 1 in the above diagram.

If the Low Pass Filter is enabled, signal 2 will be shorter than signal 1 as shown below:

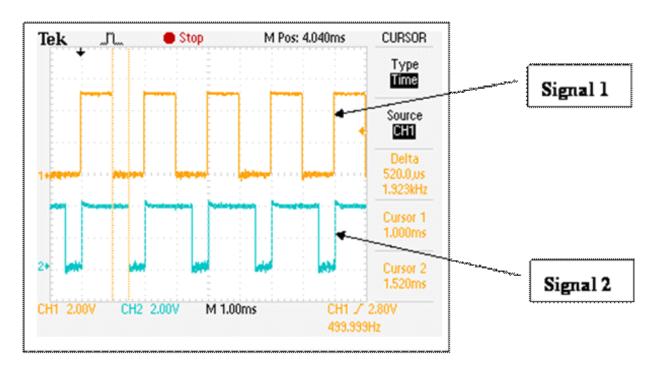

Input signal=500Hz & Low Pass Filter Enabled=1µs

#### Signal 1 =

input signal=500Hz, 50/50 duty cycle

#### Signal 2 =

input signal after Xor and Low Pass Filter, now Xor=0 and the Low Pass Filter is enabled.

Nearly all pulses are passed.

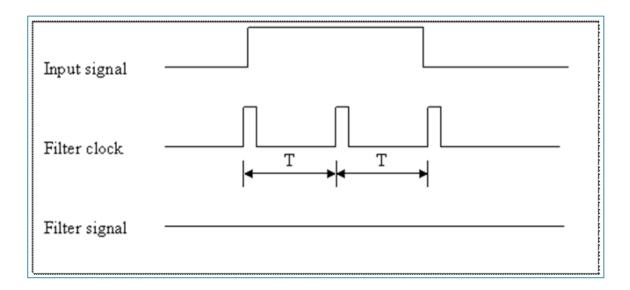

Now you can find that nearly all pulses are passed. If the input signal is increased to 600Hz, then some of the pulses are filtered as follows:

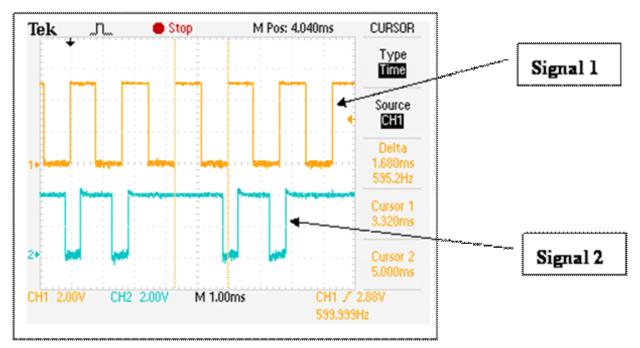

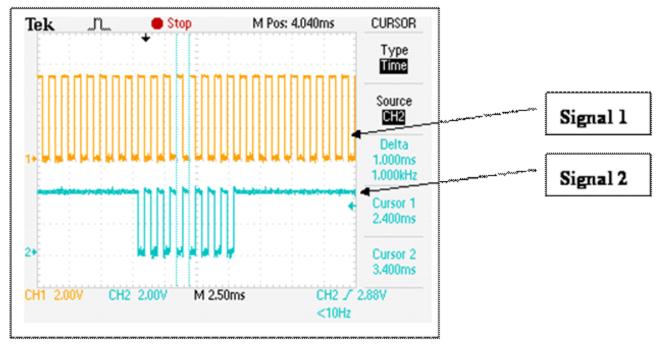

Input signal=600Hz & Low Pass Filter Enabled=1µs

## Signal 1 =

input signal=600Hz, 50/50 duty cycle.

## Signal 2 =

input signal after Xor and Low Pass Filter, now Xor =0 and Low Pass Filter is enabled.

Some pulses are filtered.

If the input signal is increased to 900Hz, then nearly all pulses are filtered as illustrated below:

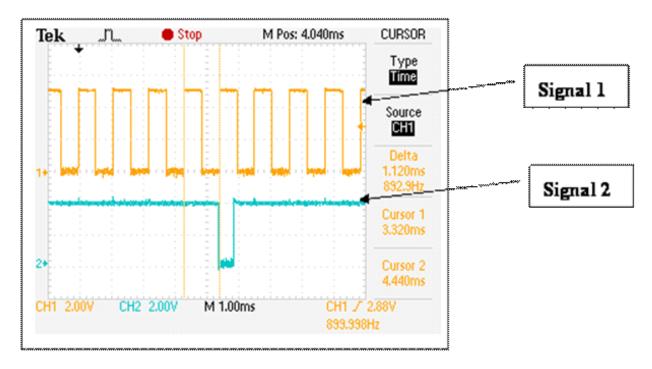

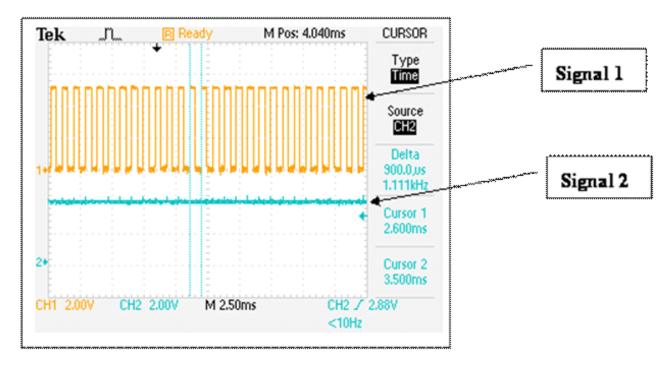

Input signal=900Hz & Low Pass Filter Enabled=1µs

#### Signal 1 =

input signal=900Hz, 50/50 duty cycle

## Signal 2 =

input signal after Xor and Low Pass Filter, now Xor=0 and the Low Pass Filter is enabled.

Nearly all pulses are filtered.

Because there are some frequency offset errors in the internal crystal, there may be some noises when the input signal width = Low Pass Filter/2 as follows:

Input signal=1000Hz & Low Pass Filter Enabled=1µs

## Signal 1 =

input signal=1000Hz, 50/50 duty cycle à pulse width=500 µs

#### Signal 2 =

input signal after Xor and Low Pass Filter, now Xor=0 and the Low Pass Filter is enabled. Signal Pulse=500 µs=Low Pass Filter/2.

Nearly all pulses are filtered, but sometimes certain noises will not be filtered.

If the input signal is increased to 1100Hz, then all pulses will be filtered as shown in Figure 1-12:

Input signal=1100Hz & Low Pass Filter Enabled=1µs

In summary, apply the minimum 1µs on Low Pass Filters.

The result of the signal being processed by the Low Pass Filter as follows:

| Input signal frequency(Hz)                             | After Low Pass Filter processing                      | Reference |

|--------------------------------------------------------|-------------------------------------------------------|-----------|

| Input signal <500Hz<br>(Low Pass Filter=1µs)           | All signals will be passed                            | Figure 1  |

| Input signal =500Hz<br>(Low Pass Filter=1µs)           | All signals should be passed                          | Figure 2  |

| Input signal =600Hz<br>(Low Pass Filter=1µs)           | Some signals will be filtered and some will be passed | Figure 3  |

| Input signal =900Hz<br>(Low Pass Filter=1µs)           | Many signals will be filtered and few will be passed  | Figure 4  |

| Input signal =1000Hz<br>(Low Pass Filter=1µs)          | Nearly all signals are filtered                       | Figure 5  |

| Input signal =1100Hz (>1k Hz)<br>(Low Pass Filter=1µs) | All signals will be filtered                          | Figure 6  |

For the same reason, if the signal pulse=Low Pass Filter, certain pulses may be filtered. Therefore, it is recommended to set the cycle time of Low Pass Filter about 5% less than the cycle time of input signal pulse as shown below:

Input pulse =1 ms = 1000 µs à set Low Pass Filter <=950 µs

if Input pulse = 100 μs , set Low Pass Filter <= 95 μs

The minimum Low Pass Filter = 1  $\mu$ s, input signal < 475K, 50/50 duty cycle

As a result, the maximum speed of the 8084 is recommended to 450K, 50/50 duty cycle.

# 2.3. Operation Mode

| Operation Mode | Description             | Number of counter and frequency sets |

|----------------|-------------------------|--------------------------------------|

| 00             | Dir/Pulse counting mode | 4 sets                               |

| 01             | Up/Down counting mode   | 4 sets                               |

| 02             | Frequency mode          | 8 sets                               |

| 03             | Up counting mode        | 8 sets                               |

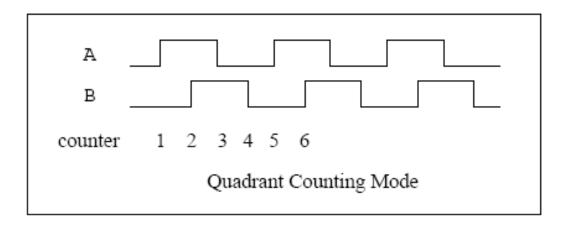

| 04             | Quadrant Counting mode  | 4 sets                               |

The input channels mapping table and working modes are indicated below:

|    | Mode 00 | Mode 01 | Mode 02     | Mode 03 | Mode 04 |

|----|---------|---------|-------------|---------|---------|

| A0 | Pulse 0 | Up 0    | Frequency 0 | Up 0    | A0      |

| В0 | Dir 0   | Down 0  | Frequency 1 | Up 1    | В0      |

| A1 | Pulse 2 | Up 2    | Frequency 2 | Up 2    | A1      |

| B1 | Dir 2   | Down 2  | Frequency 3 | Up 3    | B1      |

| A2 | Pulse 4 | Up 4    | Frequency 4 | Up 4    | A2      |

| B2 | Dir 4   | Down 4  | Frequency 5 | Up 5    | B2      |

| A3 | Pulse 6 | Up 6    | Frequency 6 | Up 6    | A3      |

| B3 | Dir 6   | Down 6  | Frequency 7 | Up 7    | B3      |

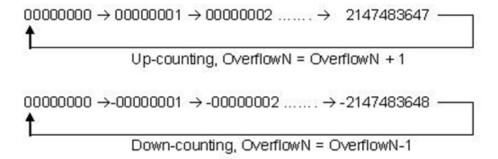

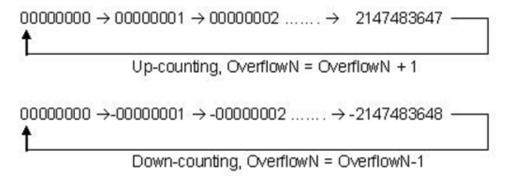

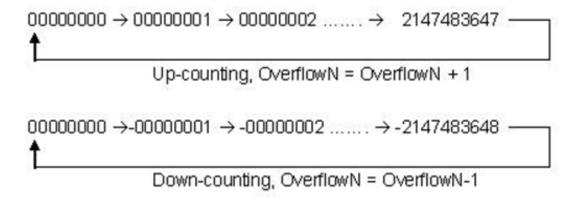

## CountN =

the counter value for channel N, 32bit wide, from -2147483648 to 2147483647

#### OverflowN =

the counting overflow number for channel N, 16bit wide, from -32768 to 32767

Total Counting Value bit = 32bit + 16bit = 48bit

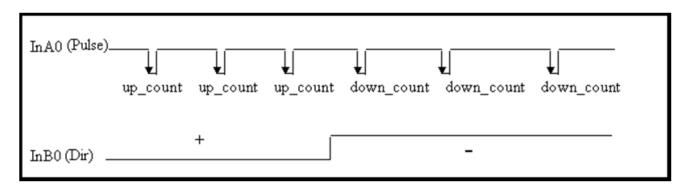

The counter operation for mode 00 (Dir/Pulse mode) is as follows:

- When InB0 is used as Dir, if InB0 is High, counter\_0 will be increased by one for every falling edge of InA0.

- If InB0 is Low, counter\_0 will be decreased by one for every falling edge of InA0.

The counter operation is given as follows:

| Pulse/Dir Counter | Counting Variable | Total Counting Value            |

|-------------------|-------------------|---------------------------------|

| A0, B0            | Count0, Overflow0 | Count0 + Overflow0 * 2147483648 |

| A1, B1            | Count2, Overflow2 | Count2 + Overflow2 * 2147483648 |

| A2, B2            | Count4, Overflow4 | Count4 + Overflow4 * 2147483648 |

| A3, B3            | Count6, Overflow6 | Count6 + Overflow6 * 2147483648 |

CountN = the counter value for channel N, 32bit wide, from -2147483648 to 2147483647

OverflowN = the counting overflow number for channel N, 16bit wide, from -32768 to 32767

Total Counting Value bit = 32bit + 16bit = 48bit

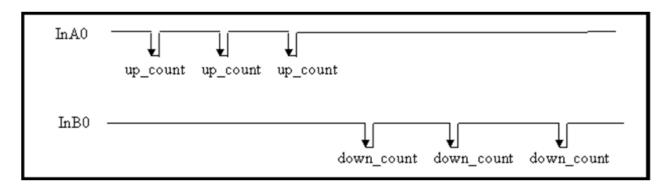

The counter operation for mode 01 (Up/Down mode) is as follows:

When InA0 is used as a UP\_clock and InB0 is used as a DOWN\_clock. The counter\_0 will be increased by one for every falling edge of InA0 and decreased by one for every falling edge of InB0.

| Up/Down Counter | Counting Variable | Total Counting Value            |

|-----------------|-------------------|---------------------------------|

| A0, B0          | Count0, Overflow0 | Count0 + Overflow0 * 2147483648 |

| A1, B1          | Count2, Overflow2 | Count2 + Overflow2 * 2147483648 |

| A2, B2          | Count4, Overflow4 | Count4 + Overflow4 * 2147483648 |

| A3, B3          | Count6, Overflow6 | Count6 + Overflow6 * 2147483648 |

#### CountN =

the counter value for channel N, 32bit wide, from -2147483648 to 2147483647

#### OverflowN =

the counting overflow number for channel N, 16bit wide, from -32768 to 32767

Total Counting Value bit = 32bit + 16bit = 48bit

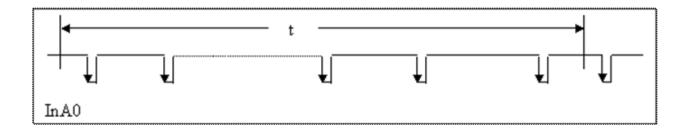

The frequency operation for mode 02 is as follows:

| Frequency | Frequency Variable |

|-----------|--------------------|

| A0        | Frequency0         |

| В0        | Frequency1         |

| A1        | Frequency2         |

| B1        | Frequency3         |

| A2        | Frequency4         |

| B2        | Frequency5         |

| A3        | Frequency6         |

| B3        | Frequency7         |

Period of update time t =0.33 second is the default setting. A user defined command can be used to change the value of t for special applications.

Frequency = Counter value / Period of scan time

Assume t = 0.1 seconds.

If count = 1 à frequency = 1/(0.1/1) = 10 Hz

If count = 10 à frequency = 1/(0.1/10) = 100 Hz

All frequency channels will be updated every 0.1 seconds for t= 0.1 seconds.

The software driver provides three ways to adjust.

They are Auto select, Low and High Frequency. (The default is Auto select)

The default configuration data is as follows:

Auto Frequency = the frequency channel will be updated every 330 million seconds;

Low Frequency = the frequency channel will be updated every 1000 million seconds;

High Frequency = the frequency channel will be updated every 100 million seconds;

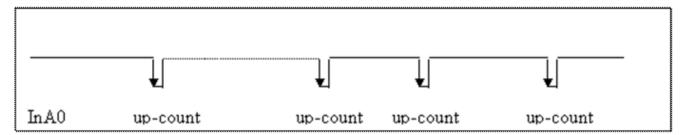

The counter operation for mode 03 is as follows:

Counter\_0 will increment by one for every falling edge of InA0

| Up Counter | Counting Variable | Total Counting Value            |

|------------|-------------------|---------------------------------|

| A0         | Count0, Overflow0 | Count0 + Overflow0 * 4294967296 |

| В0         | Count1, Overflow1 | Count1 + Overflow1 * 4294967296 |

| A1         | Count2, Overflow2 | Count2 + Overflow2 * 4294967296 |

| B1         | Count3, Overflow3 | Count3 + Overflow3 * 4294967296 |

| A2         | Count4, Overflow4 | Count4 + Overflow4 * 4294967296 |

| B2         | Count5, Overflow5 | Count5 + Overflow5 * 4294967296 |

| A3         | Count6, Overflow6 | Count6 + Overflow6 * 4294967296 |

| В3         | Count7, Overflow7 | Count7 + Overflow7 * 4294967296 |

The counter operation is as follows:

#### CountN =

current counter value for channel N, 32bit wide, from 0 to 4294967295

#### OverflowN =

The counting overflow number for channel N, 16bit wide, from 0 to 65535

Total Counting Value = CountN + OverflowN \* 4294967296 Total Counting Bit = 32bit + 16bit = 48bit

When InA0 is used as a UP\_clock and InB0 is used as a DOWN\_clock. The counter\_0 will be increased by one for every falling edge of InA0 and decreased by one for every falling edge of InB0.

# 3. Usage on the LinPAC

# LinPAC Introduction and Software Development

I-8084W can be plugged on the LinPAC-8000 . Please refer to the Web site <a href="http://www.icpdas.com/products/PAC/linpac-8000/lp-8x3x\_hardware.htm">http://www.icpdas.com/products/PAC/linpac-8000/lp-8x3x\_hardware.htm</a>

<a href="http://www.icpdas.com/products/PAC/linpac-8000/lp-8x4x\_hardware.htm">http://www.icpdas.com/products/PAC/linpac-8000/lp-8x81\_hardware.htm</a>

# I-8084W Demo for LinPAC-8000

The latest demo at C:\cygwin\LinCon8k\examples\i8k in LinPAC SDK as below: http://ftp.icpdas.com/pub/cd/linpac/napdos/lp-8x4x/sdk/

# 3.1. i8084W\_GetLibVersion

Get the version number of i8084 library Rev:5.0.0

# **Syntax**

int i8084W\_GetLibVersion()

# 3.2. i8084W\_GetLibDate

Get the date of 8084 library, Sep 03 2003

# **Syntax**

Void i8084W\_GetLibDate(char\* LibDate)

# 3.3. i8084W\_InitDriver

Configure the 8084 with the setting stored in the EEPROM.

If there is no settings stored in the EEPROM, the function will call i8084W\_RecoverDefaultSetting.

## **Syntax**

int i8084W\_InitDriver(int Slot)

## Parameter and Return Values

Slot:

1~8

#### Return:

- $0 \rightarrow OK$

- -1 → Module not found

- >0 → Some Pulse/Dir counters have one count offset (+1)

Bit0=1 A0 has one count offset (+1)

Bit2=1 A1 has one count offset (+1)

Bit4=1 A2 has one count offset (+1)

Bit6=1 A3 has one count offset (+1)

(due to the input channel is high)

## 3.4. i8084W\_SetChannelMode

There are four operation modes in I-8048W. The function is used to set the operation mode of channel of I-8084W.

### **Syntax**

int i8084W\_SetChannelMode(int Slot, int Channel, int Mode)

#### Parameter and Return Values

Slot:

1~8

Channel:

0 ~ 7

#### Mode:

- 0 → Dir/Pulse Counter

- 1 → Up/Down Counter

- 2 → Frequency

- 3 → Up Counter

- 4 --> AB Phase

#### Return:

- $0 \rightarrow No error$

- 1 → The Pulse/Dir counter has one count offset (+1)

(due to the input channel is high)

## 3.5. i8084W\_AutoScan

Auto scan the I-8084W to updates 8 channels.

#### **Syntax**

int i8084W\_AutoScan(void)

#### Parameter and Return Values

#### Remark

This function is used to update the hardware counter values.

The hardware counter is 16-bit.

User's code must call the function or i8084W\_ReadCntPulseDir,

i8084W\_ReadCntUpDown, i8084W\_ReadFreq, i8084W\_ReadCntUp before the hardware counter is overflow.

Under very high speed signal input, for example: 450K Hz, the 16-bit counter is overflow round 145 ms.

To avoid the overflow situation, user's code is recommended to call i8084W\_AutoScan every 70 ms.

# 3.6. i8084W\_ReadCntABPhase

The function is used to read ABPhase counter.

### **Syntax**

int i8084W\_ReadCntABPhase(int Slot, int Channel,long \*Cnt32U,int \*Overflow)

## 3.7. i8084W\_ReadCntPulseDir

The function is used to Read Pulse/Dir Counter

### **Syntax**

int i8084W\_ReadCntPulseDir(int Slot, int Channel,long \*Cnt32U,int \*Overflow)

#### Parameter and Return Values

```

Slot:

1~8

Channel:

0 \sim 7

Cnt32L =

32-bit → UpDown Counter

Bit31= 0 \rightarrow Up Count (count > 0)

Bit31 = 1 \rightarrow Down Count (count < 0)

Overflow =

number of overflow

Total count =

over * 0 x 80000000 + count

Example A:

Over = 1, count = 16384,

total count = (1) * 0 x 80000000 + 16384 = 2147500032

Example B:

Over = -1, count = -8192,

total count = (-1)*0x80000000 -8192 = -2147491840

```

## 3.8. i8084W\_ReadCntUpDown

The function is used to Read UpDown Counter

#### **Syntax**

int i8084W\_ReadCntUpDown(int Slot, int Channel,long \*Cnt32U,int \*Overflow)

#### Parameter and Return Values

```

Slot:

1~8

Channel:

0 ~ 7

Cnt32L =

32-bit → UpDown Counter

Bit31= 0 \rightarrow Up Count (count > 0)

Bit31 = 1 \rightarrow Down Count (count < 0)

Overflow =

number of overflow

Total count

= over * 0 x 80000000 + count

Example A:

Over = 1, count = 16384,

total count = (1) * 0 x 80000000 + 16384 = 2147500032

Example B:

Over = -1, count = -8192,

total count = (-1)*0x80000000 -8192 = -2147491840

```

# 3.9. i8084W\_ReadFreq

The function is used to read frequency.

## **Syntax**

```

int i8084W_ReadFreq(int Slot, int Channel, unsigned long *Freq);

int i8084W_ReadFreq(int Slot, int Channel, float *Freq);

```

### Parameter and Return Values

Slot:

1~8

Channel:

0 ~ 7

Freq:

Unit = Hz

## 3.10. i8084W\_ReadCntUp

The function is used to Read Up Counter

### **Syntax**

```

int i8084W_ReadCntUp(int Slot, int Channel, unsigned long *Cnt32U, unsigned int *OverFlow)

```

#### Parameter and Return Values

```

Slot:

1~8

Channel:

0 ~ 7

Cnt32U =

32-bit Up Counter

Overflow =

number of Overflow

Total count =

over * 0x100000000 + count

ExampleA:

over=1 , count=16384,

total count = (1)*0x100000000 + 16384 = 4294983680

```

# 3.11. i8084W\_ClrCnt

Clear Counter

### **Syntax**

int i8084W\_ClrCnt(int Slot, int Channel)

### Parameter and Return Values

Slot:

1~8

Channel:

0 ~ 7

#### Return:

- 0 → No error

- $1 \rightarrow$  The Pulse/Dir counter has one count offset (+1).

It is due to the pulse channel is high.

The correct initial situation is:

Pulse channel is low or open

dir signal is high or low.

## 3.12. i8084W\_RecoverDefaultSetting

The function is used to recover default setting of I-8048W.

### **Syntax**

void i8084W\_RecoverDefaultSetting(int Slot)

#### Parameter and Return Values

Slot:

1~8

#### Remark

Default settings:

XOR register=0

Channel mode= 3 (Up counter mode)

Frequency operate mode = 0 (Auto mode)

Frequency update time: Auto mode = 330 ms

Low freq mode = 1000 ms

High freq mode = 100 ms

Low Pass Filter status = disable

Low Pass Filter signal width = 1 ms

# 3.13. i8084W\_ReadXorRegister

## **Syntax**

int i8084W\_ReadXorRegister(int Slot, int Channel, int \*XorReg)

#### Parameter and Return Values

Slot:

1~8

Channel:

0~7

#### XorReg:

0 → Low active (signal from High to Low, count changed)

1 → High acitve (signal from Low to High, count changed)

#### Return:

$0 \rightarrow OK$

Others → Error codes

## 3.14. i8084W\_SetXorRegister

## **Syntax**

int i8084W\_SetXorRegister(int Slot, int Channel, int XorReg)

#### Parameter and Return Values

Slot:

1~8

Channel:

0~7

#### XorReg:

- 0 → Low active (signal from High to Low, count count changed)

- 1 → High acitve (signal from Low to High, count changed)

#### Return:

- $0 \rightarrow No error$

- 1 → The Pulse/Dir counter has one count offset (+1)

(due to the input channel is high)

## 3.15. i8084W\_ReadChannelMode

## **Syntax**

int i8084W\_ReadChannelMode(int Slot, int Channel, int \*Mode)

#### Parameter and Return Values

Slot:

1~8

Channel:

0~7

#### Mode:

- 0 → Dir/Pulse Counter

- 1 → Up/Down Counter

- 2 → Frequency

- 3 → Up Counter

- 4 --> AB Phase

# 3.16. i8084W\_ReadLowPassFilter\_Us

| Read Low Pass Filter                                                      |

|---------------------------------------------------------------------------|

| <u>Syntax</u>                                                             |

| int i8084W_ReadLowPassFilter_Us(int Slot, int Channel, unsigned int *Us); |

| Danamatan and Datum Valuas                                                |

| Parameter and Return Values                                               |

| Slot:                                                                     |

| 1~8                                                                       |

| Channel:                                                                  |

|                                                                           |

| 0~7                                                                       |

| Us:                                                                       |

| 1~32767, pulse width, unit = 0.001 ms                                     |

|                                                                           |

# 3.17. i8084W\_SetLowPassFilter\_Us

Set Low Pass Filter

### **Syntax**

int i8084W\_SetLowPassFilter\_Us(int Slot, int Channel, unsigned int Us)

### Parameter and Return Values

Slot:

1~8

Channel:

0~7

Us:

1~32767, pulse width, unit = micro second

# 3.18. i8084W\_ReadLowPassFilter\_Status

### **Syntax**

void i8084W\_ReadLowPassFilter\_Status(int Slot,int Channel,int \*Status);

### Parameter and Return Values

Slot:

1~8

Channel:

0~7

Status:

0 = disable

1 = enable

# 3.19. i8084W\_SetLowPassFilter\_Status

### **Syntax**

void i8084W\_SetLowPassFilter\_Status(int Slot,int Channel,int Status);

### Parameter and Return Values

Slot:

1~8

Channel:

0~7

Status:

0 = disable

1 = enable

# 3.20. i8084W\_ReadFreqMode

### **Syntax**

void i8084W\_ReadFreqMode(int Slot, int Channel, int \*Mode);

### Parameter and Return Values

Slot:

1~8

Channel:

0~7

\*Mode:

0 = Auto

1 = Low Frequency

2 = High Frequency

# 3.21. i8084W\_SetFreqMode

### **Syntax**

void i8084W\_SetFreqMode(int Slot, int Channel, int Mode);

### Parameter and Return Values

Slot:

1~8

Channel:

0~7

\*Mode:

0 = Auto

1 = Low Frequency

2 = High Frequency

## 3.22. i8084W\_ReadFreqUpdateTime

Reads the update time used by frequency measurement algorithm

### **Syntax**

```

void i8084W_ReadFreqUpdateTime(int Slot, int *AutoMode_UpdateTime ,

int *LowMode_UpdateTime, int *HighMode_UpdateTime);

```

#### Parameter and Return Values

Slot:

1~8

AutoMode\_UpdateTime = time period for Auto mode, unit: ms

LowMode\_UpdateTime = time period for Low Frequency mode, unit: ms

LowMode\_UpdateTime = time period for High Frequency mode, unit: ms

## 3.23. i8084W\_SetFreqUpdateTime

Sets the update time used by frequency measurement algorithm

### **Syntax**

int i8084W\_SetFreqUpdateTime(int Slot, int AutoMode\_UpdateTime, int

LowMode\_UpdateTime, int HighMode\_UpdateTime);

#### Parameter and Return Values

Slot:

1~8

AutoMode\_UpdateTime =

time period for Auto mode, unit: ms

LowMode\_UpdateTime =

time period for Low Frequency mode, unit: ms

LowMode\_UpdateTime =

time period for High Frequency mode, unit: ms

# 3.24. i8084W\_ReadDI\_Xor

### **Syntax**

int i8084W\_ReadDI\_Xor(int Slot, int \*DI);

### Parameter and Return Values

#### Slot:

1~8

\*DI: Bit0 = DI of A0 after XorControl

\*DI: Bit1 = DI of B0 after XorControl

. . .

\*DI: Bit7 = DI of B3 after XorControl

#### Return:

$0 \rightarrow OK$

<> 0 → Error codes

### **Syntax**

int i8084W\_ReadDI\_XorLPF(int Slot, int \*DI);

### Parameter and Return Values

#### Slot:

1~8

\*DI: Bit0 = DI of A0 after XorControl & Low Pass Filter

\*DI: Bit1 = DI of B0 after XorControl & Low Pass Filter

. . .

\*DI: Bit7 = DI of B3 after XorControl & Low Pass Filter

#### Return:

$0 \rightarrow OK$

<> 0 → Error codes

# 3.26. i8084W\_EepWriteEnable

Write\_Enable EEPROM

### **Syntax**

int i8084W\_EepWriteEnable(int Slot);

### Parameter and Return Values

Slot:

1~8

Return:

$0 \rightarrow OK$

Others → Error codes

# 3.27. i8084W\_EepWriteDisable

Write\_Disable EEPROM

## **Syntax**

int i8084W\_EepWriteDisable(int Slot);

### Parameter and Return Values

Slot:

1~8

Return:

$0 \rightarrow OK$

Others → Error codes

# 3.28. i8084W\_EepWriteWord

Write 16-bit data to EEP

### **Syntax**

int i8084W\_EepWriteWord(int Slot, int Addr, int Value);

### Parameter and Return Values

Slot:

1~8

Addr:

0~39 for users

40~63 for 8084 configuration

Value = two bytes integer

Return:

$0 \rightarrow OK$

-1 → Address error

# 3.29. i8084W\_EepReadWord

Read 16-bit data to EEP

#### **Syntax**

int i8084W\_EepReadWord(int Slot, int Addr, int \*Value);

### Parameter and Return Values

Slot:

1~8

Addr:

0~39 for users

40~63 for 8084 configuration

Value = two bytes integer

Return:

$0 \rightarrow OK$

-1 → Address error