# **iMPACT User Guide**

"Xilinx" and the Xilinx logo shown above are registered trademarks of Xilinx, Inc. Any rights not expressly granted herein are reserved.

CoolRunner, RocketChips, RocketIP, Spartan, StateBENCH, StateCAD, Virtex, XACT, XC2064, XC3090, XC4005, and XC5210 are registered trademarks of Xilinx, Inc.

The shadow X shown above is a trademark of Xilinx, Inc.

ACE Controller, ACE Flash, A.K.A. Speed, Alliance Series, AllianceCORE, Bencher, ChipScope, Configurable Logic Cell, CORE Generator, CoreLINX, Dual Block, EZTag, Fast CLK, Fast CONNECT, Fast FLASH, FastMap, Fast Zero Power, Foundation, Gigabit Speeds...and Beyond!, HardWire, HDL Bencher, IRL, J Drive, JBits, LCA, LogiBLOX, Logic Cell, LogicORE, LogicProfessor, MicroBlaze, MicroVia, MultiLINX, NanoBlaze, PicoBlaze, PLUSASM, PowerGuide, PowerMaze, QPro, Real-PCI, Rocket I/O, SelectI/O, SelectRAM, SelectRAM+, Silicon Xpresso, Smartguide, Smart-IP, SmartSearch, SMARTswitch, System ACE, Testbench In A Minute, TrueMap, UIM, VectorMaze, VersaBlock, VersaRing, Virtex-II Pro, Wave Table, WebFITTER, WebPACK, WebPOWERED, XABEL, XACT-Floorplanner, XACT-Performance, XACTstep Advanced, XACTstep Foundry, XAM, XAPP, X-BLOX +, XC designated products, XChecker, XDM, XEPLD, Xilinx Foundation Series, Xilinx XDTV, Xinfo, XSI, XtremeDSP, and ZERO+ are trademarks of Xilinx, Inc.

The Programmable Logic Company is a service mark of Xilinx, Inc.

All other trademarks are the property of their respective owners.

Xilinx, Inc. does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx, Inc. reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, Inc. will not assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx provides any design, code, or information shown or described herein "as is." By providing the design, code, or information as one possible implementation of a feature, application, or standard, Xilinx makes no representation that such implementation is free from any claims of infringement. You are responsible for obtaining any rights you may require for your implementation. Xilinx expressly disclaims any warranty whatsoever with respect to the adequacy of any such implementation, including but not limited to any warranties or representations that the implementation is free from claims of infringement, as well as any implied warranties of merchantability or fitness for a particular purpose. Xilinx, Inc. devices and products are protected under U.S. Patents. Other U.S. and foreign patents pending. Xilinx, Inc. does not represent that devices shown or products described herein are free from patent infringement or from any other third party right. Xilinx, Inc. assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx, Inc. will not assume any liability for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

The contents of this manual are owned and copyrighted by Xilinx. © Copyright 1994-2002 Xilinx, Inc. All Rights Reserved. Except as stated herein, none of the material may be copied, reproduced, distributed, republished, downloaded, displayed, posted, or transmitted in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording or otherwise, without the prior written consent of Xilinx. Any unauthorized use of any material contained in this manual may violate copyright laws, trademark laws, the laws of privacy and publicity, and communications regulations and statues.

# About This Manual

This guide describes the iMPACT configuration tool, a command line and GUI based tool that enables you to configure your PLD designs using Boundary-Scan, Slave Serial, and SelectMAP configuration modes, as well as the MultiPRO Desktop Programmer. You can also generate programming files using iMPACT's System ACE, PROM Formatter, SVF, and STAPL file generation modes.

# **Manual Contents**

This book contains the following chapters.

- "Introduction"

- "Cables"

- "Designing Boundary-Scan and ISP Systems"

- "Using iMPACT to Configure Devices"

- "Using iMPACT to Generate Files"

- "Troubleshooting for Boundary-Scan Chains"

- "Glossary of Terms"

- "Boundary-Scan Basics" appendix

- "Parallel Cable III (DLC 5) Schematic" appendix

- "Command Line and Batch Mode Commands" appendix

# **Additional Resources**

For additional information, go to <u>http://support.xilinx.com</u>. The following table lists some of the resources you can access from this Web site. You can also directly access these resources using the provided URLs.

| Resource             | Description/URL                                                                                                                                                                                                                                                                  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tutorials            | Tutorials covering Xilinx design flows, from design entry to verification<br>and debugging<br>http://support.xilinx.com/support/techsup/tutorials/index.htm                                                                                                                      |

| Answers<br>Database  | Current listing of solution records for the Xilinx software tools<br>Search this database using the search function at<br>http://support.xilinx.com/support/searchtd.htm                                                                                                         |

| Application<br>Notes | Descriptions of device-specific design techniques and approaches<br>http://support.xilinx.com/apps/appsweb.htm                                                                                                                                                                   |

| Data Book            | Pages from <i>The Programmable Logic Data Book</i> , which contains device-<br>specific information on Xilinx device characteristics, including readback,<br>Boundary-Scan, configuration, length count, and debugging<br><u>http://support.xilinx.com/partinfo/databook.htm</u> |

| Xcell Journals       | Quarterly journals for Xilinx programmable logic users<br>http://support.xilinx.com/xcell/xcell.htm                                                                                                                                                                              |

| Technical Tips       | Latest news, design tips, and patch information for the Xilinx design<br>environment<br>http://support.xilinx.com/support/techsup/journals/index.htm                                                                                                                             |

# Conventions

This manual uses the following conventions. An example illustrates most conventions.

# Typographical

The following conventions are used for all documents.

• Courier font indicates messages, prompts, and program files that the system displays.

speed grade: - 100

• Courier bold indicates literal commands that you enter in a syntactical statement. However, braces "{}" in Courier bold are not literal and square brackets "[]" in Courier bold are literal only in the case of bus specifications, such as bus [7:0].

rpt\_del\_net=

**Courier bold** also indicates commands that you select from a menu.

$\texttt{File} \ \rightarrow \texttt{Open}$

- *Italic font* denotes the following items.

- Variables in a syntax statement for which you must supply values

edif2ngd design\_name

• References to other manuals

See the *Development System Reference Guide* for more information.

• Emphasis in text

If a wire is drawn so that it overlaps the pin of a symbol, the two nets are *not* connected.

• Square brackets "[]" indicate an optional entry or parameter. However, in bus specifications, such as bus [7:0], they are required.

```

edif2ngd [option_name] design_name

```

• Braces "{}" enclose a list of items from which you must choose one or more.

```

lowpwr ={on|off}

```

• A vertical bar " | " separates items in a list of choices.

lowpwr ={on|off}

• A vertical ellipsis indicates repetitive material that has been omitted.

```

IOB #1: Name = QOUT'

IOB #2: Name = CLKIN'

.

.

```

• A horizontal ellipsis "..." indicates that an item can be repeated one or more times.

allow block block\_name loc1 loc2 ... locn;

# **Online Document**

The following conventions are used for online documents.

- Blue text indicates cross-references within a book. Red text indicates cross-references to other books. Click the colored text to jump to the specified cross-reference.

- <u>Blue, underlined text</u> indicates a Web site. Click the link to open the specified Web site. You must have a Web browser and internet connection to use this feature.

# Contents

### **About This Manual**

| Manual Contents | <br>iii |

|-----------------|---------|

|                 |         |

#### Conventions

| Typographical   | V  |

|-----------------|----|

| Online Document | vi |

### Chapter 1 Introduction

| Configuration Device Operations Available to Users |   |

|----------------------------------------------------|---|

| Non-Volatile Device Data Security                  |   |

| Required Files                                     |   |

| JEDEC Files                                        |   |

| BSDL Summary1-3                                    |   |

| BIT Files1-3                                       |   |

| PROM Files1-4                                      |   |

| RBT Files1-4                                       |   |

| Chain Description Files1-4                         |   |

| iMPACT Features1-4                                 |   |

| User Feedback1-5                                   |   |

| PROM Formatter1-5                                  |   |

| Serial PROMs1-5                                    |   |

| Parallel PROMs1-6                                  |   |

| System ACE1-6                                      |   |

| MultiPRO Desktop Programmer (MultiPRO)1-6          |   |

| iMPACT Platform Support                            |   |

| Starting iMPACT1-7                                 |   |

| From Project Navigator1-7                          |   |

| From the Command Line1-7                           |   |

| Exiting iMPACT                                     |   |

| Using the Interface                                |   |

| Main Window                                        |   |

| Title Bar1-7                                       |   |

| Menu Bar1-8                                        |   |

|                                                    |   |

| Toolbar                                            | h |

| Status Window1-10                                  | J |

|           | Commands and Dialog Boxes<br>Common Fields                                  | 1-10              |

|-----------|-----------------------------------------------------------------------------|-------------------|

|           | Selection Dialog Boxes                                                      | 1-11              |

|           | Selecting Commands and Dialog Box Options                                   | 1-11              |

|           | Using the Mouse                                                             | 1-11              |

|           | Using the Keyboard                                                          | 1-12              |

|           | Using Help                                                                  | 1-12              |

|           | Help Menu                                                                   | 1-12              |

|           | Toolbar Help Button                                                         |                   |

|           | F1 Key                                                                      |                   |

|           | Help Button in Dialog Boxes                                                 | 1-13              |

|           | Architecture Support                                                        | 1-13              |

| Chapter 2 | Cables                                                                      |                   |

|           | Download Cables                                                             | 2_1               |

|           | Cable Support                                                               |                   |

|           | Cable Baud Rates                                                            | <u>2-2</u><br>2-2 |

|           | Software and Cable Interface                                                |                   |

|           | Cable Auto Connect (Automatic)                                              | 2-3               |

|           | Cable Setup (Manual)                                                        | 2-3               |

|           | Resetting the Cable                                                         | 2-5               |

|           | Disconnecting the Cable                                                     |                   |

|           | Target Board Requirements                                                   | 2-5               |

|           | High Performance Ribbon Cable                                               | 2-5               |

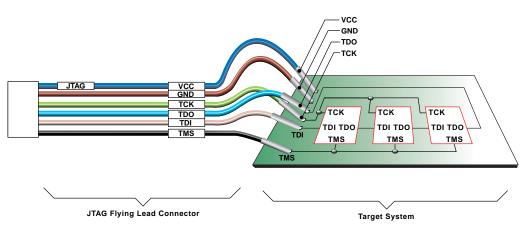

|           | Flying Lead Connectors                                                      | 2-6               |

|           | Flving Leads                                                                | 2-6               |

|           | Mode Pin Connections for FPGAs Only                                         | 2-6               |

|           | Parallel Cables                                                             | 2-7               |

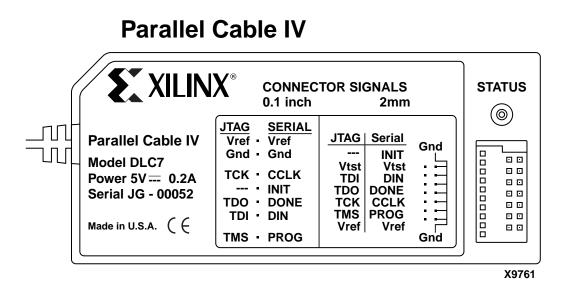

|           | Parallel Cable IV                                                           | 2-7               |

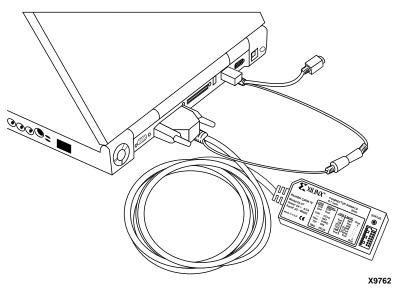

|           | Connecting to Host Computer                                                 |                   |

|           | Cable Power                                                                 | 2-8               |

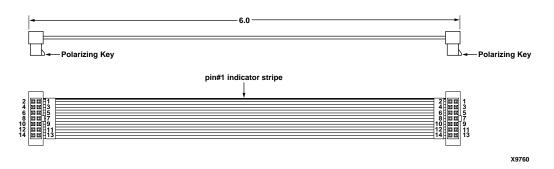

|           | High Performance Ribbon Cable                                               | 2-9               |

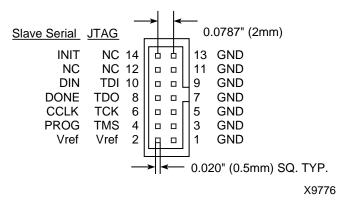

|           | Target Board Header                                                         |                   |

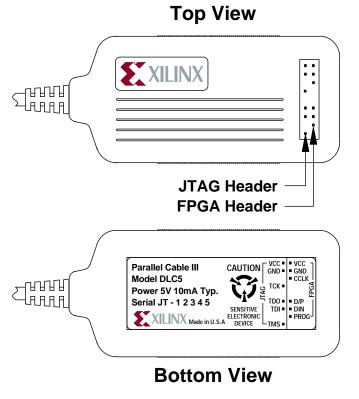

|           | Parallel Cable III                                                          | 2-12              |

|           | Connecting for System Operation                                             | 2-13              |

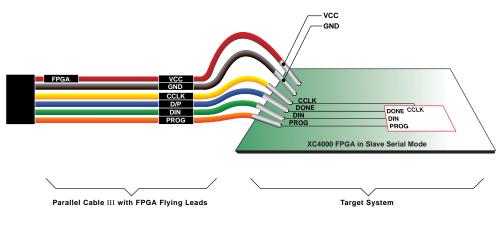

|           | Serial Configuration Connection                                             |                   |

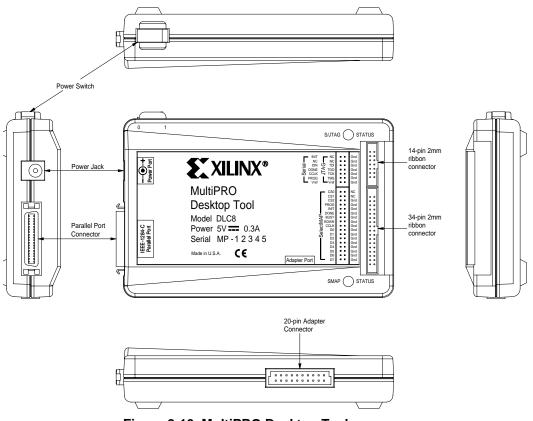

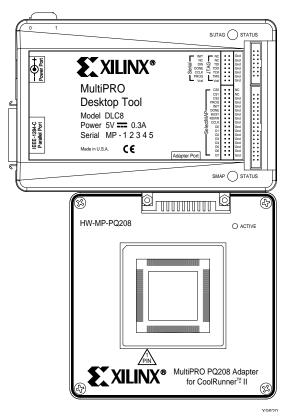

|           | MultiPRO Desktop Tool                                                       | 2-17              |

|           | Connecting to Host Computer                                                 |                   |

|           | Cable Power                                                                 | 2-19              |

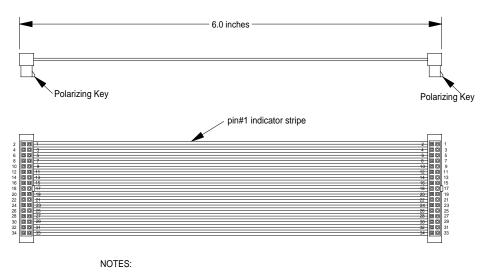

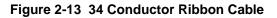

|           | High Performance Ribbon Cables                                              | 2-19              |

|           | Desktop Programming                                                         |                   |

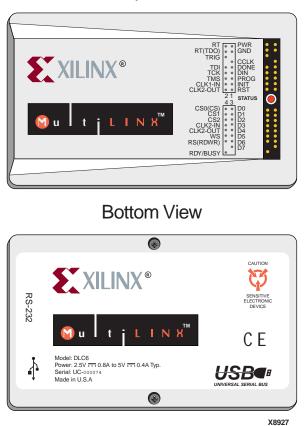

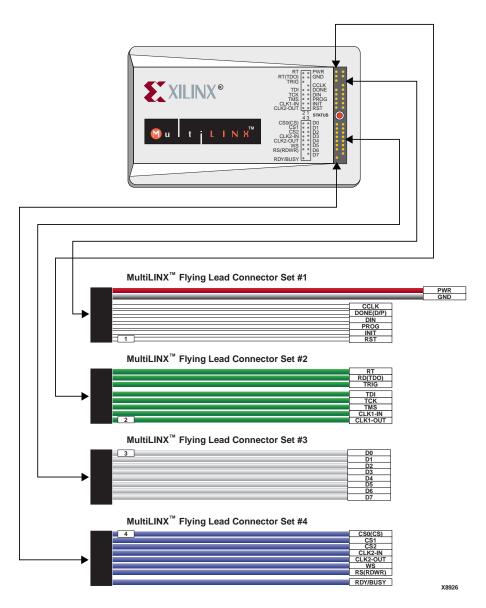

|           | MultiLINX Cable                                                             |                   |

|           | MultiLINX Power Requirements                                                | Z-ZO              |

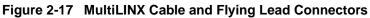

|           | MultiLINX Cable and Flying Leads<br>MultiLINX Connection and Power Sequence | <u>2</u> -20      |

|           | Connecting Cable to Target System                                           |                   |

|           |                                                                             | 2-30              |

| Chapter 3 | Designing Boundary-Scan and ISP Systems                                     |                   |

#### Connecting Devices in a Boundary-Scan Chain ......3-1

|                                                                                                      | ~ ~  | <b>`</b> |

|------------------------------------------------------------------------------------------------------|------|----------|

| FPGA Device Considerations                                                                           |      |          |

| Bitstream Considerations                                                                             |      |          |

| Virtex Considerations                                                                                |      |          |

| Device Behavior Notes                                                                                |      |          |

| Selecting a Configuration Mode                                                                       | 3-4  | 1        |

| FPGA Supported Modes                                                                                 | 3-5  | 5        |

| FPGĂ Supported Modes<br>JTAG or Boundary-Scan Mode                                                   | 3-5  | 5        |

| SelectMAP/Slave-Parallel Modes                                                                       | 3-5  | 5        |

| Master SelectMAP Mode                                                                                | 3-5  | 5        |

| Master-Serial Mode                                                                                   |      |          |

| Slave-Serial Mode                                                                                    |      |          |

| CPLD/PROM Supported Modes                                                                            | 3_6  | 2        |

| Standalone Programmer Mode                                                                           | 2 0  | 5        |

| JTAG or Boundary-Scan Mode                                                                           |      | 5        |

| Dragromming and Configuring Ontiona                                                                  |      | 2        |

| Programming and Configuring Options                                                                  |      | 2        |

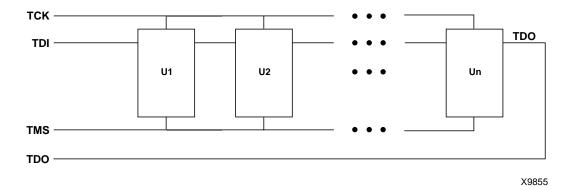

| CPLD Programming Options                                                                             |      | 2        |

| ATE/Embedded Solutions                                                                               | 3-1  | <u>_</u> |

| MultiPRO Desktop Programmer                                                                          | 3-1  | (        |

| Third Party Programmers                                                                              | 3-8  | 3        |

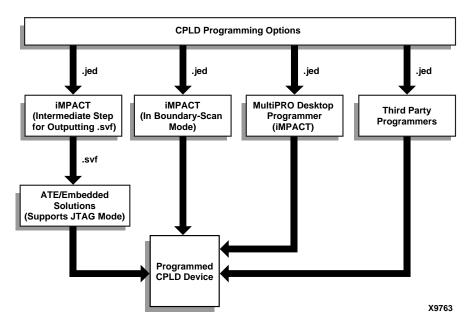

| FPGA Configuration Flows                                                                             | 3-8  | 3        |

| Third Party Programmers<br>FPGA Configuration Flows<br>Embedded Solutions                            | 3-8  | 3        |

| PROM                                                                                                 | 3-9  | 9        |

| PROMGen/PROM Formatter                                                                               | 3-9  | 9        |

| Third Party Programmers<br>Xilinx Common Configuring and Programming Setups<br>CPLD JTAG Chain Setup | 3-1  | 10       |

| Xilinx Common Configuring and Programming Setups                                                     | 3-1  | 10       |

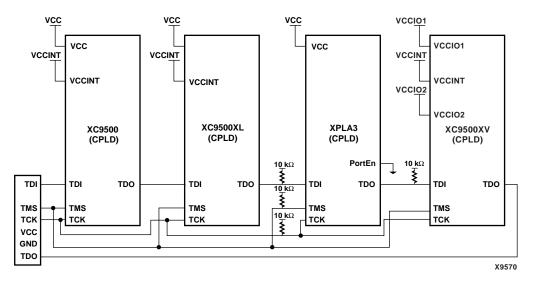

| CPLD JTAG Chain Setup                                                                                | 3-1  | 10       |

| Hardware Considerations                                                                              |      | 11       |

| General JTAG Checklist                                                                               |      |          |

| XC9500/XL/XV Specific Checklist                                                                      | 3-1  | 12       |

| XPLA3 Specific Checklist                                                                             | 3-1  | 13       |

| XPLA3 Specific Checklist                                                                             | o    | 13       |

| Software Download Considerations                                                                     |      | 13       |

| Prototyping Environment                                                                              | J-   | 14       |

| Prototyping Environment<br>Production Environment                                                    |      | 14       |

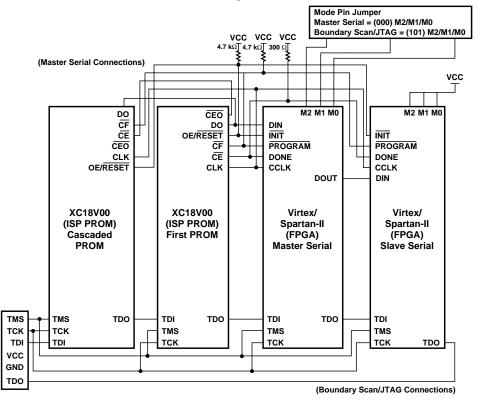

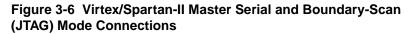

| Virtex Series or Spartan-II Master Serial and Boundary-Scan (JT                                      |      | Com      |

| bination Setup                                                                                       | ۲G)  |          |

| bination Setup                                                                                       |      | 14       |

| Hardware Considerations                                                                              |      | 10       |

| Virtex Spartan-II Master Serial and Boundary-Scan (JTAG) M                                           | loge | Con-     |

| nections                                                                                             | 3-1  | 16       |

| Software Implementation Considerations                                                               | 3-1  | 17       |

| Software Download Considerations                                                                     | 3-1  | 18       |

| Prototyping                                                                                          | 3-1  | 18       |

| Production                                                                                           | 3-1  | 18       |

| Configuration Checklist                                                                              | 3-1  | 18       |

|                                                                                                      |      |          |

# Chapter 4 Using iMPACT to Configure Devices

| Configuration Mode General Informa | ation4-1 |

|------------------------------------|----------|

| Connecting to a Cable              | 4-3      |

| Boundary-Scan Configuration Mode   |          |

| Automatically Creating the Chain                 | 4-5  |

|--------------------------------------------------|------|

| Manually Creating the Chain                      |      |

| Assigning Configuration Files                    | 4-7  |

| Saving the Chain Description                     | 4-9  |

| Edit Preferences                                 | 4-10 |

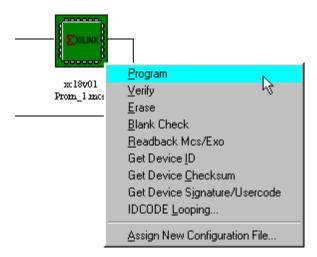

| Available Boundary-Scan Operations               | 4-11 |

| Performing Boundary-Scan Operations              | 4-12 |

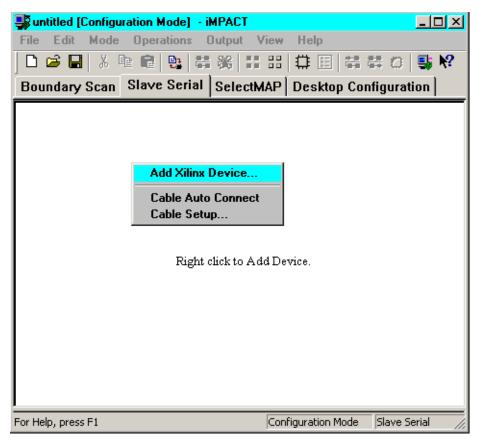

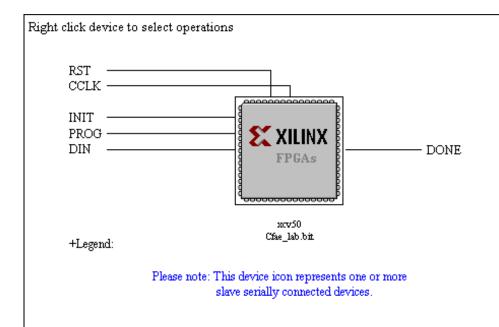

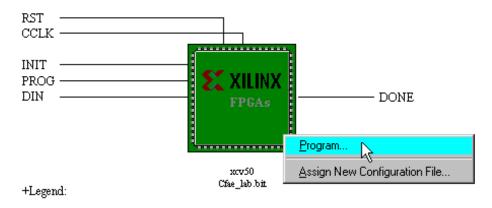

| Slave Serial Configuration Mode                  | 4-15 |

| Adding a Device                                  | 4-15 |

| Programming the Device                           | 4-18 |

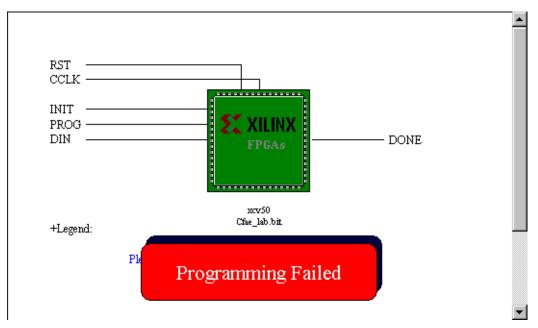

| Troubleshooting Slave Serial Configuration       | 4-19 |

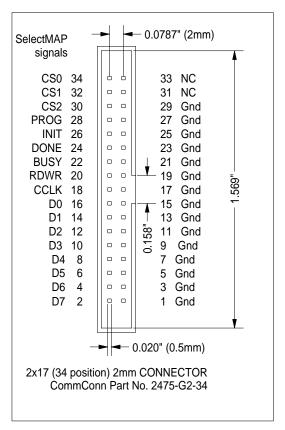

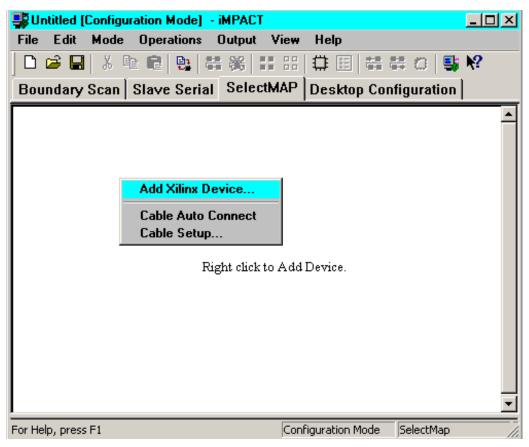

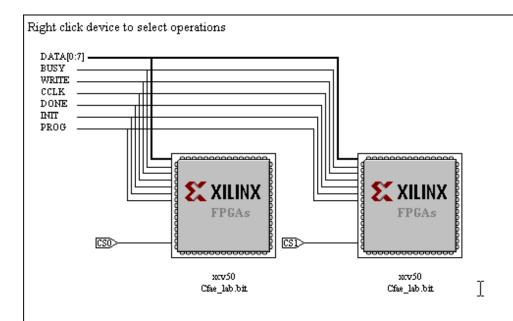

| SelectMAP Configuration Mode                     | 4-21 |

| Adding a Device                                  | 4-21 |

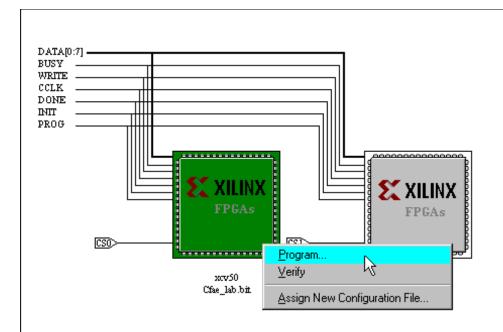

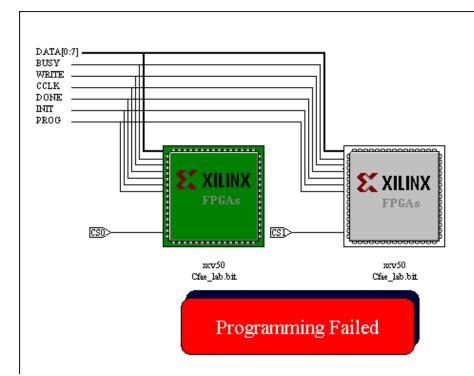

| Programming and Verifying a Device               | 4-24 |

| Troubleshooting SelectMAP Programming and Verify |      |

| Desktop Configuration Mode                       |      |

| Automatically Identifying the Device             |      |

| Manually Identifying the Device                  |      |

| Assigning a Configuration File                   | 4-28 |

| Setting Options                                  | 4-28 |

| Performing Device Operations                     | 4-30 |

|                                                  |      |

### Chapter 5 Using iMPACT to Generate Files

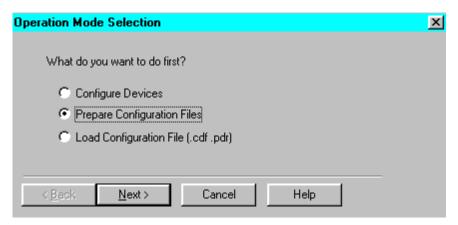

| General File Mode Instructions                                                         | 5-2        |

|----------------------------------------------------------------------------------------|------------|

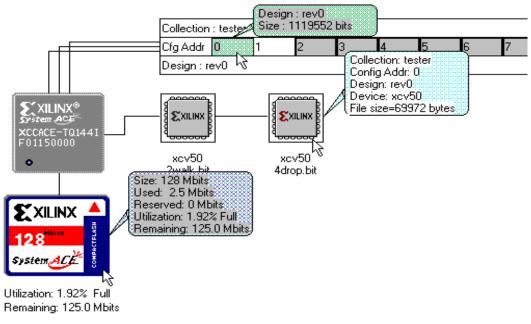

| Creating System ACE Programming Files                                                  | 5-3        |

| System ACE CF Settings                                                                 | 5-4        |

| Size                                                                                   | 5-4        |

| Reserve Space                                                                          | 5-4        |

| System ACE CF Collection Name                                                          | 5-4        |

| Location                                                                               | 5-4        |

| Configuration Address                                                                  | 5-4        |

| Design Name                                                                            | 5-5        |

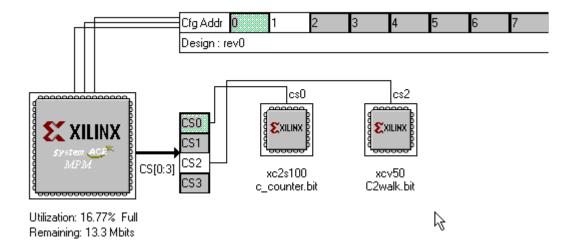

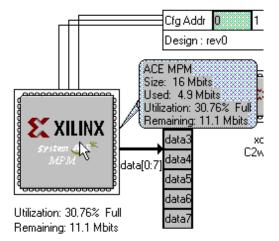

| System ACE MPM Settings                                                                | 5-5        |

| Size (16,32,64, Generic)                                                               | 5-5        |

| System ACE MPM Name                                                                    | 5-5        |

| Location                                                                               | 5-5        |

| Target in: Slave Serial Mode or SelectMAP Mode<br>Slave Serial Mode > Number Of Chains | 5-5        |

| Slave Serial Mode > Number Of Chains                                                   | 5-5        |

| SelectMAP Mode > Specify CS Pin to be used in this                                     | design 5-6 |

| Configuration Address                                                                  |            |

| File Generation > Compress File                                                        | 5-6        |

| Adding Files to System ACE Devices                                                     |            |

| System ACE CF                                                                          | 5-7        |

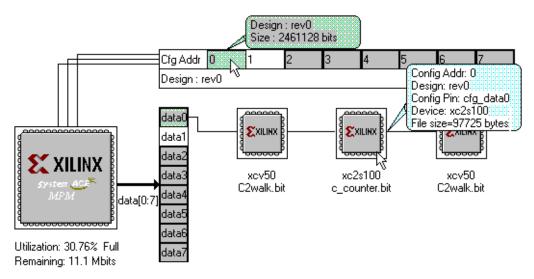

| System ACE CF Screen                                                                   | 5-7        |

| Viewing Different Configuration Addresses                                              | 5-9        |

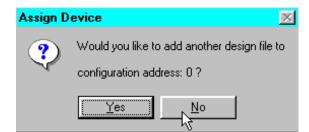

| Adding More Devices After the Wizard Has Finished .                                    | 5-9        |

| Assigning a Different File to a Device                                                 | 5-9        |

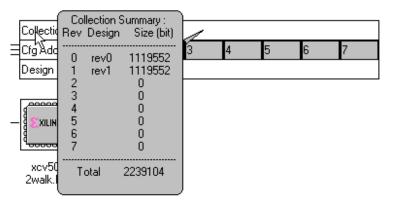

| Managing Multiple Collections                                                          | 5-9        |

| Generating System ACE CF Files                                                         |            |

|                                                                                        |            |

| System ACE MPM                                      | 5-11 |

|-----------------------------------------------------|------|

| System ACE MPM Screen                               | 5-11 |

| Viewing Different Configuration Addresses           | 5-14 |

| Adding More Devices After the Wizard Has Finished . | 5-14 |

| Assigning a Different File to a Device              | 5-14 |

| Generating System ACE MPM Files                     |      |

| Creating PROM Formatter Programming Files           | 5-16 |

| General PROM File Information                       | 5-16 |

| PROMs                                               | 5-16 |

| PROM Formatter Files                                | 5-16 |

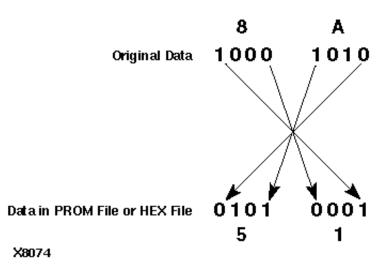

| BIT Swapping in PROM Files                          | 5-17 |

| Implementing Your Applications                      | 5-18 |

| Single Application PROM Files                       | 5-19 |

| Multiple Application PROM Files                     | 5-19 |

| Configuration Setups                                | 5-20 |

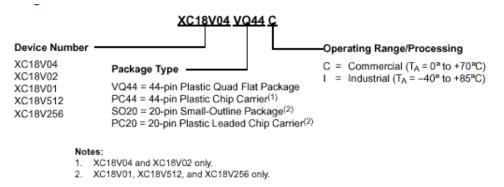

| XILINX PROM Part Names                              | 5-20 |

| PROM Formatter Operations                           | 5-20 |

| Serial PROM Settings                                | 5-20 |

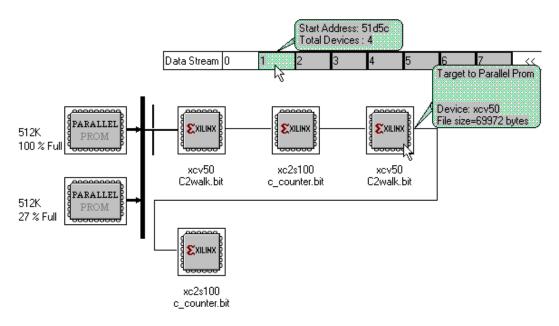

| Parallel PROM Settings                              |      |

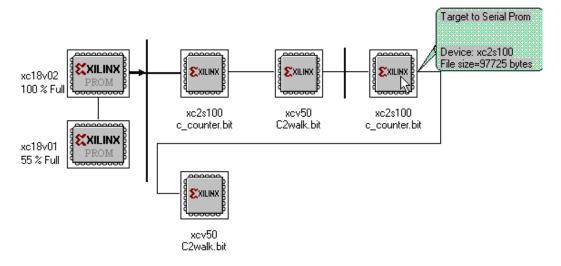

| Adding Files to PROM Devices                        | 5-22 |

| Generating PROM Files                               | 5-23 |

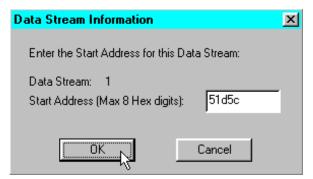

| Serial PROM File Creation                           | 5-23 |

| Parallel PROM File Creation                         | 5-25 |

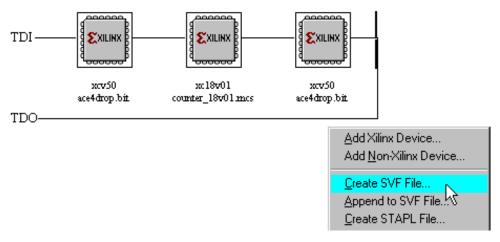

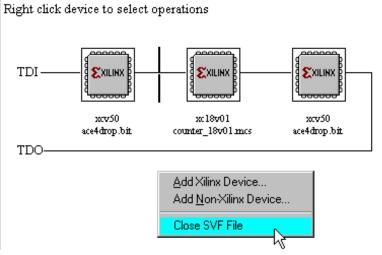

| Creating an SVF or STAPL File                       | 5-27 |

| Creating the chain                                  | 5-27 |

| Selecting the Programming File                      | 5-27 |

| Writing to an SVF or STAPL File                     | 5-28 |

### Chapter 6 Troubleshooting for Boundary-Scan Chains

| Communication             | 6-1 |

|---------------------------|-----|

| Improper Connections      | 6-2 |

| Improper or Unstable Vcc  | 6-3 |

| Boundary-Scan Chain Debug | 6-3 |

| System Noise              | 6-5 |

#### **Glossary of Terms**

# Appendix A Boundary-Scan Basics

| Boundary-Scan/IEEE Standard 1149.1   | A-1 |

|--------------------------------------|-----|

| What can it be used for?             | A-1 |

| How does it work?                    | A-2 |

| The TAP Controller                   | A-2 |

| The Instruction Register             | A-2 |

| The Data Registers                   |     |

| Impact Test Access Port              | A-2 |

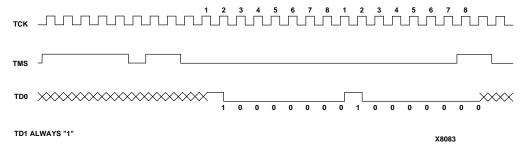

| JTAG TAP Controller                  | A-3 |

| JTAG TAP Controller States           | A-3 |

| Mandatory Boundary-Scan Instructions | A-5 |

| Optional Boundary-Scan Instructions  | A-5 |

|                                      |     |

|            | Configuring the Parallel Download Cable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | .A-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

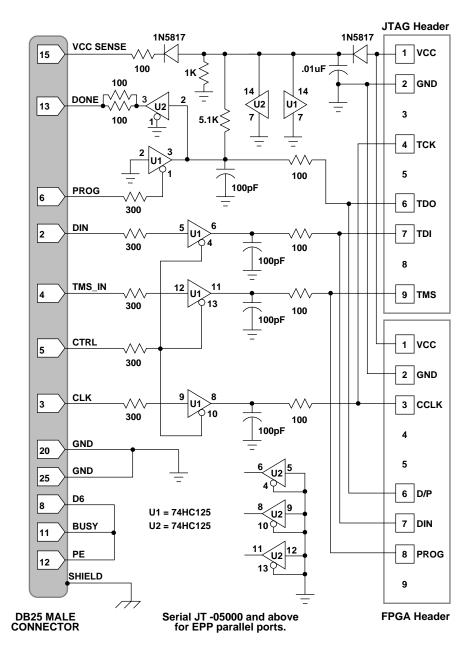

| Appendix B | Parallel Cable III (DLC 5) Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Appendix C | Command Line and Batch Mode Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|            | Difference Between Command Line and Batch Mode Operation<br>Command Line Options<br>Batch Mode Commands<br>Batch Mode Definitions<br>General Configuration Mode Commands<br>Boundary-Scan Mode Specific Commands<br>Boundary-Scan Mode Specific Commands<br>File Generation Mode Commands<br>PROM Formatter Specific Commands<br>System ACE Specific Commands<br>Example Batch Mode Command Sequences<br>General Batch Command Sequences<br>General Batch Command Sequences<br>General Batch Command Sequences<br>Command Sequence Example 1: Creating a Chain Using<br>vice<br>Command Sequence Example 2: Chain Consisting of: XC<br>(programmed), Third Party Device (bypassed) XC18v04 (p<br>grammed), XC18v04 (bypassed with host file)<br>Command Sequence Example 3: Using JTAG to Automati<br>Identify a Chain<br>Command Sequence Example 3: Using JTAG to Automati<br>Identify a Chain<br>Command Sequence Example 4: Loading a .cdf File and F<br>ming a Device<br>JTAGPROG to iMPACT Script Migration<br>Getting Started<br>Determining the Part Name<br>Programming and Verifying a Device<br>JTAGPROG<br>iMPACT (XC18V00 Family)<br>iMPACT (XC18V00 Family)<br>iMPACT (SVF mode)<br>Example: C2V1000 Device (bypassed with a .bit file) in a Ch<br>an XC18v04 Device (programmed) in a Chain with a XC18v07<br>passed with a BSDL file)<br>Example: XC2v1000 (programmed) in a Chain with a XC18v07<br>passed with a BSDL file)<br>Example: XC2v1000 (programmed) in a Chain with a XC18v07<br>passed with a BSDL file)<br>Example: XC2v1000 (programmed) in a Chain with a XC18v07<br>passed with a BSDL file)<br>Example: XC2v1000 (programmed) in a Chain with a XC18v07<br>passed with a BSDL file)<br>Example: XC2v1000 (programmed) in a Chain with a XC18v07<br>passed with a BSDL file)<br>Example: XC2v1000 (programmed) in a Chain with a XC18v07<br>passed with a BSDL file)<br>JTAGPROG<br>iMPACT<br>iMPACT (SVF mode)<br>Example: Chain Consisting of XC18v04 (programmed), Third F | .C-2<br>.C-2<br>.C-3<br>.C-4<br>.C-5<br>.C-6<br>.C-6<br>.C-7<br>.C-10<br>.C-10<br>.C-10<br>.C-11<br>.C-11<br>.C-13<br>.C-14<br>.C-14<br>.C-14<br>.C-14<br>.C-15<br>.C-16<br>.C-17<br>.C-17<br>.C-17<br>.C-17<br>.C-18<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-17<br>.C-17<br>.C-17<br>.C-17<br>.C-17<br>.C-17<br>.C-18<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-11<br>.C-17<br>.C-17<br>.C-17<br>.C-17<br>.C-17<br>.C-17<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-11<br>.C-11<br>.C-11<br>.C-11<br>.C-15<br>.C-16<br>.C-17<br>.C-17<br>.C-17<br>.C-17<br>.C-17<br>.C-17<br>.C-17<br>.C-17<br>.C-17<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-11<br>.C-11<br>.C-14<br>.C-15<br>.C-16<br>.C-17<br>.C-17<br>.C-17<br>.C-17<br>.C-17<br>.C-17<br>.C-17<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C-19<br>.C |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| vice (bypassed), XC18v04 (programmed), XC18v04 ( | bypassed with a |

|--------------------------------------------------|-----------------|

| .bsd file)                                       | C-20            |

| JTAGPROG                                         | C-20            |

| MPACT                                            | Č-20            |

| iMPACT (SVF mode)                                |                 |

# **Chapter 1**

# Introduction

This chapter introduces you to the basic concepts of the iMPACT software and related Xilinx in-system programmable products. You can use iMPACT to download, read back and verify design configuration data as well as to create PROM, SVF, STAPL, System ACE CF and System ACE MPM programming files. This chapter contains the following sections:

- "Configuration Device Operations Available to Users"

- "Non-Volatile Device Data Security"

- "Required Files"

- "iMPACT Features"

- "iMPACT Platform Support"

- "Starting iMPACT"

- "Using the Interface"

- "Using Help"

- "Architecture Support"

# **Configuration Device Operations Available to Users**

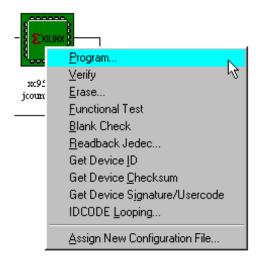

*Program.* Downloads the contents of the JEDEC, BIT or PROM file to the device.

*Verify.* Reads back the contents of the device configuration and compares them with the JEDEC, BIT or PROM file.

Erase. Clears device configuration information.

*Functional Test.* Applies user-specified functional vectors from the JEDEC file to the device using the JTAG INTEST instruction,

comparing results obtained against expected values. Reports any differences to the user.

*Blank Check.* Checks whether a device is in a programmed or erased state.

*Readback.* Reads back the contents of the device configuration and creates a new JEDEC or PROM file with the results.

*Program XPLA UES.* This is a Coolrunner only option. Programs the user electronic signature of the selected devices.

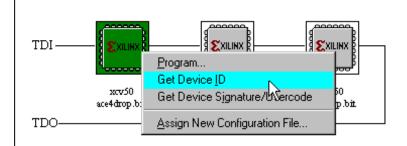

*Get Device ID.* Reads the contents of the JTAG IDCODE register. Displays contents for the user.

*Get Device Checksum.* Reads back the contents of device configuration registers and calculates a checksum for comparison against the expected value specified in the JEDEC or PROM file.

*Get Device Signature/Usercode.* For FPGAs and CPLDs this value is selected by the user during program file generation. The specified value is translated to binary values in the JEDEC file. During device programming these values are loaded into the JTAG USERCODE register. This function reads the contents of the USERCODE register and displays the result.

*Get XPLA Device UES.* This is a CoolRunner only option. Gets the user electronic signature from the selected devices in the JTAG chain.

*IDCODE Looping.* Performs IDCODE operations a specified number of times.

### Non-Volatile Device Data Security

Any Xilinx XC9500 family device selected for programming can be secured with the Write Protect or Read Protect or both. CoolRunner, CoolRunner-II, and PROM devices can be secured with the Read Protect only.

When enabled, Read Protect disables reading the programmed contents of a device (the IDCODE, USERCODE and all Boundary-Scan registers remain readable).

Write Protect enables only the reading of the programmed data. The device contents cannot be altered or re-programmed.

When both Read Protect and Write Protect are enabled, the device programmed data can be neither read nor re-programmed.

# **Required Files**

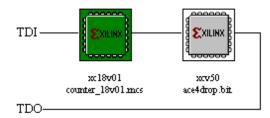

For Boundary-Scan programming, you need to provide JEDEC files for each CPLD family device, BIT files for each Xilinx FPGA device, .mcs or .exo files for each PROM device, and BSDL files for the remaining devices.

For Slave Serial programming, you must provide a single BITfile if there is only one FPGA, or an .mcs/.exo file for Serial daisy chains with multiple FPGAs.

For SelectMAP programming, you must provide a BITfile for each target device.

### **JEDEC Files**

JEDEC files are CPLD programming files generated by the Xilinx fitter. They are ASCII text files containing programming information that describes the desired functional implementation of the user's design. One JEDEC file is required for each CPLD device in the JTAG programming chain.

# **BSDL Summary**

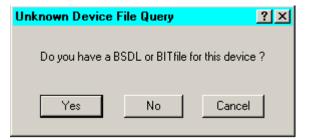

The Boundary-Scan Description Language (BSDL) files use a subset of VHDL to describe the Boundary-Scan features of a device. iMPACT automatically extracts the length of the instruction register from the BSDL file to place non-Xilinx devices in bypass mode. Xilinx BSDL files are located automatically by iMPACT.

# **BIT Files**

BIT files are Xilinx FPGA configuration files generated by the Xilinx FPGA design software. They are proprietary format binary files containing configuration information. One BIT file is required for each Xilinx FPGA in a Boundary-Scan chain, for a single Slave Serial connected device, or for each SelectMAP connected device.

### **PROM Files**

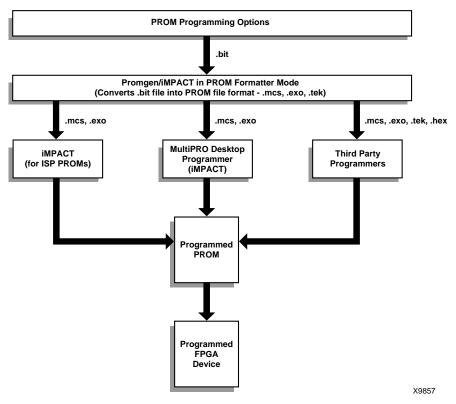

PROM files are PROM programming files generated either by iMPACT using the PROM Formatter tab in the File Generation mode, or by the command line utility, PROMGen. The PROM files are ASCII text files used to specify configuration data. PROM files are also used to download a serial daisy chain of multiple FPGAs.

A Xilinx PROM file may consist of one or more data streams. In this context, a data stream represents all the configuration data required to implement a given application. Each data stream contains one or more BIT files and once saved, has a separate preamble and length count.

The PROM file can be formatted in one of three industry standard formats: Intel MCS-86<sup>®</sup> (.mcs), Tektronix TEKHEX (.tek), and Motorola EXOR-macs (.exo).

The PROM Formatter performs the same function as the PROMGen program, which can be executed from the UNIX<sup>™</sup> or PC command line. Refer to the *Development System Reference Guide* for details about PROMGen.

### **RBT Files**

A Raw BIT File is an ASCII version of the BIT file. The only difference is that the header information in a BIT File is removed from the Raw BIT File. This is also created by BitGen and is used to program a single FPGA.

# **Chain Description Files**

A Chain Description file is used to save and restore information about the composition of device configuration chains. It stores information about the order of devices in the chain and the configuration data file associated with each device.

# **iMPACT** Features

You can use iMPACT to perform the following functions.

- Configure one or more devices

- Verify configuration data for single devices

• Create PROM, SVF, STAPL, System ACE CF, and System ACE MPM programming files.

For downloading, use any of the three configuration data file types (BIT, JEDEC, or PROM) and any download cable.

For single device verification of Xilinx FPGAs, use a BIT file. In addition, you will need to generate a MSK file. Be certain to include the readback symbol in your design and optionally, the STARTUP symbol. Verification ensures that a device's configuration memory contents match the source configuration file contents. It does not ensure the device has started up and is functioning. Only actual system verification can verify start up and overall function.

# **User Feedback**

When using the graphical user interface, immediate feedback is provided by a scrolling log file and alert boxes. Detailed information regarding operation history and status is displayed in the status window and collected in the iMPACT log file.

# **PROM Formatter**

The PROM Formatter tab enables you to format BIT files into a PROM file compatible with Xilinx and third-party PROM programmers. It is also used to concatenate multiple bitstreams into a single PROM file for daisy chain applications. This feature also enables you to take advantage of the Xilinx FPGA reconfiguration capability, as you can store several applications in the same PROM file.

PROM files are also compatible with iMPACT's configuration mode. You can use iMPACT to download a PROM file to an XC18V00 series PROM, a single FPGA, or a slave serial daisy chain of FPGA devices.

#### Serial PROMs

Serial PROMs are PROMs that are read one BIT at a time. In Serial PROM mode, you can create files that:

- Configure a single device with one or more PROM devices.

- Configure daisy-chained devices with one or more PROM devices.

#### Parallel PROMs.

A Parallel PROM is a PROM that is read one byte at a time. In Parallel PROM mode, you can create files that:

- Configure a single device with one or more applications.

- Configure daisy-chained devices with one or more applications.

# System ACE

System ACE is a Xilinx-developed configuration environment that enables space-efficient, pre-engineered, high-density configuration solutions for systems with multiple FPGAs. There are two versions of System ACE; System ACE CF and System ACE MPM. See the "Using iMPACT to Generate Files" chapter for more information.

# MultiPRO Desktop Programmer (MultiPRO)

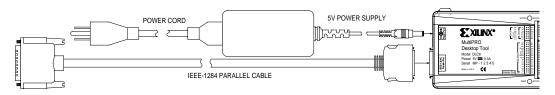

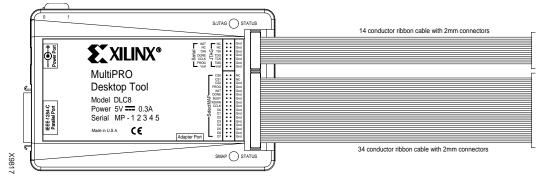

The MultiPRO download cable is a multi-function download cable capable of facilitating socket based, single device configuration using Boundary-Scan as well as standard device configuration using Slave Serial, or SelectMAP interfaces.

- The MultiPRO connects to your PC using an IEEE-1284 standard parallel port.

- The MultiPRO supports the CoolRunner-II CPLD family, and the XC 18V00 Flash PROM family.

# **iMPACT** Platform Support

iMPACT supports the following platforms.

Table 1-1

Platform Support

| Cable     | Platforms               | Ports      |

|-----------|-------------------------|------------|

| MultiLINX | Sol/Win2000/ME/XP       | RS-232,USB |

| Parallel  | WinNT/Win2000/<br>ME/XP | Parallel   |

| MultiPRO  | WinNT/Win2000/<br>ME/XP | Parallel   |

# Starting iMPACT

This section explains how to start and exit iMPACT.

# **From Project Navigator**

To start iMPACT from Project Navigator, follow these steps:

• In the Processes for Current Source window, double click the "Configure Device (iMPACT)" selection under the "Generate Programming File" process.

# From the Command Line

To start iMPACT from the UNIX<sup>®</sup> or  $DOS^{TM}$  command prompt, enter the following command:

impact

If you want to start iMPACT with a .bit, .cdf, or .jed extension, or use iMPACT in batch mode, please see Appendix C for further instructions.

# **Exiting iMPACT**

To exit iMPACT, select File — Exit. If you have an open window, you are prompted to save the data before quitting the application.

# **Using the Interface**

This section describes the iMPACT interface.

### **Main Window**

The main window is the background against which all other windows are displayed.

#### Title Bar

The title bar displays the program name followed by the name of the currently loaded design.

#### Menu Bar

The menu bar, located at the top of the window, includes the File, Edit, Mode, Operations, Output, View, and Help menus. You can also select menu commands by typing the letter underlined in the menu name while holding down the Alt key.

#### Toolbar

The toolbar, located below the menu bar, consists of buttons that you can use to execute commands. Place the mouse pointer over each button to display the command associated with the button. The command name appears as a "tool tip" and the status bar provides more descriptive information.

| Button | Name  | Function                                                                                                       |

|--------|-------|----------------------------------------------------------------------------------------------------------------|

| D      | New   | Removes all configuration descrip-<br>tions from all tabs to let you start a<br>new configuration description. |

| Ê      | Open  | Open an existing CDF file.                                                                                     |

|        | Save  | Saves the active chain file. Clicking<br>this button is the same as selecting<br>Save in the file menu.        |

| Ж      | Cut   | Removes a selection from the<br>iMPACT main window and tempo-<br>rarily stores it on the clipboard.            |

|        | Сору  | Copies a device and temporarily<br>stores a copy of it on the clipboard.                                       |

|        | Paste | Inserts data stored on the clipboard into the iMPACT main window.                                              |

| Button     | Name                                  | Function                                                                               |

|------------|---------------------------------------|----------------------------------------------------------------------------------------|

|            | Toggle<br>Mode                        | Switches iMPACT tabs between<br>Configuration and File Generation<br>modes.            |

|            | Initialize<br>Chain                   | Automatically detects the number<br>and types of devices in a Boundary-<br>Scan chain. |

| ×          | Debug<br>Chain                        | Initiates rudimentary Boundary-Scan<br>TAP debug operations.                           |

|            | Select All                            | Selects all the devices in the chain.                                                  |

|            | Unselect All                          | Unselects all the devices in the chain.                                                |

| ⇔          | Add Xilinx<br>Device                  | Adds a new Xilinx device to the chain.                                                 |

| *=<br>*=   | Assign New<br>Configura-<br>tion File | Changes the current device configu-<br>ration file selection.                          |

| <b>*-3</b> | Program                               | Configures the selected device or devices.                                             |

|            | Verify                                | Verifies the correct configuration has<br>been programmed to the device.               |

| Button    | Name  | Function                                                                                                                                                                                                                                                |

|-----------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ö         | Erase | Erases the contents of a programmed device.                                                                                                                                                                                                             |

|           | About | Displays the program information and copyright.                                                                                                                                                                                                         |

| <b>\?</b> | Help  | Invokes context-sensitive help. When<br>you click this button, the cursor<br>changes into a large question mark<br>with an arrow. You can then select an<br>object, such as a menu command or a<br>toolbar button, and receive help for<br>that object. |

#### **Status Window**

The status window, located at the very bottom of the iMPACT window, is broken into five individual display panes on the right side, and general display section on the left. The status window provides command and application state information. When you select a menu command, a brief description of the command's function appears on the left side status window. The five right side status panes display (from left to right) the application operation mode, the active sub mode, the cable being used, the cable port, and the cable port speed.

# **Commands and Dialog Boxes**

You communicate with iMPACT by selecting commands from the menus and the toolbar.

#### **Common Fields**

The fields shown in the following table are common to most dialog boxes.

Table 1-2 Common Dialog Box Fields

| Dialog Box Field | Function                                                                                                   |

|------------------|------------------------------------------------------------------------------------------------------------|

| ОК               | Closes the dialog box and implements the<br>intended action according to the settings in the<br>dialog box |

| Help             | Displays information on that particular dialog box                                                         |

| Cancel           | Closes the dialog box without affecting any action                                                         |

| Cancel All       | Cancels the current configuration setup                                                                    |

The standard file open and file save dialog boxes enable you to load a project file or save a project file. This type of dialog box includes a file browser.

#### **Selection Dialog Boxes**