# Multi-ICE<sup>®</sup>

Version 2.1

**User Guide**

Copyright © 1998-2001 ARM Limited. All rights reserved. ARM DUI 0048E

## Multi-ICE User Guide

Copyright © 1998-2001 ARM Limited®. All rights reserved.

#### **Release Information**

The following changes have been made to this document.

Change history

| Date           | Issue | Change                            |

|----------------|-------|-----------------------------------|

| June 1998      | А     | First Release                     |

| November 1998  | В     | Internal Release                  |

| December 1998  | С     | Updated for Multi-ICE Release 1.3 |

| January 2001   | D     | Updated for Multi-ICE Version 2.0 |

| September 2001 | Е     | Updated for Multi-ICE Version 2.1 |

#### **Proprietary Notice**

Words and logos marked with  $^{\otimes}$  or  $^{\bowtie}$  are registered trademarks or trademarks owned by ARM Limited. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM Limited shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

#### **Conformance Notices**

This section contains ElectroMagnetic Conformity (EMC) notices and other important notices.

#### Federal Communications Commission Notice

This device is test equipment and consequently is exempt from part 15 of the FCC Rules under section 15.103 (c).

#### CE Declaration of Conformity

This equipment has been tested according to ISE/IEC Guide 22 and EN 45014. It conforms to the following product EMC specifications:

The product herewith complies with the requirements of EMC Directive 89/336/EEC as amended.

#### **Confidentiality Status**

This document is Open Access. This document has no restriction on distribution.

#### **Product Status**

The information in this document is final (information on a developed product).

#### Web Address

http://www.arm.com

# Contents Multi-ICE User Guide

|           | Preface |                                                     |      |

|-----------|---------|-----------------------------------------------------|------|

|           |         | About this document                                 | xiv  |

|           |         | Feedback                                            | xix  |

| Chapter 1 | Intro   | duction                                             |      |

|           | 1.1     | About Multi-ICE                                     | 1-2  |

|           | 1.2     | Availability and compatibility                      | 1-3  |

|           | 1.3     | Basic principles                                    |      |

|           | 1.4     | Introduction to the Multi-ICE components            | 1-7  |

|           | 1.5     | New features and changes from previous versions     | 1-11 |

| Chapter 2 | Getti   | ing Started                                         |      |

| -         | 2.1     | System requirements                                 |      |

|           | 2.2     | Connecting the Multi-ICE hardware                   | 2-5  |

|           | 2.3     | Connecting to nonstandard hardware                  |      |

|           | 2.4     | Starting the software                               |      |

| Chapter 3 | Usin    | g the Multi-ICE Server                              |      |

| •         | 3.1     | About the Multi-ICE server menus                    |      |

|           | 3.2     | Multi-ICE server device configuration files         |      |

|           | 3.3     | Server configuration                                |      |

|           | 3.4     | Using the Multi-ICE server with multiple processors |      |

| Chapter 4  | Debugging with Multi-ICE |                                                            |          |

|------------|--------------------------|------------------------------------------------------------|----------|

|            | 4.1                      | Compatibility with ARM debuggers                           | 4-2      |

|            | 4.2                      | Connecting Multi-ICE to ADW, ADU, or AXD                   | 4-3      |

|            | 4.3                      | Configuring the Multi-ICE DLL                              |          |

|            | 4.4                      | Configuring and debugging multiple processors              |          |

|            | 4.5                      | Debugger internal variables                                |          |

|            | 4.6                      | Post-mortem debugging                                      |          |

|            | 4.7                      | Access to CP15                                             |          |

|            | 4.8                      | Semihosting                                                |          |

|            | 4.9                      | Watchpoints and breakpoints                                |          |

|            | 4.10                     | Debugging applications in ROM                              |          |

|            | 4.11                     | Accessing the EmbeddedICE logic directly                   |          |

| Chapter 5  | Trou                     | bleshooting                                                |          |

|            | 5.1                      | Troubleshooting                                            | 5-2      |

|            | 5.2                      | Error messages                                             |          |

| Chapter 6  | Svet                     | em Design Guidelines                                       |          |

|            | -                        | •                                                          | <u> </u> |

|            | 6.1                      | About the system design guidelines                         |          |

|            | 6.2                      | System design                                              |          |

|            | 6.3                      | ASIC guidelines                                            |          |

|            | 6.4                      | PCB guidelines                                             |          |

|            | 6.5                      | JTAG signal integrity and maximum cable lengths            |          |

|            | 6.6                      | Compatibility with EmbeddedICE interface target connectors | 6-16     |

| Appendix A |                          | er Configuration File Syntax                               |          |

|            | A.1                      | IR length configuration file                               |          |

|            | A.2                      | Device configuration file                                  | A-3      |

| Appendix B | Brea                     | kpoint Selection Algorithm                                 |          |

|            | B.1                      | Multi-ICE internal breakpoints                             | B-2      |

|            | B.2                      | How the debugger steps and runs code                       | B-4      |

|            | B.3                      | Breakpoint and watchpoint allocation algorithm             |          |

| Appendix C | Com                      | mand-line Syntax                                           |          |

|            | C.1                      | Multi-ICE server                                           | C-2      |

| Appendix D | Proc                     | essor-specific Information                                 |          |

|            | D.1                      | The ARM1020T (Rev 0) processor                             | D-2      |

|            | D.2                      | The Intel 80200 (XScale microarchitecture) processor       |          |

| Appendix E | CP14                     | 5 Register Mapping                                         |          |

|            | E.1                      | • • • •                                                    | E 0      |

|            | E.1<br>E.2               | About register mapping                                     |          |

|            | E.2<br>E.3               | ARM710T processor registers                                |          |

|            | ∟.3                      | ARM720T processor registers                                | ⊏-4      |

|            | E.4   | ARM740T processor registers                                | E-5  |

|------------|-------|------------------------------------------------------------|------|

|            | E.5   | ARM920T and ARM922T processor registers                    | E-6  |

|            | E.6   | ARM925T processor registers                                | E-10 |

|            | E.7   | ARM940T processor registers                                | E-14 |

|            | E.8   | ARM946E-S processor registers                              | E-17 |

|            | E.9   | ARM1020T processor registers                               | E-20 |

|            | E.10  | Intel 80200 (XScale microarchitecture) processor registers | E-24 |

| Appendix F | JTAG  | Interface Connections                                      |      |

|            | F.1   | Multi-ICE JTAG interface connections                       | F-2  |

|            | F.2   | Multi-ICE JTAG port timing characteristics                 | F-5  |

|            | F.3   | TCK frequencies                                            | F-7  |

|            | F.4   | TCK values                                                 | F-11 |

| Appendix G | User  | I/O Connections                                            |      |

|            | G.1   | Multi-ICE user I/O pin connections                         | G-2  |

|            | Gloss | sary                                                       |      |

Contents

# List of Tables Multi-ICE User Guide

|            | Change history                                                      | ii   |

|------------|---------------------------------------------------------------------|------|

| Table 2-1  | Supported operating systems for Multi-ICE Version 2.1               | 2-2  |

| Table 3-1  | TCK frequency for autoconfigure                                     | 3-3  |

| Table 3-2  | Scale and multiplier values                                         | 3-23 |

| Table 3-3  | Scale values for clocking speeds                                    | 3-23 |

| Table 4-1  | ARM7 family debugger variable support                               | 4-31 |

| Table 4-2  | ARM9 family debugger variable support                               | 4-32 |

| Table 4-3  | ARM10 family and XScale microarchitecture debugger variable support | 4-32 |

| Table 4-4  | Cache selection type values                                         | 4-34 |

| Table 4-5  | Breakpoints                                                         | 4-50 |

| Table E-1  | ARM710T processor registers                                         | E-3  |

| Table E-2  | ARM720T processor registers                                         | E-4  |

| Table E-3  | ARM740T processor registers                                         | E-5  |

| Table E-4  | ARM920T and ARM922T processor registers                             | E-6  |

| Table E-5  | ARM920T and ARM922T cp15 register 7 accesses                        | E-7  |

| Table E-6  | ARM920T and ARM922T cp15 register 8 accesses                        | E-8  |

| Table E-7  | ARM925T processor registers                                         |      |

| Table E-8  | ARM925T cp15 register 7 accesses                                    | E-11 |

| Table E-9  | ARM925T cp15 register 8 accesses                                    | E-12 |

| Table E-10 | ARM925T cp15 register 7 accesses                                    | E-13 |

| Table E-11 | ARM940T processor registers                                         | E-14 |

| Table E-12 | ARM940T cp15 register 7 accesses                                    |      |

| Table E-13 | ARM946E-S processor registers                                       | E-17 |

| Table E-14 | ARM940T cp15 register 7 accesses          | . E-19 |

|------------|-------------------------------------------|--------|

| Table E-15 | ARM1020T processor registers              |        |

| Table E-16 | ARM1020T cp15 register 7 accesses         | . E-21 |

| Table E-17 | ARM1020T cp15 register 8 accesses         | . E-22 |

| Table F-1  | JTAG pinouts                              | F-3    |

| Table F-2  | Multi-ICE IEEE 1149.1 timing requirements | F-5    |

| Table F-3  | TCK frequencies                           | F-7    |

| Table F-4  | TCK values                                | . F-11 |

| Table G-1  | User I/O connections                      | G-2    |

# List of Figures **Multi-ICE User Guide**

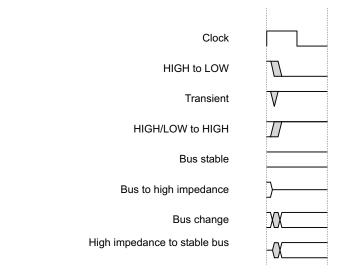

| Figure Pre-1 | Key to timing diagram conventions                  | xvii |

|--------------|----------------------------------------------------|------|

| Figure 1-1   | The Multi-ICE interface unit                       | 1-7  |

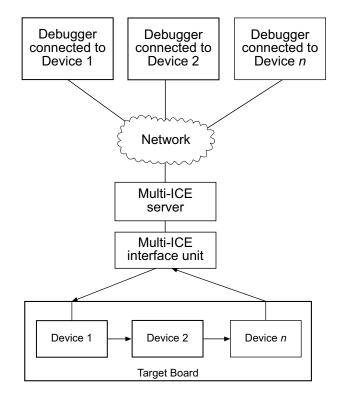

| Figure 1-2   | Connecting multiple debuggers and multiple targets | 1-9  |

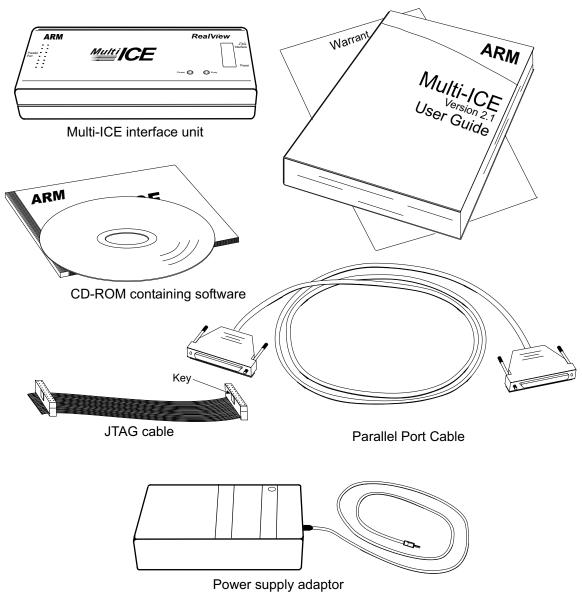

| Figure 2-1   | The Multi-ICE product kit                          | 2-6  |

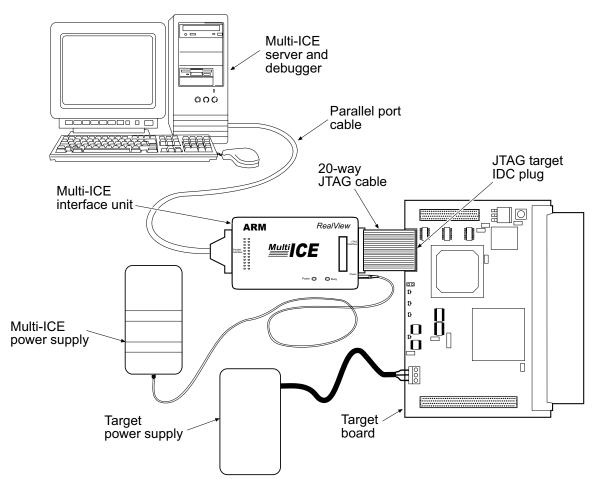

| Figure 2-2   | Multi-ICE interface unit cable connection          | 2-7  |

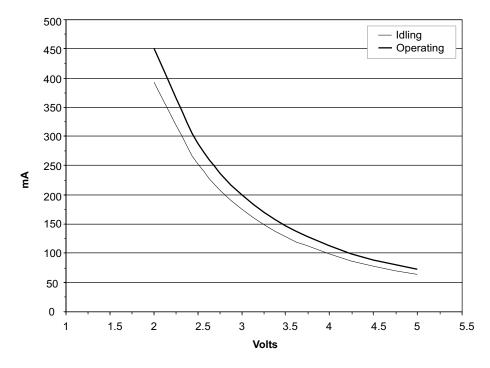

| Figure 2-3   | Multi-ICE current consumption with voltage         | 2-11 |

| Figure 2-4   | Start menu items for Multi-ICE                     | 2-12 |

| Figure 2-5   | Unconfigured Multi-ICE server window               | 2-14 |

| Figure 2-6   | Multi-ICE server window configured for an ARM7TDMI |      |

| Figure 3-1   | Multi-ICE server menu items                        | 3-2  |

| Figure 3-2   | The File menu                                      | 3-3  |

| Figure 3-3   | The View menu                                      | 3-5  |

| Figure 3-4   | The Run Control menu                               | 3-6  |

| Figure 3-5   | The Connection menu                                | 3-7  |

| Figure 3-6   | The Settings menu                                  | 3-7  |

| Figure 3-7   | The Help menu                                      | 3-8  |

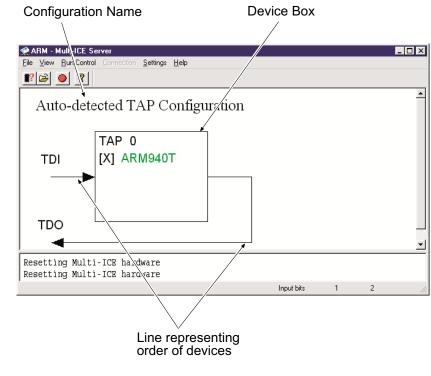

| Figure 3-8   | Autoconfiguring an ARM940T                         |      |

| Figure 3-9   | TAP driver status dialog                           |      |

| Figure 3-10  | TAP Controller Device ID register format           | 3-16 |

| Figure 3-11  | The Start-up Options dialog                        | 3-16 |

| Figure 3-12  | The Port Settings dialog                           | 3-18 |

| Figure 3-13  | The User Output Bits dialog                        | 3-20 |

| Figure 3-14  | Status of the user input bits                      | 3-21 |

|              |                                                    |      |

| Figure 3-15 | The JTAG Settings dialog 3-21                                                       |

|-------------|-------------------------------------------------------------------------------------|

| Figure 3-16 | Setting up interaction between devices                                              |

| Figure 3-17 | Cascade operation 3-29                                                              |

| Figure 3-18 | Setting up the poll frequency 3-30                                                  |

| Figure 4-1  | The AXD Options menu                                                                |

| Figure 4-2  | The AXD Choose Target dialog 4-4                                                    |

| Figure 4-3  | Selecting the Multi-ICE DLL using AXD 4-5                                           |

| Figure 4-4  | The ADW and ADU Options menu 4-5                                                    |

| Figure 4-5  | ADW configuration dialog with Multi-ICE active 4-6                                  |

| Figure 4-6  | Selecting the Multi-ICE DLL using ADW 4-6                                           |

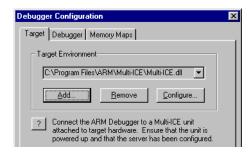

| Figure 4-7  | Multi-ICE Configuration dialog 4-8                                                  |

| Figure 4-8  | Multi-ICE Welcome dialog 4-9                                                        |

| Figure 4-9  | Driver Details dialog 4-10                                                          |

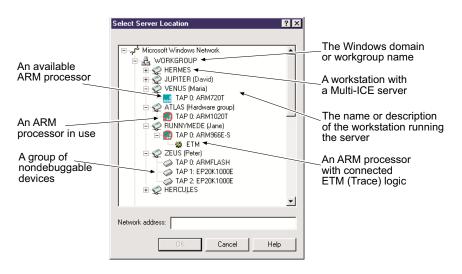

| Figure 4-10 | Server Browse dialog 4-12                                                           |

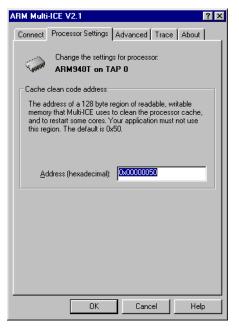

| Figure 4-11 | Multi-ICE Processor Settings tab showing cache setting 4-14                         |

| Figure 4-12 | Multi-ICE Processor Settings tab showing XScale settings 4-15                       |

| Figure 4-13 | Multi-ICE Advanced settings tab 4-16                                                |

| Figure 4-14 | Trace configuration tab 4-18                                                        |

| Figure 4-15 | About tab 4-19                                                                      |

| Figure 4-16 | Channel viewer controls 4-20                                                        |

| Figure 4-17 | Saving a named target configuration 4-23                                            |

| Figure 4-18 | Configuring AXD to run a configuration script 4-26                                  |

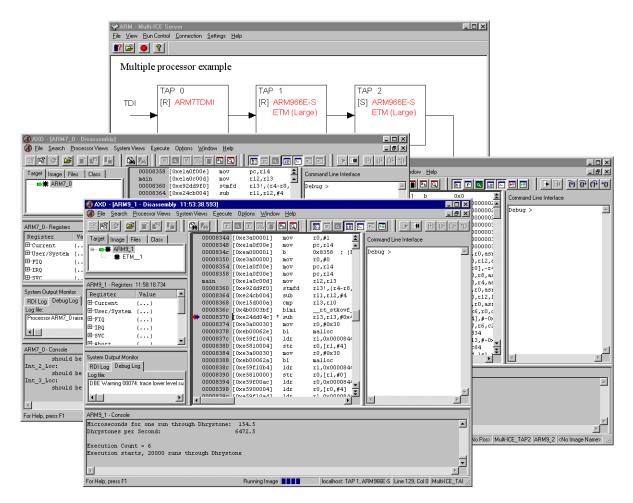

| Figure 4-19 | Three AXDs and the Multi-ICE server configured for a multiple processor target 4-27 |

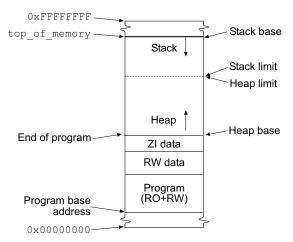

| Figure 4-20 | Relating top_of_memory to single section program layout 4-36                        |

| Figure 4-21 | Register view showing EmbeddedICE logic registers 4-57                              |

| Figure 4-22 | The View Registers menu 4-58                                                        |

| Figure 4-23 | The Display Co-processor Regs dialog 4-58                                           |

| Figure 4-24 | EmbeddedICE logic registers in the Raw Co-processor 0 view 4-59                     |

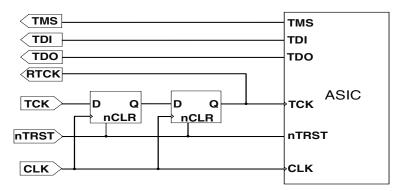

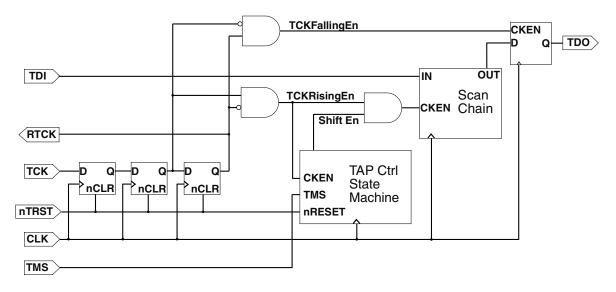

| Figure 6-1  | Basic JTAG port synchronizer                                                        |

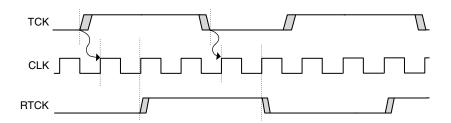

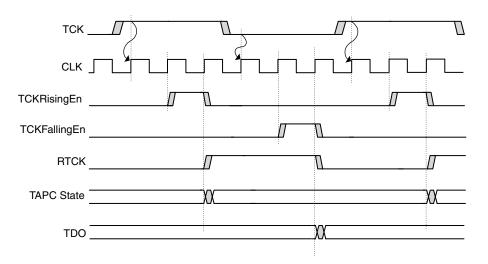

| Figure 6-2  | Timing diagram for the Basic JTAG synchronizer in Figure 6-1 6-5                    |

| Figure 6-3  | JTAG port synchronizer for single rising-edge D-type ASIC design rules 6-5          |

| Figure 6-4  | Timing diagram for the D-type JTAG synchronizer in Figure 6-3 6-6                   |

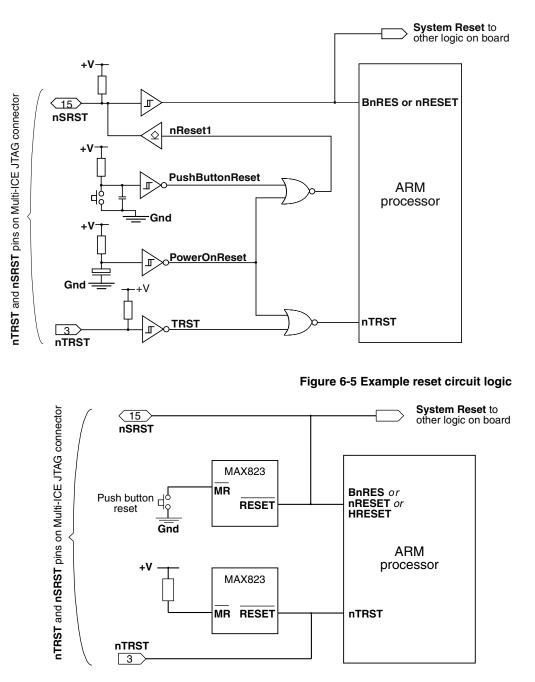

| Figure 6-5  | Example reset circuit logic 6-8                                                     |

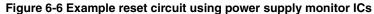

| Figure 6-6  | Example reset circuit using power supply monitor ICs 6-8                            |

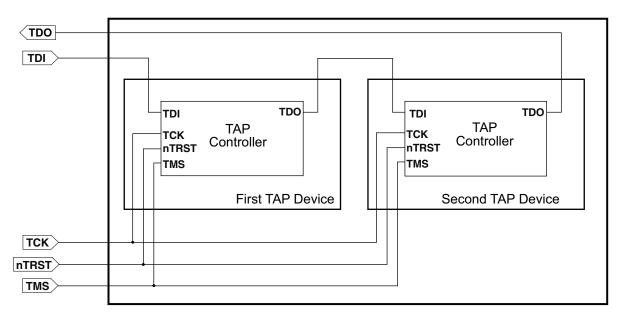

| Figure 6-7  | TAP Controllers serially chained in an ASIC 6-10                                    |

| Figure 6-8  | Typical PCB connections                                                             |

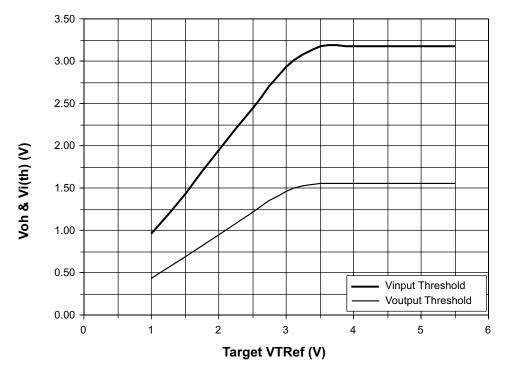

| Figure 6-9  | Target interface voltage levels 6-12                                                |

| Figure F-1  | JTAG pin connections, top view F-2                                                  |

| Figure F-2  | Multi-ICE JTAG port timing diagram F-5                                              |

| Figure G-1  | User I/O pin connections G-2                                                        |

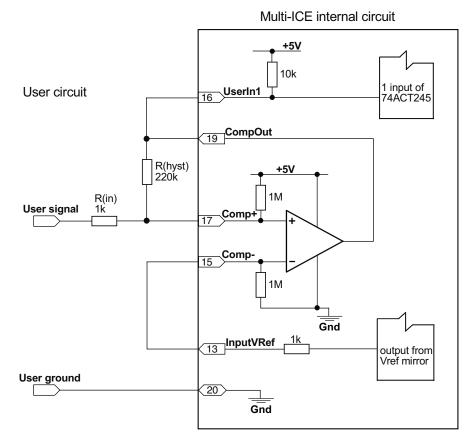

| Figure G-2  | Converting user-input signals to TTL levels G-4                                     |

# Preface

This preface introduces the Multi-ICE Version 2.1 User Guide. It explains the structure of the user guide and lists other sources of information that relate to Multi-ICE and ARM debuggers.

This preface contains the following sections:

- About this document on page xiv

- *Feedback* on page xix.

## About this document

This document describes the ARM *Multi-processor EmbeddedICE interface unit* (Multi-ICE) Version 2.1.

#### Intended audience

This document is written for users of Multi-ICE on Windows or Unix platforms, using either the ARM *Software Development Toolkit* (SDT) or *ARM Developer Suite* (ADS) development environments. It is assumed that you are a software engineer with some experience of the ARM architecture, or a hardware engineer designing a product that is compatible with Multi-ICE.

Parts of this document assume you have some knowledge of JTAG technology. If you require more information on JTAG, refer to *IEEE Standard 1149.1*, available from the *Institute of Electrical and Electronic Engineers* (IEEE). Refer to the IEEE website for more information at:

http://www.ieee.org/

#### Organization

This document is organized into the following chapters and appendices:

#### **Chapter 1** Introduction

Read this chapter for a description of:

- what is provided in the Multi-ICE product

- the purpose of the EmbeddedICE logic within the CPU

- what has changed between Multi-ICE Version 2.1 and Version 2.0, between Version 2.0 and Release 1.4, and between Release 1.4 and Release 1.3.

#### Chapter 2 Getting Started

Read this chapter for information on how to start working with Multi-ICE. The chapter includes the hardware and software system requirements, how to connect up the hardware, and how to start the Multi-ICE server.

#### Chapter 3 Using the Multi-ICE Server

This chapter describes how you use the Multi-ICE server, including a more detailed description of configuring the server. There are also sections describing the execution control and user I/O features.

#### Chapter 4 Debugging with Multi-ICE

This chapter describes how to:

- connect Multi-ICE to an ARM debugger

- change the behavior of Multi-ICE using internal variables

- implement watchpoints and breakpoints and what this means to you

- access the EmbeddedICE logic directly.

You must read this chapter in conjunction with the debugger user documentation, for example the *ADS Debuggers Guide*.

#### Chapter 5 *Troubleshooting*

Read this chapter for a troubleshooting guide and a list of error messages.

#### Chapter 6 System Design Guidelines

Read this chapter for information about designing ARM-based ASICs and PCBs that can be debugged using Multi-ICE.

It includes:

- suggested clocking and reset circuit diagrams

- how to chain TAP controllers

- suggested physical connector types and pinouts

- a description of logic voltage level adaption

- how power consumption varies with supply voltage.

#### Appendix A Server Configuration File Syntax

This appendix describes the server configuration file. This file describes a target device group to Multi-ICE.

#### Appendix B Breakpoint Selection Algorithm

This appendix describes how Multi-ICE allocates your breakpoints and internally generated breakpoints to the hardware. You must read it if you require specific types of breakpoint to be allocated to target memory regions.

#### Appendix C Command-line Syntax

This appendix describes the command-line syntax of the Multi-ICE server.

#### Appendix D Processor-specific Information

This appendix describes the differences in the way that Multi-ICE behaves on the ARM10 and XScale microarchitecture processors.

#### Appendix E CP15 Register Mapping

This appendix contains details relating to register mapping information for the ARM7-based, ARM9-based, ARM10-based, and XScale processors containing a system control coprocessor (CP15).

#### Appendix F JTAG Interface Connections

This appendix describes and illustrates the JTAG pin connections.

#### Appendix G User I/O Connections

This appendix describes and illustrates the additional input and output connections provided in Multi-ICE.

#### **Typographical conventions**

The following typographical conventions are used in this document:

| bold              | Highlights ARM processor signal names within text, and interface<br>elements such as menu names. Can also be used for emphasis in<br>descriptive lists where appropriate. |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| italic            | Highlights special terminology, cross-references and citations.                                                                                                           |  |

| monospace         | Denotes text that can be entered at the keyboard, such as commands, file names and program names, and source code.                                                        |  |

| <u>mono</u> space | Denotes a permitted abbreviation for a command or option. The<br>underlined text can be entered instead of the full command or option<br>name.                            |  |

| typewriter italic |                                                                                                                                                                           |  |

|                   | Denotes arguments to commands or functions where the argument is to<br>be replaced by a specific value.                                                                   |  |

| typewriter bold   |                                                                                                                                                                           |  |

Denotes language keywords when used outside example code.

#### **Timing diagram conventions**

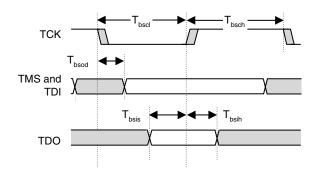

This manual contains timing diagrams. Figure Pre-1 explains the components used in these diagrams. Any variations are clearly labeled when they occur. Therefore, no additional meaning must be attached unless specifically stated.

#### Figure Pre-1 Key to timing diagram conventions

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

#### **Further reading**

This section lists publications by ARM Limited, and by third parties, that are related to this product.

#### **ARM** publications

This document contains information that is specific to Multi-ICE Version 2.1.

The following documents relate specifically to Multi-ICE:

- *Multi-ICE Reference Guide* (ARM DUI 0154)

- ARM Multi-ICE Installation Guide (ARM DSI 0005)

- Multi-ICE file Readme.txt, supplied on the Multi-ICE distribution CD and installed with the product

- Multi-ICE file proclist.txt, a list of the processors supported by Multi-ICE. and installed with the product.

If you are using Multi-ICE Version 2.1 with the *ARM Developer Suite* (ADS) v1.1, refer to the following books in the ADS document suite for information on other components of ADS:

- Trace Debug Tools User Guide (ARM DUI 0118)

- ADS Installation and License Management Guide (ARM DUI 0139)

- *Getting Started* (ARM DUI 0064)

- CodeWarrior IDE Guide (ARM DUI 0065)

- ADS Debuggers Guide (ARM DUI 0066)

- ADS Developer Guide (ARM DUI 0056)

- ARM Application Library Programmers Guide (ARM DUI 0081).

The following additional documentation that might be useful is provided with the ARM Developer Suite:

• *ARM Architecture Reference Manual* (ARM DDI 0100). This is supplied in DynaText format as part of the online books, and as a PDF file.

In addition, refer to the following documentation for specific information relating to ARM products:

- ARM Reference Peripheral Specification (ARM DDI 0062)

- the ARM datasheet or technical reference manual for your hardware device.

#### Other publications

The following publications might also be useful to you, and are available from the indicated sources:

- *The Intel® XScale™ Core Developer's Manual*, Datasheet, advance information. Ref 27341401-002. Intel Corp. 2000.

- *IEEE Standard Test Access Port and Boundary Scan Architecture* (IEEE Std. 1149.1) describes the JTAG ports with which Multi-ICE communicates.

# Feedback

ARM Limited welcomes feedback both on Multi-ICE and on the documentation.

### Feedback on Multi-ICE

If you have any problems with Multi-ICE, please contact your supplier. To help us provide a rapid and useful response, please give:

- the Multi-ICE version you are using

- details of the platforms you are using, including both the host and target hardware types and operating system

- where appropriate, a small standalone sample of code that reproduces the problem

- a clear explanation of what you expected to happen, and what actually happened

- the commands you used, including any command-line options

- if possible, sample output illustrating the problem

#### Feedback on this document

If you have any comments on this document, please send email to errata@arm.com giving:

- the document title

- the document number

- the page number(s) to which your comments refer

- a concise explanation of your comments.

General suggestions for additions and improvements are also welcome.

Preface

# Chapter 1 Introduction

This chapter introduces Multi-ICE Version 2.1, and describes its software components and documentation. It contains the following sections:

- About Multi-ICE on page 1-2

- Availability and compatibility on page 1-3

- Basic principles on page 1-4

- Introduction to the Multi-ICE components on page 1-7

- New features and changes from previous versions on page 1-11.

# 1.1 About Multi-ICE

Multi-ICE is the EmbeddedICE logic debug solution from ARM. It enables you to debug software running on ARM processor cores that include the EmbeddedICE logic.

Multi-ICE provides the software and hardware interface between a *Joint Test Action Group* (JTAG) *IEEE Standard 1149.1* port on the hardware using a small interface unit and a Windows or UNIX debugger using the ARM *Remote Debug Interface* (RDI) running on a workstation.

You can use Multi-ICE with systems that contain one or more ARM CPUs or DSP processors. It also supports the *Embedded Trace Macrocell* (ETM). The external hardware and software to decode this information is available separately from ARM Limited.

The Multi-ICE Version 2.1 product comprises:

- An interface unit that connects the parallel port of a workstation to the JTAG interface of an ASIC that includes debug and EmbeddedICE capability.

- A cable to connect the interface unit to a parallel port. (This is underneath the foam packaging.)

- A 20-way ribbon cable. This connects the Multi-ICE interface unit to the target.

- Software on CD-ROM that enables an ARM debugger to communicate with the interface unit. The software includes the following components:

- the Multi-ICE server

- a Dynamic Link Library (DLL) to use with the debugger

- documentation in PDF and Dynatext formats

- example programs demonstrating the TAPOp *Application Program Interface* (API).

- Documentation, including:

- a printed copy of this User Guide

- the installation CD insert

- a warranty notice and end user license.

A 20-way to 14-way cable adaptor for use with targets that use a 14-way target connection is available on request from ARM, part number HPI-0027.

# **1.2** Availability and compatibility

Multi-ICE is available from ARM Limited and its resellers as a package that includes:

- a JTAG hardware interface

- a software interface component that connects, using RDI, to an external debugger, supplied separately.

Upgrades from earlier versions of Multi-ICE are available. Please contact your reseller or check on the ARM Limited website for details.

The ADS Version 1.1 product includes the following fully supported debuggers:

- *ARM eXtended Debugger* (AXD, both Windows and UNIX versions)

- ARM Debugger for Windows (ADW)

- ARM Debugger for UNIX (ADU).

Multi-ICE is also compatible with third-party debuggers that conform to the ARM standard RDI 1.5.1 interface.

Contact ARM Limited directly regarding OEM licenses.

# 1.3 Basic principles

The EmbeddedICE<sup>®</sup> logic and the ARM processor debug extensions enable Multi-ICE to debug software running on an ARM processor. The following topics are covered:

- Debug extensions to the ARM core on page 1-4

- *The EmbeddedICE logic* on page 1-4

- *The ICE extension unit* on page 1-5

- *How Multi-ICE differs from a debug monitor* on page 1-5.

#### — Note —

To determine whether a specific ARM processor has support for JTAG debugging, refer to the datasheet or technical reference manual.

#### 1.3.1 Debug extensions to the ARM core

The extensions consist of a number of scan chains around the processor core and some additional signals that are used to control the behavior of the core for debug purposes. The most significant of these additional signals are:

- **BREAKPT** This core signal enables external hardware to halt processor execution for debug purposes. When HIGH, the current memory access is tagged as breakpointed and the core stops when this instruction is executed.

- **DBGRQ** This core signal is a level-sensitive input that causes the CPU core to enter debug state when the current instruction has completed.

- **DBGACK** This core signal is an output from the CPU core that goes HIGH when the core is in debug state allowing external devices to determine the current state of the core.

Multi-ICE uses these, and other signals, by using the debug interface of the processor core, for example by writing to the control register of the EmbeddedICE logic. For more details, refer to the debug interface section of the ARM datasheet or technical reference manual for your core.

#### 1.3.2 The EmbeddedICE logic

The EmbeddedICE logic is the integrated on-chip logic that provides JTAG debug support for ARM cores. EmbeddedICE/RT is a superset of EmbeddedICE that includes extensions supporting real-time debug, including setting breakpoints on a running target.

The EmbeddedICE logic is accessed through the TAP controller on the ARM core using the JTAG interface. See Chapter 6 *System Design Guidelines* for details of designing this into your own target.

The standard EmbeddedICE logic consists of:

- two watchpoint units

- a control register

- a status register

- a set of registers implementing the Debug Communications Channel link.

For more details on the *Debug Communications Channel* (DCC), see the *ADS Developer Guide*.

You can program one or both of the watchpoint units to halt the execution of instructions by the ARM CPU core. Execution is halted when a match occurs between the values in the watchpoint registers and the values currently appearing on the address bus, data bus, and selected control signals.

You can mask any bit to prevent it from affecting the comparison. Either watchpoint unit can be configured to be a watchpoint (monitoring data accesses) or a breakpoint (monitoring instruction fetches).

For more information, refer to the relevant section of the appropriate ARM datasheet or a technical reference manual.

#### 1.3.3 The ICE extension unit

The *ICE Extension Unit* (IEU) is a logic block that can be added to the EmbeddedICE logic when a processor is fabricated. The IEU extends the number of hardware breakpoint units available to the debugger using extra comparators and an extra JTAG scan chain. It is available in different sizes, providing up to 30 additional units. Multi-ICE supports the logic automatically on processors that include it.

#### 1.3.4 How Multi-ICE differs from a debug monitor

A debug monitor, such as the Angel<sup>M</sup> debug monitor provided with the *ARM Firmware Suite* (AFS), is an application that runs on your target hardware in conjunction with your application, and requires target resources (for example, memory, access to exception vectors, and time) to be available.

The EmbeddedICE debug architecture requires almost no resources. Rather than being an application on the board, it works by using:

• additional debug hardware within the core, that is, parts that enable the host to communicate with the target

• an external interface unit that buffers and translates the core signals into something usable by a host computer.

The EmbeddedICE debug architecture allows debugging to be as non-intrusive as possible:

- the target being debugged requires very little special hardware to support debugging

- in most cases you do not have to set aside memory for debugging in the system being debugged and you do not have to incorporate special software into the application

- execution of the system being debugged is only halted when a breakpoint or watchpoint unit is triggered, or you request that execution is halted.

## **1.4** Introduction to the Multi-ICE components

This section introduces the components of the Multi-ICE product, and describes how they fit together:

- The Multi-ICE interface unit on page 1-7

- The Multi-ICE parallel port driver on page 1-7

- *The Multi-ICE server* on page 1-8

- *The portmap application* on page 1-9.

If you are using the Multi-ICE DLL on a UNIX workstation, you must connect that workstation to the Windows workstation running the server using a TCP/IP network.

For more information about the Multi-ICE server see Chapter 2 *Getting Started* and Chapter 3 *Using the Multi-ICE Server*. For more information about the Multi-ICE Debugger interface see Chapter 4 *Debugging with Multi-ICE*.

#### 1.4.1 The Multi-ICE interface unit

The Multi-ICE interface unit provides the hardware to allow a Windows workstation to control multiple JTAG capable devices. The unit is shown in Figure 1-1. The unit has a parallel port at one end, and a 20-pin JTAG connector and external power input at the other. A cable is supplied to connect the interface unit to the workstation parallel port.

| ARM<br>President | RealView |

|------------------|----------|

|                  |          |

#### Figure 1-1 The Multi-ICE interface unit

The interface unit gives the Windows workstation direct control of basic JTAG operations. This means new debugging features and support for new processors can be added with software updates.

#### 1.4.2 The Multi-ICE parallel port driver

Although the Multi-ICE interface unit connects to your Windows workstation through a standard parallel port, Multi-ICE does not use the standard parallel port driver. Instead, an optimized driver is used that allows high-speed communication with the interface unit. This driver is installed automatically when you install Multi-ICE, and is

configured using options in the Multi-ICE server. On Windows NT 4.0, you can see the Multi-ICE parallel port driver in the Devices control panel. On the other supported variants of Windows, there is no way to access it.

The parallel port driver is only required on the Windows workstation that runs the Multi-ICE server.

#### 1.4.3 The Multi-ICE server

The Multi-ICE server is an application that runs on the Windows workstation connected to the interface unit. The Multi-ICE server can address each JTAG device individually, without affecting other devices on the board. It uses this ability to create virtual connections for each of the JTAG devices on the board. Debugging software can attach to one of these virtual connections, and perform debugging operations with no knowledge of the other devices on the board, as shown in Figure 1-2 on page 1-9.

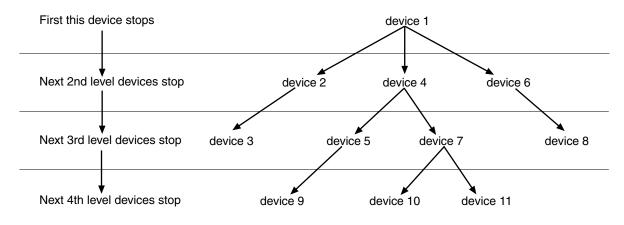

The Multi-ICE server enables multiple concurrent connections, so if you have a target with multiple processors, you can run several debuggers and connect each one to a different processor on the board. This allows you to easily debug multiprocessor systems. The server can also perform a synchronized start or stop of processors, for debugging multiprocessor systems where the processors interact with each other.

#### Figure 1-2 Connecting multiple debuggers and multiple targets

The Multi-ICE server also supports connections across a network, so the debugging software can be run on a different computer to the server, or on several different computers if that is appropriate.

#### 1.4.4 The portmap application

To support network connections, an additional application must be running on the Windows workstation that runs the Multi-ICE server. This application is called the portmapper, and allows software on other computers on the network to locate the Multi-ICE server.

The portmapper is normally started automatically by the Multi-ICE server. It runs in a minimized console window, and requires no intervention by you. You can change the Multi-ICE server settings to prevent the portmapper being started if you do not require network connections, or if you already have another portmapper running on your Windows workstation.

#### 1.4.5 The Multi-ICE DLL

The Multi-ICE DLL is a software module that translates debugger commands, for example, start, stop, and download, into JTAG control sequences for a particular processor. It fits between a debugger, for example AXD, providing the user interface and the Multi-ICE server controlling the JTAG devices.

The Multi-ICE DLL is supplied in the form of a Windows or UNIX dynamically linked library. The Multi-ICE Version 2.1 DLL provides support for debugging on a wide range of ARM cores (see proclist.txt for a list of supported cores). It can also be used with any graphical debugger that supports the RDI 1.5.1 interface. This includes all current ARM graphical debuggers (AXD, ADW, and ADU)

## 1.5 New features and changes from previous versions

This section describes the new features and other changes to the product:

- New features in Multi-ICE Version 2.1 on page 1-11

- Changes in Multi-ICE Version 2.1 on page 1-11

- *New features in Multi-ICE Version 2.0* on page 1-12

- Changes in Multi-ICE Version 2.0 on page 1-13

- New features in Release 1.4 on page 1-13.

#### 1.5.1 New features in Multi-ICE Version 2.1

The new features in Multi-ICE Version 2.1 are:

#### New processor support

| ARM7 cores | $ARM7TDMI^{\text{\tiny TM}} (Rev 4), ARM7TDMI-S^{\text{\tiny TM}} (Rev 4).$ |

|------------|-----------------------------------------------------------------------------|

| ARM9 cores | ARM922T <sup>™</sup> (Rev 0), ARM925T, and                                  |

|            | ARM946E-S <sup>™</sup> (Rev 1).                                             |

#### New operating system support

Windows Me.

#### Improved XScale processor support

Changes to the way XScale processors are supported means that it is no longer necessary to reset the processor when connecting to it. See *The Intel 80200 (XScale microarchitecture) processor* on page D-3 for more information.

#### Improved hardware interface

The Multi-ICE interface unit now includes an external power supply option, enabling it to be connected to systems that cannot supply sufficient power.

#### **Hot-plug support**

The new power supply capabilities enable the Multi-ICE interface unit to be plugged into a running target board and the running program analyzed without restarting the target.

#### 1.5.2 Changes in Multi-ICE Version 2.1

Changes in Multi-ICE Version 2.1 are:

**TAPOp API** Minor changes to the TAPOp API clarify and streamline the affected functions.

#### 1.5.3 New features in Multi-ICE Version 2.0

The new features in Multi-ICE Version 2.0 were:

#### New processor support

| ARM7 cores | ARM7TDMI-S (Rev 1 and Rev 2), ARM7TDI-S <sup>™</sup><br>(Rev 2), and Samsung KS32C50100.                              |

|------------|-----------------------------------------------------------------------------------------------------------------------|

| ARM9 cores | ARM9E-S <sup>™</sup> (Rev 0), ARM920T <sup>™</sup> (Rev 1),<br>ARM946E-S (Rev 0), and ARM966E-S <sup>™</sup> (Rev 0). |

| ARM10 core | $ARM1020T^{\text{\tiny TM}} \text{ (Rev 0), } ARM10200T^{\text{\tiny TM}} \text{ (Rev 0).}$                           |

|            | 1.4                                                                                                                   |

#### Intel XScale microarchitecture

Intel 80200.

#### New operating system support

Windows 2000 and Solaris 7.

#### Support for the ARM Developer Suite

Full support for ADS v1.1, including the Trace Debug Tools (TDT).

#### Better target processor descriptions

Targets that have additional components, for example, system coprocessors and floating point units, can now be described and presented more clearly in the user interface, and are also no longer hard coded in the Multi-ICE DLL.

#### New Configuration dialog

The configuration dialog is now simpler to use, and includes support for the ARM TDT, and you can now search for Multi-ICE servers running on workstations using the Windows Network Browser service.

#### Embedded Trace Macrocell (ETM) and MultiTrace<sup>™</sup> support

Multi-ICE supports access to the ETM.

MultiTrace is the ARM execution trace solution (available as a separate product) that includes the additional software and hardware.

#### **RealMonitor support**

Multi-ICE supports access to *RealMonitor* (RM), the ARM real-time debug solution.

#### **EmbeddedICE/RT** is supported

Multi-ICE supports processors containing ARM cores that contain the EmbeddedICE/RT extensions.

#### Autoconfiguration extensions

Autoconfiguration now supports the ARM Integrator<sup>™</sup> boards in configuration mode, making the FPGA firmware on these boards easier to modify.

#### 1.5.4 Changes in Multi-ICE Version 2.0

Changes in Multi-ICE Version 2.0 were:

Start MenuThe Windows Start  $\rightarrow$  Programs menu entry is now ARM Multi-ICEv2.0 and the default install location is Program Files\ARM, for consistency<br/>with other ARM applications.

#### **Breakpoint algorithm changes**

The watchpoint and breakpoint allocation algorithms have been rewritten and so the actual allocation to hardware breakpoint units has changed.

For more detail see Appendix B Breakpoint Selection Algorithm.

arm9\_restart\_code\_address

The ARM debugger internal variable arm9\_restart\_code\_address has been removed, and an interface providing equivalent functionality added to the Multi-ICE configuration dialog.

#### 1.5.5 New features in Release 1.4

The features that were new in Release 1.4 are:

#### **New Processor Support**

ARM920T (Rev 0) and ARM940T<sup>™</sup> (Rev 1). A software update to Release 1.4 provided support for ARM966E-S (Rev 0).

#### New Operating System Support

Windows 98.

#### Support for the ARM Developer Suite

Full support for ADS v1.0, including support for RDI 1.5.1.

#### Improved demand paged memory support

Demand paged memory can make it hard to know where the system memory is in the address space, so extra facilities were added to support this.

## **Performance enhancements**

Debugging performance was improved, especially with ARM9 cores.

# Chapter 2 Getting Started

This chapter describes how to connect the parts of Multi-ICE together and how to configure the Multi-ICE server software. It contains the following sections:

- System requirements on page 2-2

- Connecting the Multi-ICE hardware on page 2-5

- Connecting to nonstandard hardware on page 2-9

- *Starting the software* on page 2-12.

## 2.1 System requirements

This section describes the hardware and software requirements of Multi-ICE:

- *Host software requirements* on page 2-2

- *Host hardware requirements* on page 2-3

- *Target hardware requirements* on page 2-4.

#### 2.1.1 Host software requirements

There are two distinct software components in Multi-ICE Version 2.1:

- the Multi-ICE server, that must be run on the computer the interface unit is attached to

- the Multi-ICE DLL, that can be run on another computer.

Table 2-1 identifies the operating systems you can use for each of these components.

| Multi-ICE Version 2.1 server | Multi-ICE Version 2.1<br>DLL                                                          |

|------------------------------|---------------------------------------------------------------------------------------|

| Yes                          | Yes                                                                                   |

| No                           | Yes                                                                                   |

| No                           | Yes                                                                                   |

|                              | server       Yes       Yes       Yes       Yes       Yes       Yes       Yes       No |

Table 2-1 Supported operating systems for Multi-ICE Version 2.1

The graphical debuggers supplied in v1.0.1 and v1.1 of ADS, and SDT 2.51 are all compatible with the Multi-ICE Version 2.1 DLL, as are debuggers supplied by third parties that conform to the ARM RDI 1.5.1 specification.

If you are running a debugger under UNIX, for example AXD, you must use another computer connected to it that can run the Multi-ICE server software. The workstation running UNIX must have networking software that supports a TCP/IP connection to the Multi-ICE server, and must meet the minimum software requirements specified in the debugger installation notes.

## Networking software

If you require remote access to the server, your operating system must be installed with its supplied networking software. If the TCP/IP stack is not present during installation, the following warning text is displayed:

TCP/IP protocol does not appear to have been set up on this computer. Setup will continue. Please install TCP/IP if you want to use Multi-ICE remote access features.

## Automatic dialup

Automatic dialup might be triggered when you use Multi-ICE because Multi-ICE uses network facilities. You can prevent unnecessary dialups by either:

- disabling **Allow Network Connections** on the Multi-ICE server **Settings** menu and only using This Computer as the server name in the DLL

- disabling automatic dialup.

## 2.1.2 Host hardware requirements

This section defines the minimum recommended hardware requirements for installing and running the Multi-ICE DLL and, on Windows, the Multi-ICE server.

## **Disk space**

If you carry out a full installation of the software, up to 20MB of hard disk space is required.

## To use the Multi-ICE software on Windows

To use the Multi-ICE server and DLL on Windows, you require the following:

- 200MHz Pentium processor

- system memory:

- 32MB RAM for Windows 95, Windows 98, and Windows Me

- 64MB RAM for Windows NT 4.0 and Windows 2000.

- CD-ROM drive (can be used across a network)

- an OS supported graphics device capable of VGA resolution or better

- parallel port

- network card (if remote access to the server is required).

## To use the Multi-ICE DLL on Solaris

To use the Multi-ICE DLL on Solaris, you need the following:

- Sun UltraSparc or compatible machine

- Solaris 2.6 or Solaris 7, with the *Common Desktop Environment* (CDE)

- CD-ROM drive (this can be a networked CD-ROM drive)

- connected network interface.

## To use the Multi-ICE DLL on HP-UX

To use the Multi-ICE DLL on HP-UX, you need the following:

- HP PA-RISC v1.1 or v2.0 processor

- HP-UX 10.20

- CD-ROM drive (can be used across a network)

- connected network interface.

#### 2.1.3 Target hardware requirements

Multi-ICE Version 2.1 has been designed to be very flexible, but it has the following target hardware requirements:

- A device interface conforming to the IEEE1149.1 (JTAG) specification.

- Electronic signals available to the interface, and within the limits of current and voltage specified in Chapter 6 *System Design Guidelines*.

- An IDC connector on the target board wired as described in *Multi-ICE JTAG interface connections* on page F-2, unless you are using the old 14-way EmbeddedICE connector or you construct a new cable.

- A maximum cable length between target board and Multi-ICE interface unit of 20cm, unless one or more of the modifications described in Chapter 6 *System Design Guidelines* is used.

- One or more ARM architecture CPUs containing supporting debug logic that is linked into a JTAG scan chain. This includes most ARM7 and ARM9 cores, the ARM1020T core, and the Intel 80200 (XScale microarchitecture) processor. It does not include the StrongARM<sup>®</sup> processors.

A full list of supported processors, including full CPUs, is provided with the installation in the file proclist.txt.

# 2.2 Connecting the Multi-ICE hardware

This section explains how to set up the hardware for Multi-ICE:

- What you require on page 2-5

- *Connection instructions* on page 2-7.

## 2.2.1 What you require

To set up the hardware you require the following items from the Multi-ICE product kit, shown in Figure 2-1 on page 2-6:

- the parallel cable, a round cable with a male D connector at each end

- the JTAG cable, a flat ribbon cable with a square *Insulation Displacement Connector* (IDC) socket at each end

- the Multi-ICE interface unit.

Depending on the type of target hardware you are using you might also require the following items:

- The supplied power adaptor, set to supply 9V to the Multi-ICE interface unit using a 2.1mm jack plug. Using this prevents Multi-ICE drawing its power from the target.

- The JTAG interface adaptor, ARM part number HPI-0027B. This is a small PCB with one 14-way and one 20-way connector mounted on it, and is available from ARM on request.

You must also provide the following items:

- a Windows workstation with an available parallel port, running an operating system supported by the Multi-ICE server (see Table 2-1 on page 2-2)

- some target hardware containing a JTAG-capable device supported by Multi-ICE (see *Target hardware requirements* on page 2-4).

## Figure 2-1 The Multi-ICE product kit

## 2.2.2 Connection instructions

You must connect the Multi-ICE interface unit to the your workstation and to the target hardware. An example is shown in Figure 2-2 on page 2-7.

## Figure 2-2 Multi-ICE interface unit cable connection

To connect the hardware together:

1. Ensure the Multi-ICE software is installed on the host machine. This is described in the section on installing the Multi-ICE software in the *Multi-ICE Installation Guide*.

- 2. Connect one end of the parallel cable to the parallel port of the host computer (variously labeled *Printer*, *Parallel*, *IEEE 1284*, or with a graphic), and the other end of the cable to the Multi-ICE interface unit.

- 3. If independent power to the Multi-ICE unit is required, for example because the target cannot supply sufficient current or because you are connecting to an already-running target, you must connect the external power supply to the Multi-ICE interface unit and switch it on.

<u>Note</u> If you are connecting Multi-ICE to hardware that is powered and running, for example to find out what is happening, refer to *Post-mortem debugging* on page 4-38.

- 4. Connect one end of the JTAG cable to the JTAG connector on the Multi-ICE interface unit, and the other end of the cable to either:

- the JTAG connector on the target board, if this is a 20-way IDC connector conforming to the Multi-ICE connection standard

- the 20-way connector on the optional JTAG interface adaptor, if the target JTAG connector is a 14-way IDC connector conforming to the EmbeddedICE Interface Unit connection standard.

If the target board has another variety of connector, see *Connecting to nonstandard hardware* on page 2-9.

The IDC sockets used for this cable are keyed using a small protrusion that must be matched up with a slot in the plug.

5. If it is not already powered up, switch on the power to the target board.

# 2.3 Connecting to nonstandard hardware

This section describes how to set up the Multi-ICE hardware when the target board does not have the ARM style 20-way IDC connector. It is split into the following sections:

- Compatibility with PID, PIE, and PIV ARM development boards on page 2-9

- Nonstandard connectors on page 2-9

- *Power supply* on page 2-10.

## 2.3.1 Compatibility with PID, PIE, and PIV ARM development boards

To use Multi-ICE with early ARM development boards, you must short the following resistors:

## ARM7TDMI® header (HHI-0016B)

Resistor R1 (only if modification box number 1 is not marked with an X).

## ARM PIV7T board (HBI-0008B)

Resistor R12.

## ARM PIE7 board (HBI-0004B)

Resistor R53.

These modifications do not make the target board incompatible with the EmbeddedICE interface unit.

—— Note ———

You must manually reset the ARM Development Board (PID) before loading and running an image because power-up does not always provide a clean reset.

## 2.3.2 Nonstandard connectors

The Multi-ICE product is supplied with cables using 20-way IDC sockets wired to the ARM standard. Plugs suitable for this connector are fitted on all current ARM development boards and several third-party target boards. Some ARM development targets, for example the ARM Development Board (PID) CPU header cards, use a 14-way socket that is signal-compatible with the new 20-way socket. An adaptor card is available from ARM on request to allow connection to these boards.

Boards made using the *Texas Instruments* (TI) JTAG interface definition use the same 14-way IDC connector as the ARM boards, but use a different signal assignment. If you think your target might use this connector (for example, if the board is made by TI), you

must check the target board reference manual *before* using Multi-ICE. An adaptor to allow Multi-ICE to connect to these boards is available from ARM free of charge on request. Quote part number HPI 0068A.

If the target you are using does not use an ARM style connector, or you are involved in designing a target board, refer to the *Multi-ICE Reference Guide* for more information.

## 2.3.3 Power supply

Power is supplied to the Multi-ICE interface unit through:

- pin 2 (**Vsupply**) on the 20-way JTAG connector, drawing current from the target power supply

- the power input jack.

The minimum target power supply voltage is 2V, and the maximum is 5V. You can calculate the approximate operating current using the formula:

$$800 \text{mA} \times \left(\frac{1.5 \text{V}}{target V}\right)^2$$

– Note ––

A graph of this function is shown in Figure 2-3 on page 2-11. On power-up, the Multi-ICE interface unit draws more current than the graph shows, and the power supply must be capable of delivering this. As a general guide, 440mA at 3.3V has been measured. If the target supply voltage or its current capability is too low, you must use the external power input jack.

You can provide power to the Multi-ICE interface unit using the power input jack from a consumer power transformer (sometimes referred to as a wall-wart). The transformer must be rated to supply between 9 and 12V at 500mA minimum. If you use the external power jack, you can connect to targets using logic voltages of 1V to 5V.

Shorting out this resistor does not affect the operation of the ARM EmbeddedICE Interface Unit, and, on target boards built by ARM Limited, does not affect the operation of the target board.

The original EmbeddedICE interface unit literature stated that the target power supply  $V_{dd}$  must have a series resistor in the feed to the JTAG interface power pin. For Multi-ICE to operate correctly from the target power supply, this resistor *must not* be present.

Figure 2-3 Multi-ICE current consumption with voltage

# 2.4 Starting the software

This section explains how to get the Multi-ICE software running. More detailed information on the software is provided in:

- Chapter 3 Using the Multi-ICE Server

- Chapter 4 Debugging with Multi-ICE .

If you have not already installed the software, do so now. Details on how to install the software are given in the *Multi-ICE Installation Guide*.

The following sections describe:

- Microsoft Windows start program menu for Multi-ICE on page 2-12

- Starting the Multi-ICE server on page 2-13

- Other Multi-ICE server startup features on page 2-15.

## 2.4.1 Microsoft Windows start program menu for Multi-ICE

After you have installed Multi-ICE on a Microsoft Windows computer, the menu items shown in Figure 2-4 are available on the Windows Programs menu. The order of items on this menu might differ from that shown.

#### Figure 2-4 Start menu items for Multi-ICE

The items are:

#### Help for Multi-ICE Server

Displays the Multi-ICE server online help files.

#### **Help for Multi-ICE**

Displays the Multi-ICE online help files.

## **Multi-ICE Server**

Runs the Multi-ICE server.

**Portmap** Runs the Portmap application, required for network access to the server.

**Readme** View the product Readme file in Windows Notepad. This contains any additional comments that are not included in the manuals.

## Setup for Multi-ICE

Runs the Multi-ICE setup program. This enables you to install additional components, repair, or remove the Multi-ICE Version 2.1 software from your workstation.

Files that have been moved from their original location, and files created in the Multi-ICE installation directory since the installation occurred, are not deleted when you remove or repair the installation.

## TAPOp Guide

Display the Multi-ICE Version 2.1 TAPOp API Reference Guide using the installed PDF file viewer.

—— Note ———

This item is only available if you have installed the PDF documentation.

**User Guide** Display the Multi-ICE Version 2.1 User Guide using the installed PDF file viewer. The user guide is also supplied as a printed manual.

— Note ——

This item is only available if you have installed the PDF documentation.

## 2.4.2 Starting the Multi-ICE server

To start the Multi-ICE server:

- 1. Ensure that:

- the Multi-ICE interface unit is plugged into the workstation

- the Multi-ICE interface unit is plugged into the target JTAG connector

- the target is powered up

- the green power light on the interface unit is glowing brightly.

For more information refer to Connecting the Multi-ICE hardware on page 2-5.

2. Select Start  $\rightarrow$  Programs  $\rightarrow$  ARM Multi-ICE v2.1  $\rightarrow$  Multi-ICE Server.

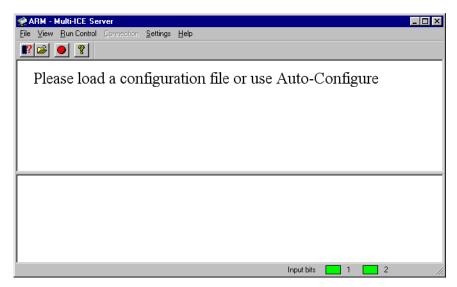

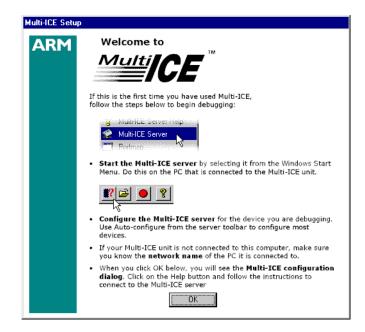

The software displays the Multi-ICE server window, shown in Figure 2-5. The portmap application might also be started and minimized, depending on the host computer configuration.

Figure 2-5 Unconfigured Multi-ICE server window

- 3. If a dialog appears informing you that the Multi-ICE hardware cannot be found, click on OK and recheck the items listed in step 1.

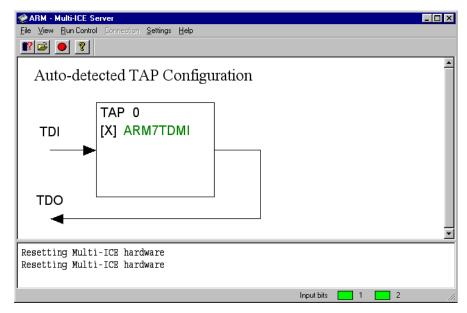

- 4. Configure the server. This can usually be done using the Autoconfiguration command. Select **File**  $\rightarrow$  **Auto-configure** and wait until the server has examined the target. If the server reports that the device is UNKNOWN then the server has to be configured manually. Refer to Chapter 3 *Using the Multi-ICE Server* for details of manually configuring the server. If the configuration works, the screen looks similar to Figure 2-6.

## Figure 2-6 Multi-ICE server window configured for an ARM7TDMI

More information on configuration and the autoconfigure command is provided in *Server configuration* on page 3-14.

## 2.4.3 Other Multi-ICE server startup features

This section includes more information about starting the Multi-ICE server.

## Using the server on a workstation without a TCP/IP stack installed

If there is no TCP/IP stack installed on the workstation when you start the Multi-ICE server for the first time, a warning message is displayed and the **Settings** item **Allow Network Connections** is automatically unchecked.

Network settings are remembered between sessions.

## Starting without hardware

You can start the Multi-ICE server software without the interface unit being connected. A message box appears containing the text:

Could not find the Multi-ICE hardware. Please check that the hardware is properly connected to the parallel port and powered up

This message is just a warning. To start using the server:

- 1. Ensure the interface unit is connected to the parallel port and to the target, and that it is powered.

- 2. Load a configuration into the server using File  $\rightarrow$  Load configuration or File  $\rightarrow$  Auto-configure.

## No network connection

In some circumstances, on machines with no network software installed or with incorrect network settings, the Multi-ICE server terminates immediately after it starts up. This means you have no opportunity to switch off the **Allow Network Connections** setting (see *Using the server on a workstation without a TCP/IP stack installed* on page 2-15 and *Settings menu* on page 3-7).

If you experience this problem, run the script Non\_tcp\_ip.reg (in the Multi-ICE installation directory) by **Open**ing it in Windows Explorer. This prevents the server trying to use the network by switching off the **Allow Network Connections** setting in the system registry.

## Starting the server minimized

You can create a shortcut icon to start the server minimized, as follows:

- 1. Right-click over the server icon and choose Create Shortcut.

- 2. Right-click over the shortcut and choose **Properties**.

- 3. Click on the **Shortcut** tab.

- 4. Select **Minimized** from the **Run** drop-down menu.

- 5. Click **OK**.

To start the server minimized, double click on the shortcut icon.

# Chapter 3 Using the Multi-ICE Server

This chapter describes how you use the Multi-ICE server. It contains the following sections:

- About the Multi-ICE server menus on page 3-2

- *Multi-ICE server device configuration files* on page 3-9

- Server configuration on page 3-14

- Using the Multi-ICE server with multiple processors on page 3-25.

# 3.1 About the Multi-ICE server menus

This section gives an overview of the menu items on the Multi-ICE server:

- *Menu structure* on page 3-2

- *File menu* on page 3-2

- *View menu* on page 3-5

- Run control menu on page 3-5

- Connection menu on page 3-6

- Settings menu on page 3-7

- *Help menu* on page 3-8.

## 3.1.1 Menu structure

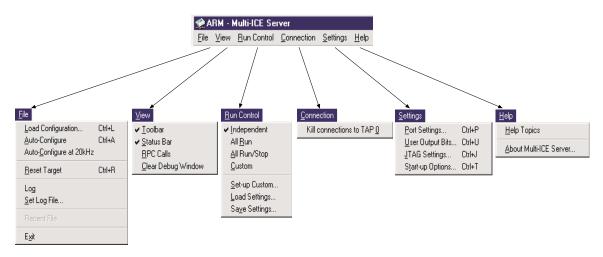

Figure 3-1 shows the submenus and their items.

## Figure 3-1 Multi-ICE server menu items

## 3.1.2 File menu

The File menu allows you to configure the Multi-ICE server and control the logging of TAPOp requests, and is shown in Figure 3-2 on page 3-3.

| Eile                        |        |  |  |

|-----------------------------|--------|--|--|

| Load Configuration          | Ctrl+L |  |  |

| Auto-Configure              | Ctrl+A |  |  |

| Auto-Configure at 20kHz     |        |  |  |

| <u>R</u> eset Target Ctrl+R |        |  |  |

| Log                         |        |  |  |

| Set Log File                |        |  |  |

| Recent File                 |        |  |  |

| Exit                        |        |  |  |

Figure 3-2 The File menu

The menu contains the following items:

#### Load Configuration

Displays a dialog box that you use to enter the name and path of a configuration file. This item is used for the manual configuration of Multi-ICE. This is described in *The IRlength.arm configuration file* on page 3-13.

#### **Auto-Configure**

Interrogates the device(s) connected to the JTAG scan chain and creates a configuration file containing what was found. See Table 3-1 for the actual frequencies used.

Table 3-1 TCK frequency for autoconfigure

| Menu entry              | TCK frequency during autoconfigure | TCK frequency in normal operation |

|-------------------------|------------------------------------|-----------------------------------|

| Auto-Configure          | 1MHz                               | 10MHz <sup>a</sup>                |

| Auto-Configure at 20kHz | 20kHz                              | 20kHz                             |

a. 1MHz for targets with more than one TAP, or for devices that are known to need a slower frequency unless adaptive clocking is used.

Autoconfiguration is described in *Automatic device configuration* on page 3-9. Unrecognized devices are marked as UNKNOWN, but you can add these to a lookup table, as described in *The IRlength.arm configuration file* on page 3-13.

## —— Note ——

If autoconfiguration of a known processor fails (showing UNKNOWN), reset the processor using a hardware reset button or a power-cycle and try the autoconfigure again.

## Auto-Configure at 20kHz

This item does the same as the Auto-Configure item, but uses a **TCK** frequency that never exceeds 20kHz. See Table 3-1 on page 3-3 for the actual frequencies used. This can be useful when the JTAG cable or the device is not capable of reliable operation at higher frequencies, or when the device might be in a sleep mode (when the slow system clock prevents the device responding sufficiently quickly to faster **TCK**s).

When manual configuration is used, the **TCK** frequencies indicated for **Auto-Configure** in Table 3-1 are used unless the configuration file specifies alternate timing parameters.

## **Reset Target**

Resets the target hardware. Clicking the **Reset Target** button in the toolbar is equivalent to selecting this menu item.

You can control the action of **Reset Target**, so that it asserts **nSRST**, **nTRST**, or both signals. (**nSRST** and **nTRST** are explained in the *Glossary*.) You can do this either from the JTAG **Settings** dialog (see *The JTAG Settings dialog* on page 3-21) or from a **Reset** section in the configuration file (see *Multi-ICE server device configuration files* on page 3-9).

You can also reset the target hardware from the debugger, using the system\_reset internal variable (see *Debugger internal variables* on page 4-30). This method asserts **nSRST**, but does not assert **nTRST**.

Log Turns remote procedure call logging on or off. When turned on, a tick is displayed next to the menu item and text describing the TAPOp protocol requests received by the server are written to a log file.

Use Set Log File to specify the filename that is used.

#### Set Log File...

Displays a dialog box that you use to enter the name and path of a log file.

- **Recent File** Displays a list of the eight most recent configuration files you have used.

- **Exit** Closes the Multi-ICE server.

#### 3.1.3 View menu

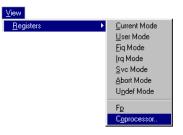

The **View** menu controls the display of the Multi-ICE server window and is shown in Figure 3-3:

## Figure 3-3 The View menu

The menu contains the following items:

**Toolbar** Turns the tool bar on or off. When the tool bar is displayed, a tick is displayed next to the menu item. The tool bar gives you quick access to the following functions:

**File**  $\rightarrow$  **Auto-Configure** attempts to automatically configure the server

**E** File  $\rightarrow$  Load Configuration prompts you for the name of a configuration file

**Output** File  $\rightarrow$  Reset Target resets the target using **nTRST** or **nSRST** or both

**Provide Set Weight Representation**  $\mathbb{P}$  **Help Topics** displays the Multi-ICE online help.

- **Status Bar** Turns the status bar on or off. When the status bar is displayed, a tick is displayed next to the menu item. The **Status** bar displays information on the current state of Multi-ICE.

- **RPC Calls** Turns the debug window on or off. When the debug window is active, a tick is displayed next to the menu item and all the TAPOp requests are displayed in the debug window.

#### **Clear Debug Window**

Clears all text in the debug window.

#### 3.1.4 Run control menu

The **Run Control** menu controls the synchronized stopping and starting of multiple cores and is shown in Figure 3-4.

## Figure 3-4 The Run Control menu

The menu contains the following items:

| Independent                                                                              | Makes all configured devices behave independently. There is no interaction between devices.                                                                                                                                 |  |

|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| All Run                                                                                  | Starts all devices as close to simultaneously as the hardware allows.                                                                                                                                                       |  |

| All Run/Stop                                                                             | Makes all configured devices:                                                                                                                                                                                               |  |

|                                                                                          | • run when all connected debuggers have indicated that their processor can start                                                                                                                                            |  |

|                                                                                          | • stop if any one of the devices stop.                                                                                                                                                                                      |  |

| Custom                                                                                   | Makes configured devices interact as you have specified using the <b>Set-up Custom</b> action.                                                                                                                              |  |

| Set-up Custom                                                                            | Displays a dialog that enables you to specify the way in which devices interact. See <i>Setting up interaction between devices</i> on page 3-28 and <i>Setting up the poll frequency</i> on page 3-30 for more information. |  |

| Load Settings                                                                            | Displays a dialog box that enables you to load run control settings previously saved using <b>Save Settings</b> .                                                                                                           |  |

| Save Settings                                                                            | Displays a dialog box that enables you to save the run control settings to a file.                                                                                                                                          |  |

| The items on this menu are described in detail in the section Using the Multi-ICE server |                                                                                                                                                                                                                             |  |

The items on this menu are described in detail in the section *Using the Multi-ICE server* with multiple processors on page 3-25.

## 3.1.5 Connection menu

The **Connection** menu lists all TAP controllers in use and gives you the option to kill connections individually, and is shown in Figure 3-5.

#### Figure 3-5 The Connection menu

—— Caution ———

Only kill connections when other attempts to disconnect the client have failed.

Killing a connection between the server and an active client can result in the client crashing or exhibiting other undesirable behavior.

#### 3.1.6 Settings menu

The **Settings** menu allows you to configure the way the server uses the JTAG port, and is shown in Figure 3-6.

| Settings         |           |        |

|------------------|-----------|--------|

| Port Se          | ttings    | Ctrl+P |