F. MORANCHO

# **THÈSE**

#### En vue de l'obtention du

#### DOCTORAT DE L'UNIVERSITE DE TOULOUSE

Délivrée par : l'Université Toulouse III - Paul Sabatier

Discipline ou spécialité : Conception de Circuits Microélectroniques et Microsystème

#### Présentée et soutenue par Moustafa ZERARKA

Le 19 juillet 2013

Étude des régimes extrêmes de fonctionnement en environnement radiatif des composants de puissance en vue de leur durcissement pour les applications aéronautiques et spatiales

#### **JURY**

Président

Professeur, UPS, Toulouse

| C. SCHAEFR | Professeur, IPG, Grenoble               | Rapporteur         |

|------------|-----------------------------------------|--------------------|

| H. MOREL   | Directeur de Recherche, INSA, Lyon      | Rapporteur         |

| D. FLORES  | Professeur, CSIC, Barcelone             | Examinateur        |

| A. TOUBOUL | Maître de Conférences, IES, Montpellier | Examinateur        |

| M. BAFLEUR | Directrice de Recherche, LAAS, Toulouse | invitée            |

| P. AUSTIN  | Professeur, UPS, Toulouse               | directeur de thèse |

Ecole doctorale : GEET Unité de recherche : LAAS-CNRS Directeur de thèse : Patrick AUSTIN

Àmon père Abedelkader à ma mère Fohra À mes sœurs Nacira, Oumelkhier et Djahida À mes frères Abdelhadi et Omar Àma femme Khadidja

#### Remerciements

Les travaux présentés dans ce mémoire ont été effectués au sein du groupe Intégration des Systèmes de Gestion de l'énergie (ISGE) du Laboratoire d'Analyse et d'Architecture des Systèmes (LAAS) du Centre National de la Recherche Scientifique (CNRS) à Toulouse, dans le cadre de projet EPOPE « Effects of Particles On Power Electronics » financés par le centre de recherche "EADS Innovation Works" (IW) du groupe EADS.

À l'issue de cette thèse, je souhaite tout d'abord remercier Messieurs CHATILA, SANCHEZ et ARLAT directeurs successifs du LAAS pour m'avoir accueilli au sein du Laboratoire. Je tiens aussi à remercier Madame Marise BAFLEUR et Monsieur Frédéric MORANCHO, responsables successifs du groupe ISGE, de m'avoir ouvert les portes de leur équipe et permis d'entreprendre cette étude. Je tiens à remercier également Monsieur Alain CAZARRE directeur de l'école doctorale Génie Electrique, Electronique, Télécommunications (GEET).

Je remercie tout particulièrement Monsieur Patrick AUSTIN qui a dirigé ces travaux pour ses qualités scientifiques et pédagogiques, pour sa confiance et son soutien. En plus, ses qualités humaines, son sens de l'humour et sa bonne humeur font qu'il est toujours agréable à côtoyer et travailler avec lui. Je lui adresse, par ces quelques mots, ma plus profonde gratitude.

Je remercie énormément Messieurs Christian SCHAEFFER et Hervé MOREL pour avoir accepté d'être les rapporteurs de mes travaux de thèse. Je remercie également les membres du jury, Messieurs David FLORES, Antoine TOUBOUL et Monsieur Frédéric MORANCHO qui m'a fait l'honneur de présider le jury de ma thèse.

J'exprime tous mes remerciements et ma sympathie à Gaëtan TOULON pour avoir suivi et participé à mes travaux. Les discussions scientifiques que nous avons pu avoir durant toutes ces années ont toujours été très enrichissantes pour moi. Je tiens vraiment à lui exprimer ma profonde reconnaissance pour le temps qu'il a consacré pour corriger et finaliser ce travail dans les bonnes conditions.

Un grand merci à Mesdames Marise bafleur, Josiane TASSILI et Karine ISOIRD ainsi que Monsieur frédéric MORANCHO qui ont suivi de près mes travaux et qui ont toujours pris le temps de répondre à mes questions et corriger soigneusement les articles qu'on a fait ensemble.

Je voudrais également remercier et exprimer mon amitié à Houssem HARBESS et Hakim TAHIR, les premiers qui m'ont appris à construire une jonction P/N sous Sentaurus, pour leurs aides pertinents dans ce travail, par l'échange d'informations, les discussions instructives et par l'entraide sur tous les plans sans oublier les agréables moments familiaux et l'ambiance folle des petits adorables Tarik et Wafa.

Je remercie particulièrement Monsieur Henri SCHNIDER avec qui j'ai commencé mon aventure au LAAS, C'était très agréable de mener le stage de MASTER2 avec toi. Merci pour la qualité d'encadrement qui m'a donné l'envie de continuer dans la recherche, merci pour tes conseilles et surtout ta gentillesse.

Je souhaite remercier vivement toute l'équipe ISGE pour son bienveillance et son soutien durant ces années; Magali BRUNET, Abdelhakim BOURENNANE, Patrick TOUNSI,... sans oublier l'aimable secrétaire du groupe Madame Claude LAFORE.

Je remercie tous le service du personnel du LAAS en particulier Camille CAZENEUVE pour leurs soutiens administratifs durant la thèse.

Je tiens aussi à saluer et remercier mes collègues et amis du laboratoire dont bon nombre a d'ailleurs quitté le laboratoire : Youcef GHERFI, abedelilah ELKHADIRI, Abedenour AOUINA, Fahed BETAHER, Chafe CHABALA, Hamza BOUKABACH, Sylvain NOBLECOURT, Emanuel, Yoann CHARLON, Mehdi BRAHAMI, Lyamine HIDJAZI, Youcef ZATOUT, Mourad BENKACI, Sami HEBIB, Hamada METMAT, Mohamed LALAMI, Amin BOUKADJAR, Farouk ZAHAR, Aymen, Nadia BELAID, Hamida, Sabeha ZEDEK, Asma, Amel ALI SLIMAN, Ali KARA, Djaffar BELHARET, Ibrahim Albluwi, Ahmed DAROUICHE .... merci beaucoup pour les bons moments que nous avons passé ensembles.

Je tiens à exprimer mon amitié à lyes DjAGHLAF (croco de ponsan), à mes deux anciens colocataires les deux BOURENNANE Walid et Imad ainsi qu'à Toufik AZOUI (ghoulba) sans oublier Bilal ALMASRI avec lesquels j'ai passé des aventures et des moments inoubliables, merci pour l'entraide sur tous les plans, vous étiez toujours présent dans les moments difficiles. A propos de ces moments j'aimerais également saluer et remercier infiniment Abedennasser HAMIDI d'avoir pris soin de moi durant toute ma convalescence (merci encore !)

Je tiens aussi à remercier nos amis d'ALSAT Aissa BOUTTE, Salah eddine BENTATA, Hichem HENNA et Mahmoud pour les agréables moments que nous avons passé ensembles, merci encore à Aissa de m'accueillir si chaleureusement à ma 1ere arrivée ici à Toulouse et de bien m'orienter pour toutes mes premières démarches, merci pour ton soutiens durant toutes ces années.

Je remercie énormément ma femme pour sa patience et son soutien durant ces deux dernières années de la thèse.

Enfin, les mots manquent au remerciement auprès de ceux qui nous donnent toujours du bonheur, ma mère, mon père, mes sœurs et mes frères, je vous adresse, par ces quelques mots, ma plus profonde reconnaissance et gratitude pour vos encouragements, votre patience, votre soutien et tous ce que vous avez fait pour moi depuis mon premier pas à l'école jusqu'à ce jour.

## Table des matières

| Liste des s | symboles                                                               | 5  |

|-------------|------------------------------------------------------------------------|----|

| Liste des l | Figures                                                                | 7  |

| Introduct   | Introduction générale                                                  |    |

| _           | I. L'environnement radiatif naturel et son effet sur les composants de | _  |

| •••••       |                                                                        | 17 |

| 1 Introd    | uction                                                                 | 19 |

| 2 Les co    | omposants de puissance                                                 | 19 |

| 2.1         | Le transistor MOS de puissance                                         | 20 |

| 2.2         | L'IGBT                                                                 | 22 |

| 3 L'env     | ironnement radiatif naturel                                            | 24 |

| 3.1         | Rayonnement cosmique                                                   | 24 |

| 3.2         | Effet du soleil                                                        | 25 |

| 3.2.1       | Les éruptions solaires                                                 | 25 |

| 3.2.2       | Le vent solaire                                                        | 26 |

| 3.2.3       | Cas représentatifs (GOES-5 et GOES-7)                                  | 27 |

| 3.3         | Environnement spatial proche de la terre                               | 27 |

| 3.3.1       | Magnétosphère                                                          | 27 |

| 3.3.2       | Les ceintures de radiation                                             | 28 |

| 3.3.3       | Cas représentatifs (Hipparcos)                                         | 30 |

| 3.4         | Récapitulatif des particules présentes dans l'environnement spatial    | 30 |

| 3.5         | Environnement atmosphérique                                            | 31 |

| 4 Interac   | ction rayonnement - matière                                            | 33 |

| 4.1         | Interaction neutron, proton - silicium                                 | 34 |

| 4.2         | Interactions ion-silicium                                              | 35 |

| 5  | Notion   | de Pouvoir d'Arrêt et de Transfert d'Energie Linéique                            | 36 |

|----|----------|----------------------------------------------------------------------------------|----|

| 6  | Notion   | ı de range                                                                       | 37 |

| 7  | Répart   | ition spatiale et temporelle de la trace d'ionisation                            | 37 |

| 8  | Effets   | des rayonnements sur les MOSFET de puissance                                     | 38 |

| 8  | .1       | Effets de dose                                                                   | 38 |

| 8  | .2       | Les Evénements Singuliers (SEE)                                                  | 39 |

|    | 8.2.1    | Single Event Burn-out (SEB)                                                      |    |

|    | 8.2.2    | Single Event Gate Rupture (SEGR)                                                 | 41 |

|    | 8.2.3    | Single Event Latch-up (SEL)                                                      | 42 |

| 9  | Représ   | sentation de la sensibilité radiative                                            | 43 |

| 10 | Etat de  | e l'art sur les phénomènes du Single Event Burn-out et Single Event Latch-up     | 44 |

| 1  | 0.1      | Le burn-out                                                                      | 44 |

| 1  | 0.2      | Le latch-up                                                                      | 52 |

| 11 | Con      | clusion                                                                          | 55 |

| Ch | apitre I | I. Etude comportementale de déclenchement du SEB dans les composants d           | le |

| pu | iissance | ***************************************                                          | 57 |

| 1  | Introdu  | uction                                                                           | 59 |

| 1  | Descri   | ption des outils des simulations TCAD et du véhicule test de simulation          | 59 |

| 1  | .1       | L'outil de simulations 2D TCAD                                                   | 59 |

| 2  | Compa    | araison des résultats SILVACO/SENTAURUS                                          | 63 |

| 2  | .1       | Recherche du volume sensible et des critères de déclenchement                    | 64 |

| 3  |          | rche du volume sensible et critères de déclenchement pour différente technologie |    |

| pa | r simula | tion TCAD-2D                                                                     | 69 |

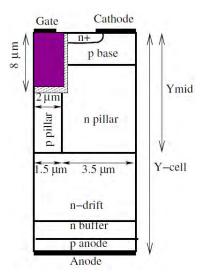

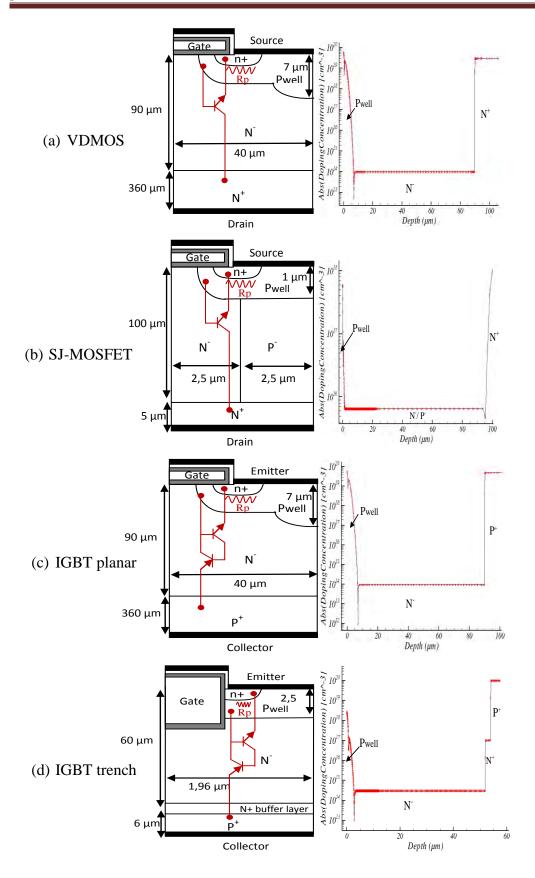

| 3  | .1       | Véhicule test de simulation                                                      | 69 |

| 3  | .2       | Conditions des simulations                                                       | 71 |

| 3               | .3      | Analyse des résultats de simulation pour le VDMOS et SJ-MOSFET                | 72      |

|-----------------|---------|-------------------------------------------------------------------------------|---------|

|                 | 3.3.1   | Effet de la position d'impact                                                 | 72      |

|                 | 3.3.2   | Effet de la profondeur de l'impact                                            | 72      |

|                 | 3.3.3   | Effet du range de l'ion                                                       | 74      |

|                 | 3.3.4   | Analyse des résultats pour différentes polarisations V <sub>DS</sub>          | 78      |

| 3               | .4      | Analyse des résultats de simulation pour l'IGBT planar et l'IGBT trench       | 80      |

|                 | 3.4.1   | Effet de la position d'impact                                                 | 80      |

|                 | 3.4.2   | Effet de la profondeur d'impact                                               | 81      |

|                 | 3.4.3   | Effet du range de l'ion                                                       | 82      |

|                 | 3.4.4   | Analyse des résultats pour différentes polarisations V <sub>CE</sub>          | 84      |

| 3               | 5.5     | Traces ionisantes horizontales générées au sein de l'épitaxie                 | 89      |

| 3               | .6      | Synthèse des résultats (MOSFETs / IGBTs)                                      | 91      |

| 3               | .7      | Effet de la température                                                       | 95      |

| 4<br><b>C</b> h |         | II. Solutions de durcissement des composants de puissance                     |         |

| 1               | Introdu | nction                                                                        | 101     |

| 2               | Phénoi  | nènes physiques lors d'un court-circuit dans un IGBT                          | 101     |

| 3               | Différe | entes approches de durcissement                                               | 102     |

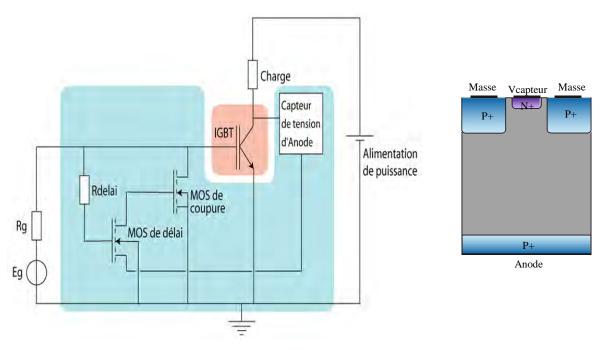

| 3               | .1      | Approche circuit (Circuits de protection rapprochée contre les courts-circuit | s). 102 |

|                 | 3.1.1   | Circuits basés sur la détection d'une surtension                              | 102     |

|                 | 3.1.2   | Circuits basés sur la détection de surintensité                               | 106     |

| 4               | Appro   | che design                                                                    | 107     |

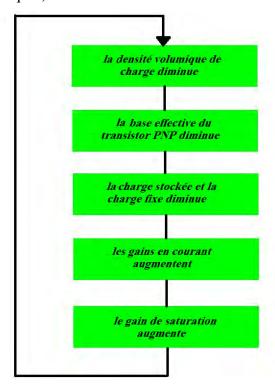

| 4               | .1      | Rappel sur le fonctionnement parasite de l'IGBT                               | 107     |

| 4               | 2       | Augmentation du niveau de courant de latch-up                                 | 108     |

| 4               | 3       | Structures IGBT proposées                                                     | 111     |

|                 | 4.3.1   | Description des structures                                                    | 111     |

|                 | 4.3.2   | Sensibilités des structures étudiées                                          |         |

|                 | 4.3.2   | Sensionnes des structures étudiées                                            | 113     |

| (VDMO       | S/IGBT)                                                                  | 118 |

|-------------|--------------------------------------------------------------------------|-----|

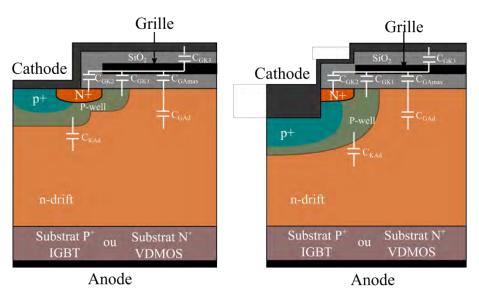

| 4.4.1       | Principe de la structure                                                 | 118 |

| 4.4.2       | Influence des paramètres de la tranchée                                  | 119 |

| 4.4.3       | Comportement dynamique                                                   | 124 |

| 4.4.4       | Sensibilité contre les ions lourds de la structure à cathode en tranché. | 128 |

| 4.4.5       | Etude préliminaire en vue d'une réalisation technologique                | 134 |

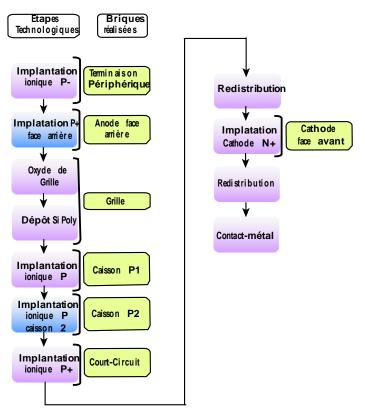

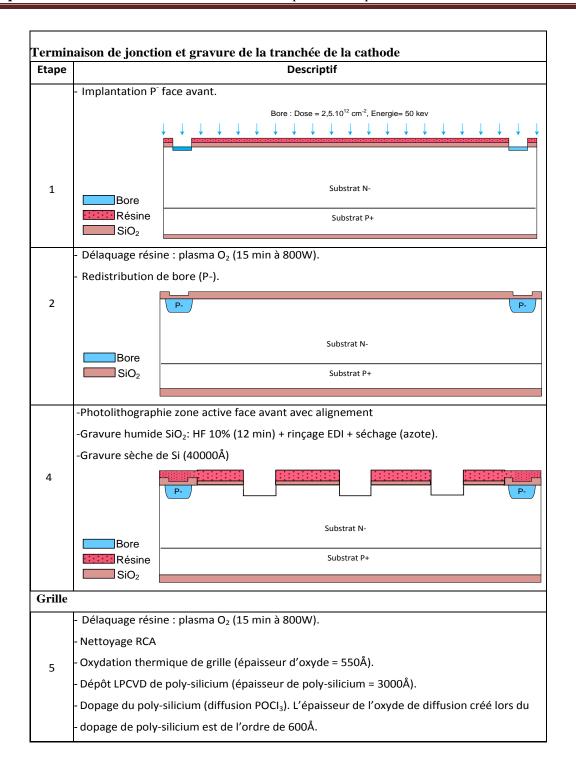

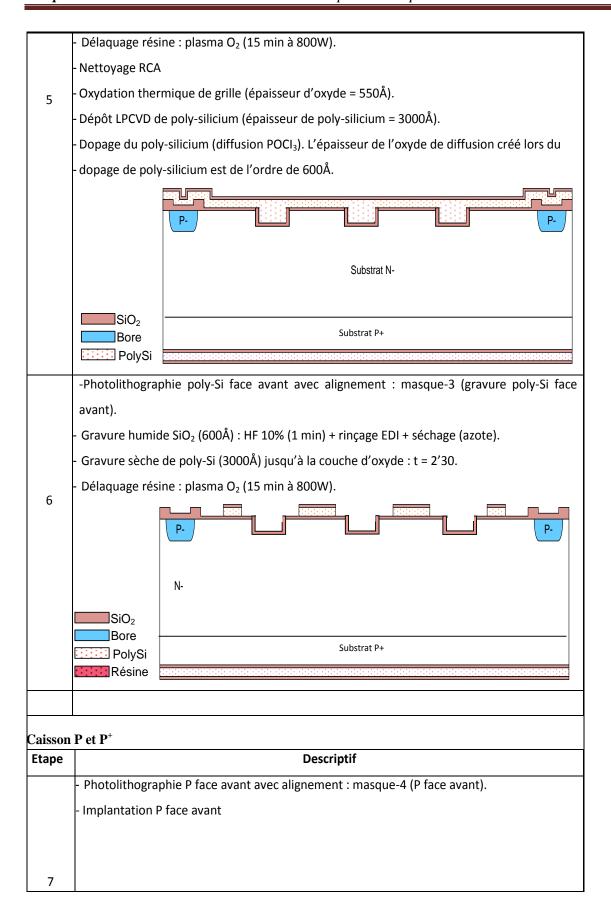

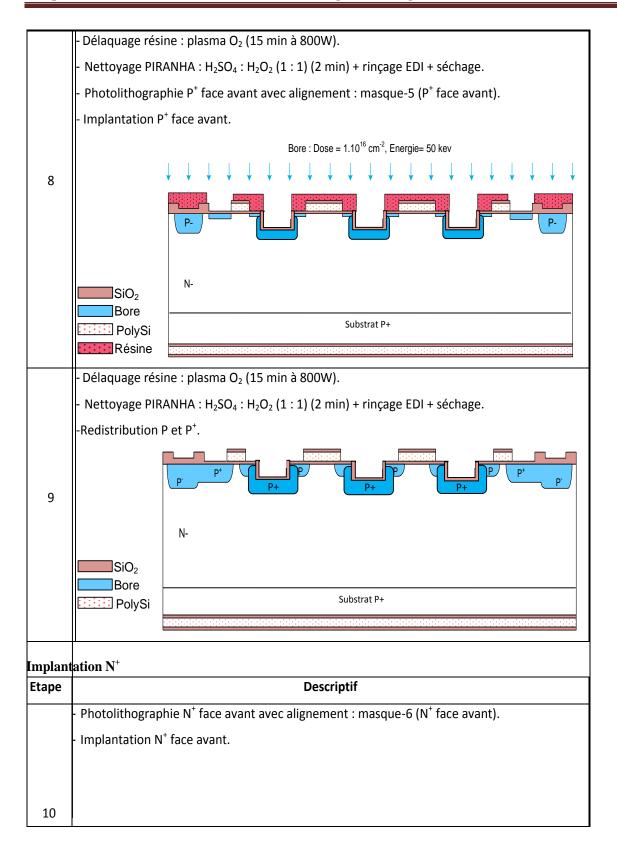

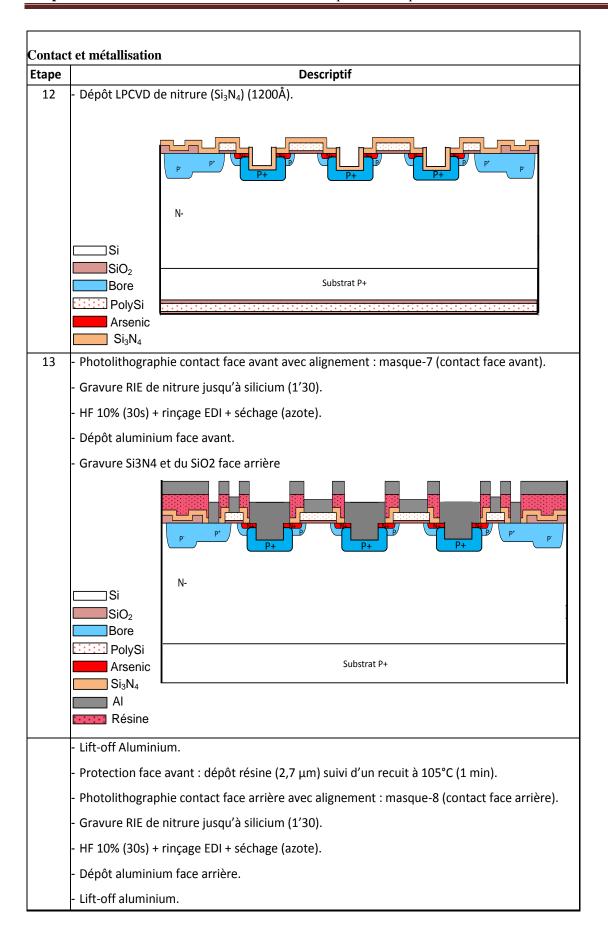

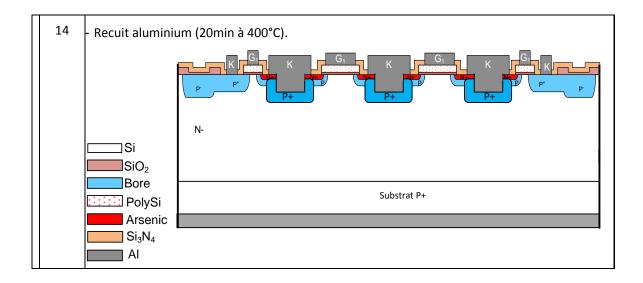

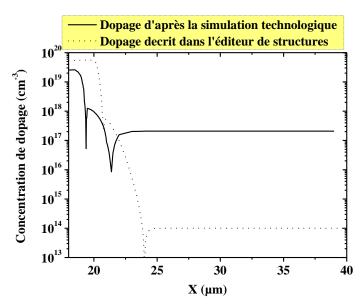

| 2.4         | 4.5.1 Présentation et description de la filière flexible                 | 134 |

| 2.4         | 4.5.2 Procédé technologique proposé                                      | 135 |

| 5 Concl     | usion                                                                    | 141 |

| Conclusio   | on générale                                                              | 143 |

| Bibliogra   | phies                                                                    | 149 |

| Liste des ] | publications                                                             | 157 |

| Résumé      |                                                                          | 159 |

| Abstract.   |                                                                          | 160 |

## Liste des symboles

CAK Capacité interélectrode collecteur - cathode

CCE Capacité interélectrode collecteur - émetteur

CDS Capacité interélectrode source - drain

CGA Capacité interélectrode grille – anode

CGC Capacité interélectrode grille – collecteur

CGD Capacité interélectrode grille – drain

CGE Capacité interélectrode grille – émetteur

С CGK Capacité interélectrode grille – cathode

CGK1 Capacité d'oxyde mince de la zone de canal

Сдк2 Capacité de déplétion entre la grille et le N+ de cathode

CGK3 Capacité due à la présence d'oxyde épais entre grille et cathode

CGs Capacité interélectrode grille – source

DMOS Double Diffused Metal Oxide Semiconductor

E champ électrique

E Energie de l'ion incident

Ec Valeur du champ électrique critique

EES Effets d'Evénements Singuliers

Eox épaisseur de l'oxyde

GLET: Energie de Transfert Linéaire

GTO Gate Turn-Off Thyristor

IA Courant d'anode

Ic Courant de collecteur

In Courant de drain

IG Courant du générateur de grille

*IGBT* Insulated-Gate Bipolar Transistor

JFET Junction Field Effect Transistor

LDMOS Lateral Double diffusé Metal Oxide Semiconductor

$L_{EI}$  longueur contenant l'émetteur  $N^+$

$L_{E2}$  longueur contenant l'émetteur N<sup>+</sup> et la région de diffusion P<sup>+</sup>

LET Linear Energy Transfer (transfert d'énergie linéique)

$L_T$  largeur de la tranchée

MOS Metal Oxide semiconductor

MOSFET Metal Oxide Semiconductor Field Effect Transistor

NPT Non-Punch-Through

PT Punch-Through

R(w) variation spatiale du taux de génération

$R_{ON}$  la résistance à l'état passant

Rp résistance de la région P sous la diffusion N<sup>+</sup> de cathode

SEB Single Event Burnout

SEE Single Event Effect

SEGR Single Event Gate Rupture

SEL Single Event Latchup

SEU Single Event Upset

SJ Superjunction

SOA Safe Operating Area

T(t) variation temporelle du taux de génération

TCAD Technology Computer Aided Design

Vaк Tension cathode – anode

VBE Tension émetteur – base

Vce Tension émetteur – collecteur

VDMOS Vertical Double Diffused MOS

V<sub>DS</sub> Tension source – drain

V<sub>G</sub>к Tension cathode – grille

V<sub>G</sub>s Tension source – grille

$W_T$  profondeur de la tranchée de la structure proposée

$X_{P+}$  profondeur de jonction de la région de diffusion  $P^+$

## Liste des Figures

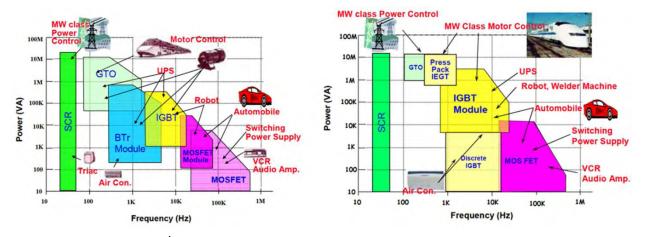

| Figure 1-1: Évolution de la gamme d'utilisation des composants de puissance                                    | 20          |

|----------------------------------------------------------------------------------------------------------------|-------------|

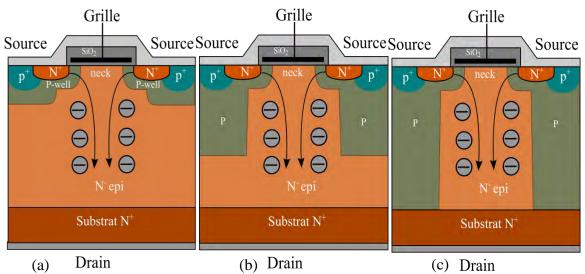

| Figure 1 - 2 : Coupe verticale d'un transistor MOSFET. VDMOS (a), SSJMOS (b), SJMOS (c)                        | 22          |

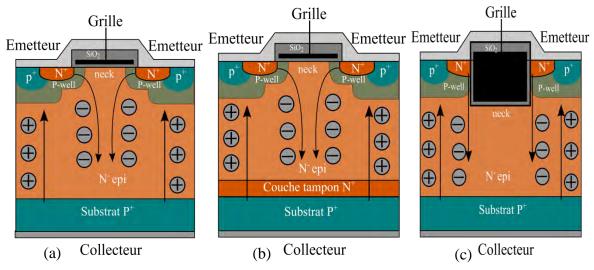

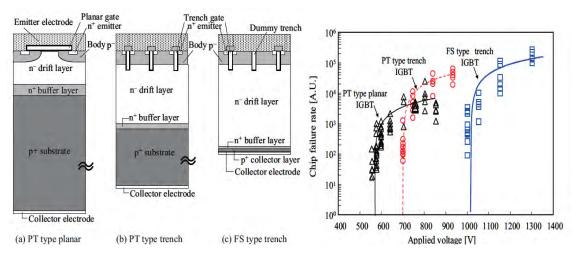

| Figure 1-3: Coupe verticale d'un transistor IGBT. IGBT NPT (a), IGBT PT (b) et IGBT trench (c)                 | 24          |

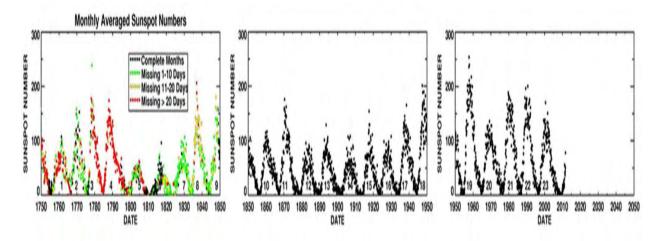

| Figure 1-4: Nombre de tâches solaires depuis 1750 et jusqu'à 2012[SOLA-12]                                     | 25          |

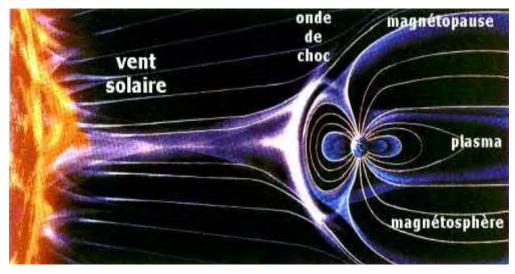

| Figure 1-5: Représentation de la déformation de la magnétosphère exercée par le vent solaire                   | 27          |

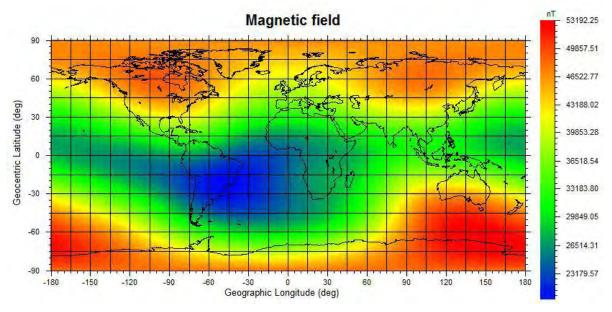

| Figure 1-6: Carte de rigidité de coupure verticale (en Giga Volts)                                             | 28          |

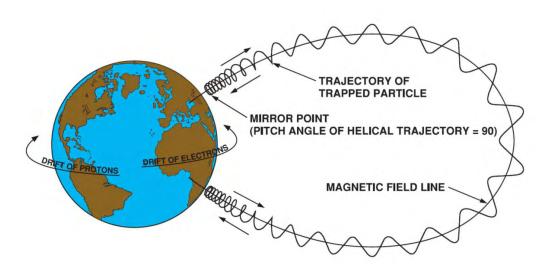

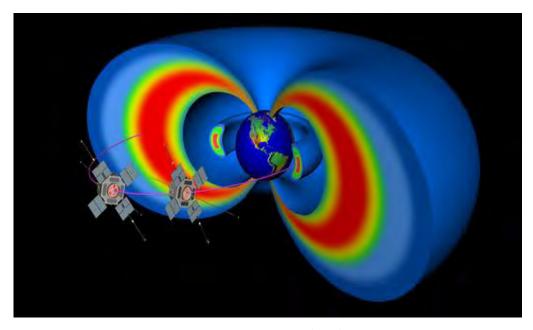

| Figure 1-7: Mouvement des particules piégées dans la magnétosphère terrestre (d'après [STASS-88])              | 29          |

| Figure 1-8: Les ceintures de radiations                                                                        | 30          |

| Figure 1-9 : Effet des radiations spatiales sur la magnétosphère et ses déformations sous l'interaction ave    | c le vent   |

| solaire [LUU-09]                                                                                               | 31          |

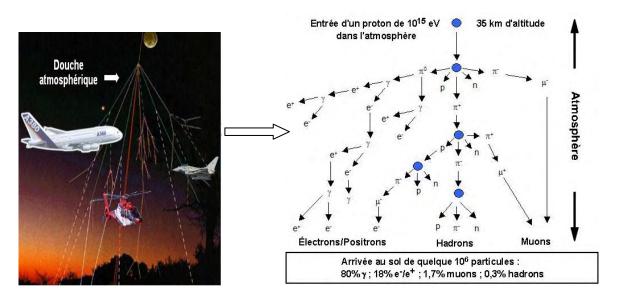

| Figure 1- 10 : Gerbe atmosphérique liée à l'interaction d'une particule ionisante avec la haute atmosphère     | 32          |

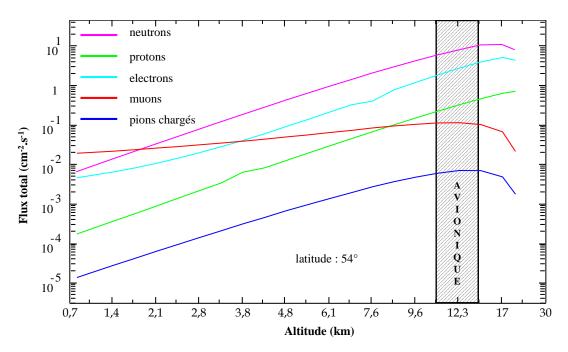

| Figure 1-11: Flux total des particules se trouvant dans l'atmosphère en fonction de leur altitude [BRIE-71]    | ] 33        |

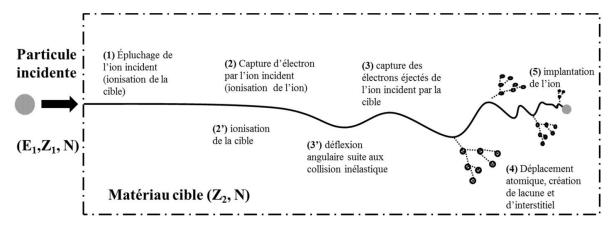

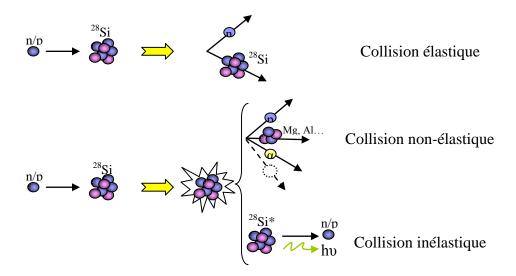

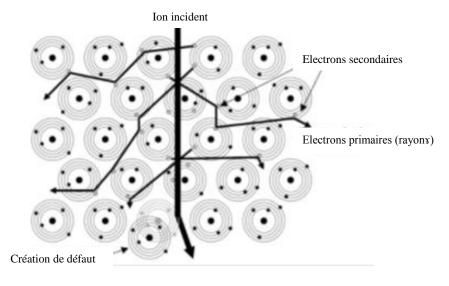

| Figure 1- 12 : Parcours et les différents mécanismes d'interactions d'une particule énergétique dans la mati   | ère 34      |

| Figure 1- 13 : Représentation schématique des deux catégories d'interactions nucléaires                        | 35          |

| Figure 1- 14: Interaction ion-silicium [HUBE-01]                                                               | 35          |

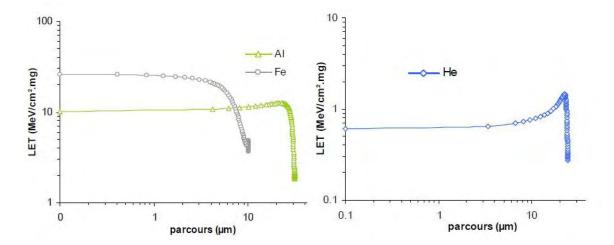

| Figure 1- 15: Profil de pouvoir ionisant pour trois ions. A gauche: Ion aluminium (Al), Ion Fer (Fe); A co     | droite, Ion |

| alpha (He) avec observation du pic de Bragg. [LUU-09]                                                          | 36          |

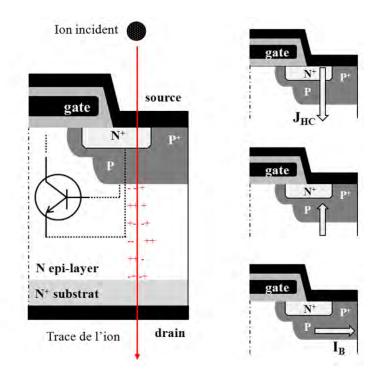

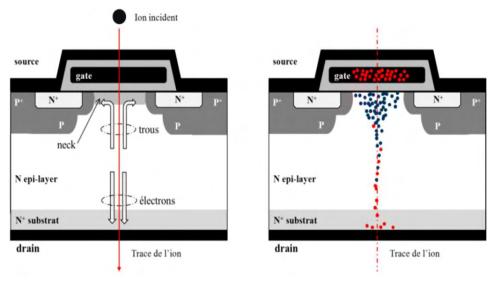

| Figure 1- 16 : Mécanismes de déclenchement du SEB.                                                             | 41          |

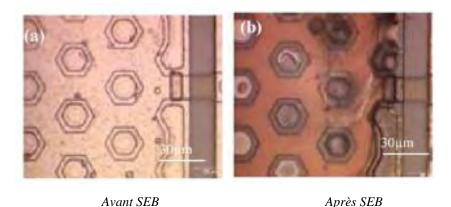

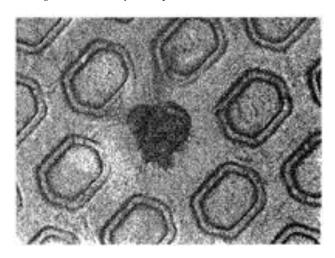

| Figure 1- 17: Single Event Burnout dans une MOSFET                                                             | 41          |

| Figure 1- 18 : Mécanismes de déclenchement du SEGR.                                                            | 42          |

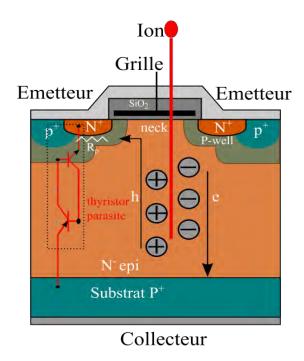

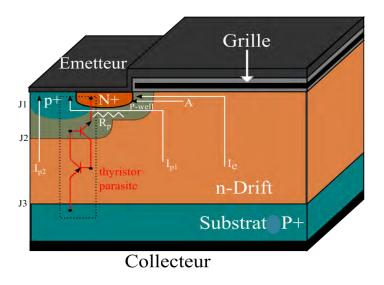

| Figure1- 19: Thyristor parasite dans un IGBT NPT                                                               | 43          |

| Figure 1-20: Single event latchup dans les IGBTs [LORF-99]                                                     | 43          |

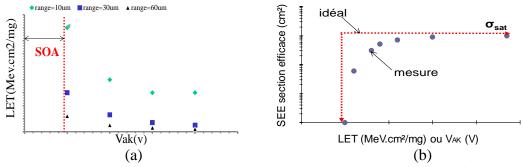

| Figure 1-21: Safe Operating Area (SOA) (a) et section efficace pour un ion incident (b) pour un ion donné      | śe 44       |

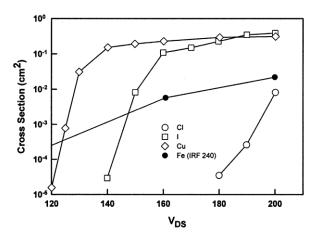

| Figure 1-22: SEB sections transversales en fonction de la tension drain-source V, pour un transistor MC        | OSFET de    |

| puissance 2N6766.                                                                                              | 45          |

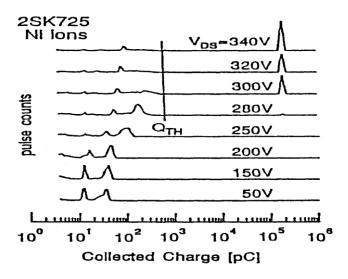

| Figure 1 - 23 : Collection de charge d'un burnout mesurée à l'aide d'un système d'analyseur de hauteur         | de pulses   |

| couplé avec un amplificateur sensible.                                                                         | 48          |

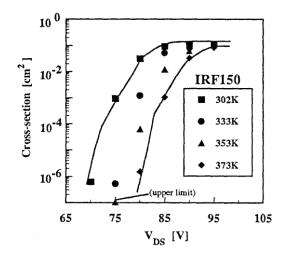

| Figure 1 - 24 : Dépendance de SEB sur la température [JOHN-92]                                                 | 48          |

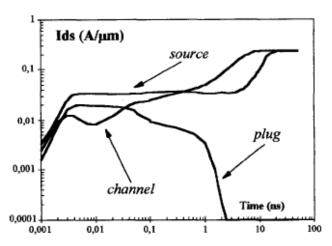

| Figure 1 - 25 : Résultat de la simulation d'une seule cellule. variations de courant à                         | points      |

| d'impact différents pour un ion Br de 180 MeV [ROUB-93].                                                       | 49          |

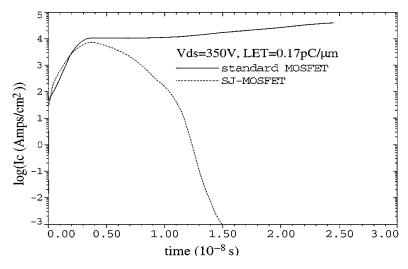

| Figure 1 - 26 : Variation de la densité de courant du collecteur en fonction de temps pour un MOSFET stand     | dard et un  |

| MOSFET à super jonctions [HUAN-00]                                                                             | 50          |

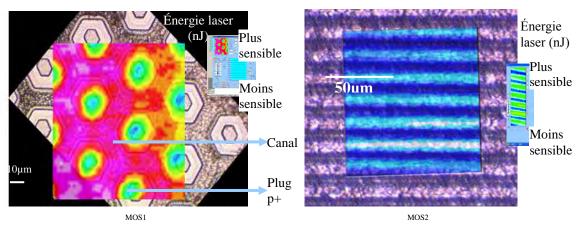

| Figure 1 - 27 : Superposition de la cartographie laser face arrière et de la photo de sa face avant correspond | lante pour  |

| 2 types de MOS [Luu-08]                                                                                        | 51          |

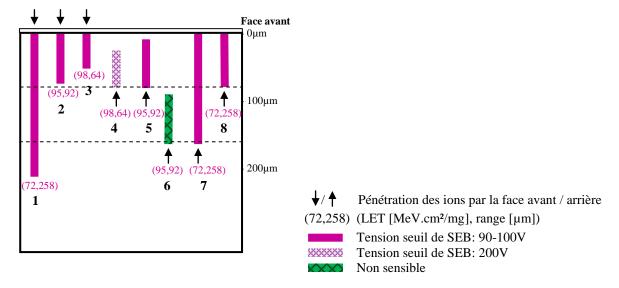

| Figure 1-28 : Schéma des traces d'ionisation pénétrant par la face avant ou arrière dans une cellule           | MOSFET      |

| d'IRF830A pour différentes épaisseurs de substrat.                                                             | 52          |

| Figure 1 - 29 : Comparaison d'immunité au latchup entre (a) ALL, (b) carré et (c) hexagonales (les flèches     | indique le  |

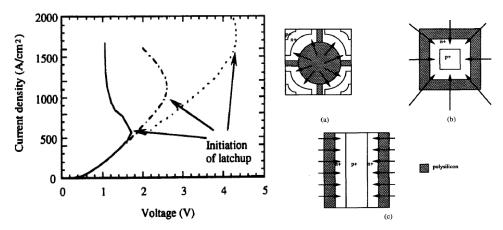

| flux du courant des trous)                                                                                     | 53          |

| Figure 1-30 : Modifications proposées sur la diffusion P+ de l'émetteur par Lorfevre [LORF-99]                 | 54          |

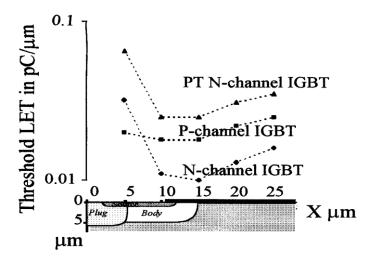

| Figure 1- 31 : Simulations du LET seuil SEL en fonction de la position d'impact de l'ion en surfac             | e pour 3    |

| technologies d'IGBT: à canal N PT et NP et à canal P NPT                                                       | 54          |

| Figure 1- 32 : Taux de défaillance SEB en fonction de la tension appliquée pour différent technologie          | e d'IGBT    |

| [NISH-10]                                                                                                      | 54          |

| Figure1- 33 : Structure Semi-SJ IGBT                                                                                                                                      | 5 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

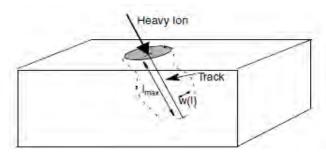

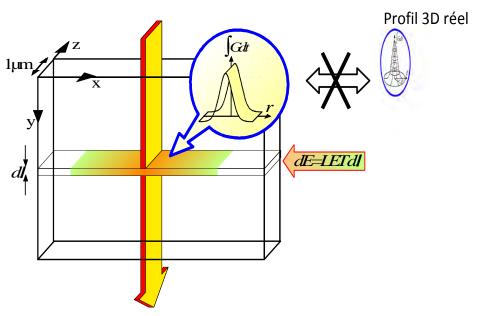

| Figure 2- 1: Paramètres d'un ion lourd pénétrant un semi-conducteur [SENT-09]                                                                                             | 2 |

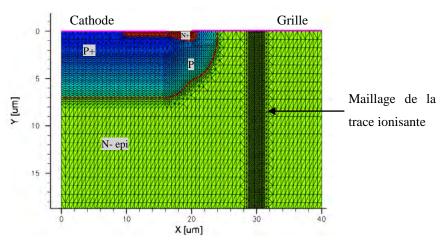

| Figure 2- 2: Représentation de maillage de la zone active de la demi-cellule d'IGBT planar simulé                                                                         |   |

| Figure 2- 3 : Allure de la trace d'ionisation pour des simulations 2D [LORF-99]                                                                                           |   |

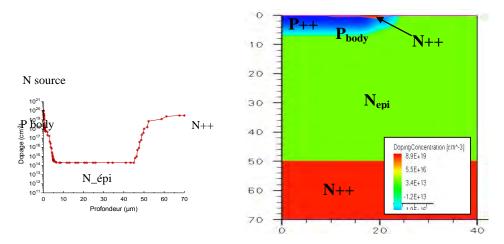

| Figure 2- 4: Profil de dopage de la cellule de MOSFET simulée en fonction de la profondeur (SILVACO). Section                                                             |   |

| perpendiculaire de la cellule à travers la source, le corps P, la zone épitaxiée et le substrat N++ (gauche), image de la demi                                            |   |

| cellule simulée avec ses niveaux de dopage (SENTAURUS) (droite)                                                                                                           |   |

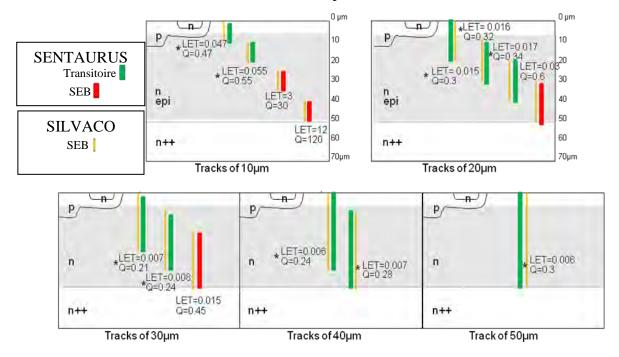

| Figure 2- 5: Schématisation de traces ionisantes dans la demi-cellule de MOSFET polarisée à 500V et simulée                                                               |   |

| par SILVACO et SENTAURUS                                                                                                                                                  |   |

| Figure 2- 6: Schématisation de traces ionisantes dans la demi-cellule de MOSFET polarisée à 500V. Les traces son                                                          |   |

| positionnées à la même abscisse x mais à différentes profondeurs et sont simulées chacune indépendamment                                                                  |   |

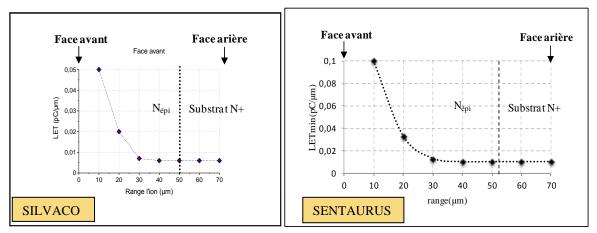

| Figure 2- 7: LET minimal provoquant un SEB en fonction du range de l'ion arrivant en incidence normale sur la                                                             |   |

| face avant de la cellule VDMOS simulé par SILVACO (à gauche) et par SENTAURUS (à droite)                                                                                  |   |

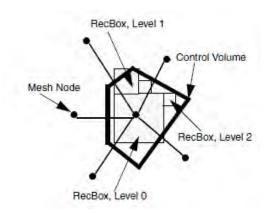

| Figure 2- 8: Exemple de zones rectangulaires [SENT-09]                                                                                                                    |   |

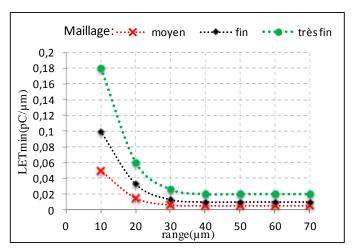

| Figure 2- 9: LET minimal provoquant un SEB en fonction du range de l'ion arrivant en incidence normale sur l                                                              |   |

| face avant de la cellule VDMOS simulé avec différent niveau de maillage                                                                                                   |   |

| Figure 2- 10: Figure demi-cellules simulées avec leurs dimensions géométriques (à gauche), profil de dopage d                                                             |   |

| chaque cellule simulée en fonction de la profondeur (à droite).                                                                                                           |   |

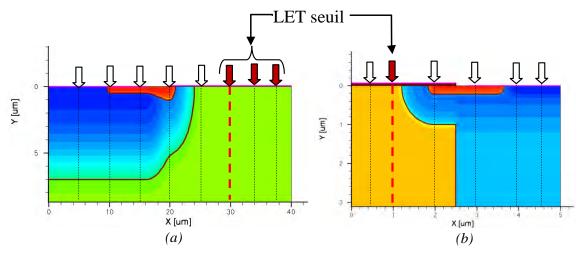

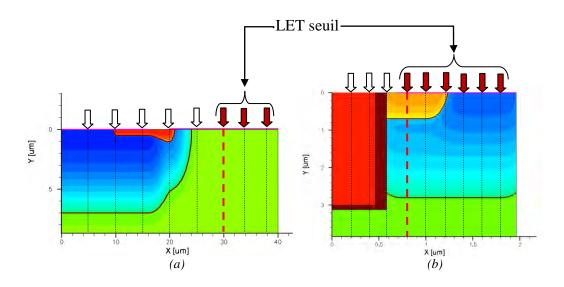

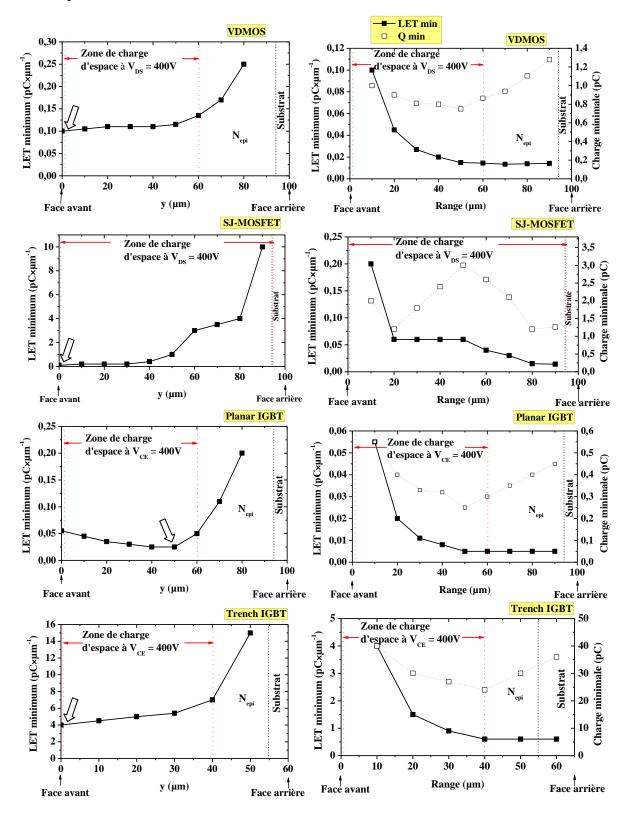

| Figure 2- 11: LET minimal provoquant un SEB dans un VDMOS (a) et un SJ-MOSFET (b) pour différente                                                                         |   |

| positions d'impact (x = variable, y=0, range=10µm, VDS=400 V)                                                                                                             |   |

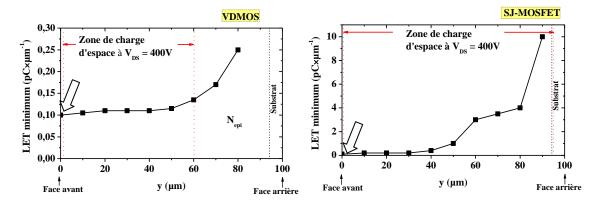

| Figure 2- 12: LET minimal provoquant un SEB en fonction de la profondeur de pénétration de l'ion arrivant en                                                              |   |

| incidence normale sur la face avant de la demi-cellule VDMOS (à gauche) et SJ-MOSFET (à droite) (y=ariable, range=10                                                      |   |

| μm, VDS=400 V)                                                                                                                                                            |   |

| Figure 2- 13: Traces positionnées à deux profondeurs différentes dans un VDMOS (à gauche) et SJ-MOSFET (                                                                  |   |

| droite)                                                                                                                                                                   |   |

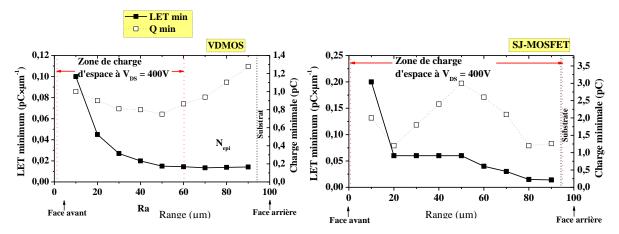

| Figure 2- 14: LET minimal provoquant un SEB et la charge déposée correspondante en fonction de la profondeu                                                               |   |

| de pénétration de l'ion arrivant en incidence normale sur la face avant de la demi-cellule VDMOS (à gauche) et SJ-MOSFE                                                   |   |

| (à droite) (range=variable, VDS=400 V)                                                                                                                                    |   |

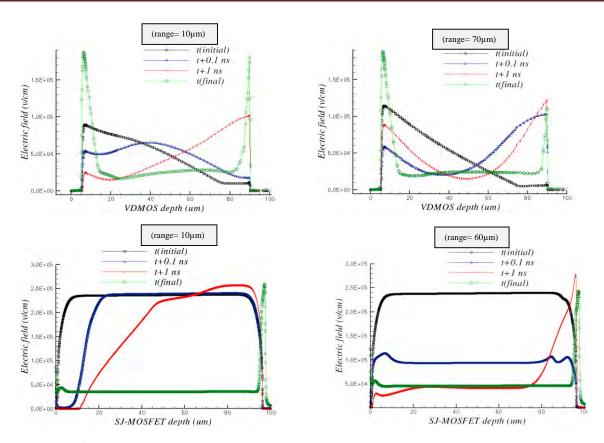

| Figure 2- 15: évolution du champ électrique suite à un impact ionisant vertical d'un grand range (à droite) et d'un                                                       |   |

| petit range (à gauche) dans les demi-cellules de VDMOS (haut) et SJ-MOSFET (bas) polarisée à 400V                                                                         |   |

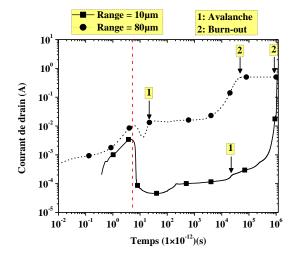

| Figure 2- 16: Comparaison de l'évolution du courant Ids en fonction du temps suite à un impact ionisant vertica                                                           |   |

| d'un grand et d'un petit range dans la demi-cellule de VDMOS                                                                                                              |   |

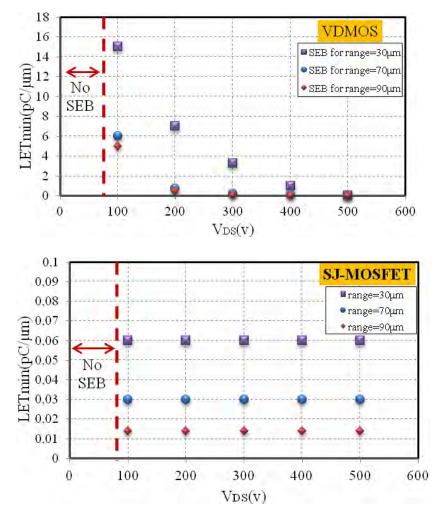

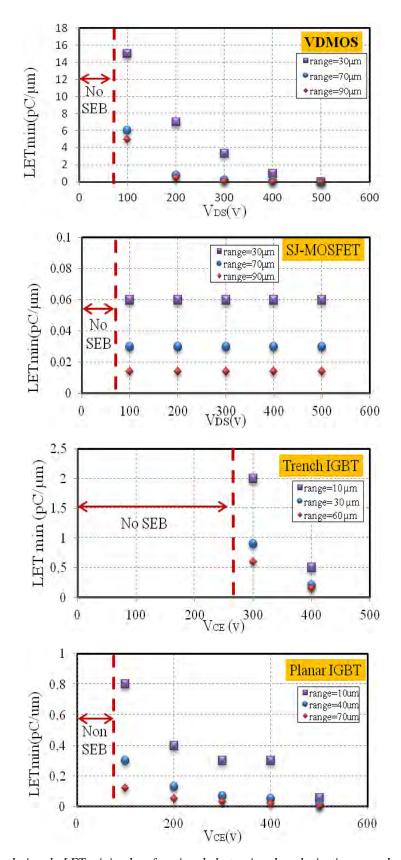

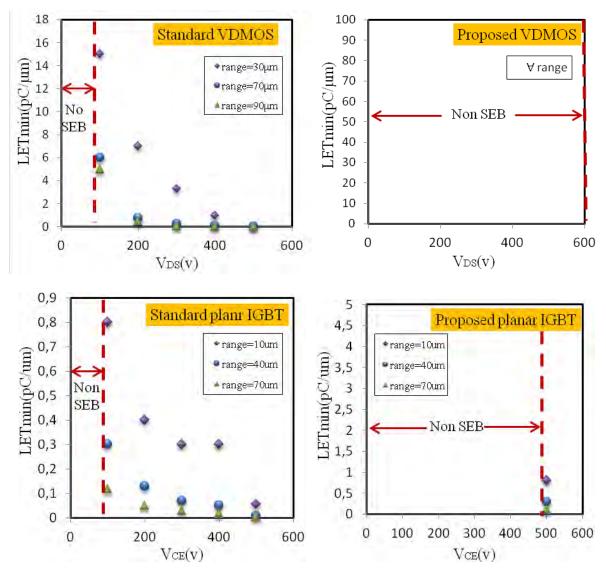

| Figure 2- 17: LET minimal provoquant un SEB en fonction de la tension de polarisation VDS pour un VDMOS                                                                   |   |

| (haut) et SJ-MOSFET (bas), (range=30,70 et 90 μm, VDS= variable)                                                                                                          |   |

| Figure 2- 18: LET minimal provoquant un SEB dans un IGBT planar (a) et un IGBT trench (b) pour différente                                                                 |   |

| positions d'impact (x = variable, y=0, range=10µm, VCE=400 V)                                                                                                             |   |

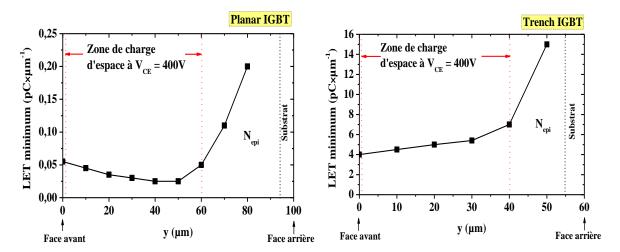

| Figure 2- 19: LET minimal provoquant un SEB en fonction de la profondeur de pénétration de l'ion arrivant en                                                              |   |

|                                                                                                                                                                           |   |

| incidence normale sur la face avant de la demi-cellule d'IGBT planar (à gauche) et IGBT trench (à droite) (y=variable range=10 µm, VCE=400 V)                             |   |

| Figure 2- 20: LET minimal provoquant un SEB et la charge déposée correspondante en fonction de la profondeu                                                               |   |

|                                                                                                                                                                           |   |

| de pénétration de l'ion arrivant en incidence normale sur la face avant de la demi-cellule d'IGBT planar (à gauche) et IGBT trench (à droite) (range=variable, VCE=400 V) |   |

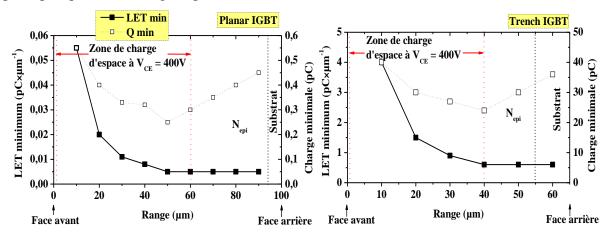

| Figure 2- 21: évolution du courant de collecteur en fonction du temps suite à un impact ionisant (VCE=400 V) 8:                                                           |   |

| 1 iguie 2- 21. evolution du coulain de confecteul en ionetion du temps suite à un impact iomsant ( v CE=400 v ) 8.                                                        | , |

| Figure 2- 22: Evolution du champ électrique suite à un impact ionisant vertical d'un grand range (à droite) et d' | un  |

|-------------------------------------------------------------------------------------------------------------------|-----|

| petit range (à gauche) dans les demi-cellules d'IGBT planar (haut) et IGBT trench (bas) polarisée à 400V          | 84  |

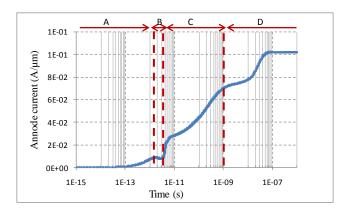

| Figure 2- 23: LET minimal provoquant un SEB en fonction de la tension de polarisation VCE pour un IGBT pla        | nar |

| (haut) et IGBT trench (bas), (x=30 μm, y=0μm, range=30,70 et 90 μm)                                               | 85  |

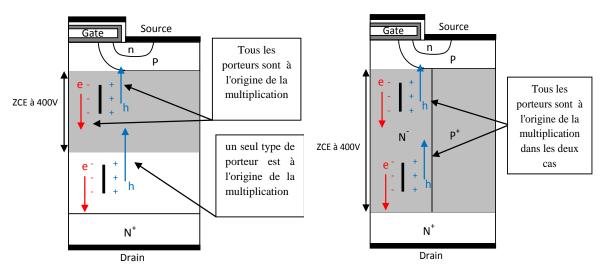

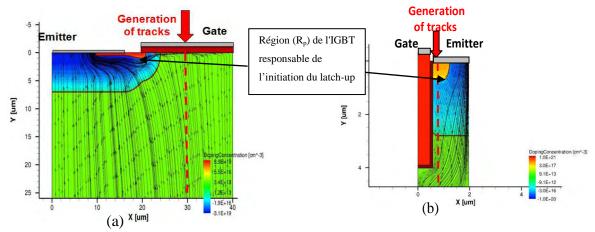

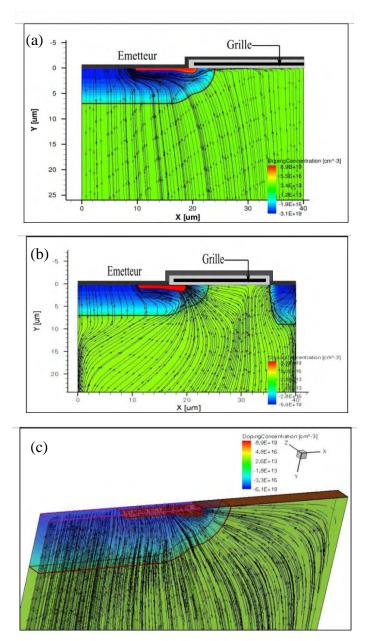

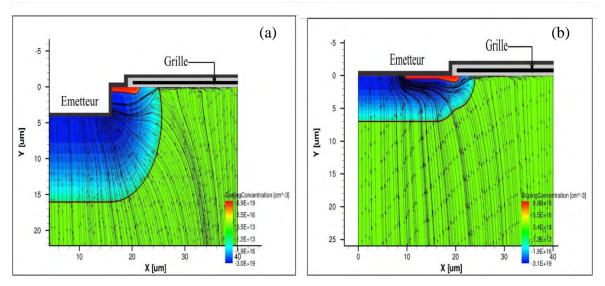

| Figure 2- 24: Distribution de lignes de courant des trous après l'impact et avant le déclenchement du thyris      | tor |

| parasite dans une structure d'IGBT planar (a) et trench (b)                                                       | 86  |

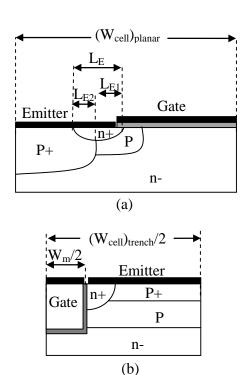

| Figure 2- 25: Les paramètres géométriques de la zone active pour l'analyse de la densité de courant de latchup d  | 'un |

| IGBT planar (a) et d'un IGBT trench (b)                                                                           | 88  |

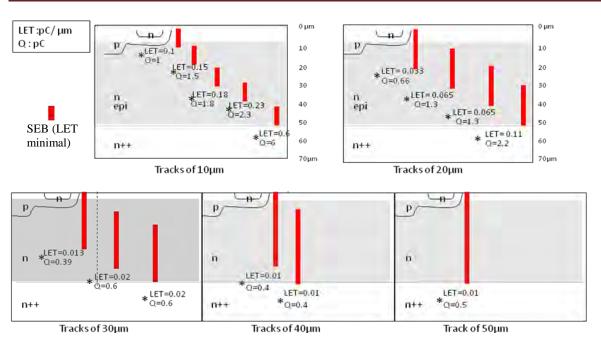

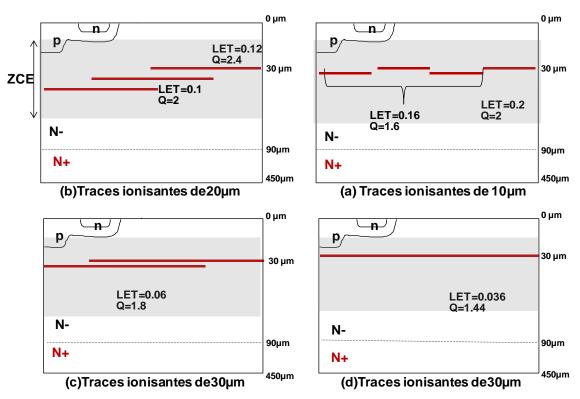

| Figure 2- 26: Schématisation de traces ionisantes horizontales dans la demi-cellule de VDMOS polarisée à 400      | )V. |

| Les traces sont positionnées à la même profondeur z=30 µm mais à différentes abscisses et sont simulées chacu     | ıne |

| indépendamment. Le LET est en pC/μm et le range en μm                                                             |     |

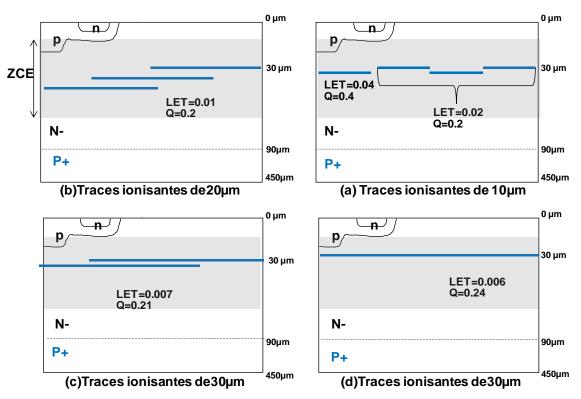

| Figure 2- 27: Schématisation de traces ionisantes horizontales dans la demi-cellule d'IGBT polarisée à 400V. I    |     |

| traces sont positionnées à la même profondeur z=30 µm mais à différentes abscisses et sont simulées chacu         |     |

| indépendamment. Le LET est en pC/μm et le range en μm                                                             |     |

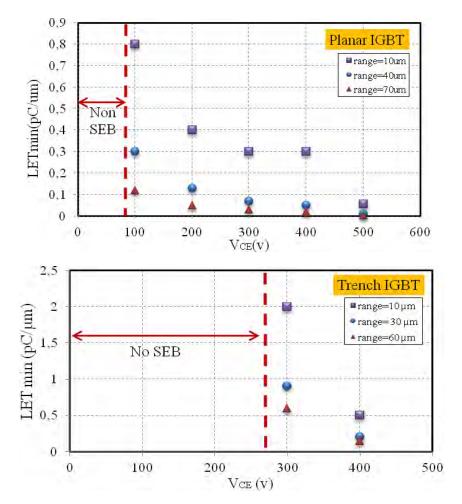

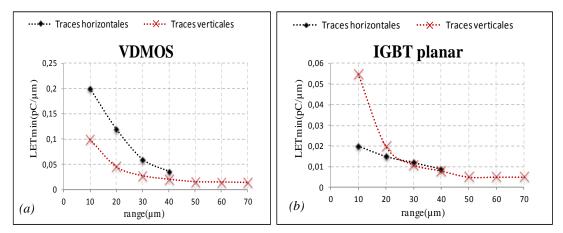

| Figure 2- 28: LET minimal provoquant un SEB en fonction de la profondeur de pénétration (a) et en fonction        |     |

| range (b) de l'ion arrivant en incidence normale sur la face avant de chaque cellule                              |     |

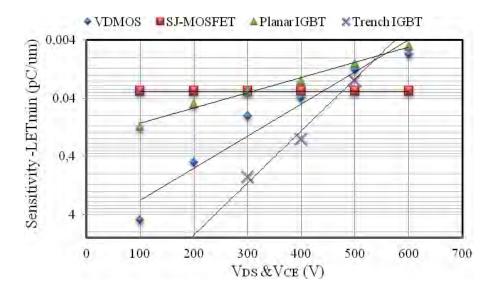

| Figure 2- 29: Evolution du LET minimal en fonction de la tension de polarisation pour des ions arrivant           |     |

| incidence normale sur la face avant de chaque cellule avec différent range                                        |     |

| Figure 2- 30 : Evolution du LET minimal en fonction de la tension de polarisation pour des ions arrivant          |     |

| incidence normale sur la face avant de chaque cellule et pénétrant 2/3 de la region épitaxiée                     |     |

| Figure 2- 31: Comparaison entre les traces ionisantes horizontales et verticales pour un VDMOS (a) et pour        |     |

| IGBT planar (b)                                                                                                   |     |

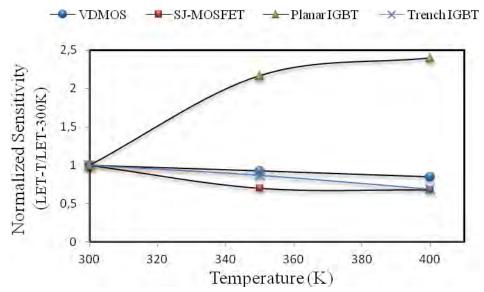

| Figure 2- 32: sensibilité normalisée en fonction de la température pour un ion pénétrant 2/3 de la region épitax  |     |

| de chaque composant (x=30, y=0, VDS&VCE=400V)                                                                     |     |

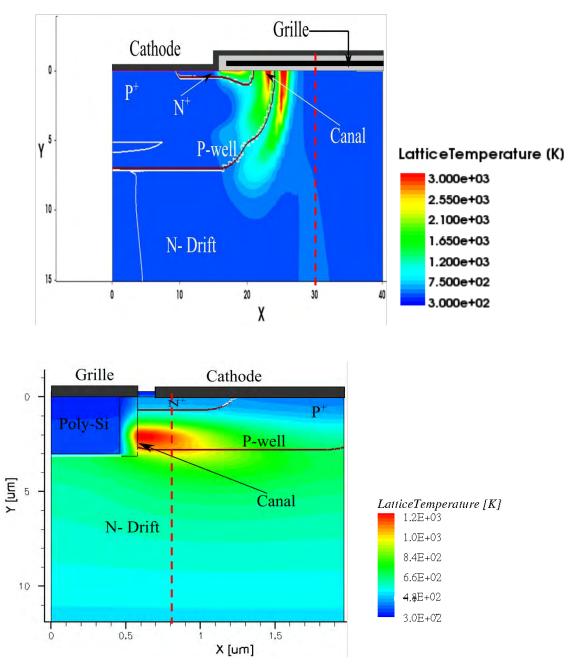

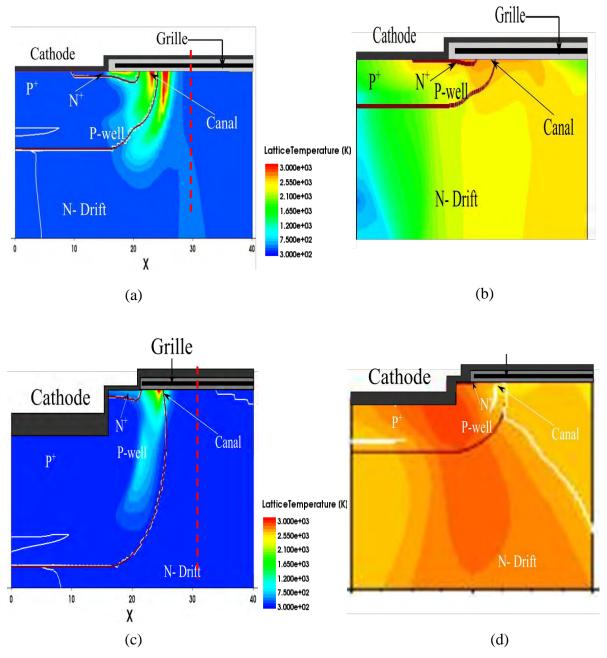

| Figure 2- 33: Distribution de la température dans les structures (haut) de type planar (VDMOS et IGBT), (b        |     |

| IGBT de type trench                                                                                               |     |

| IOB i de type delicii                                                                                             | 91  |

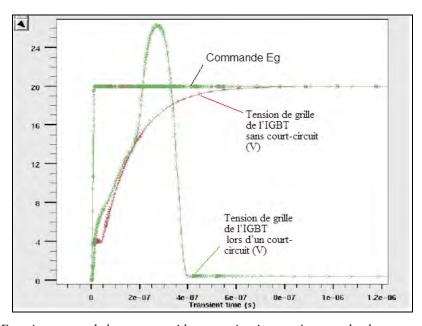

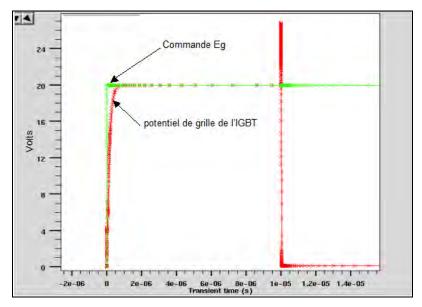

| Figure3- 1 : Phénomènes physiques lors d'un C.C dans un IGBT                                                      | Ω1  |

| Figure 3- 2 : (a) Circuit de protection contre les courts-circuits, (b) Capteur de tension d'anode                |     |

| Figure 3 : Fonctionnement de la structure si le court-circuit est présent sur la charge au moment de la mise      |     |

| conduction de l'interrupteur.                                                                                     |     |

| Figure 3- 4: Fonctionnement de la structure si le court-circuit se produit alors que l'interrupteur de puissance  |     |

| trouve déjà à l'état passant                                                                                      |     |

| ·                                                                                                                 |     |

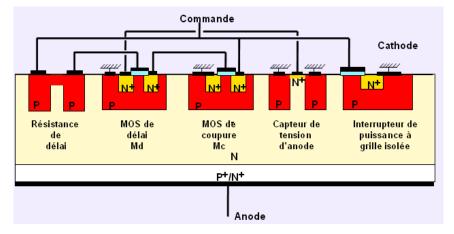

| Figure 3-5: Structure intégrée du circuit de détection et de protection                                           |     |

| Figure 3-6: Coupe schématique du circuit équivalent du circuit de protection par détection du courant             |     |

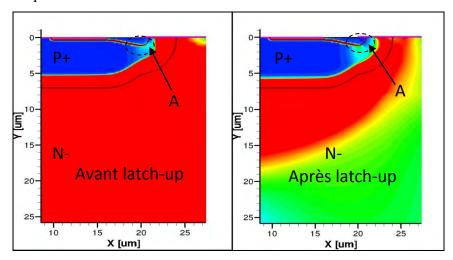

| Figure 3-7: Latchup du thyristor parasite dans un IGBT                                                            |     |

| Figure3-8: (a) Géométrie d'un IGBT planar montrant les segments LE1 et LE2, (b) influence du segment LE1          |     |

| la densité de courant du latchup et la tension de seuil                                                           |     |

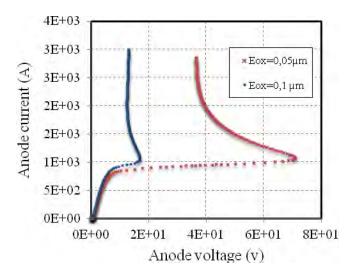

| Figure3- 9 : Caractéristiques IA(VAK) d'un IGBT planar pour deux concentrations en surface de la région P-wel     |     |

| pour deux épaisseurs d'oxyde de grille différentes                                                                |     |

| Figure3- 10 : Caractéristiques IA(VAK) (a) et IA(VGK) (b) d'un IGBT planar pour deux épaisseurs d'oxyde           |     |

| grille différentes.                                                                                               |     |

| Figure3- 11 : Représentation schématique de la première modification de la structure par la diffusion de P+ dans  |     |

| région intercellulaire (IGBT-1).                                                                                  | 12  |

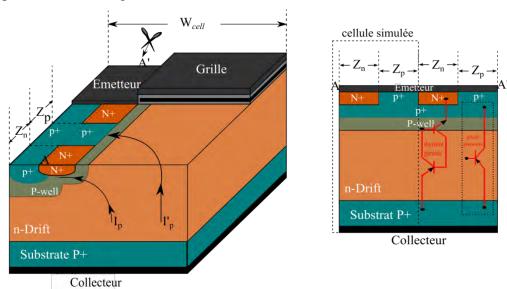

| Figure3- 12 : (a) Représentation schématique de la deuxième modification de la structure par la diffusion de                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | P+   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

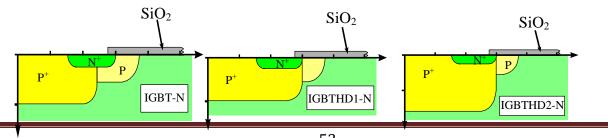

| dans la région N+ émetteur (IGBT-2), (b) coupe 2D dans AA'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | l 12 |

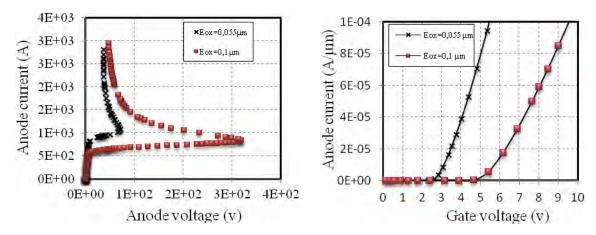

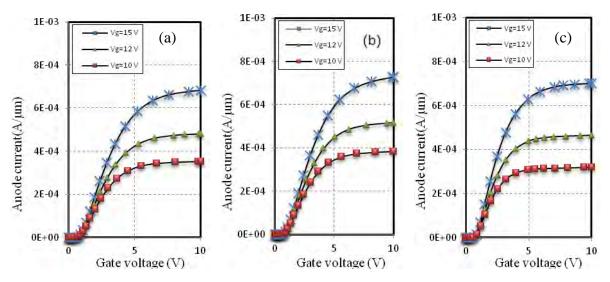

| Figure 3-13 : caractéristiques de sortie $I_A = f(V_{AK})$ de (a) l'IGBT standard, (b) l'IGBT-1 et (c) l'IGBT-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | l 13 |

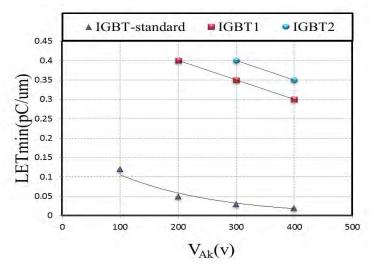

| Figure3- 14 : Minimal LET déclenchant un SEB pour différentes polarisations d'un ion lourd provenant de la f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ace  |

| avant d'IGBT standard, IGBT-1 et IGBT-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | l 14 |

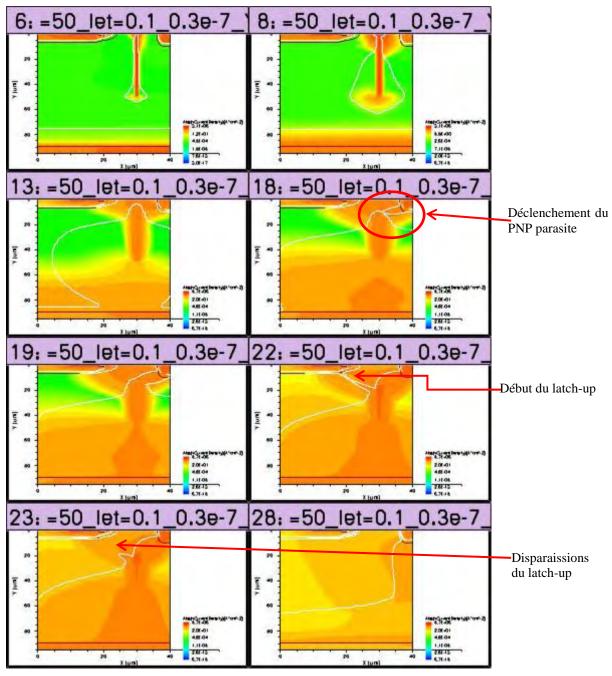

| Figure 3- 15 : Distribution de courant total à différents instants après l'impact dans l'IGBT-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | l 15 |

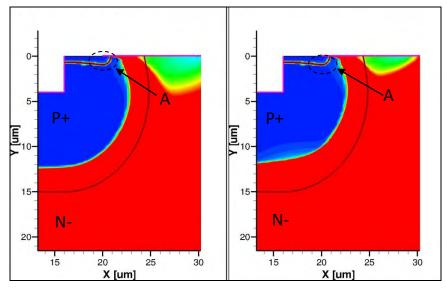

| Figure 3- 16 : Distribution de lignes de courant des trous dans une structure standard (a), l'IGBT-1 (b) et l'IGB'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Г-2  |

| (c)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | l 16 |

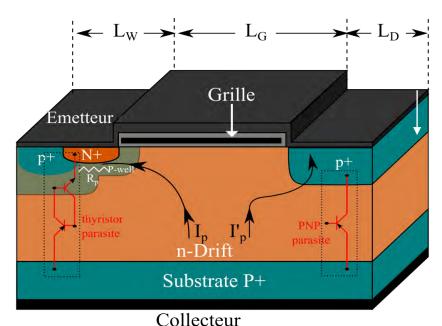

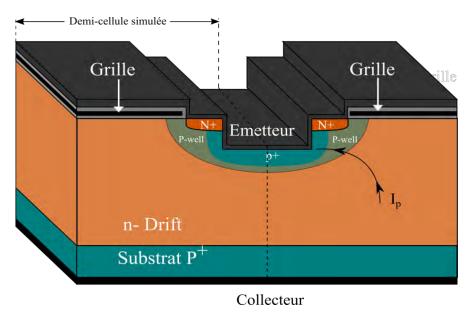

| Figure3- 17 : Cellule de l'IGBT proposé (cathode en tranchée)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | l 19 |

| Figure 3- 18 : Demi-cellules d'IGBT standard (a) et l'IGBT proposé (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | l 19 |

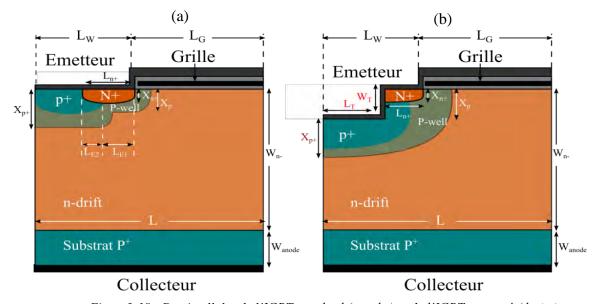

| Figure 3- 19 : Caractéristiques $I_A(V_{AK})$ (a) et $I_A(V_{GK})$ (b) de l'IGBT standard et l'IGBT proposé pour différent de l'IGBT proposé pour de l'IGBT proposé | ites |

| longueur de la tranchée LT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 120  |

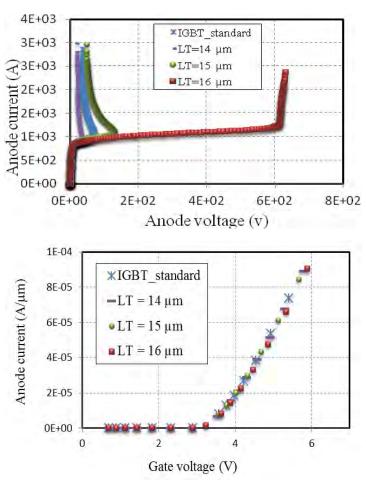

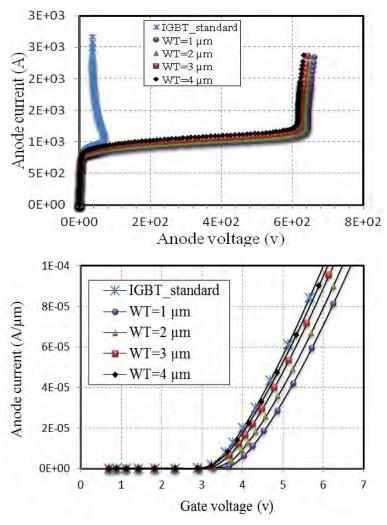

| Figure 3- 20 : Caractéristiques $I_A(V_{AK})$ (haut) et $I_A(V_{GK})$ (bas) de l'IGBT standard et l'IGBT proposé p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | our  |

| différentes profondeurs de la tranchée WT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 121  |

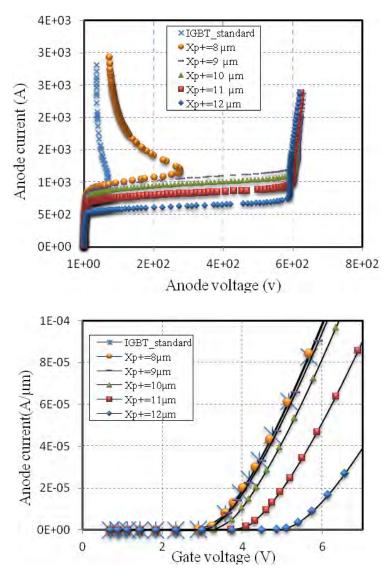

| Figure 3- 21 : Caractéristiques $I_A(V_{AK})$ (haut) et $IA(V_{GK})$ (bas) de l'IGBT standard et l'IGBT proposé p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | our  |

| différentes profondeurs de dopage P+                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 122  |

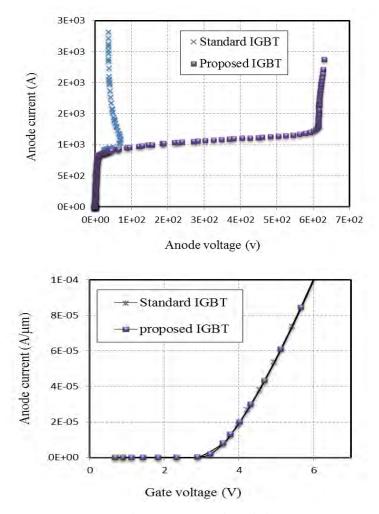

| Figure 3-22 : Caractéristiques IA(VAK) (haut) et IA(VGK) (bas) de la structure IGBT proposée et standard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

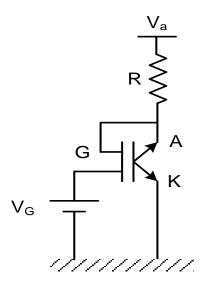

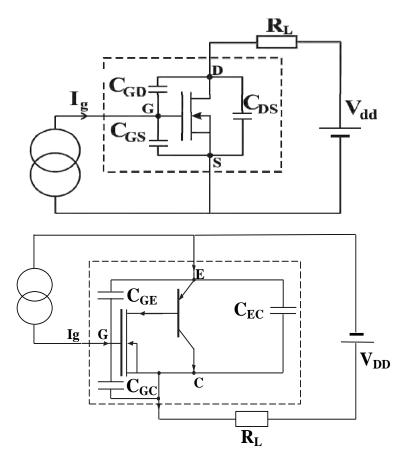

| Figure 3- 23 : Circuit de commutation sur une charge résistive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 124  |

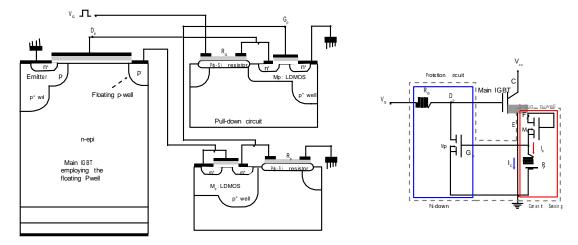

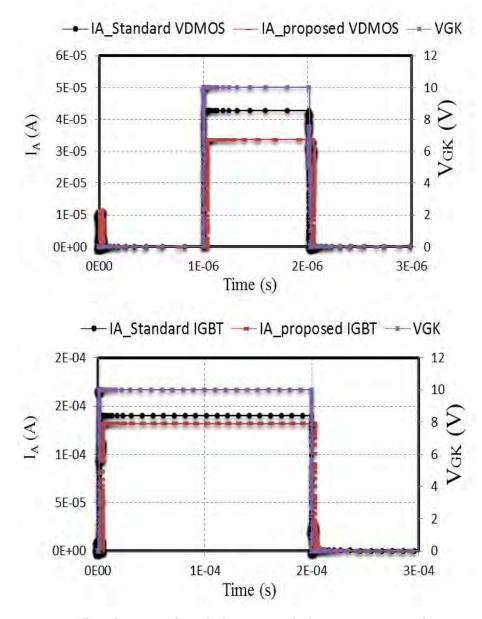

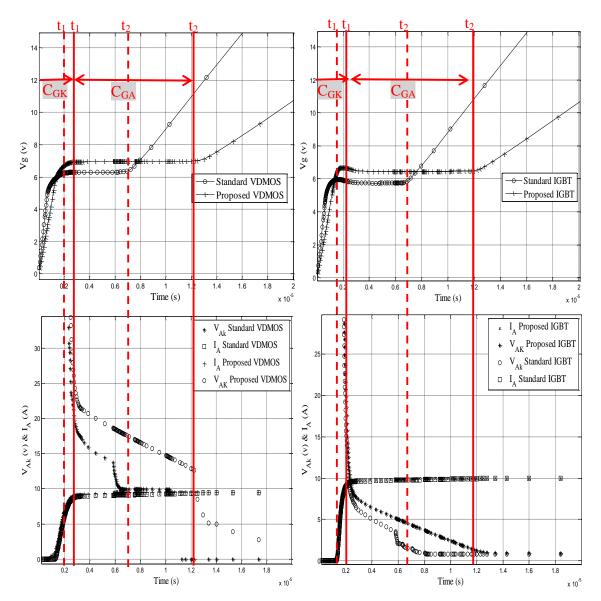

| Figure 3- 24: Allure du courant d'anode durant un cycle de commutation pour les structures VDMOS (haut)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ) et |