# **AAS 12**

Analog Acquisition System, A/D 12 Bit

## MANUALE UTENTE

Via dell' Artigiano, 8/6 40016 San Giorgio di Piano (Bologna) ITALY E-mail: grifo@grifo.it

http://www.grifo.it http://www.grifo.com Tel. +39 051 892.052 (r.a.) FAX: +39 051 893.661

**AAS 12** Rel. 2.00 *Edizione 20 Marzo 1992*

GPC®, grifo®, sono marchi registrati della ditta grifo®

## **AAS 12**

**Analog Acquisition System, A/D 12 Bit**

## MANUALE UTENTE

La scheda AAS 12 è una struttura di conversione A/D del tipo storage, nel formato standard Europa da 100x160 mm. Essa opera direttamente sul Bus industriale Abaco® e quindi può essere comandata da una delle numerose schede di CPU o GPC® presenti su tale BUS.

La AAS 12 può essere vista a tutti gli effetti come un oscilloscopio digitale storage con una memoria di 64 K conversioni ed una risoluzione verticale di 12 bit. La programmabilità delle funzioni quali la velocità, il numero delle conversioni e la sorgente del trigger la rendono un sofisticato strumento di indagine per congelare eventi analogici anche molto veloci.

- Interfacciamento con il BUS Industriale Abaco®

- 1 linea di A/D converter a 12 Bit; 3 µs di tempo di conversione

- Range del segnale in ingresso selezionabile tra: +10/-10; 0/+10V; 0/+5V oppure 4-20 mA

- Amplificatore Programmabile d'ingresso con rappporto: x1; x100; x200; x500

- Tempo di campionamento programmabile via software con incrementi di 250 ns, da un minimo di 5 μs ad un massimo di 16,384 ms. Questo significa che alla massima velocità di conversione si possono memorizzare 320 ms di un evento con una risoluzione di 5 μs, oppure superare i 17 minuti di registrazione adoperando il massimo tempo di campionamento

- Il numero di conversioni è programmabile e va da uno fino ad un massimo di 65536 (RAM di bordo da 128 K)

- Selezione del trigger interno, esterno oppure sullo stesso segnale d'ingresso programmabile via software

- Modalità di funzionamento Master/Slave in un sistema di più schede

- Sample/Hold con tempo di sample di 1,5 µs

- Possibilità di gestione in interrupt tramite Bus

- Mappaggio in I/O tramite Dip Switch in modalità estesa o normale 8 byte consecutivi occupati in indirizzamento

- Unica tensione di alimentazione: 5 V; 900 mA

Via dell' Artigiano, 8/6 40016 San Giorgio di Piano (Bologna) ITALY

ALIAN TECHNOLOGY E-mail: grifo@grifo.it

http://www.grifo.it http://www.grifo.com

**AAS 12**

Rel. 2.00

Edizione 20 Marzo 1992

GPC®, grifo®, sono marchi registrati della ditta grifo®

Tel. +39 051 892.052 (r.a.) FAX: +39 051 893.661

## Vincoli sulla documentazione grifo® Tutti i Diritti Riservati

Nessuna parte del presente manuale può essere riprodotta, trasmessa, trascritta, memorizzata in un archivio o tradotta in altre lingue, con qualunque forma o mezzo, sia esso elettronico, meccanico, magnetico ottico, chimico, manuale, senza il permesso scritto della **grifo**<sup>®</sup>.

## **IMPORTANTE**

Tutte le informazioni contenute sul presente manuale sono state accuratamente verificate, ciononostante **grifo**<sup>®</sup> non si assume nessuna responsabilità per danni, diretti o indiretti, a cose e/o persone derivanti da errori, omissioni o dall'uso del presente manuale, del software o dell' hardware ad esso associato.

**grifo**<sup>®</sup> altresi si riserva il diritto di modificare il contenuto e la veste di questo manuale senza alcun preavviso, con l' intento di offrire un prodotto sempre migliore, senza che questo rappresenti un obbligo per **grifo**<sup>®</sup>.

Per le informazioni specifiche dei componenti utilizzati sui nostri prodotti, l'utente deve fare riferimento agli specifici Data Book delle case costruttrici o delle seconde sorgenti.

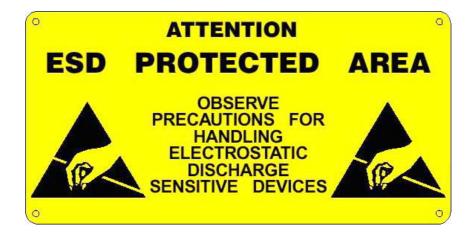

### LEGENDA SIMBOLI

Nel presente manuale possono comparire i seguenti simboli:

Attenzione: Pericolo generico

Attenzione: Pericolo di alta tensione

Attenzione: Dispositivo sensibile alle cariche elettrostatiche

## **MARCHI REGISTRATI**

GPC<sup>®</sup>, grifo<sup>®</sup>: sono marchi registrati della grifo<sup>®</sup>.

Altre marche o nomi di prodotti sono marchi registrati dei rispettivi proprietari.

## INTRODUZIONE

L'uso di questi dispositivi è rivolto - **IN VIA ESCLUSIVA** - a personale specializzato. Questo prodotto non è un **componente di sicurezza** così come definito dalla direttiva **98-37/CE**.

I pin della scheda non sono dotati di protezione contro le cariche elettrostatiche. Visto che esiste un collegamento diretto tra numerosi pin della scheda ed i rispettivi pin dei componenti di bordo e che quest'ultimi sono sensibili ai fenomeni ESD, il personale che maneggia la scheda è invitato a prendere tutte le precauzioni necessarie per evitare i possibili danni che potrebbero derivare dalle cariche elettorostatiche.

Scopo di questo manuale é la trasmissione delle informazioni necessarie all'uso competente e sicuro dei prodotti. Esse sono il frutto di un'elaborazione continua e sistematica di dati e prove tecniche registrate e validate dal Costruttore, in attuazione alle procedure interne di sicurezza e qualità dell'informazione.

I dati di seguito riportati sono destinati - **IN VIA ESCLUSIVA** - ad un utenza specializzata, in grado di interagire con i prodotti in condizioni di sicurezza per le persone, per la macchina e per l'ambiente, interpretando un'elementare diagnostica dei guasti e delle condizioni di funzionamento anomale e compiendo semplici operazioni di verifica funzionale, nel pieno rispetto delle norme di sicurezza e salute vigenti.

Le informazioni riguardanti installazione, montaggio, smontaggio, manutenzione, aggiustaggio, riparazione ed installazione di eventuali accessori, dispositivi ed attrezzature, sono destinate - e quindi eseguibili - sempre ed in via esclusiva da personale specializzato avvertito ed istruito, o direttamente dall'ASSISTENZA TECNICA AUTORIZZATA, nel pieno rispetto delle raccomandazioni trasmesse dal costruttore e delle norme di sicurezza e salute vigenti.

I dispositivi non possono essere utilizzati all'aperto. Si deve sempre provvedere ad inserire i moduli all'interno di un contenitore a norme di sicurezza che rispetti le vigenti normative. La protezione di questo contenitore non si deve limitare ai soli agenti atmosferici, bensì anche a quelli meccanici, elettrici, magnetici, ecc.

Per un corretto rapporto coi prodotti, é necessario garantire leggibilità e conservazione del manuale, anche per futuri riferimenti. In caso di deterioramento o più semplicemente per ragioni di approfondimento tecnico ed operativo, consultare direttamente l'Assistenza Tecnica autorizzata.

Al fine di non incontrare problemi nell'uso di tali dispositivi, é conveniente che l'utente - PRIMA DI COMINCIARE AD OPERARE - legga con attenzione tutte le informazioni contenute in questo manuale. In una seconda fase, per rintracciare più facilmente le informazioni necessarie, si può fare riferimento all'indice generale e all'indice analitico, posti rispettivamente all'inizio ed alla fine del manuale.

#### 1. INTRODUZIONE

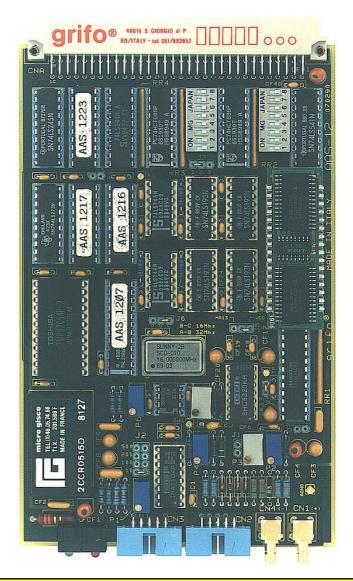

Questo manuale fornisce tutte le informazioni hardware e software per consentire all' utente il miglior utilizzo della scheda AAS 12.

### 2. CARATTERISTICHE GENERALI DELLA SCHEDA

La scheda AAS 12 (Analog Acquisition System A/D 12 bit) e' una potente periferica provvista di 1 linea di conversione analogica digitale.

Il formato della scheda e' quello unificato standard EUROPA da  $100 \times 160 \text{ mm}$ .

Le principali caratteristiche della scheda sono le seguenti:

- 1 linea di conversione da 12 bit;

- Ingresso differenziale in tensione o in corrente;

- Tempo di conversione pari a 3 ysec;

- 2 segnalazioni visive;

- Connessioni con il mondo esterno tramite connettori normalizzati del tipo A/D Abaco(R) e tramite connettori professionali di tipo UHF miniatura;

- Memoria locale per i risultati delle conversioni per una profondita\ massima di 128 KByte;

- Circuiteria di trigger per sincronizzare le conversioni anche con un segnale esterno;

Il tutto puo' essere comodamente gestito da software, tramite l'interfaccia al BUS ABACO(R) di cui la scheda e' provvista.

Il sistema coincide con una macchina a stadi in cui la sucessione degli eventi e' gestita autonomamente dalla stessa scheda.

In questo modo la AAS 12 e' in grado di catturare anche fenomeni molto veloci pur operando con linguaggi tipicamente comodi ma lenti, quali gli interpreti BASIC, senza dover scrivere delle apposite procedure in linguaggio macchina.

Infatti la scheda di CPU o GPC che la comanda si deve limitare a programmare la scheda con gli appositi parametri, che specificano il tipo di funzionamento, e a conversioni ultimate, andare a leggere i risultati di queste nella memoria locale della scheda.

La AAS 12 puo' essere vista a tutti gli effetti come un oscilloscopio digitale storage con una memoria di 64K conversioni ed una risoluzione verticale di 12 bit.

La programmabilita' delle funzioni quali la velocita' ed il numero delle conversioni e la sorgente del trigger la rendono un preciso e sofisticato strumento di indagine.

## 2.1. Sezione Analogica.

La scheda AAS 12 e' dotata di una sofisticata sezione analogica a cui e' affidato il condizionamento del segnale d'ingresso e la sua conversione. In particolare questa sezione e' caratterizzata da:

- Amplificatore d'ingresso programmabile con rapporto di x10; x100; x200; x500;

- Selezione hardware del range di variazione della tensione d'ingresso che puo' essere settato in +10/-10; 0/+10; 0/+5;

- Sample/Hold sul segnale d'ingresso con tempo di sample di 1,5 ysec.;

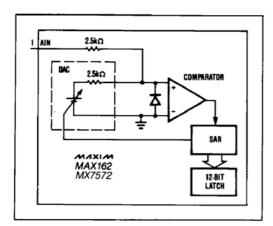

- A/D Converter da 12 bit con tempo di conversione di 3 ysec. che sfrutta il principio delle approssimazioni sucessive (SAR);

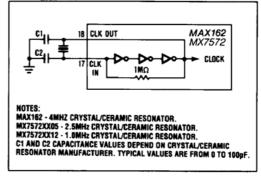

## 2.2. Dispositivo di Clock.

La scheda AAS 12 e' provvista di 1 segnale di clock su cui sono basate tutte le regolamentazioni temporali della macchina a stati della scheda.

La frequenza di lavoro della scheda e' ottenuta a partire da un oscillatore da 16 MHz che opportunamente diviso puo' fornire alla logica della scheda una frequenza di 4 o 2 Mhz a seconda della posizione di un apposito jumpers.

## 2.3. Sezione di Controllo.

Con sezione di controllo s'intende la circuiteria della AAS 12 che regolamenta automaticamente la sucessione dei vari stati della scheda.

Questa sezione e' completamente realizzata tramite logiche combinatorie programmabili (PAL) e, basandosi sui parametri di programmazione e sullo stato dei segnali d'interfaccia, provvede a generare tutti i segnali che governano l'operazione di conversione. Questa operazione e' del tutto indipendente dalla CPU di controllo che quindi, durante il tempo di conversione, puo' effettuare altre operazioni.

Questa sezione di controllo provvede direttamente a gestire tutti i componenti della sezione analogica, la sezione di salvataggio dati e la sezione d'interfaccia al BUS Industriale Abaco(R).

In fase di programmazione della scheda devono essere impostati alcuni parametri che vengono gestiti direttamente da questa sezione:

- Tempo di campionamento programmabile via software con incrementi di 250 nsec, da un minimo di 5ysec. fino ad un massimo di 16,384 msec.;

- Numero di conversioni programmabile da un minimo di 1 fino ad un massimo di 65535;

- Tipo di funzionamento della scheda (master o slave);

- Selezione del trigger da utilizzare;

Tramite i primi due parametri si stabilisce indirettamente il tempo di acquisizione del segnale d'ingresso che variera\(^\) quindi da un minimo di 5 ysec (pari ad una conversione con tempo di campionamento di 5 ysec) ad un massimo di circa 17 minuti (pari a 65535 conversioni con tempo di campionamento di 16,384 msec.).

## 2.4. Sezione di Salvataggio Dati.

Fa parte della sezione di salvataggio datiun'apposita circuiteria in cui vengono memorizzati i risultati delle conversioni impostate.

Il numero massimo di conversioni memorizzabili puo' variare a seconda del tipo di configurazione della scheda fino ad un massimo di 65535; tali dati vengono salvati direttamente dalla sezione di controllo e possono essere riletti dalla CPU anche per piu' volte.

# 2.5. Sezione di Interfaccia al BUS Industriale ABACO(R).

In questa sezione viene gestito il colloquio tra la sezione di controllo e la scheda di comando (CPU o GPC); in particolare tutti i dati di programmazione e tutti i risultati delle conversioni passano attraverso questa sezione, che inoltre provvede a:

- Gestire il mappaggio della scheda in I/O tramite comodi dip switch in modalita\ estesa o normale;

- Gestire la generazione di interrupt su Bus;

## 2.6. Trigger.

La scheda AAS 12 e' provvista di una circuiteria programmabile via software con cui si puo' selezionare il tipo di trigger.

### Tra questi:

- Trigger software interno: e' generato dalla sezionedi controllo in corrispondenza della programmazione software della stessa;

- Trigger hardware interno: e' generato dalla sezione analogica in corrispondenza della variazione del segnale d'ingresso in relazione ad un set tarabile tramite apposito trimmer;

- Trigger hardware esterno: deve essere generato da una circuiteria esterna;

- Ogni tipo di trigger puo' inoltre essere programmato a livello di fronte di attivazione, ovvero si puo' stabilire se il trigger si attiva in corrispondenza del fronte di salita o di discesa.

Da notare comunque che in ogni caso l'attivazione del trigger provoca l'inizio delle conversioni precedentemente programmate via software.

Piu' schede AAS 12 possono essere collegate in parallelo: in questo modo si programma via software una delle schede come master e le rimanenti come slave.

Il trigger, di conseguenza, ha effetto solo sulla scheda master e tutte le rimanenti slave saranno automaticamente comandate da quest'ultima.

### 3. SPECIFICHE TECNICHE DELLA SCHEDA

## 3.1. Caratteristiche Generali.

Tipo di BUS ABACO(R)

N.ro di linee di I/O 1 Input analogico

1 Input di trigger esterno

1 Input di sincronismo esterno

N.ro Byte indirizzamento 256 in modalita' normale

8192 in modalita' estesa

N.ro Byte occupati 8

Memoria indirizzabile U9: RAM

da 32K x 8 fino a 128K x 8 Convertitore di bordo MAX 162

Tempo di conversione 3 ysec.

Numero di conversioni programmabile da 1 a 65535

Tempo di campionamento programmabile da 5 ys a

16,384 ms con steps di 250 ns

### 3.2. Caratteristiche Fisiche.

Range d'ingresso settabile in: -10/+10; 0/+10; 0/+5

Dimensioni Formato Singola EUROPA: 100 X 160 mm.

Peso 1 85 g

Connettori BUS 64 pin DIN 41612 Corpo C

CN2,CN3: 10 vie scatolino 90 gradi

CN1,CN4: UHF miniatura

Range di temperatura da 10 a 40 gradi Centigradi

Umidita' relativa 20% fino a 90% (senza condensa)

## 3.3. Caratteristiche Elettriche.

Tensione di alimentazione +5 Vdc Corrente assorbita 900 mA

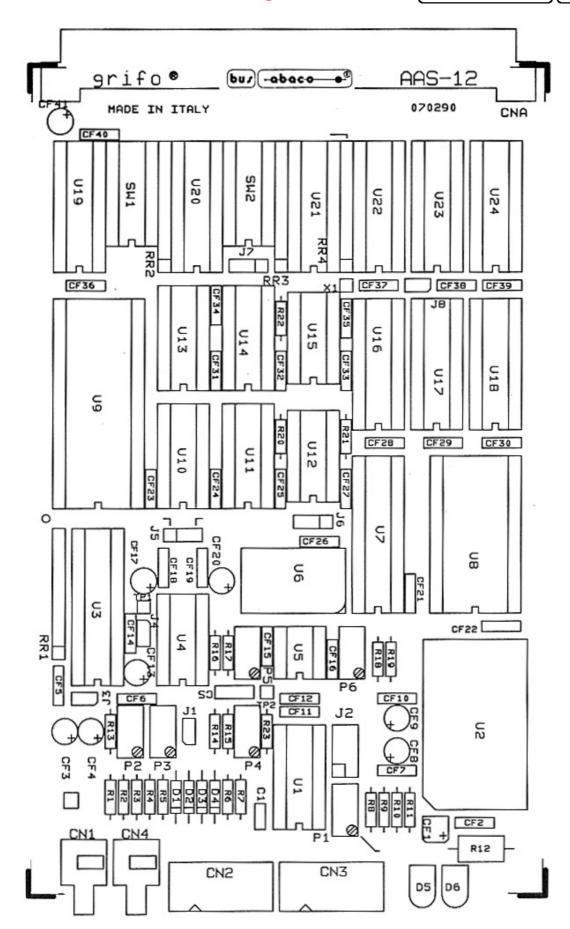

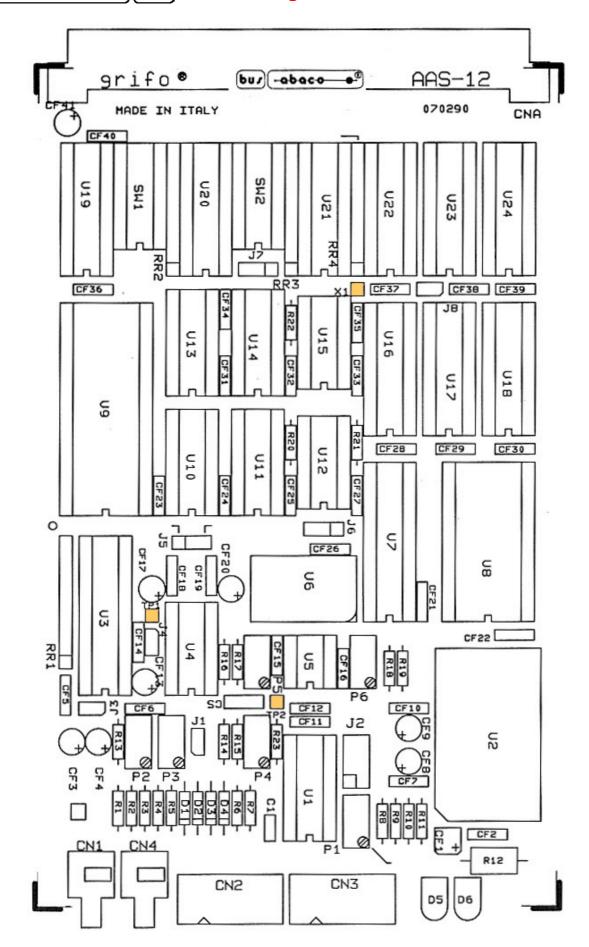

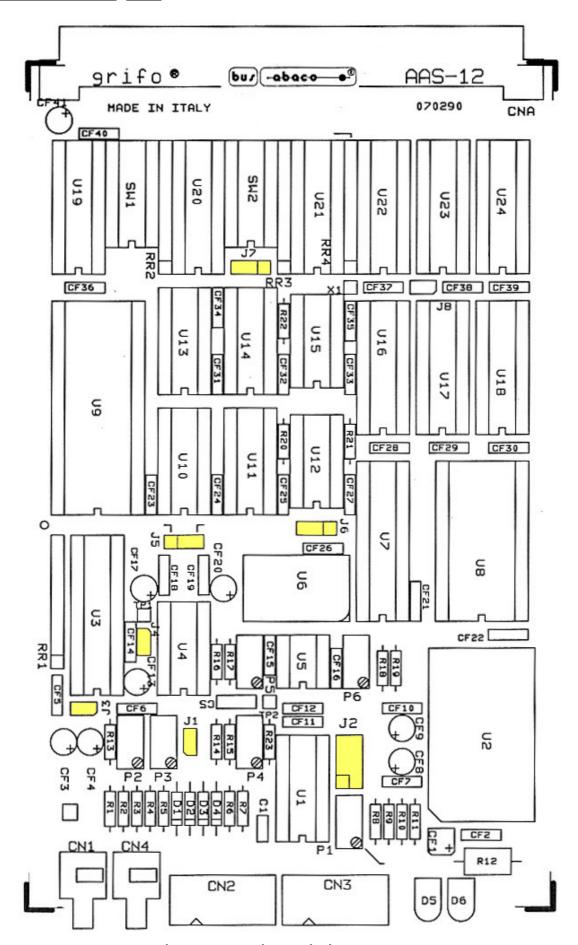

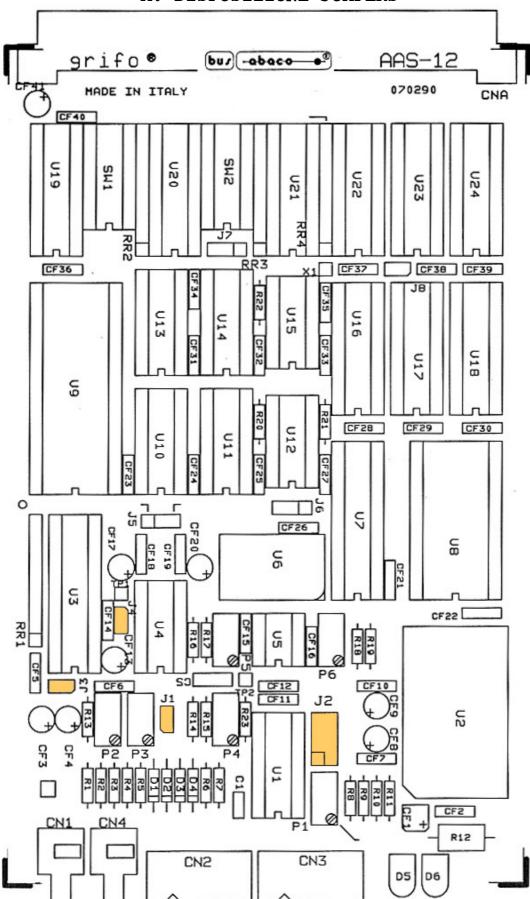

Fig. 3-1: Pianta Componenti

Rel. 2.00

**AAS 12**

### 4. INSTALLAZIONE DELLA SCHEDA

### 4.1. Introduzione.

In questo capitolo sono illustrate tutte le operazioni da compiere per il corretto funzionamento della scheda.

A questo scopo viene riportata l'ubicazione e la funzione degli strip, dei connettori, dei led, dei trimmer e dei test point presenti sulla AAS 12.

### 4.2. Connessioni con il Mondo Esterno.

Viene di seguito riportato il pin out dei cinque connettori presenti sulla scheda AAS 12; per quanto riguarda la disposizione di tali connettori si faccia riferimento alla fig. 4.2 di pag. 10.

## 4.2.1. CN1 - Connettore per Segnale Positivo

Il connettore **CN1** e' un connettore **UHF** miniatura a cui puo' essere collegato il segnale positivo dell'ingresso differenziale. Tale connettore e' da utilizzarsi al posto del **CN2** nel caso si operi in un ambiente rumoroso e su lunghe distanze.

Del connettore il contatto centrale e' collegato all'ingresso positivo, mentre la carcassa esterna e' collegata alla massa della scheda.

## 4.2.2. CN4 - Connettore per Segnale Negativo

Il connettore **CN4** e' un connettore **UHF** miniatura a cui puo' essere collegato il segnale negativo dell'ingresso differenziale.

Tale connettore e' da utilizzarsi al posto del CN2 nel caso si operi in un ambiente rumoroso e su lunghe distanze.

Del connettore il contatto centrale e' collegato all'ingresso negativo, mentre la carcassa esterna e' collegata alla massa della scheda.

## 4.2.3. CNA - Connettore per BUS ABACO(R)

Il connettore CNA e' formato da un insieme di 64 pin con cui e' possibile effettuare il collegamento della scheda con il BUS ABACO(R).

Nella tabella seguente e' rappresentato il Pin-Out del BUS e quindi anche del relativo connettore, con le variazioni per l' utilizzo di CPU a 16 bit rispetto a quelle a 8 bit.

| A               | A              | A          | pin       | C          | C                | C               |

|-----------------|----------------|------------|-----------|------------|------------------|-----------------|

| CPU<br>  16 bit | CPU<br>  8 bit | AAS<br>12  | <br> <br> | AAS        | CPU  <br>  8 bit | CPU  <br>16 bit |

| +               | h              |            | +         | +          | +                |                 |

| ļ               | GND            | GND        | 1         | GND        | GND              | !               |

| ļ               | +5V            | +5V        | 2         | +5V        | +5V              |                 |

| ļ               | D0             | D0         | 3         | <u> </u>   | *                | D8              |

| ļ               | D1             | D1         | 4         | <u> </u>   | *                | D9              |

| ļ               | D2             | D2         | 5         |            | *                | D10             |

| !               | D3             | D3         | 6         | /INT       | /INT             | ļ ļ             |

|                 | D5             | D5         | 8         | <u> </u>   | /HALT            | D11             |

|                 | D6             | D6         | 9         |            | /MREQ            |                 |

|                 | D7             | D7         | 10        | /IORQ      | /IORQ            | l               |

|                 | A0             | <b>A</b> 0 | 11        | /RD        | /RD              | /RDLDS          |

|                 | A1             | A1         | 12        | /WR        | /WR              | /WRLDS          |

|                 | A2             | A2         | 13        |            | /BUSAK           | D12             |

|                 | A3             | <b>A</b> 3 | 14        |            | /WAIT            | <b>I</b>        |

|                 | A4             | A4         | 15        |            | /BUSRQ           | D13             |

| İ               | <b>A</b> 5     | <b>A</b> 5 | 16        | /RESET     | /RESET           | ĺ               |

| İ               | <b>A</b> 6     | <b>A</b> 6 | 17        | /M1        | /M1              | /IACK           |

| İ               | A7             | <b>A</b> 7 | 18        | Ì          | /RFSH            | D14             |

| İ               | A8             | A8         | 19        | İ          | /MEMDIS          | İ               |

| j               | A9             | A9         | 20        | İ          | VDUSEL           | A22             |

| j               | A10            | A10        | 21        | İ          | /IEI             | D15             |

| j               | A11            | A11        | 22        | İ          | *                | Ris.            |

| j               | A12            | A12        | 23        | İ          | CLK              | i i             |

| i               | A13            | A13        | 24        | İ          | *                | /RDUDS          |

| i               | A14            | A14        | 25        | İ          | *                | /WRUDS          |

| j               | A15            | A15        | 26        | İ          | *                | A21             |

| <br>  A16       | *              | ·          | 27        |            | *                | A20             |

| A17             | *              |            | 28        |            | <br>  *          | A19             |

| A18             | *              |            | 29        |            | R.T.             | - [             |

|                 | +12V           | !<br>      | 30        |            | -12V             | į               |

| i               | +5V            | +5V        | 31        | '<br>  +5∨ | <br>  +5V        | i               |

| j               | GND            | GND        | 32        | GND        | GND              | i               |

| +               |                |            | +         | +          | +                | +               |

Fig. 4-1: Connettore CNA - Pin out del BUS ABACO(R).

#### LEGENDA:

Viene di seguito riportata la corrispondenza tra i segnali descritti nella precedenta tabella ed il loro significato.

#### CPU A 8 BIT

```

A0-A15= Address Bus - Bus degli indirizzi;

D0-D7= Data Bus - Bus dei dati ;

INT= Interrupt request - Richiesta di interruzione ;

NMI= Non Mascherable Interrupt - Richiesta di interruzione non

mascherabile;

HALT= Halt State - Stato di Halt ;

MREQ= Memory Request - Richiesta di memoria ;

IORQ= Input/Output Request - Richiesta di Input/Output ;

RD= Read Cycle Status - Richiesta di lettura ;

WR= Write Cycle Status - Richiesta di scrittura ;

BUSAK = BUS Aknowledge - Riconoscimento del Bus ;

WAIT= Wait - Attesa ;

BUSRQ= Bus Request - Richiesta del Bus ;

RESET= Azzeramento ;

M1= Machine Cycle One - Primo Ciclo Macchina ;

RFSH= Refresh - Rinfresco ;

MEMDIS= Memory Display - Viene emesso dal dispositivo periferico

che si sta mappando nell' area di memoria;

Selection - Abilita il dispositivo periferico ad

ad essere mappato nell' area di memoria;

IEI FIO 02,03= Abilitazione interrupt FIO 02 , 03 CLK= Clock di

sistema

R.T.= Tasto di Reset

```

#### CPU A 16 BIT

```

A0-A21= Address Bus - Bus degli indirizzi

D0-D15= Data Bus - Bus dei Dati

RD UDS= Read Upper Data Strobe - Lettura del byte superiore bus dati;

WR UDS= Write Upper Data Strobe - Scrittura del byte superiore bus dati;

IACK= Interrupt Acknowledge - Riconoscimento della richiesta di Interrupt da parte della CPU;

RD LDS= Read Lower Data Strobe - Lettura del byte inferiore bus dati;

WR LDS= Write Lower Data Strobe - Scrittura del byte inferiore bus dati;

```

Fig. 4-2: Disposizione Connettori, LEDs, Dip Switch

## 4.2.4. CN2 - Connettore per Ingresso Analogico

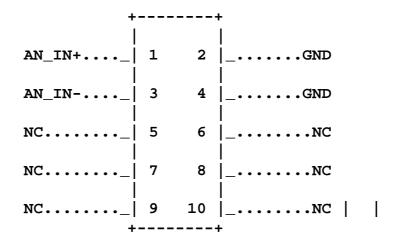

Il connettore CN2 e' composto da un insieme di 10 pin, con cui e' possibile collegare i 2 segnali dell'ingresso analogico differenziale alla sezione analogica della scheda.

Riportiamo di seguito la corrispondenza tra i pin del connettore ed i segnali collegatevi.

Fig. 4-3: Connettore CN2 - Ingresso Analogico

#### LEGENDA:

GND = - Segnale di massa della scheda.

AN\_IN+= I - Segnale positivo dell'ingresso differenziale.

AN\_IN-= I - Segnale negativo dell'ingresso differenziale.

NC = - Non Collegato.

## 4.2.5. CN3 - Connettore per Sincronismi e Trigger

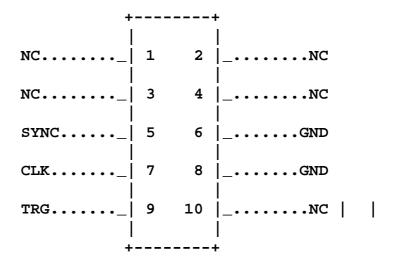

Il connettore CN3 e' composto da un insieme di 10 pin, con cui e' possibile collegare tutti i segnali di sincronismo, per il collegamento di piu' schede in parallelo, e di un eventuale trigger esterno.

Riportiamo di seguito la corrispondenza tra i pin del connettore ed i segnali collegatevi.

Fig. 4-4: Connettore CN3 - Sincronismi e trigger

#### LEGENDA:

```

GND = - Segnale di massa della scheda.

```

SYNC = I/O - Segnale di sincronismo da scheda master. CLK = I/O - Segnale di sincronismo per schede slave.

TRG = I - Segnale di trigger esterno.

NC = - Non Collegato.

Fig. 4-5: Disposizione Test Point e Trimmer

## 4.3. Test Point.

Viene di seguito riportato il significato dei quattro **Test Point** presenti sulla scheda **AAS 12**; per quanto riguarda la disposizione di tali punti di misura si faccia riferimento alla **fig. 4.5** di pag. **12**.

- AGND -> Il test point AGND e' collegato alla massa della scheda ed e' quindi da utilizzare come punto di riferimento per tutti gli strumenti di misura.

- x1 -> Il test point x1 e' collegato ad uno dei segnali ausiliari della sezione di controllo e serve per verificare la corretta sucessione di stati da parte di questa sezione.

- TP1 -> Il test point TP1 e' collegato al segnale analogico d'ingresso all'A/D Converter MAX 162 della scheda.

La funzione principale dei test point e' quella di facilitare l'operazione di collaudo e taratura della scheda, quindi il loro uso da parte dell'utente e' abbastanza improbabile.

## 4.4. Segnalazioni Visive.

La scheda AAS 12 segnala, tramite una serie di due LED, alcune particolari condizioni di stato:

- D5 -> Di colore Rosso si accende durante la fase di conversione, ovvero da quando viene attivata la prima conversione, a quando viene completata l'ultima.

- D6 -> Di colore Verde si accende in corrispondenza dell'attivazione del trigger hardware interno, ovvero quando il segnale d'ingresso ha superato il livello di trigger impostato con il trimmer P6.

Per quanto riguarda la disposizione di questi due led si faccia riferimento alla **fig. 4.2** di pag **10**.

## 4.5. Jumpers.

Esistono a bordo della AAS 12 9 strip, di cui uno su un Dip Switch, con cui e' possibile effettuare alcune selezioni che riguardano il modo di funzionamento della scheda.

Di seguito ne e' riportato l'elenco, l'ubicazione e la loro funzione.

| JUMPER         | N.VIE | UTILIZZO                                                                 |

|----------------|-------|--------------------------------------------------------------------------|

| J1<br>         | 2     | Seleziona attenuazione del segnale analogico   d'ingresso.               |

| J2<br>         | 8     | Seleziona rapporto di amplificazione del   segnale analogico d'ingresso. |

|                | 2     | Seleziona tipo di funzionamento del S/H.                                 |

| J4             | 2     | Seleziona tipo di funzionamento del S/H.                                 |

| <b>J</b> 5<br> | 3     | Seleziona dimensioni della RAM montabile su  <br>  U9.                   |

| J6             | 3     | Seleziona frequenza di lavoro della scheda.                              |

| J7             | 3     | Seleziona tipo di indirizzamento dela scheda                             |

| J8             | 2     | Collega segnale di interrupt al Bus ABACO(R)                             |

| SW2.1          | 2     | Collega segnale di M1 dal Bus ABACO(R).                                  |

Table 4-1: Tabella riassuntiva jumpers

Il jumper SW2.1 e' caratterizzato da una denominazione diversa da quella dei rimanenti jumpers in quanto e' l'unico strip incluso nel dip switch SW2.

Di seguito e' riportata la descrizione dele possibili connessioni dei 9 jumpers con la relativa funzione.

Per riconoscere tali connessioni sulla scheda si faccia riferimento alla serigrafia della stessa, dove viene sempre riportata l'indicazione del pin numero 1 da cui si ottiene la numerazione adottata nella seguente descrizione.

## 4.5.1. Jumpers a 2 vie

| +           | +                                           |                                                                                                                 | ++          |

|-------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------|

| J           | CONNESSIONE                                 | UTILIZZO                                                                                                        | DEF.        |

| J1<br>      | connesso  <br>  connesso  <br> non connesso | Disattiva circuiteria di attenuazione<br>del segnale analogico d'ingresso.<br>Attiva circuiteria di attenuazion | *  <br>     |

|             | <br>                                        | del segnale analogico d'ingresso tramite il trimmer P3.                                                         | <br>        |

| J3          | connesso  <br>                              | Collega segnale di riferimento del S/H alla tensione di riferimento dell'A/D (S/H con guadagno costante).       | į į         |

|             | <br> non connesso <br> <br>                 | Non collega segnale di riferimento del S/H alla tensione di riferimento dell'A/D.                               | i * i       |

| J4<br> <br> | connesso  <br>                              | Collega segnale di riferimento del S/H al segnale in ingresso all'A/D converter (S/H con guadagno unitario)     | j j<br>J j  |

|             | non connesso <br> <br>                      | Non collega segnale di riferimento del S/H al segnale in ingreso all'A/D converter.                             |             |

| J8<br>      | connesso                                    | Collega segnal di conversioni<br>ultimate al segnale di /INT del BUS<br>industriale Abaco(R).                   | <br>   <br> |

|             | non connesso                                | · · · · · · · · · · · · · · · · · · ·                                                                           |             |

| SW<br>  2.1 | connesso  <br> <br>                         | Collega segnale di /M1 del Bus industriale Abaco(R) alla sezione di interfaccia al Bus.                         |             |

|             | non connesso                                | Non collega segnale di /M1 del Bus Abaco(R) alla sezione di interfaccia al Bus.                                 |             |

Table 4-2: Tabella jumpers a 2 vie

L' \* contrassegna qual' e' la connessione di default, ovvero la connessione effettuata al momento del montaggio della stessa scheda.

Fig. 4-6: Disposizione Jumpers

## 4.5.2. Jumpers a 3 vie

| +           | POSIZIONE | UTILIZZO                                                                                                              | DEF        |

|-------------|-----------|-----------------------------------------------------------------------------------------------------------------------|------------|

| J5<br>      | 1-2       | Seleziona dispositivi RAM da 8K x 8 sullo zoccolo di U9.                                                              | <br> <br>  |

|             | 2-3       | Seleziona dispositivi RAM da 32K x 8 o 128K x 8 sullo zoccolo di U9.                                                  | *          |

| J6<br> <br> | 1-2       | Seleziona frequenza di lavoro della<br>scheda pari ad 1/4 della frequenza<br>dell'oscillatore di U6.                  | *          |

| <br>        | 2-3       | Seleziona frequenza di lavoro della scheda pari ad 1/8 della frequenza dell'oscillatore.                              | j<br> <br> |

| J7<br> <br> | 1-2<br>   | Seleziona tipo di indirizzamento<br>normale della scheda.<br>Seleziona tipo di indirizzamento<br>esteso della scheda. | *          |

Table 4-3: Tabella Jumpers a 3 vie

## 4.5.3. Jumpers a 8 vie

|        | J_ | +<br>  POSIZIONE | +++<br>  UTILIZZO   DEF.             |

|--------|----|------------------|--------------------------------------|

| İ      | J8 | 1-2<br>          | Seleziona rapporto di amplificazione |

| İ      |    | 3-4              | Seleziona rapporto di amplificazione |

| İ      |    | 5-6<br>          | Seleziona rapporto di amplificazione |

| j<br>I |    | 7-8<br>          | Seleziona rapporto di amplificazione |

| İ      |    | nessuna          | Seleziona rapporto di amplificazione |

| +      | +  | +                | +                                    |

Table 4-4: Tabella Jumpers a 8 vie

L' \* contrassegna qual' e' la connessione di default, ovvero la connessione effettuata al momento del montaggio della stessa scheda.

## 4.6. Trimmer.

A bordo della scheda AAS 12 sono presenti 6 trimmer con cui effettuare la taratura della sezione analogica della scheda e con cui impostare alcuni segnali di riferimento.

Tutti i trimmer che riguardano esclusivamente la taratura della scheda vengono gia' forniti nella posizione ottimale di lavoro, quindi non devono essere variati dall'utenete se non per reali esigenze.

Viene di seguito riportata una breve descrizione dei trimmer in questione specificandone la loro funzione, mentre per quanto riguarda la loro disposizione fare riferimento alla **fig. 4.5** di **pag. 12**.

- P1 -> Consente di variare un eventuale offset del segnale differenziale d'ingresso.

- P2 -> Consente di variare un eventuale offset del segnale d'uscita dal S/H della scheda.

- P3 -> Consente di variare il rapporto di attenuazione del segnale analogico d'ingresso al S/H della scheda, nel caso che il jumper J1 sia sconnesso.

- P4 -> Consente di variare un eventuale offset sul segnale analogico d'ingresso al S/H.

- P5 -> Consente di variare il guadagno del S/H nel caso che i jumpers J3 e J4 non selezionano un guadagno unitario.

- **P6** -> Consente di variare il livello per il trigger hardwre interno.

- Il range di variazione di questo segnale puo' variare nel range -10/+10 Vcc, corrispondente al massimo range d'ingresso.

## 4.7. Note.

Vengono riportate di seguito una serie di indicazioni con cui si descrive in modo piu' dettagliato quali sono le operazioni da eseguire per effettuare il giusto collegamento ed il giusto strippaggio della scheda.

## 4.7.1. Ingresso in Corrente

Il segnale differenziale d'ingresso alla scheda AAS 12 puo' essere sia in tensione che in corrente.

La selezione di quale tipo di ingresso utilizzare avviene come descritto di seguito:

## ingresso in Tensione

La scheda viene normalmente fornita per un ingresso differenziale in tensione, sprovvista della resistenza R2.

## Ingresso in Corrente

La predisposizione della scheda per un ingresso in corrente la si effettua montando sulla scheda la resistenza R2 di un valore tale da garantire comunque che la tensione che si viene a formare ai suoi capi, rimanga all'interno del range della tensione differenziale d'ingresso selezionato.

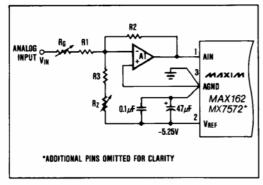

Per semplificare questa operazione fare riferimento alla fig.4.7.

## 4.7.2. Selezione del Range d'Ingresso

La scheda AAS 12 ha la possibilita' di essere settata in tre diverse condizioni corrispondenti a tre diversi range della tensione differenziale d'ingresso. In particolare lo strippaggio della scheda e' il seguente:

Range -10/+10 Vcc

J1 -> Connesso;

J3 -> Connesso;

J4 -> Non connesso;

Range 0/+10 Vcc

J1 -> Non connesso;

J3 -> Non connesso;

J4 -> Connesso;

Range 0/+5 Vcc

J1 -> Connesso;

J3 -> Non connesso;

J4 -> Connesso;

Nel caso di selezione di un rapporto di amplificazione sul segnale analogico d'ingresso > 1, il range della tensione d'ingresso alla scheda AAS 12 si riduce di un rapporto pari a quello di amplificazione.

## 4.7.3. Collegamento Parallelo di piu' Schede AAS 12

Nel caso sia necessario esaminare l'andamento di piu' segnali contemporaneamente in corrispondenza di un segnale master di riferimento, e' possibile collegare piu' schede AAS 12 sul BUS Industriale ABACO(R) che svolgono questo compito. In particolare le operazioni da effettuare sono le seguenti:

- Mappare le n schede ad indirizzi diversi;

- Collegare i vari segnali da esaminare agli appositi connettori d'ingresso (CN2 o CN1+CN4);

- Collegare assieme tutti i connettori CN3 a 10 vie delle N schede da utilizzare;

- Programmare la scheda collegata al segnale analogico di riferimento come Master (si veda par. 6.1) con i parametri di conversione desiderati;

- Programmare tutte le rimanenti schede come **Slave** (si veda par. **6.1**) con gli stessi parametri di conversione.

A questo punto in corrispondenza dell'attivazione del trigger sulla scheda master, vengono effettuate tutte le conversioni su tutte le schede.

### 5. MAPPAGGIO DELLA SCHEDA

#### 5.1. Introduzione

La scheda AAS 12 viene indirizzata in uno spazio fisico di 8 byte che possono essere allocati a partire da un indirizzo di base diverso a seconda di come viene mappata la scheda.

Questa prerogativa consente di poter montare piu' schede AAS 12 sullo stesso BUS ABACO(R), oppure di montare la scheda su di un Bus su cui sono gia' montate altre schede periferiche, ottenendo cosi' una struttura espandibile senza difficolta' e senza alcuna modifica del software gia' realizzato.

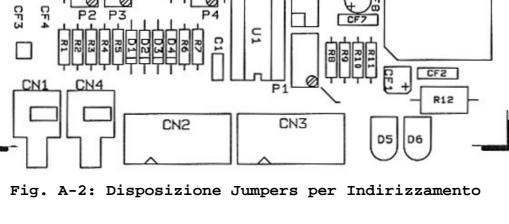

### 5.2. Indirizzamento della Scheda

L'indirizzo di mappaggio della scheda e' definibile tramite l'apposita circuiteria di interfaccia al BUS presente sulla stessa scheda; questa circuiteria utilizza due Dip Switch ad 8 vie da cui preleva l'indirizzo di mappaggio impostato dall'utente.

Di seguito viene riportata la corrispondenza dei **Dip Switch**, mentre per la selezione del tipo di indirizzamento si faccia riferimento al capitolo **4.5.2**.

Gli 8 byte occupati sono utilizzati sia in fase di output che di input, quindi saranno utilizzati sia per la programmazione della scheda che per la lettura del suo stato e la lettura delle combinazioni determinate dal convertitore.

SW1.1 -> Bit A8 SW1.2 -> Bit A9 SW1.3 -> Bit A10 SW1.4 -> Bit A11 SW1.5 -> Bit A12 SW1.6 -> Bit A13 SW1.7 -> Bit A14 SW1.8 -> Bit A15  $SW2.1 \rightarrow /M1$ SW2.2 -> N.C. SW2.3 -> N.C. SW2.4 -> Bit A3 SW2.5 -> Bit A4 SW2.6 -> Bit A5 SW2.7 -> Bit A6 SW2.8 -> Bit A7

N.B. Tali Dip Switch sono collegati con logica negata, quindi se posto in ON genera uno Zero logico, mentre se posto in OFF genera un Uno logico.

Se ad esempio si dovesse mappare la scheda AAS 12 con indirizzamento normale, all'indirizzo di base 040H, la scheda deve essere configurata come segue:

J7 -> Connessione 1-2.

SW1.n -> Indifferente.

SW2.1 -> Dipende dal tipo di scheda CPU o GPC utilizzata

SW2.2 -> Indifferente.

SW2.3 -> Indifferente.

SW2.4 -> ON

SW2.5 -> ON

SW2.6 -> ON

SW2.7 -> OFF

SW2.8 -> ON

Se invece si dovesse mappare la scheda AAS 12 con indirizzamento

esteso, all'indirizzo di base 0400H, la scheda deve essere configurata come segue:

J7 -> Connessione 2-3. SW1.1 -> ON SW1.2 -> ON SW1.3 -> OFF SW1.4 -> ON SW1.5 -> ON SW1.6 -> ON SW1.7 -> ON SW1.8 -> ON SW2.1 -> Dipende dal tipo di scheda CPU o GPC utilizzata SW2.2 -> Indifferente. SW2.3 -> Indifferente. SW2.4 -> ON SW2.5 -> ON SW2.6 -> ON SW2.7 -> ON SW2.8 -> ON

Per quanto riguarda la disposizione dei due **Dip Switch**, si faccia riferimento alla fig. **4.2** di pag. **10**.

## 5.3. Indirizzamento Registri Interni

Indicando con <indbase> il primo indirizzo degli 8 in cui e' allocata la scheda, ovvero l'indirizzo impostato tramite i dip switch come descritto nel paragrafo precedente, i registri interni della scheda sono visti agli indirizzi riportati nella seguente tabella:

| INDIRIZZO                                                                                                                                                                                                                | REGISTRO IN LETTURA                        | REGISTRO IN SCRITTURA                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-------------------------------------------|

| <pre>  <indbase>+0     <indbase>+1     <indbase>+2     <indbase>+3     <indbase>+4     <indbase>+5     <indbase>+6     <indbase>+7</indbase></indbase></indbase></indbase></indbase></indbase></indbase></indbase></pre> | ADCNTR ADSTAT DATL DATH STIME NCONV COUNT2 | INDL INDH INDH STIME NCONV COUNT2 ADCOUNT |

Table 5-1: Tabella di indirizzamento registri interni

### N.B.

In fase di utilizzo di piu' schede sul BUS ABACO(R), in fase di impostazione dell'indirizzo di mappaggio delle schede, fare attenzione a non allocare piu' schede agli stessi indirizzi (considerare indirizzo di allocazione e numero di byte occupati).

Nel caso questa condizione non venga rispettata si viene a creare una conflittualita' sul **BUS** che pregiudica il funzionamento di tutto il sistema e delle stesse schede.

## 6. GESTIONE SOFTWARE

In questo capitolo vengono riportate tutte le informazioni che riguardano l'utilizzo software della scheda AAS 12; in particolare viene riportata la descrizione di tutti i registri interni che sono stati descritti nel capitolo precedente e la sequenza di operazioni da effettuare per il giusto utilizzo della scheda.

## II Registri interni, significato

## 6.1. Significato dei Registri Interni.

Come descritto nel paragrafo **5.3** la scheda **AAS 12** occupa 8 byte di indirizzamento in cui sono allocati 10 registri da utilizzare per la programmazione della scheda.

Tali registri hanno il seguente significato:

### ADCNTR = ENA EEN M/S 1SH DEL INV TS1 TS0

### dove:

- ENA = Abilitazione generale della sezione di controllo:

se a 1 -> abilitato e viceversa;

- **EEN =** Abilitazione esterna nel caso di programmazione come slave: se a 1 -> abilitazione esterna e viceversa;

- M/S = Selezione del funzionamento Master o Slave:

se a 1 -> Master e viceversa;

- 1SH = Selezione del funzionamento One Shot pari ad una sola conversione: se a 1 -> One Shot, viceversa normale;

- DEL = Attivazione ritardo dell'inizio conversione rispetto

all'attivazione del trigger: se a 1 -> ritardo e viceversa;

- INV = Seleziona eventuale inversione del livello attivo del

trigger: se a 1 -> Trigger invertito e viceversa;

TS1 TS0 = Seleziona il tipo di trigger:

- 0 1 -> Trigger hardware esterno;

- 1 0 -> Trigger hardware interno;

- 1 1 -> Trigger software interno;

### ADSTAT = RDY RUN TRG TST NC NC NC NC

#### dove:

RDY = Indica se e' terminata la sequenza di conversioni:

se a 1 -> conversioni ultimate e viceversa;

RUN = Indica se la scheda sta` eseguendo un ciclo di conversione:

se a 1 -> ciclo di conversione in corso e viceversa;

TRG = Indica se il trigger selezionato e' stato attivato:

se a 1 -> trigger attivato e viceversa;

TST = Segnale di controllo ausiliario portato sul test point X1: se

a 1 -> segnale attivo e viceversa;

NC = Bit privo di significato;

**DATL e DATH =** Corrispondono ai due byte che contengono la combinazione a **12** bit determinata dalla conversione.

In particolare la combinazione complessiva a 12 bit e' costituita, partendo dal bit meno significativo, dagli 8 bit di DATL piu' i 4 bit meno significativi di DATH.

INDL e INDH = Devono essere utilizzati per impostare l'indirizzo

RAM della sezione di salvataggio dati.

In pratica i due registri costituiscono l'indirizzo a 16 bit (di cui INDL costituisce il byte meno significativo e INDH quello piu' significativo) che puo' essere utilizzato per:

- Stabilire l'indirizzo da cui la sezione di controllo deve iniziare la scrittura delle combinazioni dell'**A/D**;

- Stabilire l'indirizzo da cui prelevare i dati in memoria;

**STIME** = Tramite questo registro puo' essere impostato il **Sample Time** delle conversioni da effettuare (scrittura) e verificare a

che punto di questo tempo si trova la sezione di controllo

(lettura).

Tale valore e' espresso in numero di periodi di clock (si veda strippaggio del jumper J6) e puo' variare da un minimo di 15H ad un massimo di FFFFH.

Da notare che anche se il registro e' unico (8 bit) la scrittura/ lettura di dati a 16 bit avviene tramite una doppia Scrittura/ Lettura allo stesso registro; di queste due Scritture/Letture, la

prima coincide con il byte meno significativo e la seconda con quello piu' significativo.

NCONV = Tramite questo registro puo' essere impostato il numero di conversioni da effettuare (scrittura) e verificare quante conversioni siano state effettuate in un certo istante (lettura).

Tale valore coincide esattamente con il numero di conversioni e puo' variare da un minimo di 01H ad un massimo di FFFFH.

se il registro e' unico (8 Da notare che anche Scritture/Letture di dati a 16 bit avviene tramite una doppia Scritture/Letture allo stesso registro; di queste due prima coincide con Scritture/Letture, la il byte meno significativo e la seconda con quello piu' significativo.

**COUNT2 =** Tale registro e' relativo ad un contatore della sezione di controllo che al momento non viene pero' utilizzato per le operazioni di conversione. Dal punto di vista software non deve quindi essere utilizzato in nessun caso.

**ADCOUNT =** Con questo registro si effettua la programmazione della circuiteria di conteggio appartenente alla sezione di controllo.

Al fine di utilizzare correttamente questa sezione, si devono effettuare due scritture consecutive su questo registro; i dati da programmare sono rispettivamente: 34H e 70H.

## 6.2. Programmazione della Scheda.

In questo paragrafo vengono riportate tutte le informazioni necessarie al fine di poter programmare correttamente la scheda AAS 12 in relazione al tipo di funzionamento desiderato. Di seguito e' riportato un elenco di operazioni che devono obbligatoriamente essere effettuate in sequenza:

- 1) Inizializzazione della circuiteria di conteggio scrivendo i due dati 34H e 70H nel registro ADCOUNT;

- 2) Programmazione del **Sample Time** mediante la scrittura del valore a 16 bit nel registro **STIME**;

- 3) Programmazione del numero di conversioni da effettuare mediante la scrittura del valore a 16 bit nel registro **NCON**V;

- 4) Programmare l'indirizzo iniziale di salvataggio delle

combinazioni determinate dall'A/D Converter mediante la scrittura dell'indirizzo a 16 bit nei due registri INDL e INDH;

- 5) Abilitare la sezione di controllo provvedendo a specificare solo il tipo di funzionamento **Master** o **Slave** ed il tipo di trigger corrispondente allo start del ciclo di conversione mediante una scrittura nel registro **ADCNTR**;

- 6) Abilitare la sezione di controllo nella maniera utilizzata al punto 5 provvedendo a definire anche tutti gli altri parametri come tipo di trigger da utilizzare, il suo livello attivo, ecc., mediante una scrittura nel registro ADCNTR;

- 7) Attendere la fine della sequenza di conversioni mediante il test del registro di stato ADSTAT;

- 8) Disabilitare la sezione di controllo in modo da garantire la stabilita' dei dati durante la loro lettura, mediante una scrittura nel registro ADCNTR;

- 9) Programmare l'indirizzo iniziale di lettura dei dati allo stesso valore programmato al punto 4, sempre mediante una scrittura dell'indirizzo a 16 bit nei registri INDL e INDH;

- 10) Leggere un numero di combinazioni desiderate, dove il numero di tali conbinazioni deve essere <= al numero di conversioni impostate al punto 3. La lettura di tali combinazioni avviene tramite letture sucessive dei due registri DATL e DATH, quindi alla prima lettura di questi registri si ottiene la prima combinazione, alla seconda lettura si ottiene la seconda combinazione, ecc (autoincremento dell'indirizzo di lettura);

Tali operazioni sono state illustrate facendo riferimento alla descrizione dei registri interni della scheda, quindi per completezza si faccia riferimento ai par. 5.3 e 6.1.

AAS 12 Rel. 2.00 Page 3.

# 7. SCHEDE ESTERNE A CUI COLLEGARE LA AAS 12.

La scheda AAS 12 ha la possibilita' di accettare come processori la maggior parte di quelli presenti sul BUS ABACO(R) aumentando, cosi', la sua gia' notevole versatilita'.

A titolo di esempio ne riportiamo un breve elenco:

# GPC 535 (General Purpose Controller 80535)

Basata sul potente 80535 Siemens comprende, 16 linee di I/O, 3 linee di acquisizione Encoder bidirezionali a 16 bit, 32K RAM tamponati con batteria al Litio, Real Time Clock, 8 linee di A/D converter da 8 o 10 bit, linea di comunicazione in RS 232 o RS 422-485, Buzzer, unica tensione di alimentazione.

# GPC 65 (General Purpose Controller 6501AQ)

La compatibilita' software del 6501AQ Rockwell con il noto 6502, consente l' utilizzo immediato di quanto gia' sviluppato. 32K RAM tamponati con batteria al Litio, 4 linee di A/D converter da 10 bit, Key Display Controller, linea RS 422 o 423, unica tensione di alimentazione.

## GPC 97 (General Purpose Controller 8097)

Potente controllore a 16 bit basato sullo 8097 Intel con una linea RS 232 ed una in TTL, 32 linee di I/O, 8 linee di A/D converter da 10 bit, Real Time Clock, 16K RAM con batteria al Litio, unica tensione di alimentazione, comodo sviluppo su personal, ecc.

## CPU 01 (Central Processor Unit Z80)

CPU Zilog Z80 B da 6 MHz con 64K RAM dinamica ed uno zoccolo per ospitare un massimo di 32K Bytes di EPROM. Interfaccia al Bus ABACO(R) con una ampia dotazione di Firmware e Software. Disponibilita' di sistemi operativi tipo CP/M, ZCPR3, SCDOS, ecc.

# CPU 03 (Central Processor Unit Z80)

CPU Z80 H da 8MHz con due linee seriali in RS 232 C con Baud Rate settabile da software tra 50 e 38K Baud. Una delle linee e' settabile in RS 485 od in RS 422. Zoccoli per un massimo di 448K Bytes di RAM-EPROM di cui 192K RAM e 256K EPROM. Disponibile CP/M.

# GPC 02 (General Purpose Controller)

Scheda in grado di supportare la famiglia 51 Intel compreso il tipo mascherato Basic. 16 linee di I/O, 3 Counter, linea RS 232, 4 linee di A/D converter da 10 bit, Buzzer, EPROM programmer su scheda, 32K RAM con Back Up al Litio, Key Display Controller, ecc.

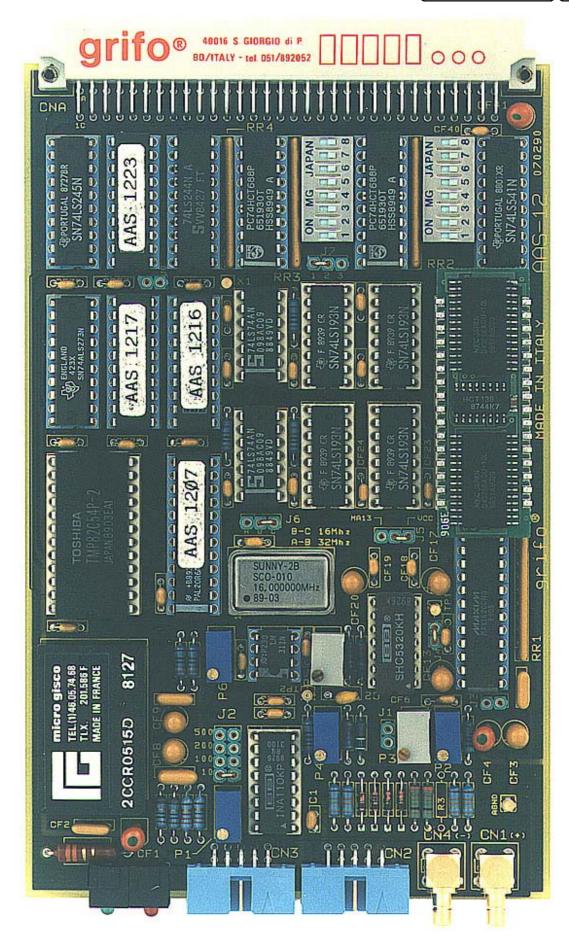

Fig. 7-1: Foto Scheda AAS 12.

AAS 12 Rel. 2.00 Page 35

# GPC F2 (General Purpose Controller Fam. 8052)

Scheda in grado di supportare la famiglia 51 Intel compreso il tipo mascherato Basic. 16 linee di I/O gestite da 8255, 2 linee RS 232, Buzzer, EPROM programmer, 32K RAM su 64K indirizzabili, Real Time Clock con batteria al Litio, 2 Timer Counter tipo 8253.

## GPC 51 (General Purpose Controller Fam. 8051)

Scheda in grado di supportare la famiglia 51 Intel compreso il tipo mascherato Basic. 16 linee di I/O, 3 Counter, linea RS 232, 4 linee di A/D converter da 10 bit, Buzzer, EPROM programmer su scheda, 32K RAM con Back Up al Litio, Orologio, Key Display Controller.

# GPC 68 (General Purpose Controller Fam. 68000)

Due linee RS 232 con Baud Rate settabile da software fino a 38 KBaud piu' una linea RS 485 o RS 422, 3 port paralleli a 8 bit e tre timer gestiti dal 68230, CPU costituita dal 68000 ad 8 MHz, 768 KByte di RAM-EPROM, Watch Dog hardware disinseribile, vari supporti software.

## GPC 80 (General Purpose Controller 84C00 )

Potente controllore o SBC basato sullo Z80. Unica tensione di alimentazione con componenti CMOS. Gestisce le FIO e dispone di implementazioni di CP/M, SCDOS, ZCPR3 ecc. 256 K EPROM, 256 K RAM tamponata con batteria al Litio; Real Time Clock; 2 linee seriali; 16 linee di I/O TTL; 4 counter.

## GPC 451 (General Purpose Controller 80C451 )

Scheda in grado di supportare 80C451 compresa la versione con EPROM. Codice compatibile 8031. 32 linee di I/O TTL; Real Time Clock; 96K a bordo di cui 32K RAM con batteria al Litio. Linea in RS 232 o 422-485. BASIC, FORTH, MONITOR in ROM, PASCAL, C, ecc.

# GPC 552 (General Purpose Controller 80C552 )

Potente controllore con 96K a bordo di cui 32K RAM con batteria al Litio; Real Time Clock; 8 linee di A/D converter da 10 bit; Watchdog; I^2C BUS; Linea in RS 232 o 422; 4 capture Timer; 3 counter; 2 PWM; I/O TTL; BASIC, FORTH, MONITOR, C, PASCAL ecc. in ROM o su PC.

## GPC 188 (General Purpose Controller 80C188)

Controllore basato sull'80C188 Intel fino a 12.5 Mhz; 256K Eprom e 256K Ram con batteria al Litio e protezione in scrittura; Real Time Clock; 4 linee di A/D converter a 13 bit; Watchdog; 2 linee seriali in RS 232, una delle quali puo' essere settata in RS 422485; 24 linee di I/O a livello TTL; vasta disponibilita' di software tra cui MONITOR DEBUGGER, compilatore PASCAL, ecc.

# MRR 16 (Multiplexers Reed Relay a 16 linee)

Scheda periferica di multiplexaggio linee analogiche tramite Reed Rele'; 16 linee di multiplexing doppie (per segnali in corrente o differenziali); visualizzazione del canale prescelto; gestione software semplificata; connettori standardizzati per il collegamento con le schede di A/D.

# MSS 16 (Multiplexers Solid State a 16 linee)

Scheda periferica di multiplexaggio linee analogiche tramite commutatori statici; 16 linee di multiplexing doppie (per segnali in corrente o differenziali); visualizzazione del canale prescelto; gestione software semplificata; connettori standardizzati per il collegamento con le schede di A/D.

# RCV 420 (Receiver Current to Voltage 4-20 mA.)

Scheda periferica provvista di 10 linee di multiplexing doppie (per segnali in corrente) e di sezione di interfaccia segnali in corrente 4-20 mA. con segnali in tensione 0-5V.; separazione galvanica tra la sezione ricevente e quella di trasformazione; connettori standardizzati per il collegamento con le linee di A/D.

# A. DISPOSIZIONE JUMPERS

Fig. A-1: Disposizione Jumpers per Sezione Analogica

AAS 12 Rel. 2.00

**-** Page 39

**AAS 12**

Rel. 2.00

# General Description

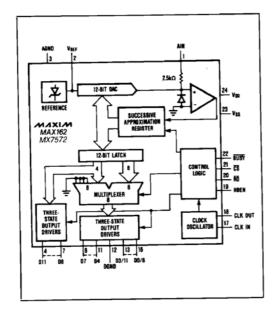

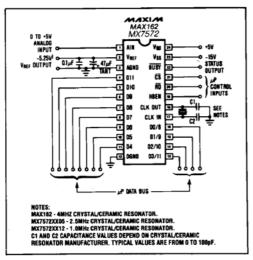

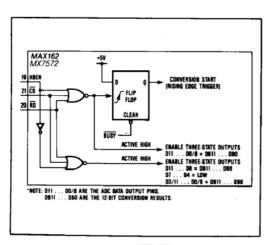

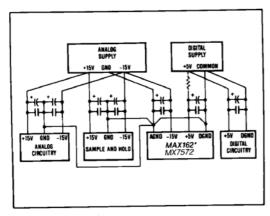

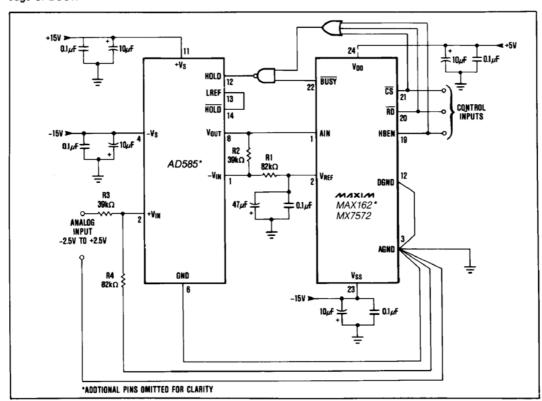

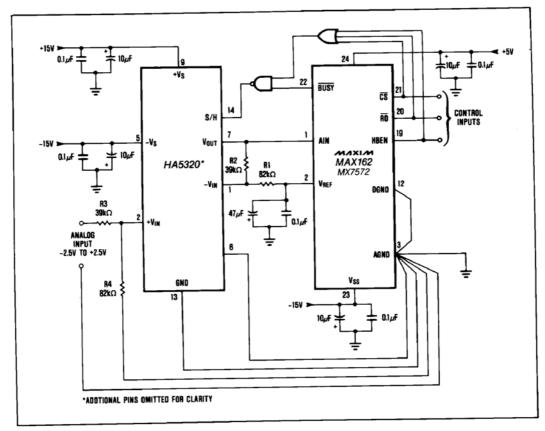

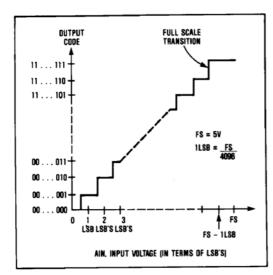

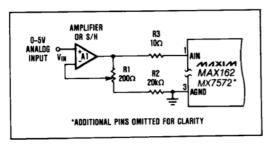

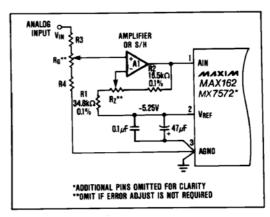

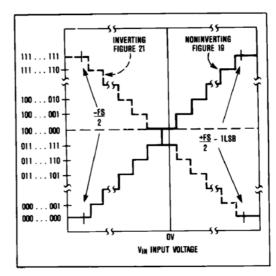

The MAX162 and MX7572 are complete 12-Bit analog-to-digital converters (ADC's) that combine high speed, low power consumption, and an on-chip voltage reference. The conversion times are 3µs (MAX162) and 5 and 12µs (MX7572). The buried zener reference provides low drift and low noise performance.

External component requirements are limited to only decoupling capacitors for the power supply and reference voltages. On-chip clock circuitry is also included which can either be driven from an external source, or in stand-alone applications, can be used with a crystal.

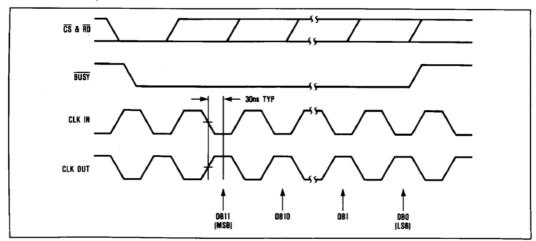

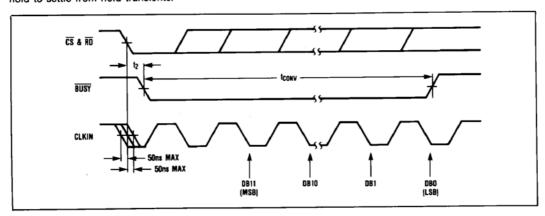

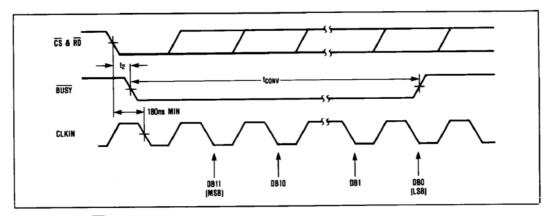

The MAX162/MX7572 uses a standard microprocessor interface architecture. Three-state data <u>outputs</u> are controlled by Read (RD) and Chip Select (CS) inputs. Data access and bus release times of 90 and 75ns respectively ensure compatibility with most popular microprocessors without resorting to wait states.

# **Applications**

Digital Signal Processing (DSP) High Accuracy Process Control High Speed Data Acquisition Electro-Mechanical Systems

# Functional Diagram

## Features

- ♦ 12-Bit Resolution and Linearity

- 3μs (MAX162), 5μs and 12μs (.MX7572)

Conversion Times

- ♦ No missing Codes

- **♦ On-Chip Voltage Reference**

- 90ns Access Time

- **♦ 215mW Max Power Consumption**

- ♦ 24-Lead Narrow DIP Package

## **Ordering Information**

| PART           | TEMP. RANGE     | PACKAGE*    | ERROR<br>(LSB) |

|----------------|-----------------|-------------|----------------|

| 3µs CONVERSION | ON TIME         |             |                |

| MAX162ACNG     | 0°C to +70°C    | Plastic DIP | ±1/2           |

| MAX162BCNG     | 0°C to +70°C    | Plastic DIP | ±1             |

| MAX162CCNG     | 0°C to +70°C    | Plastic DIP | ±1             |

| MAX162ACWG     | 0°C to +70°C    | Wide SO     | ±1/2           |

| MAX162BCWG     | 0°C to +70°C    | Wide SO     | ±1             |

| MAX162CCWG     | 0°C to +70°C    | Wide SO     | ±1             |

| MAX162CC/D     | 0°C to +70°C    | Dice**      | ±1             |

| MAX162AING     | -40°C to +85°C  | Plastic DIP | ±1/2           |

| MAX162BING     | -40°C to +85°C  | Plastic DIP | ±1             |

| MAX162CING     | -40°C to +85°C  | Plastic DIP | ±1             |

| MAX162AMRG     | -55°C to +125°C | CERDIP      | ±1/2           |

| MAX162BMRG     | -55°C to +125°C | CERDIP      | ±1             |

| MAX162CMRG     | -55°C to +125°C | CERDIP      | ±1             |

Ordering Information continued at end of data sheet.

\*All devices—24 lead packages

\*\* Consult factory for dice specifications.

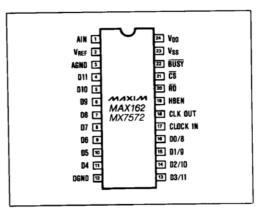

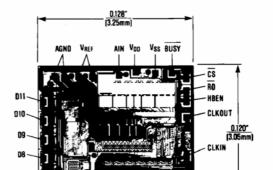

# Pin Configuration

MIXIM

Maxim Integrated Products 1

For free samples & the latest literature: http://www.maxim-ic.com, or phone 1-800-998-8800. For small orders, phone 1-800-835-8769.

# **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to DGND0.3V to +7V                                                    |

|---------------------------------------------------------------------------------------|

| V <sub>SS</sub> to DGND +0.3V to -17V                                                 |

| AGND to DGND0.3V, V <sub>22</sub> + 0.3V                                              |

| AIN to AGND15V to +15V                                                                |

| Digital Input Voltage to DGND0.3V, V <sub>DD</sub> + 0.3V (Pins 17, 19-21)            |

| Digital Output Voltage to DGND0.3V, V <sub>DD</sub> + 0.3V (pins 4-11, 13-16, 18, 22) |

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum ratings conditions for extended periods may affect device reliability.

# **ELECTRICAL CHARACTERISTICS**

(VDD = +5V  $\pm$ 5%, VSS = -15V  $\pm$ 5%; Slow Memory Mode; T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub> unless otherwise noted fCLK = 4MHz for MAX162, 2.5MHz for MX7572XX05 and 1MHz for MX7572XX12)

| PARAMETER                      | SYMBOL | CONDITIO                                                                | ONS                            | MIN      | TYP   | MAX                | UNITS  |

|--------------------------------|--------|-------------------------------------------------------------------------|--------------------------------|----------|-------|--------------------|--------|

| ACCURACY                       |        |                                                                         |                                |          |       |                    | 0.4110 |

| Resolution                     |        |                                                                         |                                | 12       |       |                    | Bits   |

|                                |        | MAX162A, MX7572L/C/U                                                    | T <sub>A</sub> = 25°C          |          |       | ±1/2               | Dito   |

| Integral Non-Linearity         | INL    | MAX162AC, AI, MX7572L/C<br>MAX162AM, MX7572U<br>MAX162B/C, MX7572K/B/T/ |                                |          |       | ±1/2<br>±3/4<br>±1 | LSB    |

| Differential Non-Linearity     | DNL    | Guaranteed Monotonic Ove                                                | r Temp.                        |          |       | ±1                 | LSB    |

|                                |        | MAX162C,<br>MX7572J/A/S                                                 | TA = 25°C<br>TA = TMIN to TMAX |          |       | ±4<br>±6           |        |

| Offset Error (Note 1)          |        | MAX162B,<br>MX7572K/B/T                                                 | TA = 25°C<br>TA = TMIN to TMAX |          |       | ±3<br>±5           | LSB    |

|                                |        | MAX162A,<br>MX7572L/C/U                                                 | TA = 25°C<br>TA = TMIN to TMAX |          |       | ±3<br>±4           |        |

|                                |        | MAX162C,<br>MX7572J/A/S                                                 | T <sub>A</sub> = 25°C          |          |       | ±15                |        |

| Full Scale Error (Note 2)      |        | MAX162B,<br>MX7572K/B/T                                                 | TA = 25°C                      |          |       | ±10                | LSB    |

|                                |        | MAX162A,<br>MX7572L/C/U                                                 | TA = 25°C                      |          |       | ±10                |        |

| Full Scale Tempco (Notes 3, 4) |        | MAX162C, MX7572J/A/S<br>MAX162B/A, MX7572K/B/T,                         | MX7572L/C/U                    |          |       | ±45<br>±25         | ppm/°C |

| ANALOG INPUT                   |        |                                                                         |                                |          |       |                    |        |

| Input Voltage Range            |        | For Bipolar Input see Figures                                           | 19-21                          | 0        |       |                    | v      |

| Input Current                  |        | AIN = 0V to +5V                                                         |                                |          |       | 3.5                | mA     |

| INTERNAL REFERENCE             |        |                                                                         |                                |          |       |                    |        |

| VREF Output Voltage            |        | T <sub>A</sub> = 25°C                                                   |                                | -5.2     | -5.25 | -5.3               | V      |

| VREF Output Tempco (Note 5)    |        | MAX162C, MX7572J/A/S<br>MAX162B/A, MX7572K/B/T,                         |                                | 40<br>20 |       | ppm/°C             |        |

| Output Current Sink Capability |        | (Note 6)                                                                |                                |          |       | 500                | μА     |

2\_\_\_\_\_\_MAXIM

# **ELECTRICAL CHARACTERISTICS (Continued)**

$(V_{DD} = +5V \pm 5\%, V_{SS} = -15V \pm 5\%; Slow Memory Mode: T_A = T_{MIN} to T_{MAX}$  unless otherwise noted fCLK = 4MHz for MAX162, 2.5MHz for MX7572XX05 and 1MHz for MX7572XX12)

| PARAMETER                                     | SYMBOL | CON                                                        | DITIONS                                                                     | MIN  | TYP               | MAX          | UNITS      |

|-----------------------------------------------|--------|------------------------------------------------------------|-----------------------------------------------------------------------------|------|-------------------|--------------|------------|

| POWER SUPPLY REJECTION                        |        |                                                            |                                                                             |      |                   |              |            |

| V <sub>DD</sub> Only                          |        | FS Change, Vss = -15                                       | V, V <sub>DD</sub> = 4.75 to 5.25V                                          |      | ±1/2              |              | LSB        |

| Vss Only                                      |        | FS Change, V <sub>DD</sub> = 5V<br>MAX162/MX7572<br>MAX162 | V <sub>SS</sub> = -14.25V to -15.75V<br>V <sub>SS</sub> = -11.4V to -12.6V  |      | ±1/8<br>±1/8      |              | LSB<br>LSB |

| LOGIC INPUTS                                  |        |                                                            |                                                                             |      |                   |              |            |

| Input Low Voltage                             | VIL    | CS, RD, HBEN, CLKIN                                        |                                                                             |      |                   | 0.8          | ٧          |

| Input High Voltage                            | VIH    | CS, RD, HBEN, CLKIN                                        | 2.4                                                                         |      |                   | ٧            |            |

| Input Capacitance (Note 7)                    | CIN    | CS, RD, HBEN, CLKIN                                        |                                                                             |      |                   | 10           | pF         |

| Input Current                                 | liN    | CS, RD, HBEN,<br>CLKIN                                     |                                                                             |      | ±10<br>±20        | μА           |            |

| LOGIC OUTPUTS                                 |        |                                                            |                                                                             |      |                   |              |            |

| Output Low Voltage                            | VoL    | D11-D0/8, BUSY, CLK                                        | OUT ISINK = 1.6mA                                                           |      |                   | 0.4          | V          |

| Output High Voltage                           | Voн    | D11-D0/8, BUSY, CLK                                        | OUT ISOURCE = 200µA                                                         | 4    |                   |              | ٧          |

| Floating State Leakage Current                | ILKG   | D11-D0/8, VOUT = 0V                                        | to V <sub>DD</sub>                                                          |      |                   | ±10          | μА         |

| Floating State Output<br>Capacitance (Note 7) | Соит   |                                                            |                                                                             |      |                   | 15           | рF         |

| CONVERSION TIME                               |        |                                                            |                                                                             |      |                   |              |            |

| MAX162                                        | tconv  | f <sub>CLK</sub> = 4MHz                                    | Synchronous<br>(13 clock cycles)<br>Asynchronous<br>(12 to 13 clock cycles) | 3    |                   | 3.25<br>3.25 | μѕ         |

|                                               |        |                                                            | Synchronous                                                                 |      |                   | 5            |            |

| MX7572XX05                                    | tCONV  | fCLK = 2.5MHz                                              | (12.5 clock cycles)<br>Asynchronous<br>(12 to 13 clock cycles)              | 4.8  |                   | 5.2          | μѕ         |

|                                               |        |                                                            | Synchronous                                                                 |      |                   | 12.5         |            |

| MX7572XX12                                    | tconv  | fclk = 1MHz                                                | (12.5 clock cycles)<br>Asynchronous<br>(12 to 13 clock cycles)              | 12   |                   | 13           | μѕ         |

| POWER REQUIREMENTS                            |        |                                                            |                                                                             |      |                   |              |            |

| VDD                                           |        | ±5% for Specified Perf                                     | ormance                                                                     | 4.75 | 5                 | 5.25         | V          |

| Vss (Note 8)                                  |        | ±5% MAX162<br>±5% MX7572                                   |                                                                             |      | -12 or -15<br>-15 |              | ٧          |

| lDD .                                         |        | CS = RD = VDD, AIN =                                       | = 5V                                                                        |      | 5                 | 7            | mA         |

| ISS                                           |        | CS = RD = VDD, AIN =                                       | = 5V                                                                        |      | 8                 | 12           | mA         |

| Power Dissipation                             |        | VDD = +5V, VSS = -15                                       | V                                                                           |      | 145               | 215          | mW         |

Note 1: Typical change over temp is  $\pm 1LSB$ Note 2:  $V_{DD} = +5V$ ,  $V_{SS} = -15V$ ,  $F_S = +5.000V$ , Ideal last code transition =  $F_S -3/2LSB$ Note 3: Full Scale  $T_S = 4.5000V$ , Ideal last code transition =  $F_S -3/2LSB$ Note 3: Full Scale  $T_S = 4.5000V$ , where 4.5000V is full scale change from  $T_S = 2.5000V$  to  $T_S = 2.5000V$ .

Note 4: Includes internal reference drift.

Note 5:  $V_{REF} = 1.5000V$ , where 4.5000V reference voltage change from  $T_S = 2.5000V$  to  $T_S = 1.5000V$ .

Note 6: Output current should not change during conversion.

Note 7: Guaranteed by design, not subject to test.

Note 8:  $V_{SS} = -1.2V \pm 5\%$  for the MAX162 only. Functional operation is guaranteed by testing offset error and full scale error.

MIXIM

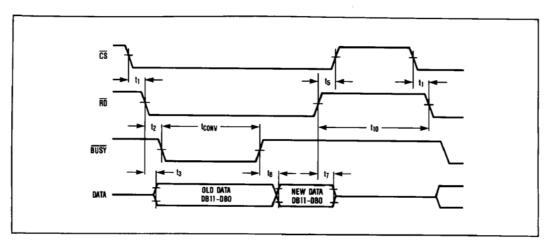

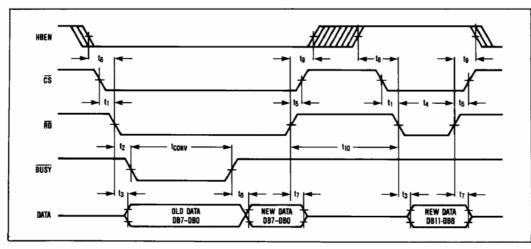

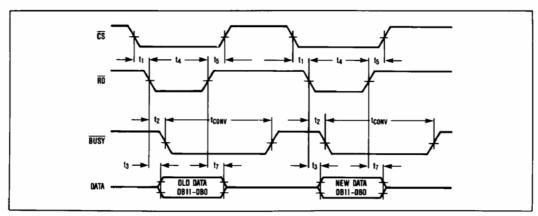

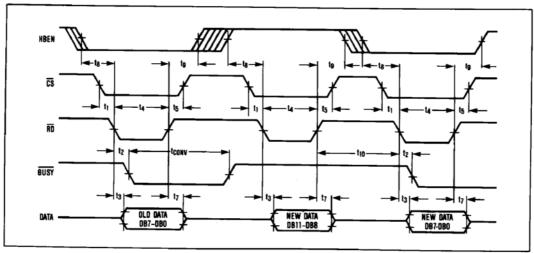

TIMING CHARACTERISTICS (Note 9)  $(V_{DD} = +5V, V_{SS} = -15V; T_A = T_{MIN} \text{ to } T_{MAX} \text{ unless otherwise noted.})$

| PARAMETER                               | SYMBOL          | CONDITIONS                                      | T <sub>A</sub> = 25°C |          |           | MX75           | 162C/I<br>72J/K/L<br>72A/B/C | MAX162M<br>MX7572S/T/U |            | UNITS |

|-----------------------------------------|-----------------|-------------------------------------------------|-----------------------|----------|-----------|----------------|------------------------------|------------------------|------------|-------|

|                                         |                 |                                                 | MIN                   | TYP      | MAX       | MIN            | MAX                          | MIN                    | MAX        | 1     |

| CS to RD Setup Time                     | t,              |                                                 | 0                     |          |           | 0              |                              | 0                      |            | ns    |

| RD to BUSY Delay                        | t <sub>2</sub>  | C <sub>L</sub> = 50pF                           |                       | 90       | 190       |                | 230                          |                        | 270        | ns    |

| Data Access Time (Note 10)              | t <sub>3</sub>  | C <sub>L</sub> = 20pF<br>C <sub>L</sub> = 100pF |                       | 60<br>70 | 90<br>125 |                | 110<br>150                   |                        | 120<br>170 | ns    |

| RD Pulse Width                          | t <sub>4</sub>  |                                                 | t <sub>3</sub>        |          |           | t <sub>3</sub> |                              | t <sub>3</sub>         |            |       |

| CS to RD Hold Time                      | t <sub>5</sub>  |                                                 | 0                     |          |           | 0              |                              | 0                      |            | ns    |

| Data Setup Time After BUSY<br>Note (10) | t <sub>6</sub>  |                                                 |                       |          | 70        |                | 90                           |                        | 100        | ns    |

| Bus Relinquish Time (Note 11)           | t <sub>7</sub>  |                                                 | 20                    |          | 75        | 20             | 85                           | 20                     | 90         | ns    |

| HBEN to RD Setup Time                   | t <sub>8</sub>  |                                                 | 0                     |          |           | 0              |                              | 0                      |            | ns    |

| HBEN to RD Hold Time                    | t <sub>9</sub>  |                                                 | 0                     |          |           | 0              |                              | 0                      |            | ns    |

| Delay Between Read Operations           | t <sub>10</sub> |                                                 | 200                   |          |           | 200            |                              | 200                    |            | ns    |

Timing specifications are sample tested at 25°C to ensure compliance. All input control signals are specified with  $t_r = t_f = 5$ ns (10% to 90% of +5V) and timed from a voltage level of +1.6V.  $t_3$  and  $t_6$  are measured with the load circuits of Figure 1 and defined as the time required for an output to cross 0.8V or 2.4V. Note 9:

Note 11: t<sub>7</sub> is defined as the time required for the data lines to change 0.5V when loaded with the circuits of Figure 2.

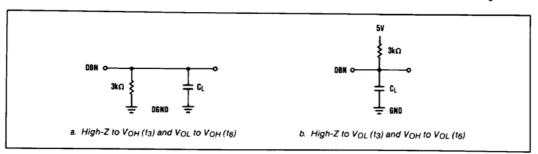

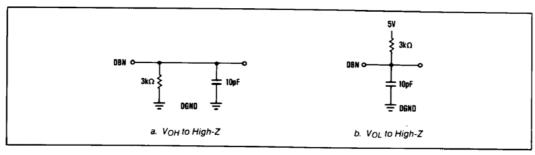

Figure 1. Load Circuits for Access Time

Figure 2. Load Circuits for Output Float Delay

MIXIM

# Pin Description

| PIN   | NAME             | FUNCTION                                                                                                                              |

|-------|------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 1     | AIN              | Analog Input, 0 to +5V unipolar input                                                                                                 |

| 2     | V <sub>REF</sub> | -5.25V Reference Output                                                                                                               |

| 3     | AGND             | Analog Ground                                                                                                                         |

| 4-11  | D11-D4           | Three-State Data Outputs                                                                                                              |

| 12    | DGND             | Digital Ground                                                                                                                        |

| 13-16 | D3/11-D0/8       | Three-State Data Outputs                                                                                                              |

| 17    | CLKIN            | Clock Input. An external TTL/CMOS compatible clock may be applied to this pin or a crystal can be connected between CLKIN and CLKOUT. |

| 18    | CLKOUT           | Clock Output. An inverted CLKIN signal appears at this pin.                                                                           |

| PIN | NAME            | FUNCTION                                                                                                                                                                          |

|-----|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19  | HBEN            | High Byte Enable Input. This pin is used to multiplex the internal 12-bit conversion result into the lower bit outputs (D7-D0/8). HBEN also disables conversion starts when HIGH. |

| 20  | RD              | READ Input. This active low signal starts a conversion when CS and HBEN are low. RD also enables the output drivers when CS is low.                                               |

| 21  | cs              | The CHIP SELECT Input must be low for the ADC to recognize RD and HBEN inputs.                                                                                                    |

| 22  | BUSY            | The BUSY Output is low when a conversion is in progress.                                                                                                                          |

| 23  | V <sub>SS</sub> | Negative Supply, -15V for MX7572 and -15V or -12V for MAX162.                                                                                                                     |

| 24  | V <sub>DD</sub> | Positive Supply, +5V.                                                                                                                                                             |

## Data Bus Output, CS & RD = LOW

| Data Das Cat | ,u., oo | w     |       |       | _     |       |        |        |        |        |        |        |

|--------------|---------|-------|-------|-------|-------|-------|--------|--------|--------|--------|--------|--------|

|              | Pin 4   | Pin 5 | Pin 6 | Pin 7 | Pin 8 | Pin 9 | Pin 10 | Pin 11 | Pin 13 | Pin 14 | Pin 15 | Pin 16 |

| MNEMONIC.    | D11     | D10   | D9    | D8    | D7    | D6    | D5     | D4     | D3/11  | D2/10  | D1/9   | D0/8   |

| HBEN = LOW   | DB11    | DB10  | DB9   | DB8   | DB7   | DB6   | DB5    | DB4    | DB3    | DB2    | DB1    | DB0    |