# GPC® 15A

**General Purpose Controller 84C15**

# MANUALE TECNICO

Via dell' Artigiano, 8/6 40016 San Giorgio di Piano (Bologna) ITALY E-mail: grifo@grifo.it

http://www.grifo.it http://www.grifo.com Tel. +39 051 892.052 (r.a.) FAX: +39 051 893.661

GPC® 15A Edizione 3.20 Rel. 28 Marzo 2000

GPC®, grifo®, sono marchi registrati della ditta grifo®

# GPC® 15A

## **General Purpose Controller 84C15**

# MANUALE TECNICO

Formato singola Europa da 100x160 mm con interfaccia per il **BUS industriale** ABACO®; CPU CMOS 84C15 con quarzo da 20 MHz; fino a 512K EPROM o 256K FLASH EPROM e fino a 128K SRAM opzionalmente tamponata; RAM/ROM disk gestite tramite FGDOS; EEPROM seriale fino a 8 K; 4 o 12 dip Switch e un jumper di configurazione leggibili da software; **2 LEDs** di attività; **Buzzer** pilotabile via software; **2** linee seriali in RS 232 di cui una settabile in RS 422, RS 485 o Current Loop con baud rate fino a 38,4 KBaud; fino a 40 linee di I/O TTL; 4 timer counter; fino a 8K di SRAM opzionalmente tamponata con RTC in grado di gestire giorno, mese, anno, giorno della settimana, ore, minuti, secondi; Watch Dogs resettabili da software visualizzati tramite LED; unica tensione di alimentazione a **5Vdc**, **180 mA**; vasta disponibilità di software di base e di ambienti di sviluppo che consentono di poter utilizzare la scheda tramite un normale PC, tra i pacchetti disponibili si possono citare: FGDOS 15A; PASCAL 80; CBZ 80; NSB8; RSD 15A; HI TECH C 80; GET 80; DDS MICRO C 85; NO ICE Z80; ecc.

Via dell' Artigiano, 8/6 40016 San Giorgio di Piano (Bologna) ITALY

E-mail: grifo@grifo.it

http://www.grifo.it http://www.grifo.com Tel. +39 051 892.052 (r.a.) FAX: +39 051 893.661

GPC<sup>®</sup> 15A

Edizione 3.20

Rel. 28 Marzo 2000

GPC®, grifo®, sono marchi registrati della ditta grifo®

# Vincoli sulla documentazione grifo® Tutti i Diritti Riservati

Nessuna parte del presente manuale può essere riprodotta, trasmessa, trascritta, memorizzata in un archivio o tradotta in altre lingue, con qualunque forma o mezzo, sia esso elettronico, meccanico, magnetico ottico, chimico, manuale, senza il permesso scritto della **grifo**<sup>®</sup>.

#### **IMPORTANTE**

Tutte le informazioni contenute sul presente manuale sono state accuratamente verificate, ciononostante **grifo**® non si assume nessuna responsabilità per danni, diretti o indiretti, a cose e/o persone derivanti da errori, omissioni o dall'uso del presente manuale, del software o dell' hardware ad esso associato.

**grifo**<sup>®</sup> altresi si riserva il diritto di modificare il contenuto e la veste di questo manuale senza alcun preavviso, con l' intento di offrire un prodotto sempre migliore, senza che questo rappresenti un obbligo per **grifo**<sup>®</sup>.

Per le informazioni specifiche dei componenti utilizzati sui nostri prodotti, l'utente deve fare riferimento agli specifici Data Book delle case costruttrici o delle seconde sorgenti.

#### LEGENDA SIMBOLI

Nel presente manuale possono comparire i seguenti simboli:

Attenzione: Pericolo generico

Attenzione: Pericolo di alta tensione

# Marchi Registrati

, GPC®, grifo®: sono marchi registrati della grifo®.

Altre marche o nomi di prodotti sono marchi registrati dei rispettivi proprietari.

# **INDICE GENERALE**

| INTRODUZIONE                                                 | 1  |

|--------------------------------------------------------------|----|

| VERSIONE SCHEDA                                              | 1  |

| INFORMAZIONI GENERALI                                        | 2  |

| SIO                                                          | 3  |

| TIMER COUNTER                                                | 3  |

| LINEE DI I/O DEL PIO                                         | 3  |

| DISPOSITIVI DI MEMORIA                                       | 3  |

| PROCESSORE DI BORDO                                          | 4  |

| COMUNICAZIONE SERIALE                                        | 4  |

| ABACO® BUS                                                   |    |

| DISPOSITIVI DI CLOCK                                         | 6  |

| LINEE DI I/O DEL PPI 82C55                                   |    |

| WATCH DOG                                                    | 6  |

| LOGICA DI CONTROLLO                                          | 6  |

| MMU                                                          |    |

| BUZZER                                                       |    |

| RTC                                                          | 7  |

| CARATTERISTICHE TECNICHE                                     | 8  |

| CARATTERISTICHE GENERALI                                     | 8  |

| CARATTERISTICHE FISICHE                                      | 8  |

| CARATTERISTICHE ELETTRICHE                                   | 9  |

| INSTALLAZIONE                                                | 10 |

| CONNESSIONI CON IL MONDO ESTERNO                             |    |

| CN1 - CONNETTORE PER I/O DEL CTC                             |    |

| CN2 - CONNETTORE PER I/O DEL PPI                             |    |

| DSW2 - ZOCCOLO PER I/O DEL PPI 82C55 DA PORT B               |    |

| CN3 - CONNETTORE LINEE SERIALI RS 422, RS 485 E CURRENT LOOP |    |

| CN4 - CONNETTORE PER COMUNICAZIONE SERIALE IN RS 232 E CTC   |    |

| CN5 - CONNETTORE PER I/O DEL PIO                             | 22 |

| K1 - CONNETTORE PER ABACO® BUS                               | 24 |

| INTERFACCIAMENTO DEGLI I/O CON IL CAMPO                      | 26 |

| SEGNALAZIONI VISIVE                                          | 26 |

| INTERFACCE PER I/O DIGITALI                                  | 27 |

| INPUT DI BORDO                                               | 27 |

| JUMPERS                                                      | 28 |

| JUMPERS A 2 VIE                                              | 30 |

| JUMPERS A 3 VIE                                              | 30 |

| JUMPER A 4 VIE                                               | 32 |

| JUMPER A 5 VIE                                               | 32 |

| RESET E WATCH DOG                                            |    |

| COMUNICAZIONE SERIALE                                        | 34 |

Rel. 3.20

| INGRESSI DI CONFIGURAZIONE                      | 36  |

|-------------------------------------------------|-----|

| INTERRUPTS                                      |     |

| SELEZIONE MEMORIE                               |     |

| DESCRIZIONE SOFTWARE                            | 40  |

| MAPPAGGI ED INDIRIZZAMENTI                      | 44  |

| MAPPAGGIO DELLE RISORSE DI BORDO                |     |

| MAPPAGGIO ABACO® BUS                            |     |

| MAPPAGGIO MEMORIE                               |     |

| MAPPAGGIO I/O                                   |     |

| DESCRIZIONE SOFTWARE DELLE PERIFERICHE DI BORDO | 50  |

| WATCH DOG ESTERNO                               |     |

| EEPROM SERIALE                                  |     |

| LEDS DI ATTIVITÀ                                |     |

| INGRESSI DI CONFIGURAZIONE                      |     |

| BUZZER                                          |     |

| MEMORY MANAGEMENT UNIT                          |     |

| SIO                                             |     |

| PIO                                             |     |

| CTC                                             |     |

| WATCH DOG INTERNO                               |     |

| SRAM TAMPONATA + RTC                            |     |

| BAUD RATE GENERATOR                             |     |

| PPI 82C55                                       | 59  |

| SCHEDE ESTERNE                                  | 60  |

| BIBLIOGRAFIA                                    | 64  |

| APPENDICE A: SCHEMI ELETTRICI                   | A-1 |

| APPENDICE B: DESCRIZIONE COMPONENTI DI BORDO    | B-1 |

| CPU Z84C15                                      | B-1 |

| APPENDICE C: INDICE ANALITICO                   | C-1 |

# INDICE DELLE FIGURE

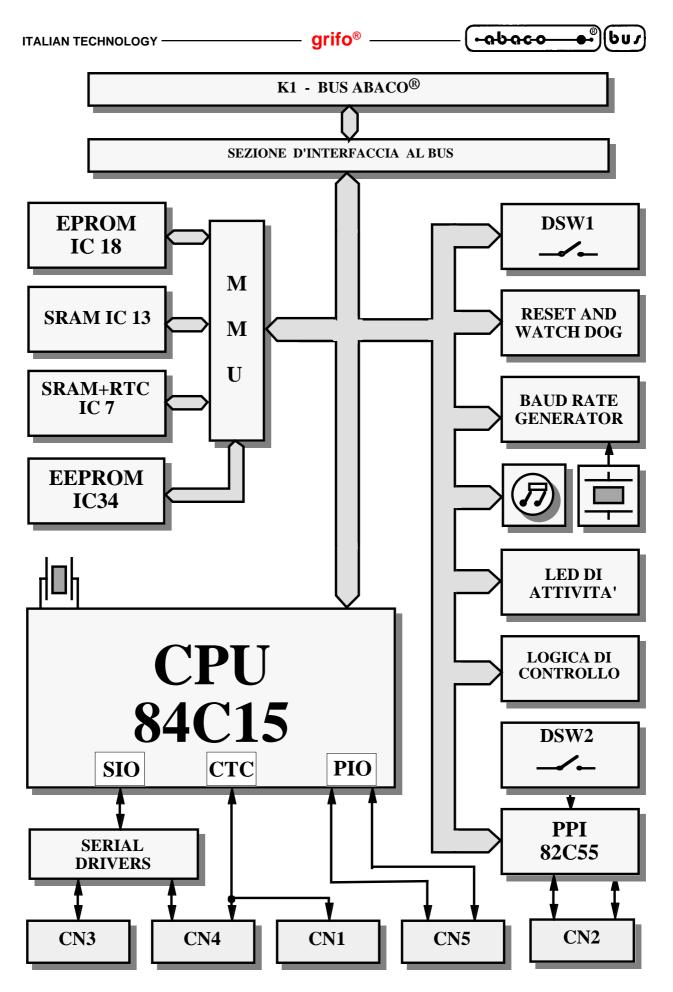

| FIGURA 1: SCHEMA A BLOCCHI                                                 | 5   |

|----------------------------------------------------------------------------|-----|

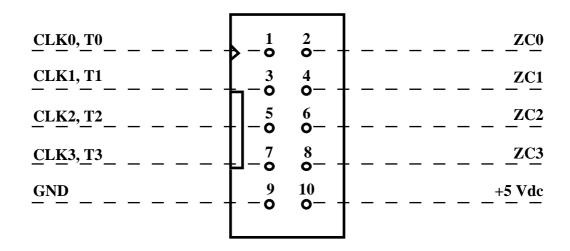

| FIGURA 2: CN1 - CONNETTORE PER I/O DEL CTC                                 | 10  |

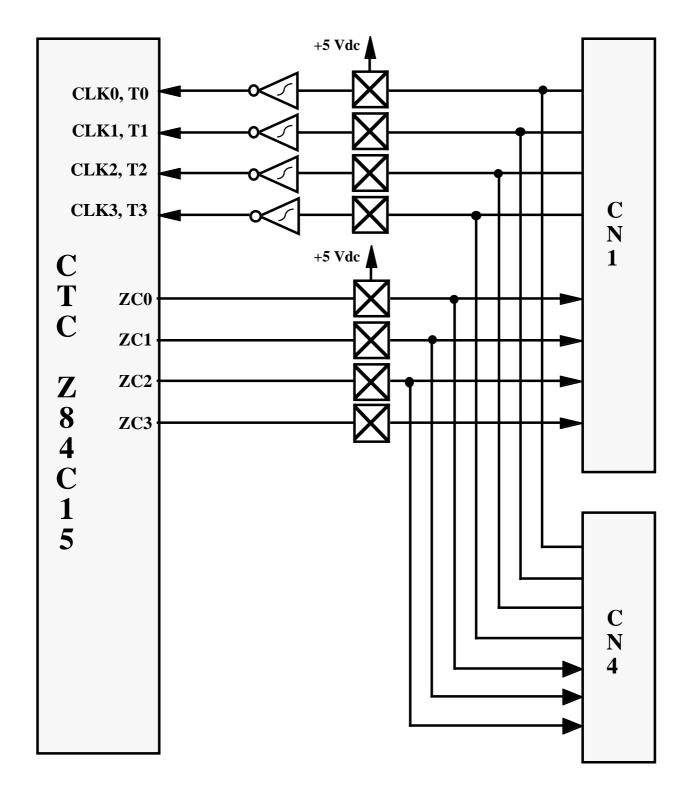

| FIGURA 3: SCHEMA DI COLLEGAMENTO CTC                                       |     |

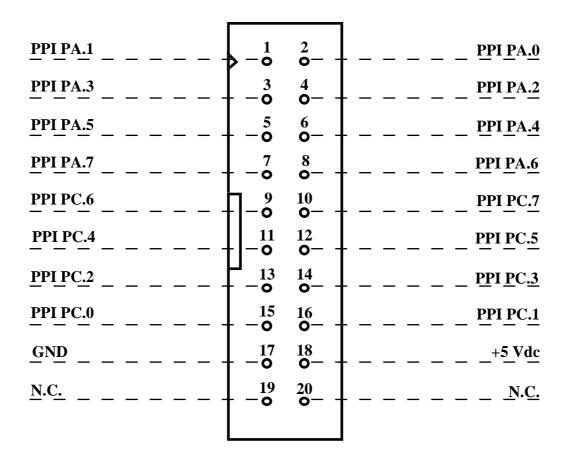

| FIGURA 4: CN2 - CONNETTORE PER I/O DEL PPI 8255 DA PORT A E C              | 12  |

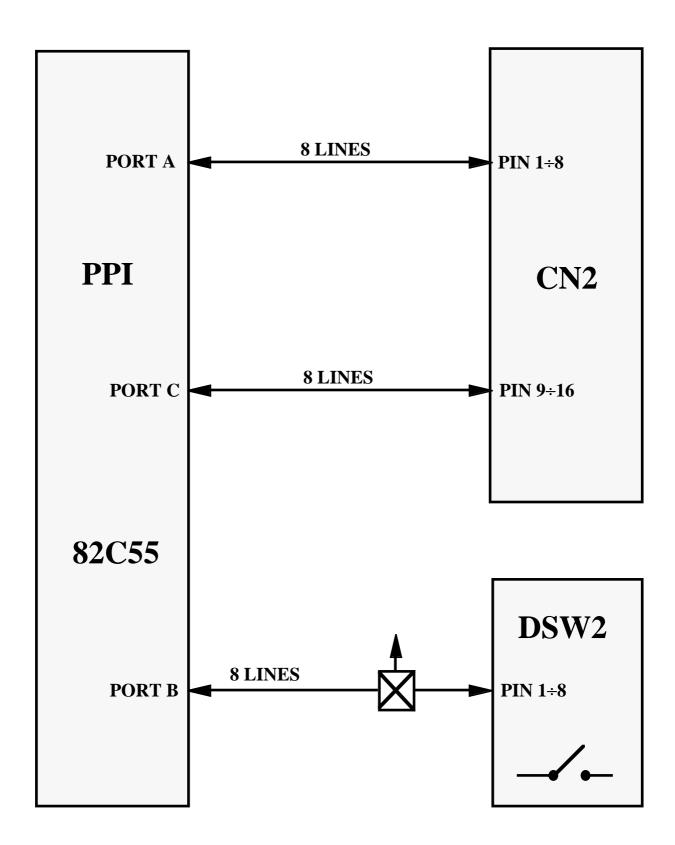

| FIGURA 5: SCHEMA DEL COLLEGAMENTO LINEE DI I/O DEL PPI                     | 13  |

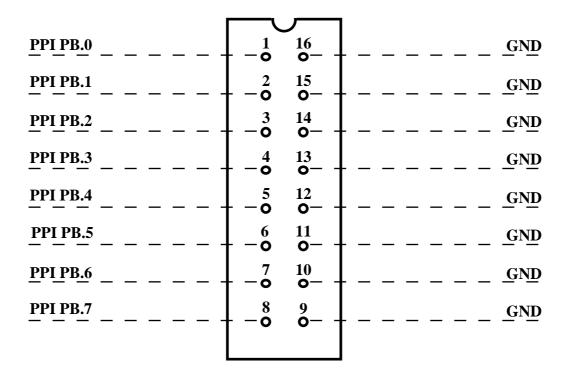

| FIGURA 6: DSW2 - ZOCCOLO PER I/O DEL PPI 82C55 DA PORT B                   | 14  |

| FIGURA 7: CN3 - CONNETTORE PER LINEE SERIALI RS 422, RS 485 E CURRENT LOOP |     |

| FIGURA 8: CN4 - CONNETTORE PER COMUNICAZIONE SERIALE IN RS 232 E CTC       |     |

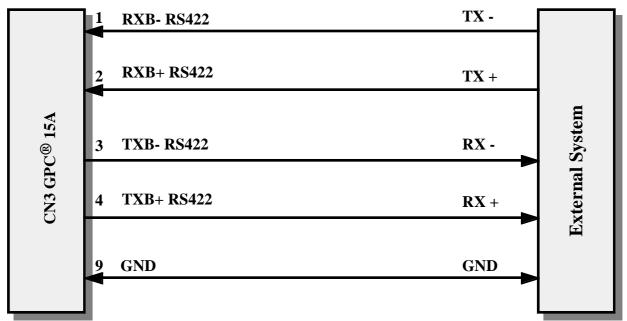

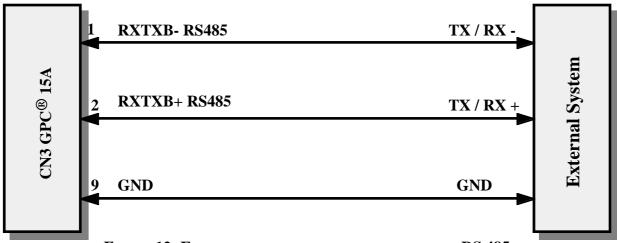

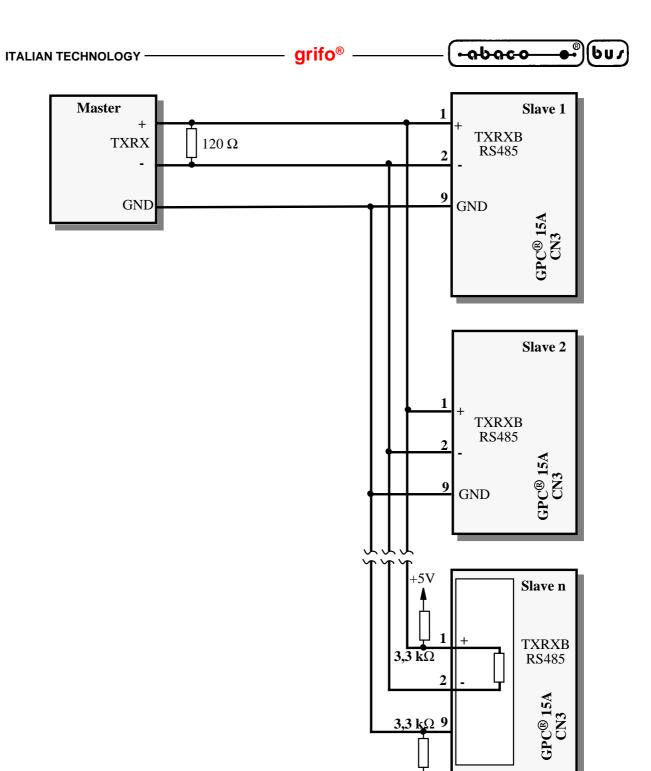

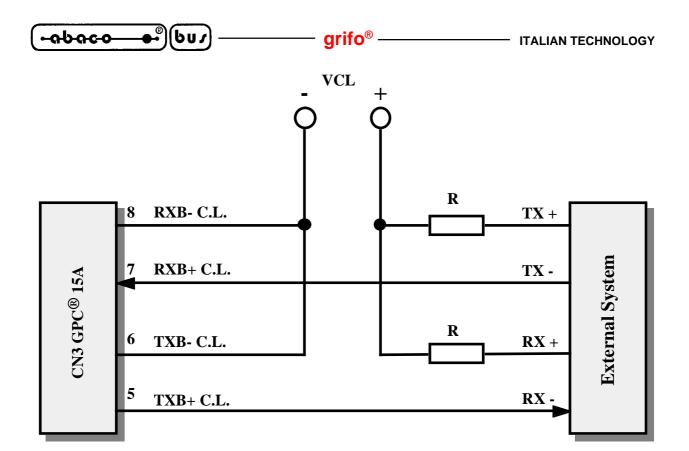

| FIGURA 9: SCHEMA DI COLLEGAMENTO SERIALI RS 422, RS 485 E CURRENT LOOP     | 17  |

| FIGURA 10: ESEMPIO DI COLLEGAMENTO PUNTO IN RS 232                         | 18  |

| FIGURA 11: ESEMPIO DI COLLEGAMENTO PUNTO PUNTO IN RS 422                   | 18  |

| FIGURA 12: ESEMPIO DI COLLEGAMENTO PUNTO PUNTO IN RS 485                   | 18  |

| FIGURA 13: ESEMPIO DI COLLEGAMENTO IN RETE IN RS 485                       | 19  |

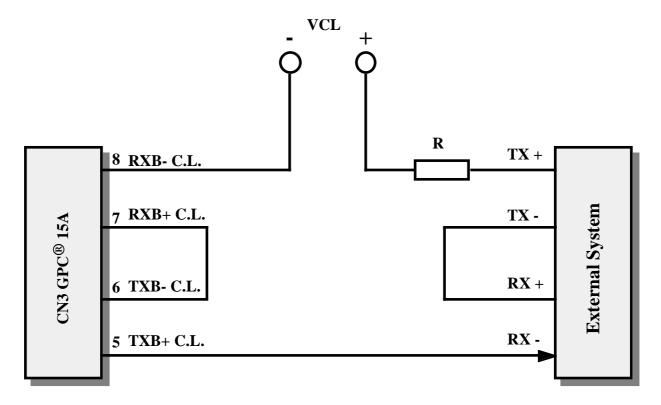

| FIGURA 14: ESEMPIO DI COLLEGAMENTO PUNTO-PUNTO IN CURRENT LOOP A 4 FILI    | 20  |

| FIGURA 15: ESEMPIO DI COLLEGAMENTO PUNTO-PUNTO IN CURRENT LOOP A 2 FILI    |     |

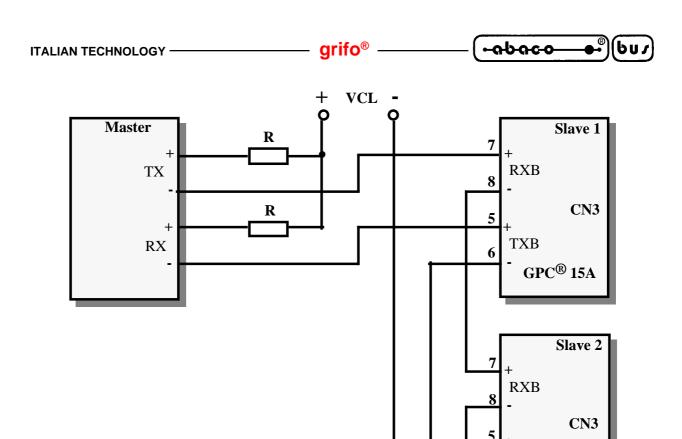

| FIGURA 16: ESEMPIO DI COLLEGAMENTO IN RETE IN CURRENT LOOP PASSIVO         | 21  |

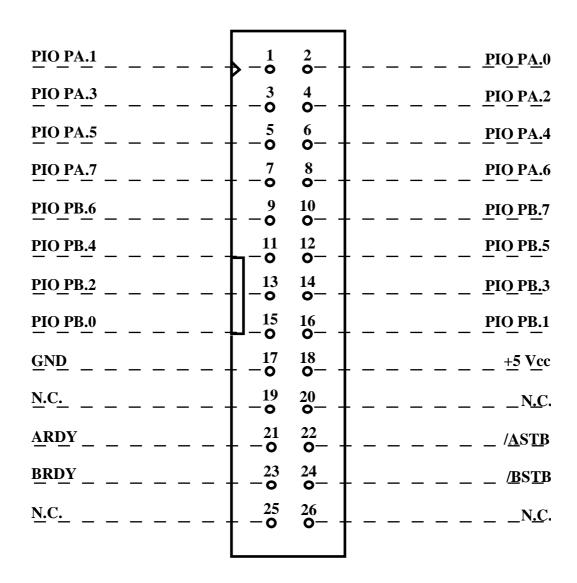

| FIGURA 17: CN5 - CONNETTORE PER I/O DEL PIO                                | 22  |

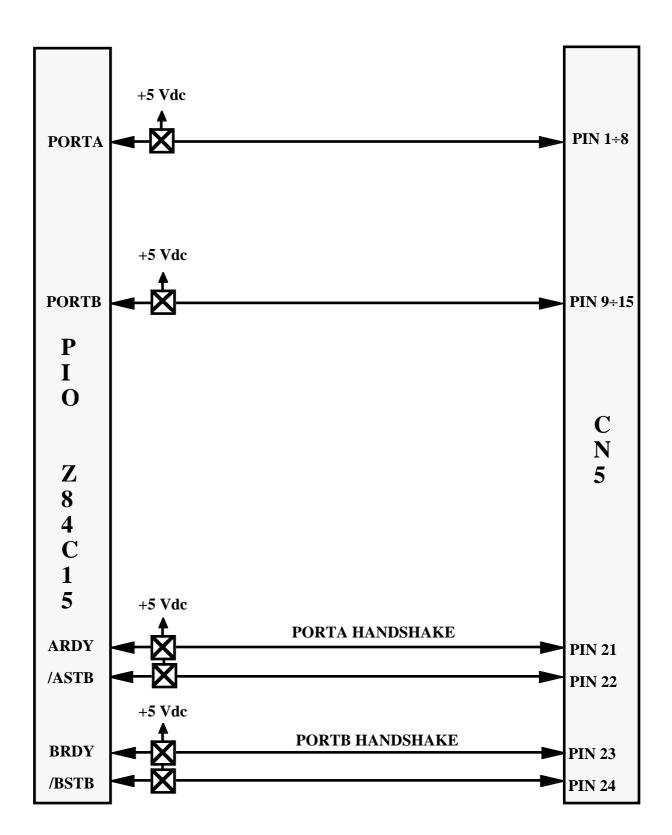

| FIGURA 18: SCHEMA DI COLLEGAMENTO DEL PIO INTERNO ALL'84C15                | 23  |

| FIGURA 19: K1 - CONNETTORE PER ABACO® BUS                                  |     |

| FIGURA 20: TABELLA DELLE SEGNALAZIONI VISIVE                               | 26  |

| FIGURA 21: TABELLA RIASSUNTIVA JUMPERS                                     | 28  |

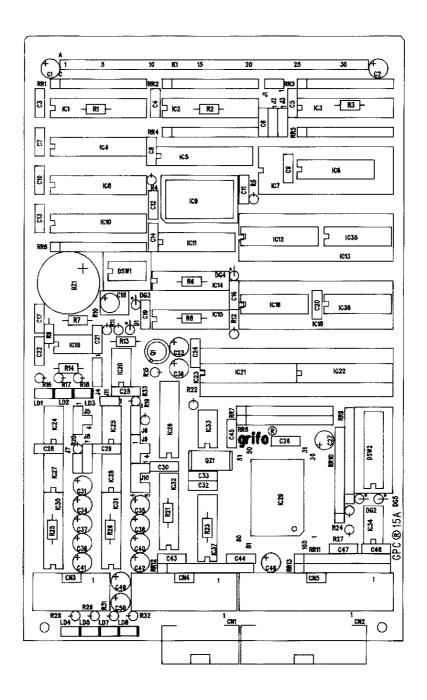

| FIGURA 22: DISPOSIZIONE CONNETTORI, MEMORIE, DIP SWITCH ETC.               | 29  |

| FIGURA 23: TABELLA JUMPERS A 2 VIE                                         |     |

| FIGURA 24: TABELLA JUMPERS A 3 VIE                                         | 30  |

| FIGURA 25: DISPOSIZIONE JUMPERS                                            | 31  |

| FIGURA 26: TABELLA JUMPERS A 4 VIE                                         | 32  |

| FIGURA 27: TABELLA JUMPERS A 5 VIE                                         | 32  |

| FIGURA 28: DISPOSIZIONE DRIVER PER COMUNICAZIONE SERIALE                   | 35  |

| FIGURA 29: TABELLA DI SELEZIONE MEMORIE                                    | 37  |

| FIGURA 30: PIANTA COMPONENTI                                               | 39  |

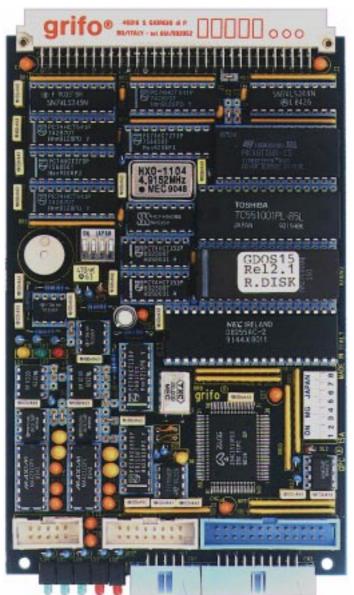

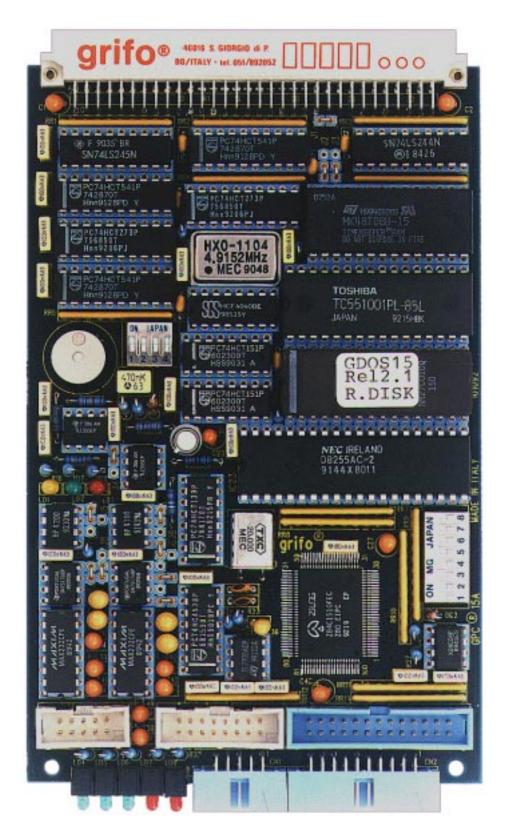

| FIGURA 31: FOTO SCHEDA                                                     |     |

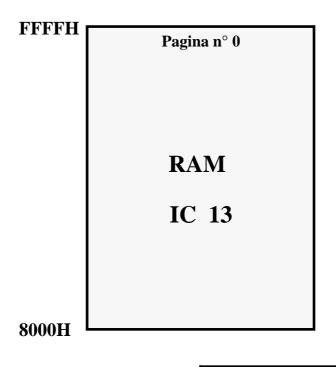

| FIGURA 32: MAPPAGGIO DELLE MEMORIE CON R/E=0                               | 46  |

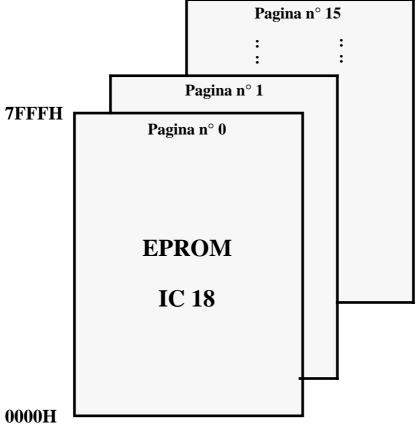

| FIGURA 33: MAPPAGGIO DELLE MEMORIE CON R/E=1                               | 47  |

| FIGURA 34: TABELLA INDIRIZZAMENTO I/O - PARTE 1                            | 48  |

| FIGURA 35: TABELLA INDIRIZZAMENTO I/O - PARTE 2                            | 49  |

| FIGURA 36: TABELLA POSSIBILI PROGRAMMAZIONI SEZIONE DI MMU                 | 53  |

| FIGURA 37: TABELLA INDIRIZZAMENTO REGISTRI DEL MODULO SRAM+RTC             | 55  |

| FIGURA 38: SCHEMA DELLE POSSIBILI CONNESSIONI                              |     |

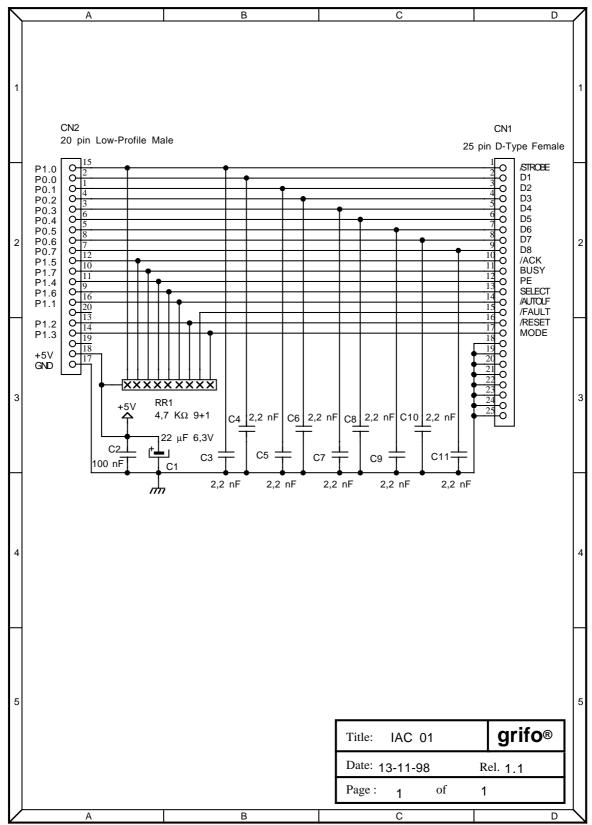

| FIGURA A1: SCHEMA ELETTRICO IAC 01                                         | A-1 |

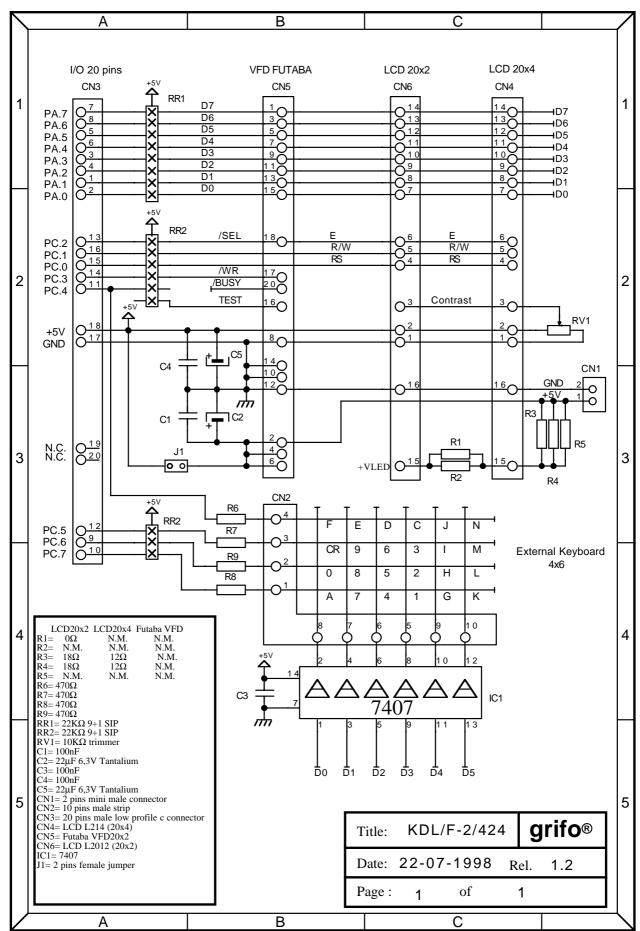

| FIGURA A2: SCHEMA ELETTRICO KDx x24                                        | A-2 |

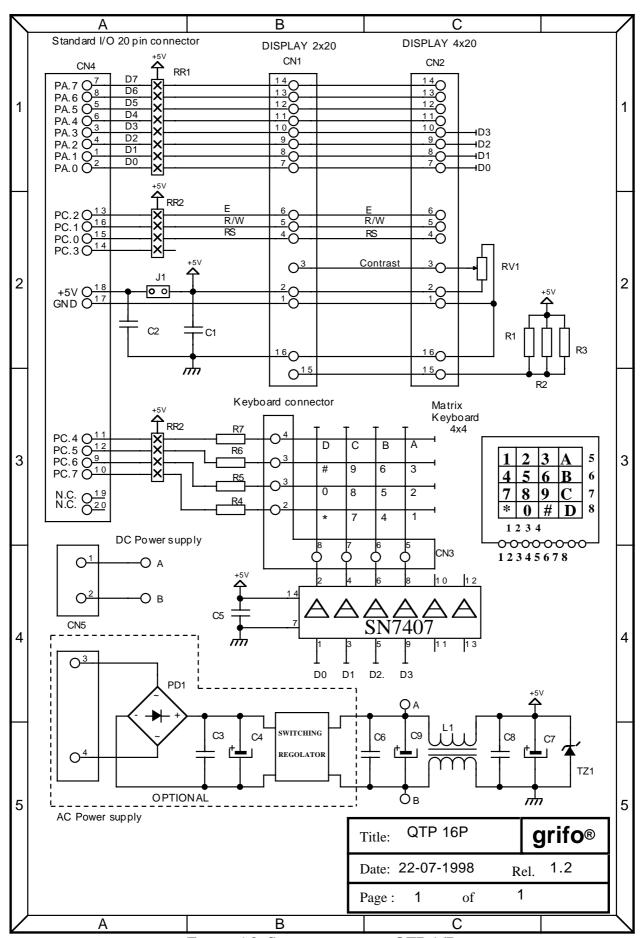

| FIGURA A3: SCHEMA ELETTRICO QTP 16P                                        | A-3 |

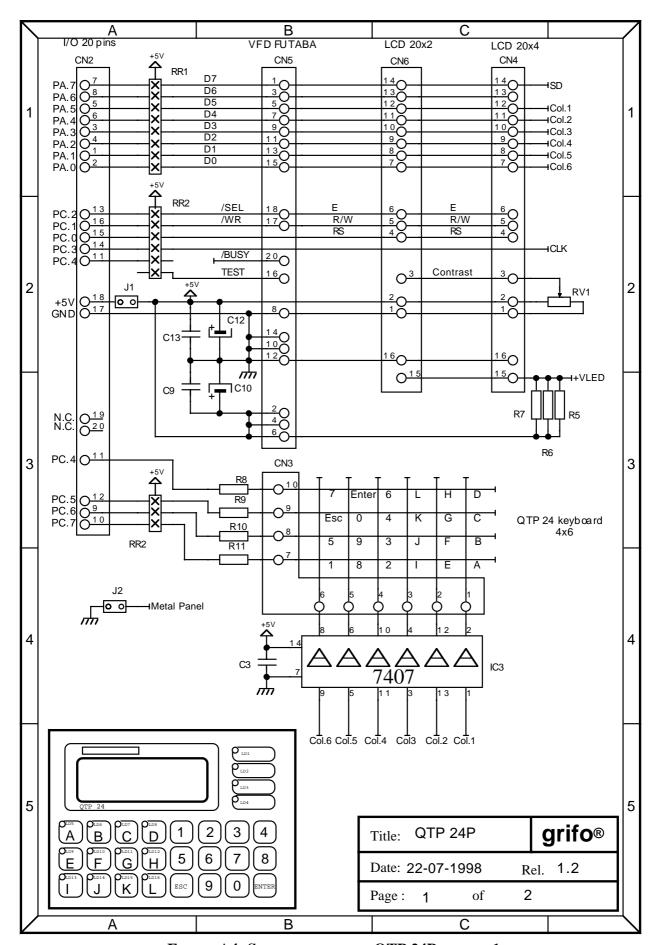

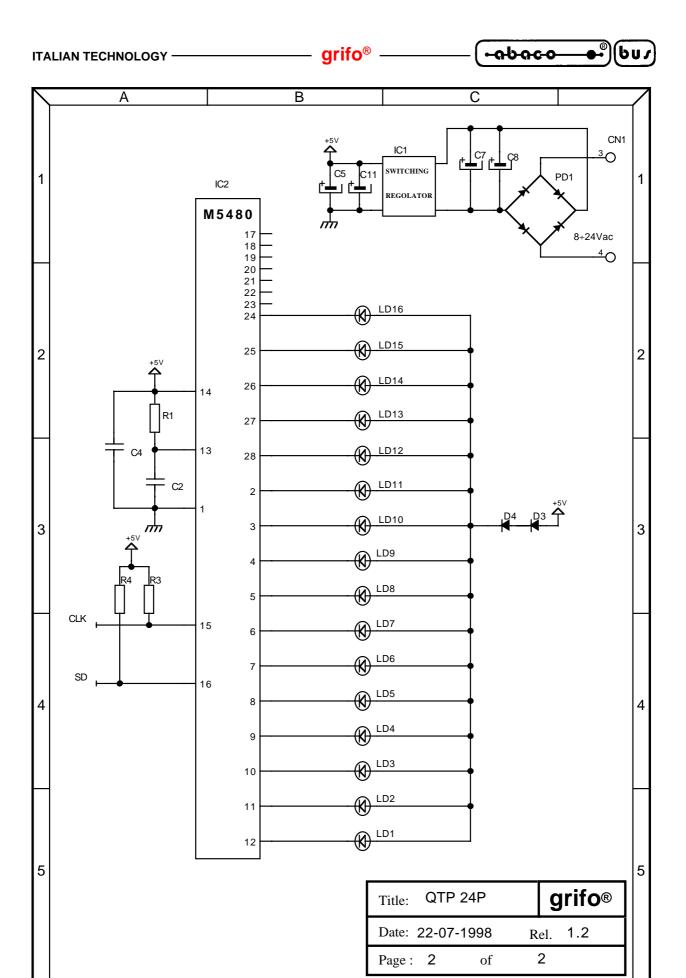

| FIGURA A4: SCHEMA ELETTRICO QTP 24P - PARTE 1                              |     |

| FIGURA A5: SCHEMA ELETTRICO QTP 24P - PARTE 2                              |     |

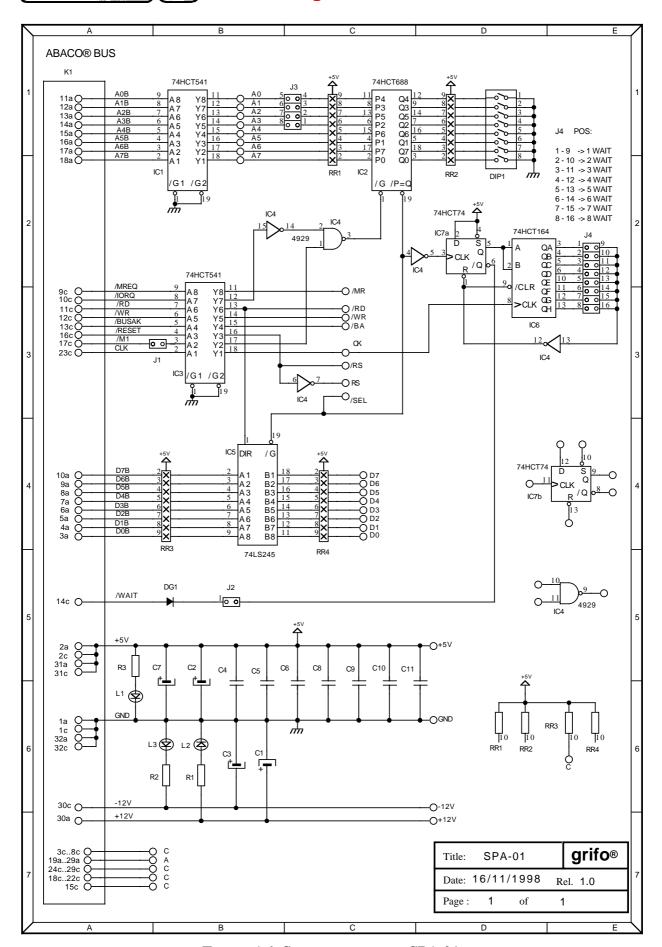

| FIGURA A6: SCHEMA ELETTRICO SPA 01                                         | A-6 |

#### INTIRODUZIONE

L'uso di questi dispositivi é rivolto - IN VIA ESCLUSIVA - a personale specializzato.

Scopo di questo manuale é la trasmissione delle informazioni necessarie all'uso competente e sicuro dei prodotti. Esse sono il frutto di un'elaborazione continua e sistematica di dati e prove tecniche registrate e validate dal Costruttore, in attuazione alle procedure interne di sicurezza e qualità dell'informazione.

I dati di seguito riportati sono destinati - IN VIA ESCLUSIVA - ad un utenza specializzata, in grado di interagire con i prodotti in condizioni di sicurezza per le persone, per la macchina e per l'ambiente, interpretando un'elementare diagnostica dei guasti e delle condizioni di funzionamento anomale e compiendo semplici operazioni di verifica funzionale, nel pieno rispetto delle norme di sicurezza e salute vigenti.

Le informazioni riguardanti installazione, montaggio, smontaggio, manutenzione, aggiustaggio, riparazione ed installazione di eventuali accessori, dispositivi ed attrezzature, sono destinate - e quindi eseguibili - sempre ed in via esclusiva da personale specializzato avvertito ed istruito, o direttamente dall'ASSISTENZA TECNICA AUTORIZZATA, nel pieno rispetto delle raccomandazioni trasmesse dal costruttore e delle norme di sicurezza e salute vigenti.

I dispositivi non possono essere utilizzati all'aperto. Si deve sempre provvedere ad inserire i moduli all'interno di un contenitore a norme di sicurezza che rispetti le vigenti normative. La protezione di questo contenitore non si deve limitare ai soli agenti atmosferici, bensì anche a quelli meccanici, elettrici, magnetici, ecc.

Per un corretto rapporto coi prodotti, é necessario garantire leggibilità e conservazione del manuale, anche per futuri riferimenti. In caso di deterioramento o più semplicemente per ragioni di approfondimento tecnico ed operativo, consultare direttamente l'Assistenza Tecnica autorizzata.

Al fine di non incontrare problemi nell'uso di tali dispositivi, é conveniente che l'utente - PRIMA DI COMINCIARE AD OPERARE - legga con attenzione tutte le informazioni contenute in questo manuale. In una seconda fase, per rintracciare più facilmente le informazioni necessarie, si può fare riferimento all'indice generale e all'indice analitico, posti rispettivamente all'inizio ed alla fine del manuale.

#### VIEIRSIONIE SCHIEIDA

Il presente manuale è riferito alla scheda **GPC® 15A** versione **250694** e successive. La validità delle informazioni riportate è quindi subordinata al numero di versione della scheda in uso e l'utente deve quindi sempre verificare la giusta corrispondenza tra le due indicazioni. Sulla scheda il numero di versione è riportato in più punti sia a livello di serigrafia che di stampato (ad esempio sul bordo della scheda, a fianco di IC23 sul lato componenti e vicino al connettore K1 sul bordo della scheda nel lato stagnature).

GPC® 15A Rel. 3.20 Pagina A

#### INFORMAZIONI GENERALI

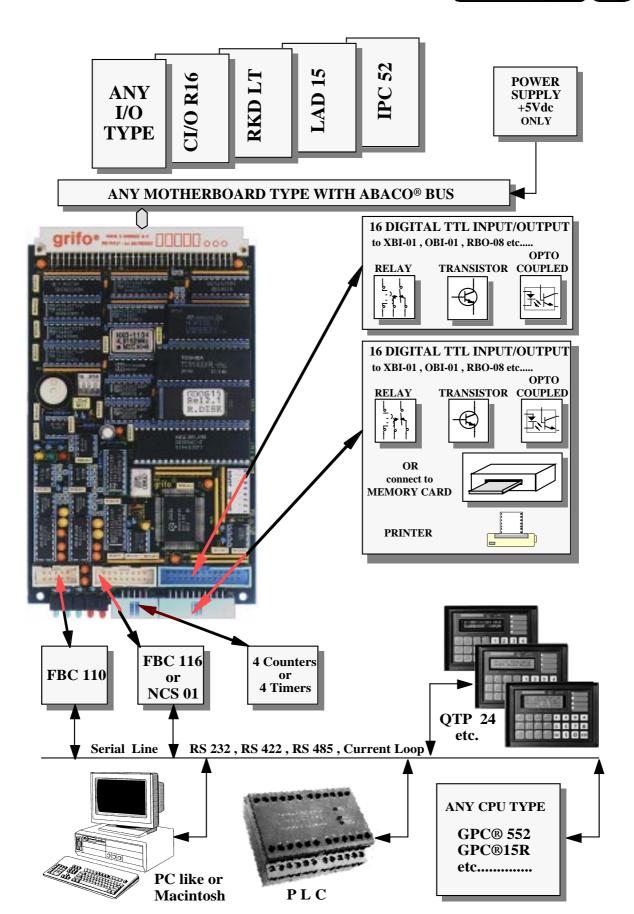

La scheda GPC<sup>®</sup> 15A é un potente modulo di controllo e di gestione nel formato standard Singola Europa da 100x160 mm. Essa opera sul potente BUS Industriale Abaco<sup>®</sup>, di cui sfrutta la ricca serie di periferiche, intelligenti e non, disponibili su questo BUS. La GPC® 15A é basata sulla potente e diffusa CPU Z84C15 Zilog, codice compatibile con il famoso Z80, ed ha a bordo scheda notevoli risorse hardware. La estrema modularità e la notevole completezza di risorse hardware della scheda GPC® 15A le consentono di poter affrontare applicazioni anche di notevole complessità con estrema disinvoltura. La programmazione e l'uso delle risorse della scheda diventa estremamente semplice grazie all'uso del potente sistema operativo romato **FGDOS**. Esso supporta i linguaggi ad alto livello quali Compilatori BASIC, PASCAL, C, ecc.; mette a disposizione le risorse di memoria come se fossero ROM/RAM disk, consentendo un immediato utilizzo ad alto livello di questi dispositivi. Consente inoltre la gestione diretta di **Display LCD** o **Fluorescenti**, di una tastiera a matrice, di una stampante parallela e delle schede PCMCIA di RAM Cards. FGDOS, oltre alla nota facilità di sviluppo e prova, consente di programmare direttamente a bordo scheda una FLASH con il programma utente. La GPC® 15A é dotata di una serie di connettori normalizzati, standard Abaco®, che le consentono di utilizzare immediatamente la numerosa serie di moduli **BLOCK** di I/O oppure permettono il collegamento, in modo molto semplice ed economico, delle interfacce da campo costruite direttamente dall'utente o da terze parti.

- Formato singola Europa da 100x160mm con interfaccia per il **BUS industriale Abaco**<sup>®</sup>.

- CPU CMOS 84C15 con quarzo da 20 MHz.

- Fino a **512K EPROM** o **256K FLASH EPROM** e fino a **128K SRAM**. Tramite **FGDOS** la memoria eccedente i 64K é vista come **RAM/ROM disk**. E' possibile cancellare e riprogrammare autonomamente la **FLASH** di bordo con il programma utente.

- **EEPROM** seriale fino a 8 K.

- **Dip Switch** da 4 vie più Dips Switch da 8 vie opzionale e jumper di configurazione leggibili da software.

- 2 LEDs di attività, posizionato sul frontale, gestibile da software.

- Buzzer gestibile via software.

- 2 linee seriali in RS 232 di cui una settabile in RS 422, RS 485 o Current Loop gestite dal potente SIO che supporta Baud Rate, settabile da software, fino a 38,4 KBaud.

- fino a **40** linee di **I/O TTL**, settabili da software, di cui 24 gestite dal **PPI 82C55** e 16 gestite dal **PIO**. 8 linee del PPI leggono un Dip Switch da 8 vie che può essere tolto, rendendo le linee disponibili per l'utente.

- 4 Timer Counter ad 8 bits

- **SRAM** e **Real Time Clock** opzionalmente tamponati in grado di gestire giorno, mese, anno, giorno della settimana, ore, minuti, secondi

- Watch Dog resettabili da software visualizzati tramite LED.

- Unica tensione di alimentazione a 5Vdc, 180 mA.

- Vasta disponibilità di software di base e di **ambienti di sviluppo** che consentono di poter utilizzare la scheda tramite un normale **PC**. Tra i pacchetti disponibili si possono citare: **FGDOS 15A**; **PASCAL 80**; **CBZ 80**; **NSB8**; **RSD 15A**; **HI TECH C 80**; **GET 80**; **DDS MICRO C 85**; **NO ICE Z80**; ecc.

Pagina 2 — GPC® 15A Rel. 3.20

#### **SIO**

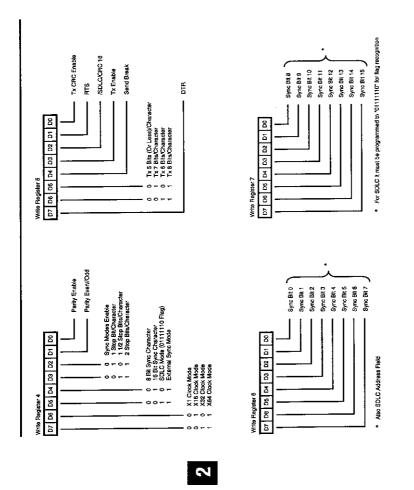

Periferica in grado di gestire due linee per la comunicazione seriale. Il dispositivo può essere utilizzato per la comunicazione con tutti i sistemi provvisti di una linea seriale bufferata in RS 232, RS 422, RS 485 o Current Loop. Dal punto di vista software è infatti definibile la velocità di comunicazione, la lunghezza della parola, il numero di stop bit, la parità e lo stato dei segnali di handshake hardware. Il tutto avviene tramite una semplice programmazione di 4 registri allocati nello spazio di I/O della CPU da un'apposita logica di controllo.

#### **TIMER COUNTER**

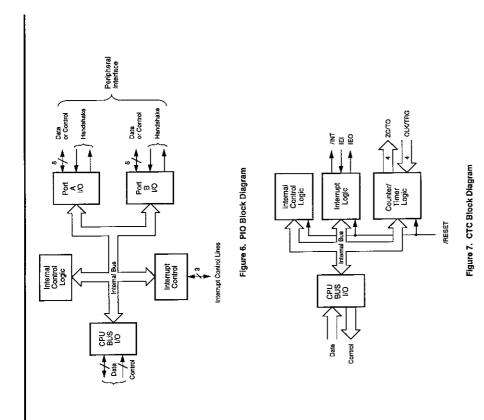

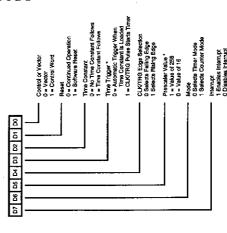

La sezione di Timer Counter di bordo é costituita dalla sezione CTC del microprocessore e dispone di 4 canali ad 8 bit indipendenti e programmabili via software. La periferica é vista tramite 4 registri, situati nello spazio di I/O dalla logica di controllo della scheda, con cui possono essere definite le modalità di funzionamento (timer o counter, prescaler, trigger, ecc.) e l'eventuale generazione d'interrupt.

#### LINEE DI I/O DEL PIO

Periferica in grado di gestire due port paralleli da 8 bit per un totale di 16 linee di I/O logico a livello TTL, con direzionalità settabile a livello di bit. Tali linee di I/O hanno la possibilità di generare interrupt. In questo modo una determinata condizione esterna può distogliere la CPU dalle normali operazioni, in modo da rispondere sempre e prontamente a tutti gli eventi. Il PIO viene completamente gestito via software tramite la programmazione di 4 registri situati nello spazio di I/O della CPU da un'apposita logica di controllo.

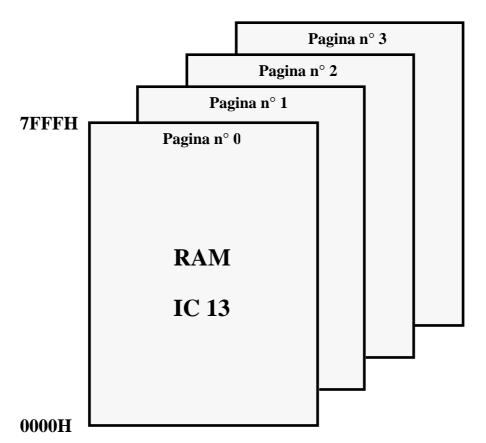

#### **DISPOSITIVI DI MEMORIA**

E' possibile dotare la scheda di un massimo di 656KBytes di memoria variamente suddivisi con un massimo di 512KBytes di EPROM o 256 KBytes di FLASH EPROM, 128KBytes di SRAM, 8KBytes di EEPROM seriale e 8KBytes di SRAM tamponata. La scelta della configurazione delle memorie presenti sulla scheda può avvenire in relazione all'applicazione da risolvere e quindi in relazione alle esigenze dell'utente. Da questo punto di vista si ricorda che la scheda viene normalmente fornita con i soli 128KBytes di SRAM di lavoro e che tutte le rimanenti memorie devono essere quindi opportunamente specificate in fase di ordine della scheda. Sfruttando la possibilità opzionale di montare fino a 8KBytes di EEPROM seriale, fino a 8KBytes di SRAM tamponata ed eventualmente montare anche i 128KBytes di SRAM di lavoro in versione tamponata si ha la possibilità di mantenere i dati anche in assenza di alimentazione. Questa caratteristica fornisce alla scheda la possibilità di ricordare in ogni condizione, una serie di parametri come ad esempio la configurazione o lo stato del sistema. Il mappaggio delle risorse di memoria avviene tramite una opportuna circuiteria di bordo, che provvede ad allocare i dispositivi all'interno dello spazio d'indirizzamento del microprocessore. Per maggiori informazioni fare riferimento al capitolo "DESCRIZIONE HARDWARE" e "DESCRIZIONE SOFTWARE DELLE PERIFERICHE DI BORDO". Per una descrizione più approfondita sui dispositivi di memoria, sugli zoccoli da utilizzare e sullo strippaggio della scheda, fare riferimento al paragrafo "SELEZIONE MEMORIE".

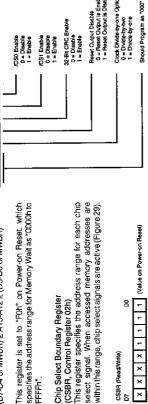

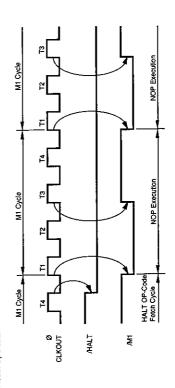

#### PROCESSORE DI BORDO

La scheda **GPC® 15A** è predisposta per accettare il processore Z84C15 prodotto dalla ZILOG. Tale processore ad 8 bit è codice compatibile con lo Z80 ed è quindi caratterizzato da un esteso set di istruzioni (158), da un'alta velocità di esecuzone e di manipolazione dati e da un efficiente gestione vettorizzata degli interrupts. Di fondamentale importanza è la presenza delle seguenti periferiche interne al microprocessore:

- 16 linee di I/O settabili a livello di bit in grado di generare interrupts (PIO);

- 4 Timer Counter ad 8 bit, con funzione di prescaler programmabile (CTC);

- 2 linee seriali asincrone o sincrone complete di segnali di handshake (SIO);

- Watch Dog Timer;

- Wait state generator;

- Frequenza di Clock programmabile;

- Interrupt controller;

- Possibilità di operare in idle e stop mode, per minimizzare i consumi;

Per maggiori informazioni a riguardo di questo componente si faccia riferimento all'apposita documentazione della casa costruttrice, oppure all'appendice B di questo manuale.

#### **COMUNICAZIONE SERIALE**

La comunicazione seriale è completamente settabile via software per quanto riguarda sia il protocollo sia la velocità (da un minimo di 300 ad un massimo di 38400 Baud) ed in modo completamente autonomo per entrambe le linee di comunicazione. Tali settaggi avvengono tramite la programmazione del SIO interno allo Z84C15 e della sezione di baud rate generator, di cui la scheda é provvista, quindi per ulteriori informazioni si faccia riferimento alla documentazione tecnica della casa costruttrice o all'appendice B di questo manuale.

Dal punto di vista hardware è invece possibile selezionare, tramite una serie di comodi jumpers, il protocollo fisico di comunicazione. In particolare una linea è sempre bufferata in RS 232, mentre la rimanente può essere bufferata in RS 232, RS 422, RS 485 o Current Loop; in quest'ultimo caso è definibile anche se la comunicazione avviene in Full Duplex o Half Duplex.

#### ABACO® BUS

Una delle caratteristiche di fondamentale importanza della **GPC**<sup>®</sup> **15A** è quella di disporre dell'interfacciamento nei confronti del BUS industriale **ABACO**<sup>®</sup>: ovvero un connettore normalizzato con cui è possibile collegare la scheda ad una serie di moduli esterni intelligenti e non. Tra questi si trovano moduli per acquisizione di segnali analogici (A/D), per la generazione di segnali analogici (D/A), per gestione di linee di I/O logico, per counter, ecc. e ne possono essere realizzati anche su specifiche richieste dell'utente. Utilizzando mother board come l'**ABB 03** o l'**ABB 05** é inoltre possibile gestire anche le schede periferiche della serie 3 e 4 provviste di **ABACO**<sup>®</sup> **I/O BUS**. Tale caratteristica rende la scheda espandibile con un ottimo rapporto prezzo/prestazioni e quindi adatta a risolvere molti dei problemi dell'automazione industriale.

Pagina 4 — — — — — [GPC® 15A Rel. 3.20

FIGURA 1: SCHEMA A BLOCCHI

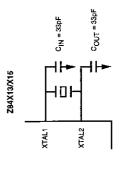

#### **DISPOSITIVI DI CLOCK**

Sulla **GPC® 15A** sono presenti due circuiti separati che provvedono a generare rispettivamente la frequenza di clock per la CPU (20 MHz) e la frequenza per la generazione del Baud Rate (4,9152 MHz), relativo alle linee di comunicazione seriale della scheda. La scelta di utilizzare due circuiti e quindi due quarzi indipendenti, è legata alla possibilità di poter variare la frequenza di lavoro della CPU senza dover intervenire sul software di gestione della comunicazione ed allo stesso tempo avere la possibilità di raggiungere le massime prestazioni in termini di tempo, sia per quanto riguarda l'esecuzione che la comunicazione seriale .

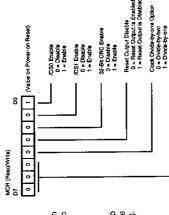

#### LINEE DI I/O DEL PPI 82C55

Periferica in grado di gestire tre port paralleli da 8 bit per un totale di 24 linee di I/O logico a livello TTL, con direzionalità settabile a livello di byte. Tali linee di I/O aprono ulteriori possibilità di impiego della **GPC**® **15A** (ad esempio nella gestione di periferiche non intelligenti, interfacce, ecc.) anche quando l'handshake delle comunicazioni è completamente da gestire via software. Il chip PPI 82C55 viene completamente gestito via software tramite la programmazione di 4 registri situati nello spazio di I/O della CPU da un'apposita logica di controllo. Nella versione base della scheda uno dei port viene impiegato per leggere il Dip Switch a 8 vie.

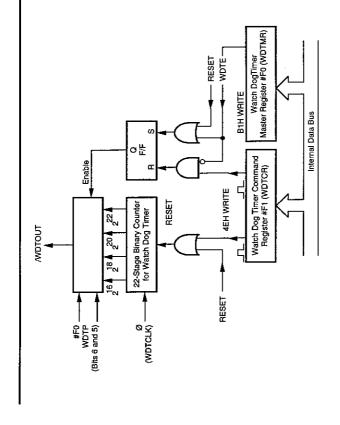

#### **WATCH DOG**

La scheda **GPC**® **15A** è provvista di due circuiterie separate di Watch Dog che, se utilizzate, consentono di uscire da stati di loop infinito o da condizioni anomale non previste dal programma applicativo. Tali circuiterie sono composte da una sezione monostabile interna al microprocessore caratterizzata da un tempo di intervento programmabile e da una sezione astabile/monostabile esterna con un tempo d'intervento tipico di circa 700 msec. La gestione avviene completamente via software (tramite l'acceso ad opportuni registri situati nello spazio d'indirizzamento della CPU) e conferisce al sistema basato sulla scheda, una sicurezza estrema. I tempi d'intervento della circuiteria di Watch Dog esterna possono essere eventualmente variati su specifica richiesta dell'utente, intervenendo su apposite reti RC; in caso di necessità contattare la **grifo**®.

#### **LOGICA DI CONTROLLO**

Il mappaggio di tutti i registri delle periferiche presenti sulla scheda e dei dispositivi di memoria, è affidata ad un'opportuna logica di controllo che si occupa di allocare tali dispositivi nello spazio d'indirizzamento della CPU. Per maggiori informazioni fare riferimento al paragrafo "MAPPAGGIO DELL'I/O".

#### **MMU**

Al fine di poter gestire in modo pratico ed efficace le configurazioni di memoria di cui può essere dotata la **GPC**<sup>®</sup> **15A**, a partire dallo spazio d'indirizzamento logico di 64 KByte del microprocessore, è stata prevista un'apposita sezione di MMU. Tale sezione provvede tramite una facile programmazione software, l'allocazione dei 64K di lavoro all'interno dello spazio di memoria.

Pagina 6 — GPC® 15A Rel. 3.20

#### **BUZZER**

Sulla **GPC**® **15A** è presente una circuiteria in grado di emettere un suono costante, basata su un buzzer capacitivo. Questa circuiteria viene abilitata e/o disabilitata via software tramite la logica di controllo e può essere utilizzata per generare allarmi acustici, feed back sonori, ecc.

#### **RTC**

Il modulo di SRAM tamponata da montare sullo zoccolo di IC 7 può essere provvisto di un completo Real Time Clock in grado di gestire ore, minuti, secondi, giorno del mese, mese, anno e giorno della settimana in modo completamente autonomo. Il componente è opzionale (come già detto nel capitolo "Dispositivi di memoria"), provvisto di batteria interna di Back Up ed è completamente gestito via software, tramite la programmazione di 8 registri situati nello spazio di I/O della CPU da un'apposita logica di controllo.

Per ulteriori informazioni a riguardo dei dispositivi periferici descritti, si faccia riferimento alla documentazione tecnica della casa costruttrice o all'appendice B di questo manuale.

GPC® 15A Rel. 3.20 Pagina 7

#### CARATTERISTICHE TECNICHE

#### **CARATTERISTICHE GENERALI**

**Risorse della scheda:** 16 (24) Input/Output programmabili TTL (PPI 82C55)

16 Input/Output (PIO)

4 Timer Counter ad 8 bit a livello TTL (CTC)

1 Linea bidirezionale RS 232

1 Linea bidirezionale RS 232, RS 422, RS 485 o Current Loop

1 Watch Dog interno alla CPU

1 Watch Dog esterno1 Real Time Clock (RTC)

1 Buzzer

1 Dip Switch da 4 dips 1 Dip Switch da 8 dips BUS industriale **ABACO**®

**Memoria indirizzabile:** IC 18: EPROM da 128K x 8 a 512K x 8

FLASH EPROM da 128K x 8 a 256K x 8

IC 13: SRAM da 128K x 8

IC 34: EEPROM seriale da 256 byte a 8192 byte

IC 7: SRAM da 2Kx8 a 8Kx8

**CPU di bordo:** ZILOG 84C15

Frequenza quarzo CPU: 20 MHz

Frequenza Baud Rate generator: 4,9152 MHz

**Tempo intervento Watch Dog:** 700 msec calibrato con un rete RC

#### **CARATTERISTICHE FISICHE**

**Dimensioni:** (L x A x P): formato EUROPA: 100 x 160 x 15 mm

**Peso:** 190 g (versione base)

**Connettori:** K1: 64 pin DIN 41612 corpo C

CN1: 10 vie scatolino 90 gradi M CN2: 20 vie scatolino 90 gradi M CN3: 10 vie scatolino verticale M CN4: 16 vie scatolino verticale M CN5: 26 vie scatolino 90 gradi M

Pagina 8 — [GPC® 15A Rel. 3.20]

italian technology — grifo® — ←¬b¬c¬→® bu /

**Range di temperatura:** da 0 a 70 gradi Centigradi

**Umidità relativa:** 20% fino a 90% (senza condensa)

### **CARATTERISTICHE ELETTRICHE**

**Tensione di alimentazione:** +5 Vcc

Corrente assorbita sui 5 Vdc: 150 mA nella configurazione base

175 mA nella configurazione massima

**Rete terminazione RS 422, 485:** Resistenza terminazione linea=  $120\Omega$

### INSTALLAZIONE

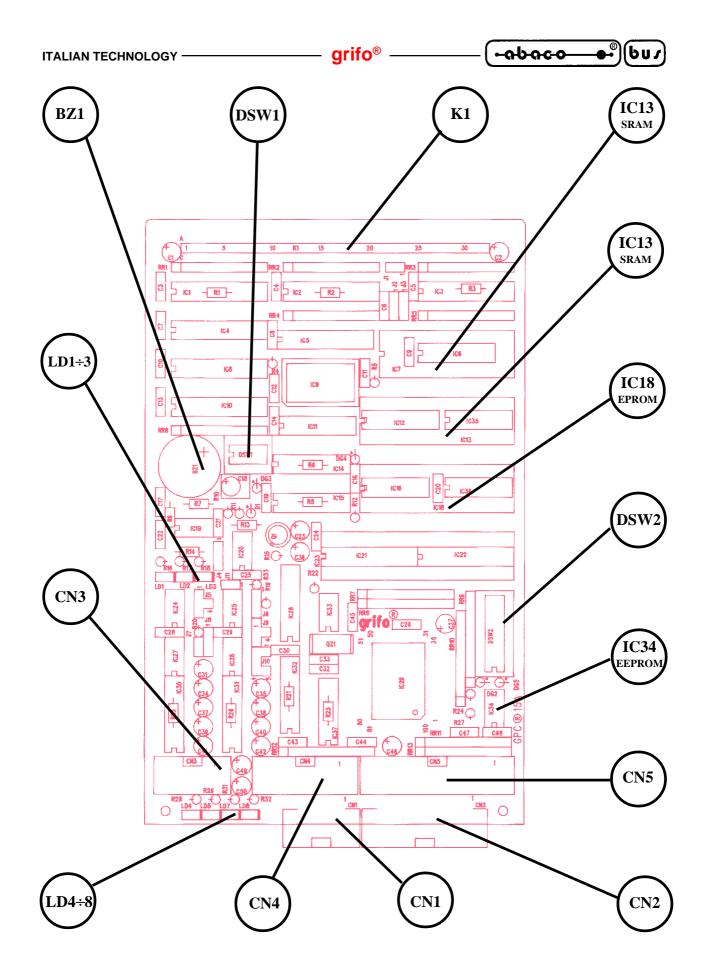

In questo capitolo saranno illustrate tutte le operazioni da effettuare per il corretto utilizzo della scheda. A questo scopo viene riportata l'ubicazione e la funzione degli strip, dei connettori, dei trimmers, dei LEDs, ecc. presenti sulla **GPC**<sup>®</sup> **15A**.

#### **CONNESSIONI CON IL MONDO ESTERNO**

l modulo **GPC**® **15A** è provvisto di 6 connettori con cui vengono effettuati tutti i collegamenti con il campo e con le altre schede del sistema di controllo da realizzare. Di seguito viene riportato il loro pin out ed il significato dei segnali collegati; per una facile individuazione di tali connettori, si faccia riferimento alla figura 22, mentre per ulteriori informazioni a riguardo del tipo di connessioni, fare riferimento alle figure successive che illustrano il tipo di collegamento effettuato a bordo scheda.

#### CN1 - CONNETTORE PER I/O DEL CTC

CN1 è un connettore a scatolino a 90 gradi con passo 2.54 mm a 10 piedini. Tramite CN1 si effettua la connessione tra i 4 canali del timer counter CTC e l'ambiente esterno. I segnali presenti su questo connettore coincidono con segnali logici a livello TTL.

FIGURA 2: CN1 - CONNETTORE PER I/O DEL CTC

Legenda:

CLKn, Tn = I - Clock Trigger del contatore n del CTC a livello TTL

ZCn = O - Zero Count Timer del contatore n a livello TTL

+5 Vdc = O - Linea di alimentazione a +5 Vcc

**GND** = - Linea di massa

Pagina 10 — GPC® 15A Rel. 3.20

FIGURA 3: SCHEMA DI COLLEGAMENTO CTC

#### CN2 - CONNETTORE PER I/O DEL PPI

CN2 è un connettore a scatolino a 90 gradi con passo 2.54 mm a 20 piedini. Tramite CN2 si effettua la connessione tra l'interfaccia periferica programmabile PPI 82C55 e l'ambiente esterno, utilizzando due dei tre port paralleli ad 8 bit. I segnali presenti su questo connettore coincidono con segnali logici a livello TTL.

FIGURA 4: CN2 - CONNETTORE PER I/O DEL PPI 8255 DA PORT A E C

### Legenda:

**PPI PA.n** = I/O - Linea digitale n del port A del PPI 82C55 **PPI PC.n** = I/O - Linea digitale n del port C del PPI 82C55

+5 Vdc = O - Linea di alimentazione a +5 Vcc

**GND** = - Linea di massa digitale

NC = - Non collegato

Pagina 12 — GPC® 15A Rel. 3.20

FIGURA 5: SCHEMA DEL COLLEGAMENTO LINEE DI I/O DEL PPI

#### DSW2 - ZOCCOLO PER I/O DEL PPI 82C55 DA PORT B

DSW2 è uno zoccolo con passo 2.54 mm a 16 piedini.

Scollegando da DSW2 il dip switch ad 8 vie, si ha la possibilità di utilizzare il port B del PPI 82C55 della scheda, per gestire fino ad 8 linee di I/O digitale a livello TTL. Per facilitare l'utilizzo di queste linee è conveniente utilizzare appositi zoccoli a perforazione d'isolante.

FIGURA 6: DSW2 - ZOCCOLO PER I/O DEL PPI 82C55 DA PORT B

Legenda:

**PPI PB.n** = I/O - Linea digitale n del port B del PPI 82C55.

**GND** = - Linea di massa.

Pagina 14 — GPC® 15A Rel. 3.20

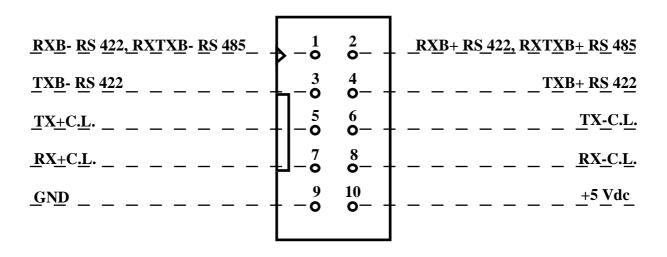

#### CN3 - CONNETTORE LINEE SERIALI RS 422, RS 485 E CURRENT LOOP

CN3 è un connettore a scatolino verticale con passo 2.54 mm a 10 piedini.

Su questo connettore sono riportati tutti i segnali per la comunicazione in RS 422, RS 485 e Current Loop della linea seriale B. La disposizione di tali segnali è stata studiata in modo da ridurre al minimo le interferenze ed in modo da facilitare le connessioni con il campo, mentre i segnali rispettano le normative definite dal CCITT relative ad ognuno degli standard di comunicazione usati. Si ricorda inoltre che l'interfaccia Current Loop é di tipo passivo.

FIGURA 7: CN3 - CONNETTORE PER LINEE SERIALI RS 422, RS 485 E CURRENT LOOP

Legenda:

| <b>RXB- RS422</b> | = I - Receive Data Negative: linea bipolare negativa di ricezione differenziale |

|-------------------|---------------------------------------------------------------------------------|

|                   | in RS 422 della seriale B                                                       |

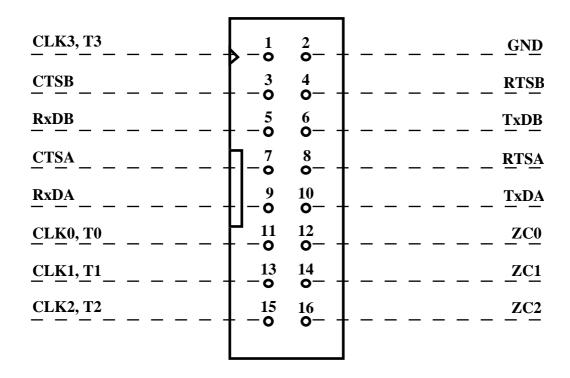

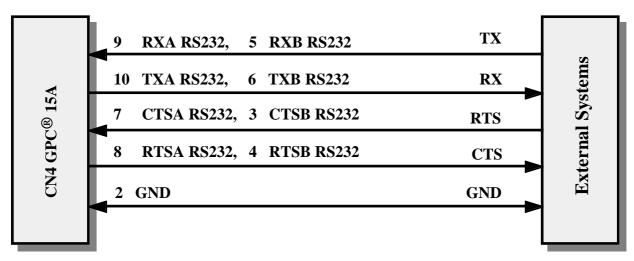

#### CN4 - CONNETTORE PER COMUNICAZIONE SERIALE IN RS 232 E CTC

CN4 è un connettore a scatolino a 90 gradi con passo 2.54 mm a 16 piedini.

Tramite CN4 si effettua la connessione delle due linee seriali in RS 232 ed i timer counter T0 e T1 a bordo della CPU con l'ambiente esterno. Le due linee seriali sono gestibili via hardware e via software tramite lo strippaggio di appositi jumpers e la programmazione degli appositi registri interni dello Z84C15. I segnali presenti su questo connettore coincidono con segnali logici a livello TTL e segnali a livello RS 232, secondo le normative definite dal CCITT; la disposizione dei segnali, é invece stata studiata in modo da ridurre al minimo le interferenze ed in modo da facilitare la connessione con il campo.

FIGURA 8: CN4 - CONNETTORE PER COMUNICAZIONE SERIALE IN RS 232 E CTC

#### Legenda:

| RxD A/B  | = 1 - Receive Data: linea di ricezione in RS 232 della linea seriale A o B          |

|----------|-------------------------------------------------------------------------------------|

| TxD A/B  | = O - Trasmit Data: linea di trasmissione in RS 232 della linea seriale A o B       |

| CTS A/B  | = I - Clear To Send: linea di abilitazione della trasmissione in RS 232 della linea |

|          | seriale A o B                                                                       |

| RTS A/B  | = O - Request To Send: linea di richiesta di trasmissione in RS 232 della linea     |

|          | seriale A o B                                                                       |

| CLKn, Tn | = I - Clock Trigger del contatore n del CTC a livello TTL                           |

| ZCn      | = O - Zero Count Timer del contatore n a livello TTL                                |

| GND      | = - Linea di massa                                                                  |

Pagina 16 — GPC® 15A Rel. 3.20

FIGURA 9: SCHEMA DI COLLEGAMENTO SERIALI RS 422, RS 485 E CURRENT LOOP

FIGURA 10: ESEMPIO DI COLLEGAMENTO PUNTO PUNTO IN RS 232

FIGURA 11: ESEMPIO DI COLLEGAMENTO PUNTO PUNTO IN RS 422

FIGURA 12: ESEMPIO DI COLLEGAMENTO PUNTO PUNTO IN RS 485

Pagina 18 — GPC® 15A Rel. 3.20

FIGURA 13: ESEMPIO DI COLLEGAMENTO IN RETE IN RS 485

**GND**

Da notare che in una rete RS 485, devono essere presenti due resistenze di forzatura (3,3 k $\Omega$ ) lungo la linea e due resitenze di terminazione (120  $\Omega$ ), alle estremità della stessa, rispettivamente vicino all'unità Master ed all'ultima unità Slave.

A bordo della **GPC**<sup>®</sup> **15A** è presente la circuiteria di terminazione, che può essere inserita o disinserita, tramite appositi jumpers, come illutrato in seguito.

In merito alla resistenza di terminazione dell'unità Master, provvedere a collegarla solo se questa non é già presente al suo interno (ad esempio molti convertitori RS232-RS485 ne sono già provvisti). Per maggiori informazioni consultare il Data-Book TEXAS INSTRUMENTS, "RS 422 and RS 485 Interface Cicuits", nella parte introduttiva riguardante le reti RS 422-485.

FIGURA 14: ESEMPIO DI COLLEGAMENTO PUNTO-PUNTO IN CURRENT LOOP A 4 FILI

FIGURA 15: ESEMPIO DI COLLEGAMENTO PUNTO-PUNTO IN CURRENT LOOP A 2 FILI

Pagina 20 — GPC® 15A Rel. 3.20

TXB

**RXB**

**TXB**

8

6

GPC® 15A

Slave n

CN<sub>3</sub>

GPC® 15A

FIGURA 16: ESEMPIO DI COLLEGAMENTO IN RETE IN CURRENT LOOP PASSIVO

Per il collegamento in Current Loop passivo sono possibili due diversi tipi di collegamento: a 2 fili ed a 4 fili. Tali connessioni sono riportate nelle figure 14 e 15; in esse é indicata la tensione per alimentare l'anello (**VCL**) e le resistenze di limitazione della corrente (**R**). I valori di tali componenti variano in funzione del numero di dispositivi collegati e della caduta sul cavo di collegamento; bisogna quindi effettuare la scelta considerando che:

- si deve garantire la circolazione di una corrente di 20 mA;

- su ogni trasmettitore cadono mediamente 2,35 V con una corrente di 20 mA;

- su ogni ricevitore cadono mediamente 2,52 V con una corrente di 20 mA;

- in caso di cortocircuito sulla rete ogni trasmettitore dissipi al massimo 125 mW;

- in caso di cortocircuito sulla rete ogni ricevitore dissipi al massimo 90 mW.

Per maggiori informazioni consultare il Data-Book HEWLETT-PACKARD, nella parte che riguarda gli opto-accoppiatori per Current Loop denominati **HCPL 4100** e **HCPL 4200**.

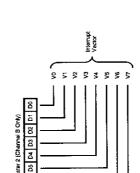

#### CN5 - CONNETTORE PER I/O DEL PIO

CN5 è un connettore a scatolino verticale con passo 2.54 mm a 26 piedini. Tramite CN5 si effettua la connessione tra l'interfaccia periferica programmabile PIO e l'ambiente esterno, utilizzando i due port paralleli ad 8 bit e le linee di handshake di cui dispone. I segnali presenti su questo connettore coincidono con segnali logici a livello TTL.

FIGURA 17: CN5 - CONNETTORE PER I/O DEL PIO

#### Legenda:

**PIO PA.n** = I/O - Linea digitale n del port A del PIO **PIO PB.n** = I/O - Linea digitale n del port B del PIO

**RDY A/B** = O - Linea di segnalazione stato del ready del port A o B

/STB A/B = I - Linea di abilitazione del port A o B +5 Vcc = O - Linea di alimentazione a +5 Vcc

GND = - Linea di massa N.C. = - Non Collegato

Pagina 22 — GPC® 15A Rel. 3.20

FIGURA 18: SCHEMA DI COLLEGAMENTO DEL PIO INTERNO ALL'84C15

#### **K1 - CONNETTORE PER ABACO® BUS**

K1 è un connettore DIN 41612 corpo C a 90 gradi da 64 piedini.

Tramite K1 si effettua la connessione tra la scheda e la serie di moduli esterni di espansione, da utilizzare per l'interfacciamento diretto con il campo. Tale collegamento è effettuato tramite il BUS industriale **ABACO**® di cui questo connettore riporta i segnali a livello TTL. Nella figura seguente è riportato il pin out del BUS e quindi anche del relativo connettore, con le variazioni per l'utilizzo di CPU a 16 Bit rispetto a quelle a 8 Bit.

| A            | A           | A       | PIN | С       | С            | C            |

|--------------|-------------|---------|-----|---------|--------------|--------------|

| BUS a 16 bit | BUS a 8 bit | GPC 15A |     | GPC 15A | BUS a 8 bit  | BUS a 16 bit |

| GND          | GND         | GND     | 1   | GND     | GND          | GND          |

| +5 Vdc       | +5 Vdc      | +5 Vdc  | 2   | +5 Vdc  | +5 Vdc       | +5 Vdc       |

| D0           | D0          | D0      | 3   | N.C.    |              | D8           |

| D1           | D1          | D1      | 4   | N.C.    |              | D9           |

| D2           | D2          | D2      | 5   | N.C.    |              | D10          |

| D3           | D3          | D3      | 6   | /INT    | /INT         | /INT         |

| D4           | D4          | D4      | 7   | /NMI    | /NMI         | /NMI         |

| D5           | D5          | D5      | 8   | N.C.    | /HALT        | D11          |

| D6           | D6          | D6      | 9   | N.C.    | /MREQ        | /MREQ        |

| D7           | D7          | D7      | 10  | /IORQ   | /IORQ        | /IORQ        |

| A0           | A0          | A0      | 11  | /RD     | /RD          | /RDLDS       |

| A1           | A1          | A1      | 12  | /WR     | /WR          | /WRLDS       |

| A2           | A2          | A2      | 13  | N.C.    | /BUSAK       | D12          |

| A3           | A3          | A3      | 14  | /WAIT   | /WAIT        | /WAIT        |

| A4           | A4          | A4      | 15  | N.C.    | /BUSRQ       | D13          |

| A5           | A5          | A5      | 16  | /RESET  | /RESET       | /RESET       |

| A6           | A6          | A6      | 17  | N.C.    | / <b>M</b> 1 | /IACK        |

| A7           | A7          | A7      | 18  | N.C.    | /RFSH        | D14          |

| A8           | A8          | N.C.    | 19  | N.C.    | /MEMDIS      | /MEMDIS      |

| A9           | A9          | N.C.    | 20  | N.C.    | VDUSEL       | A22          |

| A10          | A10         | N.C.    | 21  | N.C.    | /IEI         | D15          |

| A11          | A11         | N.C.    | 22  | N.C.    |              |              |

| A12          | A12         | N.C.    | 23  | N.C.    | CLK          | CLK          |

| A13          | A13         | N.C.    | 24  | N.C.    |              | /RDUDS       |

| A14          | A14         | N.C.    | 25  | N.C.    |              | /WRUDS       |

| A15          | A15         | N.C.    | 26  | N.C.    |              | A21          |

| A16          |             | N.C.    | 27  | N.C.    |              | A20          |

| A17          |             | N.C.    | 28  | N.C.    |              | A19          |

| A18          |             | N.C.    | 29  | /R.T.   | /R.T.        | /R.T.        |

| +12 Vdc      | +12 Vdc     | N.C.    | 30  | N.C.    | -12 Vdc      | -12 Vdc      |

| +5 Vdc       | +5 Vdc      | +5 Vdc  | 31  | +5 Vdc  | +5 Vdc       | +5 Vdc       |

| GND          | GND         | GND     | 32  | GND     | GND          | GND          |

FIGURA 19: K1 - CONNETTORE PER ABACO® BUS

Pagina 24 — GPC® 15A Rel. 3.20

#### Legenda:

#### CPU a 8 bit

**A0-A15** = O - Address BUS: BUS degli indirizzi.

**D0-D7** = I/O - Data BUS: BUS dei dati.

/INT = I - Interrupt request: richiesta d'interrupt.

/NMI = I - Non Mascherable Interrupt: richiesta d'interrupt non mascherabile.

/HALT = O - Halt state: stao di Halt.

/MREQ = O - Memory Request: richiesta di operazione in memoria.

/IORQ = O - Input Output Request: richiesta di operazione in Input Output.

/RD = O - Read cycle status: richiesta di lettura. /WR = O - Write cycle status: richiesta di scrittura.

/BUSAK = O - BUS Acknowledge: riconoscimento della richiesta di utilizzo del BUS.

**/WAIT** = I - Wait: Attesa.

/BUSRQ = I - BUS Request: richiesta di utilizzo del BUS.

/RESET = O - Reset: azzeramento.

/M1 = O - Machine cycle one: primo ciclo macchina. /RFSH = O - Refresh: rinfresco per memorie dinamiche.

/MEMDIS = I - Memory Display: segnale emesso dal dispositivo periferico mappato in memoria.

**VDUSEL** = O - VDU Selection: abilitazione per il dispositivo periferico ad essere mappato in memoria.

/IEI = I - Interrupt Enable Input: abilitazione interrupt da BUS in catene di priorità.

CLK = O - Clock: clock di sistema. /R.T. = I - Reset Tast: tasto di reset.

+5 Vdc = I - Linea di alimentazione a +5 Vcc. +12 Vdc = O - Linea di alimentazione a +12 Vcc. -12 Vdc = O - Linea di alimentazione a -12 Vcc.

**GND** = O - Linea di massa per tutti i segnali del BUS.

**N.C.** = - Non Collegato

#### CPU a 16 bit

**A0-A22** = O - Address BUS: BUS degli indirizzi.

**D0-D15** = I/O - Data BUS: BUD dei dati.

/RD UDS = O - Read Upper Data Strobe: lettura del byte superiore sul BUS dati.

/WR UDS = O - Write Upper Data Strobe: scrittura del byte superiore sul BUS dati.

/IACK = O - Interrupt Acknowledge: riconoscimento della richiesta d'interrupt da parte della

CPU.

/RD LDS = O - Read Lower Data Strobe: lettura del byte inferiore sul BUS dati.

/WR LDS = O - Write Lower Data Strobe: scrittura del byte inferiore sul BUS dati.

#### N.B.

Le indicazioni di direzionalità sopra riportate sono riferite ad una scheda di comando ( $\mathbf{CPU}$  o  $\mathbf{GPC}^{\$}$ ) e sono state mantenute inalterate in modo da non avere ambiguità d'interpretazione nel caso di sistemi composti da più schede.

#### INTERFACCIAMENTO DEGLI I/O CON IL CAMPO

Al fine di evitare eventuali problemi di collegamento della scheda con tutta l'elettronica del campo a cui la **GPC**<sup>®</sup> **15A** si deve interfacciare, si devono seguire le informazioni riportate nei precedenti paragrafi e le relative figure che illustrano le modalità interne di connessione.

- Per i segnali che riguardano la comunicazione seriale con i protocolli RS 232, RS 422, RS 485 e Current Loop fare riferimento alle specifiche standard di ognuno di questi protocolli.

- Tutti i segnali a livello TTL possono essere collegati a linee dello stesso tipo riferite alla massa digitale della scheda. Il livello 0V corrisponde allo stato logico 0, mentre il livello 5V corrisponde allo stato logico 1.

## **SEGNALAZIONI VISIVE**

La scheda GPC® 15A é dotata di 7 LEDs con cui segnala alcune condizioni di stato:

| LED      | COLORE | FUNZIONE                                                                                                                    |

|----------|--------|-----------------------------------------------------------------------------------------------------------------------------|

| LD1      | Giallo | E' attivo quando J6 è n posizione 2-3, corrispondente allo stato alto del segnale SYNCB, associata allo stato di DEBUG      |

| LD2      | Verde  | E' attivo quando J6 è n posizione 1-2, corrispondente allo<br>stato basso del segnale SYNCB, associata allo stato di<br>RUN |

| LD3      | Rosso  | Segnala, quando attivo, l'attivazione del segnale di /HALT del microprocessore                                              |

| LD4, LD5 | Verde  | LED di attività gestito via software                                                                                        |

| LD7      | Rosso  | Segnala, quando attivo, l'attivazione della circuiteria di watch dog esterna                                                |

| LD8      | Rosso  | Segnala, quando attivo, l'attivazione della linea di /RESET della scheda                                                    |

FIGURA 20: TABELLA DELLE SEGNALAZIONI VISIVE

La funzione principale di questi LEDs é quella di fornire un'indicazione visiva dello stato della scheda, facilitando quindi le operazioni di debug e di verifica di funzionamento di tutto il sistema. Per una più facile individuazione di tali segnalazioni visive, si faccia riferimento alla figura 22.

Pagina 26 — GPC® 15A Rel. 3.20

#### INTERFACCE PER I/O DIGITALI

Tramite CN2 e CN5 (connettori compatibili con standard di I/O **ABACO**®) si può collegare la **GPC**® **15A** ai numerosi moduli del carteggio **grifo**® che riportano lo stesso pin out. Dal punto di vista dell'installazione, queste interfacce richiedono solo un flat cable da 20 vie (FLT.20+20) o da 26 vie lato **GPC**® **15A** e 20 vie lato interfaccia (FLT.26+20) con cui é possibile portare anche le alimentazioni, mentre dal punto di vista software la gestione é semplice ed immediata. Di particolare interesse è la possibilità di collegare direttamente serie di moduli come:

- QTP 16P, QTP 24P, KDL x24, KDF 224, DEB 01, ecc. con cui risolvere tutti i problemi di interfacciamento operatore locale. Questi moduli sono già dotati delle risorse necessarie per gestire un buon livello di colloquio uomo-macchina (includono infatti display alfanumerici, tastiera a matrice e LEDs di visualizzazione) ad una breve distanza dalla GPC® 15A. Dal punto di vista software i driver disponibili rendono utilizzabili le risorse dell'interfaccia operatore direttamente con le istruzioni ad alto livello per la gestione della console.

- MCI 64 con cui risolvere tutti i problemi di salvataggio di grosse quantità di dati. Questo modulo é dotato di un connettore per memory card PCMCIA su cui possono essere inserite vari tipi di memory card (RAM, FLASH, ROM, ecc) nei vari size disponibili. Dal punto di vista software i driver disponibili coincidono con un completo file system e rendono utilizzabili le memory card direttamente con le istruzioni ad alto livello per la gestione dei files, oppure con procedure che consentono di leggere e scrivere dati ad indirizzi specifici della memory card.

- **IAC 01, DEB 01** con cui gestire una stampante con interfaccia parallela CENTRONICS. Quest'ultima può essere collegata direttamente all'interfaccia, con un cavo standard, e quindi gestita con le istruzioni relative alla stampante del linguaggio di programmazione utilizzato.

- **RBO** xx, **TBO** xx, **XBI** xx, **OBI** xx con cui bufferare i segnali di I/O TTL nei confronti del campo. Con questi moduli i segnali di input vengono convertiti in ingressi optoisolati di tipo NPN o PNP, mentre i segnali di output vengono convertiti in uscite galvanicamente isolate a transistor o relé.

Per maggiori informazioni relative si veda il capitolo "SCHEDE ESTERNE" e la documentazione del software utilizzato.

#### **INPUT DI BORDO**

La scheda **GPC® 15A** è provvista di due Dip Switch a 4 ed 8 vie (DSW1 e DSW2), tipicamente utilizzabili per la configurazione del sistema, i cui valori sono acquisibili via software. Le applicazioni più immediate possono essere quelle destinate al settaggio delle condizioni di lavoro od alla selezione di parametri relativi al firmware di bordo. La lettura della combinazione fissata sui dip switch avviene in logica negata (0-> dip in ON ed 1-> dip in OFF) effettuando un'operazione di input agli indirizzi di I/O dedicatogli dalla logica di controllo della scheda. Visto che il DSW2 può essere sostituito da un connettore per il campo si conclude che solo 4 dei 12 dip sono sempre disponibili sulla scheda. Per ulteriori informazioni si faccia riferimento al paragrafo "Mappaggio dell'I/O", mentre per una facile individuazione della loro posizione si veda la figura 22.

GPC® 15A Rel. 3.20 Pagina 27

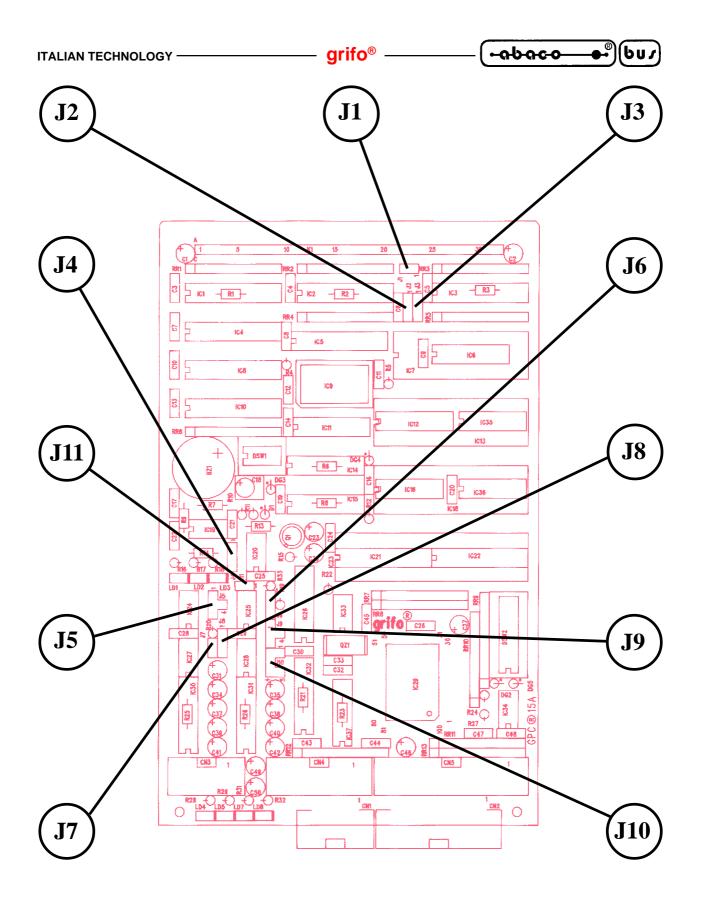

### **JUMPERS**

Esistono a bordo della **GPC**<sup>®</sup> **15A** 11 jumpers a cavaliere, con cui é possibile effettuare alcune selezioni che riguardano il modo di funzionamento della stessa. Di seguito ne é riportato l'elenco, l'ubicazione e la loro funzione nelle varie modalità di connessione.

grifo® -

| JUMPERS | N. VIE | FUNZIONE                                                                                       |

|---------|--------|------------------------------------------------------------------------------------------------|

| J1      | 2      | Collega il /RESET verso il BUS ABACO®                                                          |

| J2      | 3      | Predispone IC 7 per RAM tamponata da 2 od 8 KByte.                                             |

| Ј3      | 3      | Predispone IC 18 per EPROM o FLASH EPROM.                                                      |

| J4      | 3      | Seleziona modo di funzionamento della circuiteria di Watch Dog esterna.                        |

| J5      | 4      | Seleziona tipo di comunicazione (RS 232, RS 422, RS 485, Current Loop) per la linea seriale B. |

| J6      | 3      | Determina stato del segnale di handshake SYNCB, per la selezione della modalità RUN o DEBUG.   |

| J7, J11 | 2      | Collegano le resistenze di terminazione alla linea di ricezione in RS 422-485.                 |

| Ј8      | 3      | Seleziona driver di ricezione per la linea seriale B in RS 422, RS 485.                        |

| J9      | 4      | Seleziona connessione della circuiteria di /RESET.                                             |

| J10     | 5      | Seleziona direzionalità e modalità di attivazione della linea seriale B in RS 422-485.         |

FIGURA 21: TABELLA RIASSUNTIVA JUMPERS

Nelle sucessive tabelle é riportata una descrizione tabellare delle possibili connessioni degli 11 jumpers con la loro relativa funzione. Per riconoscere tali connessioni sulla scheda si faccia riferimento alla serigrafia della stessa o alla figura 30 di questo manuale, dove viene riportata la numerazione dei pin dei jumpers, che coincide con quella utilizzata nella seguente descrizione. Per l'individuazione dei jumpers a bordo della scheda, si utilizzi invece la figura 25. In tutte le seguenti tabelle l'\* indica la connessione di default, ovvero quella impostata in fase di collaudo, con cui la scheda viene fornita.

Pagina 28 — GPC® 15A Rel. 3.20

FIGURA 22: DISPOSIZIONE CONNETTORI, MEMORIE, DIP SWITCH ETC.

# **JUMPERS A 2 VIE**

| JUMPERS | CONNESSIONE  | UTILIZZO                                                                             | DEF. |

|---------|--------------|--------------------------------------------------------------------------------------|------|

| J1      | non connesso | Non collega il segnale di /RESET della scheda al BUS ABACO®.                         |      |

|         | connesso     | Collega il segnale di /RESET della scheda al BUS ABACO®.                             | *    |

| J7, J11 | non connessi | Non collegano resistenza di terminazione alla linea di ricezione in RS 422-485.      | *    |

|         | connessi     | Collegano resistenza nominale di terminazione alla linea di ricezione in RS 422-485. |      |

FIGURA 23: TABELLA JUMPERS A 2 VIE

# **JUMPERS A 3 VIE**

| JUMPERS | CONNESSIONE   | UTILIZZO                                                                                | DEF. |

|---------|---------------|-----------------------------------------------------------------------------------------|------|

| J2      | posizione 1-2 | Predispone IC 7 per RAM tamponate o EEPROM da 2 KByte.                                  | *    |

|         | posizione 2-3 | Predispone IC 7 per RAM tamponate o EEPROM da 8 KByte.                                  |      |

| Ј3      | posizione 1-2 | Predispone IC 18 per FLASH EPROM.                                                       |      |

|         | posizione 2-3 | Predispone IC 18 per EPROM.                                                             | *    |

| J4      | posizione 1-2 | Seleziona funzionamento astabile per la circuiteria di Watch Dog esterna.               | *    |

|         | posizione 2-3 | Seleziona funzionamento monostabile per la circuiteria di Watch Dog esterna.            |      |

| J6      | posizione 1-2 | Connette segnale SYNCB della SIO a GND, attivando LD2 e selezionando la modalità RUN.   |      |

|         | posizione 2-3 | Connette segnale SYNCB della SIO a +Vcc, attivando LD1 e selezionando la modalità DEBUG |      |

| Ј8      | posizione 1-2 | Seleziona driver di IC 27 per la ricezione in RS 422, RS 485                            | *    |

|         | posizione 2-3 | Seleziona driver di IC 28 per la ricezione in RS 422, RS 485                            |      |

FIGURA 24: TABELLA JUMPERS A 3 VIE

Pagina 30 — *GPC*® 15A Rel. 3.20

FIGURA 25: DISPOSIZIONE JUMPERS

# **JUMPER A 4 VIE**

| JUMPERS | CONNESSIONE   | UTILIZZO                                                                                           | DEF. |

|---------|---------------|----------------------------------------------------------------------------------------------------|------|

| J5      | posizione 1-2 | Predispone linea seriale B in RS 232.                                                              | *    |

|         | posizione 2-3 | Predispone linea seriale B in current loop.                                                        |      |

|         | posizione 2-4 | Predispone linea seriale B in RS 422-485.                                                          |      |

| Ј9      | posizione 1-2 | Connette circuiteria di reset al pulsante P1 esterno alla scheda, presente in alcuni mother board. | *    |

|         | posizione 2-3 | Connette circuiteria di reset alla circuiteria di Watch Dog, esterna alla CPU.                     |      |

|         | posizione 2-4 | Connette circuiteria di reset alla circuiteria di Watch Dog, interna alla CPU.                     |      |

FIGURA 26: TABELLA JUMPERS A 4 VIE

# **JUMPER A 5 VIE**

| JUMPERS | CONNESSIONE         | UTILIZZO                                                                                    | DEF. |

|---------|---------------------|---------------------------------------------------------------------------------------------|------|

| J10     | posizione 1-2 e 3-4 | Abilita trasmissione su linea seriale B in RS 422-485 in half duplex a 2 fili               |      |

|         | posizione 2-3 e 4-5 | Abilita trasmissione su linea seriale B in RS 422-485 in full duplex o half duplex a 4 fili | *    |

FIGURA 27: TABELLA JUMPERS A 5 VIE

l'\* indica la connessione di default, ovvero quella impostata in fase di collaudo, con cui la scheda viene fornita.

Pagina 32 ——— **GPC®** 15A Rel. 3.20

# **RESET E WATCH DOG**

La scheda GPC® 15A è dotata di due circuiterie di Watch Dog, una interna alla CPU ed una esterna, molto efficienti e di facile gestione software. Le caratteristiche della circuiteria esterna sono le seguenti:

- funzionamento astabile;

- tempo d'intervento di circa 700 msec;

- attivazione via hardware;

- retrigger via software;

Con il jumper J4 si seleziona il modo di funzionamento della circuiteria esterna di Watch Dog (monostabile: una volta scaduto il tempo d'intervento la circuiteria si attiva rimanendo attiva fino ad un power on o reset; astabile: una volta scaduto il tempo d'intervento la circuiteria si attiva, rimane attiva per il tempo di reset e quindi si disattiva nuovamente). La durata del temp di reset é circa 7 ms, l'intervento del Watch Dog esterno è segnalato dall'accensione del LED LD8.

Le caratteristiche della circuiteria interna sono le seguenti:

- funzionamento monostabile;

- tempo d'intervento programmabile via software;

- attivarazione via software e via hardware;

- retrigger via software;

Con il jumper J9 si seleziona la sorgente di /RESET e quindi l'attivazione delle circuiterie di Watch Dog; viste le possibilità di connessione si conclude che le due sezioni di watch dog non possono essere contemporaneamente abilitate.

Con il jumper J1 infine, si ha la possibilità di non resettare tutte le schede presenti sul BUS quando il reset di bordo viene attivato; questa possibilità è veramente interessante se esaminata in relazione all'utilizzo delle circuiterie di Watch Dog, quando l'eventuale intervento di quest'ultima circuiteria non deve influire sulle altre schede del sistema.

Si ricorda che nel funzionamento monostabile, una volta scaduto il tempo d'intervento, la circuiteria di Watch Dog si attiva rimanendo attiva fino ad un power on o reset.

In corrispondenza dell'attivazione e sucessiva disattivazione del segnale di /RESET la scheda riprende l'esecuzione del programma salvato su IC13 (all'indirizzo 0000H), partendo da una condizione di azzeramento generale.

Si ricorda inoltre che il segnale di /RESET generato dalla scheda é riportato anche sul connettore K1 (pin 16C) e che tra le sorgenti di reset della **GPC**<sup>®</sup> **15A**, oltre alla circuiteria di watch dog esterna, sono sempre presentile periferiche interne alla CPUe il contatto di reset R.T. (pin 29C di K1).

Per quanto riguarda l'operazione di retrigger della circuiteria di watch dog esterna, si faccia riferimento al paragrafo "WATCH DOG" del capitolo "DESCRIZIONE SOFTWARE DELLE PERIFERICHE DI BORDO".

GPC® 15A Rel. 3.20 Pagina 33

# — grifo®

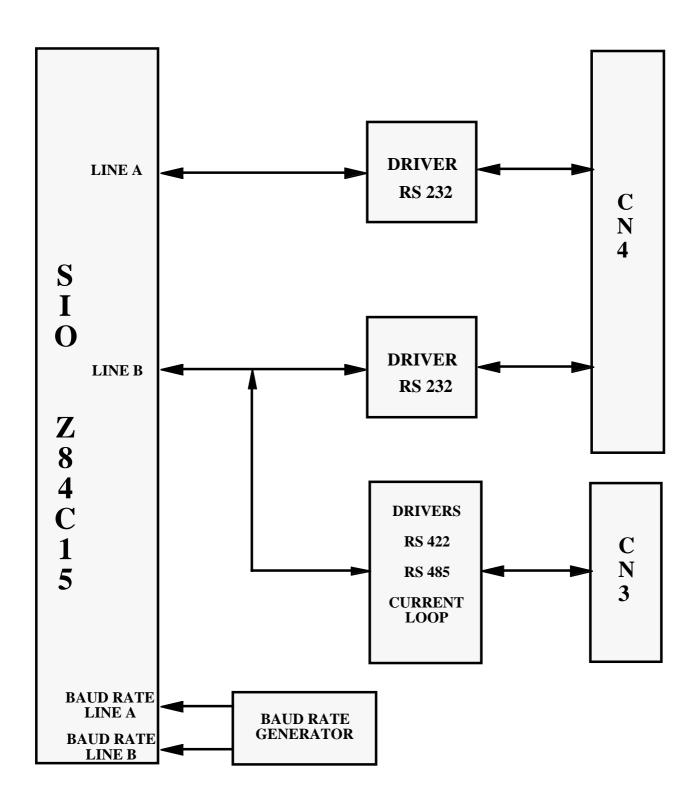

# **COMUNICAZIONE SERIALE**

La linea di comunicazione seriale A della scheda **GPC® 15A** può essere bufferata solo in RS 232, mentre la linea seriale B può essere bufferata in RS 232, RS 422, RS 485 o Current Loop. La selezione del tipo d'interfacciamento avviene via hardware e viene effettuata tramite un opportuno strippaggio dei jumpers di bordo, come può essere desunto dalla lettura delle precedenti tabelle. Dal punto di vista software sono invece definibili tutti i parametri del protocollo fisico di comunicazione tramite la programmazione dei registri interni della CPU.

Alcuni componenti necessari per le configurazioni RS 422, RS 485 e Current Loop non sono montati e collaudati sulla scheda in configurazione di default; per questo la prima configurazione della seriale B non in RS 232 deve essere sempre effettuata dai tecnici **grifo**<sup>®</sup>. A questo punto l'utente può cambiare autonomamente la configurazione seguendo le informazioni sotto riportate:

# - LINEA SERIALE B SETTATA IN RS 232 (configurazione default)

|         |   |               | IC24 | = indifferente   |

|---------|---|---------------|------|------------------|

| J5      | = | posizione 1-2 | IC25 | = indifferente   |

| J8      | = | indifferente  | IC27 | = indifferente   |

| J10     | = | indifferente  | IC28 | = indifferente   |

| J7, J11 | = | indifferente  | IC31 | = driver MAX 202 |

# - LINEA SERIALE B SETTATA IN CURRENT LOOP (opzione .CLOOP)

|         |   |               | IC24 | = HCPL 4200         |

|---------|---|---------------|------|---------------------|

| J5      | = | posizione 2-3 | IC25 | = HCPL 4100         |

| J8      | = | indifferente  | IC27 | = nessun componente |

| J10     | = | indifferente  | IC28 | = nessun componente |

| J7, J11 | = | indifferente  | IC31 | = nessun componente |

Da ricordare che l'interfaccia seriale in Current Loop é di tipo passivo e si deve quindi collegare una linea current loop attiva, ovvero provvista di un proprio alimentatore. L'interfaccia Current Loop può essere utilizzata per realizzare sia connessioni punto punto che multipunto con un collegamento a 4 o 2 fili.

#### - LINEA SERIALE B SETTATA IN RS 422 (opzione .RS 422)

|         |   |                     | IC24 | = nessun componente  |

|---------|---|---------------------|------|----------------------|

| J5      | = | posizione 2-4       | IC25 | = nessun componente  |

| J8      | = | posizione 1-2       | IC27 | = SN 75176 o MAX 483 |

| J10     | = | posizione 2-3 e 4-5 | IC28 | = SN 75176 o MAX 483 |

| J7, J11 | = | (*1)                | IC31 | = nessun componente  |

Lo stato del segnale /RTSB, gestito via software, consente di abilitare o disabilitare il trasmettitore come segue:

```

/RTSB = livello basso = stato logico 0 -> trasmettitore attivo

/RTSB = livello alto = stato logico 1 -> trasmettitore disattivo

```

Per sistemi punto punto, la linea /RTSB può essere mantenuta sempre bassa (trasmettitore sempre attivo), mentre per sistemi multipunto si deve attivare il trasmettitore solo in corrispondenza della trasmissione.

Pagina 34 — GPC® 15A Rel. 3.20

Seriale B in RS 232

Seriale B in Current Loop

Seriale B in RS 422

Seriale B in RS 485

FIGURA 28: DISPOSIZIONE DRIVER PER COMUNICAZIONE SERIALE

- LINEA SERIALE B SETTATA IN RS 485 (opzione .RS 485)

|         |   |                     | IC24 | = nessun componente  |

|---------|---|---------------------|------|----------------------|

| J5      | = | posizione 2-4       | IC25 | = nessun componente  |

| J8      | = | posizione 1-2       | IC27 | = SN 75176 o MAX 483 |

| J10     | = | posizione 1-2 e 3-4 | IC28 | = nessun componente  |

| J7, J11 | = | (*1)                | IC31 | = nessun componente  |

- arifo® -

In questa modalità le linee da utilizzare sono i pin 1 e 2 di CN3, che quindi diventano le linee di trasmissione o ricezione a seconda dello stato del segnale /RTSB, gestito via software, come segue:

```

/RTSB = livello basso = stato logico 0 -> linea in trasmissione

/RTSB = livello alto = stato logico 1 -> linea in ricezione

```

Questa comunicazione la si utilizza sia per connessioni punto punto che multipunto con un collegamento a 2 fili. Sempre in questa modalità é possibile ricevere quanto trasmesso, in modo da fornire al sistema la possibilità di verificare autonomamente la riuscita della trasmissione; infatti in caso di conflitti sulla linea, quanto trasmesso non viene ricevuto correttamente e viceversa.

(\*1) Nel caso si utilizzi la linea seriale in RS 422 o RS 485, con i jumpers J7 e J11 é possibile connettere la circuiteria di terminazione sulla linea. Tale circuiteria deve essere sempre presente nel caso di sistemi punto punto, mentre nel caso di sistemi multipunto, deve essere collegata solo sulle schede che risultano essere alla maggior distanza, ovvero ai capi della linea di comunicazione.

In fase di reset o power on, il segnale /RTSB è mantenuto a livello logico alto di conseguenza in seguito ad una di queste fasi il driver RS 485 è in ricezione o il driver di trasmissione RS 422 è disattivo, in modo da eliminare eventuali conflittualità sulla linea di comunicazione.

Per ulteriori informazioni relative alla comunicazione seriale fare riferimento agli esempi di collegamento delle figure 9÷16 ed all'appendice B di questo manuale.

#### **INGRESSI DI CONFIGURAZIONE**

La scheda **GPC**<sup>®</sup> **15A** è provvista di un Dip Switch a 4 vie (DSW1), di un Dip Switch ad 8 vie (DSW2) e di 1 jumper (J6), il quale svolge la funzione di RUN/DEBUG, tipicamente utilizzabili per la configurazione del sistema, i cui valori sono sono acquisibili via software. Le applicazioni più immediate possono essere quelle destinate al settaggio delle condizioni di lavoro od alla selezione di parametri relativi al firmware di bordo, come ad esempio: selezione della lingua di rappresentazione, identificazione del sistema all'interno di una rete di comunicazione seriale, selezione della modalità di test o di configurazione, ecc.

Si ricorda che il Dip Switch DSW2 é montato su zoccole e che occupa le linee del port B del PPI 82C55 alle quali si può accedere semplicemente rimuovendo lo stesso Dip Switch. Le modalità di acquisizione degli ingressi di configurazione sono riportate nel capitolo "DESCRIZIONE SOFTWARE DELLE PERIFERICHE DI BORDO", mentre per una facile individuazione della loro posizione si vedano le figure 22 e 25.

Pagina 36 — GPC® 15A Rel. 3.20

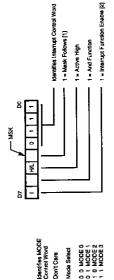

#### **INTERRUPTS**

Una caratteristica peculiare della **GPC**<sup>®</sup> **15A** è la notevole potenza nella gestione delle interruzioni. Di seguito viene riportata una breve descrizione di quali sono i dispositivi che possono generare interrupts e con quale modalità; per quanto riguarda la gestione di tali interrupts si faccia riferimento ai data sheets del microprocessore oppure all'appendice B di questo manuale.

- **ABACO**® BUS

-> Genera un /NMI sulla CPU, tramite la linea /NMI di K1.

Genera un /INT normale o vettorizzato, senza rispettare la catena di priorità daisy chain, tramite la linea /INT di K1.

- Periferiche della CPU-> Generano un /INT normale o vettorizzato, tenendo conto della catena di priorità daisy chain le sezioni: CTC, SIO, PIO.

La catena di priorità daisy chain presente sulla scheda è composta solo dalle tre periferiche SIO, PIO e CTC e può essere programmata via software tramite uno dei registri interni al microprocessore. In questo modo l'utente ha sempre la possibilità di rispondere in maniera efficace e veloce a qualsiasi evento esterno, stabilendo anche la priorità delle varie sorgenti.

Per ulteriori informazioni si veda l'appendice B di questo manuale.

#### **SELEZIONE MEMORIE**

La **GPC**<sup>®</sup> **15A** può montare fino ad un massimo di 656K bytes di memoria variamente suddivisa tra EPROM, FLASH EPROM, SRAM e EEPROM seriale. In particolare per la configurazione seguire le informazioni riportate nella seguente tabella:

| IC | DISPOSITIVO | DIMENSIONE  | STRIPPAGGIO         |

|----|-------------|-------------|---------------------|

| 18 | EPROM       | 128K Byte   | J3 in posizione 2-3 |

|    | EPROM       | 256K Byte   | J3 in posizione 2-3 |

|    | EPROM       | 512K Byte   | J3 in posizione 2-3 |

|    | FLASH EPROM | 128K Byte   | J3 in posizione 1-2 |

|    | FLASH EPROM | 256K Byte   | J3 in posizione 1-2 |

| 13 | SRAM        | 128K Byte   | -                   |

| 7  | SRAM+RTC    | 2K Byte     | J2 in posizione 1-2 |

|    | SRAM+RTC    | 8K Byte     | J2 in posizione 2-3 |

| 34 | EEPROM      | 256÷8K Byte | -                   |

FIGURA 29: TABELLA DI SELEZIONE MEMORIE

GPC® 15A Rel. 3.20 — Pagina 37

Tutti i dispositivi sopra descritti devono essere con pin out di tipo JEDEC a parte l'EEPROM seriale di IC34 che deve essere richiesta alla **grifo**® in fase di ordine della scheda. Per quanto riguarda le sigle dei vari dispositivi che possono essere montati, fare riferimento alla documentazione della casa costruttrice.

Normalmente la **GPC® 15A** é fornita nella sua configurazione di default con solamente 128K SRAM su IC13 e 512 bytes di EEPROM su IC34; ogni configurazione diversa può essere autonomamente montata dall'utente oppure richiesta nella fase di ordine. Sotto sono riportate i codici delle opzioni di memoria disponibili:

| .EE08    | -> | 1K EEPROM seriale             |

|----------|----|-------------------------------|

| .EE16    | -> | 2K EEPROM seriale             |

| .EE64    | -> | 8K EEPROM seriale             |

| .128KMOD | -> | 128K SRAM di lavoro tamponata |

| .2KMOD   | -> | 2K SRAM tamponata             |

| .8KMOD   | -> | 8K SRAM tamponata             |

| .2KRTC   | -> | 2K SRAM tamponata con RTC     |

| .8KRTC   | -> | 8K SRAM tamponata con RTC     |

Per ulteriori informazioni e costi delle opzioni, contattare direttamente la **grifo**<sup>®</sup>, mentre per una facile individuazione dei dispositivi di memoria fare riferimento alla figura 22.

Pagina 38 — GPC® 15A Rel. 3.20

FIGURA 30: PIANTA COMPONENTI

# DESCRIZIONE SOFTWARE

Questa scheda ha la possibilità di usufruire di una ricca serie di strutture software che consentono di utilizzarne al meglio le caratteristiche. In generale la scheda può utilizzare tutte le risorse software disponibili per il processore montato, ovvero i numerosi pacchetti ideati per lo Z80. Tra questi ricordiamo:

#### GET80

Completo programma di EDITOR, Comunicazione e gestione delle Memorie di Massa per le schede della famiglia 80. Questo programma, sviluppato dalla **grifo**®, consente di operare in condizioni ottimali, tutte le volte che si deve usare il **GDOS** o la versione per FLASH EPROM **FGDOS**. Viene fornito in abbinamento all'aquisto di uno dei pacchetti citati e viene personalizzato con il nome ed i dati dell'acquirente. Una serie di comodi menù a tendina facilita l'uso del programma, il quale può funzionare anche in abbinamento ad un mouse. Il programma, oltre che girare in ambiente MS-DOS, gira tranquillamente anche sulle macchine MACINTOSH in abbinamento al programma SOFT-PC. Viene fornito su dischetti MS-DOS da 3"1/2 con relativa documentazione sul manuale **GDOS 80**.

#### **GDOS 15A**

Tools di sviluppo completo per le schede della fam. 80. Viene fornito in abbinamento al programma GET80, per consentire un immediato e pieno utilizzo di questo potente strumento di sviluppo. Il GDOS può essere concettualmente diviso in due distinte strutture. Una struttura lavora essenzialmente su PC, mantenendo il collegamento con la seconda tramite la linea seriale. La seconda risiede in EPROM ed opera a bordo scheda. La parte a bordo scheda è essenzialmente un potente Sistema Operativo che si preoccupa di eseguire tutte quelle funzioni a più basso livello e nello stesso tempo consente di poter operare con linguaggi ad Alto Livello direttamente a bordo scheda. L'abbinamento delle due strutture fa si che la scheda ed il PC si comportino come un'unica macchina. Infatti la scheda usa, come se fossero le proprie, le risorse del PC come le Memoria di Massa quali i Floppy-Disk, l'Hard-Disk; la Stampante ecc. Il tutto avviene in modo completamente trasparente per l'utente il quale usa questo tipo di Macchina Virtuale esattamente come è abituato ad adoperare il suo PC. Molto interessante è la compatibilità del GDOS con tutti i linguaggi ed i programmi CP/M. Questo significa che se l'utente ha dei programmi o dei linguaggi a cui sono legate delle applicazioni o delle sue specifiche conoscenze o altro, può utilizzare tutto quanto ha, virtualmente senza cambiamenti, in modo immediato sotto GDOS.

Il **GDOS**, oltre ai tipici drivers del PC, gestisce come RAM-Disk e ROM-Disk tutte le risorse di memoria della scheda, eccedenti i 64KBytes, là dove queste siano presenti. Questo significa che i dispositivi di RAM a bordo scheda, che spesso sono Backed tramite batterie, possono essere gestite in modo diretto dai linguaggi ad alto livello, trattando comodamente come Files, le informazioni da archiviare o ricercare.

Il Tools viene fornito in EPROM, in abbinamento al disco in formato MS-DOS del **GET80**, alcuni esempi di uso e la relativa manualistica sul Sistema Operativo.

#### **FGDOS 15A**

Caratteristiche analoghe al **GDOS**, con la differenza che è in grado di programmare e cancellare le FLASH-EPROM a bordo scheda, con i programmi generati dall'utente. In questo modo non è necessario un programmatore di EPROM esterno per congelare il programma. E' inoltre possibile, tramite un PC Portatile, intervenire direttamente a bordo macchina per cambiare il programma di gestione.

Il Tools viene fornito in FLASH-EPROM, in abbinamento al disco in formato MS-DOS del **GET80**, alcuni esempi di uso e la relativa manualistica sul Sistema Operativo.

Pagina 40 — GPC® 15A Rel. 3.20

#### xGDOS MCI 150

Versione del **GDOS**, o del **FGDOS**, in grado di gestire, ad alto livello, le schedine di Memory-Card tipo PCMCIA. In abbinamento alla scheda **MCI 64**, il Sistema Operativo di bordo gestisce come RAM-Disk o ROM-Disk le Memory-Card. Questo consente di risolvere rapidamente, e senza crearsi problemi di gestione software, tutte quelle problematiche di raccolta dati che spesso si incontrano nella realizzazione di strutture di Data-Logging, gestendo questi dispositivi sempre con linguaggi ad alto livello.

Il Tools viene fornito in EPROM od in FLASH-EPROM, a secondo le necessità dell'utente, in abbinamento al disco in formato MS-DOS del **GET80**, alcuni esempi di uso e la relativa manualistica sul Sistema Operativo.

#### **CBZ-80**

Completo **Compilatore BASIC**, per la fam. di CPU Z80 compatibili, in grado di generare un codice molto compatto e molto veloce. Per poter funzionare ha bisogno di essere usato in abbinamento ad una qualsiasi delle versioni del **GDOS**. Lo **CBZ-80** consente di superare la limitazione dei 64 KBytes indirizzabili dalle CPU della famiglia 80. A questo scopo si utilizza la tecnica del CHAIN, offerta dal Sistema Operativo **GDOS** in abbinamento alle possibilità di RAM-Disk e ROM-Disk offerte dalle varie schede del carteggio **Abaco**<sup>®</sup>. Usato con il potente Editor incorporato nel programma **GET80**, si dispone di un potente strumento di lavoro per generare, con estrema efficienza e comodità, qualsiasi programma applicativo.

Il programma viene fornito in EPROM, assieme al sistema operativo della serie **GDOS**, e su dischetto MS-DOS e con il relativo manuale tecnico ed una serie di esempi.

#### PASCAL-80

Completo e molto efficiente Compilatore PASCAL per la famiglia 80 di CPU. Ha delle caratteristiche operative analoghe a quelle del **Turbo PASCAL** Ver.3 della **Borland**, a cui si fà riferimento per quanto riguarda sia le caratteristiche che la manualistica. Il **PASCAL-80** lavora in abbinamento ad una delle varie versioni di Sistema Operativo **GDOS**. Le modalità di Emulazione Terminale offerta dal programma **GET80**, supportano pienamente il tipico Editor a pieno schermo del PASCAL, compresa la gestione degli attributi. Sfruttando la possibilità di gestione di RAM-Disk e ROM-Disk, offerta dal **GDOS**, si possono sfruttare appieno le possibilità di OVERLAY del PASCAL per superare il limite dei 64KBytes di indirizzamento delle CPU della famiglia 80.