UNIVERSIDADE NOVA DE LISBOA

Faculdade de Ciências e Tecnologia

Depº de Engenharia Electrotécnica

Rede Sem Fios de Microcontroladores com Acesso Remoto Aplicada à Domótica

Por:

Gustavo José Henriques Patrício

Dissertação apresentada na Faculdade de Ciências e

Tecnologia da Universidade Nova de Lisboa para obtenção do

Grau de Mestre em Engenharia Electrotécnica e de

Computadores

Orientador: Prof. Doutor Luís Filipe dos Santos Gomes

Lisboa

2009

## **Agradecimentos**

Ao Prof. Doutor Luís Gomes por todo o apoio e orientação que tornaram esta dissertação possível, contribuindo também para a minha formação.

Ao Eng. Rogério Piteira por desde sempre me apoiar, motivar e cativar tanto para este trabalho como para toda esta área.

A todo o pessoal da Dynasys que me acolheu, nomeadamente ao Eng. Armando Nunes, Eng. Carlos Dias e D. Zélia. Quero agradecer em especial ao Eng. João Prudêncio cujos ensinamentos, apoio e orientação foram fundamentais para esta dissertação, assim como para toda a minha formação.

A todos os meus colegas e amigos que directa ou indirectamente me ajudaram e apoiaram.

Aos meus Pais, irmãos e familiares que sempre me apoiaram, e ainda à Rita por tudo.

#### Sumário

Nesta dissertação apresenta-se o desenvolvimento de um sistema formado por uma rede sem fios de microcontroladores. A rede é capaz de desempenhar funções de monitorização e actuação (sensores-actuadores), quer aplicadas à área da domótica, quer à área das redes de sensores sem fios (Wireless Sensor Networks - WSN). A rede em si é formada por dois tipos de elementos, um coordenador e vários nós. O sistema permite o seu controlo por acesso remoto através de uma página Web. A concretização deste sistema serve ainda como plataforma para a validação da ferramenta de geração automática de código PNML2C. Esta ferramenta parte de um modelo comportamental expresso em Redes de Petri (RdP) IOPT (Input Output Place Transition), e da sua representação em PNML (Petri Net Markup Language), de forma a gerar código C que o implementa. Os nós são implementados recorrendo a esta ferramenta, e os seus resultados analisados. Neste trabalho foi realizada uma rede de sensores-actuadores, capaz de desempenhar funções de monitorização e actuação típicas, recorrendo a componentes de baixo custo, tendo a sua aplicação em tarefas de domótica sido validada através de um protótipo laboratorial. Já a ferramenta PNML2C, embora não concluída, apresentou resultados bastante positivos, deixando bons indícios. A ferramenta foi integrada no ambiente de desenvolvimento e revelou-se capaz de efectuar a tradução fiel de um modelo para a sua implementação.

#### **Abstract**

This dissertation presents the development of a wireless networked microcontroller system. The network can be used for general-purpose monitoring and controlling activities, as well applied to the home automation (Domotics) area and to Wireless Sensor Networks (WSN) area. The network is composed by two elements, a coordinator and the nodes. This system can be controlled remotely through a Web page. The system development framework was also used as a platform to validate the PNML2C tool that is able to generate code automatically. This tool generates C code that implements a model expressed by an IOPT (Input Output Place Transition) Petri Net model represented using the PNML (Petri Net Markup Language) format. The network nodes are implemented using this tool, and its results are analyzed. On this dissertation, a fully functional sensor-actuator network was implemented, amenable for monitoring and actuating activities, relying only on low cost components. A laboratory prototype was developed allowing validation of the results. The PNML2C tool, although not finished, presented positive results. This tool was successfully integrated in the development framework and revealed able to produce an executable translation from the IOPT model amenable for supporting its implementation.

## Simbologia e notações

- N Conjunto dos números naturais

- ∈ Pertence ao conjunto

- σ Sequência de disparos de uma Rede de Petri

- AC Ar Condicionado

- ACKC Acknowledge Coordinator

- ACKN Acknowledge Node

- ACT Action

- AJAX Asynchronous Javascript And XML

- ARP Address Resolution Protocol

- ASCII American Standard Code for Information Interchange

- AW Asynchronous Wrapper

- **BOM Bill Of Materials**

- CCIPN Coloured Control Interpreted Petri Nets

- CPU Central Processing Unit

- CSMA Carrier-Sense Multiple Access

- **DHCP Dynamic Host Configuration Protocol**

- DNS Domain Name System

- EEPROM Electrically Erasable Programmable Read-Only Memory

- EHS European Home Systems Protocol

- EI Edifício Inteligente

- EIB European Installation Bus

- ETSI European Telecommunications Standards Institute

- EUA Estados Unidos da América

- FCC Federal Communication Commission

- FFD Full Function Device

- GALS Globally Asynchronous Locally Synchronous

- GPS Global Positioning System

- **HDL** Hardware Description Language

- HTML HyperText Markup Language

- HTTP Hypertext Transfer Protocol

- IC Integrated Circuit

ICD - In-Circuit Debug

ICMP - Internet Control Message Protocol

IDE - Integrated Development Environment

**IOPT - Input-Output Place-Transition**

IP - Internet Protocol

IrDA - Infrared Data Association

ISM - Industrial, Scientific and Medical radio bands

LAN – Local Area Network

LCD – Liquid Crystal Display

LED - Light-Emitting Diode

LS - Localmente Síncrono

MAC - Medium Acess Control

MCU - Microcontroller Unit

MdC – Modelos de Computação

MEMS - Microelectromechanical Systems

MOF - Meta-Object Facility

MPFS - Microchip File System

**NES - Networked Embedded Systems**

**NEST - Networked Embedded System Technology**

OS - Operating System

OSI - Open Systems Interconnection

PC - Personal Computer

PCB - Printed Circuit Board

PCC - Pausable Clock Control

PDA – Personal Digital Assistant

PDF - Portable Document Format

PHY - Physical Layer

PLC - Power Line Communication

PNML - Petri Net Markup Language

PPS - Peripheral Pin Select

PSV - Program Space Visibility

QVGA - Quarter Video Graphics Array

**RADAR - Radio Detection And Ranging**

RAM - Random-Access Memory

RdP – Rede de Petri

RdP-R - Redes de Petri Reactivas

RdP-RH - Redes de Petri Reactivas e Hierarquicas

**REQ** - Request

RF – Rádio Frequência

RFD - Reduced Function Device

RFID - Radio-Frequency Identification

RTCC - Real Time Clock Calendar

SoC - System on Chip

SPI - Serial Peripheral Interface

SSL- Secure Sockets Layer

SVG - Scalable Vectorial Graphics

**TCP - Transmission Control Protocol**

TDMA - Time-Division Multiple Access

**UDP - User Datagram Protocol**

UML – Unified Modeling Language

**USB - Universal Serial Bus**

VHDL - VHSIC Hardware Description Language

VHSIC - Very-High-Speed Integrated Circuits

VLSI - Very-Large-Scale Integration

WLAN - Wireless Local Area Network

WSN - Wireless Sensor Network

WPAN - Wireless Personal Area Network

XMI - XML Metadata Interchange

XML - Extensible Markup Language

## Índice de Matérias

| Agradecimentos                                    | 1  |

|---------------------------------------------------|----|

| Sumário                                           | 2  |

| Abstract                                          | 3  |

| Simbologia e notações                             | 4  |

| Índice de Matérias                                | 7  |

| Índice de Figuras                                 | 10 |

| Índice de Quadros                                 | 13 |

| Introdução                                        | 14 |

| Objectivos                                        | 14 |

| Motivação                                         | 15 |

| Estrutura da Dissertação                          | 17 |

| 1- Domótica                                       | 19 |

| 1.1- Introdução                                   | 19 |

| 1.2- Conceitos e Arquitecturas                    | 23 |

| 1.3- Tecnologias                                  | 25 |

| 1.3.1- Protocolo KNX                              | 28 |

| 1.3.2- X10                                        | 29 |

| 1.3.3- INSTEON                                    | 30 |

| 1.3.4- ZigBee                                     | 31 |

| 1.3.5- Outras Tecnologias                         | 34 |

| 1.4- Domótica em Portugal                         | 34 |

| 2- Sistemas Embutidos em Rede                     | 38 |

| 2.1- Introdução                                   | 39 |

| 2.2- Hardware                                     | 40 |

| 2.3- Software                                     | 42 |

| 2.4- Aplicações                                   | 45 |

| 3- Formalismos de Modelação                       | 48 |

| 3.1- Fluxogramas                                  | 50 |

| 3.2- Redes de Petri                               | 53 |

| 3.2.1- Enquadramento Histórico das Redes de Petri | 53 |

| 3.2.2- Conceito de Redes de Petri                 | 54 |

| 3.2.3- Estrutura das Redes de Petri               | 55 |

| 3.2.4- Disparo das transições                     | 58 |

| 3.2.5- Modelação com Rede de Petri      | 60 |

|-----------------------------------------|----|

| 3.2.6- Classes de Redes de Petri        | 63 |

| 3.2.7- PNML                             | 64 |

| 3.3- UML                                | 66 |

| 3.3.1- Diagrama de Casos de Uso         | 67 |

| 3.3.2- Diagramas de Sequência           | 69 |

| 4- Sistemas GALS                        | 70 |

| 4.1- Introdução                         | 70 |

| 4.2- Conceitos dos Sistemas GALS        | 71 |

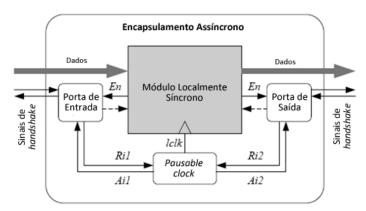

| 4.2.1- Encapsulamento Assíncrono        | 72 |

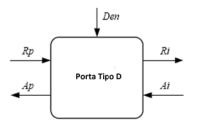

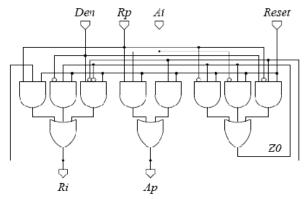

| 4.2.2- Controlador de Portas            | 73 |

| 4.2.3- Gerador do sinal de relógio      | 75 |

| 4.3- Resultados dos sistemas GALS       | 75 |

| 4.4- Vantagens e desvantagens           | 78 |

| 4.5- Utilizações de Sistemas GALS       | 80 |

| 4.6- Enquadramento                      | 81 |

| 5- Ferramentas Utilizadas               | 83 |

| 5.1- Ferramentas para as Redes de Petri | 83 |

| 5.1.1- Snoopy-IOPT                      | 83 |

| 5.1.2- Conversor PNML2C                 | 83 |

| 5.2- Ferramentas de desenvolvimento     | 85 |

| 5.2.1- MPLAB e Compilador               | 85 |

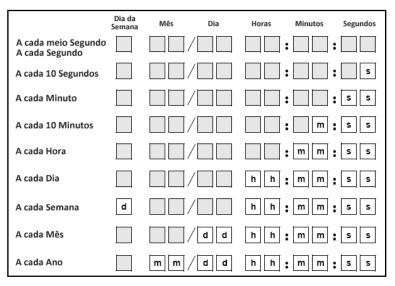

| 5.2.2- Stack TCP-IP                     | 86 |

| 5.3- Ferramentas de documentação        | 87 |

| 5.3.1- Doxygen                          | 87 |

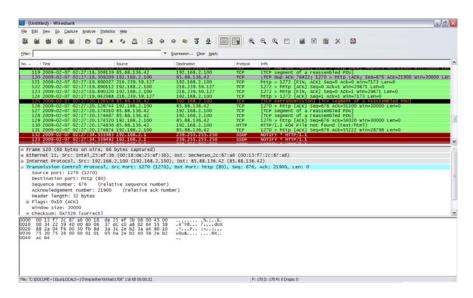

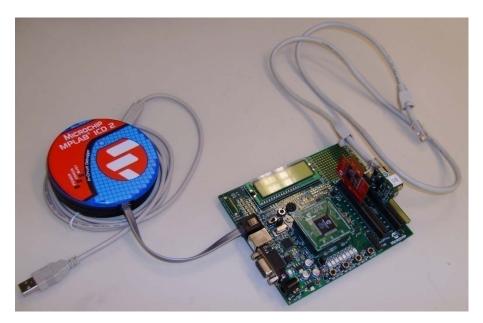

| 5.4- Ferramentas de Debug               | 87 |

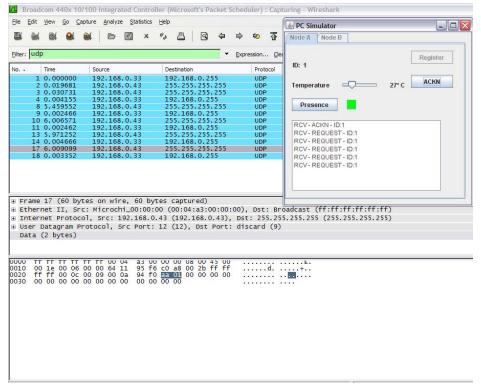

| 5.4.1- Wireshark                        | 87 |

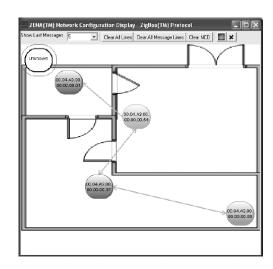

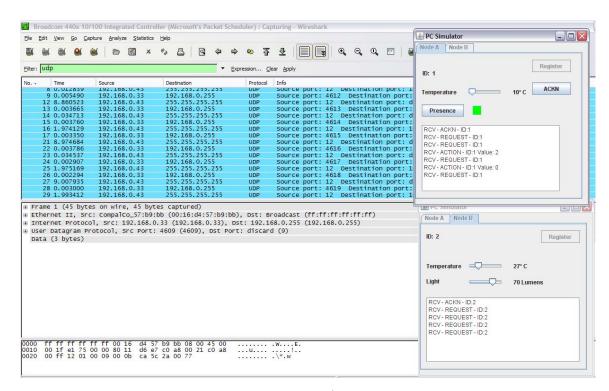

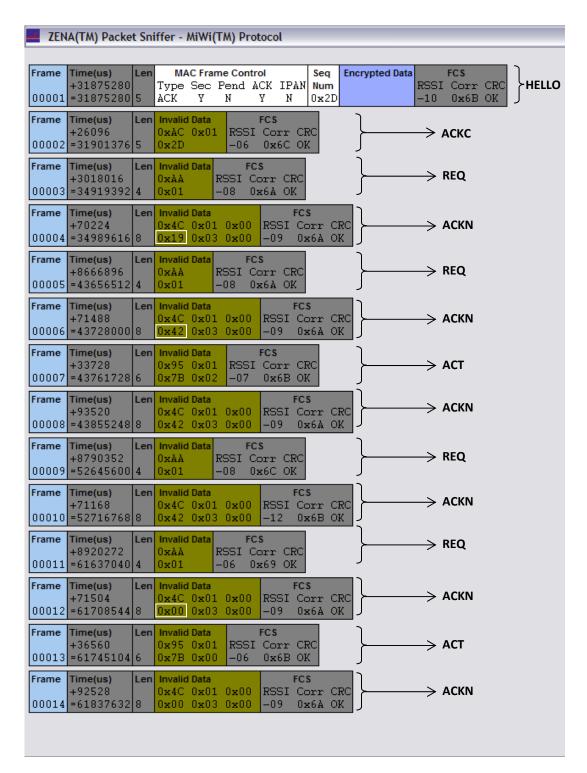

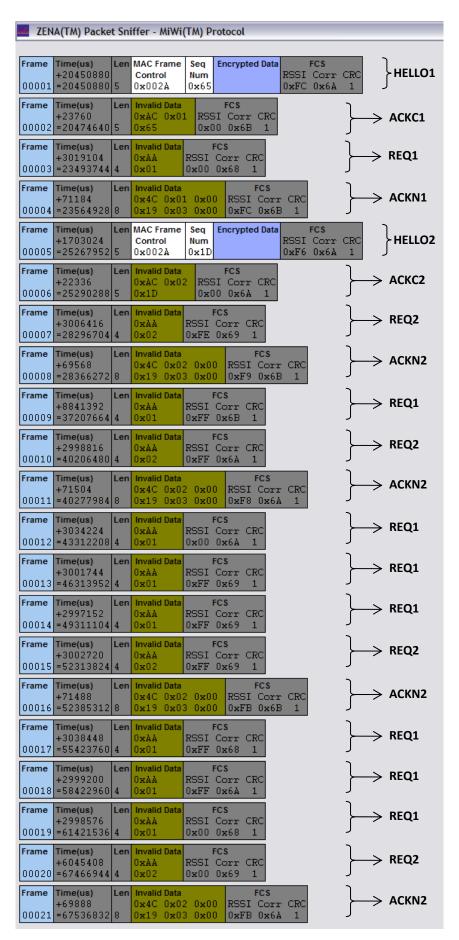

| 5.4.2- ZENA Network Analyzer            | 88 |

| 5.5- Hardware Utilizado                 | 89 |

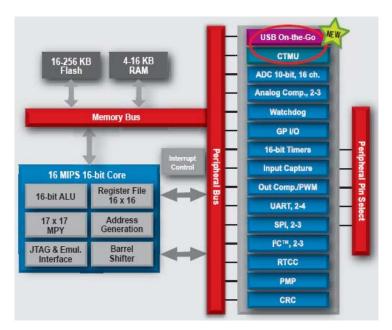

| 5.5.1- PIC24FJ128GA010                  | 89 |

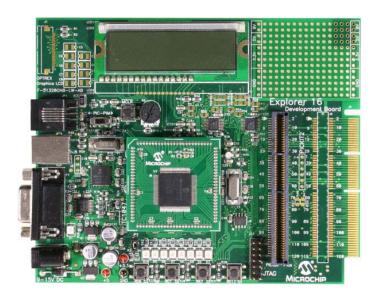

| 5.5.2- Placa Explorer16                 | 89 |

| 5.5.3- Kit PICDEM Z                     | 90 |

| 5.5.4- Ethernet PICtail Plus            | 91 |

| 5.5.5- PICtail Plus 2.4GHz RF           | 92 |

| 5.5.6- Comando IrDA – KBC56A            | 92 |

| 5.5.7- ICD2                            | 93  |

|----------------------------------------|-----|

| 6- Contribuições                       | 94  |

| 6.1- Descrição do Sistema              | 94  |

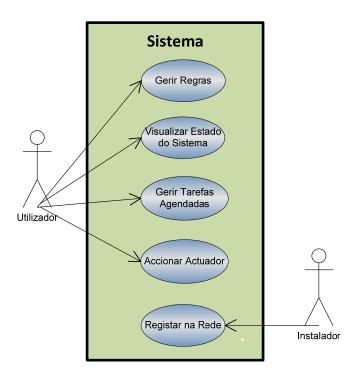

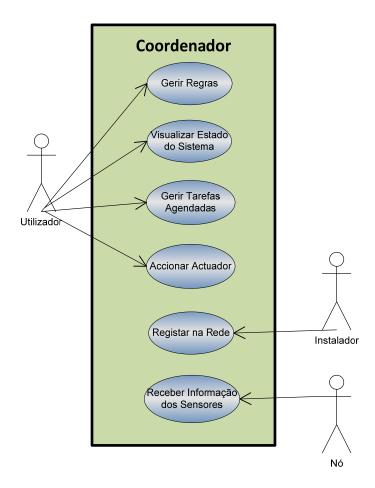

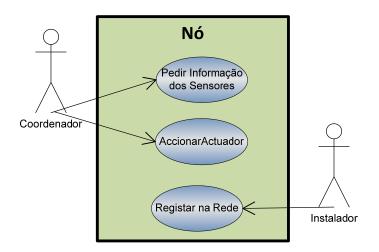

| 6.2- Casos de uso                      | 96  |

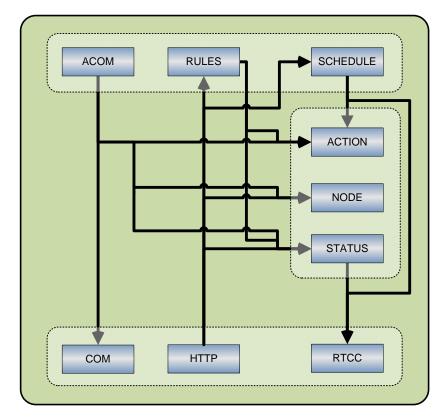

| 6.3- Arquitectura do Sistema           | 98  |

| 6.3.1- Coordenador                     | 99  |

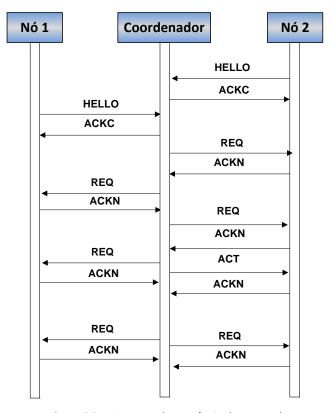

| 6.3.2- Protocolo                       | 112 |

| 6.3.3- Nó                              | 116 |

| 6.4- Teste e Resultados                | 122 |

| 6.4.1- Testes Unitários                | 122 |

| 6.4.2- Testes de Sistema               | 125 |

| 6.4.3- Resultados da ferramenta PNML2C | 128 |

| 6.4.4- Modelo de Aplicação             | 129 |

| 7- Conclusões                          | 133 |

| Referências                            | 136 |

| Anexo I – Manual de utilização         | 145 |

# Índice de Figuras

| Figura 1.1 - Exemplo de um sistema domótico, reproduzido de [HAI, 09]                   | 22 |

|-----------------------------------------------------------------------------------------|----|

| Figura 1.2 – Protocolos sem fios, adaptado de [Masters, 08]                             | 26 |

| Figura 1.3 – Rede em Estrela [Masters, 08]                                              | 26 |

| Figura 1.4 - Rede em Árvore [Masters, 08]                                               | 27 |

| Figura 1.5 - Rede em Malha [Masters, 08]                                                | 27 |

| Figura 1.6 – Lâmpada X10, extraído de [EuroX10, 09]                                     | 29 |

| Figura 1.7 - Módulo X10, extraído de [EuroX10, 09]                                      | 29 |

| Figura 1.8 – Conversor X10, extraído de [EuroX10, 09]                                   | 30 |

| Figura 1.9 – Comando X10, extraído de [EuroX10, 09]                                     | 30 |

| Figura 1.10 – Pilha de camadas ZigBee, adaptado de [Masters 08]                         | 31 |

| Figura 2.1 – Topologia típica WSN                                                       | 39 |

| Figura 2.2 – Esquema de um <i>mote</i>                                                  | 41 |

| Figura 3.1 - Terminal                                                                   | 50 |

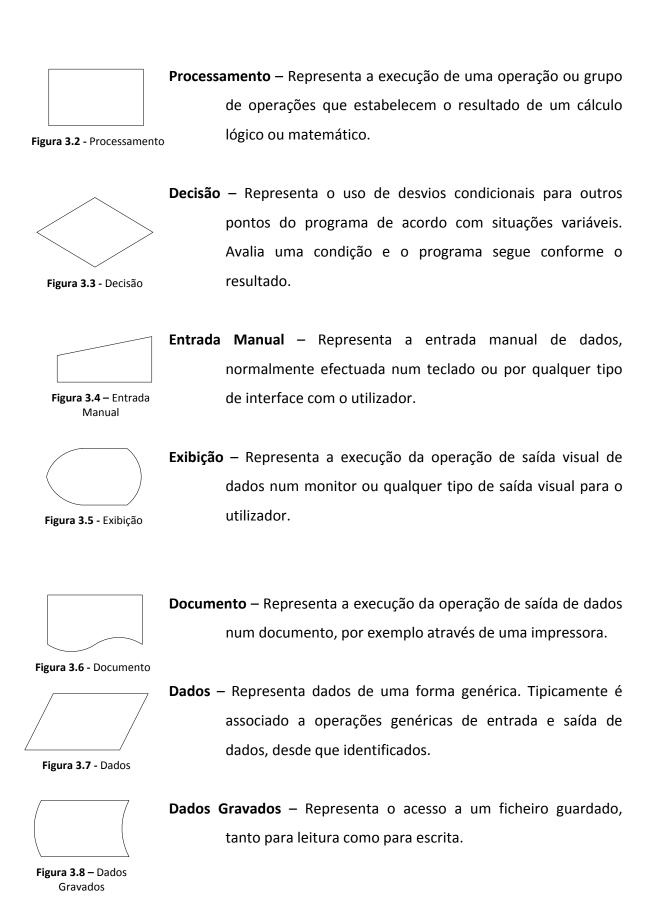

| Figura 3.2 - Processamento                                                              | 51 |

| Figura 3.3 - Decisão                                                                    | 51 |

| Figura 3.4 – Entrada Manual                                                             | 51 |

| Figura 3.5 - Exibição                                                                   | 51 |

| Figura 3.6 - Documento                                                                  | 51 |

| Figura 3.7 - Dados                                                                      | 51 |

| Figura 3.8 – Dados Gravados                                                             | 51 |

| Figura 3.9 – Preparação                                                                 | 51 |

| Figura 3.10 – Processo Predefinido                                                      | 52 |

| Figura 3.11 – Operação Manual                                                           | 52 |

| Figura 3.12 - Conector                                                                  | 52 |

| Figura 3.13 - Linha                                                                     | 52 |

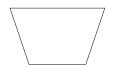

| Figura 3.14 – Exemplo de Fluxograma                                                     | 52 |

| Figura 3.15 - Lugar                                                                     | 55 |

| Figura 3.16 - Transição                                                                 | 56 |

| Figura 3.17 - Arco                                                                      | 56 |

| Figura 3.18 – Exemplo de uma Rede de Petri, adaptado de [Murata, 89]                    | 57 |

| Figura 3.19 – Rede de Petri marcada, extraído de [Reis, 08]                             | 58 |

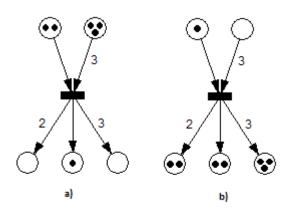

| Figura 3.22 – Disparo de uma transição (arcos com pesos)                                | 59 |

| Figura 3.20 – Transição desabilitada                                                    | 59 |

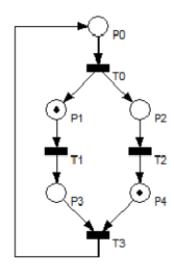

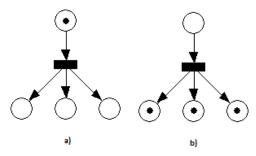

| Figura 3.21 – Disparo de uma transição. a) situação inicial. b) situação após o disparo | 59 |

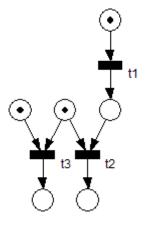

| Figura 3.23 – Paralelismo                                                               | 60 |

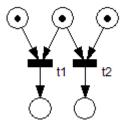

| Figura 3.24 - Conflito                                                                  | 61 |

| Figura 3.25 - Confusão                                                                  | 61 |

| Figura 3.26 - Sincronização                                                             | 61 |

| Figura 3.27 – Gestão de recursos                                                        | 61 |

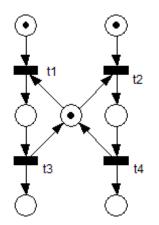

| Figura 3.28 – Lugares complementares                                                    |    |

| Figura 3.29 - Memória                                                                   | 62 |

| Figura 3.30 – Arco de teste                                                             | 62 |

| Figura 3.31 – Ferramentas Fordesign, adaptado de [Fordesign, 07]                        | 66 |

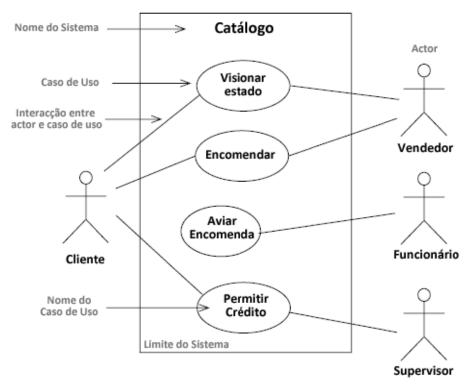

| Figura 3.32 – Exemplo de diagrama de casos de uso, adaptado de [Rumbaugh et al, 99]            | 68        |

|------------------------------------------------------------------------------------------------|-----------|

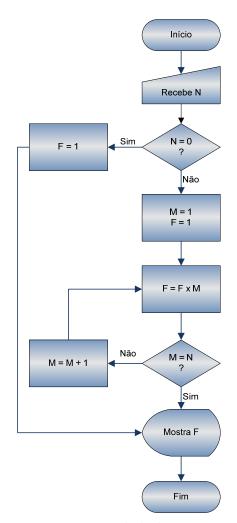

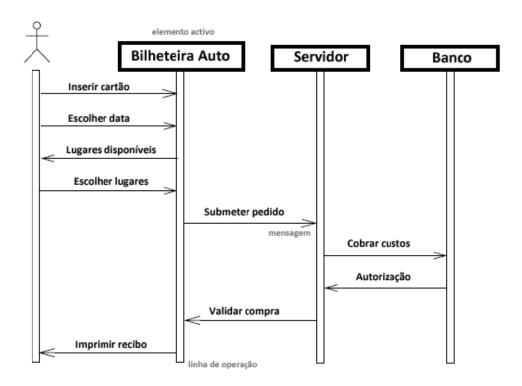

| Figura 3.33 - Exemplo de diagrama de sequência, adaptado de [Rumbaugh et al, 99]               | 69        |

| Figura 4.1 Comunicação assíncrona entre módulos, adaptado de [Muttersbach et al, 00]           | 70        |

| Figura 4.2 - Módulo funcional num sistema GALS, adaptado de [Muttersbach et al, 00]            | 73        |

| Figura 4.3 - Esquema de uma Porta tipo-D [Muttersbach et al, 00]                               | 74        |

| Figura 4.4 - Esquemático de um controlador D-type [Muttersbach et al, 00]                      | 74        |

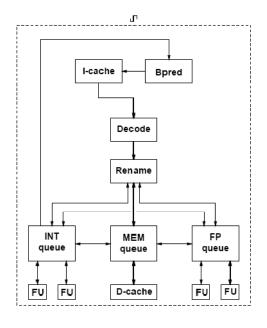

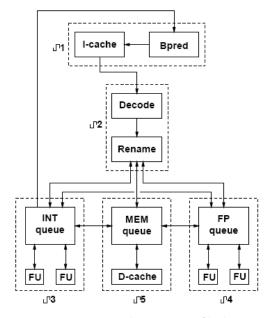

| Figura 4.5 - Processador síncrono (base), extraído de [lyer-Marculescu, 02]                    |           |

| Figura 4.6 - Processador GALS, extraído de [Iyer-Marculescu, 02]                               | 76        |

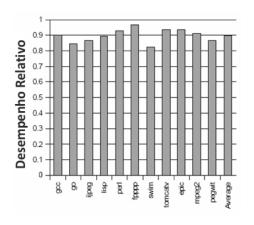

| Figura 4.7 - Desempenho do processador GALS relativo ao de base, de [Iyer-Marculescu, 02]      |           |

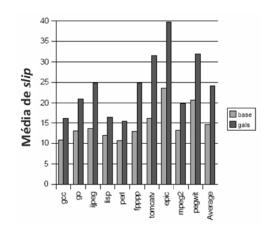

| Figura 4.8 - Média de slip, extraído de                                                        | 77        |

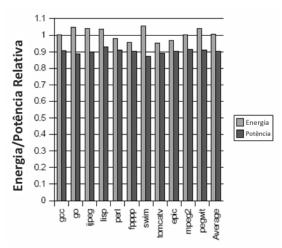

| Figura 4.9 - Consumo do processador GALS relativo ao de base, extraído de [Iyer-Marculescu, 02 | <br>]_ 78 |

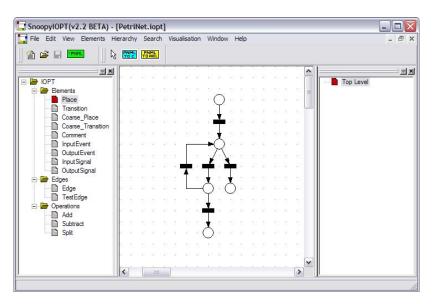

| Figura 5.1- Snoopy-IOPT                                                                        | 83        |

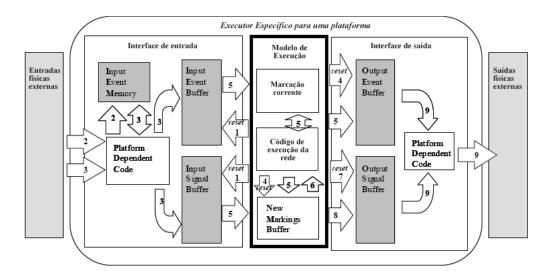

| Figura 5.2 – Arquitectura do código gerado, extraído de [Pais, 04]                             | 84        |

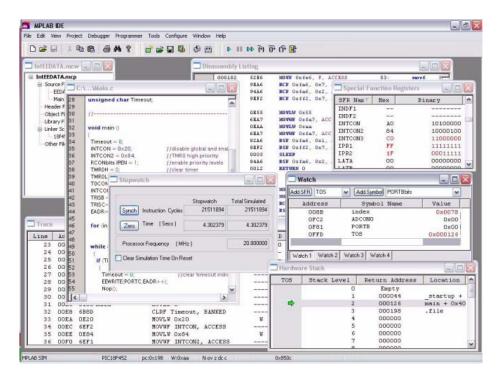

| Figura 5.3 – MPLAB IDE, extraído de [Microchip, 09]                                            | 85        |

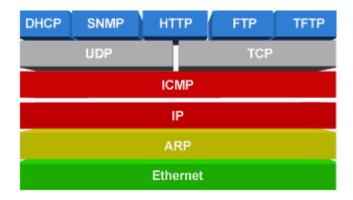

| Figura 5.4 – Stack TCP-IP da Microchip, extraído de [Microchip, 09]                            |           |

| Figura 5.5 – Captura no Wireshark                                                              | 88        |

| Figura 5.6 – Placa Zena Network Analyzer, extraído de [Microchip, 09]                          | 88        |

| Figura 5.7 – Interface gráfico do ZENA Network Analyzer, extraído de [Microchip, 09]           | 88        |

| Figura 5.8 – Diagrama de blocos PIC24F, extraído de [Microchip, 09]                            |           |

| Figura 5.9 – PIC32 PIM, extraído de [Microchip, 09]                                            | <br>90    |

| Figura 5.10 – Explorer 16, extraído de [Microchip, 09]                                         | 90        |

| Figura 5.11 – Kit PICDEM Z, extraído de [Microchip, 09]                                        |           |

| Figura 5.12 – Ethernet PICtail Plus, extraído de [Microchip, 09]                               | 91        |

| Figura 5.13 - PICTail Plus 2.4GHz RF, extraído de [Microchip, 09]                              | 92        |

| Figura 5.16 – Microchip ICD2, extraído de [Microchip, 09]                                      | 93        |

| Figura 5.14 - Receptor KBC56A, extraído de [Noritake, 09]                                      |           |

| Figura 5.15 – Comando KBC56A, extraído de [Noritake, 09]                                       | 93        |

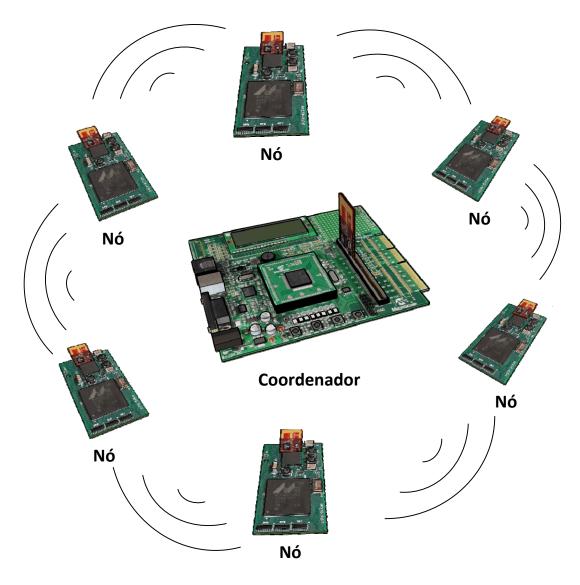

| Figura 6.1 – Topologia da rede                                                                 | 95        |

| Figura 6.2 – Diagrama de sequência do Protocolo                                                | 96        |

| Figura 6.3 – Casos de uso do Sistema                                                           | 96        |

| Figura 6.4 – Casos de uso do coordenador                                                       | 97        |

| Figura 6.5 – Casos de uso dos nós                                                              | 98        |

| Figura 6.6 – Hardware do Coordenador                                                           | _ 100     |

| Figura 6.7 – Diagrama de blocos do coordenador                                                 |           |

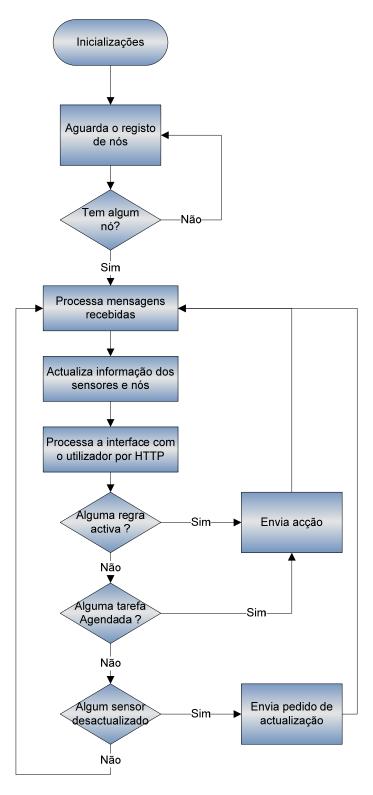

| Figura 6.8 – Fluxograma do coordenador                                                         |           |

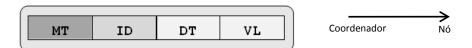

| Figura 6.9 – Mensagem HELLO                                                                    | _ 113     |

| Figura 6.10 – Mensagem ACKC                                                                    | _ 113     |

| Figura 6.11 – Mensagem REQ                                                                     | _ 113     |

| Figura 6.12 – Mensagem ACT                                                                     | _ 114     |

| Figura 6.13 – Mensagem ACKN                                                                    | _ 114     |

| Figura 6.14 – Hardware do nó                                                                   | _ 117     |

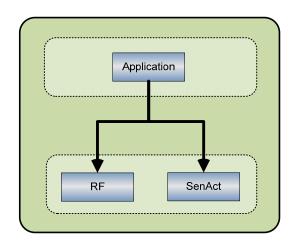

| Figura 6.15 – Diagrama de blocos do nó                                                         | _ 117     |

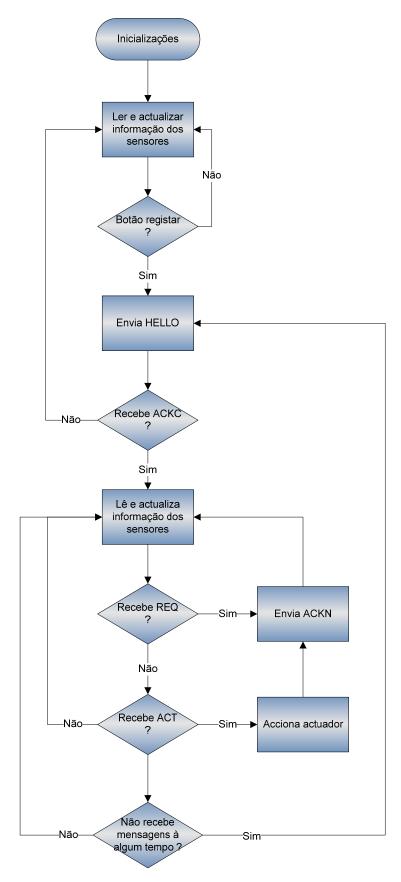

| Figura 6.16 – Fluxograma do nó                                                                 |           |

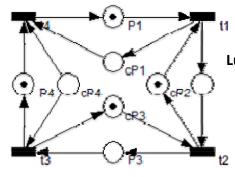

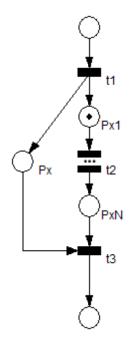

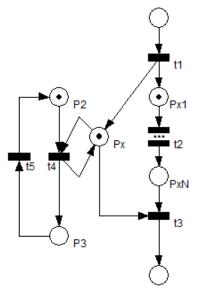

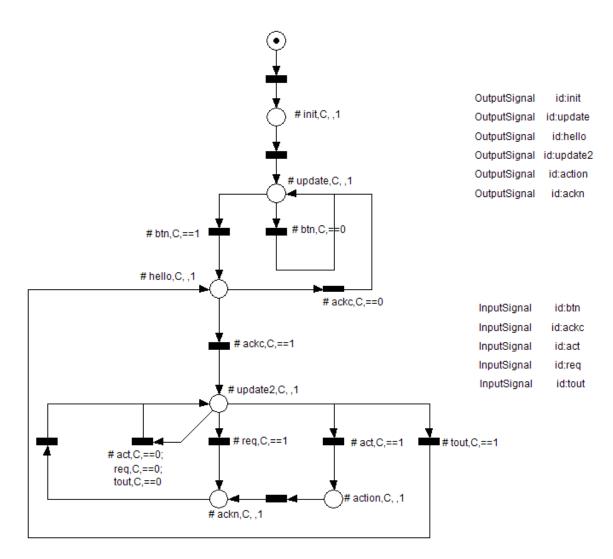

| Figura 6.17 – RdP do nó                                                                        | _ 120     |

| Figura 6.18 – 1º Teste unitário                                                                | _ 123     |

| Figura 6.19 – 2º Teste unitário                                                                | _ 124     |

|                                                                                                |           |

| Figura 6.20 – 1º Teste de sistema               | 126 |

|-------------------------------------------------|-----|

| Figura 6.21 – 2º Teste de sistema               | 127 |

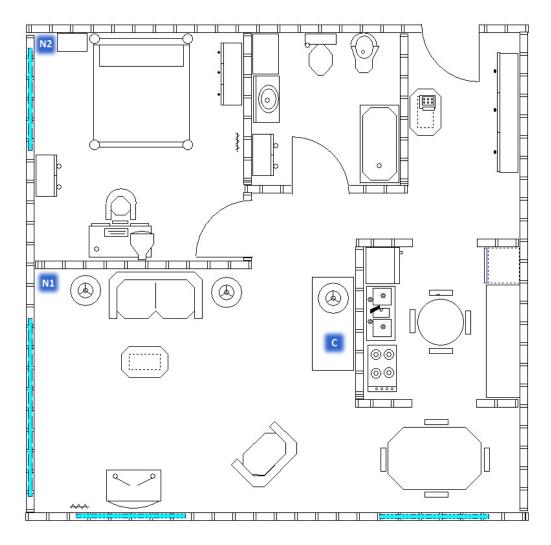

| Figura 6.22 – Planta do modelo de aplicação     | 130 |

| Figura 6.23 – Esquema 3D do modelo de aplicação | 131 |

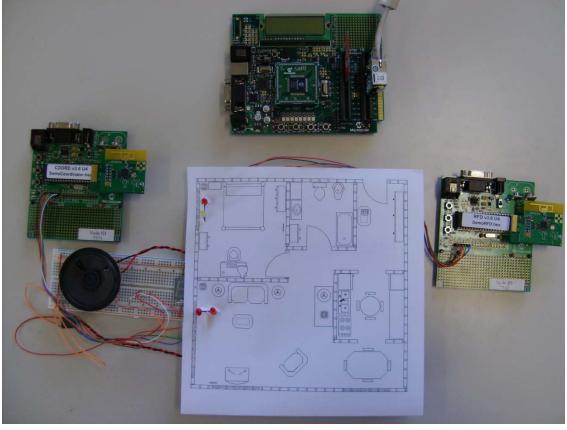

| Figura 6.24 – Protótipo do modelo de aplicação  | 131 |

| Figura 6.25 – Segundo Protótipo                 | 132 |

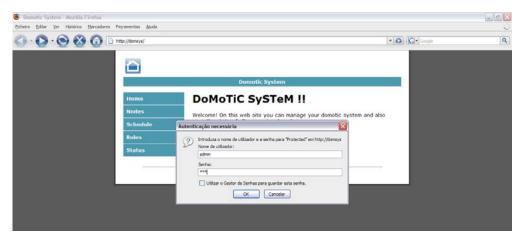

| Figura I.0.1 – Acesso à configuração            | 145 |

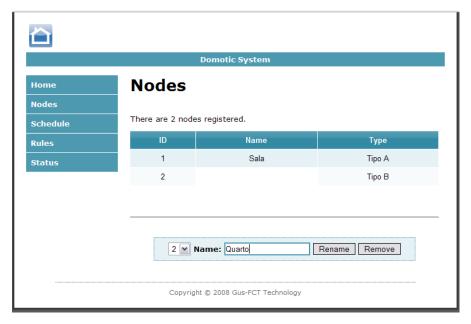

| Figura I.0.2 – Secção dos nós                   | 146 |

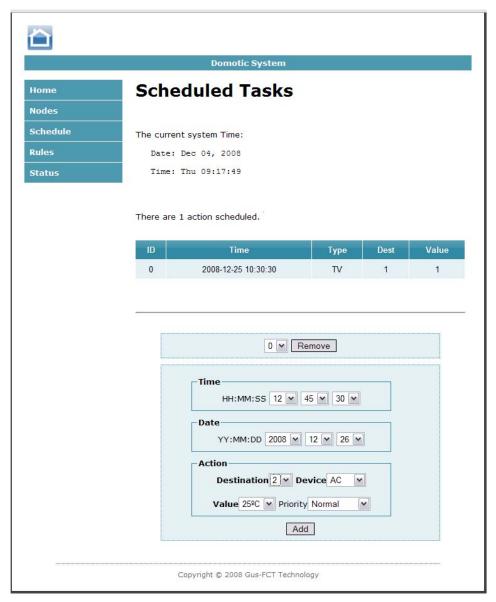

| Figura I.0.3 – Secção das tarefas agendadas     | 147 |

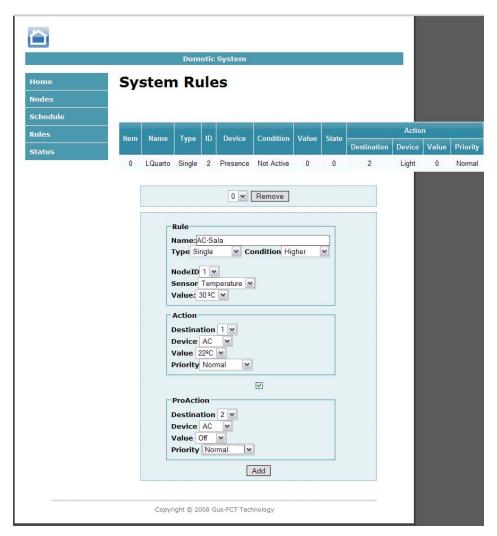

| Figura I.0.4 – Secção das regras                | 148 |

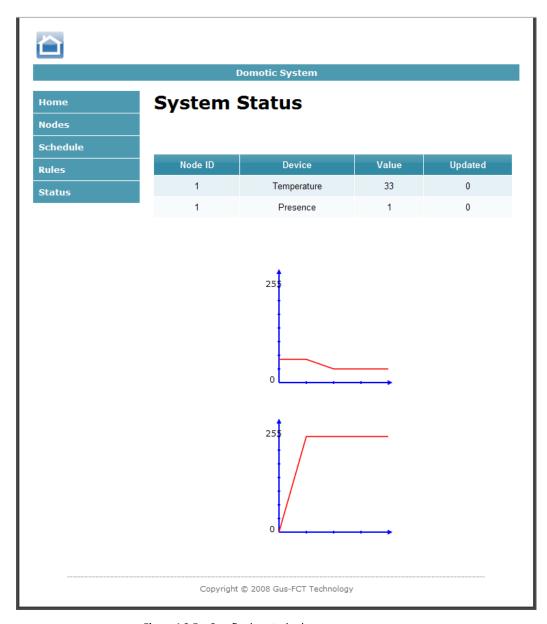

| Figura I.0.5 – Secção do estado dos sensores    | 149 |

## Índice de Quadros

| Tabela 3.1 - Classes das RdP [Lino, 03]                           | 63  |

|-------------------------------------------------------------------|-----|

| Tabela 6.1 – Formato do tempo no RTCC, adaptado de [PIC24F, 07]   | 102 |

| Tabela 6.2 – Máscaras de Alarme do RTCC, adaptado de [PIC24F, 07] | 103 |

| Tabela 7.1 – Custo das ferramentas de desenvolvimento             | 133 |

| Tabela 7.2 – Custo dos componentes                                | 134 |

## Introdução

### **Objectivos**

Esta dissertação centra-se em dois objectivos principais. O primeiro objectivo é o projecto, desenvolvimento e implementação de um sistema que forme uma rede de sensores-actuadores. O segundo objectivo consiste na validação da ferramenta de geração automática de código PNML2C.

A rede de sensores deverá ser capaz de recolher informação dos seus vários elementos e reagir conforme situações específicas. Este sistema deverá desempenhar funções quer no âmbito da domótica, quer no âmbito das redes de sensores sem fios (Wireless Sensor Networks - WSN).

Nesta rede existirá um elemento designado coordenador, onde residirá toda a inteligência do sistema. Cada elemento representa um subsistema, que quando associado a outros formam uma rede. Além deste existirão os nós que irão recolher informação dos sensores, enviando-a ao coordenador e accionar se necessário os seus actuadores. A comunicação entre estes elementos deverá ser efectuada sem fios por rádio frequência (RF).

O sistema terá que ser autónomo na medida em que deverá saber como reagir a situações previamente definidas, sem que para isso o utilizador tenha que interferir. Deverá ainda desempenhar tarefas que o utilizador agende para um momento específico.

De modo a configurar e visualizar o estado do sistema haverá um interface com o utilizador. Este será implementado no coordenador e será composto por uma página *Web*. Assim será possível ao utilizador do sistema a interacção com o mesmo remotamente.

Com a concretização deste primeiro objectivo, o sistema desenvolvido servirá como plataforma para a realização do segundo objectivo. Neste a modelação dos nós da rede deverá ser efectuada através de Redes de Petri (RdP). Partindo desta RdP será gerado código automaticamente que será implementado e testado. Assim este segundo objectivo centra-se na validação da ferramenta académica que permite a geração de código C, partindo de um modelo expresso por RdP. Esta plataforma irá pôr a interagir

um sistema composto por vários elementos cujo desenvolvimento segue diferentes metodologias.

## Motivação

A realização deste trabalho foi motivada por diversos factores. Em primeiro lugar pelo gosto pessoal em desenvolver pequenos equipamentos controlados por microcontroladores (Microcontroller Unit - MCU) com funcionalidades inovadoras. O desenvolvimento deste tipo de sistemas é sem dúvida, por agora, o que mais gosto e realização confere ao autor desta dissertação.

Desde sempre que houve um fascínio pelos sistemas embutidos, e a actual capacidade de lhes adicionar funcionalidades avançadas torna-os ainda mais apelativos.

Este trabalho reúne várias componentes interessantes. Uma dessas componentes é o desenvolvimento de um sistema embutido através da programação de microcontroladores. Outra é a possibilidade de conferir ao sistema um interface remoto através de uma página *Web*. Já a comunicação por rádio frequência é sem dúvida uma componente que confere aos sistemas uma versatilidade única.

Este gosto pelos sistemas embutidos desde sempre existiu. Produzir um pequeno programa que faça acender um LED (Light-Emitting Diode) sempre cativou muito mais o autor desta dissertação do que o tradicional HelloWorld da programação para aplicações PC (Personal Computer). Actualmente é possível em vez de acender um LED efectuar algo tão avançado como modificar uma página *Web*, enviar um e-mail ou mesmo representar esse "LED" aceso num ecrã sensível ao toque (*touch-screen*). Antigamente o interface era apenas formado por componentes como botões, LEDs e potenciómetros, sendo muito pouco apelativo para o utilizador. Neste momento é possível criar interfaces tão ricos como os criados em aplicações típicas para PC, ou ainda interfaces desenhados para a *Web* que são e continuarão a ser, sem dúvida, os que os utilizadores mais gostam e acostumados estão.

A possibilidade de visitar um equipamento remotamente através da Internet é uma ferramenta extremamente poderosa e com inúmeras potencialidades. Tanto a telemetria como o controlo remoto são áreas muito interessantes. A inclusão desta funcionalidade ao trabalho desenvolvido foi sem dúvida motivadora.

Já a comunicação sem fios por RF é também uma característica cativante. Actualmente pode-se verificar que as tecnologias sem fios têm tido uma proliferação e aceitação muito grande. Aplicado aos sistemas embutidos, vemos e aguardamos o papel que, por exemplo, o RFID poderá vir a ter na nossa sociedade.

De certo modo a motivação para esta dissertação surge com os recentes e grandes avanços na área dos sistemas embutidos, que aliados aos interesses pessoais, constituem um factor impulsionador ao desenvolvimento deste trabalho.

Mas não são apenas estes que motivam esta dissertação. A possibilidade de modelar partes do sistema através de RdP e gerar o código que a implementa, é algo extremamente aliciante. Por vezes, certos formalismos e modelações parecem não ter equivalência/aplicabilidade em sistemas reais. Essa falha na concretização de certos modelos pode ser desmotivante. Neste caso é extremamente motivador o uso de um formalismo de modelação que implemente na realidade o modelo descrito. Ferramentas deste tipo podem ser um factor decisivo no uso e aplicação de formalismos deste género.

A utilização de todos estes "ingredientes" para a implementação de um sistema aplicado à área da domótica ou ainda das WSN é muito motivador. Isto porque são áreas que estão em franca expansão e em que existem expectativas elevadas na sua utilização, sendo um desafio introduzir atitudes associadas ao desenvolvimento baseado em modelos, em particular baseado em RdP, no seu desenvolvimento.

#### Estrutura da Dissertação

Esta dissertação encontra-se dividida em sete capítulos. Começa-se, no primeiro, por introduzir a área da domótica. Inicialmente será feita uma descrição desta área e explicados alguns conceitos relacionados. Serão apresentadas várias aplicações onde a domótica se torna relevante. Serão abordadas algumas das tecnologias que dão suporte a este conceito e ainda será efectuada uma caracterização do estado actual da domótica em Portugal.

No segundo capítulo serão abordadas algumas questões relacionadas com as redes de sistemas embutidos (Networked Embedded Systems - NES). Dentro desta vasta área serão abordados os temas que dizem respeito mais especificamente às WSN. Irão ser referidas algumas das questões relacionadas com estas redes, como as implementar e quais as grandes dificuldades e desafios que esta área enfrenta. No fim são apresentadas várias aplicações destas redes.

No terceiro capítulo surge uma descrição de alguns formalismos de modelação. Será apresentada a motivação para o uso de formalismos deste género e em seguida serão abordados três formalismos de modelação. Os fluxogramas são descritos e exemplificados. As RdP serão descritas em detalhe, apresentado uma caracterização e definição das mesmas. Já o UML será brevemente abordado, sendo apenas descritas duas das muitas técnicas de modelação que este disponibiliza.

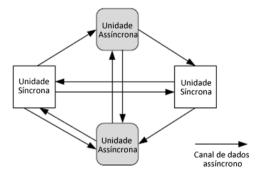

O quarto capítulo apresenta uma caracterização de um conceito para concepção de sistemas complexos, os sistemas GALS (Globally Asynchronous Locally Synchronous). Nesta caracterização explica-se o conceito, assim como as suas implementações. Em seguida são enumeradas as suas vantagens e desvantagens e são ainda apresentados os resultados de vários testes de desempenho. No final é feito um enquadramento destes sistemas nos temas desta dissertação.

O quinto capítulo apresenta todas as ferramentas que foram utilizadas neste trabalho. São referidas as ferramentas, quer de *hardware* quer de *software* que contribuíram e constituíram o trabalho desenvolvido.

É no sexto capítulo que será apresentado todo o trabalho elaborado. Nesta apresentação muitos aspectos serão abordados, desde a identificação dos objectivos/requisitos à concretização do sistema, passando pelas arquitecturas e modelos implementados.

Neste capítulo discute-se as opções tomadas ao longo do trabalho, assim como as especificidades inerentes do sistema. Na parte final deste capítulo irão ser apresentados alguns dos testes e resultados conseguidos de forma a sustentar o capítulo seguinte.

No sétimo capítulo será feito todo o balanço deste trabalho. Serão interpretados os resultados e apresentadas as conclusões finais deste trabalho assim como perspectivas futuras.

## 1- Domótica

Neste capítulo vai-se descrever sumariamente o que é Domótica, em que enquadramento surge, e ainda que tecnologias dão suporte a este conceito.

## 1.1- Introdução

O natural instinto de protecção obrigou, desde sempre, o homem a procurar abrigo. Começou por habitar em cavernas, depois em cabanas e posteriormente, com os avanços da civilização, em edifícios. À medida que estes foram evoluindo, surgiu a necessidade de controlar os seus espaços de modo a adaptá-los a diversas condicionantes, nomeadamente as alterações meteorológicas. Assim, para controlar os fluxos de ar surgiram as portas e as janelas; para controlar a luminosidade no interior, bem como por questões de privacidade, surgiram as portadas e os estores. Mais recentemente, com o aparecimento da electricidade, surgiram os interruptores para controlar o funcionamento dos dispositivos eléctricos. Todos estes "controlos" têm uma particularidade em comum: a necessidade de acção humana directa.

Com a evolução tecnológica foi possível adicionar alguns automatismos através do uso de elementos básicos como relés ou termóstatos. Estes automatismos, que surgiram nos anos 60, eram designados de automatização local, uma vez estes apenas reagiam a certos estímulos locais e não passam a informação. Já nos anos 70 com a evolução electrónica e dos sistemas baseados em microprocessadores a automação dos edifícios converge para sistemas centralizados em que a informação era concentrada numa central.

É então nos anos 80, motivados pelos novos requisitos de conforto e segurança, que surgiram sistemas para detecção de incêndios, controlo de iluminação climatização, entre outros [Nunes, 04a].

Foi com o intuito de automatizar e controlar estes processos que surgiram os Edifícios Inteligentes (EIs). Inicialmente os EIs foram criados principalmente com o objectivo de redução dos custos energéticos assim como dos de utilização e manutenção dos edifícios.

Este conceito tem sido interpretado de diversas formas, distorcido e redefinido. Várias definições são referidas em [Gomes, 97], das quais se apresenta a seguinte. Um "Edifício Inteligente deve fornecer um ambiente confortável e adaptável para o utilizador, flexível e com custos eficazes para a organização e atractivo e capaz para o proprietário; cada sistema irá interagir, de alguma forma, com todos os outros e todos os sistemas devem trabalhar em harmonia se pretender alcançar benefícios plenos para o utilizador" [Shemie, 97].

A concepção de um EI é uma área de aplicação multidisciplinar, implicando diferentes domínios do conhecimento a interagir no sentido benéfico não só dos ocupantes ou utilizadores destes edifícios, mas também dos proprietários dos mesmos. Estes benefícios são difíceis de quantificar, quer em termos económicos quer em termos ecológicos, mas podem ser associados à poupança de energia. Dos domínios do conhecimento envolvidos com contribuições relevantes nesta área destacam-se a arquitectura, as engenharias civil, electrónica e de computadores, nomeadamente de sistemas, controlo e telecomunicações [Gomes, 97].

A Domótica (em inglês mais conhecida como home automation, smart home ou mesmo domotics) surge como um ramo dos Edifícios Inteligentes mas com aplicação nas habitações. A palavra Domótica é o resultado da junção da palavra latina Domus, que significa Casa, com a palavra Robótica. Ao contrário do contexto habitual dos Els (industria e militar) a domótica procura fornecer conforto e conveniência aos lares domésticos. A ideia base é automatizar tarefas e rotinas de uma casa e ainda possibilitar a capacidade de interagir com a casa remotamente. Dos domínios do conhecimento envolvidos com contribuições relevantes nesta área destacam-se a arquitectura, as engenharias civil, electrónica e de computadores, nomeadamente de sistemas, controlo e telecomunicações [Gomes, 97]. De entre os objectivos idealizados para uma casa inteligente referem-se os seguintes:

Controlo de iluminação. Controlando cada lâmpada da casa, permitindo um ajuste energético preciso. Por exemplo, ao configurar-se cada lâmpada segundo um horário de actividade permitido, elimina-se a possibilidade de estas ficarem acesas noites inteiras por esquecimento. Ou ainda, através da instalação de sensores, permitir que a lâmpada esteja acesa apenas durante a presença de uma pessoa.

- Limpeza automática da casa. Configurando o horário de funcionamento do sistema de aspiração central, por exemplo, durante a tarde quando ninguém está em casa, evita o incómodo do ruído e possibilita que a casa se encontre limpa quando as pessoas regressam.

- Confecção de refeições. Programando o horário de funcionamento do forno, permite que a comida, previamente preparada, esteja pronta à hora de regresso das pessoas a casa.

- Irrigação de plantas. Configurando o sistema de rega, permite que em períodos prédefinidos seja fornecida a quantidade exacta de água às plantas. Este sistema pode evitar esquecimentos ou ainda ser muito útil em períodos de férias.

- Alimentação automática de animais domésticos. Utilizando um dispositivo que a horas pré-definidas liberta uma porção de ração ao animal.

- Segurança. Instalando sensores em pontos estratégicos permite accionar um sistema de alarme perante a presença de intrusos, ou efectuar o controlo de acessos de forma a gerir o tráfego de pessoas, nomeadamente em pensões ou residências.

As funcionalidades descritas, entre as muitas existentes, são meramente elucidativas, podendo ainda ser criado qualquer tipo de funcionalidade conforme os requisitos pretendidos. A grande vantagem deste tipo de soluções é que toda a gestão da casa está centralizada numa unidade que gere todos estes utensílios/dispositivos conforme os perfis/comportamentos que o utilizador pretende. Dos exemplos anteriormente mencionados foi sempre utilizado o automatismo programado. No entanto existem outras possibilidades, como por exemplo, se a central do sistema estiver com acesso à Internet, o utilizador pode accionar qualquer mecanismo quando quiser ou consultar o

estado de todos os sensores espalhados pela casa. Esta interacção remota em temporeal é uma funcionalidade extremamente importante, pois confere uma poderosa ferramenta aos seus utilizadores.

Por exemplo, se as pessoas da casa estão ausentes no trabalho ou de férias e se apercebem de que o mau tempo vai atingir a área da residência, através desta funcionalidade podem accionar remotamente os mecanismos que baixam os estores, de modo a proteger melhor a casa da intempérie.

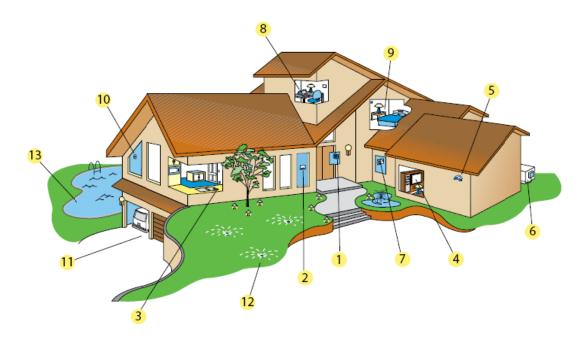

Figura 1.1 - Exemplo de um sistema domótico, reproduzido de [HAI, 09]

Apresenta-se na Figura 1.1 um exemplo de uma casa "domotizada", em que os vários pontos marcados têm o seguinte significado:

- **1-** Consola de controlo de todo o sistema. Permite a gestão da segurança, climatização, iluminação, irrigação, multimédia, etc.

- 2- Sensores para a segurança da casa.

- **3-** Iluminação com modos predefinidos, por exemplo, para ver um filme, ou para tomar a refeição.

- 4- Sistema multimédia que pode ser partilhado para todas as divisões.

- **5-** Câmaras de vigilância, que podem ser visionadas em qualquer altura, em qualquer divisão.

- 6- Gestão de energia.

- **7-** Termostato para a climatização.

- **8-** Ligação do sistema à Internet de modo a que o sistema esteja acessível em qualquer parte do mundo.

- **9-** Ligação do sistema à rede telefónica de modo a que seja também acessível pela linha telefónica.

- **10-** Sensor de movimentos para a detecção de intrusos.

- **11-** Detecção de veículos, de modo a que com a aproximação de alguém as luzes se acendam e surjam no ecrã as imagens da câmara no exterior.

- **12-** Sistema de irrigação gerido pelo sistema. Com programas estabelecidos que podem ser interrompidos em dias de chuva.

- 13- Gestão dos ciclos da piscina para a manutenção da qualidade da água.

## 1.2- Conceitos e Arquitecturas

Um sistema domótico é composto por vários nós que, espalhados pelo edifício, formam uma rede. Estes nós, instalados em locais específicos conforme as suas funções, podem ser agrupados de acordo com a seguinte classificação:

- Sensores nós que apenas recolhem informação e a enviam para outro nó. Por exemplo um nó que apenas recolhe informação sobre a temperatura e humidade de uma divisão.

- Actuadores nós que têm a capacidade de actuar sobre algo. Um exemplo será um nó num interruptor de uma lâmpada, que a acende ou apaga.

- Sensores-actuadores nós que tanto têm a capacidade de obter informação do mundo exterior, como de actuar sobre algum dispositivo. Considerando os dois exemplos anteriores, em vez de ter dois nós na mesma divisão, ter-se-ia apenas um com a capacidade de ligar e desligar a lâmpada, mas ainda estaria equipado com os sensores de temperatura e de humidade.

Em termos de inteligência do sistema este pode ter as seguintes arquitecturas.

- Centralizada quando há um nó, que costuma ser designado como coordenador, recebe toda a informação dos sensores e de qualquer outro interface com o utilizador, processa essa informação e reage enviando ordens aos actuadores, conforme os comportamentos pré-definidos. No trabalho desenvolvido nesta dissertação foi esta a arquitectura utilizada. Esta topologia pode ser vantajosa na economia de recursos, pois os nós da rede, excepto o coordenador, podem ser extremamente simples do ponto de vista de software e hardware, devido ao facto de não necessitarem de elaborar grandes processamentos. No caso dos sensores devem apenas saber recolher informação e transmiti-la. Já nos actuadores, apenas aguardam uma ordem, e actuam nos dispositivos a que estão associados. Outra vantagem do facto de ter toda a inteligência estar num único nó é que apenas é programar/configurar um necessário nó quando queremos alterar comportamento do sistema a uma situação. Já no caso de actualização em termos de firmware do sistema, apenas é necessário actualizar o coordenador, pois os sensores e actuadores continuaram a desempenhar o mesmo papel básico. Como é óbvio esta arquitectura tem a sua grande desvantagem no caso de o coordenador ficar fora de serviço, o que representa uma falha total no sistema.

- **Distribuída** quando todos os nós presentes na rede têm a capacidade de processar a informação e reagir. Esta abordagem tem a vantagem de quando algum nó deixa de funcionar, a rede apenas perde as funcionalidades associadas a esse nó e tudo o resto decorre sem problemas.

- **Mista** quando existem nós capazes de adquirir informação dos sensores, processála, reagir e depois ainda a enviam para os outros nós.

#### 1.3- Tecnologias

Actualmente existem inúmeras soluções para implementar um sistema domótico. Algumas soluções são específicas de certos fabricantes enquanto outras são normas que entidades definiram de modo a que todos os fabricantes que queiram desenvolver produtos o possam fazer desde que cumpram os requisitos (e muitas vezes paguem algumas taxas e licenciamento).

Existem diversos meios de comunicação que podem ser utilizados nas variadas soluções. Enquanto umas utilizam um só meio, outras utilizam vários, quer por questões de robustez quer por compatibilidade com outros sistemas. Os meios de comunicação utilizados podem ser: rede eléctrica, rádio frequência (RF), Bluetooth, infravermelhos (Infrared Data Association - IrDA), Ethernet formando uma rede de área local (*Local Area Network* - LAN), rede de área local sem fios (*Wireless Local Area Network* - WLAN), cabo coaxial, ou qualquer ligação através de fios tipicamente cabo com fios entrançados (*twisted-pair*).

Como o meio de comunicação utilizado no trabalho desenvolvido nesta dissertação é a RF, em seguida apresenta-se uma caracterização deste meio.

O meio de comunicação RF é muito utilizado devido à sua fácil instalação e nomeadamente ao facto de não necessitar de fios. Neste meio existem regras específicas quanto às frequências utilizadas (bandas ISM) e potências de sinal as quais são estipuladas por entidades reguladoras: a *Federal Communication Commission* (FCC) nos Estados Unidos da América (EUA), a *European Telecommunications Standards Institute* (ETSI) na Europa e a *Industry Canada* no Canadá, entre entras.

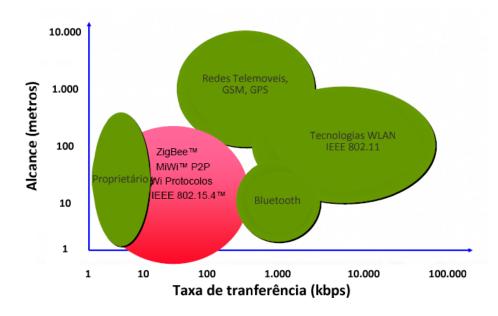

Na Figura 1.2 apresenta-se um gráfico comparativo de várias tecnologias sem fios (wireless). Nele pode-se verificar que existem muitas especificações sem fios, e que podem ter alcances e taxas de transferência bem diferentes. O meio de comunicação RF encontra-se representado na figura através da elipse que contém o IEEE 802.15.4 que é uma norma para a realização de Redes de área pessoal sem fios (Wireless Personal Area Netwoks - WPAN) de baixo ritmo. Essa elipse contém ainda alguns protocolos mais específicos que serão abordados mais á frente.

Figura 1.2 – Protocolos sem fios, adaptado de [Masters, 08]

Estas redes RF podem ter as seguintes topologias:

- em estrela;

- em árvore;

- em malha.

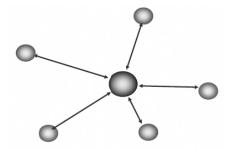

Figura 1.3 - Rede em Estrela [Masters, 08]

Na Figura 1.3 apresenta-se a topologia de rede do tipo estrela. Nesta topologia todos os nós comunicam com o coordenador de rede directamente. A grande desvantagem é que todos os nós da rede têm que estar ao alcance do coordenador, o que em certas soluções não é praticável devido a barreiras arquitectónicas, ou mesmo distâncias longas.

Figura 1.4 - Rede em Árvore [Masters, 08]

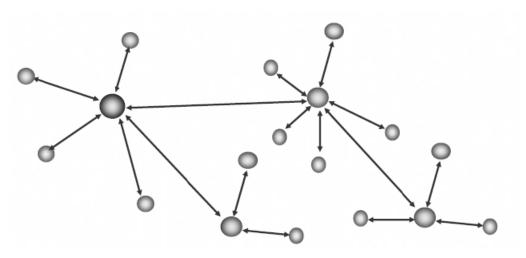

A rede em árvore (*cluster tree*), é apresentada na Figura 1.4. Nesta topologia existem nós com a capacidade de reencaminhar as mensagens de modo a que a mensagem salte de nó em nó até ao seu destino. Esta topologia já requer um maior processamento por parte dos nós que reencaminham, porque necessitam executar o encaminhamento. Nesta topologia já é possível obter qualquer distância, desde que sejam colocados nós capazes de reencaminhar, dentro do alcance dos rádios adjacentes, e o número de saltos (*hops*) não seja superior ao limite do protocolo.

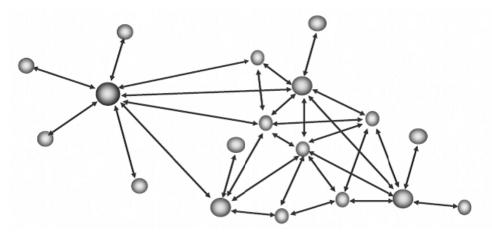

Figura 1.5 - Rede em Malha [Masters, 08]

A rede em malha (*mesh*), é apresentada na Figura 1.5. Nesta topologia todos os nós têm a capacidade de reencaminhar mensagens excepto os de funções reduzidas. No entanto, existem outras concretizações de rede em malha em que todos os nós repetem

as mensagens. Essas redes são designadas de malha dupla (*dual-mesh*) e um exemplo destas é a INSTEON. Assim, quando existe uma mensagem a enviar na rede, esta pode seguir por vários caminhos até chegar ao destino. Esta topologia é a que apresenta uma maior fiabilidade mas também é a que exige mais recursos de *hardware* e *software*. Isto porque todos os nós são capazes de reencaminhar, logo estão constantemente a retransmitir, o que em termos de gestão de baterias pode ser muito prejudicial.

Em seguida apresentam-se algumas das soluções para sistemas domóticos.

#### 1.3.1- Protocolo KNX

É uma norma aberta para o controlo de lares e edifícios. Foi criado em 1999 e é o resultado da fusão entre três normas anteriores, o European Home Systems Protocol (EHS), o BatiBUS, e o European Installation Bus (EIB). Actualmente a entidade que representa a norma é a Konnex Association.

Esta norma é baseada na tecnologia bem sucedida do EIB e alargada com os mecanismos de configuração e os meios físicos do BatiBUS e EHS.

O KNX é dos protocolos que mais meios de comunicação suporta. Estes são:

- Pares entrançados (twisted pair) a 4800 bits/s;

- Pares entrançados (twisted pair) a 9600 bits/s;

- Rede eléctrica a 110 kHz;

- Rede eléctrica a 132 kHz;

- RF a 868 MHz;

- Ethernet.

Alguns destes modos de comunicação são herdados das especificações anteriores e continua-se a dar-lhes suporte para uma maior compatibilidade entre sistemas [Weinzierl, 09] [KNX, 09].

#### 1.3.2- X10

É a norma mais comum nos EUA para residências. Esta é uma norma internacional aberta para a indústria que especifica a comunicação entre dispositivos na casa. O meio de comunicação principal é a rede eléctrica (PLC - *Power Line Communication*), mas pode ainda comunicar por RF (a 310 MHz nos EUA ou a 433 MHZ na Europa) para poder suportar dispositivos sem fios. Os pacotes transmitido tanto por RF como por rede eléctrica são muito semelhantes seguindo o formato X10.

Embora muito utilizada, esta norma tem algumas limitações. As comunicações através da rede eléctrica apresentam falhas quando alguns dispositivos domésticos estão a operar como fornos ou motores. Estes problemas podem ser minimizados com recurso à instalação de repetidores e outros componentes eléctricos. Outro problema conhecido do X10 é as interferências que dois sistemas vizinhos causam um no outro. É um protocolo lento, que apenas suporta 256 endereços para os dispositivos e não seguro. Apesar de continuar a ser muito usado, já é antigo (desenvolvido em 1975).

Uma das grandes vantagens deste protocolo é o facto de estar tão implementado que existem imensos dispositivos disponíveis no mercado com diversas funcionalidades. Como é um protocolo aberto qualquer fabricante pode produzir um dispositivo, desde que seja compatível.

Como exemplo dos dispositivos X10 apresentam as seguintes figuras.

Figura 1.6 – Lâmpada X10, extraído de [EuroX10, 09]

**Figura 1.7** - Módulo X10, extraído de [EuroX10, 09]

Na Figura 1.6 podemos observar uma lâmpada com um módulo X10 integrado no casquilho (LM15ES). Recebe assim os comandos através da rede eléctrica (cada um dos módulos X10 sabe reagir a um certo número de comandos). A Figura 1.7 apresenta um

módulo X10 que controla aparelhos eléctricos ligados a tomadas de parede (AM12G). Recebe comandos X10 para ligar ou desligar o aparelho que lhe está associado.

Já a Figura 1.8 mostra um conversor de sinais X10 RF em comandos X10 para a rede eléctrica, repetindo assim o comando recebido por RF na rede eléctrica (S4022). Apesar desta função, ele próprio é um actuador X10. Quanto à Figura 1.9, esta apresenta um comando universal com ecrã táctil e luz de fundo azul, principalmente vocacionado para o controlo de dispositivos X-10 via RF e infra-vermelhos (IrDA) para os dispositivos normais.

**Figura 1.8** – Conversor X10, extraído de [EuroX10, 09]

**Figura 1.9** – Comando X10, extraído de [EuroX10, 09]

#### **1.3.3- INSTEON**

A tecnologia INSTEON utiliza dois meios de comunicação, a rede eléctrica e a RF. Os engenheiros da *SmartLabs, Inc* analisaram os protocolos já existentes e criaram uma solução mais robusta. Como o X10 é um protocolo amplamente utilizado decidiram suportá-lo pela rede eléctrica e conferir robustez e comodidade aos utilizadores através da comunicação RF. Os dispositivos INSTEON transmitem os comandos pela linha eléctrica e ainda por RF, formando assim uma rede. Ao contrário de outras soluções como Zigbee ou Z-Wave, devido à sua complexidade nos algoritmos de encaminhamento, a rede INSTEON implementa uma rede em malha dupla. Nesta rede todos os nós repetem as mensagens que recebem de modo a obter longos alcances sem ter que distinguir nós que reencaminham de outros de funções reduzidas.

Esta tecnologia, criada em 2001, é das mais robustas e fiáveis, suportando X10 e com todas as vantagens de uma rede em malha por RF [INSTEON, 09].

#### 1.3.4- ZigBee

ZigBee é um protocolo desenvolvido pela *ZigBee Alliance* (composta por cerca de 300 companhias) de muito baixo custo, com baixos consumos para comunicações sem fios. Esta norma tem como objectivo ser utilizada nas áreas da automação de lares e edifícios, controlo industrial, periféricos para PC, aplicações sensoriais médicas, bringuedos, entre outras.

O ZigBee é baseado na norma IEEE 802.15.4 que define as especificações da camada MAC e camada física (PHY) para redes sem fios de área pessoal de baixo ritmo (Low-Rate WPANs).

O ZigBee está estruturado em camadas tal como o bem conhecido modelo OSI (Open Systems Interconnection).

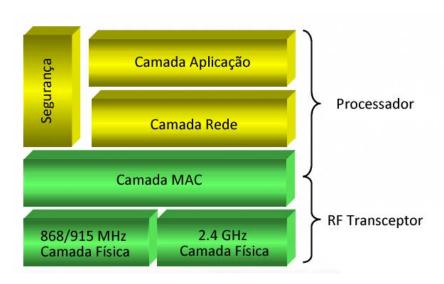

Figura 1.10 – Pilha de camadas ZigBee, adaptado de [Masters 08]

Na Figura 1.10 observam-se as duas camadas mais baixas, a camada MAC e a Física. Estas são descritas pela norma IEEE 802.15.4, e que muitas vezes vêm embutidas nos transceptores (*transceivers*) disponíveis no mercado. A camada de Rede e os mecanismos de encriptação são descritos pelo protocolo ZigBee. Muitos dos fabricantes destes componentes disponibilizam a *Stack* ZigBee elaborada (por exemplo a Mirochip e a Texas Instruments) de forma a simplificar a vida dos engenheiros. Já a

camada de aplicação é elaborada livremente pelos programadores conforme os requisitos do sistema.

Outro aspecto importante é que o ZigBee tem uma grande preocupação quanto à poupança de energia, visto a grande maioria dos seus dispositivos operarem a baterias. Já o Bluetooth é um protocolo que não tem essa preocupação e muito rapidamente gasta a energia de uma bateria (como se sabe pela experiência nos telemóveis).

O ZigBee define três tipos de nós de rede:

- Coordenador ZigBee (ZigBee Coordinator) (FFD)

- Encaminhador ZigBee (ZigBee Router) (FFD)

- Dispositivo Terminal ZigBee (ZigBee End-Device) (RFD)

Estes três tipos de nós podem ser agrupados em duas classes: os dispositivos com todas as funções (*Full Function Device* - FFD) e os dispositivos de funções reduzidas (*Reduced Function Devices* - RFD).

Os FFDs são dotados de todas as funcionalidades, estão sempre activos para receber mensagens e estão habitualmente ligados a uma fonte de energia. Já os RFD passam a maior parte do tempo adormecidos para poupar a energia das baterias. Existe a possibilidade de o seu nó parente (FFD) armazenar mensagens destinadas ao RFD, e quando este acorda requisita as suas mensagens.

Deste modo o Coordenador ZigBee é um FFD mas que actua como coordenador e executa funções muito específicas.

Podem ainda existir mais dois tipos de FFD, os simplesmente FFD e os FFD encaminhadores. A diferença reside nas topologias de rede apresentadas anteriormente. Na rede em árvore (*cluster tree*) os FFDs simples não reenviam mensagens, enquanto que nas redes em malha (*mesh*) todos os FFDs reenviam.

Já os dispositivos terminais ZigBee são sempre os RFD.

Nó parágrafo seguinte faz-se uma distinção do significado, usado até então, da palavra dispositivo. Assim, dispositivo (tradução de *device*) representa algo, quer seja

um sensor ou um actuador, que um nó da rede ZigBee possa ter. Por exemplo um nó que tenha um sensor de temperatura, e actue sobre uma lâmpada. Este nó contém dois dispositivos, embora do ponto de vista do *hardware* seja um objecto único.

Para cada dispositivo ZigBee tem de haver um perfil associado, isto é, se um nó da rede tem a capacidade de actuar sobre uma lâmpada, este nó tem um dispositivo e há forçosamente um perfil para este. Para os outros nós poderem interagir com o dispositivo daquele nó, estes sabem que o nó é de um tipo específico conhecendo assim quais os serviços que esse dispositivo oferece e como o controlar.

Este mecanismo é semelhante ao do USB (*Universal Serial Bus*). Quando introduzimos um dispositivo USB (de agora em diante a palavra dispositivo tem o significado normal) num PC, este tem que ter um perfil de utilização (*driver*) para o saber controlar e que serviços disponibiliza [ZigBee, 06] [IEEE, 06], [MASTERS, 08].

Uma das controvérsias desta tecnologia é sobre a interferência que é causada quando trabalha junto de dispositivos Bluetooth e redes WLANs devido ao facto de todas estas tecnologias operarem na mesma banda dos 2.4GHz. Existem trabalhos que estudam estes efeitos como por exemplo [Shin et al, 07].

Um dos entraves da propagação do ZigBee é os custos que lhe estão associados. Para utilização comercial do ZigBee é necessário ser membro da ZigBee™ Alliance. Para ser membro é preciso pagar US\$ 9.500 ou US\$ 3.500 conforme o estatuto do membro. O licenciamento de cada produto que uma empresa venha a desenvolver tem um custo muito elevado.

Deste modo alguns dos fabricantes de *hardware* decidiram simplificar o ZigBee e criar um protocolo proprietário, sem custos, para os sistemas que não necessitem de tamanha complexidade e robustez como a do ZigBee. Para a utilização destes protocolos proprietários é apenas necessário utilizar o *hardware* por ele fornecido. É o caso do MiWi da Microchip, do EZMac da Integration (que recentemente foi comprada pela Silicon Labs) ou do BeeKit da Freescale.

## 1.3.5- Outras Tecnologias

Existem outras soluções para criar sistemas domóticos. Alguns são protocolos abertos, outros são soluções proprietárias. A título de referência apresentam-se algumas soluções que não serão aprofundadas nesta dissertação.

- LonWorks da Echelon

- Z-Wave da Z-Wave Alliance

- C-Bus ou SquareD Clipsal da Clipsal Integrated Systems

- HomePlug da Powerline Alliance

- EnOcean

- HAI da Home Automation Inc

- ModBus da Modicon

- ONE-NET

- Domintell

- Cardio

- iDom

#### 1.4- Domótica em Portugal

"Hoje a Domótica não é uma novidade em Portugal! E a prová-lo está a existência de várias empresas a operar no ramo, com a representação e distribuição de diversas marcas internacionais, especificamente dedicadas à Domótica" [Chamusca, 06].

Caminha-se "cada vez mais ao encontro dos conceitos fundamentais da domótica. Associado ao conceito do comando e controlo dos diversos níveis de conforto em casa, a palavra Domótica passou a fazer parte do vocabulário do português moderno." [Chamusca, 06].

Alguns construtores portugueses começam já a preparar as habitações para os requisitos das instalações dos sistemas domóticos. "Na actual conjectura do ramo da construção, a Domótica surge como o maior e melhor valor acrescentado das

promoções imobiliárias, sendo as soluções dimensionadas e custeadas mediante o alvo pretendido" [Chamusca, 06]. Alguns empreendimentos novos ou em fase de construção já estão dotados de sistemas domóticos.

As empresas de Domótica indicam uma subida da procura na ordem dos 40%, apesar de estas habitações continuarem a ser uma minoria devido aos preços envolvidos. A construção preparada para a domótica é um factor de diferenciação no preço final. Os preços variam muito conforme as funcionalidades que se querem conferir à casa e às suas dimensões. Em 2007 a rede de pesquisa de Robótica previa para os próximos anos uma Europa com cerca de 15 milhões de casas inteligentes. Actualmente a massificação da inteligência doméstica, e a consequente baixa de preços, ainda é uma miragem, mas há especialistas que afirmam que estas serão a casa comum dentro de uma década.

Por enquanto estes sistemas são mais impulsionados pela segurança e pela poupança energética, uma vez que o conforto é muitas vezes visto como supérfluo na nossa sociedade.

Um factor que vai contribuir bastante para a disseminação destes sistemas em toda a Europa é a Directiva Europeia 2002/91/CE sobre o Desempenho Energético dos edifícios. Esta directiva exige que os edifícios sejam energeticamente eficientes. Todos os edifícios novos vão ter obrigatoriamente um certificado que atesta o nível de poupança de energia. Embora esta directiva seja de 2002, em 2006 apenas quatro países da União Europeia (UE) a seguiam. Prevê-se que ela esteja em fase de implementação na maioria da UE em 2009.

Para que um edifício seja energeticamente eficiente a qualidade da construção é fundamental mas a domótica pode ajudar e por isso prevê-se um aumento significativo da instalação dos sistemas domóticos [SIC, 07] [RTP, 08] [Maldonado, 06].

Em Portugal, no Museu das Comunicações, está desde Maio de 2003, em exposição a Casa do Futuro Inclusiva onde é apresentada uma solução complexa de automação doméstica, que utiliza um elevado conjunto de tecnologias de ponta, num ambiente seguro, lúdico, confortável e moderno.

Actualmente o sistema KNX é o mais utilizado na Europa e consequentemente em Portugal. Este é implementado por mais de uma centena de fabricantes na Europa e na Ásia.

Existem alguns trabalhos de investigação portugueses nesta área. Por exemplo no trabalho em [Gomes, et al, 97] e [Gomes, et al, 98] é apresentada uma metodologia para a modelação de sistemas aplicados em edifícios inteligentes. Já em [Conceição, 04] é proposta uma metodologia e arquitectura para a monitorização e vigilância de edifícios inteligentes.

Em [Nunes, 03] e [Nunes, 04b] surge uma proposta de protocolo de comunicação para edifícios inteligentes o DomoBus. Em [Nunes, 05] é apresentada uma concretização de uma rede extremamente simples e de muito baixo custo, com aplicações na área da automação de edifícios. Este trabalho tem vários aspectos em comum com o desenvolvido e apresentado nesta dissertação. Já em [Nunes, 06] é proposta uma arquitectura descentralizada para a supervisão de sistemas de automação doméstica.

Na investigação têxtil surge uma inovação desenvolvida na Universidade da Beira Interior. Chamado de DomoVest, é um "casaco domótico" com a capacidade de accionar dispositivos domóticos através de um teclado todo elaborado em tecido (ligado através de fios a um transmissor). Este foi apresentado no MOVE 08 – Mostra de trabalhos dos Cursos de Design de Moda.

Existe também um projecto iniciado pela AveiroDomus que se propôs a edificar a casa do futuro. Esta casa chamada InovaDomus que será realizada no Campus da Universidade de Aveiro, pretende repensar todo o conceito de habitat e dotar o espaço com as mais inovadores soluções tecnológicas disponíveis. Esta casa servirá como um laboratório de "tecnologia habitável".

Quanto ao mercado actual da Domótica em Portugal já existem bastantes empresas a operar e inovar.

No mercado de *software* de automação, segurança e entretenimento em casa, destaca-se o desenvolvimento da empresa QuiiQ que apresenta soluções de software capazes de gerir toda a domótica de uma casa, com uma forte componente

Multimédia (baseado no Windows Media Center). Para isso estas soluções suportam alguns protocolos conhecidos, referidos anteriormente [SIC, 08] [EXAME, 08].

Quanto a empresas a instalar sistemas domóticos ou a revender componentes actualmente já existem bastantes. Por exemplo, EuroX10, DOMUS CONNECT, JG Domótica, CentralCasa, DreamDomus, LogicHome, Domática, Hidomus entre muitas outras. Outro exemplo é a Legrand que disponibiliza dispositivos de fácil montagem para uma casa inteligente. A PT Comunicações tem ainda disponíveis pequenos kits (PowerMax e HomeGuard) com funcionalidades tipicamente domóticas como "Telesegurança" ou "Televigilância".

### 2- Sistemas Embutidos em Rede

Embora não directamente relacionadas com a área específica da Domótica as WPAN (Wireless Personal Area Network) e as WSNs são temas que merecem constar nesta dissertação. As metodologias, o hardware, o software, os protocolos e muitas outras questões são partilhadas entre a domótica usando as RF, as WPAN e as WSN.

Estas três temáticas fazem parte da área de investigação ligada às redes de sistemas embutidos (*Networked Embedded Systems* - NES) sem fios. A grande diferença entre estes três domínios é fundamentalmente a área de aplicação. Como se sabe a domótica utiliza as redes sem fios por RF em função de automatismos domésticos.

Já as WPAN são usadas para interligar dispositivos pessoais tais como telemóveis, assistentes pessoais digitais (*Personal Digital Assistant* - PDA), impressoras, máquinas fotográficas, sistemas de posicionamento global (*Global Positioning System* - GPS), comandos de consolas, brinquedos, entre outras aplicações. As WPAN surgiram principalmente com o Bluetooth.

Por sua vez, as WSN têm finalidades bem diferentes como aplicações militares, meteorológicas ou científicas.

Assim sendo, estas três áreas partilham o mesmo domínio científico e tecnológico, embora com fins diferentes. Em seguida apresenta-se uma caracterização sobre alguns temas inerentes à área das redes de sistemas embutidos (NES) sem fios, e em particular às WSNs.

Esta caracterização é muito importante uma vez que o trabalho desenvolvido nesta dissertação envolve muitas destas questões e pode, com muita facilidade, migrar e ser aplicado à área das WSN. Isto porque numa visão muito simplista, e excluindo os elementos multimédia, a domótica pode ser vista como um conjunto de sensores e actuadores que reagem a certos estímulos. Nesta visão, a domótica não será mais do que uma WSN com a capacidade de reagir e actuar (há quem considere que as WSN também podem ter actuadores, e há ainda quem considere que os seus nós não só actuam, como podem ser actores na decisão, sendo designadas de redes sem fios de sensores e actores (Wireless Sensor and Actor Network - WSAN) [Akyildiz – Kasimoglu, 04]). Claro que esta visão da domótica é muito minimalista, relata praticamente os

primeiros sistemas para os edifícios inteligentes e exclui todos os interfaces e mecanismos automatizados/inteligentes que a Domótica actual fornece.

## 2.1- Introdução

As redes de sistemas embutidos surgiram na última década com os rápidos avanços da microelectrónica na área dos microcontroladores que integrados com rádios ou através de ligações por cabo na mesma placa formaram os elementos da rede. Estas redes são tipicamente constituídas por sistemas embutidos que têm que comunicar uns com os outros formando uma rede. Cada sistema é um elemento/nó da rede. Cada elemento deve interagir com os outros elementos, mas ainda com o meio envolvente, através de sensores e/ou actuadores [Gupta et.al, 06].

WSN é o nome genérico no qual um amplo grupo de dispositivos se agrupa. Qualquer dispositivo equipado com um processador, com a capacidade de "sentir" (através de sensores), comunicar sem fios, e ainda com a habilidade de se associar e organizar com outros de modo a formar uma rede pode-se classificar um elemento de uma WSN [Dulman et.al, 06].

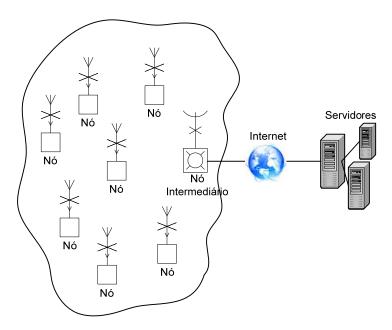

Figura 2.1 – Topologia típica WSN

Na Figura 2.1 mostra-se uma topologia típica das WSN. Nesta topologia diversos nós monitorizam uma certa área (representada pela linha que envolve os nós), e vão

recolhendo informações. Em certa altura do seu funcionamento estes transmitem a informação recolhida que viaja de nó em nó por RF, até ao nó intermediário (*gateway*) que está ligado a outra rede, por exemplo internet, e transfere a informação para um servidor que aloja e processa os dados recolhidos.

Estes nós, também conhecidos como *motes*, são tipicamente de dimensões reduzidas e relativamente baratos. São colocados na zona em que existe algo de interesse que os sensores irão monitorizar. Nas aplicações actuais destas redes os nós são estacionários mas podem perfeitamente ser montados em objectos móveis. O facto de estes serem embutidos, terem a capacidade de monitorizar através de sensores e terem a aptidão de comunicar define esta área de redes de sensores e faz a separação entre outras áreas como monitorização remota, computação móvel através de computadores portáteis, ou mesmo de sistemas de monitorização centralizada.

Estudos nesta área remontam a 1990, mas é por volta de 2004 que se torna economicamente viável a implementação destes sistemas. Desde então esta tem sido uma área com um enorme interesse no campo da investigação, quer académica quer comercial e até militar. Grande parte desta investigação tem-se focado no consumo e gestão dos recursos energéticos, nos processos de aquisição de informação pelos sensores, no modo de actuação, e ainda como gerir estas redes com imensos elementos, que entram e saem da rede a qualquer momento e fornecem serviços diferentes entre eles [Heidemann-Govindan, 05]. Existe ainda a aplicação das WSN mas em tamanhos microscópicos chamados de SmartDust. Estas redes são formadas por sistemas microelectromecânicos (microelectromechanical systems - MEMS) de tamanhos à escala nanométrica provenientes da nanotecnologia.

### 2.2- Hardware

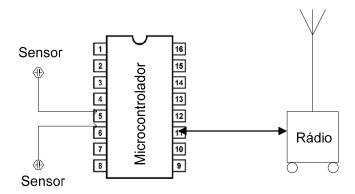

Os elementos (*motes*) têm a necessidade de ter uma unidade central de processamento (Central Processing Unit - CPU) de funções genéricas, memórias e de pinos de entrada e saída para interagir com os sensores e periféricos. Deste modo é

necessário um microcontrolador. Então os *motes* são formados essencialmente por um microcontrolador, sensores e um rádio transceptor, como mostrado na Figura 2.2.

Figura 2.2 – Esquema de um mote

Qualquer microcontrolador que preencha os requisitos pode ser utilizado, como por exemplo os da Microchip, Silicon Labs, Atmel, Texas Instruments, Freescale, entre muitos outros. Na escolha deste microcontrolador é preciso ter como factor decisivo os seus consumos. Estes são microcontroladores de muito baixo custo.

Relativamente aos transceptores há bastante oferta no mercado. Todos os fabricantes de microcontroladores mencionados acima disponibilizam também estes transceptores. Existem ainda soluções que juntam tudo num objecto único, por exemplo os SoC (System-on-Chip) da Ember. Em [Varchola-Drutaroský, 07] e [Körber et.al, 05] é apresentado um quadro comparativo destas soluções.

No trabalho desenvolvido nesta dissertação foram utilizados os microcontroladores PIC24F128GA010 e PIC18F4620 da Microchip, e os transceptores foram os MRF24J40 da Microchip também.

Os sensores acompanharam a evolução tecnológica e a miniaturização dos sistemas. Com a proliferação de sistemas MEMS muitos sensores foram incorporados nas plataformas dos nós (*motes*). Existem no mercado muitos fabricantes que disponibilizam pequenos sensores com a tecnologia MEMS. Muitos destes fabricantes estão segmentados conforme a área de aplicação. Apenas alguns estão centrados na área das WSN, por exemplo a Ember e Millenial Net [Heidemann-Govindan, 05].

#### 2.3- Software

A parte do software tem sido profundamente estudada, pois é nela que se tenta resolver os maiores desafios destes sistemas. Por exemplo, pretende-se modelar um comportamento que não desgaste as baterias, com períodos de adormecimento do hardware bem geridos, que através dum protocolo robusto mantenha uma rede complexa e ainda que tenha a capacidade de interagir com o ambiente envolvente.

A gestão da rede é muito importante porque mantém uma ligação vital entre todos os elementos de modo a permitir a sua colaboração entre eles. Sabe-se que o rádio é dos componentes destes sistemas que mais energia consome, entre 20% a 40%. Deste modo uma boa gestão de rede, através de protocolos optimizados, é de extrema importância no prolongamento da vida de um elemento, e da própria WSN.

A camada MAC está directamente ligada aos consumos energéticos. A colisão de pacotes despende energia ao originar retransmissões. Ter o transceptor activo à escuta de potenciais mensagens, ou estar constantemente a acordar o microcontrolador devido a mensagens que não lhe são destinadas resultam num gasto energético. A norma IEEE 802.11 conhecida como "wi-fi" utiliza CSMA (Carrier-Sense Multiple Acess) que escuta a portadora antes de transmitir de modo a evitar colisões. Outro método para gestão das transmissões é o TDMA (Time-Division Multiple Access) que divide o tempo em vários intervalos (*slots*) em que cada nó transmite no seu intervalo específico, não se sobrepondo a mais nenhuma transmissão. Como as WSN são redes em que a informação a transmitir é de tamanhos reduzidos foi criada uma norma para redes sem fios de baixo ritmo, a IEEE 802.15.4, especificamente para sistemas deste tipo.

Baseada nesta norma surgiram entretanto vários protocolos na camada de rede como o ZigBee e outras variações apresentadas anteriormente na secção 1.3. Estes protocolos especificam como a rede é formada, o formato das mensagens, quando se efectuam transmissões, como reencaminhar mensagens para outros nós, como sincronizar todos os nós, entre muitas outras funcionalidades [Heidemann-Govindan, 05].

De modo a facilitar a interligação das tarefas de rede, de aquisição de informação do meio envolvente e ainda processar tudo isto com recursos tão limitados como os

disponíveis num microcontrolador foram criados Sistemas Operativos dedicados (Operating System - OS), como por exemplo o eCos, o LynxOS e TinyOS. Estes OSs criam um núcleo que gere o encadeamento do processamento, conferindo tempos de execução às tarefas (*threads*) que o sistema tem a fazer. O mais conhecido e implementado na área das redes de sistemas embutidos é o TinyOS que começou como um projecto na Universidade da Califórnia, Berkeley, foi crescendo e actualmente é formado por uma grande comunidade de investigadores e entusiastas da área.

O TinyOS [TinyOS, 09] baseia-se no princípio de que a maior parte das redes de sensores são baseadas em eventos (*event-driven*), ou seja o sistema reage a eventos, por exemplo captados nos seus sensores. É composto por uma estrutura com vários componentes. Cada componente é um módulo de *software* que fornece uma abstracção dos processos internos de cada módulo, seja esse o controlo de um dispositivo de *hardware* ou alguma tarefa de como processar informação. Tipicamente em reposta a um evento captado pelos sensores ou alguma interrupção do *hardware*, são chamadas uma cadeia de componentes/módulos que respondem a esse evento.

Na abstracção implementada pelo TinyOS são fornecidos duas funcionalidades: a tarefa, que fornece a cada módulo tempo de processamento enquanto o processador estaria em espera (*idle*), e o comando, que manda um módulo executar uma função específica (tal como enviar uma mensagem). Através destas abstracções é possível modelar graficamente a aplicação. Ao enfatizar a programação baseada em eventos (*event-driven*) em vez de multi-tarefas (*muti-threading*), permite que os recursos de *hardware* sejam menores. Esta ferramenta permite a reutilização de código, melhora a modularidade do sistema através dos componentes, e minimiza o tamanho do programa que, em dispositivos limitados, é crucial.

A programação para este OS é feita através da linguagem nesC que contém as estruturas necessárias à abstracção do TinyOS: componentes, tarefas, comandos e eventos. O nesC fornece vários mecanismos para optimizar o programa para esta plataforma [Heidemann-Govindan, 05] [Gupta et.al, 06].

Muitos trabalhos estão a ser desenvolvidos com estas ferramentas, em especial na Universidade da Califórnia, Berkeley. Um desses trabalhos é o galsC.

O galsC é a linguagem para o TinyGALS, um modelo globalmente assíncrono localmente síncrono (GALS). O modelo TinyGALS fornece métodos de implementar tarefas concorrentes, chamadas de actores. No nível da aplicação os actores comunicam uns com os outros assincronamente através de mensagens. Dentro de cada actor os componentes comunicam sincronamente através da chamada de métodos. Assim o modelo de programação em termos de fluxo de controlo é globalmente assíncrono e localmente síncrono.

Este modelo tem por base o TinyOS, mas ao contrário do TinyGALS as tarefas concorrentes no TinyOS não são acessíveis como parte do interface de um componente. Falha na gestão explícita da concorrência e obriga os programadores de componentes a utilizarem semáforos na modelação da concorrência [Cheong et al, 03] [Cheong-Liu, 04]. Mais à frente, nesta dissertação, vai-se abordar o conceito GALS com maior detalhe.

Estes sistemas NES têm ainda outras dificuldades que continuam a ser estudadas.

Uma vez que os nós (*motes*) podem não ser colocados nas suas posições finais, como largados de um avião, ou terem mobilidade, é de extrema importância saberem onde se situam. Caso contrário podemos estar a receber informação do meio envolvente, mas se não sabemos qual é esse meio a informação é inútil. Assim actualmente existem algumas abordagens para a resolução desta questão. Uma delas é com o conhecimento da localização de alguns nós específicos, calculando a distância entre esses nós é possível fazer uma triangulação. Essa distância é calculada através da potência do sinal RF que chega ao receptor. Claro que existe alguma incerteza nestes cálculos, até porque a propagação varia conforme os locais e condições meteorológicas. Outras técnicas em estudo aplicam a tecnologia RADAR, ou através da contagem do numero de saltos (*hops*) de uma mensagem.

Outra dificuldade surge quando é necessária a sincronização temporal entre os elementos da rede. Esta funcionalidade pode ser importante quando se pretende fazer uma amostragem colectiva, em que todos os nós devem recolher informação dos seus sensores ao mesmo tempo. Métodos para sincronização baseiam-se num carimbo temporal (*time stamp*) que é colocado em cada mensagem de modo a que o receptor se sincronize. Deste modo toda a rede se vai sincronizando à medida que trocam

mensagens. Mais uma vez surge o problema que o tempo de propagação no ar não é constante, mas também o processamento das mensagens e o tempo de transmissão e recepção podem introduzir atrasos.

À medida que os nós fazem as suas leituras vão gerando informação. Esta informação, quando partilhada com a dos outros nós, permite prever algumas situações. A questão então é onde guardar tanta informação gerada. Existem soluções como o TinyDB ou o The Cougar Sensor Database que permitem armazenar informação de uma forma reduzida.

Outro desafio a estes sistemas é como fazer uma programação remota. Esta reprogramação pode ser efectuada através de parâmetros que ao serem alterados fazem com que o funcionamento normal mude para outro previamente implementado, o que pode acontecer quando se anteciparam certas necessidades. Outros métodos baseiam-se na alteração total ou parcial do programa que o nó tem.

Em relação à segurança nas WSN esta ainda não é muito forte. São alvos fáceis de ataques de negação de serviço (*denial of service*). Existem mecanismos de encriptação e autenticação que são utilizados para a confidencialidade das mensagens. Esta encriptação pode exigir mais processamento o que resultará num maior consumo energético. Conforme as aplicações, a segurança pode ser ou não necessária [Heidemann-Govindan, 05] [Gupta et.al, 06] [Dulman et.al, 06].

## 2.4- Aplicações

Como já vem sido referenciado ao longo desta dissertação as WSNs têm bastantes aplicações. Em seguida apresentam-se algumas delas.

# Aplicações Militares

As aplicações militares têm sido um dos catalisadores das WSN. Muito do desenvolvimento WSNs deve-se a esta área de aplicação onde podem ser utilizadas