## **SERVICE MANUAL 6700A**

## **APPLICATION LOGIC PROGRAMMING**

# **GENISYS 2000**

## **NON-VITAL LOGIC EMULATOR**

| I       | INTRODUCTION                       | 1-1  |

|---------|------------------------------------|------|

| 1.1     | FAMILY OF MANUALS                  | 1-1  |

| 1.2     | APPLICATION AND EXECUTIVE SOFTWARE | 1-1  |

| 1.3     | COMPONENTS                         | 1-2  |

| 1.3.1   | Cardfile                           | 1-2  |

| 1.3.2   | Controller PBC                     | 1-2  |

| 1.3.3   | Relay-Output PCBs                  | 1-2  |

| 1.3.4   | Optical Input PCBs                 | 1-3  |

| 1.3.5   | Power Supply Converter PCBs        | 1-4  |

| 1.4     | PROGRAMMING SPECIFICATIONS         | 1-4  |

| П       | COMPONENT DESCRIPTIONS             | 2-1  |

| 2.1     | INTRODUCTION                       | 2-1  |

| 2.1.1   | Programming Language Terms         | 2-1  |

| 2.1.2   | Reserved Words                     | 2-2  |

| 2.1.3   | User-Defined Symbols               | 2-3  |

| 2.1.4   | Delimiters                         | 2-3  |

| 2.1.5   | Formats                            | 2-3  |

| 2.1.6   | Non-Program Comments               | 2-3  |

| 2.1.7   | Compiler Switches                  | 2-4  |

| 2.2     | PROGRAM EXAMPLES                   | 2-5  |

| 2.2.1   | Local Input/Output                 | 2-5  |

| 2.2.2   | Internal Relays and Stick Logic    | 2-6  |

| 2.2.3   | Timing Relays                      | 2-7  |

| 2.2.4   | Master/Slave Communications        | 2-8  |

| 2.3     | DETAILED STATEMENT DESCRIPTIONS    | 2-9  |

| 2.3.1   | Program Statement                  | 2-9  |

| 2.3.2   | Interface                          | 2-9  |

| 2.3.3   | Local Section                      | 2-9  |

| 2.3.4   | Master                             | 2-10 |

| 2.3.4.1 | ADDRESS Declaration                | 2-11 |

| 2.3.4.2 | OUTPUT Declaration                 | 2-12 |

## **TABLE OF CONTENTS**

| 2.3.4.3   | INPUT Declaration.                         | 2-12 |

|-----------|--------------------------------------------|------|

| 2.3.5     | SERIAL.SLAVE                               | 2-12 |

| 2.3.5.1   | ADDRESS Declaration                        | 2-13 |

| 2.3.5.2   | FLAG Declaration                           | 2-13 |

| 2.3.5.2.1 | DATATRAIN VIII Specific                    | 2-14 |

| 2.3.5.2.2 | ALLEN BRADLEY DF1 Specific                 | 2-14 |

| 2.3.5.3   | OUTPUT Declaration.                        | 2-14 |

| 2.3.5.4   | INPUT Declaration.                         | 2-14 |

| 2.3.6     | ATCS.SLAVE or ARES.SLAVE                   | 2-14 |

| 2.3.6.1   | FLAG Declaration                           | 2-15 |

| 2.3.6.2   | ADDRESS Declaration                        | 2-16 |

| 2.3.6.3   | WIU.ADDRESS Declaration.                   | 2-16 |

| 2.3.6.4   | OUTPUT Declaration.                        | 2-16 |

| 2.3.6.5   | INPUT Declaration.                         | 2-16 |

| 2.3.7     | DC.CODE.LINE                               | 2-17 |

| 2.3.7.1   | FLAG Declaration                           | 2-19 |

| 2.3.7.2   | ADDRESS Declaration                        | 2-19 |

| 2.3.7.3   | INDICATION Declaration                     | 2-19 |

| 2.3.7.4   | Indication LENGTH Declaration              | 2-19 |

| 2.3.7.5   | Indication ADDRESS Declaration.            | 2-19 |

| 2.3.7.6   | OUTPUT Declaration.                        | 2-19 |

| 2.3.7.7   | CONTROL Declaration.                       | 2-20 |

| 2.3.7.8   | Control LENGTH Declaration.                | 2-20 |

| 2.3.7.9   | Control ADDRESS Declaration.               | 2-20 |

| 2.3.7.10  | INPUT Declaration.                         | 2-20 |

| 2.4       | CONFIGURATION ITEMS FOR PROGRAM PARAMETERS | 2-20 |

| 2.4.1     | VAR                                        | 2-44 |

| 2.4.2     | TIMER                                      | 2-44 |

| 2.4.3     | Main Program Body                          | 2-45 |

| 2.4.4     | ASSIGN Statement                           | 2-45 |

| 2.4.5     | Run Time System Description                | 2-46 |

| 2.4.6     | Logic Processing                           | 2-47 |

ii SM 6700A 8/96

| 2.4.7   | Remote Communications- Predefined Relays        | 2-48 |

|---------|-------------------------------------------------|------|

| 2.4.8   | Valid Bit Option                                | 2-49 |

| 2.5     | VALIDATION OPTION                               | 2-49 |

| 2.5.1   | Parameters                                      | 2-49 |

| 2.5.2   | Recommendations                                 | 2-50 |

| 2.6     | LOGIC QUEUING AND EXECUTION                     | 2-50 |

| 2.6.1   | Comparison of Hardware and Software Relay Logic | 2-50 |

| 2.6.2   | Breaks Before Makes Rule                        | 2-50 |

| 2.6.3   | Queuing Options                                 | 2-51 |

| 2.6.4   | Relay Models and Programming Techniques         | 2-52 |

| 2.7     | GENISYS 2000 DEVELOPMENT SYSTEM (G.D.S.2.)      | 2-53 |

| 2.8     | G.D.S.2 AVAILABLE FILE                          | 2-54 |

| 2.9     | G.D.S.2 COMPILER.                               | 2-54 |

| 2.10    | G.D.S.2 SIMULATOR                               | 2-55 |

| 2.10.1  | Access to Simulator                             | 2-56 |

| 2.10.2  | Procedure                                       | 2-56 |

| 2.10.3  | Standard Formats                                | 2-57 |

| 2.10.4  | Simulator Operation                             | 2-57 |

| 2.10.5  | Sample Program                                  | 2-58 |

| 2.10.6  | Help Screen                                     | 2-60 |

| 2.10.7  | Display IO Command                              | 2-61 |

| 2.10.8  | Display Triggers Command                        | 2-61 |

| 2.10.9  | Display Relays Command                          | 2-62 |

| 2.10.10 | Remove Command                                  | 2-63 |

| 2.10.11 | Input Command                                   | 2-64 |

| 2.11    | RELAY SET AND CLEAR COMMANDS                    | 2-65 |

| 2.11.1  | Non-Timer Relays                                | 2-65 |

| 2.11.2  | Timer Relays                                    | 2-65 |

| 2.11.3  | Increment Command                               | 2-68 |

| 2.11.4  | Display Timers Command                          | 2-69 |

| 2.11.5  | Execute Command                                 | 2-69 |

| 2.11.6  | Trace Command                                   | 2-70 |

| 2.11.7  | Run Command                                     | 2-71 |

| 2.11.8  | Value Command                                   | 2-73 |

| 2.11.9  | Read Command                                    | 2-74 |

## TABLE OF CONTENTS

| 2.11.10                                                                                                                  | Print Command                                                                                                                                                                                                                                                                                                                                             | 2-74                                                               |

|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| 2.11.11                                                                                                                  | Reset and Quit Commands                                                                                                                                                                                                                                                                                                                                   | 2-76                                                               |

| 2.11.12                                                                                                                  | Color CRT Commands                                                                                                                                                                                                                                                                                                                                        | 2-76                                                               |

|                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                           |                                                                    |

| III                                                                                                                      | PROGRAMMING PROCEDURES                                                                                                                                                                                                                                                                                                                                    | 3-1                                                                |

| 3.1                                                                                                                      | LOGIC AND TIMING OVERFLOWS                                                                                                                                                                                                                                                                                                                                | 3-1                                                                |

| 3.1.1                                                                                                                    | Timing Elements                                                                                                                                                                                                                                                                                                                                           | 3-1                                                                |

| 3.1.2                                                                                                                    | General Processing                                                                                                                                                                                                                                                                                                                                        | 3-1                                                                |

| IV                                                                                                                       | MISCELLANEOUS PROGRAM DESIGN                                                                                                                                                                                                                                                                                                                              | 4-1                                                                |

| 4.1                                                                                                                      | LOCAL INPUT/OUTPUT(I/O) CONSIDERATION                                                                                                                                                                                                                                                                                                                     | 4-1                                                                |

| 4.1.1                                                                                                                    | Using Slave Units as I/O Processors                                                                                                                                                                                                                                                                                                                       | 4-1                                                                |

| 4.1.2                                                                                                                    | Determining the Control Delivery Time                                                                                                                                                                                                                                                                                                                     | 4-1                                                                |

| 4.1.3                                                                                                                    | Selection Considerations                                                                                                                                                                                                                                                                                                                                  | 4-1                                                                |

| 4.1.4                                                                                                                    | Serial Communications Timing Considerations                                                                                                                                                                                                                                                                                                               | 4-1                                                                |

|                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                           |                                                                    |

| V                                                                                                                        | MISCELLANEOUS APPLICATION INFORMATION                                                                                                                                                                                                                                                                                                                     |                                                                    |

| <b>V</b> 5.1                                                                                                             | MISCELLANEOUS APPLICATION INFORMATION  GENISYS SERIAL COMMUNICATION PROTOCOL                                                                                                                                                                                                                                                                              | 5-1                                                                |

|                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                           |                                                                    |

| 5.1                                                                                                                      | GENISYS SERIAL COMMUNICATION PROTOCOL                                                                                                                                                                                                                                                                                                                     | 5-1                                                                |

| 5.1<br>5.1.1                                                                                                             | GENISYS SERIAL COMMUNICATION PROTOCOL  General Message Format                                                                                                                                                                                                                                                                                             | 5-1<br>5-1                                                         |

| 5.1<br>5.1.1<br>5.1.1.1                                                                                                  | GENISYS SERIAL COMMUNICATION PROTOCOL  General Message Format  Control Character                                                                                                                                                                                                                                                                          | 5-1<br>5-1<br>5-1                                                  |

| 5.1<br>5.1.1<br>5.1.1.1<br>5.1.1.2                                                                                       | GENISYS SERIAL COMMUNICATION PROTOCOL  General Message Format  Control Character  Station Address                                                                                                                                                                                                                                                         | 5-1<br>5-1<br>5-1                                                  |

| 5.1<br>5.1.1<br>5.1.1.1<br>5.1.1.2<br>5.1.1.3                                                                            | GENISYS SERIAL COMMUNICATION PROTOCOL  General Message Format  Control Character  Station Address  Data Bytes                                                                                                                                                                                                                                             | 5-1<br>5-1<br>5-1<br>5-2                                           |

| 5.1<br>5.1.1<br>5.1.1.1<br>5.1.1.2<br>5.1.1.3<br>5.1.1.4                                                                 | GENISYS SERIAL COMMUNICATION PROTOCOL  General Message Format  Control Character  Station Address  Data Bytes  Security Checksum                                                                                                                                                                                                                          | 5-1<br>5-1<br>5-1<br>5-2                                           |

| 5.1<br>5.1.1<br>5.1.1.1<br>5.1.1.2<br>5.1.1.3<br>5.1.1.4<br>5.1.2                                                        | GENISYS SERIAL COMMUNICATION PROTOCOL  General Message Format  Control Character  Station Address  Data Bytes  Security Checksum  Basic GENISYS PROTOCOL MASTER to SLAVE MESSAGES                                                                                                                                                                         | 5-1<br>5-1<br>5-1<br>5-2<br>5-2                                    |

| 5.1<br>5.1.1<br>5.1.1.1<br>5.1.1.2<br>5.1.1.3<br>5.1.1.4<br>5.1.2<br>5.1.2.1                                             | GENISYS SERIAL COMMUNICATION PROTOCOL  General Message Format  Control Character  Station Address  Data Bytes  Security Checksum  Basic GENISYS PROTOCOL MASTER to SLAVE MESSAGES  Common Control Message (\$F9)                                                                                                                                          | 5-1<br>5-1<br>5-1<br>5-1<br>5-2<br>5-2<br>5-2                      |

| 5.1<br>5.1.1<br>5.1.1.1<br>5.1.1.2<br>5.1.1.3<br>5.1.1.4<br>5.1.2<br>5.1.2.1<br>5.1.2.2                                  | GENISYS SERIAL COMMUNICATION PROTOCOL  General Message Format  Control Character  Station Address  Data Bytes  Security Checksum  Basic GENISYS PROTOCOL MASTER to SLAVE MESSAGES  Common Control Message (\$F9)  Acknowledge and Poll Message (\$FA)                                                                                                     | 5-1<br>5-1<br>5-1<br>5-1<br>5-2<br>5-2<br>5-2<br>5-2<br>5-2        |

| 5.1<br>5.1.1<br>5.1.1.1<br>5.1.1.2<br>5.1.1.3<br>5.1.1.4<br>5.1.2<br>5.1.2.1<br>5.1.2.2<br>5.1.2.3                       | GENISYS SERIAL COMMUNICATION PROTOCOL  General Message Format  Control Character  Station Address  Data Bytes  Security Checksum  Basic GENISYS PROTOCOL MASTER to SLAVE MESSAGES  Common Control Message (\$F9)  Acknowledge and Poll Message (\$FA)  Poll Message (\$FB)                                                                                | 5-1<br>5-1<br>5-1<br>5-1<br>5-2<br>5-2<br>5-2<br>5-2<br>5-2        |

| 5.1<br>5.1.1<br>5.1.1.1<br>5.1.1.2<br>5.1.1.3<br>5.1.1.4<br>5.1.2<br>5.1.2.1<br>5.1.2.2<br>5.1.2.3<br>5.1.2.4            | GENISYS SERIAL COMMUNICATION PROTOCOL  General Message Format  Control Character  Station Address  Data Bytes  Security Checksum  Basic GENISYS PROTOCOL MASTER to SLAVE MESSAGES  Common Control Message (\$F9)  Acknowledge and Poll Message (\$FA)  Poll Message (\$FB)  Control Data Message (\$FC)                                                   | 5-1<br>5-1<br>5-1<br>5-1<br>5-2<br>5-2<br>5-2<br>5-2<br>5-2<br>5-3 |

| 5.1<br>5.1.1<br>5.1.1.1<br>5.1.1.2<br>5.1.1.3<br>5.1.1.4<br>5.1.2<br>5.1.2.1<br>5.1.2.2<br>5.1.2.3<br>5.1.2.4<br>5.1.2.5 | GENISYS SERIAL COMMUNICATION PROTOCOL  General Message Format  Control Character  Station Address  Data Bytes  Security Checksum  Basic GENISYS PROTOCOL MASTER to SLAVE MESSAGES  Common Control Message (\$F9)  Acknowledge and Poll Message (\$FA)  Poll Message (\$FB)  Control Data Message (\$FC)  Indication Recall (Master Recall) Message (\$FD) | 5-1 5-1 5-1 5-1 5-2 5-2 5-2 5-2 5-2 5-2 5-2 5-3                    |

iv SM 6700A 8/96

| 5.1.3.1 | Acknowledge Message (\$F1)                            | 5-3  |

|---------|-------------------------------------------------------|------|

| 5.1.3.2 | Indication Data Message (\$F2)                        | 5-3  |

| 5.1.3.3 | Control Checkback Message (\$F3)                      | 5-3  |

| 5.1.4   | GENISYS Master Protocol Drivers Operation             | 5-3  |

| 5.1.5   | GENISYS Slave Protocol Driver Operation               | 5-4  |

| 5.1.6   | GENISYS Configuration Control Bytes                   | 5-4  |

| 5.1.7   | Detailed Message Formats for Master to Slave Messages | 5-5  |

| 5.1.7.1 | Common Control Message                                | 5-5  |

| 5.1.7.2 | Acknowledge and Poll Message                          | 5-5  |

| 5.1.7.3 | Poll Message                                          | 5-5  |

| 5.1.7.4 | Control Message                                       | 5-6  |

| 5.1.7.5 | Recall Message                                        | 5-6  |

| 5.1.7.6 | Control Execute Message                               | 5-6  |

| 5.1.8   | Detailed Message Formats for Slave to Master Messages | 5-6  |

| 5.1.8.1 | Acknowledge Message                                   | 5-6  |

| 5.1.8.2 | Indication Data Message                               | 5-7  |

| 5.1.8.3 | Control Data Checkback Message                        | 5-7  |

| 5.1.9   | Control Character Summary                             | 5-7  |

| VI      | SUPPLEMENTAL DATA                                     | 6-1  |

| 6.1     | TOKEN AND PARSING ERROR/WARNING MESSAGES              | 6-1  |

| 6.2     | SEMANTIC ERROR MESSAGES                               | 6-2  |

| 6.3     | CODE SYSTEM PRE-PROGRAMMED EPROMS                     | 6-10 |

| 6.4     | GENERAL EPROM PROGRAMMING INSTRUCTIONS                | 6-10 |

| 6.4.1   | GENISYS 2000 EPROM File Format Information            | 6-10 |

|         | Appendix A PARTS LIST                                 |      |

| Δ 1     | Development System Equipment                          | Δ_1  |

SM 6700A 8/96

## **List Of Illustrations**

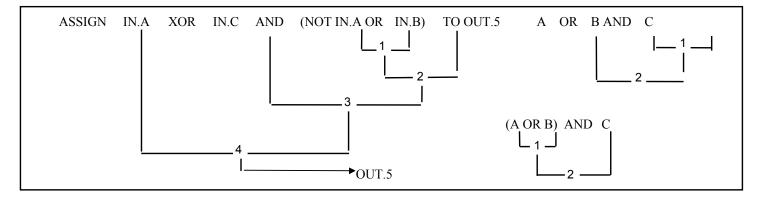

| Figure 2-1     | ASSIGN Operators and Order of Precedence Samples     | 2-46 |

|----------------|------------------------------------------------------|------|

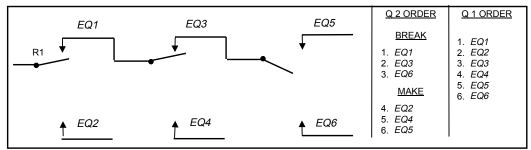

| Figure 2-2     | Queuing Options Reference Diagram                    | 2-47 |

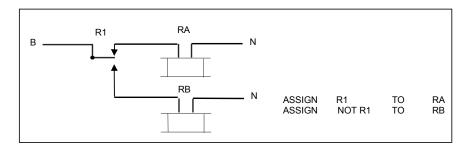

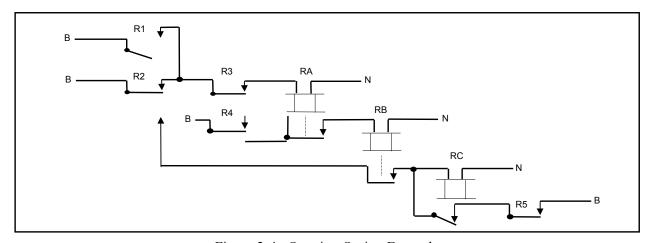

| Figure 2-3     | Example of Front and Back Contract Assignments       | 2-50 |

| Figure 2-4     | Queuing Option Example                               | 2-51 |

| Figure 2-5     | Conceptual Relay Models for GENISYS 2000 Programming | 2-52 |

| Figure 2-6     | Development System Block Diagram                     | 2-53 |

| Figure 2-7     | Initial NBR3 Trigger Screen                          | 2-62 |

|                |                                                      |      |

|                | <u>List Of Tables</u>                                |      |

| Table 2-1 Cha  | racter Set                                           | 2-1  |

| Table 2-2 GE   | NISYS 200 Reserved Words                             | 2-2  |

| Table 2-3 Del  | imiters                                              | 2-3  |

| Table 2-4 Log  | cical Operators Symbols                              | 2-45 |

| Table 2-5 ASS  | SIGN Operators Truth Tables                          | 2-46 |

| Table 2-6 Trig | gger List Development Table                          | 2-47 |

vi SM 6700A 8/96

This manual provides instructions for programming the non-vital application software of the GENISYS® 2000 Non-vital Logic Emulator (NVLE).

#### 1.1 FAMILY OF MANUALS

This manual is one of two manuals that cover the GENISYS 2000.

- (SM 6700A) Non-Vital Logic Emulator Application Logic Programming

- **(SM 6700B)** Installation and Field Maintenance Hardware Installation, Local and Serial Data Interfacing, Field Troubleshooting

The GENISYS 2000 Non-vital Logic Emulator (NVLE) is a general-purpose logic emulator and communication unit that performs the functions of various non-vital relay logic and digital logic systems, according to a custom designed software program. This program uses a Boolean high-level language, that takes inputs, performs logic and timing functions on those inputs and produces outputs. The program is conceptually similar to a system of interconnected relays. Typical applications include processing of central office controls and local indications at a centralized traffic control (CTC) system field station, and processing of local indications for a local wayside control panel.

The basic hardware elements of GENISYS 2000 include a single microprocessor-based controller Printed Circuit Board (PCB), a power supply converter PCB and a configuration of input and output PCBs determined by application. Five optional output PCBs are equipped with either 16 single-pole relay outputs or 32 optically isolated solid-state outputs for various relay or control panel lamp driving applications or both. Two optional input PCBs are equipped with 16 or 32 optical-isolator ICs for interfacing of contact-generated input signals. Power supply converter options are tailored for dc voltages from 9.5 to 35 Vdc and standard 120 Vac commercial power.

GENISYS 2000 may be interfaced directly or via many digital communication systems commonly used in remote service. A Master/Slave protocol is used for communications between a computer and GENISYS 2000 unit(s) or between two or more GENISYS 2000 units. Configurations may include stand-alone units with no serial communications links and Master/Slave systems with serial communications links. Master/Slave systems may incorporate one or more Slave GENISYS 2000 units.

Communications electrical interface options include EIA RS-423 (RS-232C compatible) or RS-422 compatible. Modems are required when more than one Slave unit is connected to a Master unit, or when direct-interface communications limits are exceeded. Each GENISYS 2000 unit may control up to 512 inputs and outputs in any combination. Up to 64 Slave units may be controlled by a Master unit, but the typical practical limit is 40 to 50 units.

#### 1.2 APPLICATION AND EXECUTIVE SOFTWARE

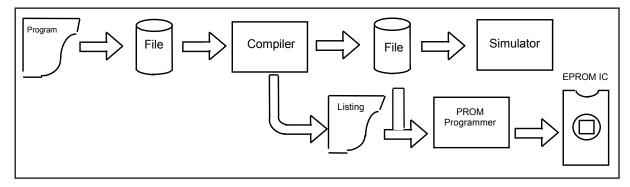

The GENISYS 2000 system incorporates independent Application and Executive Software. These are contained in separate EPROM chips on the Controller board. The Application software or logic is developed for the specific installation, either by US&S or the customer. The source program is written and compiled on a computer, using a language that enables the system logic to be expressed in terms familiar to the railway signal engineer. The finished program is converted into a form that can be entered or "burned" onto two (2) EPROM chips.

SM 6700A 8/96

The GENISYS 2000 may be programmed by using the GENISYS 2000 Development System (G.D.S.2.). This system enables the user to design and test their own program, and then load it into the system hardware. The G.D.S.2. consists of a personal computer, an EPROM Programmer and the GENISYS 2000 Development System software, which is contained on a single diskette. Presently there are five Executive Software sets. These allow the GENISYS 2000 to interface with different slave protocols. (ATCS, ARES, GENISYS/5XX Field Codes, MCS, and WB&S S2).

#### 1.3 COMPONENTS

#### 1.3.1 Cardfile

The GENISYS 2000 Non-vital Logic Emulator is housed in a standard 19-inch rack-mount cardfile. The cardfile always contains a power supply converter PCB in the far left-hand slot, a controller PCB in the second slot and between zero and 16 input and output PCBs in the remaining slots. When output PCBs are present, they must be grouped in the leftmost input/output card slots. All input PCBs must be in card slots to the right of all output PCBs. Empty slots between the last output PCB and the first input PCB must be identified in the application program as spare card slots. Because of these limitations, a GENISYS 2000 cardfile may contain a mix of 16 and 32 bit input and output cards. If required by a specific application, a cardfile may contain all input or all output PCBs in the far right-hand 16 card slots.

#### 1.3.2 Controller PCB

The Controller PCB performs all logical decisions and calculations for the GENISYS 2000 system, and serves as the remote communications interface for any external devices. Primary functions include management of local I/O (via cardfile interface boards) and remote I/O (via serial data line) as defined by the custom-designed application program. The basic integrity of the controller is continuously verified by the execution of internal watchdog and testing routines.

1-2 SM 6700A 8/96

## 1.3.3 Relay-Output PCBs

US&S provides five different relay-output PCBs which may be used in the GENISYS 2000 cardfile.

| PCB Name                       | Part Number  | Characteristics                                                                                                                                      |

|--------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16 Bit Control Delivery        | N451441-3601 | Variable duration pulse delivery (using relay outputs)                                                                                               |

| 16 Bit Constant Delivery       | N451441-7101 | Continuous delivery (using relay outputs                                                                                                             |

| 16 Bit Control and Delivery    | N451441-4701 | Variable duration pulse<br>delivery duration pulse<br>delivery for use with external<br>polar magnetic-stick storage<br>relays (using relay outputs) |

| 32 Bit Output Control          | N451441-9601 | Fixed duration pulse or constant delivery (using current sinking solid-state drivers)                                                                |

| 32 Bit Output Control (Source) | N451441-9801 | Fixed duration pulse or constant delivery (using solid-state current source drivers)                                                                 |

Solid-state output boards with current sinking drivers switch the negative side of the load, while current source drivers switch the positive side of the load. Output board selection is based on the requirements of the application.

## 1.3.4 Optical Input PCBs

US&S provides two different optical input PCBs which may be used in the GENISYS 2000 cardfile.

| 16 Bit Optical Input | N451441-7202 | Wide input voltage range (AC or DC) |

|----------------------|--------------|-------------------------------------|

| 32 Bit Input         | N451441-9701 | Wide input voltage range (DC only)  |

Older N451441-5802 optical input boards may also be used.

SM 6700A 8/96

## 1.3.5 Power Supply Converter PCBs

US&S provides two power supply converter PCBs for GENISYS 2000 which output operating power for other cardfile PCBs, and the carrier modem interface (+/- 12 Vdc) when required by application. They are as follows:

Part Number

Input Voltage

N451441-7601

9.5 to 35 Vdc

N451441-4601

120 Vac (nom.)

#### 1.4 PROGRAMMING SPECIFICATIONS

Total Bits: 4000 bits maximum (can be divided between local I/O, serial I/O and internal)

Local I/O Boards: 16 maximum per cardfile (any combination)

Local I/O Bits: 512 using 32-bit input and output PCBs

Master-to-Slave

Communications: 64 Slave units maximum, communication from Master unit

Slave-to-Master

Communications: 1 Master unit maximum, communication from Slave unit

Serial Addresses: 1 to 255 inclusive

Master Baud: 300, 600, 1200, 2400, 4800, 9600, 19200

Slave Baud: 75\*, 300, 600, 1200, 2400, 4800, 9600, 19200

\*MCS (only)

**Active Timing**

Elements: 300 maximum active at any one time in application logic

Logic Equations

Triggered: 4000 maximum

1-4 SM 6700A 8/96

## 2.1 INTRODUCTION

In the non-vital application program, various bits (input, output, internal etc.) and logic procedures are defined in a text data file on a computer. Logical bits are defined in input, output and internal declaration statements and associated with physical inputs and outputs by position. Bits can represent local parallel I/O directly connected to the unit or remote I/O which passes to devices through either the Master or Slave Serial ports. Timing values for either defining set (pick-up) or clear (drop-away) or both delays can be associated with internal or output bits. Boolean statements describe the logical relationships between bits which comprise the system logic.

The complete program, including bit definition and Boolean logic statements is referred to as the source program. The source program is processed by the compiler and converted into data tables which can be read and executed by the Executive Software on the GENISYS 2000 controller board. These data tables are programmed into two EPROMs which are installed on the controller board. The following sections describe how these basic programming operations are accomplished using the GENISYS 2000 Development System.

## 2.1.1 Programming Language Terms

The Character Set consists of the full ASCII character set, as defined for the user's computer. These are listed below in Table 2-1. Only certain characters may be used to make up user-defined symbols (refer to User-Defined Symbols, on the following page). Although all letters are acceptable, all lower case letters (a-z) are converted to upper case (A-Z) by the system. For example, "Stick" is read the same as "STICK". Lower case is only used for readability.

| FOR USER-DEFINED<br>SYMBOLS | SPECIAL CHARACTERS | SPECIAL CHARACTERS |

|-----------------------------|--------------------|--------------------|

| Upper Letters (A-Z)         | Colon:             | Backslash \        |

| Lower Letters (a-z)         | Semicolon;         | Percent Sign %     |

| Numerals (0-9)              | Comma,             | At Sign @          |

| Period .                    | Equal Sign =       | Plus Sign +        |

| Dollar Sign \$              | Open Parens. (     | Asterisk *         |

| Underscore                  | Closed Parens. )   | Tilde ~            |

|                             |                    | Double Quotes "    |

Table 2-1. Character Set

## 2.1.2 Reserved Words

A Reserved Word has a predetermined meaning to the compiler. The 114 Reserved Words are listed in Table 2-2.

| ADDRESS          | DC.CODE.LINE     | MASTER.CARRIER   | SERIAL2.STOP     |

|------------------|------------------|------------------|------------------|

| AND              | DC.CUTOUT.TIMER  | MASTER.CHECKBACK | SERIAL.BAUD      |

| ARES.FAIL.TIMER  | DC.FAIL.TIMER    | MASTER.COMMON    | SERIAL.BYTE.DLY  |

| ARES.FLAG        | DC.FLAG          | MASTER.KEYOFF    | SERIAL.CARRIER   |

| ARES.GNDLNK      | DIAG.CARRIER     | MASTER.KEYON     | SERIAL.DCD.DELAY |

| ARES.GROUND      | DIAG.FAIL.TIMER  | MASTER.PARITY    | SERIAL.FLAG      |

| ARES.HEALTH      | DIAG.KEYOFF      | MASTER.PEER.ADDR | SERIAL.KEYOFF    |

| ARES.KEYOFF      | DIAG.KEYON       | MASTER.SECURITY  | SERIAL.KEYON     |

| ARES.KEYON       | DIAG.PASSWORD    | MASTER.STOP      | SERIAL.PARITY    |

| ARES.LINK        | DIAG.PORT.ADDR   | MASTER.TIMEOUT   | SERIAL.SLAVE     |

| ARES.SLAVE       | DIAG.PORT.BAUD   | MIN              | SERIAL.STOP      |

| ARES.TIME        | DT8.PEER.ADDRESS | MSEC             | SERIAL.XMT.LIMIT |

| ASSIGN           | DT8.SLV.ADDRESS  | NOT              | SERIAL2,KEY0FF   |

| ATCS.FAIL.TIMER  | END              | OR               | SERIAL2.BYTE.DLY |

| ATCS.FLAG        | FRAME.LENGTH     | OUTPUT           | SERIAL2.CARRIER  |

| ATCS.GNDLNK      | GENISYS.2000     | PEERMODE.BT.ITVL | SET              |

| ATCS.GROUND      | IND.ACK.TIMEOUT  | PEERMODE.TIMEOUT | SLAVE.PORT.BAUD  |

| ATCS.HEALTH      | IND.BRDCST.ITVL  | PROGRAM          | SPARE            |

| ATCS.LINK        | IND.CHANGE.DELAY | QUEUE.OPTION     | TIMER            |

| ATCS.MCP         | IND.OFFSET       | RF.RETRIES       | TO               |

| ATCS.MCPLNK      | INDICATION       | SEC              | VALIDATION       |

| ATCS.SLAVE       | INPUT            | SER.FAIL.TIMER   | VAR              |

| BEGIN            | INTERFACE        | SER2.DCD.DELAY   | WIU.ADDRESS      |

| CLEAR            | ITEM             | SER2.FAIL.TIMER  | WORD             |

| CONFIGURATION    | LENGTH           | SER2.FRME.LENGTH | WORD16           |

| CONTROL          | LOCAL            | SER2.XMT.LIMIT   | WORD32           |

| CONTROL.DELIVERY | LOGIC.VERSION    | SERIAL2,KEYON    | XOR              |

| CTL.OFFSET       | MASTER           | SERIAL2.BAUD     |                  |

| DC.AUTO.RECALL   | MASTER.BAUD      | SERIAL2.PARITY   |                  |

Table 2-2. GENISYS 2000 Reserved Words

2-2 SM 6700A 8/96

## 2.1.3 User-Defined Symbols

User-defined symbols are used to create relay names in the source program. These symbols must contain characters from the first part of Table 2-1, and cannot consist of all numbers. A maximum of 16 characters may be used to create symbol names. Examples of legal symbols in G.D.S.2. Versions 1.01 and higher include:

relay.123 DOG .INPUT RELAY ITK IN.TRK.IN OUT.16

Illegal examples of the above symbols in G.D.S.2. include:

.INPUT.RELAY.4567 (Exceeds 16 characters)

RELAY#1 (Includes an illegal character)

1 2 3 4 5 (all numbers)

## 2.1.4 Delimiters

Delimiters separate individual words. Every distinct word or token in the source program must be separated by one delimiter. Extra space and tab delimiters may be inserted anywhere in the program they have no effect on the meaning of the program. Delimiters in the non-vital program language are listed in Table 2-3.

| space equal sign (=) carriage return <cr></cr> | semicolon (;) close parenthesis ()) backslash (\) | open parenthesis (() colon (:) percent (%) | tab comma (,) tilde (~) |

|------------------------------------------------|---------------------------------------------------|--------------------------------------------|-------------------------|

| at ( <b>@</b> )                                | plus sign (+)                                     | Asterisk (*)                               | Double Quotes (")       |

Table 2-3 Delimiters

#### 2.1.5 Formats

Source program statements may begin anywhere on a line with tabs. Non-significant spaces are ignored by the compiler. If a statement is too long to fit on one line, it may be continued to any number of following lines as required. The maximum allowable line length is 100 characters. If this is exceeded, an error message will be generated. Although the non-vital compiler uses a free format, statements should be arranged for easy reading.

## 2.1.6 Non-Program Comments

Miscellaneous comments may be inserted in the source program to aid the user in charting and reviewing the program. To distinguish a non-program comment from program statements, begin the statement with a percent sign (%) and end with a backslash (\). For example:

#### % THIS IS AN EXAMPLE OF A LEGAL GENISYS 2000 COMMENT\

## II COMPONENT DESCRIPTIONS

When the compiler encounters the percent sign (%), characters are ignored until it reaches a backslash (\). Switches are the exception (refer to section 2.1.7, Compiler Switches). Note that comments may begin anywhere (including the middle of a statement) and span any number of lines in a source program. However, they cannot begin in the middle of a word (ASSI%\ GN is illegal). Another example of a correct comment is as follows:

% THIS IS AN EXAMPLE OF A LEGAL GENISYS 2000 COMMENT\

The closing backslash (\) must be inserted, otherwise the compiler ignores all other characters until a backslash is found

An exclamation point appears before each comment. This character only appears if the comment is the first non-blank item on the line or spans multiple lines and is automatically inserted after the line number to help distinguish the comment from other parts of the program. Thus, if the closing backslash is accidentally omitted from the comment, the exclamation point will appear after every line number to indicate that the compiler regards all subsequent lines as comments, rather than other types of program statements.

## 2.1.7 Compiler Switches

Compiler switches are used in the source program to select various options which control the output of the compiler.

Compiler switches begin with a percent sign (%), like non-program comment. To distinguish it from a comment, a dollar sign (\$) must be placed immediately after the percent sign. After the dollar sign is a single letter representing the switch name. Next is a character(s) representing the value of the switch. All characters after the value character(s) are ignored by the compiler until it encounters the next backslash symbol (\).

| <u>Example</u>                                                                   | Comment                                             |

|----------------------------------------------------------------------------------|-----------------------------------------------------|

| %\$D+\                                                                           | Sets switch "D" to value "ON".                      |

| %\$D- THIS IS A COMMENT FOLLOWING THE SWITCH\                                    | Sets switch "D" to off. The remainder is a comment. |

| The compiler switch is as follows: $\%$ Dv\ Debug (where $v = + \text{ or } -$ ) |                                                     |

This switch informs the compiler to create a symbol table (.GID file) to be used by the Simulator and diagnostic tool. When this switch is turned on (%\$D+), the compiler retains, in a separate file, relay names assigned in the application program so that these names may be used when simulating the application logic and when using the diagnostic tool. Programs to be run on the Simulator must have the D+ switch. The program does not have to be recompiled with %\$D-\ to permit programming of PROMs. The default for this switch is %\$D+\.

## **%\$E\ Page Generator**

When the compiler encounters the %\$E\ switch, the next source line is placed at the top of a new page in the compiler listing.

2-4 SM 6700A 8/96

#### 2.2 PROGRAM EXAMPLES

## 2.2.1 Local Input/Output

The following sample program shows the basic local input/output and logic features of the non-vital program language:

```

GENISYS.2000

PROGRAM NBR1;

INTERFACE

LOCAL

OUTPUT WORD:

OUT.1, OUT.2. OUT.3, OUT.4, OUT.5;

INPUT WORD:

IN.A, IN.B, IN.C;

BEGIN

ASSIGN IN.A AND IN.B

TO OUT.1;

ASSIGN IN.A XOR IN.B

TO OUT.2;

ASSIGN IN.A OR IN.B

TO OUT.3;

TO OUT.4;

ASSIGN NOT IN.A

ASSIGN IN.C

TO OUT.5;

END

```

The section declarations in the program source file (PROGRAM, INTERFACE, LOCAL, OUTPUT WORD, OUTPUT WORD32, INPUT WORD, INPUT WORD32) when present, are always in the order shown. These are discussed later in this section.

The INTERFACE section defines all inputs and outputs for the GENISYS 2000 unit. These include both local parallel inputs and outputs, serial inputs and outputs associated with Master and Slave communication port.

The simple example shown above defines only LOCAL inputs and outputs which are processed by 16 bit input and output boards. There is one OUTPUT WORD declaration for each 16-bit output board and one INPUT WORD declaration for each 16 bit input board. (The 32-bit boards require OUTPUT WORD32 and INPUT WORD32 respectively.) A combined total of 16 OUTPUT WORDS and INPUT WORD sections may be declared, the first corresponding to card slot J3 in the GENISYS 2000 cardfile and the 16th corresponding to card slot J18. Output bits are defined within each OUTPUT WORD section (up to 16-bit output board; 32 for a 32-bit output board). The first defined corresponds to bit 0 on the output PCB; the 16th to output bit 15. Inputs are defined in the same manner. If less bits are defined than the input or output boards supports, the remaining bits on that board are treated as spare bits which have no effect on the performance of the application program.

The number, order and position of the I/O boards defined in the program must match the actual hardware configuration. Output boards must be declared first followed by input boards. Positions may be reserved for future output and input boards by declaring SPARE output and input boards. SPARE and unused input bits are ignored; SPARE and unused output bits are automatically assigned a value of 0. These may be 16 or 32 bit boards as required.

The actual system logic is defined with ASSIGN statements. These statements appear between the BEGIN and END declarations. These statements define the interconnecting logic of the inputs and outputs. The order of the ASSIGN statements will usually have no effect on the logic (refer also to section 2.4.6, Logic Processing). In this example, OUT.1 is the logical AND of the two inputs IN.A and IN.B. Similarly, OUT.2 is the

EXCLUSIVE OR and OUT.3 is the OR of the two inputs. OUT.4 is the logical NOT of IN.A, and OUT.5 directly follows IN.C.

## 2.2.2 Internal Relays and Stick Logic

The following program shows the handling of internal relays and stick logic:

```

GENISYS.2000

PROGRAM NBR2;

INTERFACE

LOCAL

OUTPUT WORD:

OUT.1, OUT.2, OUT.3, OUTA, OUT.5, OUT.6;

INPUT WORD:

IN.A, IN .B, IN.C, IN.D;

VAR

STICK;

BEGIN

TO OUT.1;

ASSIGN IN.A AND IN.B

ASSIGN IN.A XOR IN.B

TO OUT.2;

ASSIGN IN.A OR IN.B

TO OUT.3;

ASSIGN NOT IN.A

TO OUT.4;

ASSIGN IN.C

TO OUT.5;

ASSIGN IN.C OR (STICK AND NOT IN.D) TO STICK:

TO OUT.6;

ASSIGN STICK

END

```

This program is similar to the program NBR1 in the Local I/O section, however OUT.6 is added as the 6th output on the output board. Also, input IN.D, is added as the 4th input bit. A new section VAR is added to define an "internal bit". An internal bit is neither input nor output, it is only processed internally. All internal VAR bits are initially de-energized (logical "0"). An example is a stick relay.

#### **NOTE**:

#### the additional ASSIGN statement:

ASSIGN IN.C OR (STICK AND NOT IN.D) TO STICK;

When input IN.C is energized, STICK becomes energized. With the following direct assignment of STICK to OUT.6, both OUT.6 and STICK will remain energized, even if IN.C is de-energized. The internal STICK and OUT.6 will remain energized until IN.D is energized. This results in the clearing of the stick circuit. However, that if IN.C is still energized, STICK and OUT.6 will remain energized.

2-6 SM 6700A 8/96

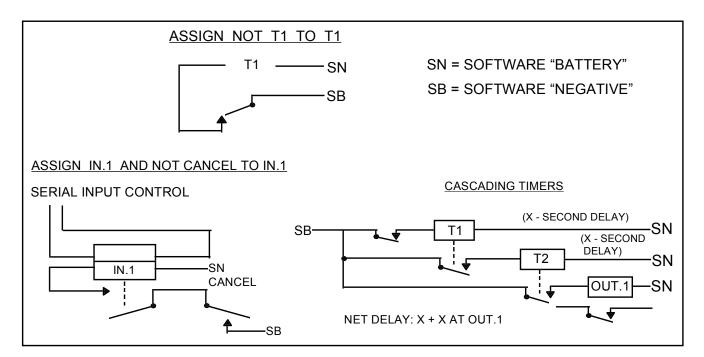

## 2.2.3 Timing Relays

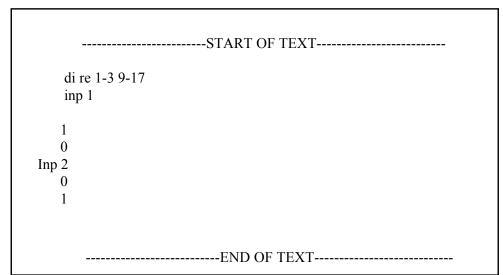

The sample program below shows the handling of timing relays. This program makes use of one timer relay. Continuing from the Program Example section, two more defined output bits, OUT.7 and OUT.8 are added. In the VAR section, another internal relay (Tl) is defined. Relays with timing characteristics are defined in the TIMER section, always after the VAR section. Every bit name specified in a TIMER statement must be previously defined as an output or internal bit. Input bits may not have timing characteristics.

```

GENISYS.2000

PROGRAM NBR3;

INTERFACE

LOCAL

OUTPUT WORD:

OUT.1, OUT.2, OUT.3, OUT.4, OUT.5, OUT.6 OUT.7, OUT.8;

INPUT WORD:

IN.A, IN.B, IN.C, IN.D;

VAR

STICK, T1;

TIMER

T1:

CLEAR = 1:SEC

SET = 1:SEC

BEGIN

ASSIGN IN.A AND IN.B

TO OUT.1;

TO OUT.2;

ASSIGN IN.A XOR IN.B

ASSIGN IN.A OR IN.B

TO OUT.3;

ASSIGN NOT IN.A

TO OUTA;

TO OUT.5:

ASSIGN IN.C

ASSIGN IN.C OR (STICK AND NOT IN.D)

TO STICK:

ASSIGN STICK

TO OUT.6;

TO T1;

ASSIGN NOT T1

ASSIGN T1

TO OUT.7;

ASSIGN NOT T1

TO OUT.8;

END

```

Note the ASSIGN statement:

ASSIGN NOT T1

**TO T1**;

The statement will take the current value of bit T1, initially (0), perform the logical NOT operation, and attempt to assign a value of 1 to T1. Because T1 is defined to have a SET or pick-up delay of 1 second, the actual value will remain at 0 for one second. When time has elapsed and the bit becomes a 1, the assignment statement will execute again, causing the value of 0 to be assigned to T1 with a one second delay (as specified by the CLEAR parameter of the timer statement). Thus, the internal bit, T1, will toggle at a one second rate.

NOTE:

the final two assignment statements added to this program:

ASSIGN T1 TO OUT 7

ASSIGN NOT T1 TO OUT 8

Outputs OUT.7 and OUT.8 will alternately flash at a one second rate OUT.7 on when T1 is 1 and OUT.8 on when T1 is 0.

#### 2.2.4 Master/Slave Communications

The following program shows the handling of Master/Slave serial communications for the Master unit:

```

GENISYS.2000

PROGRAM NBR4M;

INTERFACE

LOCAL

INPUT WORD:

IN.A, IN.B, IN.C;

MASTER

ADDRESS:2

OUTPUT:

M.OUT.1, M.OUT.2, M.OUT.3, M.OUTA, M.OUT.5;

BEGIN

ASSIGN IN.A AND IN.B

TO M.OUT.1:

ASSIGN IN.A XOR IN.B

TO M.OUT.2;

ASSIGN IN.A OR IN.B

TO M.OUT.3;

ASSIGN NOT IN.A

TO M.OUT.4;

TO M.OUT.5;

ASSIGN IN.C

END

```

This sample shows Master/Slave serial communications for the Slave unit:

```

GENISYS.2000

PROGRAM NBR45;

INTERFACE

LOCAL

OUTPUT WORD:

OUT.1, OUT.2, OUT.3; SERIAL SLAVE

SERIAL.SLAVE

ADDRESS:2

M.IN.1, M.IN.2, M.IN.3, M.IN.4, M.IN.5;

BEGIN

ASSIGN M.IN.1 OR M.IN.5

TO OUT.1;

ASSIGN M.IN.4 XOR NOT M.IN.2

TO OUT.2;

TO OUT.3;

ASSIGN M.IN.3 AND M.IN.4

END

```

The above programs allow communication between a Master and one Slave unit. The Slave unit responds to address 2. The Master unit inputs three bits of information, performs logic functions and sends five new output bits (M.OUT.1 through M.OUT.5) to the Slave unit . The Slave receives these bits (M.IN.1 through M.IN.5), performs additional logic and outputs the new computed values to the relay-output PCB in the cardfile. For a complete explanation of Master/Slave communications, refer to the section 2.3.2, Interface.

2-8 SM 6700A 8/96

## 2.3 DETAILED STATEMENT DESCRIPTIONS

## 2.3.1 Program Statement

The first statement in the program must be a DEVICE/PROGRAM statement. This statement gives a name to the program for documentation purposes.

#### **FORMAT:**

#### GENISYS.2000 PROGRAM <id>

The identifier entered here will be printed in the listing at the top of the symbol table. It is written with user-defined symbol (refer to section 2.1.3, User-Defined Symbols). Comments may be placed before a program statement.

#### 2.3.2 Interface

The INTERFACE section contains the various output and input specifications of the system. There are five possible subsections in the INTERFACE section: LOCAL I/O, MASTER I/O port, SERIAL.SLAVE I/O port, SERIAL.SLAVE I/O port, ATCS.SLAVE I/O port, ARES SLAVE I/O port and the DC.CODE.LINE I/O port. These correspond to the five output/input interfaces on the controller board. At least one of the five I/O interfaces must be defined. Each begins with a name (LOCAL, MASTER and any of the various Slave types: SERIAL.SLAVE, SERIAL.SLAVE2, ATCS.SLAVE, ARES.SLAVE, DC.CODE.LINE) that designates the type of interface. The LOCAL I/O is defined first, followed by MASTER and then the various Slave types. Select only one Slave type per application. Within each of these, outputs are defined first, followed by inputs if any. Either outputs or inputs may be blank, but not both at the same time.

#### 2.3.3 Local Section

The LOCAL subsection defines the names of the bits that are input and output on the cardfile I/O boards. (If there is no local I/O, this subsection may be omitted.)

GENISYS 2000 - 1 to 16 words may be defined, with 1 to 16 or 1 to 32 bit names on each word (board type dependent).

Each input or output WORD corresponds to a single I/O board. The first symbol defined on each word corresponds to the first input or output on the corresponding board. The second symbol corresponds to the second input or output, and so on. On interfaces where there is an unused bit between two active bits, the symbol SPARE must be used to identify the unused bit. All output boards must be fully defined ahead of input boards. Outputs or inputs that are unused at the end of a control or indication word need not be defined.

#### **NOTE**

All input boards are scanned every 50 milliseconds. Data delivery to output boards occurs as required. Pulse duration for 16-bit pulse delivery boards is selectable in the configuration section of the application program.

GENISYS.2000 PROGRAM id; INTERFACE LOCAL OUTPUT WORD: <id list>; GENISYS 2000: Up to 16 boards. <id list> (You may have up to 16 or 32 relay names, dependent on board type).

#### 2.3.4 MASTER

The MASTER section defines the input/output interface for each remote GENISYS protocol Slave with which the GENISYS 2000 MASTER serial port communicates. The definition of each Slave begins with an ADDRESS declaration which identifies the remote Slave address. Following the address declaration is the OUTPUT section which defines bits passed from the Master GENISYS 2000 unit to the GENISYS protocol. The INPUT section defines bits passed from the remote GENISYS protocol Slave to the Master unit. The MASTER section may contain up to 64 ADDRESS declarations, each one defining the interface with a different GENISYS 2000 Slave. An example follows on the next page:

2-10 SM 6700A 8/96

```

INTERFACE

MASTER

ADDRESS:1

OUTPUT:

OUT1.1, OUT1.2, OUT1.3, OUT1.4,...OUT1.n;

INPUT:

IN1.1, IN1.2, OUT1.3, OUT1.4, ... OUT1.n;

ADDRESS:

3

OUTPUT:

OUT3.1, OUT3.2, OUT3.3, OUT3.4,...OUT3.n;

INPUT:

IN3.1, IN3.2, IN3.3 ...IN3.n;

SERIAL.SLAVE

```

## 2.3.4.1 ADDRESS Declaration

The ADDRESS declaration within the MASTER section defines a remote GENISYS protocol Slave that communication is to be implemented and specifies its address. Valid addresses are 1 to 255 decimals and the addresses do not have to be consecutive. Definition of bits which are sent to the Slave and received from the Slave follow the address declaration. All defined Slaves must have either an OUTPUT or INPUT declaration as a minimum. In the normal case, both declarations are present.

SM 6700A 8/96

#### 2.3.4.2 **OUTPUT Declaration**

OUTPUT declaration immediately follows the ADDRESS declaration if outputs are to be defined. The OUTPUT declaration is not required. Following the OUTPUT declaration is a list of bits which are to be sent to the Slave. The list may contain 1 to 256 bit names separated by commas and terminated by a semicolon.

## 2.3.4.3 INPUT Declaration

INPUT declaration immediately follows the OUTPUT declaration or the ADDRESS declaration if the OUTPUT declaration is not present. The INPUT declaration is not required. Following the INPUT declaration is a list of bits which are expected to be received from the Slave unit. The list may contain 1 to 256 bit names separated by commas and terminated by a semicolon.

#### 2.3.5 SERIAL.SLAVE

The SERIAL.SLAVE section defines the input/output interface for the GENISYS 2000 Serial Slave communication port. This declaration is valid only in application programs to be used with GENISYS 2000 Executives that support a Serial Slave communication port. (Presently, these include, the GENISYS, MCS-1, DATATRAIN II and VIII, DF1 and WB&S S2 Executives.) These various code types are declared immediately after the keyword SERIAL.SLAVE:. The code type is entered as a "string" which is preceded and followed with a double quote. The valid code types are "GENISYS", "DF1", "GRSDTS", "GRSDTP", "GRSDT2", "MCS1", "MCS2" and "WBSS2". This declaration is optional. The default is "GENISYS". A GENISYS 2000 unit may be programmed to simultaneously represent up to 6 different Serial Slaves. This capability is normally used when emulating code formats with limited control and indication message lengths (MCS-1, for example) to expand the Slave communication capacity of a single GENISYS 2000 unit. While multiple Slave support is not required for the GENISYS Slave protocol, it is still available. Additionally, an independent dualport configuration may be defined using the keyword SERIAL.SLAVE2. All logic for this type is identical to the SERIAL.SLAVE type. Refer to the SERIAL2 and SER2 configuration items for port specifics. Note, SERIAL.SLAVE2 refers specifically to port 2.

The definition of each "logical Slave" begins with an ADDRESS declaration which identifies the Slave address. Following the ADDRESS declaration is the OUTPUT section which defines bits passed from the logical Slaves to its Master. The INPUT section follows the OUTPUT section and defines bits passed from the Master to the logical Slave. The SERIAL.SLAVE (and or SERIAL.SLAVE2) section may contain up to 6 ADDRESS declarations, each one defining a different Serial Slave. An example is shown on the next page:

2-12 SM 6700A 8/96

```

INTERFACE

SERIAL.SLAVE: "GENISYS" % SERIAL CODE TYPE IS AN OPTIONAL PARAMETER\

ADDRESS: 1

OUTPUT:

SLVOUT1.1, SLVOUT1.2, SLVOUT1.3, SLVOUT1.4, ... SLVOUT1.n;

INPUT:

SLVIN1.1, SLVIN1.2, SLVOUT1.3, SLVOUT1.4, ... SLVOUT1.n;

ADDRESS: 3

OUTPUT:

SLVOUT3.1, SVLOUT3.2, SVLOUT3.3, SVLOUT3.4, ... SVLOUT3.n;

INPUT:

SLVIN3.1, SLVIN3.2, SLVIN3.3 ... SLVIN3.n;

CONFIGURATION

```

#### 2.3.5.1 ADDRESS Declaration

The ADDRESS declaration within the SERIAL.SLAVE (and or SERIAL.SLAVE2) section defines a "logical Slave" and specifies its address. Valid addresses vary with the Serial Slave protocol implemented. For GENISYS and WB&S S2 protocol Slaves, valid addresses are 1 to 255 decimal. Valid addresses for MCS-1 protocol Slaves are 1 to 62 decimal. The Slave addresses do not have to be consecutive. Definition of bits which are sent to the Master and received from the Master follow the address declaration. All defined logical Slaves must have either an OUTPUT or INPUT declaration as a minimum. In the normal case both declarations are present.

#### 2.3.5.2 FLAG Declaration

The SERIAL.FLAG declaration is OPTIONAL. This parameter is defaulted to zero. It will be used in future development.

## 2.3.5.2.1 DATATRAIN VIII Specific

An optional parameter for the DATATRAIN VIII code system follows: The DATATRAIN VIII serial code type may require a specific one to four byte hexadecimal address which is specified after the optional **SERIAL.FLAG** parameter and before the **OUTPUT** keyword. Either a slave address and or a peer address may be declared. Defaults for slave and peer addresses are zero. If this parameter is specified the slave address is specified by using the keyword **DT8.SLV.ADDRESS**: followed by a variable length (1 to 4 byte) hexadecimal string which is preceded and followed by double quotes. It is also possible to specify the peer address by using the keyword **DT8.PEER.ADDRESS**: followed by a variable length (1 to 4 byte) hexadecimal string which is preceded and followed by double quotes.

## 2.3.5.2.2 ALLEN BRADLEY DF1 Specific

An optional parameter for the DF1 code system follows: The DF1 serial code type may require a specific control and indication byte offset which is specified after the optional **SERIAL.FLAG** parameter and before the **OUTPUT** keyword. Either a control offset and or a indication offset may be declared. Defaults for control and indication offsets are zero. If this parameter is specified the control offset is specified by using the keyword **CONTROL.OFFSET:** followed by an integer value in the range of 0-99 bytes. It is also possible to specify the indication offset by using the keyword **IND.OFFSET:** followed by an integer value in the range of 0-99 bytes.

#### 2.3.5.3 **OUTPUT Declaration**

The OUTPUT declaration immediately follows the ADDRESS declaration if outputs are to be defined. The OUTPUT declaration is not required. Following the OUTPUT declaration is a list of bits which are to be sent to the Master. The list may contain 1 to 256 bit names separated by commas and terminated by a semicolon. (The upper limit of 256 bits applies to GENISYS protocol Slaves. The limit for other Serial Slave types may be lower.)

#### 2.3.5.4 INPUT Declaration

INPUT declaration immediately follows the OUTPUT declaration or the ADDRESS declaration if the OUTPUT declaration is not present. Following the INPUT declaration is a list of bits which are expected to be received by the Slave. The list may contain 1 to 256 bit names separated by commas and terminated by a semicolon. (The upper limit of 256 bits applies to GENISYS protocol Slaves. The limit for other Serial Slave types may be lower.)

## 2.3.6 ATCS.SLAVE or ARES.SLAVE

The ATCS.SLAVE or ARES.SLAVE section defines the input/output interface for the GENISYS 2000 AxxS Slave communication port. This declaration is valid only in application programs to be used with GENISYS 2000 AxxS Slave protocol Executive. Up to 6 AxxS "logical Slaves" can be supported by a single GENISYS 2000 unit although only one is normally defined. The "xx" refers to ATCS or ARES Slave types; ATCS and ARES may not be mixed. In future releases, various ATCS/ARES slave types may be declared immediately following the AxxS.SLAVE keyword. Presently, the ARES slave type is "ARES" and the ATCS slave type is "ATCS". This optional parameter will follow the same syntax as SERIAL.SLAVE and DC.SLAVE. Any mixing of these two Slave types will result in a compiler error. (See section 2.3.5, SERIAL.SLAVE for additional discussion on the definition of multiple logical Slaves.)

2-14 SM 6700A 8/96

The definition of each "logical Slave" begins with an ADDRESS declaration. Following the ADDRESS declaration is the WIU.ADDRESS declaration. Following the WIU.ADDRESS is the OUTPUT section which defined bits passed from the logical Slave to its Master. The INPUT section follows the OUTPUT section and defines bits passed from the Master to the logical Slave. The ATCS/ARES.SLAVE section may contain up to 6 ADDRESS declarations, each one defining a different ATCS/ARES.Slave. An example is shown here:

```

INTERFACE

ATCS.SLAVE

ATCS.FLAG:0;

ADDRESS

WIU.ADDRESS:

"5266A1A1A100000A"

OUTPUT:

SLVOUT1.1, SLVOUT1.2, SLVOUT1.3, SLVOUT1.4, ... SLVOUT1.n;

INPUT:

SLVIN1.1, SLVIN1.2, SLVOUT1.3, SLVOUT1.4, ... SLVOUT1.n;

ADDRESS

WIU.ADDRESS:

"5266A1A1A300000A"

OUTPUT:

SLVOUT3.1, SVLOUT3.2, SVLOUT3.3, SVLOUT3.4, ... SVLOUT3.n;

INPUT:

SLVIN3.1, SLVIN3.2, SLVIN3.3 ... SLVIN3.n;

CONFIGURATION

```

#### 2.3.6.1 FLAG Declaration

The ATCS.FLAG or ARES.FLAG declaration is OPTIONAL. This parameter is defaulted to zero. It will be used in future development.

#### 2.3.6.2 ADDRESS Declaration

The ADDRESS declaration within the AxxS.SLAVE section defines a "logical Slave". The ADDRESS declaration requires no parameters in the AxxS Slave section. The WIU.ADDRESS declaration follows the ADDRESS declaration and specifies the AxxS address of the logical Slave. Definition of bits which are sent to the Master and received from the Master follow the WIU.ADDRESS declaration. All defined logical Slaves must have either an OUTPUT or INPUT declaration as a minimum. In the normal case, both declarations are present.

#### 2.3.6.3 WIU.ADDRESS Declaration

The WIU.ADDRESS declaration specifies the ATCS address for the logical Slave. This address is a 16 digit number enclosed in double quotes ("). The format of this address is as specified in the latest revision of ATCS (PTS) Specification 200. In general, the format of this address is "IRRRWWWWWW00000L" where:

I address type identifier from ATCS (PTS) Spec 200, appendix T

RRR railroad ID from ATCS (PTS) Spec. 250, Appendix F

WWWWWW field code unit identity (the format of this segment is determined by the

architecture of the specific communication network being used)

L a hexadecimal character representing the number of valid digits in the

address (A to F)

Per the ATCS address syntax rules, the address digits are left justified, "0" digits are replaced by "A", and unused digits are "0". The maximum legal length of an ATCS address is 15 digits. The 16th digit is always the number of used (non-zero) digits in the address.

Per the ARES address syntax rules, the address digits are left justified and zero (0) digits are valid in the address. The maximum legal length of the ARES address is 15 digits. The 16th digit is always the number of digits in the address.

#### 2.3.6.4 **OUTPUT Declaration**

The OUTPUT declaration immediately follows the WIU.ADDRESS declaration if outputs are to be defined. Following the OUTPUT declaration is a list of bits which are to be sent to the Master. The list may contain 1 to 256 bit names separated by commas and terminated by a semicolon.

#### 2.3.6.5 INPUT Declaration

INPUT declaration immediately follows the OUTPUT declaration or the ADDRESS declaration if the OUTPUT declaration is not present. The INPUT declaration is not required. Following the INPUT declaration is a list of bits which are expected to be received by the Slave. The list may contain 1 to 256 bit names separated by commas and terminated by a semicolon.

2-16 SM 6700A 8/96

## 2.3.7 DC.CODE.LINE

The DC.CODE.LINE section defines the input/output interface for the GENISYS 2000 DC code line Slave communication port. This declaration is valid only in application programs to be used with GENISYS 2000 DC code line Slave Executive. Following the DC.CODE.LINE keyword and a colon is a code line type enclosed in double quotes ("). Currently, the valid types are USS504, USS506, and USS514. Up to 6 DC code line "logical Slaves" (PUPS) can be supported by a single GENISYS 2000 unit. (See SERIAL.SLAVE section for additional discussion on the definition of multiple logical Slaves.)

The definition of each "logical Slave" begins with an ADDRESS declaration. Following the ADDRESS declaration is the INDICATION declaration. This declaration defines the indication (field to office) section of the DC Slave. The indication message LENGTH, indication ADDRESS, OUTPUT declaration follow in sequence.

The CONTROL declaration defines the control (office to field) section of the DC Slave. The control message LENGTH, control ADDRESS and INPUT declaration follow in sequence. The DC.CODE.LINE section may contain up to 6 ADDRESS declarations, each one defining a different DC code line Slave. An example is shown on the next page:

```

INTERFACE

DC.CODE.LINE:

"USS514"

ADDRESS

INDICATION

LENGTH:

16;

"SSLSLSLS"

ADDRESS:

OUTPUT:

SLVOUT1.1, SLVOUT1.2, SLVOUT1.3, SLVOUT1.4, ... SLVOUT1.n;

CONTROL

LENGTH:

16;

"SSLSLSLS"

ADDRESS:

INPUT:

SLVIN1.1, SLVIN1.2, SLVOUT1.3, SLVOUT1.4, ... SLVOUT1.n;

ADDRESS

INDICATION

LENGTH:

16;

"SSLSLLSS"

ADDRESS:

OUTPUT:

SLVOUT3.1, SVLOUT3.2, SVLOUT3.3, SVLOUT3.4, ... SVLOUT3.n;

CONTROL

LENGTH:

16

ADDRESS:

"SSLSLLSS"

INPUT:

SLVIN3.1, SLVIN3.2, SLVIN3.3 ... SLVIN3.n;

CONFIGURATION

```

2-18 SM 6700A 8/96

#### 2.3.7.1 FLAG Declaration

The DC.FLAG declaration is OPTIONAL. This parameter is defaulted to zero. It will be used in future development.

#### 2.3.7.2 ADDRESS Declaration

The ADDRESS declaration within the DC.CODE.LINE section defines a "logical Slave". The ADDRESS declaration requires no parameter in the DC Slave section.

#### 2.3.7.3 INDICATION Declaration

The INDICATION declaration marks the beginning of the section in which the indication characteristics of the DC Slave are specified. This section includes the indication message LENGTH, the indication ADDRESS, and the OUTPUT list which specifies the bits contained in the indication message for this Slave. The INDICATION declaration includes no parameters.

## 2.3.7.4 Indication LENGTH Declaration

The indication LENGTH declaration specifies the length of the indication message. The length of the indication message includes the address (always 8 bits), the number of indication bits to be transmitted, and 1 terminator bit. If the resulting value is an odd number, one additional bit is added. Valid values are even numbers between 10 and 64 for USS514 code lines and 16 for all other supported code lines. If the indication LENGTH declaration is omitted, the indication length defaults to 16. Notice that the specified length need not match the number of bits in the OUTPUT list, but it should be greater than the number of bits in the OUTPUT list. If the length specified is insufficient to transport all indication bits defined for the DC Slave, bits at the end of the OUTPUT list will not be included in the indication message. Bits transmitted in the indication message beyond those defined in the OUTPUT list (the indication message includes more bits than are defined) are always transmitted as short ("0") code steps. In any case, the specified indication length must match that specified for the office code unit or misoperation will result.

#### 2.3.7.5 Indication ADDRESS Declaration

The indication ADDRESS declaration specifies the address to be transmitted with the indication for this Slave. The ADDRESS is always 8 bits (steps) long and must be a valid 504, 506, 514 address. The address is specified in Long/Short (L/S) or 1/0 format and must be enclosed in double quotes ("). See the appropriate code system manual for valid addresses.

#### 2.3.7.6 **OUTPUT Declaration**

The OUTPUT declaration immediately follows the indication ADDRESS declaration if outputs are to be defined. Following the OUTPUT declaration is a list of bits which are to be sent to the office code unit. The list may contain 1 to 49 bit names for USS514 Slave, 1 to 7 bit names for a USS504 or USS506 Slave. The bit names are separated by commas. The list is terminated by a semicolon.

#### 2.3.7.7 CONTROL Declaration

The CONTROL declaration marks the beginning of the section in which the control characteristics of the DC Slave are specified. This section includes the control message LENGTH, the control ADDRESS (normally the same as the indication ADDRESS), and the INPUT list which specifies the bits contained in the control message for this Slave. The CONTROL declaration includes no parameters.

#### 2.3.7.8 Control LENGTH Declaration

The control LENGTH declaration specifies the expected length of the control message. The length of the control message includes the address (always 8 bits), the number of control bits expected in a control message, and 1 terminator bit. If the resulting value is an odd number, one additional bit is added. Valid values are even numbers between 10 and 64 for USS514 code lines and 16 for all other code lines. If the control LENGTH declaration is omitted, the control length defaults to 16. Note that the specified length need not match the number of bits in the INPUT list, but it must be greater than the number of bits in the INPUT list. Bits received in the control message beyond those in the INPUT list are discarded. If less than the specified number of bits are received, the entire message is discarded. In any case, the specified control length must match that specified for the office code unit or misoperation will result.

#### 2.3.7.9 Control ADDRESS Declaration

The control ADDRESS declaration specifies the address associated with the input bits for this Slave. The address is always 8 bits (steps) long and must be a valid 504, 506, 514 address. It should (but is not required to) match the indication ADDRESS. The address is specified in Long/Short (L/S) or 1/0 format and must be enclosed in double quotes("). See the appropriate code system manual for valid addresses.

## 2.3.7.10 INPUT Declaration

The INPUT declaration immediately follows the control ADDRESS declaration. Following the INPUT declaration is a list of bits which are expected to be received by the Slave. The list may contain 1 to 49 bit names for a USS 514 Slave or 1 to 7 bit name for a USS 504 or USS 506 Slave. The bit names are separated by commas. The list is terminated by a semicolon.

## 2.4 CONFIGURATION ITEMS FOR PROGRAM PARAMETERS

## ARES.FAIL.TIMER

**APPLICABILITY:** ARES.SLAVE

**RANGE OF VALUES:** 10 TO 600 SECONDS

**DEFAULT:** 300 SECONDS **REQUIRED/OPTIONAL:** OPTIONAL

#### **DESCRIPTION:**

ARES.FAIL.TIMER specifies the time in seconds after which the ARES communication link is declared failed when no message addressed to any of the defined ARES Slaves have been detected. When the ARES fail timer has expired, the system bit ARES.MASTER.ON is cleared. This bit can be used by the application program to obtain current status of the ARES communication link.

2-20 SM 6700A 8/96

## ARES.GNDLNK

**APPLICABILITY:** ARES.SLAVE

**RANGE OF VALUES:** VALUES BETWEEN 01 AND FE (HEX)

**DEFAULT:** 2

**REQUIRED/OPTIONAL:** OPTIONAL

#### **DESCRIPTION:**

ARES.GNDLNK sets the HDLC link address to which the ARES Slave port addresses its responses. The default should not be changed.

#### ARES.GROUND

**APPLICABILITY:** ARES.SLAVE

**RANGE OF VALUES:** SEE "SPECIFICATION OF ARES ADDRESSES"

**DEFAULT:** 0 (NULL ADDRESS)

**REQUIRED/OPTIONAL:** OPTIONAL

#### **DESCRIPTION:**