# FUR WIND SERVICE MANUAL

# **ECHO SOUNDER**

MODEL

FE-700

## © FURUNO ELECTRIC CO., LTD.

9-52, Ashihara-cho, Nishinomiya, Japan

Telephone: 0798-65-2111 Telefax: 0798-65-4200 •Your Local Agent/Dealer

All rights reserved. Printed in Japan

FIRST EDITION: APR 2000

PUB. No. SME-23660-A FE-700

(MAYA)

# How to upgrade software

Necessary tools:

- 1) A DOS/V compatible PC (NEC PC98 cannot be used.)

- 2) OS: MS-DOS/Windows 95/98

- 3) Interconnection cables: 80-0654 and SAP-161-101

- 4) New Software

Fabricate the interconnection cable between the monitor unit and the PC as below.

|      | PC                |

|------|-------------------|

| MJ6P | (D-SUB, 9 pins)   |

| >1>  | <2                |

| >2>  | <1                |

| >3>  | <3                |

| >4>  | · <del>-</del> <4 |

| >5>  | <6                |

| >6>  | <5                |

|      | <u>-</u> <7       |

|      | <8                |

| 4    | <9                |

|      |                   |

|      | >1>               |

Cable: SAP-161-101 Cable: 80-0654

- New software supplied is a self-extracting file. Make a new file on the PC, copy a

file supplied, fe700vx.exe to the new file, then, double-click the fe700vx.exe icon.

Nine files are extracted.

- Up700.bat, load600.b, load600.b96, uppg.exe, dummy.b, boot600.bin, upboot60.bat, fe700t1.bin, update.txt

- 2. Copy these files to a floppy disk to execute the program from the floppy disk.

- 3. Connect the DATA port on the FE-700 display unit to the serial I/O port of the PC.

- 4. Turn on the PC. Do not as yet turn on the FE-700.

- 6. Insert the program disk and type **A:**, followed by Enter key. A:¥> is on the screen.

- 7. Type **up700** and press Enter key.

- 8. Select baud rate "2:19200." "TARGET power on" comes on the PC screen.

- 9. Turn on the FE-700.

- 10. Wait for about 6 minutes.

The PC screen shows the progresses of updating. When loading of new software is completed, "Finish version up.ted" appears on the PC screen while the FE-700 shows normal picture.

11. Turn off the FE-700 and the PC to disconnect the cable.

**FURUNO**°

# Information

Issued by: FURUNO ELECTRIC CO., LTD.

SERVICE MANAGEMENT & COMMANDING DEPARTMENT

No.: FQ2-2004-003 1/2

Date: 2004-01

APPROVED BY

WRITTEN BY

Addenda No.2 to Service Manual for FE-700, Pub No. SME-23660

## FE-700

# Capacitor with Wrong Polarity

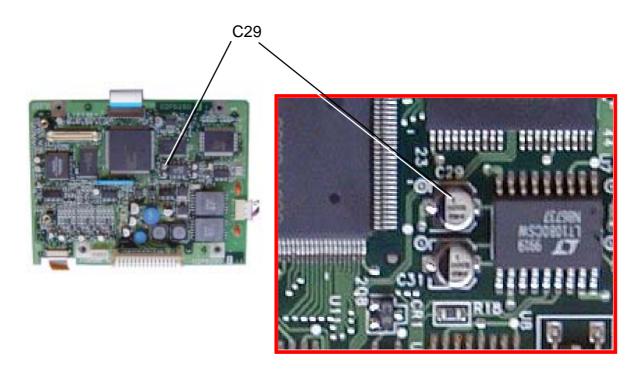

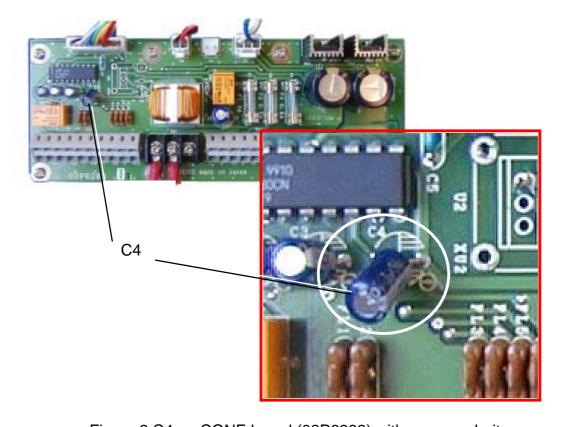

Following capacitors are fitted with wrong polarity. Change MAIN board and C4 on CONE board. If not, communication error between FE-700 and a printer/PC will result typically.

| Unit                     | Board          | Parts No. |

|--------------------------|----------------|-----------|

| Display unit, FE-701     | MAIN, 02P6280A | C29       |

| Distribution box, FE-702 | CONE, 02P6283  | C4        |

This information is applicable to the units having following serial numbers.

2232-0001 to 1860 (except for 1852), 1917, 1997,1998, 2061, 2063, 2064, 2259, 2275, 2297, 2305, 2306, 2308, 2306, 2309, 2331, 2333, 2345, 2347, 2348, 2364 to 2366, 2367, 2369, 2370, 2371, 2376, 2385, 2394, 2403, 2408 to 2416, 2419, 2423, 2428, 2435, 2436

#### Necessary parts

| Parts name | Туре        | Code number | Remarks                   |

|------------|-------------|-------------|---------------------------|

| MAIN board | 02P6280A    | 001-229-670 | C29 with correct polarity |

| Capacitor  | ECA-1HM010B | 000-135-484 | For CONE board            |

#### Identification

The PCB is wrongly marked with a - sign. When the capacitor is placed with - sign on the board, the polarity is wrong. See next page.

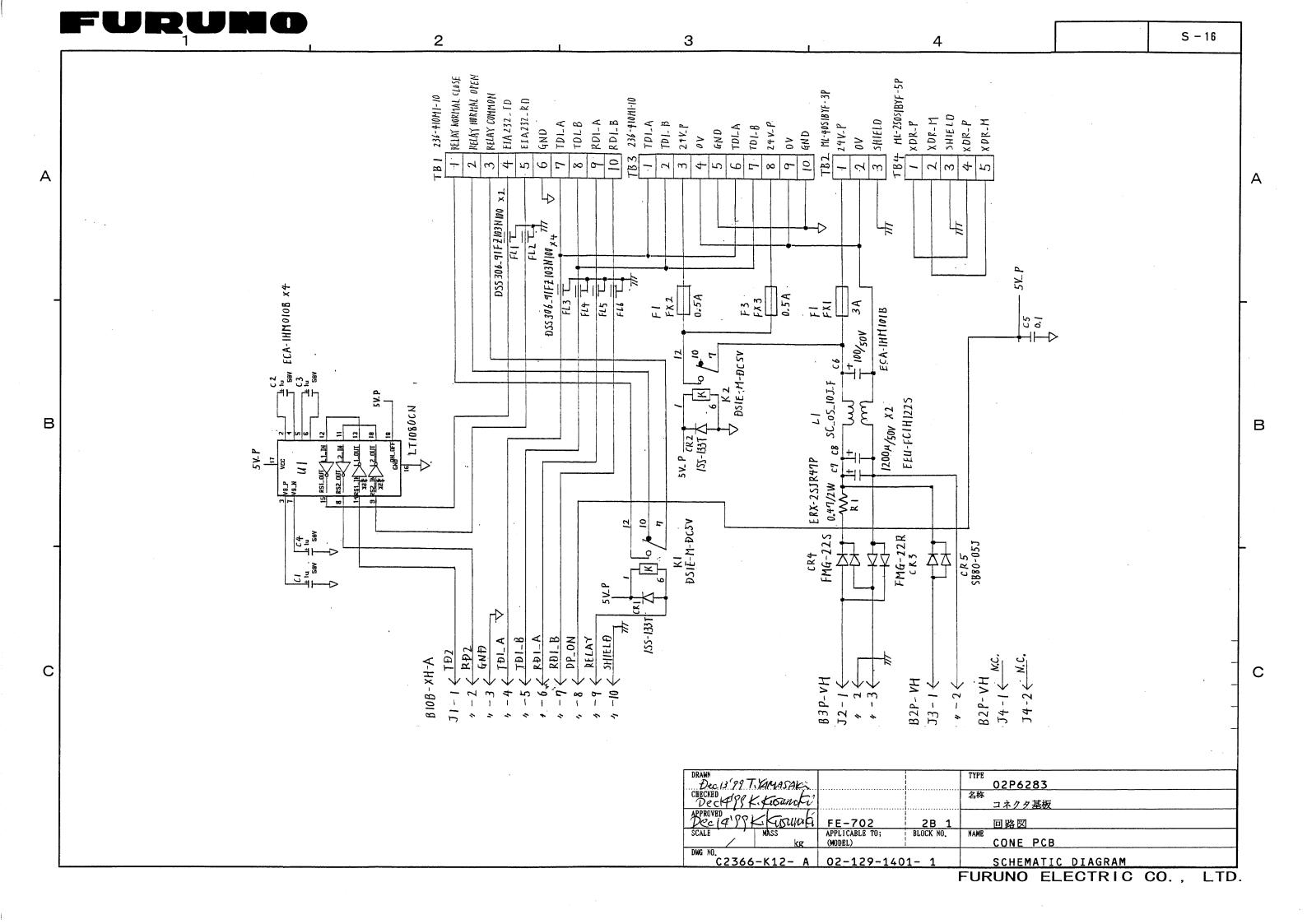

Capacitors C4 and C29 are also marked wrongly in schematic diagrams, Dwg. Nos. C2336-K12-A and C2336-K03-A respectively.

#### Note:

When MAIN board 02P6280 is replaced with 02P6280A, ANLG board must be modified. Refer to FQ2-2003-001.

#### **Factory-modified sets**

From the production in September 2003

2

E/S FCV

Figure 1 C29 on MAIN board (02P6280(A) with wrong polarity

Figure 2 C4 on CONE board (02P6283) with wrong polarity

# CONTENTS

| Gen  | eral                                    |

|------|-----------------------------------------|

| SYS  | TEM CONFIGURATION1                      |

| Chap | oter 1. Circuit Description             |

| 1.1  | GENERAL BLOCK DIAGRAM2                  |

| 1.2  | FUNCTION OF EACH UNIT3                  |

| 1.3  | POWER SUPPLY4                           |

| 1.4  | TRANSMISSION CIRCUIT7                   |

| 1.5  | RECEIVING CIRCUIT8                      |

| 1.6  | DISPLAY9                                |

| Cha  | oter 2. Maintenance                     |

| 2.1  | ADJUSTMENT12                            |

| 2.2  | REPLACEMENT OF LITHIUM BATTERY12        |

| Chap | oter 3. Troubleshooting                 |

| 3.1  | DIAGNOSTIC TEST13                       |

| 3.2  | CLEARING THE MEMORY15                   |

| 3.3  | ALARM AND ERROR MESSAGE15               |

| 3.4  | INSPECTION OF EACH BOARD16              |

| Chap | oter 4. Parts Location                  |

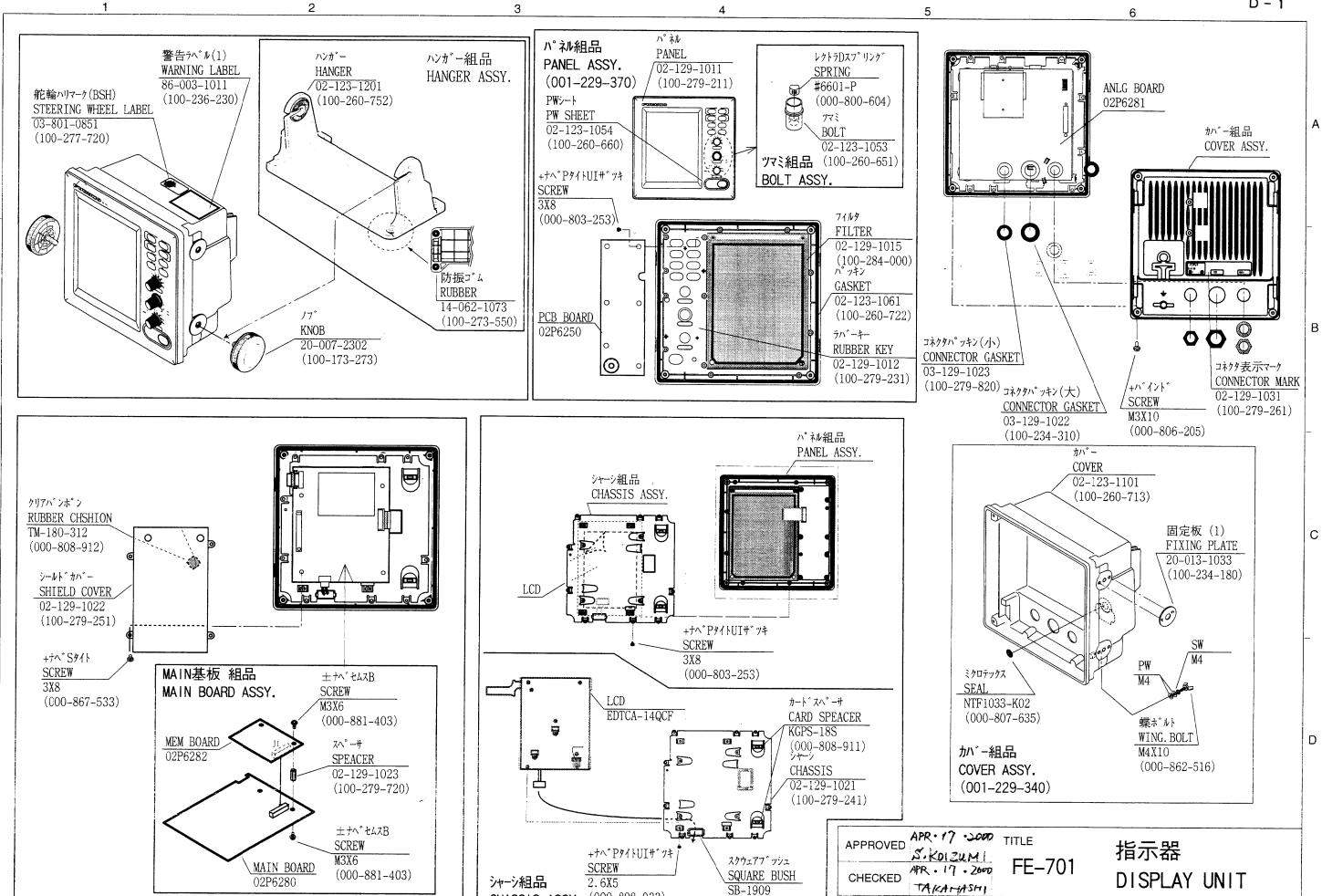

| 4.1  | DISPLAY UNIT18                          |

| 4.2  | DISTRIBUTION BOX23                      |

| 4.3  | MATCHING BOX24                          |

| 4.4  | SWITCH BOX25                            |

| Chap | oter 5. Digital interface (IEC 61162-1) |

| 5.1  | I/O SENTENCES                           |

| 5.2  | SENTENCE DESCRIPTION26                  |

| PAR  | <b>TS LIST</b> 30                       |

| Expl | oded ViewD-1                            |

| Elec | trical Parts ListE-1                    |

| Sche | ematic DiagramS-1                       |

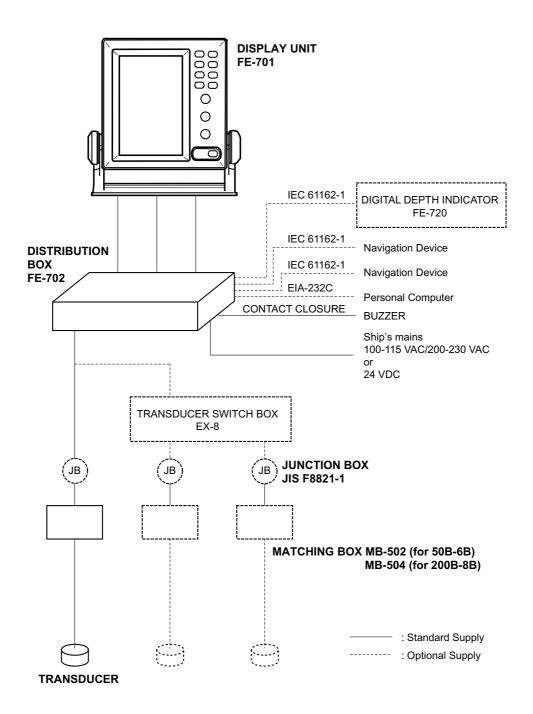

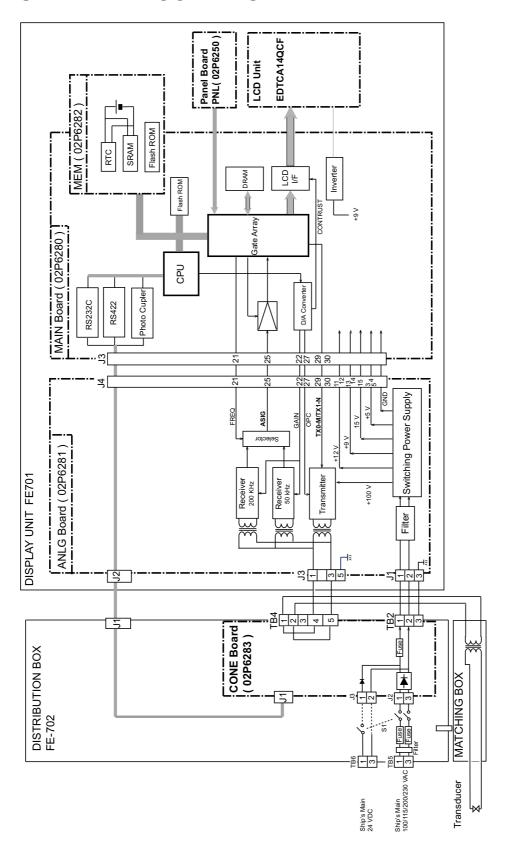

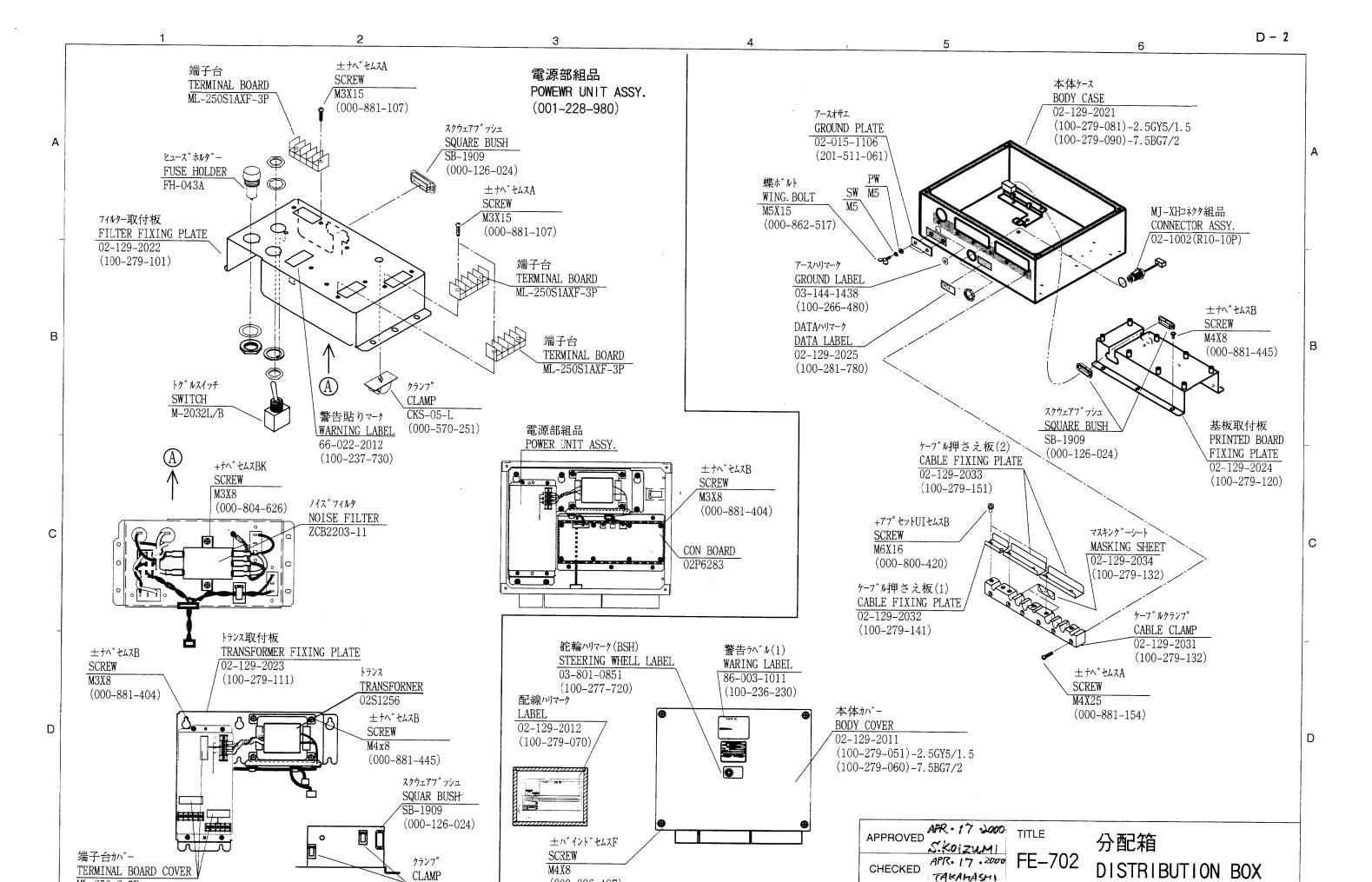

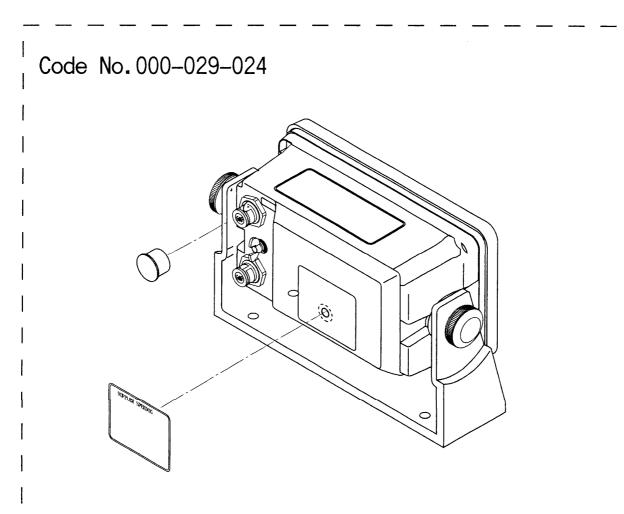

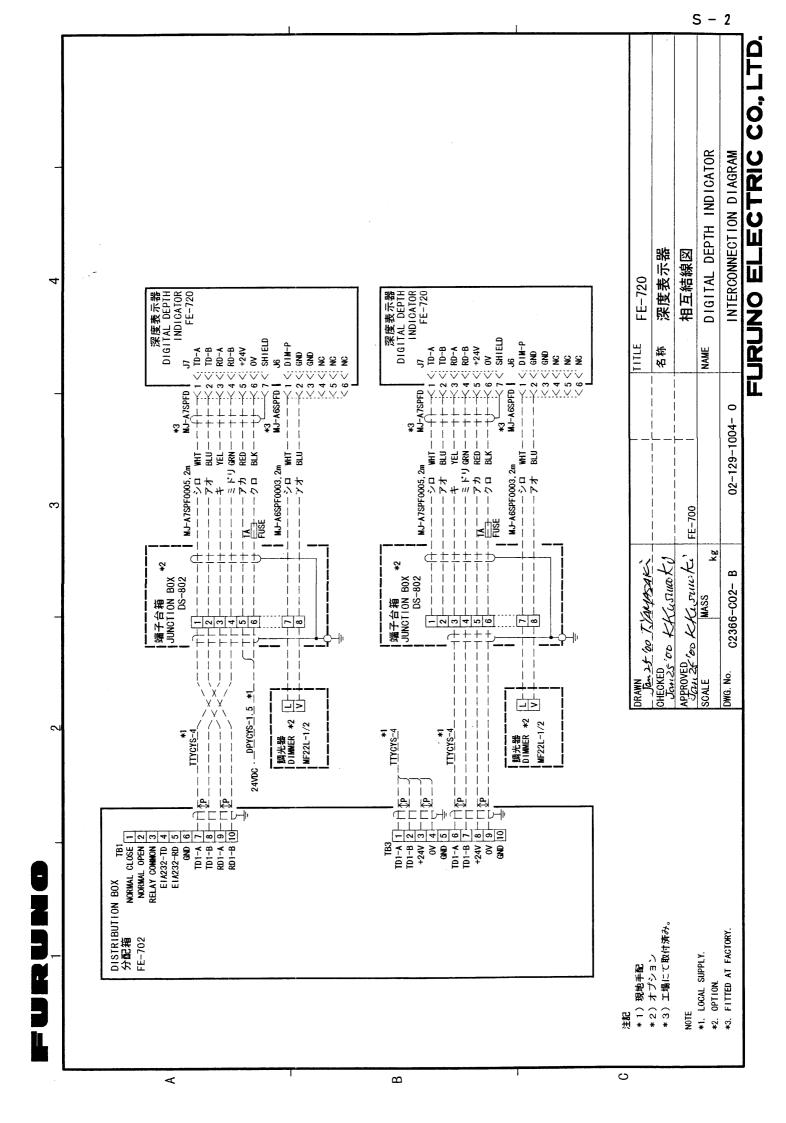

## SYSTEM CONFIGURATION

The FE-700 consists of Display Unit ( FE701 ) , Distribution Box ( FE702 ), Transducer Switching Box ( EX-8 ) and Matching Box ( MB-502/MB-504 ). The Switching Box and Matching Box connected to switching box are supplied optionally.

# **Chapter 1. Circuit Description**

# 1.1 GENERAL BLOCK DIAGRAM

Figure 1.1 General Block Diagram

# 1.2 FUNCTION OF EACH UNIT

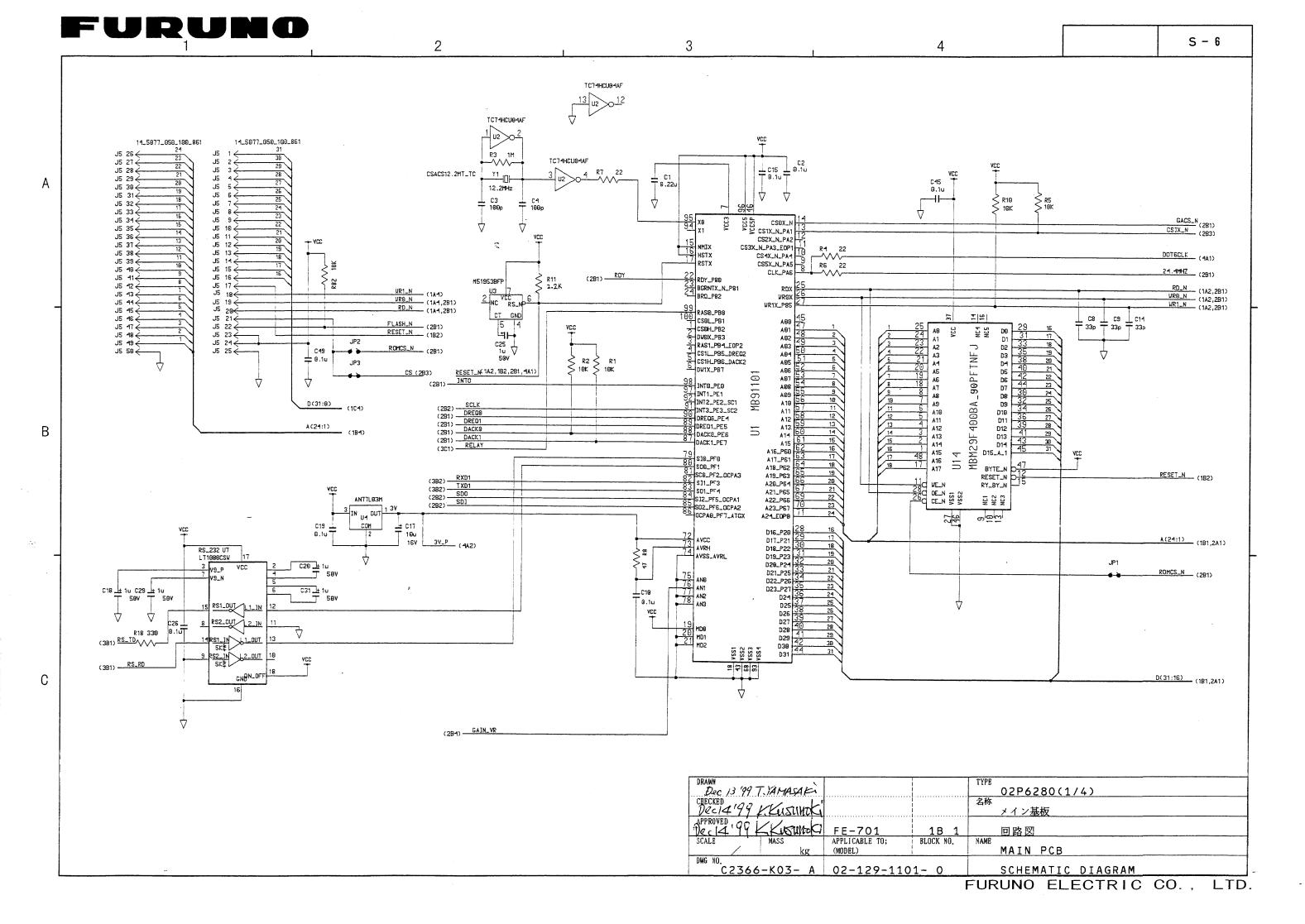

## Display Unit (FE-701)

| Board/Unit              | Functions                                                                                         |  |  |

|-------------------------|---------------------------------------------------------------------------------------------------|--|--|

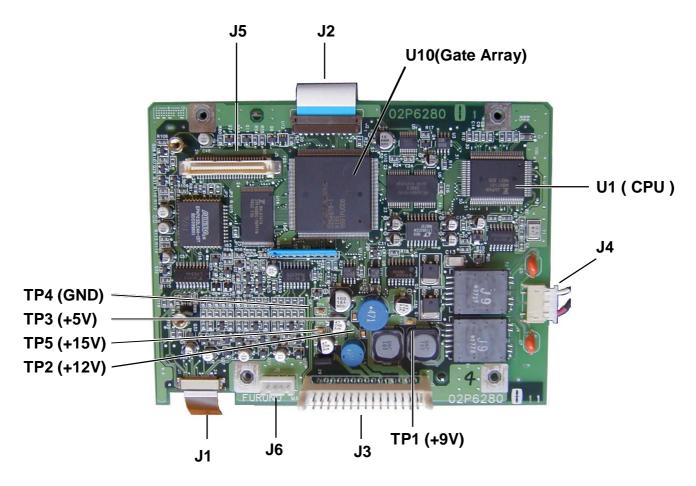

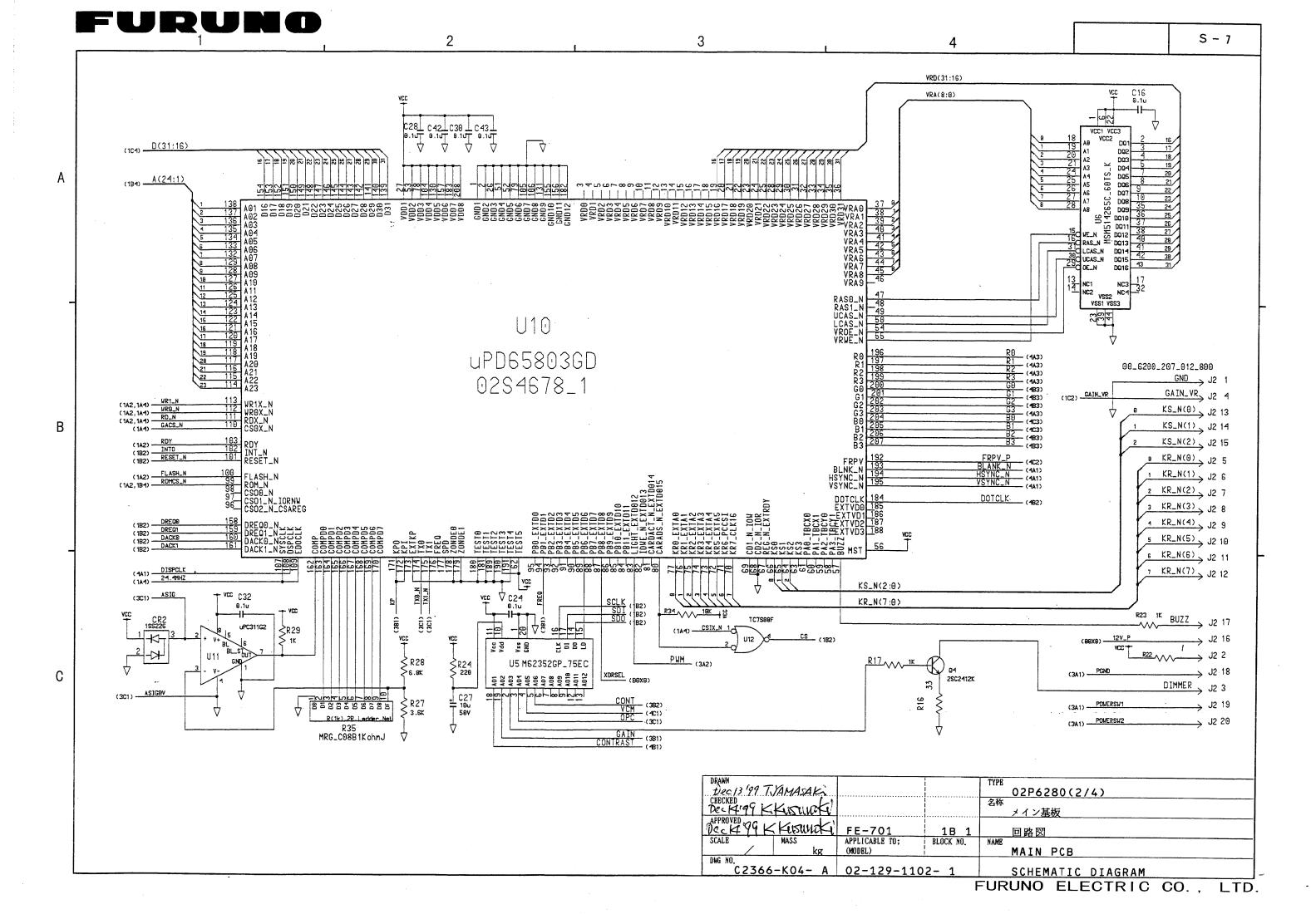

| MAIN Board<br>(02P6280) | 1) Processes depth signal by the CPU and the gate array, and converts them into the video signal. |  |  |

| ,                       | 2) Receives panel signal.                                                                         |  |  |

|                         | 3) Detects the depth.                                                                             |  |  |

|                         | 4) Generates the "SHALLOW DEPTH ALARM".                                                           |  |  |

|                         | 5) Includes a LCD I/F and an inverter for LCD backlighting.                                       |  |  |

|                         | 6) Communicates with external equipment in IEC61162-1 and RS232C data format.                     |  |  |

| ANLG Board<br>(02P6281) | Consists of a power circuit, a depth sounder circuit and an interface circuit.                    |  |  |

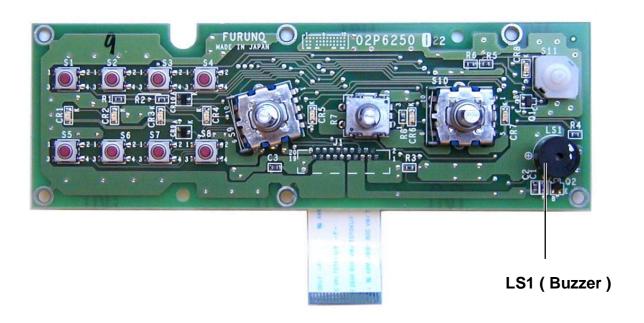

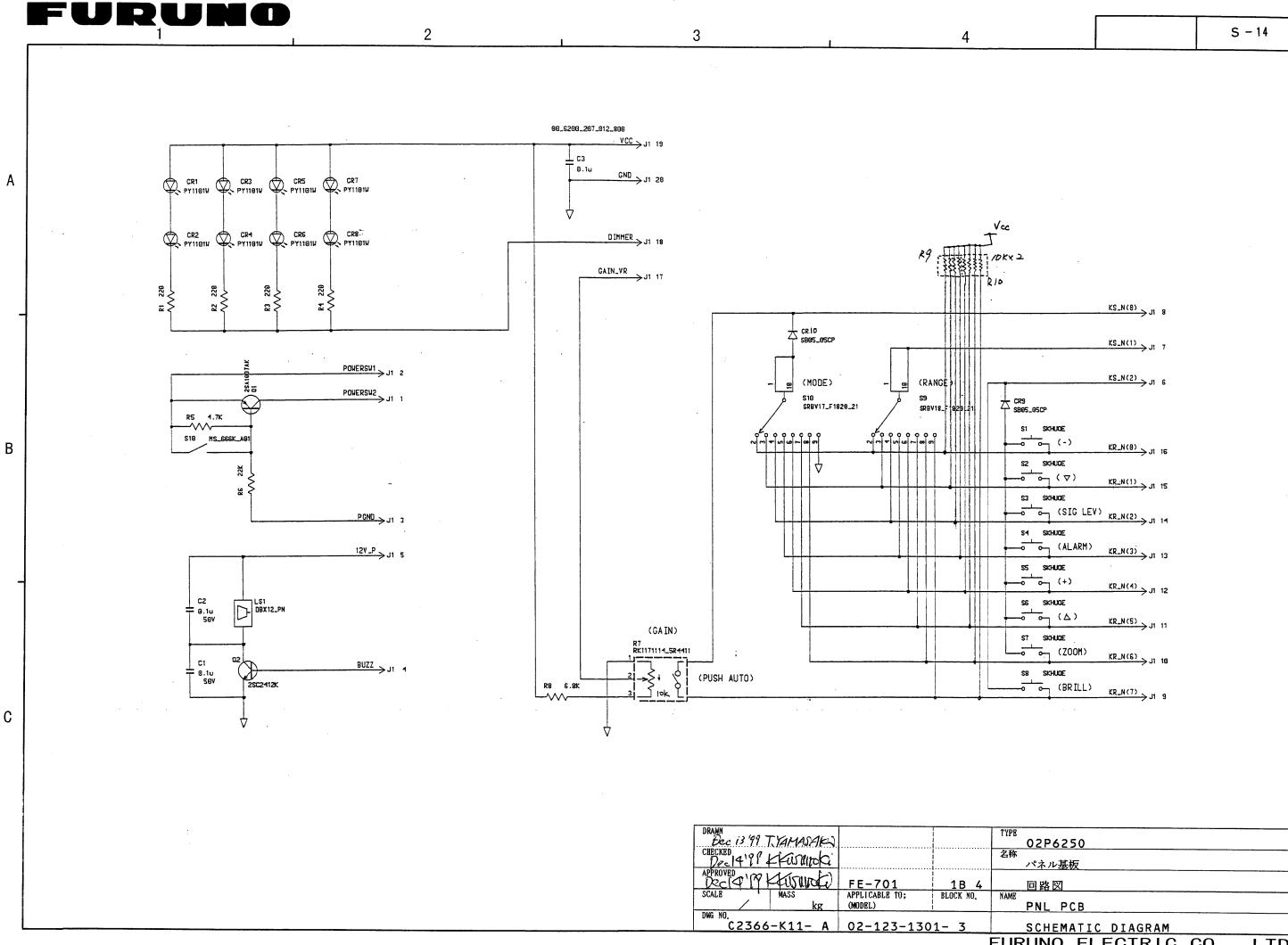

| PNL Board<br>(02P6250)  | Consists of keys, rotary switches, VRs, LEDs for panel illumination and a buzzer.                 |  |  |

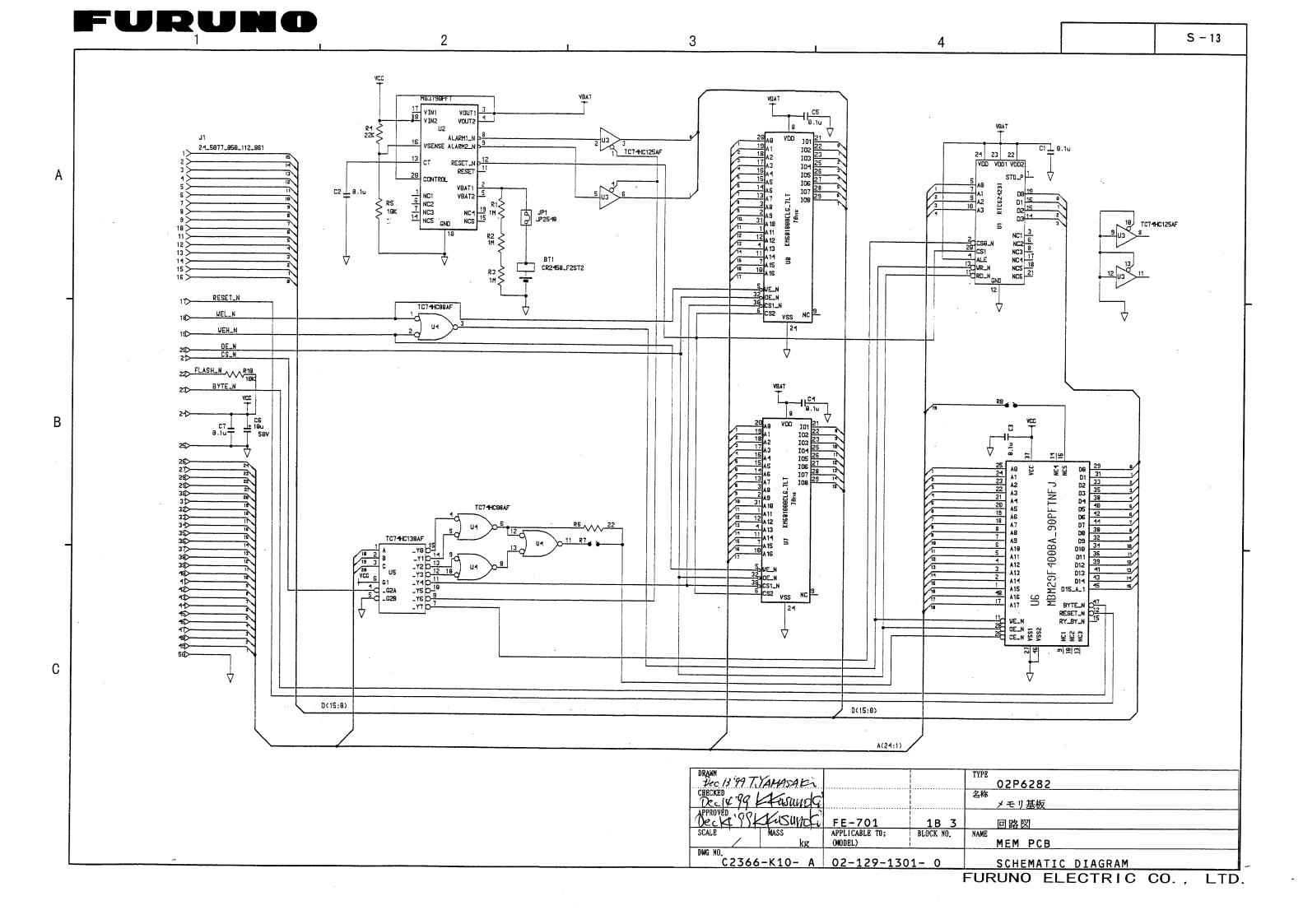

| MEM Board               | 1) Memorizes the depth and time for 24 hours.                                                     |  |  |

| (02P6282)               | 2) Contains a backup battery and a clock circuit.                                                 |  |  |

|                         |                                                                                                   |  |  |

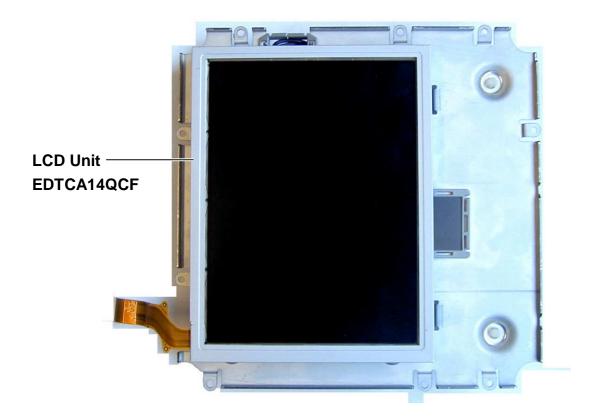

| Color Display           | Consists of an LCD and a cold cathode tube for LCD backlighting.                                  |  |  |

| (EDTCA14QCF)            |                                                                                                   |  |  |

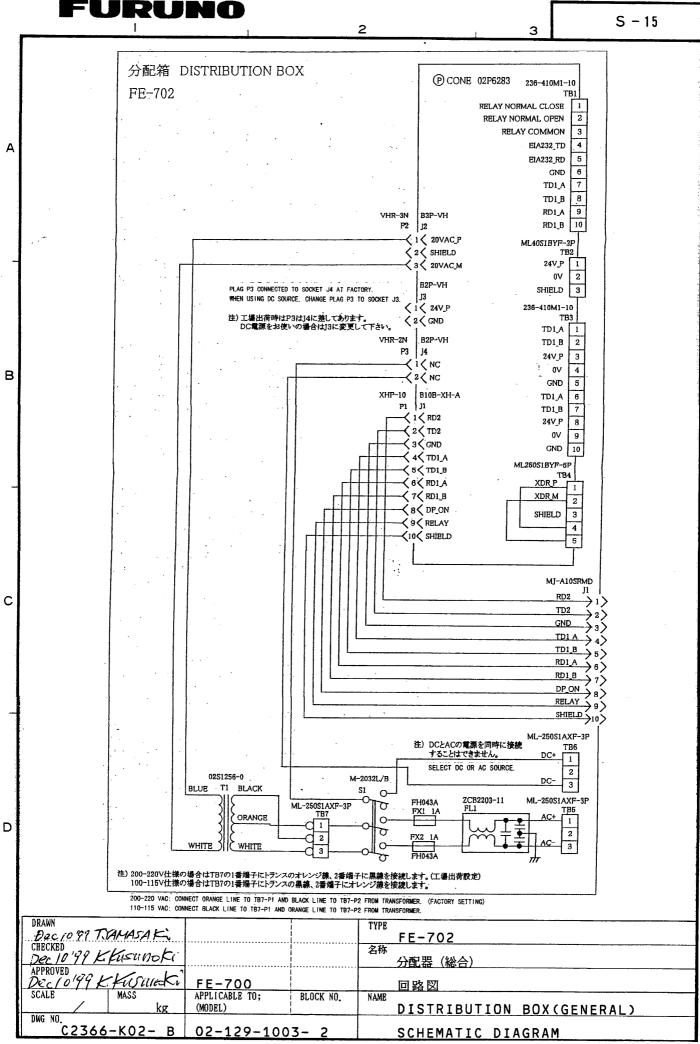

## **Distribution Box (FE-702**)

| Board/Unit | Functions                                                                |  |  |

|------------|--------------------------------------------------------------------------|--|--|

| CONE Board | 1) Interfaces the I/O signal between the Display Unit and External Unit. |  |  |

|            | 2) Converts 100/115/200/230 VAC to 24 VDC for the Display Unit.          |  |  |

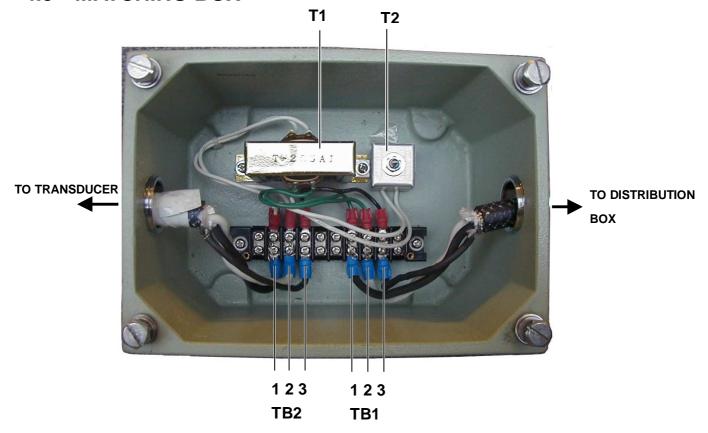

## Matching Box (MB-502/MB-504)

Matches impedance between transmitter/receiver and transducer.

## Transducer Switching Box (EX-8)

Selects the transducer to be used.

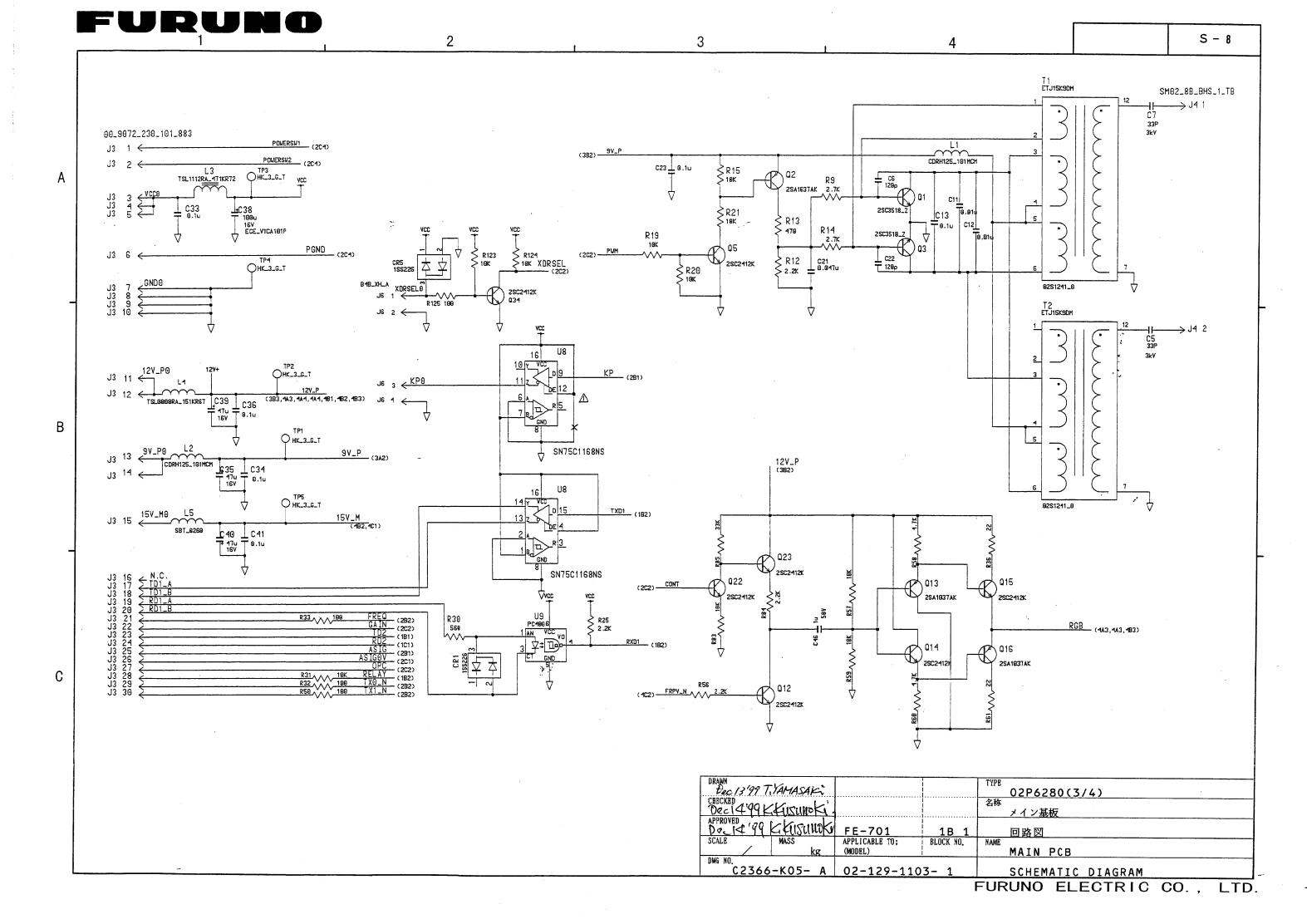

## 1.3 POWER SUPPLY

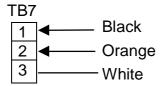

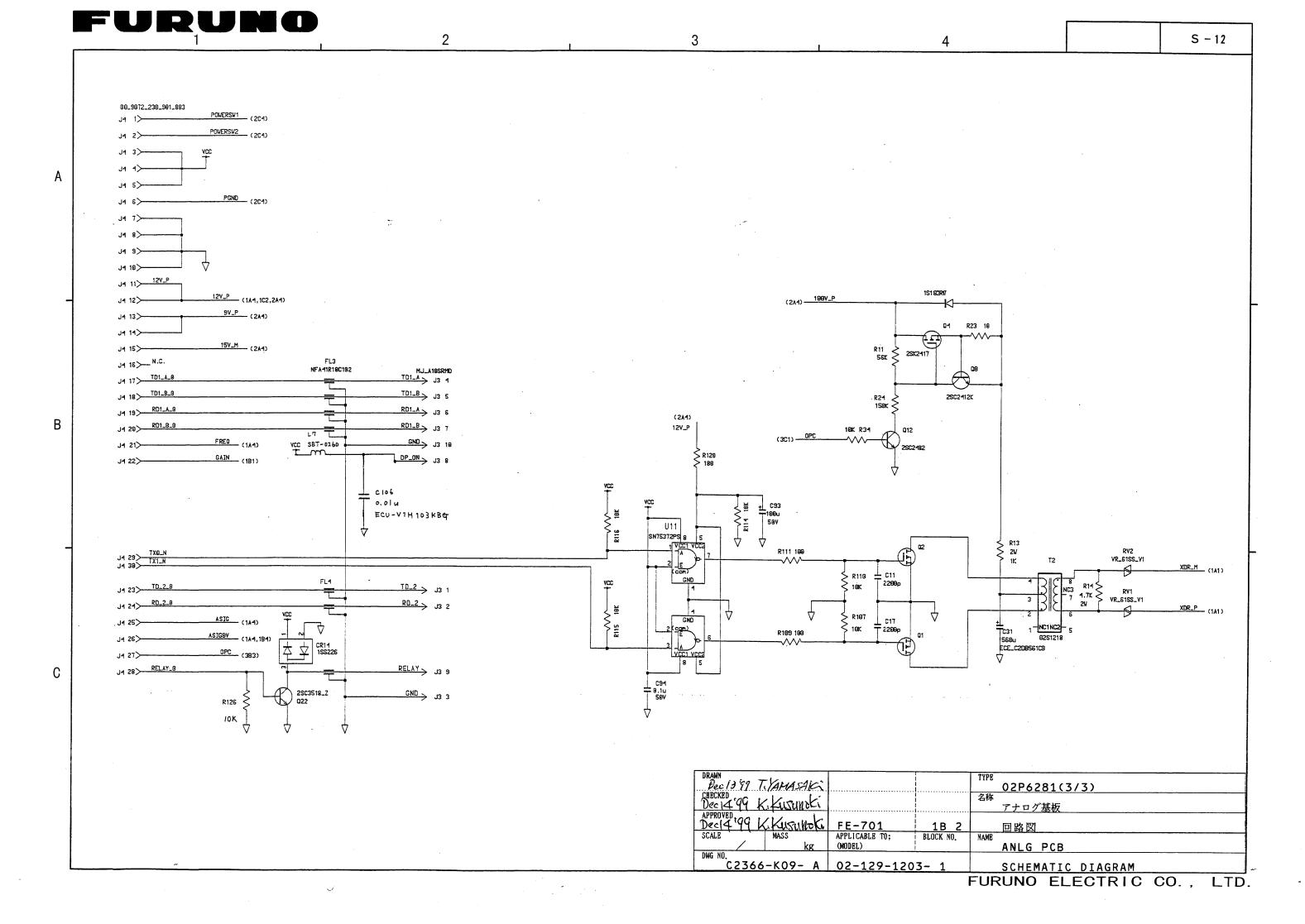

Either 24 VDC or 100-115/200-230 VAC ship's mains is connected to the Distribution Box.

The connection on TB7 must be changed depending on ship's mains, as follows.

1) When ship's main is 100 to 115 VAC;

2) When ship's main is 200 to 230 VAC;

Figure 1.2 Connections on TB7

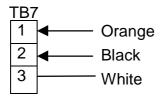

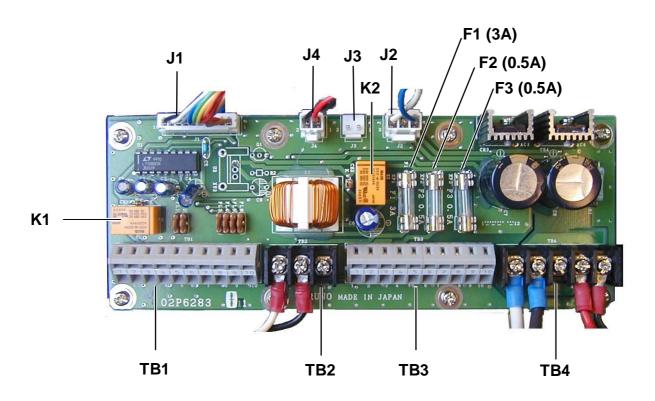

The AC supply voltage is converted to 24 VDC on the CONE board in the Distribution Box and supplied to the Display Unit and the Digital Depth Indicator.

The DP-ON signal (+5V) from the ANLG board activates the relay K2 on the CONE board in the Distribution Box, and then the 24 VDC is supplied to the Digital Depth Indicator through relay K2. See Figure 1.3.

Fig. 1.3 Power circuit on the CONE board

## **Switching Regulator Circuit**

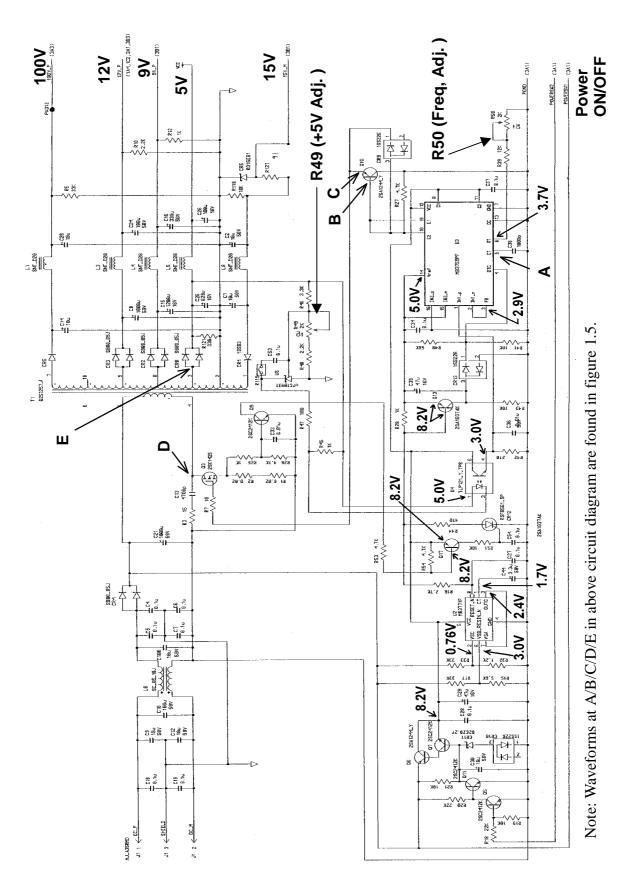

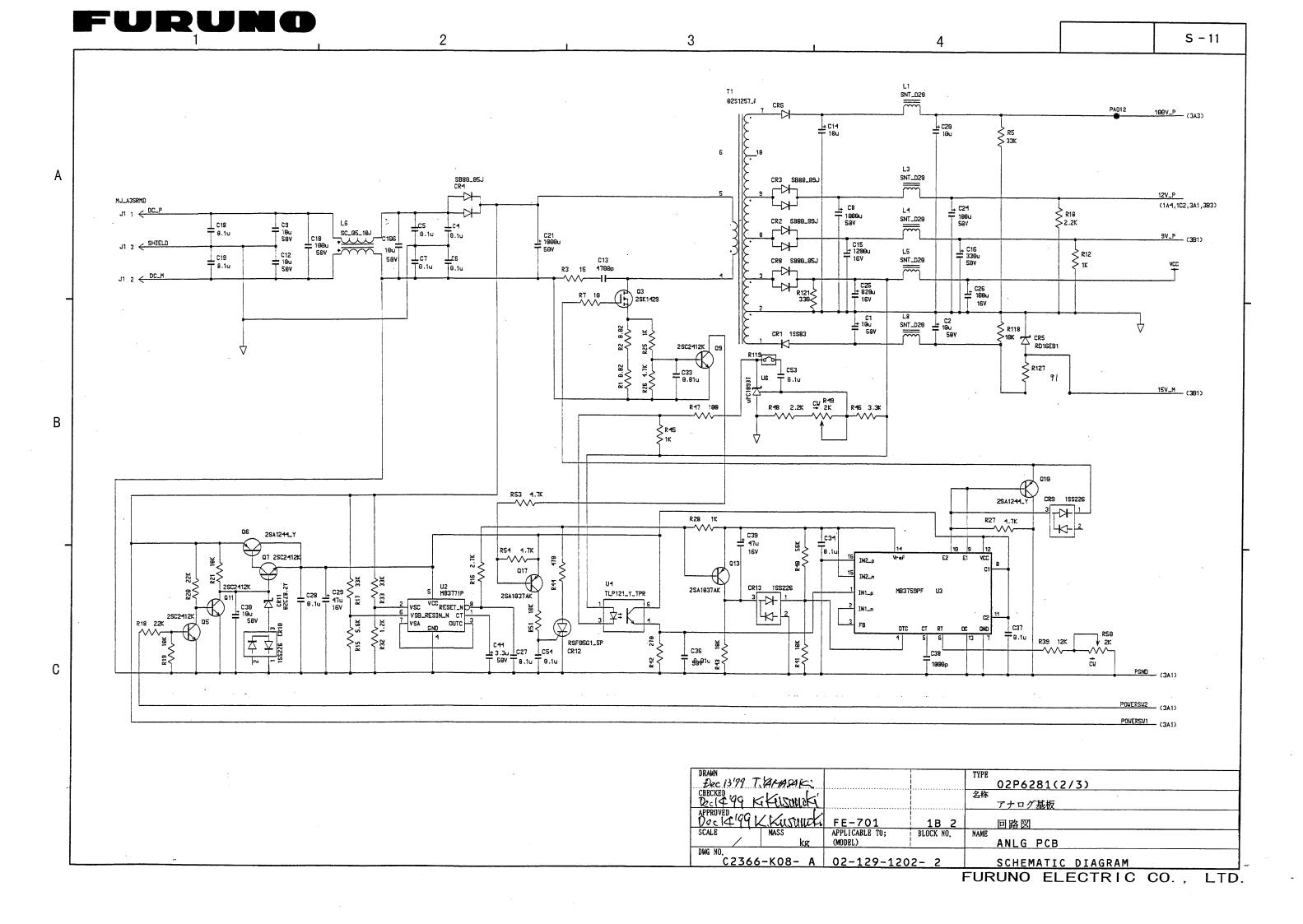

The switching regulator on the ANLG board generates 100~V for TX amplifier, 9~V for LCD inverter and 15/12/5~V for other circuits.

Figure 1.4 Switching regulator circuit on the ANLG board

Figure 1.5 Waveforms at A/B/C/D/E on the switching regulator circuit.

## 1.4 TRANSMISSION CIRCUIT

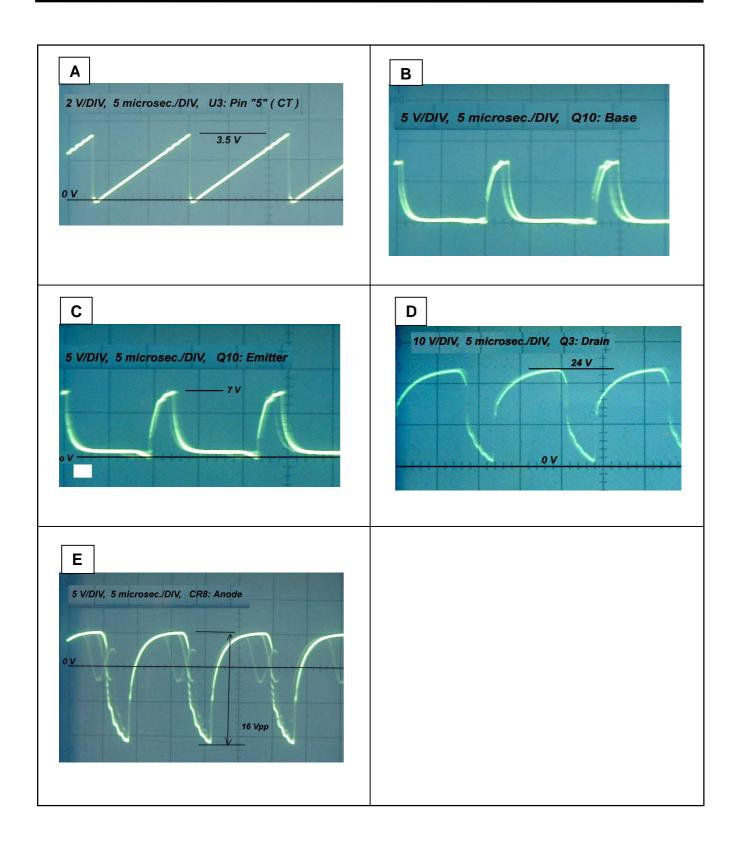

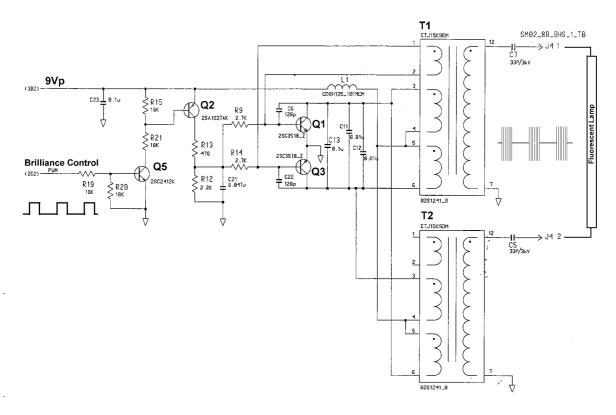

The transmission amplifier circuit is commonly used for both frequencies, 50/200 kHz. The transmission frequency is set on the System Menu 3. Transmission carrier signal "TX0/TX1" are generated by Gate Array U10 on the MAIN board 02P6280 and supplied to the TX driver circuit. Figure 1.6 shows the transmission amplifier circuit.

Figure 1.6 Transmission Circuit on the ANLG Board

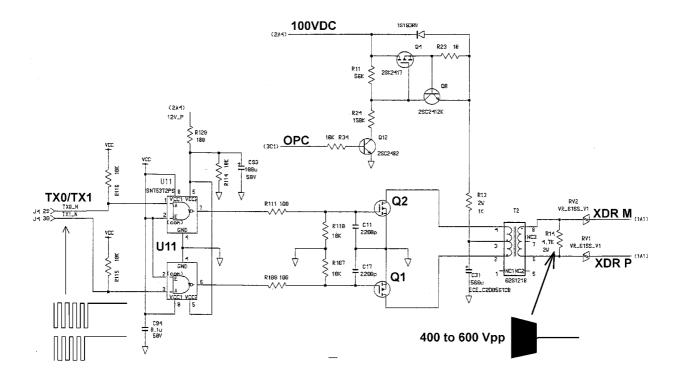

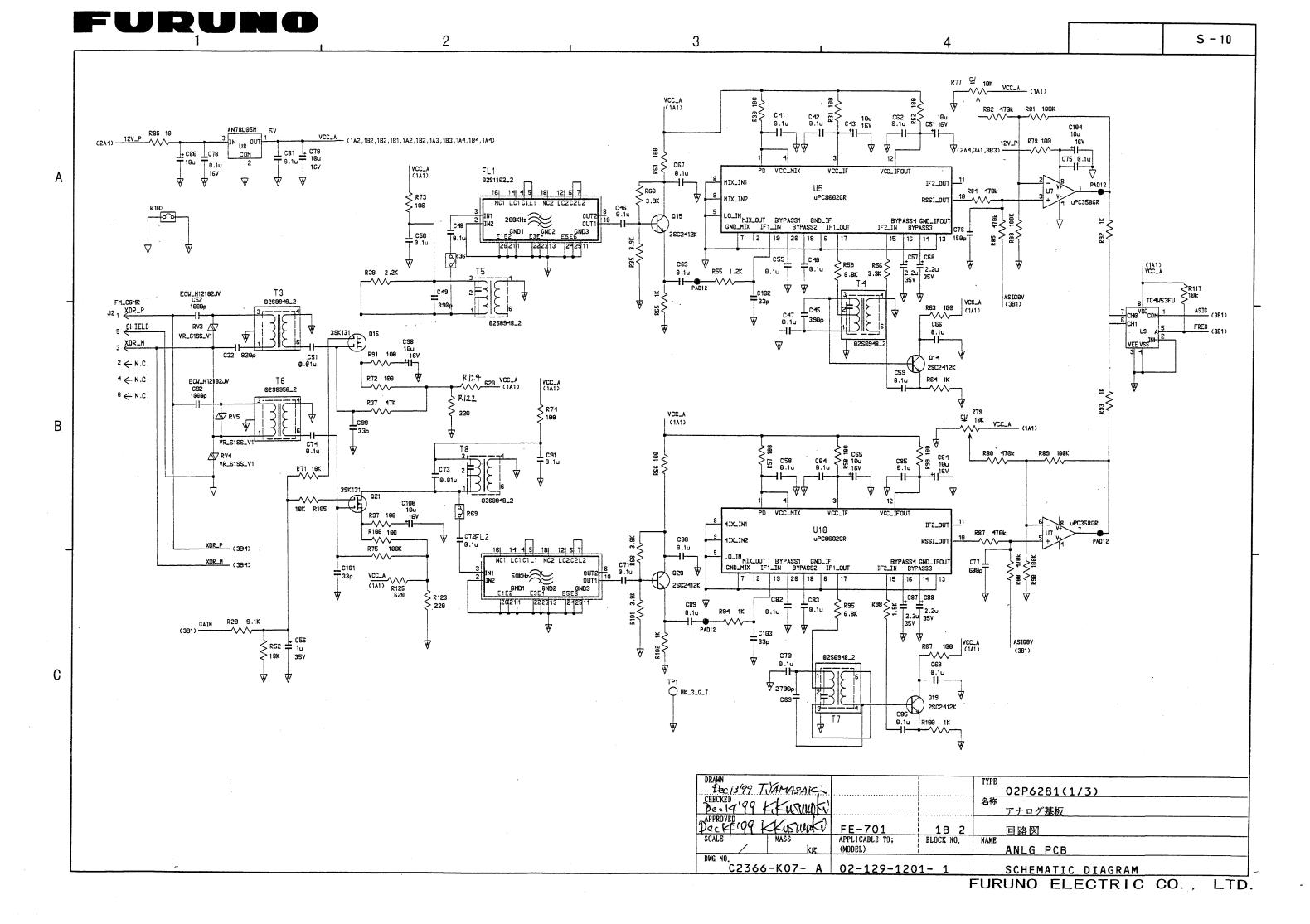

## 1.5 RECEIVING CIRCUIT

The received signal is amplified by the Log Amplifier Circuit. Both 200 and 50 kHz RX circuits are located on the ANLG board and the one of RX circuits is selected by U9 in accordance with the System Menu 3 setting.

Figure 1.7 shows the receiving amplifier circuit.

Figure 1.7 Receiving amplifier circuit on the ANLG board

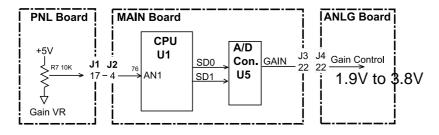

#### **Gain Control Circuit**

Figure 1.8 shows the gain control circuit. The gain VR setting is detected by the CPU as binary code data "000 to 255" which is converted to DC gain control voltage by the A/D converter U5. The gain control voltage ( 1.9 to 3.8V ) controls the amplitude of Q16/Q21 in the receiving circuit.

Figure 1.8 Gain control circuit

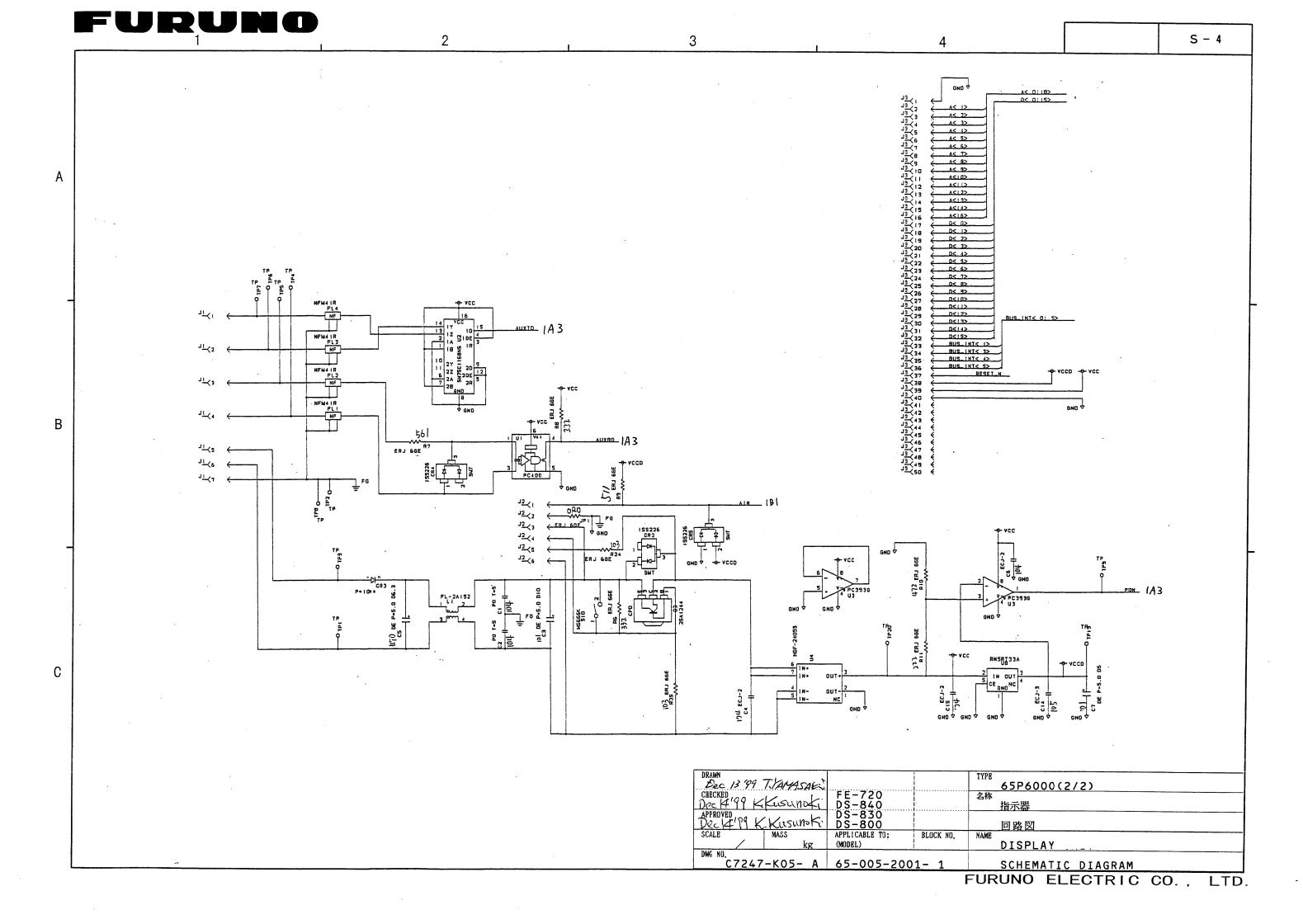

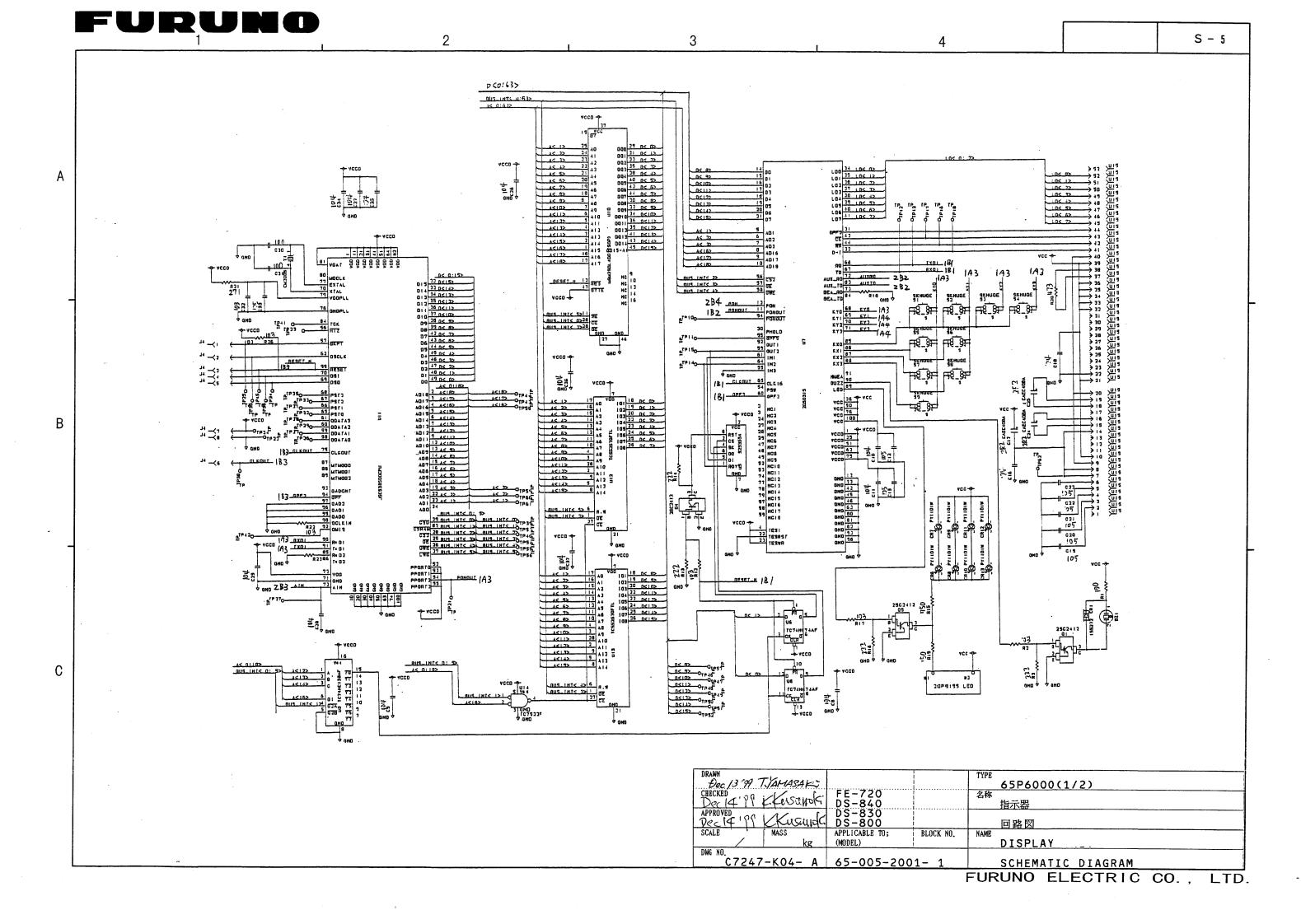

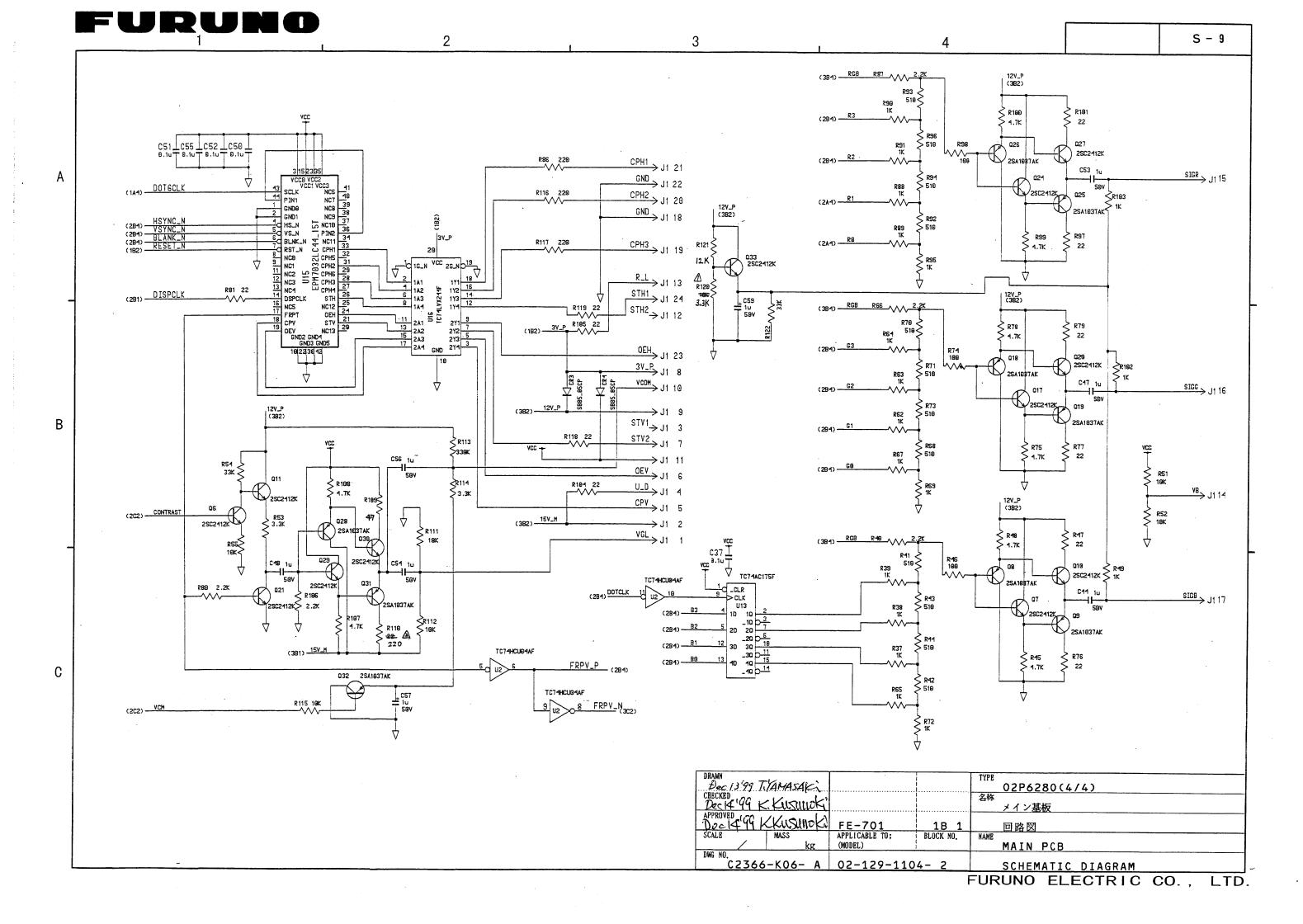

## 1.6 DISPLAY

The TFT LCD module is employed for the presentations. The control circuit and fluorescent lamp for backlighting are molded in the LCD unit "EDTCA14QCF". The life of the fluorescent lamp is approx. 20,000 hours if it is used with max. brightness.

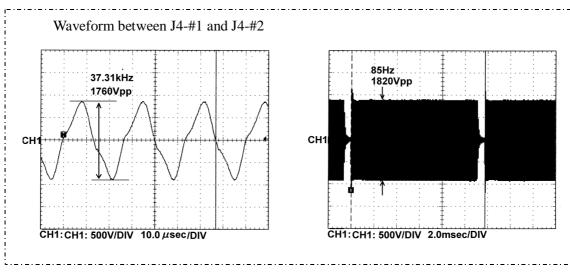

High voltage for LCD backlighting is generated on the MAIN board and is outputed from J4-#1 and #2 to the LCD unit. Figure 1.9 shows the LCD inverter circuit. The output level between J4-#1 and #2 is approx. 1.6 to 2.0kVpp when LCD unit is connected.

Figure 1.9 LCD inverter circuit on the MAIN board

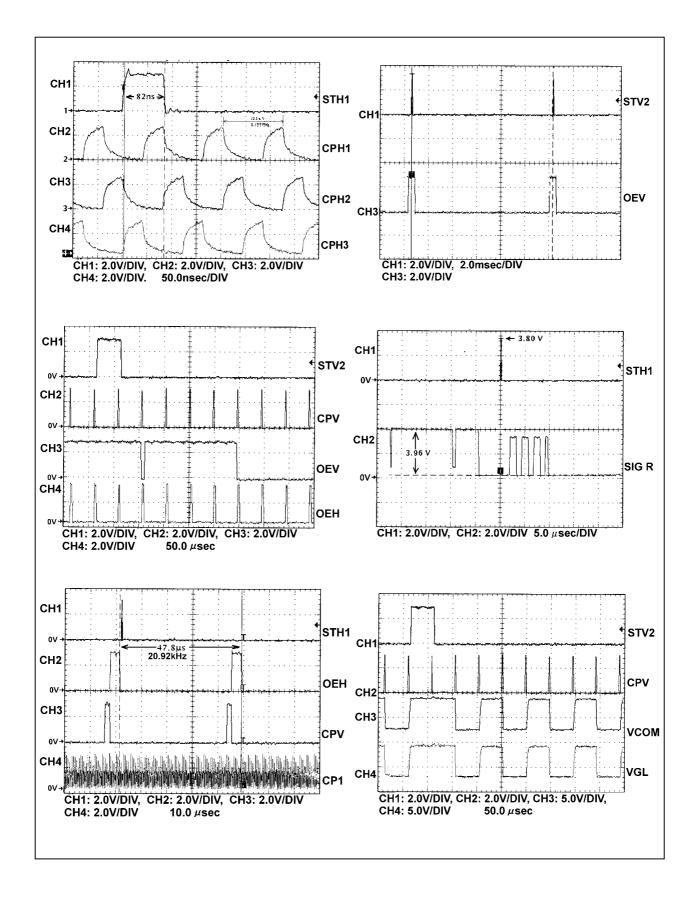

# I/O Signals of LCD Module

| Pin | Signal | Specification/Function                                                          |  |  |

|-----|--------|---------------------------------------------------------------------------------|--|--|

| 1   | STH1   | Source Driver Start Pulse 1 (When RL is High)                                   |  |  |

| 2   | OEH    | Pulse for switching the output current of the Source Driver                     |  |  |

| 3   | Q2H    | Control signal for switching the Video Data for the Source Driver               |  |  |

| 4   | CPH1   | Source Driver Sampling Pulse 1                                                  |  |  |

| 5   | CPH2   | Source Driver Sampling Pulse 2                                                  |  |  |

| 6   | CPH3   | Source Driver sampling Pulse 3                                                  |  |  |

| 7   | GND    | 0 V                                                                             |  |  |

| 8   | BLUE   | Video Signal (Blue)                                                             |  |  |

| 9   | GREEN  | Video Signal (Green)                                                            |  |  |

| 10  | RED    | Video Signal (Red)                                                              |  |  |

| 11  | VB     | Controls buffer current of Source Driver Output                                 |  |  |

| 12  | RL     | +3V ( change left/right shift direction )                                       |  |  |

| 13  | STH2   | Source Driver Start Pulse 2                                                     |  |  |

| 14  | VEE    | Positive source voltage (+5V) for the Source Driver                             |  |  |

| 15  | Vcom   | Applied voltage for facing electrode(amplitude changes with brightness control) |  |  |

| 16  | VGH    | +12V for the Gate Driver                                                        |  |  |

| 17  | VDD    | +3V for the Source Driver and Gate Driver                                       |  |  |

| 18  | STV2   | Gate Driver Start pulse 2                                                       |  |  |

| 19  | OEV    | Selects the output of the Gate Driver ( H: VGL output )                         |  |  |

| 20  | CPV    | Clocked pulse for the Gate Driver                                               |  |  |

| 21  | UD     | -15V (change upper/lower shift direction)                                       |  |  |

| 22  | STV1   | Not Used                                                                        |  |  |

| 23  | VSS    | Negative source voltage( -15V ) for Gate Driver                                 |  |  |

| 24  | Vgoff  | Gate Off voltage (The level is changed by Brightness Adjuster)                  |  |  |

Figure 1.10 Output Waveforms from LCD interface circuit

# **Chapter 2. Maintenance**

# 2.1 ADJUSTMENT

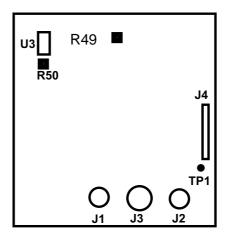

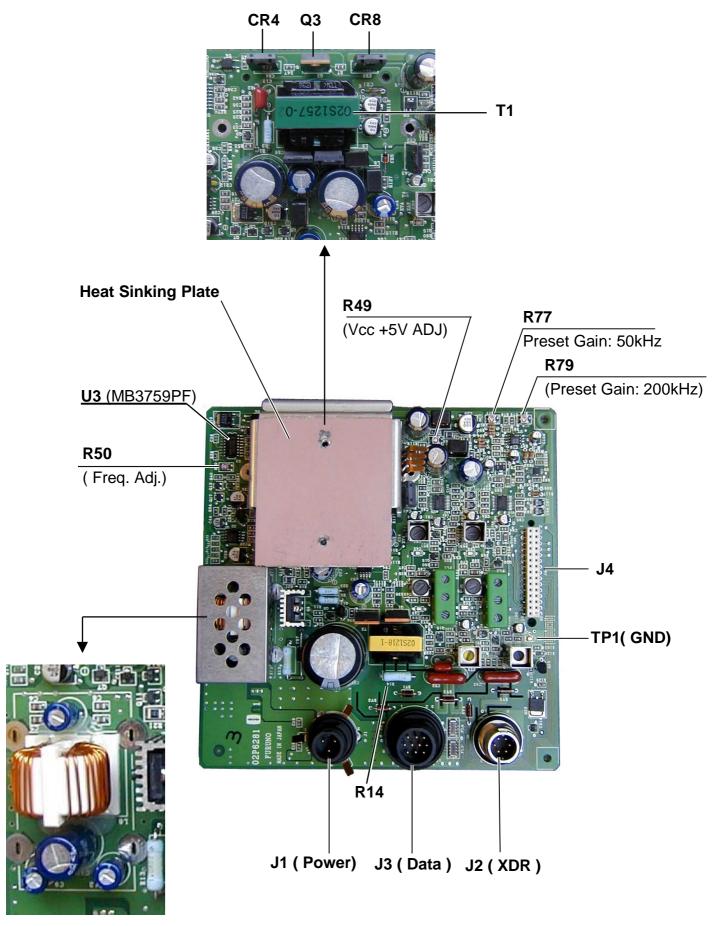

#### **ANLG** board

|                     | Measuring Point          | Ratings       | Adjuster        |

|---------------------|--------------------------|---------------|-----------------|

| Vcc (+5V)           | J5, #3 and GND ( TP1 )   | +5±0.02 V     | R49, ANLG Board |

| Switching frequency | U3,#9 and U3, #7 ( GND ) | 83.4~83.8 kHz | R50, ANLG Board |

Figure 2.1 Adjuster on the ANLG board

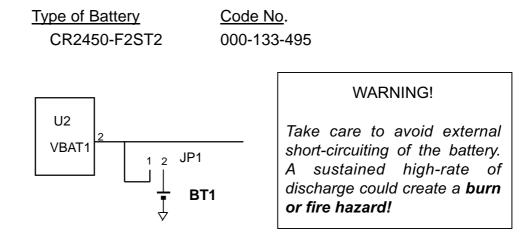

## 2.2 REPLACEMENT OF LITHIUM BATTERY

The battery on the MEM board must be replaced when the low battery alarm appears on the display.

Note: Before removing the battery, disconnect JP1.

Figure 2.2 Memory Backup Circuit on the MEM board

# **Chapter 3. Troubleshooting**

## 3.1 DIAGNOSTIC TEST

## **Function Test**

Function test is performed by the following key operation.

- 1. Press the POWER key while pressing any key.

- 2. Release the key when the optional mode selection display appears.

- 3. Press the [ ] key to select the TEST.

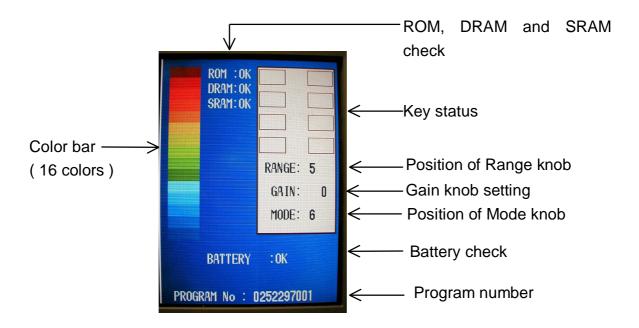

The following display appears.

Figure 3.1 Test Screen

## ROM, DRAM, SRAM and Battery check

The ROM, DRAM, SRAM and internal battery are checked and the results are displayed as OK or NG. If NG appears, following devices are suspected to be defective.

ROM NG: U14 of the MAIN board

DRAM NG: U16 of the MAIN board

SRAM NG: U7/U8 of the MEM board

Battery NG: Battery (BT 1) of the MEM board

#### **Key status**

Press and release each key (except the POWER switch) one by one. If the key is normal, its on-screen location lights in black while the key is pressed.

If some abnormal condition obtained, the PANEL and MAIN board are suspected to be defective.

## Range, Gain and Mode knobs

Operate the controls. The RANG and MODE control setting indications should be the same as actual control settings. The GAIN control setting indication should be among 0 to 235-255.

If some abnormal condition is obtained by controlling the RANGE and MODE knobs, the PANEL or MAIN board ( Gate array U10 ) is suspected to be defective.

If some abnormal condition is obtained by controlling the GAIN knob, the PANEL or U1 (CPU) of MAIN board is suspected to be defective.

## **Test Pattern**

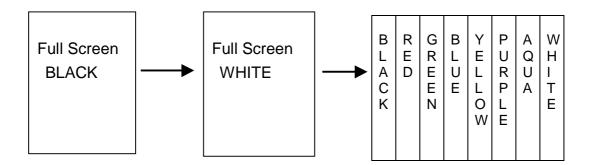

Self-test is performed by the following key operation.

- 1. Turn on the power while pressing any key.

- 2. Press the BRILL key three times. Press the BRILL key again to change the test pattern as below.

Figure 3.2 Test pattern

The "Full Screen BLACK/WHITE" checks the pixels of LCD.

The eight color gradation checks the R.G.B signals of LCD interface circuit on the MAIN board.

## 3.2 CLEARING THE MEMORY

To clear all data in the memory, follow the steps below. Factory settings are restored after this operation.

- 1. Turn on the power while pressing any key. Release the keys when the optional mode window appears.

- 2. Press the [▲] key. The following window appears.

Restore factory settings.

[+]:YES [-]: NO

3. Press the + key to clear the memory. The following display appears while data is being cleared;

Set data to default.

4. After cleared, the OPTIONAL MODE menu appears.

## 3.3 ALARM AND ERROR MESSAGE

When the Lithium Battery voltage becomes less than 2.66V, "LOW BATTERY ALARM" message is displayed on the screen in red.

When the IEC61162 data is interrupted, "EPFS ERROR" message is displayed on the screen in red. The EPFS ERROR message is displayed only when DATA 1 screen of OS DATA display is selected.

When the depth becomes shallower than the set range, "SHALLOW DEPTH ALARM" message is displayed on the screen and the alarm sounds.

# 3.4 INSPECTION OF EACH BOARD

| Board/Unit : MAIN board (02P6236) |        |                                                  |              |                                                                                                                  |  |

|-----------------------------------|--------|--------------------------------------------------|--------------|------------------------------------------------------------------------------------------------------------------|--|

| Signal                            | In/Out | Measuring Points                                 | Measured by  | Rating/Remarks                                                                                                   |  |

| FREQ                              | Output | ANLG Board                                       | Oscilloscope | 50 kHz : [H]                                                                                                     |  |

|                                   |        | J4, #21 and GND                                  |              | 200 kHz : [L]                                                                                                    |  |

|                                   |        |                                                  |              | (L=0 V, H=5 V)                                                                                                   |  |

| TX0/TX1                           | Output | ANLG Board<br>J4, #29 and GND<br>J4, #30 and GND | Oscilloscope | TX0  TX1  Changes depending on range setting                                                                     |  |

|                                   |        |                                                  |              | <ol> <li>TX0 and TX1 have opposite phase each other.</li> <li>Frequency is equal to the TX frequency.</li> </ol> |  |

| KP                                | Output | MAIN Board<br>J6, #3 and J6, #4                  | Oscilloscope | Changes depending on range setting                                                                               |  |

| GAIN                              | Output | ANLG Board<br>J4, #22 and GND                    | Multimeter   | Changes according to gain setting  Setting [0]: about 1.9 V Setting [5]: about 3.1 V Setting [10]: about 3.8 V   |  |

| IEC61162<br>TD-A , TD-B           | Output | ANLG Board<br>J4, #17 and #18                    | Oscilloscope | about 1 sec  Changes depending on data                                                                           |  |

| Board/Unit : MAIN board (02P6236) |            |                                    |              |                                                                                              |

|-----------------------------------|------------|------------------------------------|--------------|----------------------------------------------------------------------------------------------|

| Signal                            | In/Out     | Measuring Points                   | Measured by  | Rating/Remarks                                                                               |

| Vcc                               | Power Line | J4, #3 and GND                     | Multimeter   | +5±0.02V                                                                                     |

| +12 V                             | Power Line | J4, #11 and GND                    | Multimeter   | +12.0±0.5V                                                                                   |

| +9 V                              | Power Line | J4, #13 and GND                    | Multimeter   | +9.0±0.3V                                                                                    |

| -15 V                             | Power Line | J4, #15 and GND                    | Multimeter   | -15.0± 0.5V                                                                                  |

| ASIG                              | Output     | J4, #25 and GND                    | Oscilloscope | Oscillation 5V Line Seabed Fish                                                              |

| Primary<br>Power                  | Power Line | Q6 Collector and J4,<br>#6 (P.GND) | Multimeter   | About 9V                                                                                     |

| TX-H<br>TX-C                      | Output     | Across R14                         | Oscilloscope | Connect XDR and put into water.  Shift: 0m Range: 200m  50kHz: 400~600Vpp 200kHz: 400~600Vpp |

|                                   |            |                                    |              |                                                                                              |

# **Chapter 4. Parts Location**

# **4.1 DISPLAY UNIT**

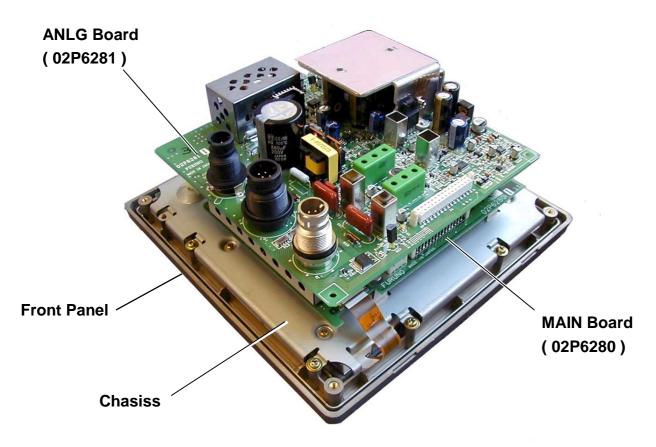

Figure 4.1 Parts Assembly

Figure 4. 2 Front Panel Assembly

Figure 4.3 LCD Unit

Figure 4.4 Front Panel

Figure 4.5 MAIN Board ( 02P6280 )

Figure 4.6 MEM Board ( 02P6282 )

Figure 4.7 PANEL Board ( 02P6250 )

Figure 4.8 ANLG Board ( 02P6281 )

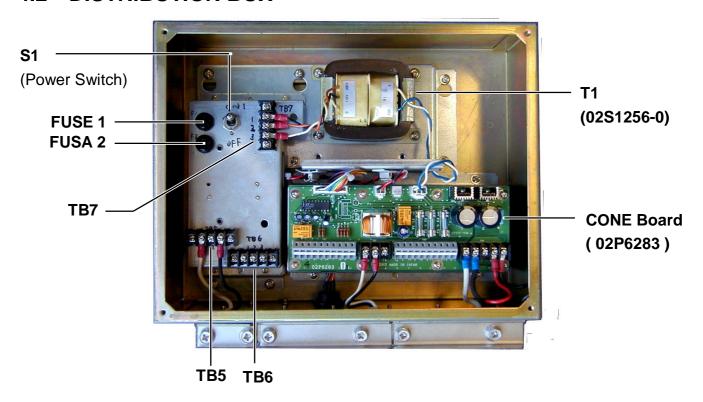

# 4.2 DISTRIBUTION BOX

Figure 4.9 Distribution Box (FE702)

Figure 4.10 CONE Board ( 02P6283 )

# 4.3 MATCHING BOX

| FREQ    | T1      | T2     | XDR     |

|---------|---------|--------|---------|

| 50 kHz  | T-203BJ | T-204B | 50B-6B  |

| 200 kHz | T-205AJ | T-206A | 200B-8B |

Figure 4.11 Matching Box (MB502)

# **4.4 SWITCH BOX**

Figure 4.12 Switch Box, Front View

Figure 4.13 Switch Box, Inside View

# Chapter 5. Digital interface (IEC 61162-1)

## 5.1 I/O SENTENCES

## Input

RMA, RMC, GLL, GGA, VTG, ZDA

## Output

DPT, DBS, DBT

## 5.2 SENTENCE DESCRIPTION

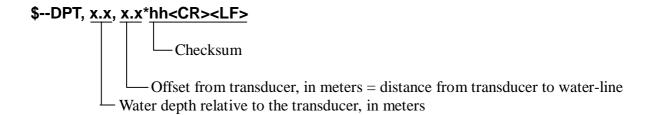

## **DPT - Depth**

1MG Resolution A.224 (VII). Water depth relative to the transducer and offset of the measuring transducer.

Positive offset numbers provide the distance from the transducer to the waterline. Negative offset numbers provide the distance from the transducer to the part of the keel of interest.

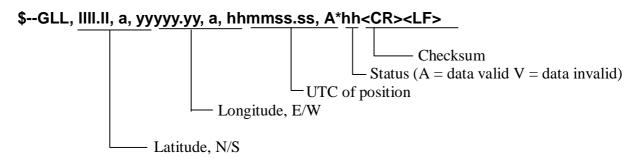

# **GLL - Geographic position - latitude/longitude**

Latitude and longitude of present vessel position, time of position fix and status.

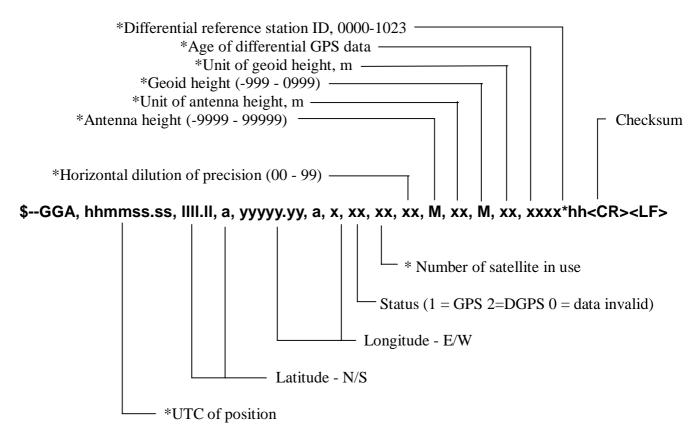

## GGA - Global positioning system (GPS) fix data

Time, position and fix related data for a GPS receiver.

\*: Not used

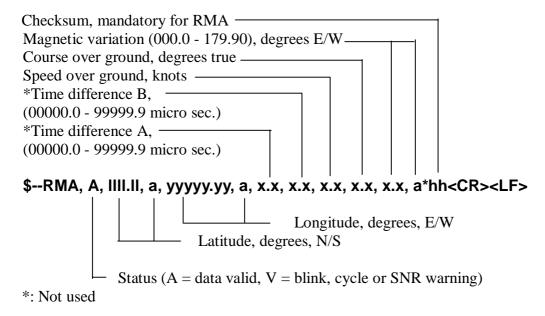

## RMA - Recommended minimum specific LORAN-C data

Position, course and speed data provided by a LORAN-C receiver. Time differences A and B are those used in computing latitude/longitude. Checksum is mandatory in this sentence. This sentence is transmitted at intervals not exceeding 2 s and is always accompanied by RMB when a destination waypoint is active. RMA and RMB are the recommended minimum data to be provided by a LORAN-C receiver. All data fields must be provided, null fields used only when data is temporarily unavailable.

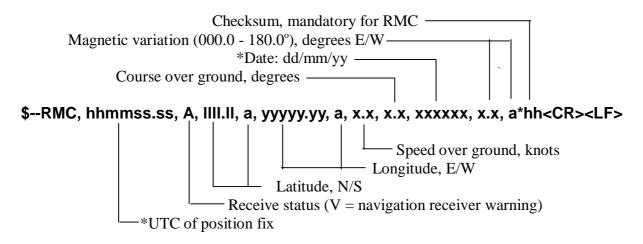

## RMC - Recommended specific GPS/TRANSIT data

Time, date, position, course and speed data provided by a GPS or TRANSIT navigation receiver. Checksum is mandatory in this sentence. This sentence is transmitted at intervals not exceeding 2 s and is always accompanied by RMB when a destination waypoint is active. RMC and RMB are the recommended minimum data to be provided by a GPS or TRANSIT receiver. All data fields must be provided, null fields used only when data is temporarily unavailable.

<sup>\*:</sup> Not used

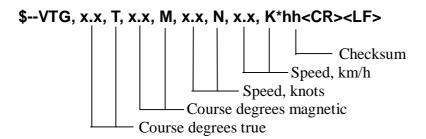

## VTG- Course over ground and ground speed

The actual course and speed relative to the ground

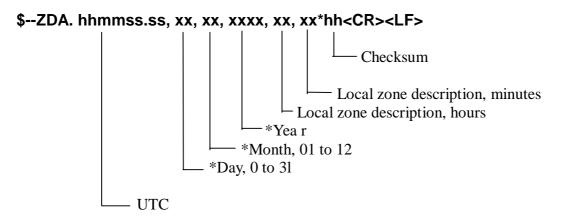

## **ZDA - Time and date**

UTC, day, month, year and local time zone.

\*: Not used

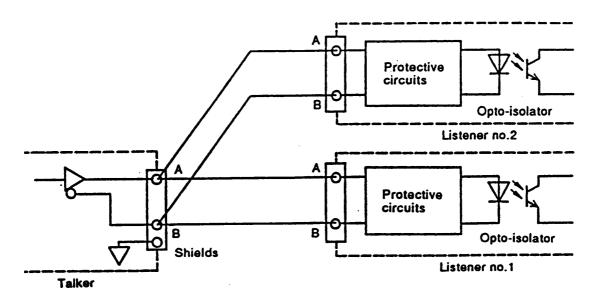

Figure 5.1 Input and output circuit

## PARTS LIST

| UNIT   | NAME                          | TYPE       | CODE NUMBER |

|--------|-------------------------------|------------|-------------|

| FE-701 | MAIN Board Assembly(MAIN/MEM) |            | 001229190   |

|        | MAIN Board                    | 02P6280    | 001229200   |

|        | MEM Board                     | 02P6282    | 001229220   |

|        | ANLG Board                    | 02P6281    | 001229240   |

|        | PNL Board                     | 02P6250    | 001389720   |

|        | LCD                           | EDTCA14QCF | 000142777   |

| FE-702 | CONE Board                    | 02P6283    | 001229030   |

CHASSIS ASSY. (000-808-933)

(000-806-246)

APR 17 -2000 DWG. NO. F. MI TO SHI

DRAWN

В

D

C2366-E01-A

(000-806-407)

CKS-05-L

(000-570-251)

ML-250-C-5P

(000-142-772)

APR . 14 . 2000

I. MI (754)

DRAWN

DWG. NO.

C2366-E02-A

| APPROVED | MAY. 8. 2000<br>Takenha shi   | TITLE  | 深度表示器                   |

|----------|-------------------------------|--------|-------------------------|

| CHECKED  | APR · 28 · 200,<br>TAKA HASHI | FE-720 | DIGITAL DEPTH INDICATOR |

|          |                               |        | C2366-E03-B             |

## FURUNO

電気部品表

**ELECTRICAL PARTS LIST**

2000年 4月

| Model    | FE-701/FE-720                    |      |  |

|----------|----------------------------------|------|--|

| Unit     | Unit 指示器/深度表示器                   |      |  |

|          | DISPLY UNIT/DIGITAL DEPTH INDICA |      |  |

| Ref.Dwg. | C2366-K01-A                      | Page |  |

| Blk.No.  |                                  | E-1  |  |

| SYMBOL | ТҮРЕ                  | CODE No.    | REMARKS        | SHIPPABLE<br>ASSEMBLY |

|--------|-----------------------|-------------|----------------|-----------------------|

| 回路記号   | 型式                    | コード番号       | 備考             | 出荷単位組品                |

|        | PRINTED CIRCUIT BOARD | プリント基板      |                |                       |

|        | 02P6281, ANLG         | 001-229-240 |                | Х                     |

|        | 02P6282, MEM          | 001-229-220 |                | Х                     |

|        | 02P6280, MAIN         | 001-229-190 |                | Х                     |

|        | 65P6000, ICP          | 002-889-330 | FE-720         |                       |

|        | PANEL ASSEMBLY        | パネル組品       |                |                       |

|        | FE-701                | 001-229-370 | w/PNL 02P6250付 | X                     |

|        | COVER                 | カバー組品       |                |                       |

|        | FE-701                | 001-229-340 |                | X                     |

|        | LCD                   | LCD         |                |                       |

|        | EDTCA-14QCA           | 000-142-777 |                |                       |

|        | CABLE w/CONNECTOR     | コネクタ付ケ-     | - ブル           |                       |

|        | 65S1227               | 000-142-659 | MJ-PH, 6P      |                       |

|        | 65S1228               | 000-142-660 | MJ-PH, 7P      |                       |

## FURUNO FE-702 Model Unit 分配箱 電気部品表 DISTRIBUTION BOX **ELECTRICAL PARTS LIST** C2366-K02-B Ref.Dwg. Page 2000年 4月 E-2 Blk.No. SYMBOL TYPE **REMARKS** CODE No. SHIPPABLE **ASSEMBLY** 回路記号 型式 コート・番号 備考 出荷単位組品 PRINTED CIRCUIT BOARD プリント基板 02P6283,CONE 001-229-030 Χ **POWER ASSEMBLY** 電源組品 FE-702 001-228-980 Χ **TRANSFORMER** トランス T1 02S1256-0 000-142-779 **SWITCH** スイッチ M-2032L/B 000-474-351 **FILTER** フィルタ ZCB2203-11 FL1 000-128-847 **FUSE** ヒューズ F1 **FGMB 1A 250V** 000-142-771 F2 **FGMB 1A 250V** 000-142-771 **FUSE HOLDER** ヒュース・オルタ・ー FX1 FH043A 000-138-885 FX2 FH043A 000-138-885 **TERNINAL BOARD** 端子台 TB5 ML250S1AXF-3P 000-142-535 TB6 ML250S1AXF-3P 000-142-535 TB7 ML250S1AXF-3P 000-142-535 **JACK** ジャック MJ-A10SRMD 000-126-663 **CABLE W/CONNECTOR** コネクタ付ケーブル 02-1001 (2P) 001-228-800 **VH CONNECTOR** 02-1002 (R10-10P) 001-228-860 **MJ-XH CONNECTOR**

FURUNO ELECTRIC CO., LTD.

FURUNO ELECTRIC CO., LTD.