# Development of a VHDL Generator for Scheduled Data Flow Graphs

**MASTER THESIS**

submitted by

HAGEN STÜBING

# **Honour declaration**

Hereby I assure that the presented thesis was made without any help of third persons and only with the indicated sources and means. All the figures and paragraphs taken from the sources are clearly marked.

Darmstadt, 21.11.2006

### **Preface**

The presented work is created in contents of a master thesis that I have prepared for the "Universitat Politecnica de Catalunya" in Spain. At the "Technical University of Darmstadt" this thesis is submitted as a "Studienarbeit".

The thesis consists of three parts. The enclosed CD-Rom contains the VHDLGenerator program with the corresponding installation files as well as the source code. The documentation of the VHDLGenerator Program is the paper at hand. For quick reference a user manual is available. The user manual is a copy of the most important notes, helpful when starting to work with VHDLGenerator.

The structure of this thesis is closely related to the execution order of the program. The development of the VHDLGenerator program required knowledge of different fields of programming. For streaming the text files you have to know the Java streaming concepts, while the VHDLGenerator error detection is based on Java exception handling. Because the output file is written in a hardware description language (VHDL) one has to deal with the constraints of hardware design. Furthermore the theoretical background of minimization algorithms has to be understood in order to realize the Left Edge Algorithm that is used for register minimization. So as heterogeneous as the knowledge base is, as heterogeneous is the structure of this thesis. The different topics are addressed in the order they are executed inside the VHDLGenerator program.

Every chapter is related to one working step of VHDLGenerator. It always starts with a general explanation and theoretical background of a used concept and then explains how the theory is adapted to the specific case.

Hagen Stübing

Contents

# **Contents**

| Ho  | nour (  | declarat | ion         |                                         | IV   |

|-----|---------|----------|-------------|-----------------------------------------|------|

| Pre | eface . |          |             |                                         | V    |

| Co  | ntents  |          |             |                                         | VI   |

| Lis | st of F | igures   |             |                                         | VIII |

| 1   | Intro   | duction  | 1           |                                         | 1    |

| 2   | The     | Data Fl  | ow Graph    | Presentation                            | 4    |

|     | 2.1     | Data F   | Representa  | ation Form                              | 4    |

|     | 2.2     | Graph    | s in gener  | al                                      | 5    |

|     | 2.3     | Task C   | Graphs      |                                         | 6    |

|     | 2.4     | Data F   | low Grap    | hs                                      | 8    |

|     | 2.5     | HCDN     | 1 in gener  | ral                                     | 8    |

|     | 2.6     | HCDN     | I Gramma    | ar                                      | 9    |

|     | 2.7     | HCDN     | I and Data  | a Flow Graphs                           | 11   |

| 3   | The     | Data Fl  | ow Graph    | Compiler                                | 12   |

|     | 3.1     | Comp     | iler in gen | eral                                    | 12   |

|     | 3.2     | The Pa   | arser stage | ·                                       | 14   |

|     |         | 3.2.1    | Parser T    | heory                                   | 14   |

|     |         | 3.2.2    | The HCl     | DM Parser                               | 15   |

|     |         |          | 3.2.2.1     | Java streaming concepts in general      | 15   |

|     |         |          | 3.2.2.2     | Parsing inside VHDL Converter           | 16   |

|     |         |          | 3.2.2.3     | Parsing the HCDM file                   | 18   |

|     |         |          | 3.2.2.4     | Parsing the Scheduling File             | 22   |

|     |         |          | 3.2.2.5     | Parsing the Components File             | 22   |

|     | 3.3     | The Pi   | eConverte   | er stage                                | 23   |

|     |         | 3.3.1    | Sorting of  | of the Tasks                            | 23   |

|     |         | 3.3.2    | Register    | Optimization                            | 27   |

|     |         | 3.3.3    | Error-de    | tection and recovery techniques         | 33   |

|     |         |          | 3.3.3.1     | Java Exception handling in general      | 35   |

|     |         |          | 3.3.3.2     | Exception handling inside VHDLGenerator | 37   |

|     | 3.4     | The C    | onverter s  | tage                                    | 42   |

|     |         | 3.4.1    | The VH      | DL Code Generator                       | 42   |

Contents

|     |       | 3.4.2 The VHDL Testbench Generator            | 44          |

|-----|-------|-----------------------------------------------|-------------|

|     |       | 3.4.2.1 Testbenches in general                | 44          |

|     |       | 3.4.2.2 Testbench creating for VHDL           | Converter44 |

| 4   | The   | Graphical User Interface                      | 47          |

|     | 4.1   | Java Swing vs. AWT                            | 47          |

|     | 4.2   | The Model-View-Controller Architecture in Jav | ya48        |

|     | 4.3   | The VHDLGenerator GUI                         | 50          |

|     | 4.4   | GUI Reference Manual                          | 52          |

| 5   | Cone  | clusions                                      | 56          |

|     | 5.1   | The Test Program                              | 56          |

|     | 5.2   | Simulation Results                            | 60          |

|     | 5.3   | Synthesis Results                             | 65          |

| App | pendi | x A                                           | 68          |

| App | pendi | x B                                           | 71          |

| Ref | erenc | ces                                           | 81          |

List of Figures VIII

# **List of Figures**

| Figure 1: proposed Design Flow                              | 2  |

|-------------------------------------------------------------|----|

| Figure 2: Task Graph example                                | 6  |

| Figure 3: HCDM Task Graph example screenshot                | 7  |

| Figure 4: Data Flow Graph example                           | 8  |

| Figure 5: Task description in HCDM                          | 10 |

| Figure 6: Model of a classical compiler                     | 12 |

| Figure 7: Model of the Data Flow Compiler                   | 13 |

| Figure 8: State Chart expressions                           | 17 |

| Figure 9: Parser State Chart                                | 18 |

| Figure 10: Task declaration inside HCDM                     | 19 |

| Figure 11: BNF description of Parser pattern                | 20 |

| Figure 12: Scheduling File example                          | 22 |

| Figure 13: Components File example                          | 23 |

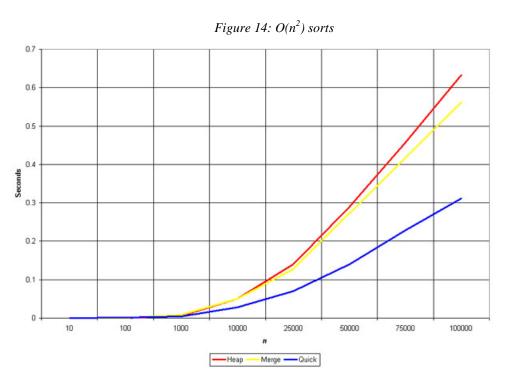

| Figure 14: O(n²) sorts                                      | 25 |

| Figure 15: O(n log b) sorts                                 | 25 |

| Figure 16: Quicksort pseudo code                            | 26 |

| Figure 17: Vertex Coloring pseudo code                      | 28 |

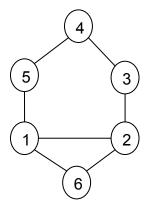

| Figure 18: Compatibility Graph                              | 29 |

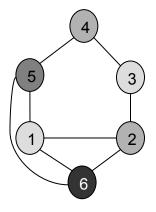

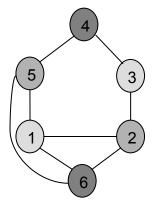

| Figure 19: Non-minimum Coloring Figure 20: Minimum Coloring | 29 |

| Figure 21: Left Edge pseudo code                            | 31 |

| Figure 22: Left Edge pseudo code for VHDLGenerator          | 33 |

| Figure 23: Error Level classification                       | 34 |

| Figure 24: Exception handling in Java                       | 36 |

| Figure 25: throw statement                                  | 36 |

| Figure 26: try-catch                                        | 37 |

| Figure 27: Error Type Reference                             | 41 |

| Figure 28: VHDL Testbench                                   | 44 |

| Figure 29: concatenating algorithm description              | 45 |

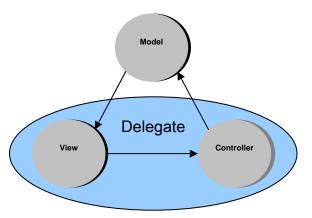

| Figure 30: classical MVC architecture                       | 49 |

| Figure 31: Swing MVC architecture                           | 49 |

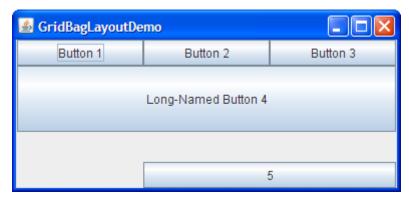

| Figure 32: GridBagLayout example screenshot                 | 50 |

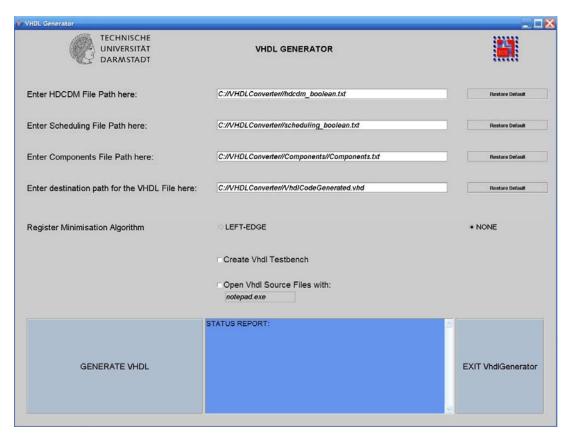

| Figure 33: VHDLGenerator GUI screenshot                          | 52 |

|------------------------------------------------------------------|----|

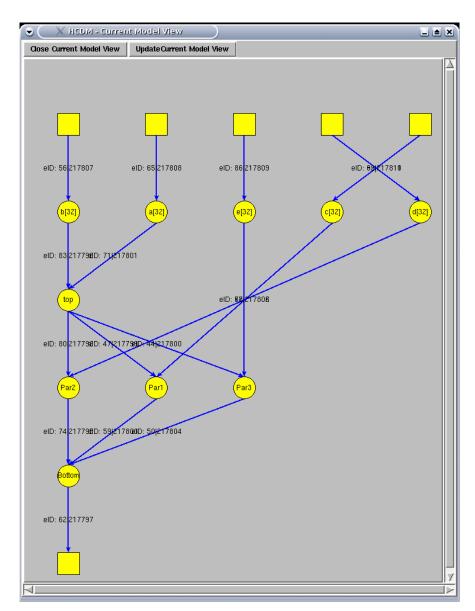

| Figure 34: HCDM Boolean DFG screenshot                           | 57 |

| Figure 35: HCDM description                                      | 59 |

| Figure 36: HCDM Boolean example scheduling                       | 60 |

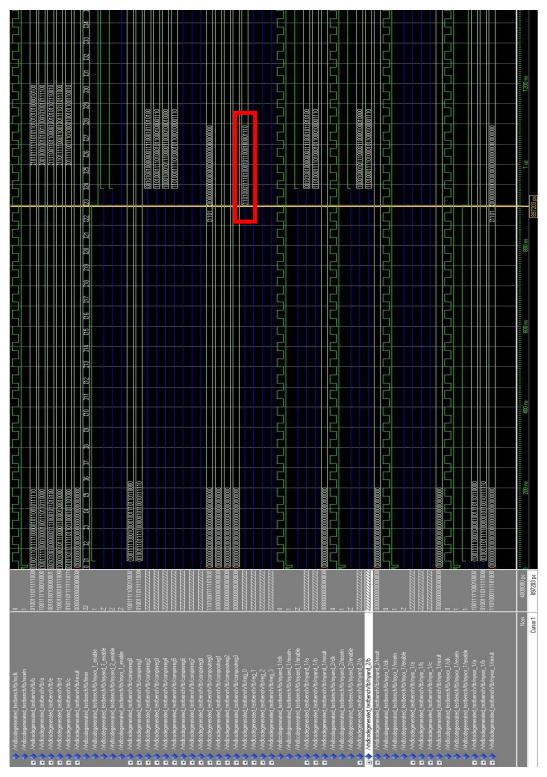

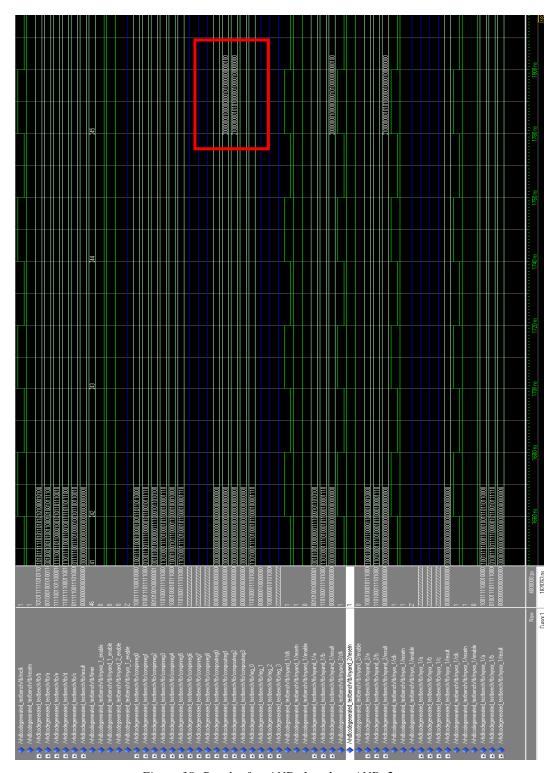

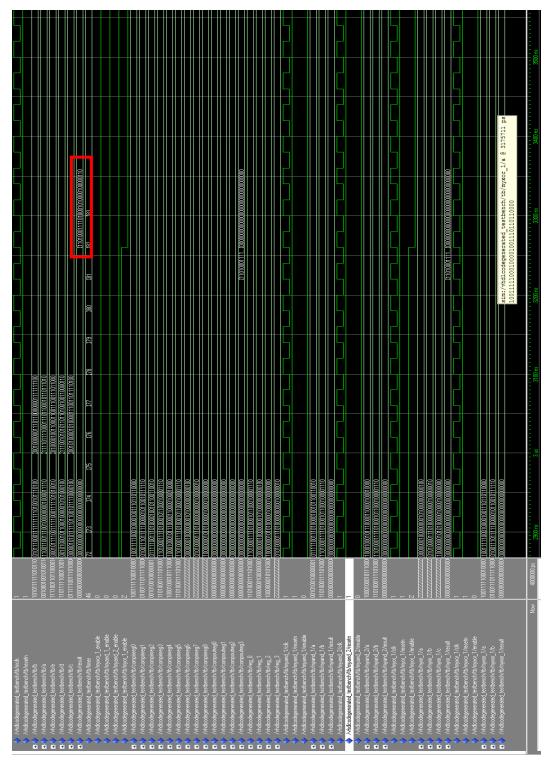

| Figure 37: Result of myXOR_1                                     | 61 |

| Figure 38: Result of myAND_1 and myAND_2                         | 62 |

| Figure 39: Figure 5.6: Final result of myOR_1                    | 63 |

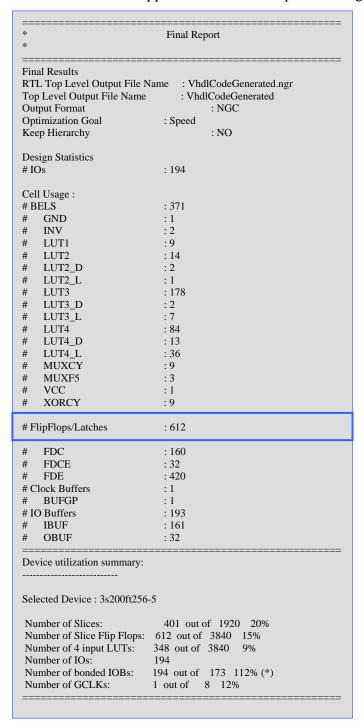

| Figure 40: Synthesis report without register                     | 65 |

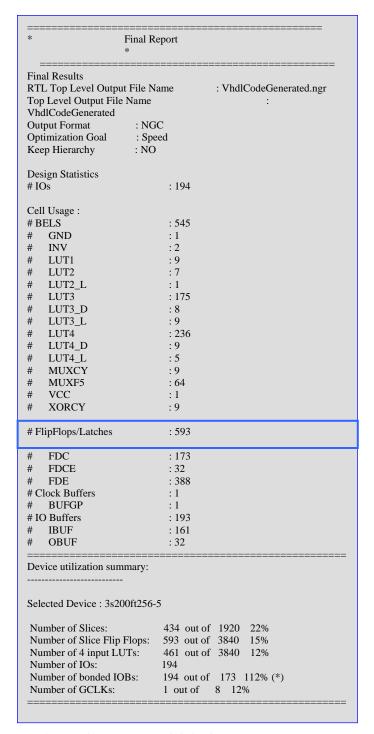

| Figure 41: Synthesis report with left edge register minimization | 66 |

| Figure 42: VHDL code without register minimization               | 67 |

| Figure 43: VHDL code with Left Edge register minimization        | 67 |

| Figure 44: complete VHDL code without register minimization      | 74 |

| Figure 45: complete VHDL code with register minimization         | 76 |

| Figure 46: The used XOR component                                | 77 |

| Figure 47: The used OR component                                 | 78 |

| Figure 48: The used AND component                                | 79 |

| Figure 49: The generated VHDL testbench                          | 81 |

Introduction page 1

# 1 Introduction

Common hardware design flows that are in use today, can not satisfy the correctness requirements of cryptographic applications, where an implementation error might violate the security. For this reason the *Faculty of Integrated Circuits and Systems* at the *Technical University of Darmstadt* started to develop a new design flow, appropriate for cryptographic applications. In contents of this work a VHDLGenerator is designed, which is part of that new developed hardware design flow. The objective of this VHDLGenerator is to convert a Data Flow Graph description into synthesizable VHDL code.

A central aspect of the design flow is the desired support for automated verification after code entry. Although it is aimed towards cryptography, most aspects can be adopted to other domains. We will discuss first how the new design flow looks like, and then we explain how this work is related to it. Finally the overall structure is explained.

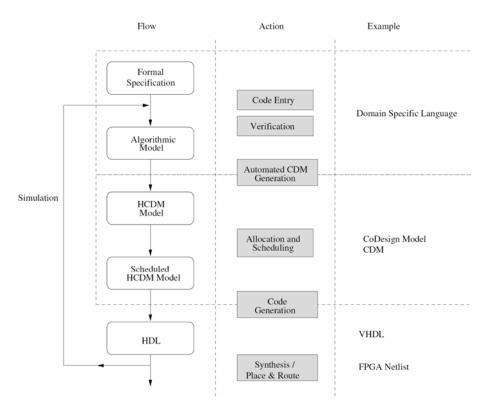

The proposed design flow is shown in Figure 1.1. The different design phases are represented in the left column. The middle column denotes the actions required in the corresponding design phase, while the right column gives concrete examples for each design phase.

Introduction page 2

Figure 1: proposed Design Flow

The first step consists of the Code Entry Phase. There the developer generates an algorithmic implementation in the design language. The implementation has to follow the requirements of a formal specification.

An automated verification tool is used to test the implementation against the specification given by the developer.

The next step in the design flow is an automated scheduling and allocation process. For this purpose the HCDM tool is used. The HCDM Generator is a tool that has been created by Stephan Klaus [1] in contents of a dissertation at the Technical University of Darmstadt. HCDM is used to describe data dependencies between different tasks in form of task graphs. Scheduling and resource allocation is done automatically. A more detailed description of the HCDM tool is given in chapter 2.

The last step of the design flow is the Code Generation. Right at this point starts the work of the implemented VHDLGenerator. Its purpose is exactly to parse the results of HCDM, i.e. the data flow graph together with the scheduling information and generate synthesizable VHDL source code.

Introduction page 3

When starting to design the VHDLGenerator program one has to partition the incidental converting work. It turned out to be of great advantage to introduce three different working stages.

The structure of this thesis mirrors directly the internal stages of the VHDLGenerator program. Composed out of three processing stages, the input is parsed, then pre-processed and finally converted to VHDL code. All three stages are written in Java [24].

The first stage parses the necessary files in order to extract all relevant information. The Parser stage is described in chapter 3.3.

The second stage is the PreConverter stage, described in chapter 3.4. This stage contains the *heavy weighted* methods that do most of the work. Register minimization, Exception handling and the setting of the case-statements are only some tasks that are handled by the PreConverter stage.

The third and final stage converts the pre-processed data to VHDL code. Because of the extensive work of the PreConverter, the methods of this stage are more *light weighted*. The VHDL generator stage is subject of chapter 3.4.

VHDLGenerator offers a fourth optional stage. Depending on the users settings a testbench for the converted VHDL code can be created. How the testbench is constructed is explained in chapter 3.4.2.

The VHDLGenerator usage is greatly simplified by creating a Graphical User Interface (GUI) that is presented in chapter 4.

To demonstrate the correct behaviour of VHDLGenerator a benchmark program is constructed. Chapter 5 tells how the test program and its results look like.

# 2 The Data Flow Graph Presentation

In the next sections it is explained why we use Data Flow Graphs to describe high level hardware applications. The background of graph theory is explained more in detail, than it would have been necessary for this chapter. But when it comes to explain Register Optimization this additional information will be helpful.

The HCDM tool is introduced as an easy and comfortable way to create task graphs. The basic differences between Task Graphs and Data Flow Graphs are described. It is explained how the Task Graphs, generated by HCDM, are manipulated in order to obtain Data Flow Graphs.

# 2.1 Data Representation Form

When generating VHDL code it is of great importance to use an appropriate representation form for implementation, that reflects the basic nature of hardware description languages. Hardware implementations allow for example parallel computation. So our chosen data representation form should support parallel structures also. And second, we target dataflow intensive algorithms. While this is a severe limitation in general, for HW implementations it is acceptable. The Control Flow is described implicitly by the presetting for scheduling and allocation inside HCDM.

Furthermore the representation form should be easy to extract by means of a parser.

Given the two criteria of parallel data representation and simplicity of extraction, a graph based description turns out to be the best solution. We will use Data Flow Graphs, which are a subtype of graphs that also allow representing external inputs and outputs. In fact Data Flow Graphs show similar characteristics as digital hardware components. In the DFG a task can only fire if all of its inputs are ready and, the scheduled component is free to process. In the same manner VHDL Components are constructed.

A general description of graph based data representation is following in the next section.

To cover our second goal of extraction simplicity the previous mentioned HCDM tool could be used. This tool allows drawing Task Graphs graphically via a GUI. It

generates automatically a textual graph description, which follows a well-defined grammar that could be used to construct a pattern for the parser. Moreover HCDM also includes timing aspects. It performs scheduling of different tasks on predefined resources. That issue covers the synchronisation aspect of common VHDL design. With respect to these aspects HCDM is considered to be an appropriate tool. The last sections of these paragraphs are dedicated to the HCDM tool.

## 2.2 Graphs in general

A graph G(V,E) consists of vertices V and its relations E. Vertices are often called nodes. The relations E are the edges between the vertices. Graphs can be categorized into two groups: directed graphs and undirected graphs.

Undirected graphs are graphs that express a slack relation between vertices with temporal order between them. A compatibility graph is a good example for an undirected graph. We will work with compatibility graphs in chapter 3.3.2 in context of register optimization.

A directed graph got a directed dependency between consecutive vertices. In short, a directed graph is an undirected graph but with a temporal order of its vertices. The HCDM Tool uses directed graphs.

Directed graphs can be used to represent procedural languages with imperative semantics. That means we want to express an algorithm with a language that takes care of the execution order. Calculation of one step is therefore based on results of the previous steps, which gives us a temporal order.

The representation of the calculation flow is done graphically in terms of its vertices (the tasks, represented as nodes) and its relations (the dependencies, represented as branches). The direction is indicated by drawing an arrow.

We discuss the differences between two types of sequencing graphs: the task graph and the data flow graph.

## 2.3 Task Graphs

The Task Graph is the one implemented forhe HCDM Generator. This sequencing

graph has only task vertices. That includes, that also the dependencies only relate tasks. Task Graphs have two important characteristics: They are acyclic and polar. Acyclic means that the graph includes a partial order between its tasks. Polar means that it got a source vertex at the beginning and sink vertex at the end of the graph. In the HCDM tool the source vertex and the sink vertex are joined to the Root task.

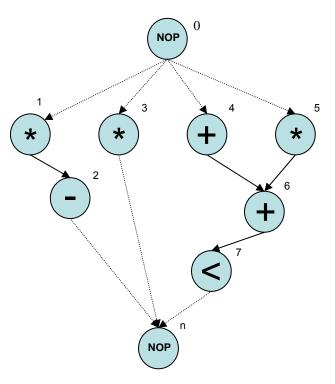

Figure 2: Task Graph example

This task does not implement any function but indicates the begin and the end of the graph. This fact will be important later when it comes to parsing of the tasks.

All the initial tasks are successors of the Root Task and all final tasks are predecessors of the Root Task. Figure 2.1 shows an example of a task graph.

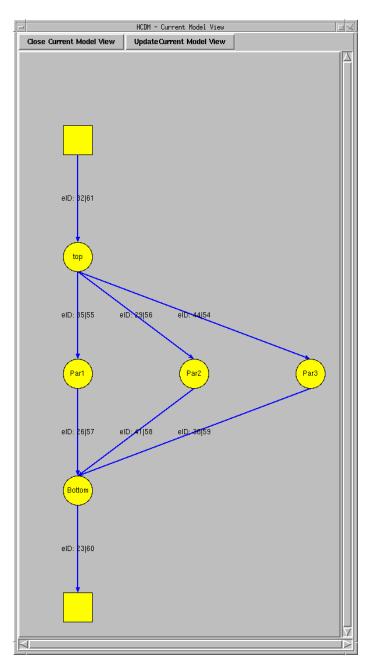

Corresponding Tasks graphs designed by HCDM could look like the example in Figure 2.2.

Figure 3: HCDM Task Graph example screenshot

## 2.4 Data Flow Graphs

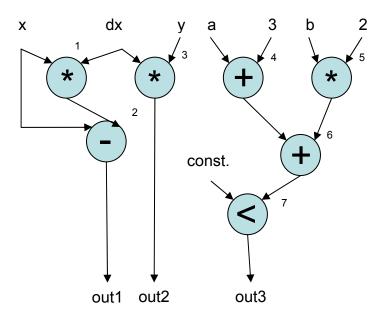

Compared to the Task Graph the Data Flow Graph (DFG) includes additional vertices. To every task in the graph possible external operators are appended. So a Data Flow Graph does not only give the data dependency between two consecutive tasks, but also the dependency of every task on external inputs.

Figure 4: Data Flow Graph example

The destination for the task result can be either another component or an external output port. So a Data Flow Graph could be considered as an extended Task Graph. Figure 2.3 shows an example of a Data Flow Graph.

# 2.5 HCDM in general

The HCDM tool implements a set of genetic algorithms to generate an optimal resource binding and scheduling for a set of allocated resources and a CoDesign Model (CDM). A CDM is an extended Task Graph Model.

The HCDM flow graph is basically described in terms of processes, their resources and the relations between them. Processes can be considered as tasks that run on a specified resource. A resource could be a physical component on which the process

runs. To every pair of process and resource and execution time is associated, which describes for which period of time the process is running on the resource. The different processes can be connected by branches. Branches represent data dependencies, i.e. a process followed by a second process connected by a branch indicates that the calculation of the second process is dependant on the results of the first process.

In that way a directed hierarchical graph for representing algorithms of any kind can be drawn. The Task Graph is entered graphically via a graphical user interface. From the graphical representation a text file is generated that represents the textual description of the graph. Note that the drawn HCDM data flow graph does only specify the data dependencies of the implementation. It does not contain a sequential ordering of the operations. The order is generated during the scheduling and does not require any further user interaction. The designer has to define the resources and the tool will generate a corresponding scheduling and allocation.

### 2.6 HCDM Grammar

HCDM produces two different output text files. One is a file with the textual description of the graph. The other text file describes the scheduling for the different tasks on the specified components. For parsing these two files later on, the meaning of the grammar of these two files is important.

The whole HCDM grammar and an example of a graph text file written with the HCDM grammar are added to the appendix of this thesis. For demonstration we state here an example of a task description written in HCDM. Further examples are following in the chapter on parsing.

```

TASK 14 {

NAME { Par2 }

OPTIMIZATIONTYPE { 1 }

IMPORTANCE { 1 }

FAILURE PROBABILITY { 0.5 }

LEVEL { -3 }

PRIORITY { -4 }

TIMING { 0 }

RESOURCES { (2,20 ) (5,20 ) }

IORELATIONS {

IORELATION {

INPUT { 84 181 }

OUTPUT { 78 }

CONDITION { true }

}

SUBTASKS {

}

```

Figure 5: Task description in HCDM

One can see that the graph description always starts with a declaration of the used resources. Shortly after, the tasks are defined. Each task contains several fields for setting task parameters. The HCDM grammar contains a PRIORITY field where the parameter for list schedul-ing has to be entered. Safety critical task can be marked inside the IMPORTANCE field. Furthermore the failure probability of a task can be taken into account inside the FAILURE\_PROBABILITY field. In the last section the relation between the tasks are de-fined. Tasks are connected over branch numbers inside IORELATION. These are all fields that are important for the original purpose of HCDM which is to perform scheduling and binding for embedded systems. When using HCDM for generating VHDL code most of these parameters will be ignored. In fact we only consider here the ones that are relevant for our VHDL conversion. More to this in the chapter on parsing.

The Scheduling File produced by HCDM is quite self-explanatory and does not really need a specified grammar. The first line defines the start time and stop time of every task. In the second line the binding of every task with its resource is stated.

## 2.7 HCDM and Data Flow Graphs

As mentioned before HCDM has been created to design Task Graphs. That means that the tool does not provide any methods to represent external operators, needed for the Data Flow Graph.

Without changing the HCDM program itself, it is still possible to adapt its functionality to create DFGs, which will be described next:

For creating the Task Graph, HCDM provides two graphical elements: Circles that represent the Tasks and directed branches that represent the data dependencies. If we want to represent external operators, the task circles could be used.

We use "pseudo" tasks to implement external inputs. External Inputs are defined as Tasks that are direct successors of the root task. We can identify them by comparing the branch numbers.

In quite the same manner the external outputs are simulated. Outputs are defined to be the last tasks inside the DFG. They have outgoing branches back to the root task, which is an adequate characteristic for filtering them out.

The name of the external operators is handed over the same name field as used for the task names (see HCDM grammar). In the later converted VHDL code these inputs also own a certain bit length.

Inside the HCDM grammar for the Task construct there are several possible fields where to hand over the data type. In principle it is possible to enter the bit length into any of the predefined Task fields like IMPORTANCE, LEVEL or TIMING that are not used for our DFG converting. Because of simplicity and particularly because of consistential reasons we decide to enter the bit length right behind the variable name, separated by brackets. That implies, that when parsing the Task NAME field to VHDL, the name itself and the bit length have to be separated and stored individually.

# 3 The Data Flow Graph Compiler

The nomination and structure that is applied to the VHDL Converter program is basically the same that is also used to describe the behaviour of a compiler for high level languages. In fact if we define a compiler accordingly to [5] as "a program that translates programs written in a high-level programming language into native machine language of a digital computer" the VHDL Converter can be considered as a compiler. In fact the program shows similar characteristics as a compiler and we will orientate on the principles of compiler construction.

# 3.1 Compiler in general

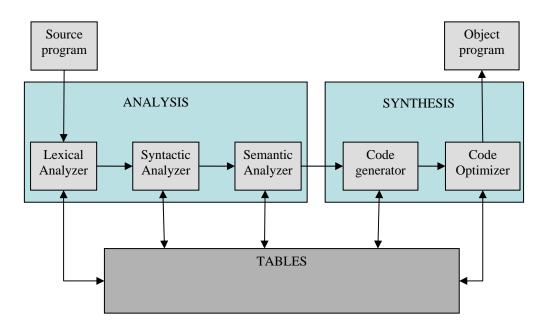

In the next section the basic components of a common compiler are stated. Figure 6 shows the model of a common compiler.

Figure 6: Model of a classical compiler

The compilation process is composed out of two parts: The analysis of the source program and the synthesis of its corresponding object program. During the analysis part the source program is fragmented into its basic parts and processed via a lexical, syntactic and semantic analyser. The pattern to distinguish between between keywords and relevant information are taken out of tables. The Lexical Analyzer needs tables to look up the Keyliterals, while the Syntactic Analyzer looks up the Keywords.

The extracted raw material is forwarded then to the synthesis which builds the equivalent object program modules.

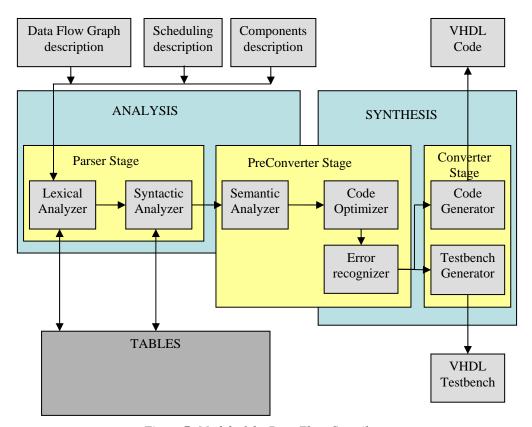

For our VHDLGenerator program we orientate on that classical compiler model. Thereby the basic structure is kept the same to some extend. Figure 7 shows the adjusted compiler model for VHDLGenerator.

Figure 7: Model of the Data Flow Compiler

As it can be seen, instead of one source program, we receive three text files that need to be extracted. In the drawing the analyzers are related to the Java classes in which they are executed. The boxes in beige indicate the membership to each class. Before the VHDL Code is generated an output register optimisation is performed via Left Edge algorithm in the code optimization phase during the PreConverter stage. Possible errors are detected and printed out. Optional a testbench could be generated. In the following we will explain more in detail how the different stages work.

### 3.2 The Parser stage

In this section the design of the HCDM parser will be developed. First an introduction to parsing theory is given, where the different concepts and term declarations are explained. It is shown how these concepts are applied to the actual problem. A state chart diagram is developed to demonstrate the behaviour of the implemented Java Parser.

## 3.2.1 Parser Theory

In general parsing is defined as a process that analyzes a given sequence of literals and tries to extract the desired information according to a predefined grammar. That is the so called syntax analysis. Before the information could be analyzed, the given sequence needs to be sampled literal by literal, to extract the keywords.

The elementary operation of every syntax analysis is called *lexical analysis*. The lexical analysis got as an input the literal sequence of the to be parsed data. It identifies literals that belong together and passes them as *Lexemes* one layer up to the syntax analysis.

The *syntax analysis* then uses the given grammar to figure out the meaning of every Lexeme and the relation between adjacent Lexemes.

So a Parser can be thought of having two layers that work in parallel. On the first layer a *Lexemer* scans the input sequence and produces valid Lexemes. To distinguish between two successive Lexemes the Lexemer needs to know the predefined separation literals. Separation literals can be set for example as white space or closing braces. According to *Maximal Munch Rule* literals are assembled until such a separation literal appears.

On the second layer a *Tokenizer* absorbs the Lexemes and produces tokens according to the grammar. Tokens are considered to be a pair of Lexemes. First Lexeme indicates the token type and second the token value. In most cases these two Lexemes are consecutive in the parsed text. The tokens are stored for further processing.

If we pick up the idea of seeing the VHDLGenerator as a Complier there has to be a third stage following, the semantic analysis. During this step the actual meaning of the collected tokens is determined and an intermediate form of source code is generated. The semantic analysis is done inside the PreConverter class and will be explained in the following sections.

#### 3.2.2 The HCDM Parser

The implemented HCDM Parser is orientated on the previously introduced parser theory. We only make some slight changes in the nomenclature for the parser program code. Instead of naming the assembled literals as *Lexemes* they are named as *Words*. For the documentation we will use both synonyms.

Furthermore it is not possible to run the two processes for *Syntax Analysis* and *Lexical Analysis* in parallel as it is recommended. That is basically due to the fact that Java is interpreted sequentially. So we need to serialize the two processes. How the serialization is realized can be seen from the state chart below.

To convert the Data Flow Graph into synthesizable VHDL code the necessary information from three text files has to be parsed. Before we come to discuss the parser itself, basic concepts of streaming text files in Java need to be explained.

## 3.2.2.1 Java streaming concepts in general

In order to parse, the available data has to be serialized previously. This means, we need to find a method to read the data in and give it out literal by literal. In our case the data will be at text file and a literal will be a single char value.

Java offers the possibility to handle data in form of streams that means to read and create streams. A stream can be considered as a batch of data on its way from some source to some specified destination. The big advantage is, that we can abstract from the kind of data that is streamed. That way the destination process does not have to care about where the stream comes from and the source process does not have to take care where the string is going to. In our case we are parsing from a text file into a storage variable of type Array List.

All inputs and outputs in Java are realized as streams. To use streams the package java.io.\* has to be included. The streams descend all from a common abstract class. The class *InputStream* implements the interface *Reader*. *OutputStream*

implements the interface *Writer*. All classes that inherit from one of the two classes provide the basic same functionality.

The class *Reader* offers interfaces to open, read and close files. The class *InputStreamReader* and *StringReader* implement that interface. For our purpose we will use these two classes and another subclass called *FileReader*, which inherits from *InputStreamReader*, to read the text files produced by HCDM. To create and read streams with these classes is quite simple. If the path of the file is given to the constructor of FileReader, the file is opened in the read modus automatically. If the opening fails, a FileNotFoundException is thrown. So the method call always has to be placed inside a *try-catch* block. More on the topic error and exception handling in section 3.3.3.

Within a loop the method read() applied to the FileReader object returns the text, sampled character by character. The return value is of type *int* and typeasted to *char*. This will be the smallest data unit the parser will work with. According to parser theory this single char value is nominated as *Literal*.

Inside the Parser code it will not only be necessary to parse a whole text file but also to parse tokens out of a string. For this issue we use an instance of the class StringReader. A string can be streamed in the similar way as a file.

The Parser only absorbs information out of text files and therefore we only need instances of type Reader. But later on it will be required to stream the converted VHDL code back into a text file. The output streaming in Java is done simultaneously as for the input stream. The used instance is of type FileWriter and implements the interface Writer. Like previously, the full path of the destination file is handed over by the constructor. The method write() appends a given string to the end of the text. The call has to be done inside a *try catch* block.

## 3.2.2.2 Parsing inside VHDL Converter

To construct the VHDL Code basically three different text files need to be parsed: The HCDM file that describes the tasks, ports and the hierarchical relation between them. The scheduling file sets start and stop times for the tasks and how they are bind to the components. The scheduling is necessary because we are dealing with limited resources. We also need to know which components are available and how their interface looks like. This information is contained in the components file.

The parsing procedure is quite the same for every text file of the three, so we will explain it only once. First it is explained how the parsing is realized in general. Second, the information we want to extract out of every file is stated.

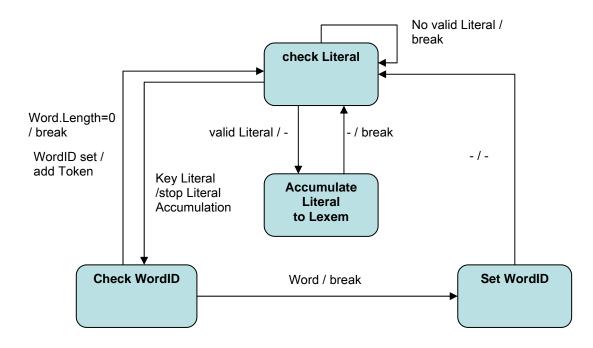

The parsing process can be explained in terms of a deterministic finite state machine that is shown in figure 9. To understand the state chart some explanation of the expressions needs to be given:

| Expression         | Meaning                                                             |  |

|--------------------|---------------------------------------------------------------------|--|

| valid Literal      | a literal that is a possible part of a Lexeme (word)                |  |

| KeyLiteral         | A literal that determines the end of a Word                         |  |

| Word               | Lexeme                                                              |  |

| Word_ID            | Stores the meaning of the consequent Lexeme to built the token pair |  |

| not-relevant Lexem | Lexeme that is not part of a Token                                  |  |

| KeyWord            | First Lexeme of a Token (indicates the type of the token)           |  |

Figure 8: State Chart expressions

The program enters into the *checkLiteral* state every time a new literal is pushed out of the stream.

If the current literal is not a *valid* literal, that means not a KeyLiteral or part of Lexeme, the parser breaks off the current iteration and takes the next literal in line. If the literal is valid but not a KeyLiteral, the literal is accumulated to the current Lexeme. KeyLiterals are defined for example as white space or closing braces. If one of these characters comes out of the stream, the Lexeme accumulation is aborted and the WordID is checked.

If a matching WordID is set, the current Lexeme has to be the second Lexeme of a token pair. So the Token is stored. Analogous if the WordID is not set, the current Lexeme is neither a non-relevant Lexeme nor a KeyWord of a token pair. In the last case, the corresponding WordID is being set and the state machine continues accumulating literals.

Figure 9: Parser State Chart

## 3.2.2.3 Parsing the HCDM file

The file that contains most of the needed information is the HCDM.hcdm txt-file. The HCDM file is, as already described in chapter 2, a textual description of the data flow graph. So once the graph is drawn inside HCDM, the tool creates this file and saves it into a specified directory. We now want to use the explained Java streaming concepts and the Parser state machine to extract the relevant information out of the HCDM File. The HCDM file contains a lot of not needed or redundant information. Figure 10 demonstrates how Tasks are stated inside the HCDM grammar.

```

TASK 14 {

TASK DECLARATION

NAME { Par2 }

OPTIMIZATIONTYPE { 1 }

IMPORTANCE { 1 }

FAILURE_PROBABILITY { 0.5 }

LEVEL { -3 }

PRIORITY { -4 }

TIMING { 0 }

RESOURCES { (2,20)(5,20)}

IORELATIONS {

IORELATION {

INPUT { 84 181 }

HIERACHICAL RELATION

TO OTHER TASKS

OUTPUT {78 }

CONDITION { true }

}

SUBTASKS {

TASK 17 {

EXTERNAL INPUT

NAME { b[32] }

DECLARATION

OPTIMIZATIONTYPE { 1 }

IMPORTANCE { 1 }

FAILURE_PROBABILITY { 0.5 }

LEVEL { -3 }

PRIORITY { -4 }

TIMING { 0 }

RESOURCES { (4,0)}

IORELATIONS {

IORELATION {

INPUT { 48 }

OUTGOING BRANCH

OUTPUT {87}

CONDITION { true }

```

Figure 10: Task declaration inside HCDM

In fact the only information we want to get is: the *name* and *bit width* of external inputs, the task names and the hierarchical relation between them. So out of the HCDM grammar we choose the keywords NAME, INPUT and OUTPUT. When the state machine is in the *WordIDcheck* state, the Token is constructed when the WordID is set. So during the transition from this state back to the initial state, the token has to be stored somewhere. We decided to build a class with name Task in order to store all tokens. Tokens are stored inside attributes of this class.

The Parser pattern can be described best in terms of a Backus-Naur Form (BNF). The BNF in figure 11 is referenced to the HCDM grammar stated in the appendix and only describes the fields that are extracted by the parser.

```

<name>

'NAME { '<taskname> | <port>'}'.

\theta \mid \langle \text{string} \rangle.

<taskname>

\theta | <portname> <leftdelimiter> <integer>

<port>

<rightdelimiter>.

<portname>

\theta | <string>.

<iorelation> →

'INPUT {' <idlist> '}'

'OUTPUT {' <idlist> '}'.

\theta | <integer> ' ' <idlist>.

<idlist>

<integer>

<digit> | <integer> <digit>.

<letter> | <string> <letter>.

<string>

'a' | 'b' | 'c' | ...| 'z' | 'A' | 'B' | 'C'

<letter>

| ... | 'Z'.

'1'|'2'|'3'|'4'|'5'|'6'

<digit>

<leftdelimiter>

→ '['.

<rightdelimiter>

→ ']'.

```

Figure 11: BNF description of Parser pattern

Two important not yet mentioned design rules have to be taken into account when drawing DFG's with HCDM:

- When we model a component with a task symbol in HCDM, we have to take care that we are drawing the corresponding inputs of the task in exactly the same order as they are stated inside the component entity. If we do so HCDM will assign ascending branch numbers to the task and VHDLGenerator can parse the associations correctly.

- 2) If a task got more than one proceeding task, HCDM will generate an output branch for each proceeding task. In VHDL these outputs should only be related to one VHDL component output. Note that VHDLGenerator is aware of that and discards the different branches in a way that it produces a single output that is routed to every following component.

That way the parser goes from task to task, extracts the relevant information and puts everything into a variable of type ArrayList. Once all tasks are extracted the external input and output ports need to be separated from the real tasks to generate the top level interface. So an algorithm is started that identifies input and output ports, allocates them to the respective task and deletes them out of the ArrayList. To filter out the external ports we make use of the previously mentioned fact that external Inputs are designed tasks that are direct successors of the root task and external Outputs have outgoing branches back to the root task.

The bit length of every input or output port is parsed from the name by using the discussed Java StringReader concepts.

## 3.2.2.4 Parsing the Scheduling File

The second file produced by HCDM is a scheduling file like it is shown in figure 12. The scheduling file is parsed in the same manner as the HCDM file.

```

true: b[32] (0,0), a[32] (0,0), top (0,20), Par2 (20,40), Par3 (20,40),

Bottom (60,70), result[32] (70,70),

BINDING { (Par2-myAnd_2) (b[32]-Input_2) (Bottom-myOr_1) (top-myXor_1) (a[32]-Input_3) (Par3-myAnd_1) (result[32]-Output_1) }

```

Figure 12: Scheduling File example

In the first line of the scheduling file the start and stop times of the tasks are listed. Keywords are here the task names of the task that are already stored in the ArrayList variable. To every task the start time and stop time token is assigned. Later on one single time unit produced by HCDM will mapped to a single clock cycle inside the VHDL code.

Note that the first entries in the scheduling file are the external inputs and outputs. These have to be removed out of the task array afterwards. Also the word "true" is only used as delimiter and is therefore ignored during the parsing process.

When the schedule parsing has finished, the parsing of the component-binding starts. The trigger for the binding line is the keyword "BINDING" which is the first word in line. Extracted Tokens are associated to the respective task.

### 3.2.2.5 Parsing the Components File

The components on which the tasks run have to be specified somewhere. For that reason a text file is created to enter the needed components. To simplify the parsing work we can completely abstract from the components behavior. In fact it is only necessary to define the interface of a component. The behavior will be included later as a library inside the generated VHDL code. Figure 13 shows how the components file looks like. Note that the commentary will at the beginning will be ignored by the parser.

```

/* NOTE: Enter all used components, with their input and output ports, except the "clk", "reset" and "enable" which are generated automatically */

NAME {myXor} INPUT {a[32],b[32]} OUTPUT {result[32]}

NAME {myAnd} INPUT {a[32],b[32]} OUTPUT {result[32]}

NAME {myOr} INPUT {a[32],b[32],c[32]} OUTPUT {result[32]}

```

Figure 13: Components File example

So to every component the following information has to be entered: the components name, the inputs ports and output ports with the adequate bit width. Every component is expected to have a *clock*, a *reset* and an *enable* input. So thesis parameters are not entered by hand but generated automatically.

The components are parsed separately from the tasks and stored inside a different ArrayList called *UsedComponents*. We will need them later for components declaration inside the VHDL code. Furthermore they are used for error detection, which will be subject of chapter 3.3.3.

## 3.3 The PreConverter stage

The Parser stage delivers two objects for further processing. One is called *Tasks* and contains all assigned tasks with their specified attributes. The other is called *AllComponents* and contains an ArrayList of all used VHDL components. The goal of the PreConverter stage is now to prepare the collected data for the final VHDL Converter stage.

In the following chapter the theory of the different processing steps of the PreConverter are explained. Special attention is taken on the part about register optimization.

The concepts are discussed in the same order as the related methods are executed inside the PreConverter code.

### 3.3.1 Sorting of the Tasks

During the execution of the VHDLGenerator program it occurs quite often that we have to sort arrays. Ports need to be sorted by their branch number, case-statements by their execution time and tasks by their start time. So because of the high usage of

sorting algorithm it is worth to have a deeper look in it, in order to choose the most appropriate one.

When we want to perform the Left Edge algorithm it is of great importance to have the tasks sorted in ascending order to their Start Times. So the first step of the PreConverter stage is the sorting of the tasks.

An appropriate algorithm for sorting has to be selected. Appropriate algorithm means here that we want to find an algorithm that sorts a given set of items with the lowest complexity. We define complexity here as number of steps and time units.

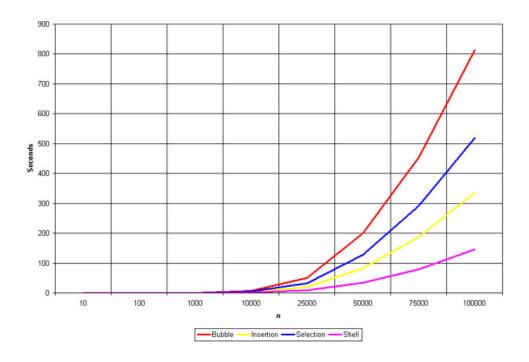

In general one can categorize sorting algorithms either by their algorithm structure (Divide&Conquer form [9]) or by their complexity [10]. Using the second categorization most of the common sorting algorithms are divided further into basically two classes of algorithms with respect to their execution time. For the first class of algorithms, the execution time increases quadratic ally with the number of items. The second class needs n\*log n complexity with being n the number of items. Figure 14 and 15 [10] demonstrate how typical algorithms of each class behave for large n.

Big-O notation is used, where the O represents the complexity of the algorithm, n stands for the number of items to be sorted and the whole expression inside parenthesis determines a measure for complexity.

Inside the complexity class the algorithms may still vary in their constant runtime factor ( how much time each of the n\*log n steps takes).

Figure 15: O(n log b) sorts

As it can be seen the Quick Sort algorithm yields the best performance. Quick sort works onto the divide-and-conquer principle and uses recursive structures. That may cause problems for applications with resource limitation. For VHDLGenerator we

expect to have sufficient computation power and memory space, so that recursion is not a drawback for us.

The dividing (partitioning) works in a way that we first choose a pivot element. All elements that are greater than the pivot element are put into a new partition. All elements that are smaller than the pivot are put into a second partition. Then the algorithm is repeated for each partition separately. At the end all partitions are concatenated.

Figure 16 [9] gives pseudo code for the Quicksort algorithm:

```

Quicksort (X, 1, r)

1 if l<r

then split \leftarrow PARTITION(X, 1, r)

3

Quicksort(X,1,split)

4

Quicksort(X, split+1, r)

PARTITION (X, 1, r)

1 pivot \leftarrow X [1]

2 i \leftarrow 1-1

3 j \leftarrow r+1

4 while TRUE

5

do repeat j←j-1

6

until X [j] <= pivot</pre>

7

repeat i←i+1

8

until X [i] >= pivot

9

if i<j

10

then exchange X [i] \leftrightarrow X [j]

11

else return j

```

Figure 16: Quicksort pseudo code

## 3.3.2 Register Optimization

The implemented VHDL Converter has to deal with resource constraints. On one hand the number of available instances of one component type is limited. This implicates a scheduling of the tasks which is done by the HCDM tool and will not be discussed further. On the other hand we want to use a minimum amount of registers. A result coming out of one of the components has to be stored in a register until it is further processed. A register in VHDLGenerator is considered to be a signal of type std\_logic\_vector with the same bit length as the result vector. Depending on the task hierarchy not every result needs a private register. A register could be reused once the previous value has been passed to the input of the next component. So we would like to find an algorithm for yielding an optimum number of registers.

A result of a component can be considered as a variable with a certain *lifetime*. The Lifetime of a variable is defined as "the interval from its birth to its death, where the former is the time at which the value is generated as an output of an operation and the latter is the latest time at which the variable is referenced as an input to another operation"[2].

So first step would be to find the BirthTime and DeathTime of every task result. As it has been already turned out during the parsing of the Tasks it is always quite useful to extract the desired information and store it into an object ArrayList for further processing. We will proceed here in the same way. For these purposes a class TaskOuputLifetime is created that contains the following attributes which have to be set for every task: TaskName, BirthTime, DeathTime, RegisterName and RegisterBitWidth. So the ArrayList is filled with TaskOutputLifetime objects corresponding to every task.

The BirthTime attribute is identically with the Stoptime attribute inside the task object and can be taken over directly. Note that the Stoptime is stated inside the scheduling file and has been parsed in the parser stage before.

The DeadTime is found out with a bit more effort. If an output variable is used as input for more than one component, we need to find the component with the **latest** StartTime, i.e. we are looking for the maximum of all possible proceeding DeathTimes. So we first check which are the successor tasks of our current task. Then the StartTime of each is collected into an array. After having done this we go

through this array, compare all elements with each other, pick up the highest value and assign this value to the DeathTimes attribute of the current TaskOutputLifetime object. The procedure is then repeated for every task until all lifetimes of the task outputs are found.

With this data now the optimum number of needed output register can be calculated using a minimization algorithm. There are basically two different methods to proceed: Finding the minimum number of registers either using *Clique Partitioning* or using *Graph Coloring*.

Clique Partitioning is described in [2] and has been first implemented by Tseng [15]. We observe that solving the register optimization with clique partitioning is NP - Complete. It does not guarantee an optimal result.

The second alternative is the Graph Colouring approach. This algorithm promises optimal results with complexity  $O(n^2)$ . An appropriate representative of Graph Colouring algorithms is the **Left-Edge Algorithm**.

We will first explain the theoretical background of the left edge algorithm, talk about its development and then show how it is realized inside VHDL Converter.

Accordingly to [2] the underlying theory of the Left Edge Algorithm is the Graph Colouring optimization problem. The Graph Colouring searches a vertex colouring with a minimum number of colours. In the algorithm below the different colours are represented by integer numbers.

Figure 17: Vertex Coloring pseudo code

At the beginning every node got a colour number of 0. The algorithm is applied to the compatibility graph in figure 18. Note that compatibility graphs are undirected graphs.

Figure 18: Compatibility Graph

The result is shown in Figure 19. In comparison figure 20 shows the optimum colouring. So the colouring graph algorithm does not yield optimal results. One way to improve the algorithm is the swapping colour method. In our example we reach the optimal solution either by backtracking or by swapping the colours of vertex v5 and v4.

Figure 19: Non-minimum Coloring

Figure 20: Minimum Coloring

Fortunately the Left Edge Algorithm holds an interesting property. The underlying graph built with our concept of lifetimes of variables belongs to a subgroup of graphs called interval graphs. Colouring the intervals is equivalent to colouring the vertices. For interval graphs the colouring algorithm needs polynomial time for solving and

one important note: the result is **optimal**. This is based on the fact that interval graphs have *perfect vertex elimination scheme*. For detailed description on the definition of perfect graphs and *perfect vertex elimination scheme* take a look inside [2]. For Perfect Vertex Elimination Scheme there is no need of backtracking or colour swapping.

The original Left Edge Algorithm as proposed by Hashimoto and Stevens[13] has been developed to solve channel routing problems. The goal was to assign wires to a minimum number of routing tracks.

As a first step the wires are sorted with increasing order of their left end points from the left edge of the channel. That is the reason why this algorithm is called "Left-Edge". Now the assignment starts. The first wire at the left is assigned to the first track. Then we find the first wire whose left edge is to the right of the last selected wire and assign this one to the current track. If we reach the last column, the assigned wires are removed and a new track is started.

This algorithm is repeated until no more wires can be assigned to tracks. Figure 21 [14] shows the pseudo code for the proposed algorithm

```

Algorithm LEA

Begin

1

Sort all nets on their left most end positions:

2

Initialize the tracks t_1, t_2, ..., t_d

(t_1 is the lowest track);

3

for each net n_i \in sorted list

for each t_i, i from 1 to d

5

if n_i doesn't overlap with any nets

in t_i

6

then assign n_i to t_i

endfor

8

delete n_i from the list

9

endfor

END.

```

Figure 21: Left Edge pseudo code

As it can be seen Left Edge algorithm uses a Greedy approach. Nevertheless the Left Edge Algorithm gains an **optimal** solution and is of complexity  $O(n^2)$ .[14].

Kurdahi and Parker [14] grabbed this idea and used the same principle for register minimization. There the wires correspond to the previous discussed lifetime of variables and the routing tracks are the to be minimized registers. The left and right edges of the wires are considered to represent the birth and death time of a variable formally known as lifetime. Accordingly to [14] all different lifetimes have to be collected inside a table. We have already discussed the procedure at the beginning of the chapter. Having done this, the goal of the Left Edge Algorithm is to assign output variables(wires) to registers(tracks) so as to minimize the total number of registers(tracks) to store the output value. Two wires cannot share a track if they overlap in space, whereas two variables cannot share a register if they overlap with their lifetimes.

The presented algorithm is used inside the program REAL (Program for REgister ALlocation) which has been developed by Kurdahi and Parker. Very similar to

VHDLGenerator, REAL gets as input a data flow graph whose operations have been scheduled, along with a lifetime table of the values in the DFG. REAL also has to deal with resource constraints, like number and type of operators used to implement the operations. Scheduling can be overlapping. In the paper of Kurdahi and Parker also register allocation for conditional branches is discussed. Conditional branches are not supported by HCDM so far and will not be discussed in contents of this work. As REAL is optimal for non-pipelined designs with no conditional branches we also expect VHDLGenerator to give optimal results when using the same algorithm.

As implemented inside VHDLGenerator, the Left Edge Algorithm works in a quite simple but efficient way. The encoding in Java is realised based on the pseudo code shown in figure 22.

Lifetimes are extracted as explained before.

Note that the first step of the Left Edge algorithm, the ordering of the lifetimes is done inherently when the tasks are sorted by their lifetimes, as shown in part 3.1.1.

The next step would be to pick up the first lifetime, allocate it to a register (colour) and check for overlapping with other lifetimes. If we consider the tasks to be sorted in ascending order to their Start Times a criterion for non overlapping lifetimes can be formulated quite easy:

Two Lifetimes do not overlap, when the death time of the first is smaller or equal the start time of the next lifetime.

Outputs with non overlapping lifetimes are packed into one register. Then the first element is deleted and the algorithm starts again. The whole procedure is repeated until all lifetimes are processed. As a final step the found lifetime register pairs are transferred to the tasks in a way that inside the task object the corresponding *OutputRegister* attribute is set.

```

ALGORITHM VHDL GENERATOR LEA

BEGIN

1

SORT tasks in ascending order to their start times

2

EXTRACT all Lifetimes and store them.

3

LOOP

4

Take first element out of lifetimes

6

//Compare to all other lifetimes

7

IF (Deathtime of first Lifetime <=</pre>

Birthtime of next Lifetime)

8

ASSIGN both tasks to same register

9

10

REMOVE first lifetime out of list

11

END LOOP

12

END LOOP

```

Figure 22: Left Edge pseudo code for VHDLGenerator

Note that PreConverter also offers another method with name allocateOutputRegister(). This method allocates non minimized registers to the tasks, i.e. every task gets a separate output register. This method could be used instead of the doLeftEdgeAlgorithm() method when we do not have to deal with resource constraints. The user of VHDLGenerator has can choose between these two modes in the graphical user interface.

### 3.3.3 Error-detection and recovery techniques

Although various tests have shown that VHDLGenerator program itself accomplishes its job in a correct way, you are never aware of faults that are introduced from the user's side. What is desirable is software that reacts robust to the users input. Software "is robust if it describes reasonable behaviour even when it is misused or used in error "[12]. Of course "reasonable" is an expandable item. We will define it here for the VHDLGenerator in a way that we say: the program should catch inputs that lead to a failure. The user should be informed where and why the error occurred.

Furthermore it is often of use, to test the obtained results against the specification for faults. How to write system level tests for VHDL programs will be part of chapter 3.4.

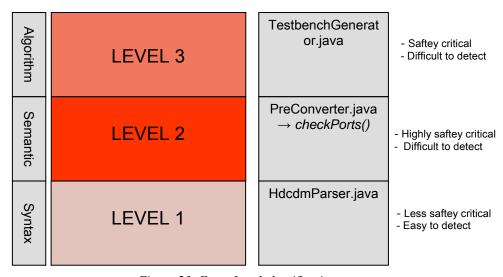

We categorize possible faults into three abstraction levels on which they may appear. Figure 23 illustrates the different error levels where the intensity of the color indicates the impact of the error on the design.

On **first** level there are the faults that are inserted on the syntactical level. That means for some reason the given input is faulty and cannot be further processed. In our case a level one fault could be a mistake due to the grammar of the to be parsed text. Level one faults can be detected as an error very soon during the processing of the program and therefore do not lead to a failure.

On the **second** level we have to deal with faults that entered in a way that they are not detected as an error by the program itself. The faults are handed over through the whole process and end in a complete failure when the final operation is put into process. These kinds of faults are the worst because they may end in production errors. So it is highly recommendable to catch these faults and transform them into an error before they end up into a failure.

Figure 23: Error Level classification

On the **third** level we want to handle faults that result neither into an error nor into a failure. These faults are made at the behavioural description of the input. In our case this means that the entered algorithm graph does not follow its specification. Like in a compiler these kinds of faults cannot be detected, because they take into account the given specification on which the entered algorithm is based. VHDLGenerator has no knowledge about that. The only chance to get rid of these

faults is to demonstrate the programmer how his implemented algorithm works. The programmer himself has to compare the result with the desired specification and perform possible changes.

In this chapter we will only discuss the faults of level one and two because these are the kind of faults that are treated by the HCDMParser and PreConverter stage. Third level faults are subject of chapter 3.4.

## 3.3.3.1 Java Exception handling in general

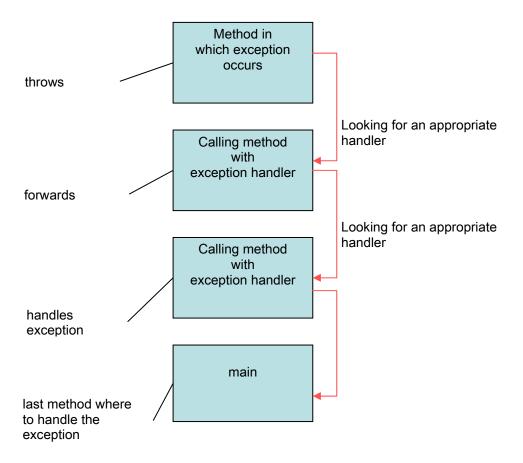

Java offers comfortable constructs to catch and handle errors in form of exceptions in programs. In general an exception in Java is an event, which occurs during the execution of a program, and disrupts the normal flow of the program's instructions. The program flow is then bended over to the exception handling routine.

All exceptions are thrown inside the execution of a method. Methods that are able to throw exceptions got the extension *throws Exceptions* next to the method identifier.

*Exception* is a Java class of its own. There exist several classes that inherit from Exception and specify the different types of Exceptions. Note that one can also create an own exception class and define a specific behaviour there.

So throwing an exception means creating an instance of this class and hand it over to the runtime system. The runtime system has to find an appropriate handler for the exception. As first step the runtime system gives the exception to the method above that calls the method in which the exception is thrown. The calling method either has to catch the exception and handle it or forward it to the method above. In the last case a new exception object has to be created that encapsulates the original exception message. That way an exception can be handled from the method it occurred up to the first method executed in the program. If not before, the exception has to be definitely handled there. The scheme is shown in the figure 24.

Figure 24: Exception handling in Java

Exceptions objects are created and thrown using the keywords *new* and *throw*. Messages are added over the constructor field. The throw statement could be embedded for example into an *if*-clause like:

```

public void example() throws ExceptionType{

if(condition) {

throw new ExceptionType(Message);

}

}

```

Figure 25: throw statement

In the calling method, all methods that might throw an exception have to be placed inside a try-catch block. Methods following after a try statement are executed and in case of an exception the runtime system jumps into the appropriate catch block. The stress lies upon "appropriate" catch block. The calling method can only handle exceptions that are part of one of its catch blocks. If for example a method throws an

exception of type IOException, then the calling method needs a case statement that covers this type. An example is shown in figure 26.

```

try{

example(); // throws a

ExceptionType

} catch (FileNotFoundException f) {

...

} catch (ExceptionType e) {

...

}

```

Figure 26: try-catch

There exist other concepts like the *finally* block, which will not be discussed here. When writing an Exception handler for VHDLGenerator we will need to know how to create own Exception classes and how to throw, catch and handle Exceptions in Java.

## 3.3.3.2 Exception handling inside VHDLGenerator

As mentioned in the introduction of this chapter, one of the goals of the HCDMParser and PreConverter stage is to catch and handle faults of level one and two.

First we like to figure out all possible faults that might appear when executing VHDLGenerator and categorize them. The table in Figure 27 shows one out of several possibilities how to classify the different faults. The table is thought as a reference for the user to get a more detailed documentation of the error message printed out by VHDLGenerator.

Every error got an error code that is printed out. Errors belonging to level one are of format 1.x, level two starts with 2.x. The Java Exception Type divides the levels further into the different Exception classes. All possible exceptions could be only generated in classes that contain executable methods, namely HCDMParser, PreConverter and VHDLGenerator. The location column gives information about working step in which the exception was thrown. Finally a description of the error and short proposition for solving is given.

Note that all exceptions thrown are forwarded up to the very first calling method, where they are handled.

Level one exceptions occur when input data is faulty and the runtime system cannot proceed. These exceptions are safety non-critical because they result directly in an error and do not sneak through the whole process. They are generated by the Java runtime system automatically. An object is created and a message is added. All we have to do is write an appropriate handler that catches the exception, add an individual text and finally print out the whole message.

Level two faults are safety critical and also more difficult to detect. Let us see why and how they could appear:

VHDLGenerator does not take care whether the produced VHDL code is compilable or not. It just converts given input files into text file which contents could be interpreted as VHDL code. No guarantee of syntactical or semantic correctness is given. Some of these errors inside the VHDL code are detected by the VHDL Compiler and can therefore be corrected afterwards. But we could also imagine a scenario, where errors are not even recognized during the synthesis.

So in order to reduce possible error sources VHDLGenerator should adapt to at least two faulty "level two" user inputs:

Every tasks runs on a component that got a specified number of input ports. So a task needs as many inputs branches as the corresponding component got input ports. We should beware of assigning more ports, because then one will be unused. Assigning fewer ports will lead to floating ports which causes undetermined system behaviour.

Once it is checked whether the number of input ports fit, we further have to verify the bit length of each port. In the Components File the bit length of every component port is stated in brackets next to the identifier. The Input ports bit length has to match with this bit length. Otherwise similar problems than for the previous case appear. We have to check for over and under assignment of bit length.

All level two faults are detected by the method *checkPorts()* inside the PreConverter stage.

*checkPorts()* throws an exception of type PortException. PortException is a self-made Exception type, that does nothing more than specify the level two exceptions and store messages.

The procedure for finding the errors is straightforward. One loop iterates all tasks and compares the number of ports with the associated component ports. If a mismatch occurs a PortException with error report is thrown. The same procedure applies for a bit width mismatch.

| Error | .Java            |                    |                                                        |

|-------|------------------|--------------------|--------------------------------------------------------|

| Code  | <b>Exception</b> | Location           | Description                                            |

|       |                  |                    |                                                        |

| 1.1   | IOException      | HcdmParser         | The desired Hcdm File is not found in the given        |

|       |                  |                    | filepath.                                              |

|       |                  |                    | Make sure that the path is correct and the             |

|       |                  |                    | HCDM File really exists inside the specified           |

|       |                  |                    | directory.                                             |

|       |                  |                    | Note that directories have to be                       |

|       |                  |                    | separated by "//".                                     |

|       |                  |                    | New entered paths always have to be                    |

|       |                  |                    | confirmed with "Enter"                                 |

|       |                  |                    |                                                        |

| 1.2   | IOException      | HcdmParser         | The desired Scheduling File is not found in the        |

| -     |                  |                    | given filepath.                                        |

| -     |                  |                    | Make sure that the path is correct and the             |

|       |                  |                    | Scheduling File really exists inside the               |

|       |                  |                    | specified directory.  Note that directories have to be |

|       |                  |                    | separated by "//".                                     |

| -     |                  |                    | New entered paths always have to be                    |

|       |                  |                    | confirmed with "Enter"                                 |

|       |                  |                    | commined with Enter                                    |

| 1.3   | IOException      | HcdmParser         | The desired Components File is not found               |

|       | 1                |                    | in the given filepath.                                 |

|       |                  |                    | Make sure that the path is correct and the             |

|       |                  |                    | Components File really exists inside the               |

|       |                  |                    | specified directory.                                   |

|       |                  |                    | Note that directories have to be                       |

| _     |                  |                    | separated by "//".                                     |

|       |                  |                    | New entered paths always have to be                    |

|       |                  |                    | confirmed with "Enter"                                 |

|       |                  |                    |                                                        |

| 1.4   | IOException      | VHDLConverter      | The desired path to which the Vhdl File                |

|       |                  |                    | should be created is not valid.                        |

|       |                  |                    | Please enter a reachable directory.                    |

|       |                  |                    | Note that directories have to be                       |

|       |                  |                    | separated by "//".                                     |

|       |                  |                    | New entered paths always have to be                    |

| 1.5   | IOException      | TestbenchGenerator | The Testbench could not be created.                    |

|       | 202option        | - John Chichard    | TestbenchGenerator uses the same destination           |

|       |                  |                    | path as already used for the VHDL file.                |

|       |                  |                    | Look further for Error Code 1.4                        |

|       |                  |                    |                                                        |

|       |                  |                    |                                                        |

|       |                  |                    |                                                        |

|       |                  |                    |                                                        |

|       |                  |                    |                                                        |

|       |                  |                    |                                                        |

| Error | Java          |                    |                                                                                 |

|-------|---------------|--------------------|---------------------------------------------------------------------------------|

| Code  | Exception     | Location           | Description                                                                     |

|       |               |                    | the VHDL file could not be found on the                                         |

|       |               |                    | computer.                                                                       |

|       |               |                    | Make sure that the spelling is correct and that                                 |

|       |               |                    | the specified program is able to read text files.                               |

|       |               |                    | Note that the code is a simple text file and can                                |

|       |               |                    | always be opened by a text editor like                                          |

| _     |               |                    | "notepad" or "Kedit"                                                            |

| 1.7   | P             | D. C.              | HODME'L G                                                                       |

| 1.7   | Exception     | PreConverter       | HCDM File Syntax incorrect.                                                     |

|       |               |                    | The information is entered in the wrong way.  Recheck the grammar               |

| -     |               |                    | Recheck the grannial                                                            |

| 1.7   | Exception     | PreConverter       | Scheduling File Syntax incorrect.                                               |

|       |               |                    | The information is entered in the wrong way                                     |

|       |               |                    | due to the grammar. Verify that the scheduling                                  |

|       |               |                    | file got the correct format.                                                    |

|       |               |                    | The correct format is stated in the                                             |

| -     |               |                    | VHDLGenerator Reference Manual                                                  |

| 1.7   | Exception     | PreConverter       | Components File Syntax incorrect.                                               |

|       |               |                    | The information is entered in the wrong way                                     |

|       |               |                    | Recheck the grammar                                                             |

| 1.0   | F             | VIIDI C            | The constitute WHDL 6:1.1                                                       |

| 1.8   | Exception     | VHDLConverter      | The converting to VHDL failed.  Make sure that the data flow graph is specified |

|       |               |                    | in a                                                                            |

|       |               |                    | correct way (no loops, no tasks without inputs).                                |

|       |               |                    | _                                                                               |

| 1.9   | Exception     | TestbenchGenerator | Testbench could not be created.                                                 |

|       |               |                    | Recheck if VHDL code is testable.                                               |

| 2.0   | PortException | PreConverter       | More Ports are assigned to the component                                        |

|       |               |                    | than allowed.                                                                   |

|       |               |                    | Increase either number of ports or                                              |

|       |               |                    | decrease number of component ports                                              |

| 2.2   | Dout F        | Duo Comment        | The Input post hit width days and Co. 14. 1                                     |

| 2.2   | PortException | PreConverter       | The Input port bit width does not fit with the                                  |

|       |               |                    | specified component input bit width. Change either Input Bit Width of Port or   |

|       |               |                    | component                                                                       |

|       |               |                    | Component                                                                       |

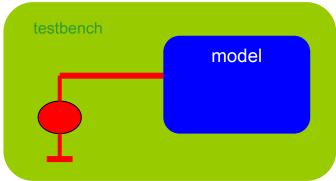

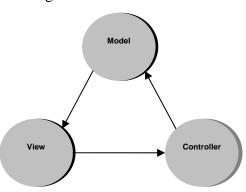

| 2.3   | PortException | PreConverter       | The output port bit width does not fit with the                                 |