# Seminar 1

#### Contents

- Definition of microcontroller (mC)

- Definition of Digital Signal Processor (DSP)

- Criteria for performance comparison of mCs e DSPs

- Performance measurements

Simone Buso - Seminar 1

# Microcontrollers (mCs)

A microcontroller is a processor specifically designed and optimized to perform control, timing, supervising tasks on various target devices. It is characterized by the availability of relatively large amounts of "on chip" memory (ROM, EEPROM, Flash ...) and of several peripheral units, for different functions (I/O, A/D conversion, timer, counters, PWM, ...). It is normally characterized by reduced complexity and low cost.

Simone Buso - Seminar 1

# Microcontrollers (mCs)

Peripheral units in mCs:

- A/D converters (number of bit, conversion speed, linearity vary a lot among different devices)

- Timer and counters

- PWM modulators

- External memories (ROM, EEPROM, FLASH)

- Communicaion ports (serial, I2C, field bus e.g. CAN)

Simone Buso - Seminar 1

# Microcontrollers (mCs)

The use of mCs is very common for the implementation of:

- portable measurement instruments;

- PC periferals;

- fax/photocopiers;

- home appliances;

- cell phones;

- industrial applications, in particular in the automotive and electrical drives fields.

Simone Buso - Seminar 1

# Digital Signal Processors (DSPs)

DSPs are microprocessors specifically designed and optimized to efficiently perform real time signal processing tasks. They are characterized by high computational power and relatively low cost (if compared to general purpose processors). Particular care is taken in minimizing the power consumption (e.g. in embedded portable applications).

#### Digital Signal Processors (DSPs) Several different DSP families are available on the market. They all exhibit some common features: • availability of a built-in multiplier circuit (MAC instruction); • capability to operate multiple memory

- capability to operate multiple memory accesses in a single clock cycle;

- specific addressing modes for circular registers and stacks;

- sophisticated program flow control instructions;

- availability of DMA circuitry (top level).

Simone Buso - Seminar 1

# Digital Signal Processors (DSPs)

The major application areas for DSPs are related to:

- coding/decoding of speech, hi-fi audio segnals, video signal processing;

- compression/decompression of data;

- encryption/decryption of data;

- mixing of audio and video signals;

- sound synthesis.

Simone Buso - Seminar 1

### DSPs vs mCs

Traditionally, mCs were used in the implementation of control functions, thanks to the wide range of peripheral units available on-chip. The computational power was limited (CPUs had 8 bits or less, no hardware multiplier).

DSPs were used, instead, almost only for signal-processing applications, where the key parameter is computational power.

Currently, the differences in the application fields of mCs and DSPs are a lot fuzzier.

Simone Buso - Seminar 1

## DSPs vs mCs

More recent DSPs include peripheral units traditionally typical of mCs. On the other hand, mCs present, at least in top range models, hardware organizations and computational powers closer and closer to those typical of DSPs. Costs and performance may be very close and, for particular applications, the choice of the device may be quite difficult.

We definitely need criteria to compare different devices.

Simone Buso - Seminar 1

# DSPs vs mCs

The fundamental parameters for the comparison are, of course, cost and performance.

To minimize the cost parameter, for given specifications, it is normally required to take into account not only the device cost, but also the estimated development time, the so called time to market.

Simone Buso - Seminar 1

# DSPs vs mCs

The cost of device is largely dependent on the expected production volume.

Time and resources required by the development of the application are a function of several factors, like:

- availability of high quality and high reliability development tools;

- effective technical support from the device manufacturer.

### DSPs vs mCs

The application specifications determine the **performance level** required for the selected microprocessor in terms of:

- required peripheral units and their basic parameters (e.g. A/D converter with 8, 10 or 12 bits);

- operating conditions (e.g. maximum allowable power consumption, temperature range);

- required computational power (real time control, signal processing ...).

Simone Buso - Seminar 1

11

#### Performance measurement

The perfomance level of any processor can be measured only in terms of time required to excute a given program.

In the case of mCs or DSPs this is the same time the processor effectively spends on the program instructions (computation time), unless an operating system coordinating several tasks in time sharing is running on the device.

#### Simone Buso - Seminar 1

#### Estimation of computation time

The computation time of a program is a key parameter in real time applications (both in control and signal processing). This can be estimated based on three parameters:

- processor clock period;

- number of clock cycles required by the instructions in the program;

- number of di instructions required by the program.

Simone Buso - Seminar 1

13

15

17

#### Estimation of computation time

The clock period and the number of clock cycles required by the various program instructions can be read on the processor datasheet/user manual.

The number of instructions required by a given algorithm is a function of the processor architecture.

By architecture we mean the set of resources that are available to the programmer for the implementation of the algorithm (instruction set). Simone Buso - Seminar 1

### Estimation of computation time

Any given architecture can be implemented in different ways at the hardware level.

We therefore make a distinction between processor organization and architecture: the former is the particular hardware implementation of the latter.

The architecture has a direct effect on the number of instructions required by a given program. The organization determines the clock period and the number of clock cycles required by any instruction.

Simone Buso - Seminar 1

#### Estimation of computation time

The computation time of a program can be estimated by using the following formula:

$$T_{cal} = T_{clk} \cdot \sum_{i=1}^{N_{cl}} N_i \cdot NC_i$$

(1)

where  $T_{clk}$  is the processor clock period,  $N_i$  is the number of class *i* instructions in the program,  $NC_i$  is the average number of clock cycles required by class *i* instructions,  $N_{cl}$  is the number of considered instruction classes.

# Stimation of computation time

Relation (1) assumes that the program is not interrupted by other processes and neglects the delays due to memory accesses.

To increase the speed of a processor, we therefore need to:

- reduce the clock cycle (T<sub>clk</sub>);

- reduce the number of cycles required by the more commonly used instructions (NC);

- reduce the number of instructions required by a given algorithm.

14

#### Speed limits!

Reducing the clock cycle duration always implies the increase of power consumption for the processor.

This can be limited by reducing also the supply voltage.

Which tells us why there is a strong need for lower and lower power supply voltages (<1V) in computer applications.

The limitations are basically technological (we need new processes/materials).

Simone Buso - Seminar 1

# Speed limits!

The reduction of the number of clock cycles required by an instruction calls for a more sophisticated hardware organization of the processor, e.g. wired control instead of micro-programmed control, higher degree of parallelism (achievable in several different ways: VLIW, SIMD, etc.) or the use of pipelines.

This trend leads to complex processors, with high cost. The limitation in this case is basically "economical".

Simone Buso - Seminar 1

19

21

23

# Speed limits!

The number of instructions required by a given algorithm is a function of the processor architecture, i.e. of its instruction set, as seen by the programmer/compiler.

The reduction of this parameter leads to complex instruction set computers (CISC), instead of reduced (and simple) instruction set computers (RISC). This again affects the processor organization and its cost. That's why RISC processors are a lot more used than CISC processors.

Simone Buso - Seminar 1

# Maximizing performance

The processor performance is a function of both its architecture and of its organization, at the hardware level.

The maximization of performance calls for a co-ordinated design of hardware and software.

The problem is further complicated by the action of several design constraints such as:

- cost;

- electric power consumption.

Simone Buso - Seminar 1

#### Performance measurements

A typical way to measure a general purpose processor performance is to use benchmarking, i.e. the execution of suitably designed test programs. This method helps to evaluate the overall processor performance, including memory management.

Recently the same strategy is being applied also to DSPs. The considered test programs are typical signal processing algorithms (FFT, FIR, IIR filters etc.).

#### Performance measurements

The usual benchmarking method for general purpose processors uses complete applications (e.g. SPEC method).

This approach cannot be used with DSPs, because the results would be strongly dependent on the quality of the adopted compiler.

Besides, any code optimization becomes very difficult and comparison of different devices almost impossible. Kernel benchmarking is the adopted solution.

Simone Buso - Seminar 1

20

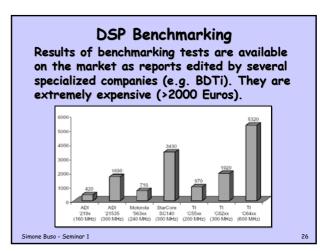

### **DSP Benchmarking**

Benchmarking programs must have, at least, the following basic features:

- relevance with respect to the typical DSP applications;

- clear and precise definition (e.g. what type of DFT algorithm is considered);

- 3) simplicity;

- 4) optimization: they must be easy to optimize for any given DSP architecture.

25

27

29

Simone Buso - Seminar 1

# Performance indexes

The following list include the more commonly encountered perfomance indexes:

- MACS: MAC operations per second

- MIPS: millions of instructions per second

- MOPS: millions of operations per second

- FLOPS: millions of floating point operations per second

All the indexes give little information on the actual processor speed. They do not allow any comparison between different devices.

Simone Buso - Seminar 1

# Performance indexes

The MACS index shows the maximum number of multiplies (with sum on the accumulator) a CPU is able to operate in a second (peak value).

However, in any DSP program, a lot of different operations are used (e.g. sums, memory read/write ...), whose impact on speed is not described by the index.

The MACS index does not give any serious measure of the actual processor speed.

Simone Buso - Seminar 1

28

## Performance indexes

The MIPS index shows the maximum number of instructions a CPU is able to execute in a second (peak value).

But, the number of instructions required by any algorithm depends on the CPU architecture (a single instruction can perform different amounts of operations in different architectures) and also on the compiler quality.

It is, at most, only possible to compare devices sharing the same basic architecture. Simone Buso - Seminar 1

## Performance indexes

The MOPS index shows the maximum number of operations a CPU is able to execute in a second (peak value).

Its definition is ambiguous itself, because it does not clearly define what exactly is an operation, or at least what is the reference set of operations, if any.

The meaning of the index is therefore not very clear and this should not be considered for comparison purposes.

#### Performance indexes

The FLOPS index shows the maximum number of floating point operations a CPU is able to execute in a second (peak value).

The validity of this index is similar to that of the MOPS index, with the further limitation that it can be applied only to floating point architectures.

None of the presented indexes takes into account other key issues for CPU performance measurement, like, for example, memory management and organization.

Simone Buso - Seminar 1

#### Example: MIPS vs Computation Time

Average number of Instruction classes clock cycles (NC) Α 1 В 2

С

3

32

34

A processor has 3 different instruction classes. Each class requires a different number of clock cycles. Any given program will use a certain amount of instructions of each class (compiler dependent).

Simone Buso - Seminar 1

31

33

35

|            | Compiler /                                                                       | Compiler / Number of instructions<br>Per class (hundreds) |                   |         |  |  |  |

|------------|----------------------------------------------------------------------------------|-----------------------------------------------------------|-------------------|---------|--|--|--|

|            | Programmer                                                                       | A                                                         | В                 | C       |  |  |  |

|            | 1                                                                                | 5                                                         | 1                 | 1       |  |  |  |

|            | 2                                                                                | 10                                                        | 1                 | 1       |  |  |  |

| two<br>alg | o different comp<br>o different progr<br>porithm, using a c<br>tructions and a c | rams for<br>different                                     | the sam<br>number | e<br>of |  |  |  |

the three classes.

Simone Buso - Seminar 1

# **Example: MIPS vs Computation Time** Applying (1) we can now evaluate the computation time of the two programs. We find: $T_{cal1} = T_{clk} \cdot 100 \cdot (5 \cdot 1 + 1 \cdot 2 + 1 \cdot 3) = 1000 \cdot T_{clk}$ $T_{col2} = T_{clk} \cdot 100 \cdot (10 \cdot 1 + 1 \cdot 2 + 1 \cdot 3) = 1500 \cdot T_{clk}$ The second program has a computation time longer than the first by 50%. It is then much slower the the first.

Simone Buso - Seminar 1

| Example: MIPS vs Computation Time                                                        |  |  |  |  |

|------------------------------------------------------------------------------------------|--|--|--|--|

| If we compute the MIPS index for the two<br>programs we find:                            |  |  |  |  |

| $MIPS_1 = 10^{-6} \cdot 100 \cdot (5+1+1)/(1000 \cdot T_{clk}) =$                        |  |  |  |  |

| 0.7 ·F <sub>clk</sub> ·10 <sup>-6</sup>                                                  |  |  |  |  |

| $MIPS_2 = 10^{-6} \cdot 100 \cdot (10 + 1 + 1) / (1500 \cdot T_{cik}) =$                 |  |  |  |  |

| 0.8 · F <sub>clk</sub> · 10 <sup>-6</sup>                                                |  |  |  |  |

| The second program has a higher MIPS rate compared to the first. According to this index |  |  |  |  |

the second program should be faster!

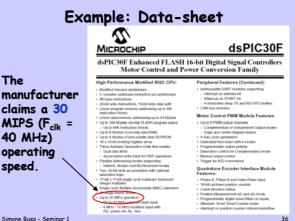

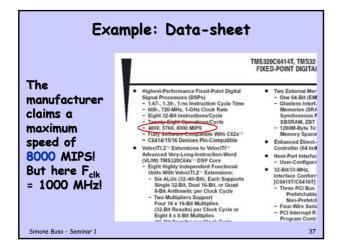

| Example: Data-sheet                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                  |                                     |                                                                                      |  |  |  |  |

|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------|--|--|--|--|

|                                                                                                   | MOTOROLA                                                                                                                                                                                                                                                                                                                                                                                                         |                                     |                                                                                      |  |  |  |  |

| The<br>manufacturer<br>claims a<br>maximum<br>speed of 40<br>MIPS (F <sub>clk</sub> =<br>80 MHz). | Technical Data   56F801 16-bit Hybrid Con   • Up to 30 MIPS operation at 60MHz core   • Up to 40 MIPS operation at 80MHz core   • Up to 40 MIPS operation at 80MHz core   • DSP and MCU functionality in a unified,<br>C-efficient architecture   • MCU-friendly instruction set supports both<br>DSP and controller functions: MAC, bit<br>manipulation unit, 14 addressing modes   • Hardware DO and REP loops | itrol<br>:<br>:<br>:<br>:<br>:<br>: | Ber<br>8K×16<br>1K×16<br>2K×16<br>2K×16<br>Serial P.<br>General<br>JTAG/G<br>On-chip |  |  |  |  |

| Simone Buso - Seminar 1                                                                           | 6-channel PWM Module                                                                                                                                                                                                                                                                                                                                                                                             |                                     | 38                                                                                   |  |  |  |  |