# MPC823ADSDB User's Manual

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, aspecifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights on the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and fits officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and (M) are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

© 1997 Motorola, Inc. All Rights Reserved.

PowerPC<sup>™</sup> is a registered trademark of IBM Corporation and is used by Motorola under license from IBM. I<sup>2</sup>C<sup>™</sup> is a registered trademark of Philips Corporation.

All other trademarks are the property of their respective owners.

# SECTION 1 INTRODUCTION

This document is the MPC823ADS daughterboard operation guide. The daughterboard encompasses the MPC823 device along with some necessary logic that must be close to the MPC823 and peripherals. These peripherals are dedicated to the MPC823, but are not necessarily required for any other member of the MPC8xx Family. The daughterboard has two sets of matching connectors—one set on the print side (on the bottom of the board) and one on the component side (on the top of the board). Those on the print side connect to a matching set found on the MPC8xxFADS, while those on the component side are to serve hardware expansion via a dedicated adaptor. Also a set of logic analyzer connectors is featured matching the new high-density HP16500 logic analyzer adaptors to provide fast connection to a logic analyzer while saving board space and reducing EMI.

#### 1.1 TERMINOLOGY

- ADI—Application Development Interface

- ADS—Application Development System

- · BCSR—Board Control and Status Register

- BGA—Ball Grid Array

- DB—Daughterboard

- GPCM—General-Purpose Chip-Select Machine

- GPL—General-Purpose Line (associated with the UPM)

- I/R-Infra-Red

- Spec—Engineering Specification Document

- UPM—User Programmable Machine

- ZIF—Zero Input Force

#### 1.2 RELATED DOCUMENTATION

- MPC823 User's Manual

- · ADI Board Specification

- MPC8xxFADS User's Manual

- Analog Devices' ADV7176 Data Sheet at http://www.analog.com/products/sheets/ ADV7176.html.

- Philip's PDIUSBP11 Data Sheet. May be obtained from http:// www.semiconductors.philips.com/acrobat/4417.pdf

MOTOROLA

MPC823ADSDB USER'S MANUAL

| ntroduction |  |  |

|-------------|--|--|

|             |  |  |

#### 1.3 SPECIFICATIONS

The MPC823ADS daughterboard specifications are shown in Table 1-1

Table 1-1. MPC823ADS Daughterboard Specifications

| CHARACTERISTICS                    | SPECIFICATIONS                                   |

|------------------------------------|--------------------------------------------------|

| Microprocessor                     | MPC823 @ 50MHz                                   |

| Addressing<br>Total address range: | 4G Internal<br>64M External*                     |

| Operating temperature              | 0°C – 30°C                                       |

| Storage temperature                | -25°C – 85°C                                     |

| Relative humidity                  | 5% – 90% (non-condensing)                        |

| Dimensions: Length Width Thickness | 5.87" (149mm)<br>4.37" (111mm)<br>0.063" (1.6mm) |

NOTE: \* denotes the maximum contiguous block of memory that may be accessed. It can reside, however, anywhere within the 4G addressing space.

#### 1.4 FEATURES

- MPC823 Operation At a Maximum 50MHz

- Onboard Video Support Using the AD7176 Video Encoder with Shutdown Option

- RGB, Composite and S-Video Connection Options

- LCD Panel Connection Support with 4-Bit per Color Support

- USB Port with Shutdown Option (BCSR-Controlled). Support for Both Type A and B USB Connectors.

- USB Port Speed Control (BCSR-driven)

- 5V Supply for USB Port (BCSR-controlled)

- Selectable KAPWR Source—3.3V or Externally Supplied

- Selectable VDDL Source—3.3V or 2.2V

- Selectable Clock Source—32768Hz Crystal Resonator or 4MHz Clock Generator That Can be Easily Changed to Any 3.3V-Powered Oscillator with a 3–5MHz Frequency Range

- On-Board Expansion Connectors, Including All MPC823 Pins and MPC8xxADS Control and Status Signals.

- Onboard High-Density Logic Analyzer Connectors That Support Fast Connection to HP16500 Logic Analyzer

- MPC821 Modem Tool Support

MPC823ADSDB USER'S MANUAL

MOTOROLA

LOGIC ANALYZER

CONNECTORS

MOTHERBOARD AND

EXPANSION CONNECTORS

AD7176

VIDEO

ENCODER

CLOCKS

RESULT A RESULT

Figure 1-1. MPC823ADS Daughterboard Block Diagram

#### 1.5 CHANGES FROM PREVIOUS REVISION (DRAFT 0.1)

- · Video controller is reset only by software via BCSR. Not affected by hard reset.

- Changed SCC2 port to MPC823ADS connection scheme. See **Section 4.7 Communication Ports** for more information.

- Added USB power control (BCSR-controlled) with power-on indication LED.

- Added 3.3V pull-up resistors over USB's D+ and D- lines. Connection scheme of these

resistors depends on USB port's speed. See Section 4.7.1 USB Port for more

information.

- Added support for MPC821 modem tool. See Section 4.8.1 MPC821 Modem Tool Support for more information.

- The selection of power-on reset source is moved onboard from the MPC8xxFADS.

- Part numbers are provided for all connectors.

Introduction

# SECTION 2 CONFIGURATION AND INSTALLATION

This section contains information about preparing, configuring, and installing the MPC823ADS daughterboard. When you receive your daughterboard, you should unpack the shipping carton and verify the contents against the packing list. If the contents were damaged during shipping, call your local Motorola sales office, explain the problem, and you should receive another package. If the contents are undamaged, save the packing slip and start configuring the board for your design.

**Caution:** Avoid touching the integrated circuitry of the board with your hands since static discharge can damage circuits.

#### 2.1 CONFIGURING THE BOARD

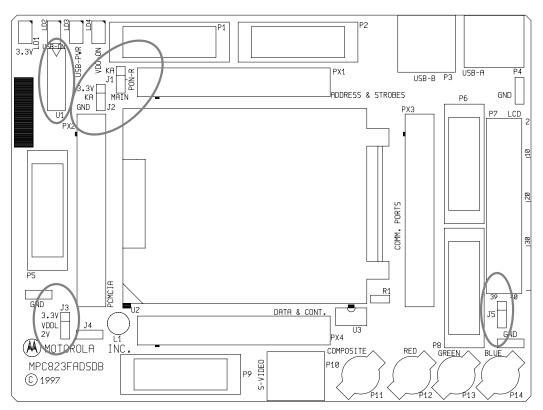

Before you configure the MPC823ADS daughterboard, you may have to change the jumpers settings before you can install the board into your system. Since they are factory set and tested, they may not be set correctly for your particular configuration. Figure 2-1 illustrates the location of these jumpers, LEDs, and connectors on the board. The MPC823ADS daughterboard settings contain the following parameters that you can change for your specific configuration:

- · Clock generator

- · Power-on reset source

- MPC823 keep-alive power source

- MPC823 internal logic supply source

- ADV7176 video controller's I2C free address bit

Configuration and Installation

Figure 2-1. MPC823ADS Daughterboard Top-Side Parts Locator

#### 2.1.1 Replacing the Clock Generator

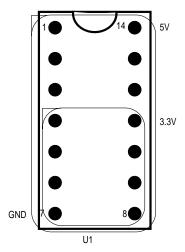

When replacing the clock generator (U1), all you need to know is that there are two supply levels. A 5V supply is available at Pin 14 and a 3.3V supply is available at Pin 11.

Configuration and Installation

Figure 2-2 illustrates that a 5V oscillator (with 3.3V output only) can be used with a 14-pin form-factor, while 3.3V oscillators can be used with an 8-pin form-factor.

Figure 2-2. Clock Generator (U1) Power Sources

Inserting a 14-pin form-factor 3.3V clock generator into U1 could cause permanent damage to your device. Since the MPC823 clock input is not 5V-tolerant, any clock generator inserted into U17 must have a 3.3V-compatible output. If you insert a 5V output clock generator into U17, you could cause permanent damage to the MPC823 microprocessor.

Configuration and Installation

#### 2.1.2 Selecting the Power-On Reset Source

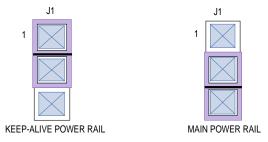

The functionality of the power-on reset logic changes with each revision of the MPC823. For your purposes, this means that you may need to select a different source to generate a power-on reset. To select your power-on reset source, you need to set J1 on the MPC823ADS daughterboard. When the J1 jumper is between positions 1 and 2, a power-on reset is generated by the keep-alive power rail (KAPWR). For example, when KAPWR goes below 2.005V, a power-on reset is generated. When the J1 jumper is between positions 2 and 3, a power-on reset is generated from the main 3.3V power rail. In other words, when the 3.3V power rail gets below 2.805V, a power-on reset is generated.

Figure 2-3. Power-On Reset Source

#### 2.1.3 Selecting the VDDL Source

The J3 jumper is used to select the VDDL, which supplies the MPC823's internal logic. When the J3 jumper is between positions 1 and 2, VDDL is supplied with 3.3V of power. When the J3 jumper is between positions 2 and 3, VDDL is supplied with 2.2V of power. The J3 jumper is factory set between positions 1 and 2.

Figure 2-4. VDDL Source

Configuration and Installation

#### 2.1.4 Selecting the Keep-Alive Power Source

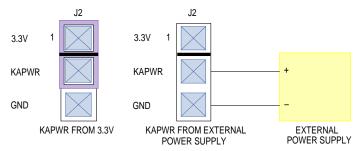

The J2 jumper is used to select the keep-alive power source. When the J2 jumper is between positions 1 and 2, the keep-alive power is fed from the main 3.3V bus. When you need to connect an external power source (such as a battery) to the keep-alive power rail, it should be connected between positions 2 (the positive pole) and 3 (GND) without any jumper connected.

Figure 2-5. Keep-Alive Power Source

#### 2.1.5 Selecting the ADV7176's I<sup>2</sup>C Slave Address

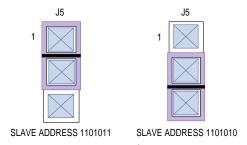

The ADV7176 video encoder has two possible slave addresses that can be selected using the J5 jumper. When J5 is between positions 1 and 2, the slave address is 1101011. When the jumper is between positions 2 and 3, the slave address is 1101010. The J5 jumper is factory set to positions 2 and 3.

Figure 2-6. ADV7176 I<sup>2</sup>C Slave Address

#### 2.2 INSTALLING THE DAUGHTERBOARD

To begin with, the MPC823ADS daughterboard must be plugged into the MPC8xxFADS motherboard. Make sure there is no power connected to either board. Place the MPC823ADS daughterboard over the motherboard connectors so that the PM1–PM4 of both boards are aligned. Then press the board gently into position. This process should be relatively unproblematic since the connectors are arranged in a nonsymmetrical form.

MOTOROLA

MPC823ADSDB USER'S MANUAL

# SECTION 3 OPERATION

This section contains the necessary information you need to operate the MPC823ADS daughterboard.

#### 3.1 INDICATORS

The MPC823ADS daughterboard does not have any switches, but it has eight indicators:

- · Four GND bridges

- A 3.3V indicator

- · A USB-On indicator

- · A USB power indicator

- · A VDO-On indicator

#### 3.1.1 GND Bridges

There are four GND bridges on the MPC823ADS daughterboard. They can be used to assist you with easy ground access points for general measurements and a logic analyzer connection.

Warning: The onboard GND bridges physically resemble the J4 jumper and you should take care not to mistake it for a GND jumper. Doing so could cause permanent damage to your MPC823ADS daughterboard or MPC8xxFADS motherboard. When you are connecting to a GND bridge, use only insulated GND clips to keep from damaging the board.

#### 3.1.2 3.3V Indicator

The yellow 3.3V LED (LD1) indicates that the 3.3V power bus is receiving power from the MPC823ADS board.

#### 3.1.3 USB-On Indicator

The yellow USB-On indicator LED (LD2) indicates that the USB transceiver is enabled for USB reception (the receive buffer is driven towards the MPC823). When it is not lit, the receive buffer is three-stated and the USB pins can be used for another function. See BCSR4 of the MPC8xxFADS User's Manual for more information.

MOTOROLA

MPC823ADSDB USER'S MANUAL

#### 3.1.4 USB-PWR Indicator

The yellow USB-PWR LED indicates that the 5V power is being driven to pin 1 of the USB connectors P3 and P4. When the it is not lit, it indicates that Pin 1 of these connectors is floating and the MPC823ADS daughterboard can be connected to an external USB master. See BCSR4 of the MPC8xxFADS User's Manual for more information.

#### 3.1.5 VDO On Indicator

When the yellow VDO On LED is lit, it may indicate that the video encoder is enabled on the  $I^2C^{\otimes}$  bus. This is a *soft* indication since the ADV7176 is enabled and disabled via the  $I^2C$  port. This indication allows your application software to visually indicate that the video encoder is on. See BCSR4 of the *MPC8xxFADS User's Manual* for more information.

#### 3.1.6 Memory Map

The memory map is the same on all daughterboards. See **Section 3.3 Memory Map** of the *MPC8xxFADS User's Manual* for more information.

#### 3.1.7 Programming the MPC8xx Registers

To program the MPC8xx registers, see **Section 3.1.7 Programming the MPC8xx Registers** of the *MPC8xxFADS User's Manual*.

# SECTION 4 FUNCTIONALITY

This section describes these main functions of the MPC823ADS daughterboard:

- Reset

- Interrupts

- · Clock generator

- · Video support

- · LCD panel support

- PCMCIA port

- · Communication ports and their expansion

- · Board control and status register

- · Debug port

#### 4.1 RESET

There are three sources of reset for the MPC823 device:

- · Power-on reset

- · Hard reset

- · Soft reset

#### 4.1.1 Power-On Reset

On the MPC823ADS daughterboard, a power-on reset can be generated from a keep-alive power bus or a main power bus. A jumper is used to select one of these sources. When you select the keep-alive power bus, a dedicated voltage detector made by Seiko (S-8051HN-CD-X), which has a detection voltage range of 1.795–2.005V, generates the power-on reset. During a keep-alive power-on, or when there is a voltage drop of that input into the above range, a power-on reset is generated (the PORESET input of the MPC823 is asserted for approximately 4 seconds).

When you select the main power bus, a dedicated voltage detector made by Seiko (S-8052ANY-NH-X), with a detection voltage range of 2.595–2.805V, generates the power-on reset. During a main 3.3V bus power-on, or when there is a voltage drop of that input into the above range, a power-on reset is generated (the PORESET input of the MPC823 is asserted for approximately 4 seconds). The main power-on reset also generates a power-on reset to all logic on the motherboard.

MOTOROLA

MPC823ADSDB USER'S MANUAL

| Functionality |  |

|---------------|--|

|---------------|--|

The power-on reset configuration is read by the MPC823 when PORESET is asserted to the MPC82. See **Section 4.1.6.1 Power-On Reset Configuration** of the *MPC8xxFADS User's Manual* for more information.

#### 4.1.2 Hard Reset

A hard reset is generated from four possible sources:

- A main power-on reset

- · A manual hard reset generated on the motherboard

- A debug port hard reset

- An internal source of the MPC823

When the open-drain HRESET signal is asserted, hard reset configuration data is driven on the data bus by the motherboard logic. See **Section 4.1.6.2 Hard Reset Configuration** of the *MPC8xxFADS User's Manual* for details.

#### 4.1.3 Soft Reset

A soft reset is generated from three possible sources:

- The debug port controller on the motherboard

- · A manual soft reset generated on the motherboard

- An internal source of the MPC823

The motherboard logic makes a soft reset configuration available to the MPC823 when a soft reset is generated to the MPC823. See **Section 4.1.6.2 Soft Reset Configuration** of the *MPC8xxFADS User's Manual* for details.

#### 4.2 INTERRUPTS

The only external interrupt that is applied to the MPC823 via its interrupt controller is the abort (NMI) interrupt, which is generated by a push-button and logic residing on the motherboard.

#### **4.3 CLOCK GENERATOR**

Although most of the clock generator logic is found on the daughterboard, it is explained in detail in the motherboard manual since it is common to all daughterboards. See **Section 4.3 Clock Generator** of the *MPC8xxFADS User's Manual* for more information.

**Functionality**

#### 4.4 VIDEO SUPPORT

The MPC823ADS daughterboard has full onboard support for video. A direct connection can be made between the MPC823ADS daughterboard and a video monitor supporting either RGB, Composite or S-Video input standards.

The Analog Devices ADV7176, which is an NTSC/PAL video encoder, can be controlled by the MPC823 I<sup>2</sup>C port. Since an I<sup>2</sup>C slave has a unique address, you can connect another I<sup>2</sup>C slave with the expansion connector without any buffering. The ADV7176 can be put in low-power mode while another I2C device is used offboard via the expansion connectors. The ADV7176 is clocked by an onboard 27MHz clock generator (U11), which can be three-stated with the VDOEXTCK signal from the motherboard's board control and status register 4 (BCSR4). When the clock generator is disabled (three-stated), the MPC823 can clock the ADV7176 if 27MHz can be achieved using a multiplication factor (MF).

Warning: If U1 is enabled and the MPC823 drives the PD3/VDOCLK signal to the ADV7176, it could cause permanent damage to the MPC823 and 27MHz clock generator.

Using BCSR4's VDORST signal, the software can reset the video encoder. Notice that this is a falling-edge reset, instead of a level-sensitive reset. The video encoder supports three types of video inter-connects:

- · S-Video via the P10 connector on the daughterboard

- Composite video via the P11 connector on the daughterboard

- RGB video via the P12–P14 connectors on the daughterboard

You can enable or disable the video encoder at any time via its I<sup>2</sup>C port. For more information see the ADV7176 data sheet for more information.

#### 4.4.1 ADV7176 Power Considerations

The ADV7176 is an analog device, which requires a *quiet* power supply. Therefore, its power supply is filtered by a  $\Pi$  network and is isolated from the noisy digital supply. The ground of the device is isolated from the digital ground by means of a peninsula to avoid noisy digital GND currents. The D/As of the ADV7176 require a stable and clean 1.2V voltage reference, which can be obtained from U3 (an AD589 voltage reference device).

#### 4.5 LCD PANEL SUPPORT

A dedicated LCD connector is provided with your board to allow connection to an LCD panel. This connector contains the MPC823 Port D pins and any additional LCD Port B pins. When the video encoder is in low-power mode, you can connect to an LCD panel with the port D pin and three Port B pins (the Port B pins add 1 bit per color which makes it a 4,4,4 color word). The LCD connector is a superset of the LCD connector that exists on the MPC821ADS, which makes it easy to move tools between the two boards and to connect the additional color bits.

**MOTOROLA**

MPC823ADSDB USER'S MANUAL

To make connecting even easier, there are 5V supply pins available on the additional pins of the LCD connector. For a signal description of the LCD connector, see Table 5-8 in this manual.

#### 4.6 PCMCIA PORT

The MPC823 has only one PCMCIA port and it resides on the PCMCIA port B pins. It is routed to the PCMCIA port on the MPC823AADS. The default hard reset configuration of the MPC823ADS sets up these pins as PCMCIA port B pins.

The PCMCIA port on the MPC823ADS is intended to reside on the PCMCIA port A of the MPC823. Therefore, there is a cross between PCMCIA ports A and B on the motherboard connectors. The port B signals are connected in the same place that is reserved for the PCMCIA port A pins. For more information, see **Section 4.10 PCMCIA Port** of the *MPC8xxFADS User's Manual*.

#### 4.7 COMMUNICATION PORTS

The MPC823 has the following communication ports that can be used in a variety of ways on the MPC823ADS daughterboard:

- · A USB port that is connected to a USB transceiver onboard

- A serial communication controller (SCC2) that can operate as an Ethernet port, an infra-red port (IrDA), or an RS-232 port #2.

- A serial management controller (SMC1) that is connected to RS-232 port #1 of the MPC823ADS

- A serial management controller (SMC2) that is not used onboard.

- An inter-integrated circuit (I<sup>2</sup>C) that is used to program the video encoder

- · A serial peripheral interface (SPI) that is not used onboard

Using BCSR1 or BCSR4, the software can enable or disable all of the communication ports. See BCSR1 and BCSR4 in the MPC8xxFADS User's Manual for details.

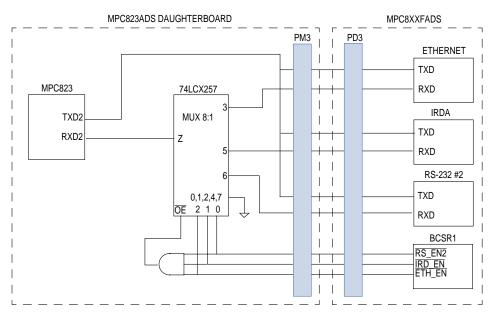

To protect against possible contention, the RxD lines of the Ethernet port, IrDA port, and RS-232 port #2 of the MPC823ADS are multiplexed to the RXD2 input. Use the appropriate enable bits in the BCSR1 to select between the three RxD lines. When one and only one of the  $\overline{ETH_EN}$ ,  $\overline{IRD_EN}$ , or  $\overline{RS_EN2}$  bits in the BCSR1 is enabled, its respective communication port RxD line is driven to RXD2 of the MPC823. If two or more of these lines are simultaneously enabled and then 0 is driven to RXD2. When none of them are asserted, the output of the mux is three-stated and the RXD2 line of the MPC823 can be used for another function.

Functionality

Figure 4-1 illustrates how to connect Ethernet, IrDA, and RS-232 Serial Port #2 is connected to the SCC2 and selection is accomplished.

Figure 4-1. SCC2 Connection Scheme

#### **4.7.1 USB Port**

The universal serial bus (USB) port resides on the MPC823ADS daughterboard and is driven by the USB port of the MPC823. A dedicated USB transceiver (the PDIUSBP11 by Philips) is provided with the daughterboard. Also provided is a three-state buffer that separates this port from the MPC823's USB port, so that you can disable a port and use the MPC823 USB pins offboard.

To properly support the different speeds of the USB, the detachable 3.3V pull-up resistors are provided on the D+ and D- lines of the USB. They are controlled by the USB\_SPD bit of the BCSR4. When the USB\_SPD bit is in low-speed mode, D- is pulled up while D+ continues to float. When the USB\_SPD bit is in high-speed mode, D+ is pulled up while D-continues to float. The USB\_SPD bit is connected to the SPEED input of the USB transceiver, which sets it to the preferred operation range.

In Revision ENG, a 5V power source is provided to the USB connector and it is controlled by the USB\_VCC0 bit in the BCSR4. When the USB\_VCC0 bit is driven low, a 5V source is connected to Pin 1 of the USB connectors.

To support both types of physical connections, two USB connectors (Type A and Type B) are provided in parallel. For additional information on USB pin connection to those connectors, see BCSR4 later in this manual.

MOTOROLA

MPC823ADSDB USER'S MANUAL

| Functionality |  |

|---------------|--|

|               |  |

#### 4.7.2 Ethernet Port

The SCC2 of the MPC823 can operate as an Ethernet port. It can be connected to the ethernet transceiver on the MPC823ADS if the ETH\_EN bit of the BCSR1 is asserted and the IRD\_EN and RS\_EN2 bits in the same register are inactive. For more information, see **Section 4.11.3 Board Control and Status Register 1** of the *MPC8xxFADS User's Manual*.

#### 4.7.3 Infra-Red Port

The SCC2 of the MPC823 can operate as a fast IrDA port. It can be connected to the fast IrDA transceiver on the MPC823ADS if the IRD\_EN bit of the BCSR1 is asserted and the ETH\_EN and RS\_EN2 bits in the same register are inactive. For more information, see **Section 4.11.3 Board Control and Status Register 1** and **Section 4.9.2 Infra-Red Port** of the MPC8xxFADS User's Manual.

#### 4.7.4 RS-232 Ports

There can be two RS-232 ports with this application. The RS-232 port #1 of the MPC823ADS is connected to the SMC1 of the MPC823. The RS-232 port #2 of the MPC823ADS can be connected to the SCC2 of the MPC823 if the RS\_EN2 bit in the BCSR1 is asserted and the ETH\_EN and IRD\_EN bits in the same register are inactive.

Both ports can be enabled or disabled at any time using the BCSR1. For more information, see **Section 4.11.3 Board Control and Status Register 1** and **Section 4.9.3 RS-232 Port** of the *MPC8xxFADS User's Manual*.

#### 4.8 COMMUNICATION PORT EXPANSION

On the MPC823ADS board, all of the MPC821 and MPC860 communication port pins were available at a 96-pin DIN 41612 connector (P13). This connector is compatible with P8 of the MPC8xxFADS. Since the MPC823 has a unique and partial set of communication ports, the pin assignment is different. Therefore, it is important that you carefully examine any tool you create for this connector before it is connected to an MPC8xxFADS with a daughterboard attached to it.

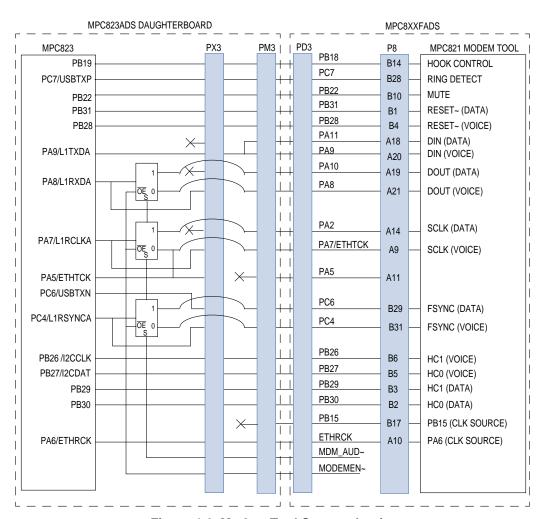

#### 4.8.1 MPC821 Modem Tool Support

The MPC821 modem tool uses the MPC821 time-slot assigner (TSA) TDM ports A and B. However, the MPC823 has only one TDM port. Therefore, the data portion of the tool, which originally used TDM port B, is now multiplexed with the voice portion so that they both reside on TDM port A of the MPC823. To support this multiplexing, two signals are introduced from the MPC823ADS; MODEM\_EN, which enables the mux, and MDM\_AUD, which selects between the data and voice codecs of the modem tool.

Functionality

Figure 4-2 illustrates the modem tool support logic.

Figure 4-2. Modem Tool Support Logic

| Functionality |  |

|---------------|--|

|---------------|--|

Before operating the modem tool, the following conditions should be met.

- The Ethernet, USB, and video ports must be disabled since they only use a few lines that are common to the modem application. These ports must be disabled when their respective enable bits in the BCSR1 and BCSR4 are negated. This does not apply for the video encoder, however, which is enabled and disabled with the I²C port. The video encoder uses the I²C port for initializations, but once they are complete the port can be used for other applications.

- Use PB19 for hook control, instead of PB18, which was used with the MPC821.

- Assert the MODEM\_EN bit in the BCSR4. For more information, see BCSR4 in the MPC8xxFADS User's Manual.

- With the MPC821, one of the optional clock sources for the modem was PB15, which

does not exist on the MPC823. Since it was not used with the working application, no

replacement was provided for this signal and it remains unconnected.

- To select between the voice and data portions of the modem, set the MDM\_AUD bit in the BCSR4. For more information, see BCSR4 in the MPC8xxFADS User's Manual).

#### 4.9 BOARD CONTROL AND STATUS REGISTER

Most board control and status register (BCSR) control signals and some status signals are available on the motherboard connectors and the expansion connectors. The BCSR controls most of the functions available on the MPC823ADS daughterboard and on the MPC8xxFADS. See **Section 4.11 Board Control and Status Register** of the *MPC8xxFADS User's Manual* for more information.

#### 4.10 DEBUG PORT

The MPC823 uses the motherboard connectors to connect to the MPC823ADS board's debug port controller. For details, see **Section 4.12 Debug Port Controller** in the MPC8xxFADS User's Manual.

The debug port on the daughterboard resides on the MPC823 JTAG port. There is no support for the debug port to reside on the PCMCIA port B pins. Since the VFLS[0:1] pins, which are usually required by the debug port controller to monitor the run/debug mode status, are being used for PCMCIA port B, you must use the FRZ signal that is connected to the MPC823ADS debug port controller.

# SECTION 5 SIGNAL DESCRIPTIONS

This section contains signal information for supporting, maintaining, and connecting to the MPC823ADS daughterboard.

#### 5.1 INTERCONNECT SIGNALS

The MPC823ADS daughterboard uses the following connectors to interconnect with external devices.

- P1, P2, P5, P6, P8, and P9—Logic analyzer connectors

- P3 and P4—USB connectors

- P7—LCD panel connector

- P10, P11, P12, P13, and P14—Video connectors

- PM1, PM2, PM3, and PM4—Motherboard connectors

- PX1, PX2, PX3, and PX4—Expansion connectors

- MPC823ADS P8—Serial port expansion connector<sup>1</sup>

#### 5.1.1 P1, P2, P5, P6, P8, and P9-Logic Analyzer Connectors

These connectors are 38-pin, receptacle MICTOR connectors manufactured by AMP. Each connector connects to a dedicated adaptor for an HP16500 Series logic analyzer, which interconnects to two 16-bit pods. Since all the signals on these connectors are also on the motherboard connectors and expansion connectors, they are described in the MPC823 User's Manual as well.

MOTOROLA

MPC823ADSDB USER'S MANUAL

<sup>1.</sup> This connector is located on the motherboard. It is documented here since its contents depends on the daughterboard.

Signal Descriptions

**Table 5-1. P1 Interconnect Signals**

| PIN NUMBER | SIGNAL | PIN NUMBER | SIGNAL |

|------------|--------|------------|--------|

| 1          | _      | 2          | _      |

| 3          | GND    | 4          | _      |

| 5          | TEA    | 6          | BSWE0  |

| 7          | SDRMCS | 8          | BOWLO  |

| 9          | CS5    | 10         | BSWE1  |

| 11         | CE1B   | 12         | BSWE2  |

| 13         | CE2B   | 14         | BSWE3  |

| 15         | BR     | 16         | DRM_W  |

| 17         | BG     | 18         | EDOOE  |

| 19         | BB     | 20         | GPL2   |

| 21         | BI     | 22         | GPL3   |

| 23         | BURST  | 24         | GPL4A  |

| 25         | _      | 26         | GPL4B  |

| 27         | _      | 28         | GPL5A  |

| 29         | BVS2   | 30         | GPL5B  |

| 31         | BVS1   | 32         | F_CS   |

| 33         | BWP    | 34         | BCSRCS |

| 35         | BCD2   | 36         | DRMCS1 |

| 37         | BCD1   | 38         | DRMCS2 |

Signal Descriptions

Table 5-2. P2 Interconnect Signals

| PIN NUMBER | SIGNAL     | PIN NUMBER | SIGNAL |

|------------|------------|------------|--------|

| 1          | <b>—</b> . | 2          | _      |

| 3          | GND        | 4          | _      |

| 5          | TA         | 6          | TS     |

| 7          | 10         | 8          | A16    |

| 9          | TS         | 10         | A17    |

| 11         | TA         | 12         | A18    |

| 13         | R_₩        | 14         | A19    |

| 15         | REG_A      | 16         | A20    |

| 17         | TSIZ1      | 18         | A21    |

| 19         | A6         | 20         | A22    |

| 21         | A7         | 22         | A23    |

| 23         | A8         | 24         | A24    |

| 25         | A9         | 26         | A25    |

| 27         | A10        | 28         | A26    |

| 29         | A11        | 30         | A27    |

| 31         | A12        | 32         | A28    |

| 33         | A13        | 34         | A29    |

| 35         | A14        | 36         | A30    |

| 37         | A15        | 38         | A31    |

Signal Descriptions

**Table 5-3. P5 Interconnect Signals**

| PIN NUMBER | SIGNAL  | PIN NUMBER | SIGNAL |

|------------|---------|------------|--------|

| 1          | _       | 2          | _      |

| 3          | GND     | 4          | _      |

| 5          | _       | 6          | _      |

| 7          | DSCK    | 8          | DSDI   |

| 9          | BBVD2   | 10         | _      |

| 11         | BBVD1   | 12         | DSDO   |

| 13         | BRDY    | 14         | FRZ    |

| 15         | ALE_B   | 16         | NMI    |

| 17         | SPKROUT | 18         | ĪRQ1   |

| 19         | MODCK1  | 20         | ĪRQ2   |

| 21         | MODCK2  | 22         | ĪRQ7   |

| 23         | WAIT_B  | 24         | _      |

| 25         | RSTCNF  | 26         | EXTCLK |

| 27         | TEXP    | 28         | _      |

| 29         | HRESET  | 30         | DP0    |

| 31         | SRESET  | 32         | DP1    |

| 33         | PORST   | 34         | DP2    |

| 35         | _       | 36         | DP3    |

| 37         | _       | 38         | V3.3   |

**Table 5-4. P6 Interconnect Signals**

| PIN NUMBER | SIGNAL | PIN NUMBER | SIGNAL |

|------------|--------|------------|--------|

| 1          | _      | 2          | _      |

| 3          | GND    | 4          | _      |

| 5          | _      | 6          | SYSCLK |

| 7          | USBRXD | 8          |        |

| 9          | USBOE  | 10         | _      |

| 11         | USBRXP | 12         | _      |

| 13         | USBRXN | 14         | _      |

| 15         | USBTXP | 16         | PC12   |

| 17         | USBTXN | 18         | TPSQEL |

| 19         | TXD2   | 20         | PC14   |

| 21         | RXD2   | 22         | BINPAK |

| 23         | TMS    | 24         | _      |

| 25         | I2CDAT | 26         | SPARE2 |

| 27         | I2CCLK | 28         | _      |

| 29         | PB28   | 30         | RSDTR1 |

| 31         | PB29   | 32         |        |

| 33         | PB30   | 34         | RSDTR2 |

| 35         | LCD_A  | 36         | RSRXD1 |

| 37         | TRST   | 38         | RSTXD1 |

Signal Descriptions

**Table 5-5. P8 Interconnect Signals**

| PIN NUMBER | SIGNAL  | PIN NUMBER | SIGNAL |

|------------|---------|------------|--------|

| 1          | _       | 2          | -      |

| 3          | GND     | 4          | _      |

| 5          | _       | 6          | VDOCLK |

| 7          | _       | 8          | VDOCER |

| 9          | _       | 10         | _      |

| 11         | PA4     | 12         | _      |

| 13         | ETHTCK  | 14         | HSYNC  |

| 15         | ETHRCK  | 16         | VSYNC  |

| 17         | PA7     | 18         | BLANK  |

| 19         | PA8     | 20         | FIELD  |

| 21         | PA9     | 22         | VD0    |

| 23         | ETHLOOP | 24         | VD1    |

| 25         | TPFLDL  | 26         | VD2    |

| 27         | E_RENA  | 28         | VD3    |

| 29         | E_CLSN  | 30         | VD4    |

| 31         | PB16    | 32         | VD5    |

| 33         | LCD_C   | 34         | VD6    |

| 35         | E_TENA  | 36         | VD7    |

| 37         | LCD_B   | 38         | SPARE3 |

Signal Descriptions

Table 5-6. P9 Interconnect Signals

|               |        | i          |        |

|---------------|--------|------------|--------|

| PIN<br>NUMBER | SIGNAL | PIN NUMBER | SIGNAL |

| 1             | _      | 2          | _      |

| 3             | GND    | 4          | _      |

| 5             | _      | 6          |        |

| 7             | D0     | 8          | D16    |

| 9             | D1     | 10         | D17    |

| 11            | D2     | 12         | D18    |

| 13            | D3     | 14         | D19    |

| 15            | D4     | 16         | D20    |

| 17            | D5     | 18         | D21    |

| 19            | D6     | 20         | D22    |

| 21            | D7     | 22         | D23    |

| 23            | D8     | 24         | D24    |

| 25            | D9     | 26         | D25    |

| 27            | D10    | 28         | D26    |

| 29            | D11    | 30         | D27    |

| 31            | D12    | 32         | D28    |

| 33            | D13    | 34         | D29    |

| 35            | D14    | 36         | D30    |

| 37            | D15    | 38         | D31    |

Signal Descriptions

#### 5.1.2 P3 and P4-USB Connectors

The MPC823ADS daughterboard supports both Type A and Type B USB connectors. P3 is Type B and P4 is Type A (both of which are manufactured by AMP). Their pinout is identical and their signals are shown in Table 5-7.

Table 5-7. P3 and P4 Interconnect Signal

| PIN NUMBER | SIGNAL | INPUT/OUTPUT | DESCRIPTION                                                                                                                                                                                                                                                                |

|------------|--------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | USBPWR | 0            | USB Power. To support USB Host function, this pin can be driven with a 5V BCSR–controlled source. See BCSR4 in the MPC8xxFADS User's Manual for more information. When the MPC823 daughterboard is configured as a USB slave, the power should be turned off for that pin. |

| 2          | D-     | I/O          | USB negative (differential) data line.                                                                                                                                                                                                                                     |

| 3          | D+     | I/O          | USB positive (differential) data line.                                                                                                                                                                                                                                     |

| 4          | GND    | _            | MPC823 daughterboard Ground plane.                                                                                                                                                                                                                                         |

#### 5.1.3 P7-LCD Panel Connector

The LCD panel connector is a 40-pin (2x20) header connector, which is compatible with the LCD panel connector that is on the MPC821ADS, plus an expansion to support the 4-bit per color added for the MPC823. To allow for an easier migration for MPC821 users, the signals are assigned so that panels that were connected to the MPC821ADS can be connected directly. The P7 are shown in Table 5-8.

Table 5-8. P7 Interconnect Signals

| PIN<br>NUMBER | SIGNAL  | INPUT/OUTPUT | DESCRIPTION                                                    |

|---------------|---------|--------------|----------------------------------------------------------------|

| 1             | SHIFT_C | I/O          | LCD Shift Clock                                                |

| 2             |         |              |                                                                |

| 3             | GND     | _            | _                                                              |

| 4             |         |              |                                                                |

| 5             | LOE     | I/O          | Output Enable for TFT Displays or Passive Panels LCD_AC Signal |

| 6             | GND     | _            | _                                                              |

| 7             | HSYNC   | I/O          | Display Line Beginning Mark                                    |

| 8             | GND     | _            | _                                                              |

| 9             | VSYNC   | I/O          | New Frame Beginning Mark                                       |

| 10            |         |              |                                                                |

| 11            | GND     | _            | _                                                              |

| 12            |         |              |                                                                |

| 13            | LD0     | I/O          | LCD Data Line 0                                                |

| 14            | GND     | _            | _                                                              |

MPC823ADSDB USER'S MANUAL

MOTOROLA

Signal Descriptions

Table 5-8. P7 Interconnect Signals (Continued)

| PIN<br>NUMBER | SIGNAL | INPUT/OUTPUT | DESCRIPTION                                                       |

|---------------|--------|--------------|-------------------------------------------------------------------|

| 15            | LD1    | I/O          | LCD Data Line 1                                                   |

| 16            | GND    | _            | _                                                                 |

| 17            | LD2    | I/O          | LCD Data Line 2                                                   |

| 18            | GND    | _            | _                                                                 |

| 19            | LD3    | I/O          | LCD Data Line 3                                                   |

| 20            | GND    | _            | _                                                                 |

| 21            | LD4    | I/O          | LCD Data Line 4                                                   |

| 22            | GND    | _            | _                                                                 |

| 23            | LD5    | I/O          | LCD Data Line 5                                                   |

| 24            | GND    | _            | _                                                                 |

| 25            | LD6    | I/O          | LCD Data Line 6                                                   |

| 26            | GND    | _            | _                                                                 |

| 27            | LD7    | I/O          | LCD Data Line 7                                                   |

| 28            | GND    | _            | _                                                                 |

| 29            | LD8    | I/O          | LCD Data Line 8                                                   |

| 30            | GND    | _            | _                                                                 |

| 31            |        |              |                                                                   |

| 32            | _      | _            | Pin is Cut to Allow 30-Pin Connector Insertion                    |

| 33            |        |              |                                                                   |

| 34            |        |              |                                                                   |

| 35            | LCD_A  | I/O          | Mux'ed on PB31. The MSB for the LCD Data Word.                    |

| 36            | VCC    | 0            | 5V Supply                                                         |

| 37            | LCD_B  | I/O          | Mux'ed on PB19. The Middle of the Additional Three LCD Data Bits. |

| 38            | VCC    | 0            | 5V Supply                                                         |

| 39            | LCD_C  | I/O          | Mux'ed on PB17. The LSB of the Additional Three LCD Data Bits.    |

| 40            | VCC    | 0            | 5V Supply                                                         |

MOTOROLA

MPC823ADSDB USER'S MANUAL

| Signal Descriptions |  |

|---------------------|--|

|---------------------|--|

#### 5.1.4 P10, P11, P12, P13, and P14-Video Connectors

The following connectors support various standards in video connectivity:

- P10 is a 4-pin subminiature DIN connector that conforms to the S-Video standard

- P11 is a coaxial RCA connector that carries composite video

- P12, P13, and P14 carry red, green, and blue (RGB) video signals (correspondingly)

The signals are shown in Tables 5-9 through 5-13 below.

Table 5-9. P10 Interconnect Signals

| PIN NUMBER | SIGNAL       | INPUT/OUTPUT | DESCRIPTION                                                                                                                        |

|------------|--------------|--------------|------------------------------------------------------------------------------------------------------------------------------------|

| 1          | _            | _            | Unused. Nonexistent with This Connector, Although Counted for Pin<br>Numbering. This Connector is a Subset of the DIN-8 Connector. |

| 2          |              |              | Numbering. This connector is a Subset of the Diff-6 Connector.                                                                     |

| 3          | GND          |              | _                                                                                                                                  |

| 4          |              | _            | Unused. Nonexistent with This Connector, Although Counted for Pin Numbering. This Connector is a Subset of the DIN-8 Connector.    |

| 5          | GND          | _            | _                                                                                                                                  |

| 6          | Green/Luma/Y | 0            | Luma signal. From the ADV7176 Video Encoder.                                                                                       |

| 7          | 1            | l            | Unused. Nonexistent with This Connector, Although Counted for Pin Numbering. This Connector is a Subset of the DIN-8 Connector.    |

| 8          | Red/Chroma/V | 0            | Chroma signal.                                                                                                                     |

Table 5-10. P11 Interconnect Signals

| PIN NUMBER | SIGNAL    | INPUT/OUTPUT | DESCRIPTION                                    |

|------------|-----------|--------------|------------------------------------------------|

| 1          | GND       | _            | _                                              |

| 2          | Composite | 0            | Composite Video from the ADV7176 Video Encoder |

|  | Signal Descriptions |

|--|---------------------|

|--|---------------------|

**Table 5-11. P12 Interconnect Signals**

|   | PIN NUMBER | SIGNAL       | INPUT/OUTPUT | DESCRIPTION                                                  |

|---|------------|--------------|--------------|--------------------------------------------------------------|

| Ī | 1          | GND          | _            | _                                                            |

|   | 2          | Red/Chroma/V | 0            | Red Component of RGB. Generated by the ADV7176 Video Encoder |

#### **Table 5-12. P13 Interconnect Signals**

| PIN<br>NUMBER | SIGNAL       | INPUT/OUTPUT | DESCRIPTION                                                     |

|---------------|--------------|--------------|-----------------------------------------------------------------|

| 1             | GND          | _            | _                                                               |

| 2             | Green/Luma/Y | 0            | Green Component of RGB. Generated by the ADV7176 Video Encoder. |

#### **Table 5-13. P14 Interconnect Signals**

| PIN<br>NUMBER | SIGNAL           | INPUT/OUTPUT | DESCRIPTION                                                    |

|---------------|------------------|--------------|----------------------------------------------------------------|

| 1             | GND              | _            | _                                                              |

| 2             | Blue/Composite/U | 0            | Blue Component of RGB. Generated by the ADV7176 Video Encoder. |

MOTOROLA

MPC823ADSDB USER'S MANUAL

Signal Descriptions

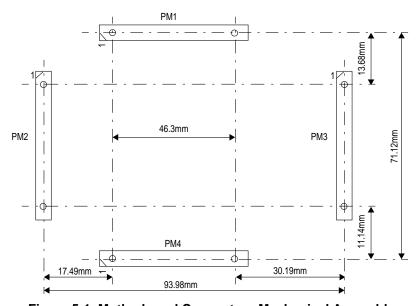

#### 5.1.5 PM1 to PM4-Motherboard Connectors

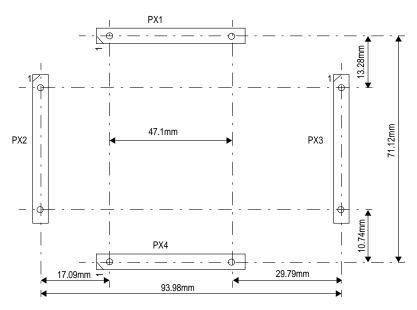

These connectors, which connect to their mates on the motherboard, are 140-pin interboard, male connectors manufactured by Molex. These connectors are arranged in a square shape to provide the shortest PCB routes possible. As shown in Figure 5-1, the connectors are not in a perfectly symmetrical shape. This prevents you from inserting the daughterboard incorrectly.

Figure 5-1. Motherboard Connectors Mechanical Assembly

| Sigr | nal Descriptions |

|------|------------------|

|------|------------------|

The motherboard connectors' signals are shown in Tables15-14 through 15-17.

**Table 5-14. PM1 Interconnect Signals**

| Table 5-14. PWT interconnect Signals |        |              |                                                                                                                                                                          |  |  |

|--------------------------------------|--------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PIN NUMBER                           | SIGNAL | INPUT/OUTPUT | DESCRIPTION                                                                                                                                                              |  |  |

| 1                                    | BB     | I/O, L       | Bus Busy signal. Pulled up on the MPC823ADS.                                                                                                                             |  |  |

| 2                                    | VCC    | _            | _                                                                                                                                                                        |  |  |

| 3                                    | DRM_W  | I,L          | GPL0 lines used as R/W signal for the DRAM SIMM or as an A10 line for the SDRAM                                                                                          |  |  |

| 4                                    | VCC    | _            | 5V Bus                                                                                                                                                                   |  |  |

| 5                                    | TEA    | I/O, L, O.D. | Transfer Error Acknowledge. Pulled up, not driven on board.                                                                                                              |  |  |

| 6                                    | VCC    | _            | _                                                                                                                                                                        |  |  |

| 7                                    | BR     | I/O,L        | Bus Request signal. Pulled up on the MPC823ADS, but otherwise unused.                                                                                                    |  |  |

| 8                                    | VCC    | _            | _                                                                                                                                                                        |  |  |

| 9                                    | BURST  | I/O, L       | Burst indication. Pulled up on the MPC823ADS, but otherwise unused.                                                                                                      |  |  |

| 10                                   | VCC    | _            | _                                                                                                                                                                        |  |  |

| 11                                   | GPL4A  | X,L          | UPMA General-Purpose Line 4. Not used on the MPC8xxFADS.                                                                                                                 |  |  |

| 12                                   | VCC    | _            | _                                                                                                                                                                        |  |  |

| 13                                   | TA     | I/O, L       | Transfer Acknowledge signal. Indicates end of bus cycle, used with MPC823ADS logic.                                                                                      |  |  |

| 14                                   | VCC    | _            | _                                                                                                                                                                        |  |  |

| 15                                   | TS     | I/O, L       | Transfer Start signal. Pulled up, but otherwise unused on the MPC823ADS.                                                                                                 |  |  |

| 16                                   | VCC    |              |                                                                                                                                                                          |  |  |

| 17                                   | GPL5B  | O, L         | General-Purpose Line 5 of UPMB. Not used on the MPC823ADS.                                                                                                               |  |  |

| 18                                   | VCC    |              |                                                                                                                                                                          |  |  |

| 19                                   | BG     | I/O, L       | Bus Grant signal. Pulled up on the MPC823ADS, but otherwise unused.                                                                                                      |  |  |

| 20                                   | VCC    |              |                                                                                                                                                                          |  |  |

| 21                                   | GPL4B  | O, L         | General-Purpose Line 4 of UPMB. Not used on the MPC823ADS.                                                                                                               |  |  |

| 22                                   | VCC    |              |                                                                                                                                                                          |  |  |

| 23                                   | R_W    | I/O, L       | Read/Write signal. Pulled up on the MPC823ADS and used by MPC8xxFADS logic.                                                                                              |  |  |

| 24                                   | VCC    |              |                                                                                                                                                                          |  |  |

| 25                                   | BCSRCS | I/O, L       | CST of the MPC823. Used as chip-select for the BCSRs. Pulled up. When BCSR is removed from the local map, this signal can be used offboard via the expansion connectors. |  |  |

| 26                                   | VCC    | 0            | 5V bus.                                                                                                                                                                  |  |  |

| 27                                   | GPL5A  | X,L          | UPMA General-Purpose Line 5. Not used on the MPC823ADS.                                                                                                                  |  |  |

| 28                                   | VCC    | 0            | 5V bus.                                                                                                                                                                  |  |  |

|                                      |        |              |                                                                                                                                                                          |  |  |

MOTOROLA

MPC823ADSDB USER'S MANUAL

Signal Descriptions

**Table 5-14. PM1 Interconnect Signals (Continued)**

| PIN NUMBER | SIGNAL | INPUT/OUTPUT | DESCRIPTION                                                                                                                                                                                                                                                               |

|------------|--------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29         | BI     | I/O,L        | Burst Inhibit signal. Pulled up, but otherwise unused on the MPC823ADS.                                                                                                                                                                                                   |

| 30         | _      | _            | Not Connected. Reserved.                                                                                                                                                                                                                                                  |

| 31         | CE2B   | O,L          | PC-card Enable 2. Enables odd address bytes. Connected to the MPC823ADS PC-card control logic.                                                                                                                                                                            |

| 32         | GND    | _            | MPC8xxFADS Ground plane.                                                                                                                                                                                                                                                  |

| 33         | CS5    | O, L         | Chip-Select line 5. Not used on the MPC823ADS.                                                                                                                                                                                                                            |

| 34         | GND    | _            | _                                                                                                                                                                                                                                                                         |

| 35         | CE1B   | I, L         | PC-card Enable 1 for PCMCIA slot B. Enables the even address bytes. Connected to the MPC823ADS PC-card control logic.                                                                                                                                                     |

| 36         | GND    | _            | _                                                                                                                                                                                                                                                                         |

| 37         | F_CS   | I/O, L       | Chip-select Line 0. Used as chip-select for the flash SIMM on the MPC823ADS. Pulled up on the motherboard. When the flash is disabled via the BCSR, this signal can be used offboard via the expansion connectors.                                                        |

| 38         | GND    | _            | _                                                                                                                                                                                                                                                                         |

| 39         | CE1B   | O, L         | See pin 35. Duality exists since the MPC823 uses slot B controls for the MPC823ADS PC-card, originally residing over slot A.                                                                                                                                              |

| 40         | GND    | _            | _                                                                                                                                                                                                                                                                         |

| 41         | CE2B   | O, L         | See pin 31. Duality exists since the MPC823 uses slot B controls for the MPC823ADS PC-card, originally residing over slot-A                                                                                                                                               |

| 42         | GND    | _            | _                                                                                                                                                                                                                                                                         |

| 43         | DRMCS2 | I/O, L       | Chip-Select Line 3. Used as chip-select line for the second bank of the DRAM SIMM. Pulled up on the motherboard. When the DRAM is disabled via the BCSR, or when a single bank of DRAM SIMM is being used, this signal can be used offboard via the expansion connectors. |

| 44         | GND    | _            | _                                                                                                                                                                                                                                                                         |

| 45         | DRMCS1 | I/O, L       | Chip-Select Line 2. Used as chip-select line for the first bank of the DRAM SIMM. Pulled up on the motherboard. When the DRAM is disabled via the BCSR, thsi signal can be used offboard via the expansion connectors.                                                    |

| 46         | GND    | _            | _                                                                                                                                                                                                                                                                         |

| 47         | SDRMCS | I/O, L       | Chip-Select Line 4. Used as chip-select for the synchronous DRAM. Pulled up on the motherboard. When the SDRAM is disabled via the BCSR, this signal can be used offboard via the expansion connectors.                                                                   |

| 48         | GND    | _            | _                                                                                                                                                                                                                                                                         |

| 49         | GPL3   | O, L         | UPMA or UPMB General-Purpose Line 3. Used as $\overline{\rm WR}$ signal for the SDRAM.                                                                                                                                                                                    |

| 50         | GND    | _            | _                                                                                                                                                                                                                                                                         |

| 51         | GPL2   | O, L         | General-Purpose Line 2 for UPMA or UPMB. Used with the SDRAM as a CAS signal.                                                                                                                                                                                             |

| 52         | GND    | _            | _                                                                                                                                                                                                                                                                         |

| 53         | BSWE3~ | O, L         | UPM Byte Select 3, GPCM Write Enable 3, or PCMCIA WE. Selects the LSB within a word for the SDRAM, EDO DRAM and flash SIMM or qualifies writes for the PC-card.                                                                                                           |

|            |        |              |                                                                                                                                                                                                                                                                           |

5-14 MPC823ADSDB USER'S MANUAL

MOTOROLA

Signal Descriptions

**Table 5-14. PM1 Interconnect Signals (Continued)**

| Table 5-14. Finit interconnect Signals (Continued) |        |              |                                                                                                                                                                                              |  |

|----------------------------------------------------|--------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PIN NUMBER                                         | SIGNAL | INPUT/OUTPUT | DESCRIPTION                                                                                                                                                                                  |  |

| 54                                                 | GND    | _            | _                                                                                                                                                                                            |  |

| 55                                                 | BSWE2~ | O, L         | UPM Byte Select 2, GPCM Write Enable 2, or PCMCIA OE. Selects the offset 2 byte within a word for the SDRAM, EDO DRAM, and flash SIMM or open data buffers for read from PC-card.            |  |

| 56                                                 | GND    | _            | _                                                                                                                                                                                            |  |

| 57                                                 | BSWE1~ | O, L         | UPM Byte Select 1, GPCM Write Enable1, or PCMCIA I/O Write. Selects the offset 1 byte within a word for the SDRAM, EDO DRAM and flash SIMM or functions as I/O write for the PCMCIA channel. |  |

| 58                                                 | GND    | _            | _                                                                                                                                                                                            |  |

| 59                                                 | BSWE2~ | O, L         | See pin 55. The duality due to separation of BS[0:3]_A from WE[0:3]/BS[0:3]_B with other members of the MPC8xx Family.                                                                       |  |

| 60                                                 | GND    | _            | _                                                                                                                                                                                            |  |

| 61                                                 | BSWE0~ | O, L         | UPM Byte Select 0, GPCM Write Enable 0, or PCMCIA I/O Read. Selects the offset 0 byte within a word for the SDRAM, EDO DRAM and flash SIMM or functions as I/O reads from PC-card.           |  |

| 62                                                 | GND    | _            | _                                                                                                                                                                                            |  |

| 63                                                 | _      | _            | _                                                                                                                                                                                            |  |

| 64                                                 | GND    | _            | _                                                                                                                                                                                            |  |

| 65                                                 | EDOOE~ | O,L          | UPMA or UPMB General-Purpose Line 1. Used for Output Enable with EDO DRAM SIMMs that have this input (most of them don't). Used also as RAS signal for the SDRAM.                            |  |

| 66                                                 | GND    | _            | _                                                                                                                                                                                            |  |

| 67                                                 | BSWE0  | O, L         | See pin 61. The duality due to separation of BS[0:3]_A from WE[0:3]/BS[0:3]_B with other members of the MPC8xx Family.                                                                       |  |

| 68                                                 | GND    | _            | _                                                                                                                                                                                            |  |

| 69                                                 | BSWE3  | O, L         | See pin 53. The duality due to separation of BS[0:3]_A from WE[0:3]/BS[0:3]_B with other members of the MPC8xx Family.                                                                       |  |

| 70                                                 | GND    | _            | _                                                                                                                                                                                            |  |

| 71                                                 | A31    | O, T.S.      | Address line 31.                                                                                                                                                                             |  |

| 72                                                 | GND    | _            | _                                                                                                                                                                                            |  |

| 73                                                 | BSWE1  | O, L         | See pin 57. The duality due to separation of BS[0:3]_A from WE[0:3]/BS[0:3]_B with other members of the MPC8xx Family.                                                                       |  |

| 74                                                 | GND    | _            | _                                                                                                                                                                                            |  |

| 75                                                 | TSIZ1  | O, T.S.      | Transfer Size 1. Used in conjunction with TSIZ0 to indicate the number of bytes remaining in an operand transfer. Not used on the MPC823ADS.                                                 |  |

| 76                                                 | GND    |              | _                                                                                                                                                                                            |  |

| 77                                                 | REG_A  | O, T.S., L   | TSIZ0/REG-Transfer Size 0 or PCMCIA REG. Used with the PCMCIA port as attribute memory select or I/O space select.                                                                           |  |

| 78                                                 | GND    | _            | _                                                                                                                                                                                            |  |

| 79                                                 | A30    | O, T.S.      | Address line 30.                                                                                                                                                                             |  |

| 80                                                 | GND    | _            | _                                                                                                                                                                                            |  |

| 81                                                 | A21    | O, T.S.      | MPC823's Address line 21.                                                                                                                                                                    |  |

|                                                    |        |              |                                                                                                                                                                                              |  |

MOTOROLA

MPC823ADSDB USER'S MANUAL

Signal Descriptions

**Table 5-14. PM1 Interconnect Signals (Continued)**

| PIN NUMBER | SIGNAL | INPUT/OUTPUT | DESCRIPTION               |

|------------|--------|--------------|---------------------------|

| 82         | GND    | _            | _                         |

| 83         | A20    | O, T.S.      | MPC823's Address line 20. |

| 84         | GND    | _            | _                         |

| 85         | A7     | O, T.S.      | MPC823's Address line 7.  |

| 86         | GND    | _            | _                         |

| 87         | A15    | O, T.S.      | MPC823's Address line 15. |

| 88         | GND    | _            | _                         |

| 89         | A14    | O, T.S.      | MPC823's Address line 14. |

| 90         | GND    | _            | _                         |

| 91         | A13    | O, T.S.      | MPC823's Address line 13. |

| 92         | GND    | _            | _                         |

| 93         | A6     | O, T.S.      | MPC823's Address line 6.  |

| 94         | GND    | _            | _                         |

| 95         | A12    | O, T.S.      | MPC823's Address line 12. |

| 96         | GND    | _            | _                         |

| 97         | A11    | O, T.S.      | MPC823's Address line 11. |

| 98         | GND    | _            | _                         |

| 99         | A19    | O, T.S.      | MPC823's Address line 19. |

| 100        | GND    | _            | _                         |

| 101        | A9     | O, T.S.      | MPC823's Address line 9.  |

| 102        | GND    | _            | _                         |

| 103        | A18    | O, T.S.      | MPC823's Address line 18. |

| 104        | GND    | _            | _                         |

| 105        | A10    | O, T.S.      | MPC823's Address line 10. |

| 106        | GND    | _            | _                         |

| 107        | A17    | O, T.S.      | MPC823's Address line 17. |

| 108        | GND    | _            | _                         |

| 109        | A16    | O, T.S.      | MPC823's Address line 16. |

| 110        | GND    | _            | _                         |

| 111        | A8     | O, T.S.      | MPC823's Address line 8.  |

| 112        | GND    | _            | _                         |

| 113        | A29    | O, T.S.      | MPC823's Address line 29. |

| 114        | GND    | _            | _                         |