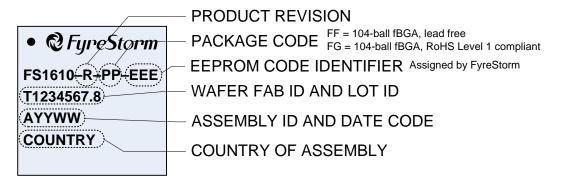

Leading the Digital Power Revolution <sup>TM</sup>

## **GENERAL DESCRIPTION**

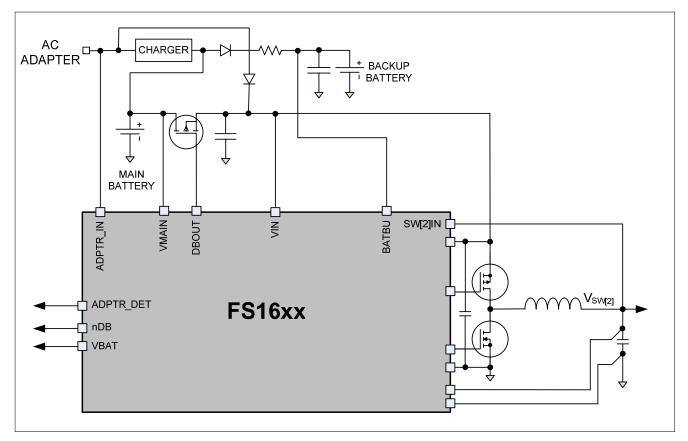

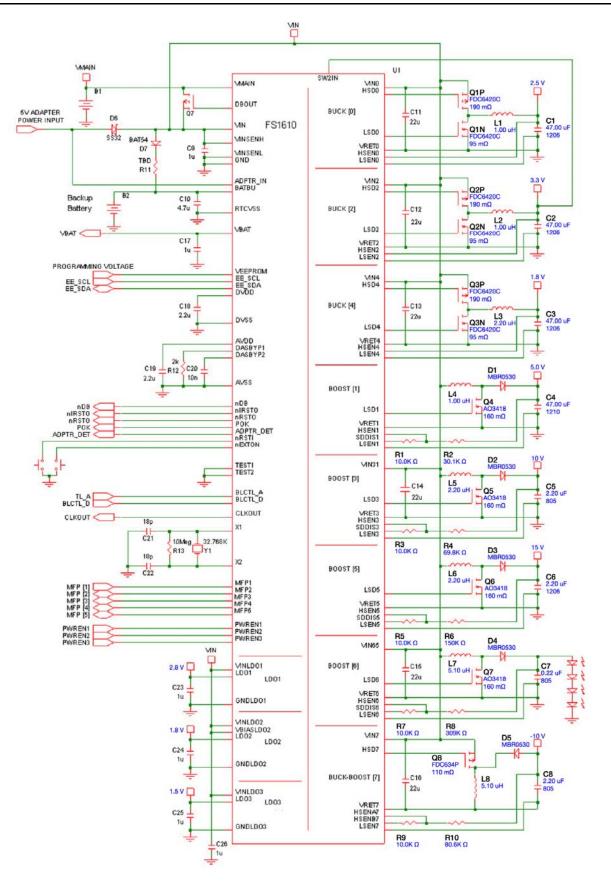

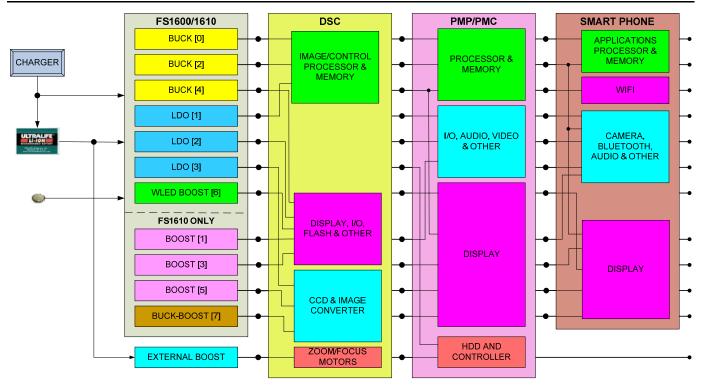

FyreStorm's FS1610 Advanced Power Management Controller utilizes proprietary digital technology to provide a fully programmable power subsystem solution for sophisticated mobile devices such as digital still cameras, feature-phones, smart-phones, PDAs and handheld computers. Compared to traditional implementations, an FS1610 based solution reduces PCB area, and its digital technology, which allows full programmability, results in faster design cycles, allowing quicker time-to-market for the end product. It reduces glue logic by interfacing seamlessly to processors such as Intel's PXA family, Freescale Semiconductor's MX families, Samsung's ARM9-based family and AMD's Au1200 family.

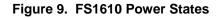

The FS1610 provides eight highly efficient switch-mode converters (three buck converters, one White LED driver, three boost converters and one buck-boost converter) and has integrated drivers that directly drive external MOSFETs. A patented digital control algorithm reduces capacitor and inductor size and cost, reduces quiescent current and improves conversion efficiency. Additionally, the FS1610 provides three low-power LDO regulators with internal pass FETs, a Real-Time-Clock with a programmable alarm and a Watchdog Timer.

Start-up configuration of the device is stored in an internal EEPROM that can be programmed by the user, and can then be managed by the host processor via the device's  $I^2C$  or UART serial port. Load activation and shedding profiles can also be specified in the EEPROM and by the host. The FS1610 is also capable of standalone operation using the parameters loaded from the EEPROM at start-up.

The FS1610 is provided in a space-efficient, 8 x 8 FBGA package.

# **APPLICATIONS**

- Feature phones and smart phones

- Portable media players and MP3 players

- PDAs and hand-held computers

- Digital still cameras and camcorders

- Other portable electronics equipment

#### **KEY FEATURES**

- **Eight switching converters**

- Three buck (step-down) converters

Two converters available in Low Power mode for high efficiency at low load currents

- Three boost (step-up) converters

- One buck-boost (step-up) converter for negative output voltage

- One constant current boost White LED driver

- High efficiency (typically 90%+) from 5% to 100% of programmed maximum current in active mode

- Converters drive external MOSFET(s) directly

- Switching converters feature all-digital loop control technology

- Real-time analysis provides optimal power system control and operation

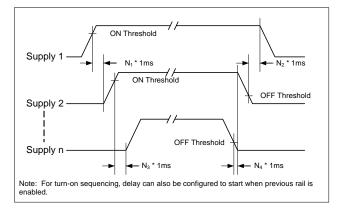

- Precise supply-to-supply matching and tracking

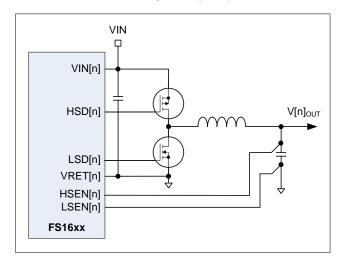

- Programmable power-up and -down slew rates

- Programmable load connection and shedding

- Reduced component count yields smaller size and lower cost

- Three LDOs

- Input voltage range: 2.8 to 5.5 Volts

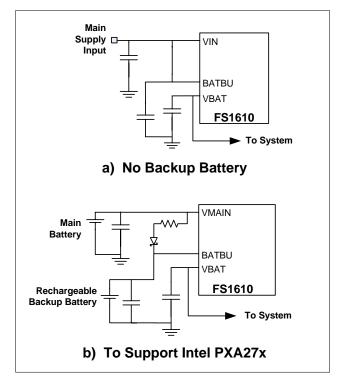

- Battery backup switching support

- Dynamic programming for all buck and LDO power rails

- Power-up supply characteristics can be modified without hardware changes by reprogramming the device's EEPROM

- Fast and simple design with FyreStorm's Webbased Design Center

- Capable of stand-alone operation using the parameters loaded from the EEPROM at start-up

- No serial interface with host required

- Utilize device pins for status/control

- Integrated system support

- Real time clock with alarm and Watchdog timer

- Programmable host controller interrupt output

- Power Good and Power-on-Reset outputs

- Remote management via I<sup>2</sup>C or UART interface to host processor

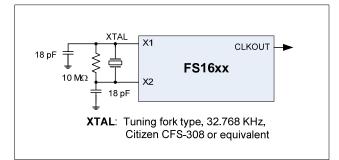

- Operates from a low-cost 32.768 KHz crystal or external clock input

- Provides buffered 32 KHz output to the system

- Low power consumption

- 50 µA in shutdown mode with RTC enabled

- 128 bytes user data space in EEPROM

- 8 x 8 mm FBGA package with 0.5 mm ball pitch

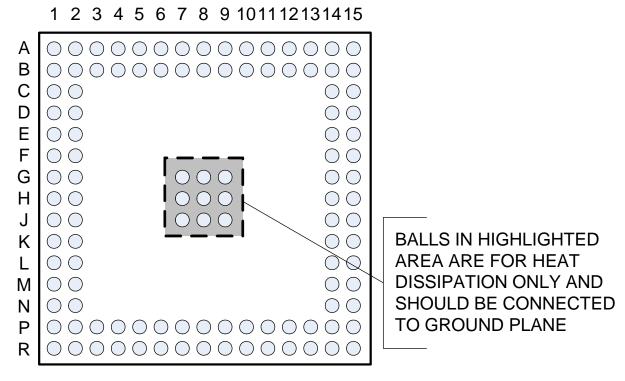

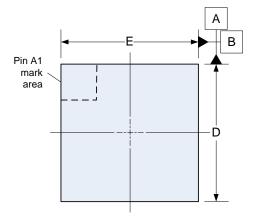

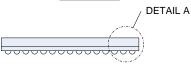

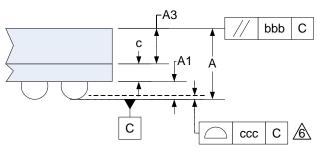

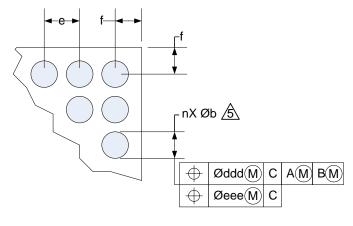

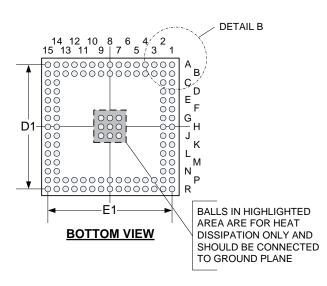

#### **FS1610 PIN CONFIGURATION**

FS1610 Pin Configuration – Top View, Looking Through Package

| PIN | FUNCTION  | PIN | FUNCTION   | PIN | FUNCTION  | PIN | FUNCTION | PIN | FUNCTION  |

|-----|-----------|-----|------------|-----|-----------|-----|----------|-----|-----------|

| A1  | PWREN[1]  | B7  | BATBU      | F1  | LDO[1]    | L2  | HSENB[7] | P11 | nEXTON    |

| A2  | X1        | B8  | VBAT       | F2  | GNDLDO[1] | L14 | HSD[2]   | P12 | V_EEPROM  |

| A3  | X2        | B9  | MFP[2]     | F14 | VRET[3]   | L15 | VIN[2]   | P13 | ADPTR_DET |

| A4  | CLKOUT    | B10 | POK        | F15 | LSD[3]    | M1  | HSENA[7] | P14 | LSD[0]    |

| A5  | ADPTR_IN  | B11 | PWREN[2]   | G1  | VINLDO[1] | M2  | LSEN[7]  | P15 | VRET[0]   |

| A6  | VIN       | B12 | PWREN[3]   | G2  | N/C       | M14 | LSD[2]   | R1  | DNC       |

| A7  | GND       | B13 | DVSS       | G14 | VIN[31]   | M15 | VRET[2]  | R2  | HSEN[4]   |

| A8  | VMAIN     | B14 | HSD[7]     | G15 | LSD[1]    | N1  | HSEN[6]  | R3  | N/C       |

| A9  | MFP[5]    | B15 | VRET[7]    | H1  | AVDD      | N2  | LSEN[6]  | R4  | HSEN[3]   |

| A10 | nRSTO     | C1  | VINLDO[3]  | H2  | AVSS      | N14 | HSD[0]   | R5  | HSEN[2]   |

| A11 | DVDD      | C2  | N/C        | H14 | N/C       | N15 | VIN[0]   | R6  | HSEN[1]   |

| A12 | BLCTL_D   | C14 | VRET[6]    | H15 | VRET[1]   | P1  | HSEN[5]  | R7  | HSEN[0]   |

| A13 | MFP[1]    | C15 | LSD[6]     | J1  | VINSENH   | P2  | LSEN[5]  | R8  | SDDIS[3]  |

| A14 | MFP[4]    | D1  | LDO[2]     | J2  | VINSENL   | P3  | LSEN[4]  | R9  | SDDIS[6]  |

| A15 | MFP[3]    | D2  | GNDLDO[2]  | J14 | HSD[4]    | P4  | LSEN[3]  | R10 | nRSTI     |

| B1  | LDO[3]    | D14 | VIN[7]     | J15 | VIN[4]    | P5  | LSEN[2]  | R11 | nDB       |

| B2  | GNDLDO[3] | D15 | VIN[65]    | K1  | BLCTL_A   | P6  | LSEN[1]  | R12 | EE_SDA    |

| B3  | RTCVDD    | E1  | VINLDO[2]  | K2  | DAS_BYP1  | P7  | LSEN[0]  | R13 | EE_SCL    |

| B4  | RTCVSS    | E2  | VBIAS_LDO2 | K14 | LSD[4]    | P8  | SDDIS[1] | R14 | TEST[2]   |

| B5  | DBOUT     | E14 | VRET[5]    | K15 | VRET[4]   | P9  | SDDIS[5] | R15 | TEST[1]   |

| B6  | SW[2]IN   | E15 | LSD[5]     | L1  | DAS_BYP2  | P10 | nIRSTO   |     |           |

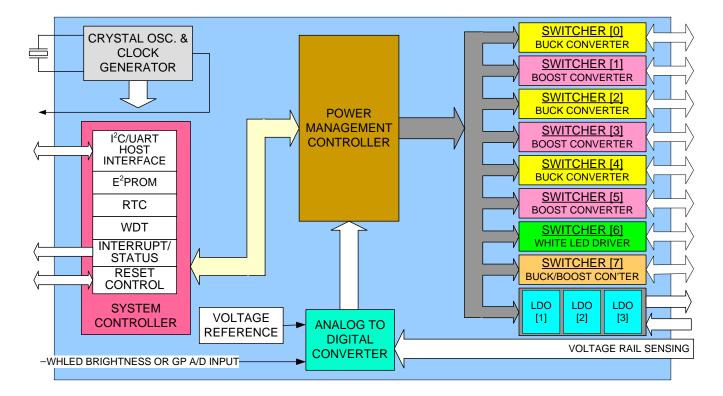

# FS1610 BLOCK DIAGRAM

#### **CONVENTIONS**

Unless otherwise noted, a positive logic (active High) convention is assumed throughout this document, whereby a positive voltage ( $V_{IH}$ ) causes assertion of an input signal and indicates an asserted output signal. An 'n' preceding the signal name, e.g., nINTR, indicates that the input or output signal is asserted in a Low state ( $V_{IL}$ ). Whenever a signal is separated into

# ELECTRICAL SPECIFICATIONS

#### Absolute Maximum Ratings<sup>1</sup>

numbered bits, e.g., D[7], D[6], ..., D[0], the family of bits may also be shown collectively, e.g., as D[7:0].

The designation 0xNNNN indicates a number expressed in hexadecimal notation (N = 0, 1, 2, ..., 9, A, ..., E, F). The designation 0bXXXX indicates a number expressed in binary notation (X = 0, 1).

| Parameter                                                               | Min   | Max   | Unit |

|-------------------------------------------------------------------------|-------|-------|------|

| Input voltage, all analog and power input pins except ADPTR_IN          | - 0.3 | + 6   | V    |

| Input voltage, ADPTR_IN pin                                             | - 0.3 | + 6   | V    |

| Input voltage, all digital input and output pins                        | - 0.3 | + 4.0 | V    |

| Input voltage, HSEN[7:0], LSEN[7:0]                                     | - 0.3 | + 6   | V    |

| Continuous current, pins LSD[0], HSD[0], LSD[2], HSD[2], LSD[4], HSD[4] | - 25  | 25    | mA   |

| Continuous current, pins LSD[1], LSD[3], LSD[5], LSD[6], HSD[7]         | - 25  | 25    | mA   |

| Continuous power dissipation                                            |       | 0.7   | W    |

| Junction temperature                                                    |       | + 125 | °C   |

| Operating ambient temperature range                                     | - 20  | + 85  | °C   |

Notes:

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this data sheet is not implied. Exposure of the device to Absolute Maximum Rating conditions for extended periods may affect device reliability.

# **Electrical Parameters - General**

| Symbol             | Parameter                                                                                            | Conditions                                         | Min          | Тур  | Max            | Unit |  |

|--------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------|------|----------------|------|--|

|                    | Input voltage: VMAIN, VIN, VIN[0], VIN[2], VIN[4], VIN[7], VIN[31], VIN[65], VBIAS_LDO2 <sup>4</sup> |                                                    | 2.8          |      | 5.5            |      |  |

|                    | Input voltage VINLDO[3, 1]                                                                           |                                                    | 1.8          |      | VIN            |      |  |

| VINP               | Input voltage VINLDO[2]                                                                              |                                                    | 1.8          |      | VBIAS_<br>LDO2 | V    |  |

|                    | Input voltage ADPTR_IN                                                                               |                                                    | 0            |      | 5.8            |      |  |

|                    | Input voltage V_EEPROM                                                                               | Not connected for normal operation                 | 1.8          | 2.5  | 3.3            |      |  |

| $V_{\text{BU}}$    | Input voltage, BATBU                                                                                 |                                                    | 2.75         |      | 5.5            | V    |  |

| $V_{SW[2]IN}$      | Input voltage, SW[2]IN                                                                               |                                                    | 0            |      | VIN            | V    |  |

|                    | Operating Current VMAIN                                                                              |                                                    |              |      | 2              | μA   |  |

|                    | Operating current BATBU                                                                              | SHUTDOWN state,<br>CLKOUT disabled, $I_{VBAT} = 0$ |              | 50   |                | μA   |  |

|                    |                                                                                                      | LOWPOWER – SW[2, 0]<br>enabled, no loads           |              | 150  |                | μA   |  |

|                    | Operating current VIN                                                                                | SHUTDOWN                                           |              | 5    |                | μA   |  |

|                    |                                                                                                      | READY                                              |              | 4    |                | mA   |  |

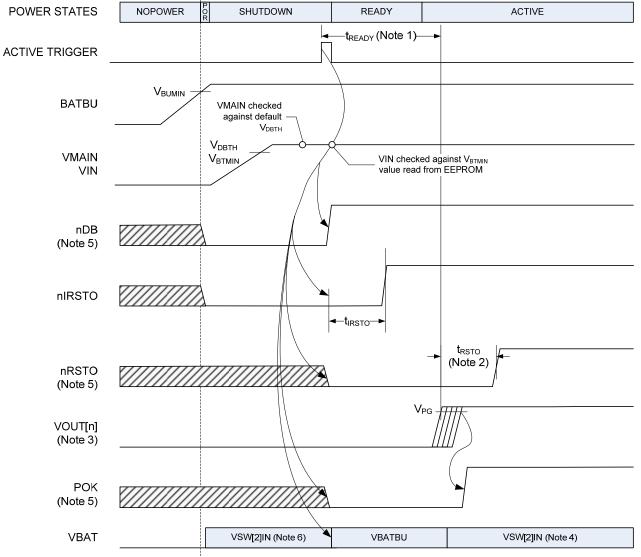

| t <sub>READY</sub> | SHUTDOWN to READY state delay <sup>3</sup>                                                           |                                                    |              |      | 200            | ms   |  |

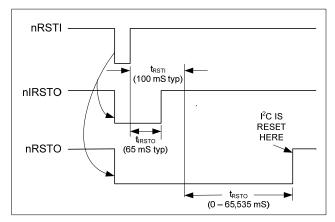

| t <sub>RSTI</sub>  | nRSTI input debounce time <sup>2, 3</sup>                                                            | nRSTI de-asserted                                  |              | 100  |                | ms   |  |

| t <sub>EXTON</sub> | nEXTON input debounce time <sup>2, 3</sup>                                                           | nEXTON asserted or de-<br>asserted                 |              | 100  |                | ms   |  |

| t <sub>RSTO</sub>  | nRSTO timer period (programmable in EEPROM) <sup>3</sup>                                             |                                                    | 0            |      | 65,535         | ms   |  |

| t <sub>IRSTO</sub> | nIRSTO timer period <sup>3</sup>                                                                     | nRSTI asserted                                     |              | 65   |                | ms   |  |

| $V_{\text{DBTH}}$  | Dead battery threshold programming range <sup>1</sup>                                                |                                                    | 2.70         | 3.10 | 3.30           | V    |  |

|                    | Dead Battery detect threshold programming resolu-<br>tion                                            |                                                    |              | 50   |                | mV   |  |

|                    | Dead Battery detect threshold accuracy                                                               | VMAIN decreasing                                   | -2           |      | 2              | %    |  |

| $V_{\text{DBHYS}}$ | Dead Battery detect comparator hysteresis                                                            | VMAIN increasing                                   | <tbd></tbd>  | 150  |                | mV   |  |

| $V_{\text{LBTH}}$  | Low battery threshold programming range                                                              |                                                    | 0            |      | 5.5            | V    |  |

|                    | Low Battery detect threshold programming resolu-                                                     | ACTIVE                                             |              | 1.34 |                | mV   |  |

|                    | tion                                                                                                 | LOWPOWER                                           |              | 85   |                | IIIV |  |

|                    | Low Battery detect threshold accuracy                                                                |                                                    | -0.5         |      | 0.5            | %    |  |

| V <sub>DBOH</sub>  | DBOUT output-High voltage                                                                            | I <sub>O</sub> = 100 μA                            | VIN –<br>0.1 |      |                | V    |  |

| $V_{\text{DBOL}}$  | DBOUT output-Low voltage                                                                             | I <sub>O</sub> = -100 μA                           |              |      | 0.1            | V    |  |

|                    | ADPTR_IN detect threshold voltage                                                                    | ADPTR_IN increasing                                | VMAIN        |      | VMAIN<br>+ 0.2 | V    |  |

|                    | ADPTR_IN detect comparator hysteresis                                                                | ADPTR_IN decreasing                                | <tbd></tbd>  | 150  |                | mV   |  |

| T <sub>ADPT</sub>  | ADPTR_IN detect debounce time <sup>2, 3</sup>                                                        | ADPTR_IN asserted                                  |              | 100  |                | ms   |  |

|                    | Thermal Sensor Accuracy                                                                              | Junction temperature                               | -10          |      | 10             | °C   |  |

|                    | -                                                                                                    | Temperature rising                                 |              | 105  |                | °C   |  |

| $T_{TAL}$          | Thermal alarm threshold (based on thermal sensor accuracy)                                           | Temperature falling                                |              | 95   |                | °C   |  |

| T <sub>TSD</sub>   | Thermal shutdown threshold (based on thermal sensor accuracy)                                        |                                                    |              | 115  |                | °C   |  |

|                    |                                                                                                      | evel Signals                                       | I            |      |                |      |  |

|                    | Output-Low voltage: All digital outputs                                                              | $I_{OL} = -4 \text{ mA}$                           |              |      | 0.4            | V    |  |

# 🛯 FyreStorm

#### **FS1610**

| Symbol | Parameter                                             | Conditions                                                 | Min | Тур | Max  | Unit |

|--------|-------------------------------------------------------|------------------------------------------------------------|-----|-----|------|------|

|        | Output-High voltage: All digital outputs, unless oth- | When configured as active outputs, $I_{OH} = 4 \text{ mA}$ | 2.0 |     | 2.4  | V    |

|        | erwise specified                                      | When configured as open-<br>drain output                   |     |     | 3.75 | V    |

|        | Output-High voltage: CLKOUT                           | I <sub>OH</sub> = 1 mA, C <sub>O</sub> = 50 pF             | 2.0 |     | 2.4  | V    |

| VIH    | Input-High voltage: All digital inputs                |                                                            | 1.6 |     | 3.75 | V    |

| VIL    | Input-Low voltage: All digital inputs                 |                                                            |     |     | 0.4  | V    |

|        | Input leakage current: All digital inputs except      | Input voltage = 3.6 V                                      | - 1 |     | + 1  | μA   |

|        | nRSTI and nEXTON                                      | Input voltage = 0 V                                        | - 1 |     | + 1  | μA   |

|        | Output-High leakage current: All open-drain outputs   | Output voltage = 3.6 V                                     |     |     | 0.2  | μA   |

|        | Input leakage current: nRSTI and nEXTON               | Input voltage = 2.5 V                                      | - 1 |     | + 1  | μA   |

|        |                                                       | Input voltage = 0 V                                        | 62  | 125 | 150  | μA   |

1. V<sub>DBTH</sub> is set to a default value of 3.10 V during the internal power-on-reset cycle. It may then be changed by data in the EEPROM.

Debounce interval is measured from the last bounce detected.

Based on 32.768 KHz crystal frequency

4. VIN, VIN[0], VIN[2], VIN[4], VIN[7], VIN[31], VIN[65] must be at the same voltage

#### **Electrical Parameters – LDO Regulators**

VIN = 3.0 V - 5.5 V,  $T_A = -20^{\circ}C$  to 85°C unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$  and VIN = 3.6V.  $C_{OUT} = 0.47 \mu$ F unless otherwise noted. erwise specified.

| Symbol           | Parameter                                                     | Conditions                                                                       | Min   | Тур  | Max         | Unit |

|------------------|---------------------------------------------------------------|----------------------------------------------------------------------------------|-------|------|-------------|------|

|                  | LDO                                                           | [1], LDO[3]                                                                      |       |      |             |      |

|                  | Output voltage programming range                              |                                                                                  | 0.9   |      | 3.3         | V    |

|                  | Output voltage programming resolution                         |                                                                                  |       | 50   |             | mV   |

|                  | Initial voltage accuracy                                      | $I_{OUT} = 0$                                                                    | - 0.5 |      | 0.5         | %    |

|                  | Output voltage change under load                              | $I_{OUT} = 0$ to 60 mA,<br>$C_{OUT} = 2.2 \ \mu\text{F}$ , X5R                   |       | - 35 | - 50        | mV   |

|                  | Dropout voltage                                               | I <sub>OUT</sub> = 60 mA                                                         |       | 200  | <tbd></tbd> | mV   |

|                  | Maximum output current <sup>1</sup>                           |                                                                                  | 60    |      |             | mA   |

|                  | Quiescent current, VINLDO[x]                                  | No load                                                                          |       |      | 1           | μA   |

|                  | Quiescent current, VIN                                        | Enabled, no load                                                                 |       | 45   | tbd         | μA   |

|                  |                                                               | LDO disabled                                                                     |       |      | 1           | μA   |

| V <sub>PG</sub>  | POK threshold                                                 | Rising                                                                           |       | 95   |             | %    |

| V PG             |                                                               | Falling                                                                          |       | 90   |             | %    |

| t <sub>FLT</sub> | POK response time to out of regulation program-<br>ming range |                                                                                  | 1     |      | 255         | ms   |

|                  | External output capacitor                                     | $R_{ESR} < 50 \text{ m}\Omega$<br>$L_{ESL} < 3 \text{ nH}$<br>1 Mhz < f < 50 MHz | 470   | 1000 | 2200        | nF   |

|                  | PSRR                                                          | f =10 KHz, I <sub>OUT</sub> = 60 mA                                              | 40    |      |             | db   |

|                  |                                                               | f =100 KHz, I <sub>OUT</sub> = 60 mA                                             | 30    |      |             | db   |

|                  |                                                               | LDO[2]                                                                           | •     | •    |             |      |

|                  | Output voltage programming range                              |                                                                                  | 0.9   |      | 3.3         | V    |

|                  | Output voltage programming resolution                         |                                                                                  |       | 50   |             | mV   |

|                  | Initial voltage accuracy                                      | $I_{OUT} = 0$                                                                    | - 0.5 |      | 0.5         | %    |

|                  | Output voltage change under load                              | $I_{OUT} = 0$ to 60 mA,<br>$C_{OUT} = 2.2 \ \mu$ F, X5R                          |       | - 35 | - 50        | mV   |

FS1610

# 🛯 FyreStorm

| Symbol           | Parameter                                                     | Conditions                                                  | Min | Тур  | Max         | Unit      |

|------------------|---------------------------------------------------------------|-------------------------------------------------------------|-----|------|-------------|-----------|

|                  | Dropout voltage                                               | I <sub>OUT</sub> = 60 mA                                    |     | 200  | <tbd></tbd> | mV        |

|                  | Maximum output current <sup>1</sup>                           |                                                             | 60  |      |             | mA        |

|                  | Noise                                                         | VBIAS_LDO2 = 3.3V<br>10 Hz < f < 100 KHz                    |     | 20   | <tbd></tbd> | μV<br>RMS |

|                  | Quiescent current, VINLDO[2]                                  | No load                                                     |     |      | 1           | μA        |

|                  | Quiescent current VBIAS LDQ2                                  | Enabled, no load                                            |     | 45   | tbd         | μA        |

|                  | Quiescent current, VBIAS_LDO2                                 | LDO disabled                                                |     |      | 1           | μA        |

| V <sub>PG</sub>  | POK threshold                                                 | Rising                                                      |     | 95   |             | %         |

| V PG             |                                                               | Falling                                                     |     | 90   |             | %         |

| t <sub>FLT</sub> | POK response time to out of regulation program-<br>ming range |                                                             | 1   |      | 255         | ms        |

|                  | External output capacitor                                     | $R_{ESR}$ < 50 mΩ<br>$L_{ESL}$ < 3 nH<br>1 Mhz < f < 50 MHz | 470 | 1000 | 2200        | nF        |

|                  | PSRR                                                          | f =10 KHz, I <sub>OUT</sub> = 60 mA                         | 40  |      |             | db        |

|                  |                                                               | f =100 KHz, I <sub>OUT</sub> = 60 mA                        | 30  |      |             | db        |

1. The aggregate internal power dissipation for all LDOs combined must not exceed 500 mW.

# **Electrical Parameters – Switching Regulators**

$VIN = 3.0 \text{ V} - 5.5 \text{ V}, \text{ } \text{T}_{\text{A}} = -20^{\circ}\text{C} \text{ to } 85^{\circ}\text{C} \text{ unless otherwise noted.} \text{ Typical values are at } \text{T}_{\text{A}} = +25^{\circ}\text{C} \text{ and } \text{VIN} = 3.6\text{V}.$

| Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Parameter                                   | Conditions                                                 | Min         | Тур | Max                  | Unit  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------------------------------------------------------------|-------------|-----|----------------------|-------|

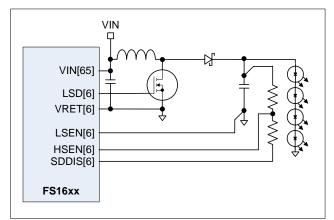

| Constant Current Boost Regulator: SW[6]           ILED         Maximum output current         30         mA           Output current programming resolution         1.0         mA           Output current accuracy         ILED = 20 mA <tbd>±8         <tbd>%           Number of series LEDs         VLED = 4.1V max.         2         10         Units           Over-voltage protection threshold accuracy         -5         5         %           LSD[6] RDSON         Output current = 25 mA         4.8         6.3         Ohm           Input leakage current: HSEN[6], LSEN[6]         ±1         <tbd>±4         <tbd>±4           Output-Low voltage, SDDIS[6] output         IoL = 0.1 mA         5         mV           fsweb         Switching frequency         8 x f<sub>CLK</sub>         Hz           Incremental operating current, VIN         SW[6] enabled, I<sub>LED</sub> = 30 mA         2         mA           Incremental supply current at VIN[65]         SW[6] enabled, I<sub>LED</sub> = 30 mA         100         µA           BLCTL_D input PWM frequency         100         500         Hz           Output sequencing turn-off threshold         Output is disabled         VIN         V           IPrG         POK threshold         90         %         ms</tbd></tbd></tbd></tbd> |                                             |                                                            |             |     |                      |       |

| I <sub>LED</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Maximum output current                      |                                                            | 30          |     |                      | mA    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Output current programming resolution       |                                                            |             | 1.0 |                      | mA    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Output current accuracy                     | $I_{LED} = 20 \text{ mA}$                                  | <tbd></tbd> | ±8  | <tbd></tbd>          | %     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Number of series LEDs                       | $V_{LED} = 4.1V \text{ max.}$                              | 2           |     | 10                   | Units |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Over-voltage protection threshold accuracy  |                                                            | - 5         |     | 5                    | %     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                             | Output current = 25 mA                                     |             | 4.8 | 6.3                  | Ohm   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                             | Output current = - 25 mA                                   |             | 2.4 | 3.1                  | Ohm   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Input leakage current: HSEN[6], LSEN[6]     |                                                            |             | ±1  | <tbd></tbd>          | μA    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Output-Low voltage, SDDIS[6] output         | I <sub>OL</sub> = 0.1 mA                                   |             |     | 5                    | mV    |

| f <sub>SW6</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Switching frequency                         |                                                            |             |     | $8 	ext{ x f}_{CLK}$ | Hz    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Incremental operating current, VIN          | SW[6] enabled, I <sub>LED</sub> = 30 mA                    |             | 2   |                      | mA    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Incremental supply current at VIN[65]       | SW[6] enabled, I <sub>LED</sub> = 30 mA                    |             | 100 |                      | μA    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | BLCTL_D input PWM frequency                 |                                                            |             | 100 | 500                  | Hz    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Output sequencing turn-off threshold        | Output is disabled                                         | VIN         |     |                      | V     |

| I <sub>PG</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | POK threshold                               |                                                            | 90          |     |                      | %     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                             |                                                            | 1           |     | 255                  | ms    |

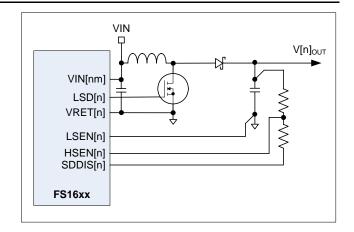

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Synchronous Buck Re                         | gulators: SW[0], SW[2], SW[4]                              |             | •   |                      |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Output voltage programming range            |                                                            | 0.85        |     | 3.3                  | V     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Output voltage programming resolution       |                                                            |             | 5   |                      | mV    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Output voltage accuracy                     | $I_{OUT} = 0$ to 300 mA, includes line and load regulation | - 2.5       |     | 0.5                  | %     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DVM voltage step size (EEPROM configurable) |                                                            | 5           |     | 300                  | mV    |

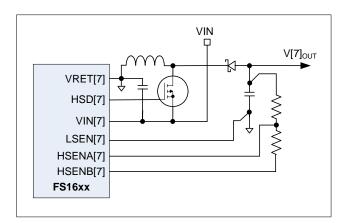

#### Symbol Parameter Conditions Min Тур Max 31 x DVM voltage step time (EEPROM configurable) T<sub>CLK</sub>/4 T<sub>CLK</sub>/4 Switching frequency 16f<sub>CLK</sub> f<sub>SW0</sub> SW[x] enabled, static load, Incremental operating current at VIN pin 1 ACTIVE mode SW[x] enabled, switching at Supply current at VIN[x] pin 200 maximum f<sub>SW0</sub> Input leakage current: HSEN[4, 2, 0], LSEN[4, 2, 0] <tbd> ±1 Output current = 25 mA 2.4 3.1 Output impedance: HSD[4, 2, 0] Output current = - 25 mA 4.8 6.3 Output current = 25 mA 4.8 6.3 Output impedance: LSD[4, 2, 0] Output current = - 25 mA 2.4 3.1 Current limit as percentage of programmed output <tbd> <tbd> POK threshold 97.5 $V_{PG}$ POK response time to out of regulation program-255 1 ming range Output sequencing turn-off threshold (EEPROM Output is disabled 500 programmable) Boost Regulators: SW[1], SW[3], SW[5], Buck-Boost Regulator SW[7] Output voltage programming range SW[5, 3, 1] VIN 25.0 Output voltage programming range SW[7] -1.0 -20.0 Output Voltage Accuracy Output current 0 - 30 mA -0.5 0.5 Output voltage programming resolution Of programmed range 0.1 Output current = 25 mA 4.8 6.3 Output impedance: LSD[5, 3, 1] Output current = – 25 mA 2.4 3.1

|                 |                                                                   |                                                    |     |      | -                 | -   |

|-----------------|-------------------------------------------------------------------|----------------------------------------------------|-----|------|-------------------|-----|

|                 | Output impedance: HSD[7]                                          | Output current = 25 mA                             |     | 2.4  | 3.1               | Ohm |

|                 |                                                                   | Output current = - 25 mA                           |     | 4.8  | 6.3               | Ohm |

|                 | Input leakage current: HSEN[A7, B7, 5, 3, 1],<br>LSEN[7, 5, 3, 1] |                                                    |     | ±1   | <tbd></tbd>       | μA  |

|                 | Output-Low voltage: SDDIS[5, 3, 1] outputs                        | I <sub>OL</sub> = 0.1 mA                           |     |      | 5                 | mV  |

|                 | Switching frequency                                               |                                                    |     |      | 8f <sub>CLK</sub> | KHz |

|                 | Incremental operating current at VIN pin (SW[5,3,1])              | Rail enabled, static load                          |     | 350  |                   | μA  |

|                 | Incremental operating current at VIN pin (SW[7])                  | Rail enabled, static load                          |     | 500  |                   | μA  |

|                 | Incremental supply current at VIN[xy] pin                         | Rail enabled, switching at maximum f <sub>sw</sub> |     | 50   |                   | μA  |

|                 | Current-limit as percentage of programmed output                  |                                                    |     | 150  |                   | %   |

| V <sub>PG</sub> | POK threshold                                                     |                                                    |     | 97.5 |                   | %   |

|                 | POK response time to out of regulation program-<br>ming range     |                                                    | 1   |      | 255               | ms  |

|                 | Output sequencing turn-off threshold                              | Output is disabled                                 | VIN |      |                   | V   |

**FS1610**

🛯 FyreStorm

Unit

μs

KHz

mΑ

μA

μA

Ohm

Ohm

Ohm

Ohm

%

%

ms

m٧

V

V

%

%

Ohm

Ohm

### **Electrical Parameters – BLCTL\_A Input**

| VIN = $3.0 \text{ V} - 5.5 \text{ V}$ , $T_A = -20^{\circ}\text{C}$ to $85^{\circ}\text{C}$ unless otherwise noted. | Typical values are at $T_{A} = +25^{\circ}$ C and VIN = 3.6V. |

|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| $V_{11} = 0.0$ V $0.0$ V, $T_A = 20$ 0 to 00 0 differences of the wave horizon.                                     |                                                               |

| Symbol | Parameter                 | Conditions        | Min         | Тур         | Max | Unit |

|--------|---------------------------|-------------------|-------------|-------------|-----|------|

|        | Input voltage             |                   | 0           |             | VIN | V    |

| Ri Ri  | Range: 0 – 1.375 V        |                   | <tbd></tbd> |             |     |      |

|        |                           | Range: 0 – 2.75 V |             | <tbd></tbd> |     | mV   |

|        |                           | Range: 0 – 5.5 V  |             | <tbd></tbd> |     |      |

|        | Measurement data accuracy |                   | - 0.5       |             | 0.5 | %    |

### Electrical Parameters – VBAT Switch<sup>1</sup>

$VIN = 3.0 \text{ V} - 5.5 \text{ V}, \text{ } \text{T}_{\text{A}} = -20^{\circ}\text{C} \text{ to } 85^{\circ}\text{C} \text{ unless otherwise noted.} \text{ Typical values are at } \text{T}_{\text{A}} = +25^{\circ}\text{C} \text{ and } \text{VIN} = 3.6\text{V}.$

| Symbol | Parameter                | Conditions                                                              | Min | Тур           | Max | Unit |

|--------|--------------------------|-------------------------------------------------------------------------|-----|---------------|-----|------|

|        | Output voltage, VBA I    | SW[2] on and in regulation                                              |     | $V_{SW[2]IN}$ |     | V    |

|        |                          | SW[2] off or out of regulation                                          |     | $V_{BATBU}$   |     | V    |

|        | VBAT switch voltage drop | $I_{OUT}$ = 20 mA,<br>V <sub>BATBU</sub> and V <sub>SW2IN</sub> = 3.0 V |     | 100           | 200 | mV   |

|        | VBAT output current      |                                                                         |     |               | 30  | mA   |

1. 'VBAT Switch' is the internal SPDT switch that connects BATBU or SW[2]IN to the VBAT output.

# **AC Electrical Parameters**

$VINA = VIND = 3.0 V - 5.5 V, T_A = -20^{\circ}C \text{ to } 85^{\circ}C \text{ unless otherwise noted.}$  Typical values are at T\_A = +25^{\circ}C and VINA = VIND = 3.6 V.

| Symbol                                   | Parameter                            | Conditions                               | Min  | Тур | Max | Unit  |  |  |  |

|------------------------------------------|--------------------------------------|------------------------------------------|------|-----|-----|-------|--|--|--|

| I <sup>2</sup> C Serial Interface Timing |                                      |                                          |      |     |     |       |  |  |  |

|                                          | Clock frequency                      |                                          | 0    |     | 400 | KHz   |  |  |  |

|                                          | Bus-free time between START and STOP |                                          | 1.3  |     |     | μs    |  |  |  |

|                                          | SCL low Period                       |                                          | 1.3  |     |     | μs    |  |  |  |

|                                          | SCL high Period                      |                                          | 1.0  |     |     | μs    |  |  |  |

|                                          | SDA hold Time                        |                                          | 0    |     |     | μs    |  |  |  |

|                                          | SDA setup Time                       |                                          | 100  |     |     | ns    |  |  |  |

|                                          | STOP condition setup time            |                                          | 1.0  |     |     | μs    |  |  |  |

|                                          | Repeated START condition setup time  |                                          | 1.0  |     |     | μs    |  |  |  |

|                                          | Real-Tim                             | e-Clock Timing                           | -    | •   |     |       |  |  |  |

|                                          | Granularity                          |                                          | 1    |     |     | s     |  |  |  |

|                                          | Span                                 |                                          |      |     | 10  | years |  |  |  |

|                                          | Alarm Setting Accuracy               |                                          | 0    |     | 1   | s     |  |  |  |

|                                          | Alarm latency                        | Alarm triggered to nINTR output asserted |      |     | 200 | ms    |  |  |  |

|                                          | Watch-do                             | g Timer Timing                           | _    | _   |     |       |  |  |  |

|                                          | Interval range                       |                                          | 0.05 |     | 32  | s     |  |  |  |

|                                          | Granularity                          |                                          | 5    |     |     | ms    |  |  |  |

|                                          | Latency                              | Alarm triggered to nINTR output asserted |      |     | 5   | ms    |  |  |  |

|                                          | Watchdog reset input pulse width     |                                          | 100  |     |     | ns    |  |  |  |

| FS1610           | 0                               |                     |        | <b>o</b> ryi |        |      |

|------------------|---------------------------------|---------------------|--------|--------------|--------|------|

| Symbol           | Parameter                       | Conditions          | Min    | Тур          | Max    | Unit |

|                  | Cryst                           | al Oscillator Input |        |              |        |      |

| f <sub>CLK</sub> | Crystal Frequency <sup>1</sup>  |                     | 30     | 32.768       | 32.8   | KHz  |

| T <sub>CLK</sub> | Clock period                    |                     | 30.488 | 30.158       | 33.333 | μs   |

|                  | V <sub>IH</sub> , X1 input      |                     | 1.6    | 2.0          | 2.8    | V    |

|                  | V <sub>IL</sub> , X1 input      |                     | -0.3   | 0.4          | 0.6    | V    |

|                  | Input leakage, X1               |                     |        | 0.1          | 1      | μA   |

|                  | External Capacitance, X1 and X2 |                     |        | 18           |        | pF   |

|                  | Stabilization time              |                     |        |              | 1      | s    |

1. For accurate timekeeping with the RTC and WDT, a crystal frequency of 32.768 KHz ± 100 ppm should be used.

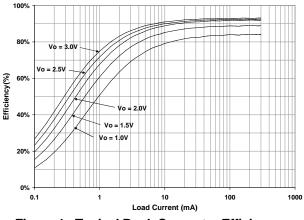

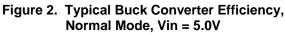

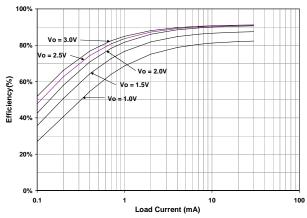

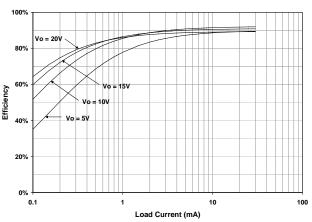

Figure 1. Typical Buck Converter Efficiency, Normal Mode, Vin = 3.9V

🛯 FureStorm

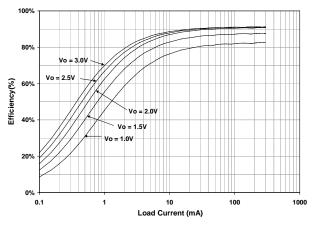

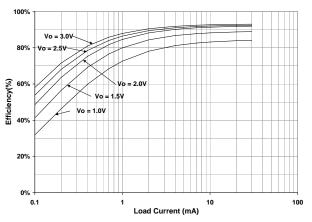

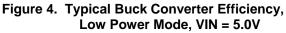

Figure 3. Typical Buck Converter Efficiency, Low Power Mode, Vin = 3.9V

Figure 5. Typical Boost Converter Efficiency, VIN = 3.9V

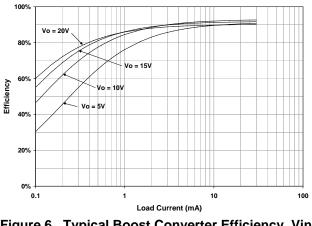

Figure 6. Typical Boost Converter Efficiency, Vin = 5.0V

FyreStorm

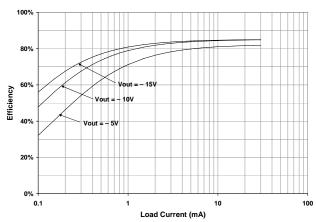

Figure 7. Typical Buck-Boost Converter Efficiency, VIN = 3.9V

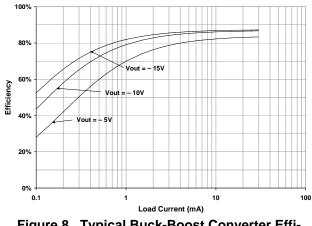

Figure 8. Typical Buck-Boost Converter Efficiency, VIN = 5.0V

# **PIN DESCRIPTIONS**

| Pin No. | Type <sup>1</sup> | Name   | Description <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|-------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A2      | Ι                 | X1     | Crystal or External 32KHz Clock Input.<br>Note: A clock is required for device operation, even if the RTC and/or Watchdog are not used.                                                                                                                                                                                                                                                                                              |

| A3      | O <sub>A</sub>    | X2     | Crystal Output.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| A4      | 0                 | CLKOUT | 32 KHz Output. Configurable buffered output of the crystal oscillator.                                                                                                                                                                                                                                                                                                                                                               |

| A10     | 0                 | nRSTO  | <b>Power-On Reset Output.</b> nRSTO is asserted during the internal power-on-reset period of the FS1610. See COLD START POWER-ON SEQUENCE. It can be programmed to be asserted during an out-of-regulation condition on any supply or upon an nRSTI event. Refer to Table 1 if not used.                                                                                                                                             |

| P10     | 0                 | nIRSTO | <b>Intel Power-On Reset Output.</b> nIRSTO is asserted for $t_{IRSTO}$ during initial power-up.<br>See COLD START POWER-ON SEQUENCE. Connect to nRESET of Intel PXA27x processors. It is also asserted upon an nRSTI active event, if the WDT expires and when the chip transitions to SHUTDOWN state. Refer to Table 1 if not used.                                                                                                 |

| R10     | I                 | nRSTI  | <b>Manual Reset Input.</b> If this input is asserted, nRSTO and nIRSTO are asserted.<br>These outputs remain asserted until $t_{RSTO}$ and $t_{IRSTO}$ , respectively, after nRSTI is deasserted and the de-bounce interval, $t_{RSTI}$ , is completed. No power rails are modified. An internal pull-up resistor is provided. If driven from logic, it must be driven from an open drain output to prevent reverse leakage current. |