# TLE983x BC-Step

**BootROM User Manual**

V 2.60, 2012-05

## Automotive Power

Edition 2012-05 Published by Infineon Technologies AG 81726 München, Germany © Infineon Technologies AG 2012. All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie"). With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of noninfringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

| Version                  | Authors   |                 |                  |  |  |  |  |  |

|--------------------------|-----------|-----------------|------------------|--|--|--|--|--|

| Previous Version: V 2.12 |           |                 |                  |  |  |  |  |  |

| V2.60                    | 02 May 12 | Initial Release | IFX Technologies |  |  |  |  |  |

#### Table 0-1 Revision History

#### Trademarks of Infineon Technologies AG

AURIX™, C166™, CanPAK™, CIPOS™, CIPURSE™, EconoPACK™, CoolMOS™, CoolSET™, CORECONTROL™, CROSSAVE™, DAVE™, DI-POL™, EasyPIM™, EconoBRIDGE<sup>™</sup>, EconoDUAL<sup>™</sup>, EconoPIM<sup>™</sup>, EconoPACK<sup>™</sup>, EiceDRIVER<sup>™</sup>, eupec<sup>™</sup>, FCOS<sup>™</sup>, HITFET<sup>™</sup>, HybridPACK<sup>™</sup>, I<sup>2</sup>RF<sup>™</sup>, ISOFACE<sup>™</sup>, IsoPACK<sup>™</sup>, MIPAQ™. ModSTACK™, mv-d™, NovalithIC™. OptiMOS™. ORIGA™. POWERCODE™; PRIMARION™, PrimePACK™, PrimeSTACK™, PRO-SIL™. PROFET™, RASIC™, ReverSave™, SatRIC™, SIEGET™, SINDRION™, SIPMOS™, SOLID FLASH™, TEMPFET™, thinQ!™, TRENCHSTOP™, SmartLEWIS™. TriCore™.

#### Other Trademarks

Advance Design System<sup>™</sup> (ADS) of Agilent Technologies, AMBA<sup>™</sup>, ARM<sup>™</sup>, MULTI-ICE<sup>™</sup>, KEIL<sup>™</sup>, PRIMECELL<sup>™</sup>, REALVIEW<sup>™</sup>, THUMB<sup>™</sup>, µVision<sup>™</sup> of ARM Limited, UK. AUTOSAR<sup>™</sup> is licensed by AUTOSAR development partnership. Bluetooth<sup>™</sup> of Bluetooth SIG Inc. CAT-ig<sup>™</sup> of DECT Forum. COLOSSUS<sup>™</sup>, FirstGPS<sup>™</sup> of Trimble Navigation Ltd. EMV™ of EMVCo. LLC (Visa Holdings Inc.). EPCOS™ of Epcos AG. FLEXGO<sup>™</sup> of Microsoft Corporation. FlexRay<sup>™</sup> is licensed by FlexRay Consortium. HYPERTERMINAL<sup>™</sup> of Hilgraeve Incorporated. IEC<sup>™</sup> of Commission Electrotechnique Internationale. IrDA™ of Infrared Data Association Corporation. ISO™ of INTERNATIONAL ORGANIZATION FOR STANDARDIZATION. MATLAB<sup>TM</sup> of MathWorks, Inc. MAXIM™ of Maxim Integrated Products, Inc. MICROTEC™, NUCLEUS™ of Mentor Graphics Corporation. MIPI™ of MIPI Alliance, Inc. MIPS™ of MIPS Technologies, Inc., USA. muRata™ of MURATA MANUFACTURING CO., MICROWAVE OFFICE™ (MWO) of Applied Wave Research Inc., OmniVision™ of OmniVision Technologies, Inc. Openwave™ Openwave Systems Inc. RED HAT™ Red Hat, Inc. RFMD™ RF Micro Devices, Inc. SIRIUS™ of Sirius Satellite Radio Inc. SOLARIS<sup>™</sup> of Sun Microsystems, Inc. SPANSION<sup>™</sup> of Spansion LLC Ltd. Symbian<sup>™</sup> of Symbian Software Limited. TAIYO YUDEN™ of Taiyo Yuden Co. TEAKLITE™ of CEVA, Inc. TEKTRONIX™ of Tektronix Inc. TOKO™ of TOKO KABUSHIKI KAISHA TA. UNIX<sup>™</sup> of X/Open Company Limited. VERILOG<sup>™</sup>, PALLADIUM<sup>™</sup> of Cadence Design Systems, Inc. VLYNQ<sup>™</sup> of Texas Instruments Incorporated. VXWORKS<sup>™</sup>, WIND RIVER™ of WIND RIVER SYSTEMS. INC. ZETEX™ of Diodes Zetex Limited.

Last Trademarks Update 2011-11-11

| <b>1</b><br>1.1<br>1.2<br>1.3                                                             | Introduction                                                                                                                                                                | . 7<br>. 7                             |

|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| <b>2</b><br>2.1<br>2.2                                                                    | Overview                                                                                                                                                                    | . 8                                    |

| <b>3</b><br>3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7<br>3.1.7.1 |                                                                                                                                                                             | 11<br>12<br>12<br>12<br>13<br>13<br>14 |

| <b>4</b><br>4.1<br>4.2<br>4.3<br>4.3.1<br>4.3.2                                           | LIN BSL mode LIN BSL features LIN BSL mode overview Phase I: Automatic synchronization to the host General description Calculation of BR_VALUE and PRE values               | 17<br>17<br>20<br>20<br>21             |

| 4.4<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.3.1                                                 | Phase II: LIN BSL communication protocol and the working modes         Node Address for Diagnostic (NAD)         Block type         Checksum         Classic / LIN checksum | 23<br>24<br>24                         |

| 4.4.3.2<br>4.4.4<br>4.4.4.1<br>4.4.4.2<br>4.4.4.3                                         | Programming checksum<br>Mode selection<br>Receiving the header block<br>The activation of working mode 0, 2 and 8<br>The activation of working mode 1, 3 and 9              | 25<br>25<br>26                         |

| 4.4.4.4<br>4.4.4.5<br>4.4.4.6<br>4.5                                                      | The activation of working mode 4The activation of working mode 6The activation of working mode APhase III: Response protocol to the host                                    | 29<br>31<br>31<br>34                   |

| 4.5.1<br>4.5.2<br>4.5.2.1<br>4.5.2.2                                                      | Acknowledgement response<br>Error response<br>Block Type Error (FF <sub>H</sub> )<br>Checksum Error (FE <sub>H</sub> )                                                      | 35<br>35                               |

| 4.5.2.3<br>4.5.2.4<br>4.5.3<br>4.6<br>4.6.1<br>4.7<br>4.8<br>4.8.1<br>4.9                                                                                                                                        | Protection Error (FD <sub>H</sub> )<br>Response overview<br>Mode A response<br>Fast LIN BSL<br>Entering Fast LIN BSL<br>After-Reset conditions<br>User defined parameters for LIN BSL<br>Programming NAC and NAD<br>WDT1 refreshing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 35<br>37<br>38<br>38<br>40<br>41                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| <b>5</b><br>5.1<br>5.1.1<br>5.2<br>5.2.1<br>5.2.1.1<br>5.2.1.2<br>5.2.1.3<br>5.2.2<br>5.2.2.1<br>5.2.2.2<br>5.2.2.1<br>5.2.2.2<br>5.2.2.3<br>5.2.2.4<br>5.2.2.5<br>5.2.2.6<br>5.2.2.7<br>5.2.2.8<br>5.3.1<br>5.4 | UART BSL mode<br>Phase I: Automatic serial synchronization to the host<br>General description<br>Calculation of BR_VALUE and PRE values<br>Phase II: Serial communication protocol and the working modes<br>Serial communication protocol<br>Transfer block structure<br>Transfer block structure<br>Response codes to the host<br>The selection of working modes<br>Receiving the header block<br>The activation of working mode 0<br>The activation of working mode 1<br>The activation of working mode 2<br>The activation of working mode 3<br>The activation of working mode 4<br>The activation of working mode 4<br>The activation of working mode A<br>User defined parameters for UART mode<br>Programming NAC<br>WDT1 refreshing | $\begin{array}{c} 42\\ 43\\ 44\\ 45\\ 45\\ 46\\ 49\\ 49\\ 51\\ 52\\ 53\\ 54\\ 56\\ 57\\ 61\\ 62\\ \end{array}$ |

| <b>6</b><br>6.1<br>6.2.1<br>6.2.2<br>6.3<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>6.3.5                                                                                                                            | NVM         NVM overview         NVM organisation         NVM configuration sectors organisation         100 Time Programmable data         One-Time Programmable (OTP)         NVM user routines organisation         Opening assembly buffer routine         NVM programming routine         NVM page erasing routine         Abort NVM programming routine         Read NVM status routine                                                                                                                                                                                                                                                                                                                                              | 64<br>66<br>66<br>72<br>72<br>74<br>75<br>76<br>77                                                             |

| 6.3.6   | Read user calibration data                        | . 78  |

|---------|---------------------------------------------------|-------|

| 6.3.7   | Read NVM config status routine                    |       |

| 6.3.8   | Read NVM ECC2 address routine                     | . 79  |

| 6.3.9   | Read NVM protection status routine                | . 80  |

| 6.3.10  | Set NVM program protection (code) routine         | 81    |

| 6.3.11  | Clear NVM program protection (code) routine       | 81    |

| 6.3.12  | Set NVM read protection (code) routine            |       |

| 6.3.13  | Clear NVM read protection (code) routine          |       |

| 6.3.14  | Set NVM program protection (data) routine         | . 83  |

| 6.3.15  | Clear NVM program protection (data) routine       |       |

| 6.3.16  | Set NVM read protection (data) routine            |       |

| 6.3.17  | Clear NVM read protection (data) routine          | . 84  |

| 6.3.18  | Read OTP data routine                             | . 85  |

| 6.3.19  | Program OTP routine                               | . 86  |

| 6.3.20  | LIN autobaud routine                              | . 87  |

| 6.3.21  | UART autobaud routine                             | . 87  |

| 6.3.22  | User XRAM download routine                        | . 88  |

| 6.3.23  | Read 100 Time Programmable parameter data routine | . 88  |

| 6.3.24  | Program 100 Time Programmable routine             | . 89  |

| 6.3.25  | Sector Erasing Routine                            | . 89  |

| 6.3.26  | User clock setting routine                        | . 90  |

| 6.3.27  | NVMCLKFAC setting routine                         | . 90  |

| 6.3.28  | XRAM MBIST starting routine                       | . 91  |

| 6.3.29  | XRAM MBIST check routine                          | . 91  |

| 6.4     | NVM user applications                             |       |

| 6.4.1   | NVM integrity handling (Service Algorithm)        | . 92  |

| 6.4.2   | Supporting background NVM operation               | . 93  |

| 6.4.3   | Emergency operation handling                      |       |

| 6.4.3.1 | Emergency operation handling - Type 1 routines    | . 94  |

| 6.4.3.2 | Emergency operation handling - Type 2 routines    |       |

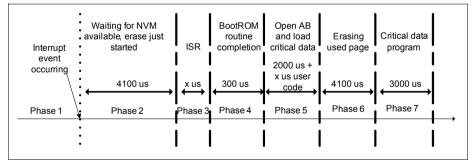

| 6.4.3.3 | Emergency operation handling timing               |       |

| 6.4.4   | NVM user routines operation                       |       |

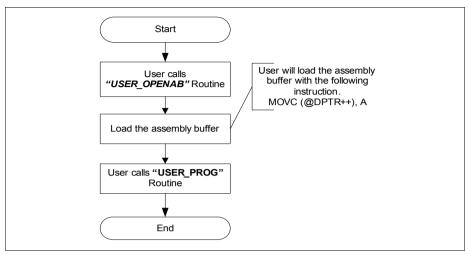

| 6.4.4.1 | NVM user programming operation                    | . 98  |

| 6.4.4.2 | Tearing-safe Programming                          |       |

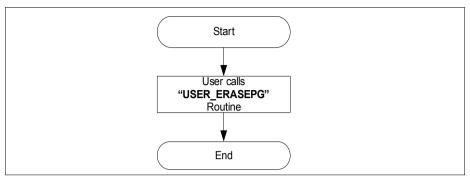

| 6.4.4.3 | NVM user erase operation                          |       |

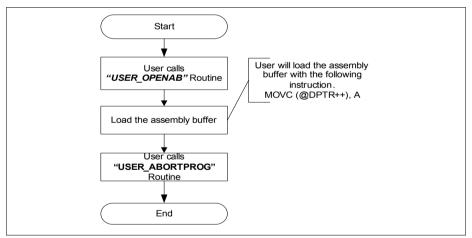

| 6.4.4.4 | NVM user programming abort operation              |       |

| 6.4.5   | Protection mechanism on NVM                       | . 100 |

#### Introduction

## 1 Introduction

This document specifies the BootROM firmware behavior for the TLE983x family. The specification is organised into the following major sections:

- BootROM Overview

- Startup Procedure

- · LIN and UART BSL features

- NVM structure and user routines description.

### 1.1 Purpose

The document describes the functionalities of the BootROM firmware.

### 1.2 Scope

The BootROM firmware for the TLE983x family will provide the following features

- Startup procedure for stable operation of TLE983x chip

- BSL mode for users to download and run code from NVM and XRAM

- NVM organization and operation

### 1.3 Abbreviations and special terms

List of terms and abbreviations used throughout the document:

- BSL BootStrap Loader

- CS Configuration Sector

- DAP Device Access Port

- EOT End of Transmission

- EVR Embedded Voltage Regulator

- NAC No Activity Count

- NAD Node address for diagnostic

- NVM Non Volatile Memory

- OCDS On-Chip Debug Support

- PEM Program Execution Mode

- SA Service Algorithm

- WDT WatchDog Timer

#### Overview

### 2 Overview

This specification includes the description of the operations and tasks defined to support the general startup behaviour and various boot options

### 2.1 Firmware architecture

TLE983x on-chip BootROM consists of the startup procedure, the bootstrap loader via LIN, the bootstrap loader via UART, NVM user routines, NVM integrity handling routines and on-chip debug support.

The BootROM in TLE983x, is located at  $0000_{\rm H}$  in Bank 0 during active memory map 1 and  $9000_{\rm H}$  in Bank 2 at active memory map 0. Upon a hardware reset, microcontroller will always be in the active memory map 1 (by default) and execute the BootROM code. The beginning of the startup procedure changes the memory map setting and does a long jump (ljmp) to the subroutine, MAIN. This instruction will then capture the absolute address of subroutine MAIN, do a swap to active memory map 0 and execute the remaining BootROM code at  $9000_{\rm H}$  in Bank 2 in active memory map 0. Active memory map 1 will be just a stepping stone to active memory map 0, all other instructions will be executed in the active memory map 0.

The startup procedure also includes the EVR calibration, map-RAM initialisation, on-chip oscillator configurations, NVM protection enabling and branching to the different modes. The deciding factor will be on the latch values of TMS, P0.0 and P0.2 upon a reset. During reset, these signals are latched at the rising edge of RESET pin.

There are generally 2 operation modes in the BootROM:

- User / BSL mode

- OCDS mode

For user mode, it will just execute the startup procedure and finally jumping to  $0000_{\rm H}$  to execute the user program.

Table 2-1 lists the boot options available in the TLE983x.

#### Overview

| TMS <sup>1)</sup> /DAP1 | P0.0<br>/DAP0 | P0.2 | Mode / Comment                       |

|-------------------------|---------------|------|--------------------------------------|

| 0                       | Х             | Х    | User mode / BSL mode <sup>2)3)</sup> |

| 1                       | 0             | Х    | Device test mode <sup>4)</sup>       |

| 1                       | 1             | 0    | OCDS mode with DAP port              |

| 1                       | 1             | 1    | Device test mode <sup>4)</sup>       |

#### Table 2-1 TLE983x Boot options

<sup>1)</sup> When TMS is latched 1 (i.e. high) upon reset, DAP pins will be enabled by hardware. When TMS = 1, P0.0 must be 1. The hardware enable of DAP pins with these boot configuration must not be changed by port control.

<sup>2)</sup> On-chip OSC is selected as PLL input. System is running on LP\_CLK until firmware switches to PLL output before jumping to user code. Exception is with hardware reset where user settings are retained.

<sup>3)</sup> Boot in user mode or BSL mode depends on the NAC word in user memory (NVM).

<sup>4)</sup> Power up with special internal settings. At completion, device runs in endless loop. No flash code execution is performed.

### 2.2 Program structure

The different sections of the BootROM provide the following basic functionalities.

#### Startup procedure

The startup procedure is the main control program in the BootROM. It is the first software controlled operation in the BootROM that is executed after any reset.

The startup procedure will perform configuration sector verification, EVR calibration, onchip oscillator trimming, map-RAM initialisation, BootROM protection, NVM protection and decode the pin-latched values of the TMS, P0.0 and P0.2 to determine which mode it will jump to.

#### User mode

It is used to support user code execution at NVM address 0000<sub>H</sub>.

#### LIN BSL mode

It is used to support BSL via LIN like protocol. Downloading of code/data to XRAM and NVM related programming is supported in this mode.

#### UART BSL mode

It is used to support BSL via UART protocol. Downloading of code/data to XRAM and NVM related programming is supported in this mode.

#### Overview

### OCDS mode

To support the OCDS, a portion of the BootROM is used to store the OCDS initialization, and a Monitor program which will interact with the external debugger. By default, through the OCDS mode, the DAP interface is enabled.

### 3 Startup procedure

This chapter describes the BootROM startup procedure in TLE983x.

The startup procedure is the first software-controlled operation in the BootROM that is automatically started after every reset. Certain operations are skipped depending on the type of reset and the error which might occur. Refer to **Section 3.1** for further details.

### 3.1 Program structure

First task executed by the startup firmware is switching to active memory map 0. Afterwards, the type of reset is checked. For power-on reset or brown-out reset or wakeup reset from sleep mode, XRAM and IRAM memory tests and initialization are started while they are skipped for the other resets. Anyhow, in the startup code monitor IRAM is used to avoid destroying the user IRAM content.

After that, depending on the type of reset, the firmware will do NVM protection, NVM map-RAM initialisation, on-chip oscillator trimming, PLL setting and analog module trimming. It will decode the pin-latched values of the TMS, P0.0 and P0.2 to determine which mode it will jump to.

If bootup mode is OCDS mode, the WDT1 is disabled. For entry to user mode, the WDT1 remains active. Next, it will wait for NVM module to be ready.

For software, or watchdog reset, the following steps are skipped:

- NVM Map-RAM initialisation

- Setting of oscillator and PLL

- Download of analog modules trimming parameters from first 100TP page

- · Download of user configuration data from OTP or 100TP page into the XRAM

- Switching system clock input to PLL output

- Clearing of NMI status and presupply warning status before exit to user mode or OCDS mode

### 3.1.1 Test and initialisation of IRAM and XRAM

A functional test on IRAM (both user IRAM and monitor IRAM) and XRAM (optional) is executed after power on reset, brown out reset or wake-up reset from sleep mode. The test consists of a linear write/read algorithm using alternating data.

In case an error is detected the device is set to loop endlessly. Moreover, in case the test is completed successfully, XRAM and IRAMs are initialised to zero with proper ECC status. This is needed to prevent an ECC error during user code execution due to a write operation to an un-initialised location (with invalid ECC code).

While IRAM tests are automatically started after every power on reset, brown out reset or wake-up reset from sleep mode, the XRAM test is optional. It can be enabled and controlled by proper programming of the bytes stored in first 100TP page as described in the **Table 6-4**.

In particular the relevant parameters are:

- CS\_XRAM\_MBIST\_STARTUP\_EN (offset=74<sub>H</sub>): When set to C3<sub>H</sub> it enables the XRAM test after a power on reset, brown out reset or wake-up reset from sleep mode. All other values will be ignored and XRAM test at startup will not be enabled.

- CS\_XRAM\_MBIST\_LOW\_BOUND\_H: (offset=75<sub>H</sub>): It defines the high Byte of the starting address of the XRAM range to be tested. This Byte is ignored if XRAM test is not enabled.

- CS\_XRAM\_MBIST\_LOW\_BOUND\_L: (offset=76<sub>H</sub>): It defines the low Byte of the starting address of the XRAM range to be tested. This Byte is ignored if XRAM test is not enabled.

- CS\_XRAM\_MBIST\_HIGH\_BOUND\_H: (offset=77<sub>H</sub>): It defines the high Byte of the ending address of the XRAM range to be tested. This Byte is ignored if XRAM test is not enabled.

- CS\_XRAM\_MBIST\_HIGH\_BOUND\_L: (offset=78<sub>H</sub>): It defines the low Byte of the ending address of the XRAM range to be tested. This Byte is ignored if XRAM test is not enabled.

Once the user IRAM test, IRAM initialisation and the optional XRAM test are done, monitor IRAM is selected and the startup procedure proceeds to check on the NVM status while XRAM initialisation is still running. The firmware will wait for XRAM initialization to be completed before exiting to user code.

### 3.1.2 NVM initialisation routine

This routine will set the NVM protection according to the password in the configuration sector.

### 3.1.3 NVM map-RAM initialisation

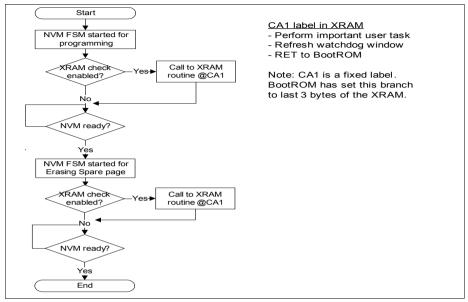

The map-RAM initialisation operation is triggered to restore the map-RAM contents. If one or more errors are detected in the map-RAM initialisation, the service algorithm routine is called to do the repair (refer to **Section 6.4.1**).

### 3.1.4 Oscillator trimming and system clock selection

After every power on reset, brown out reset or wake-up reset from sleep mode the system runs with an internal low precision clock (nominally 20 MHz). During the start up procedure, the internal oscillator and PLL are trimmed to a fixed standard value of 24 MHz. In order to reduce the boot time, the start up procedure continues to run with the low precision clock while the PLL is locking. System clock will be switched to PLL output before jumping to user or BSL mode in case of successful lock. Once user mode is entered, user is allowed to set the final desired frequency by proper register setting or by means of the dedicated user routine (refer to Section 6.3.26).

### 3.1.5 Analog module trimming

In this routine, the trimming values of voltage regulators, LIN module, temperature sensor, LS switch, HS switch and other analog modules are read from the configuration sector and written into the respective external SFR. Protected Bits of the addressed external SFRs will not be affected by this operation. For user mode or OCDS mode, checksum on 100TP page is evaluated. In case of error, default values are used. Refer to **Table 6-4** for a list of user parameters in 100TP page.

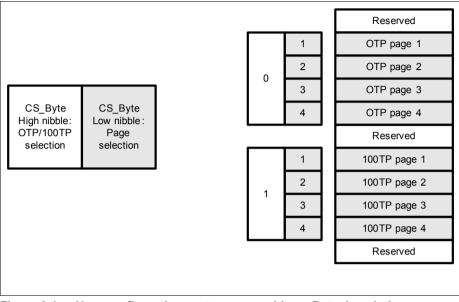

### 3.1.6 User configuration data download

The firmware provides a routine to download data stored in user accessible configuration sector pages (OTP and 100TP) during the startup flow. In particular, the routine copies a specified number of Bytes from a selected CS page (starting always from first Byte in the page) into the XRAM (starting at a given address). The routine is by default disabled and can be enabled and controlled by proper programming of the Bytes stored in first 100TP page (refer to Figure 6-1) as described in the Table 6-4. This routine is anyhow not performed after a software or watchdog reset.

Relevant parameters for routine control are:

- CS\_USER\_CAL\_STARTUP\_EN (offset=79<sub>H</sub>): When set to C3<sub>H</sub> it enables the user data download from an OTP or 100TP page into the XRAM during startup flow. All other values will be ignored and the routine will not be executed at startup.

- CS\_USER\_CAL\_XADDH: (offset=7A<sub>H</sub>): It defines the high Byte of the XRAM starting address where to copy data downloaded from CS. This Byte is ignored if the routine is not enabled.

- CS\_USER\_CAL\_XADDL: (offset=7B<sub>H</sub>): It defines the low Byte of the XRAM starting address where to copy data downloaded from CS. This Byte is ignored if the routine is not enabled.

- CS\_USER\_CAL\_CS\_PAGE: (offset=7C<sub>H</sub>): It defines the CS page where data has to be downloaded from (refer to Figure 6-1). This Byte is ignored if the routine is not enabled.

- CS\_USER\_CAL\_NUM: (offset=7D<sub>H</sub>): It defines the number of Bytes to be downloaded starting from the first Byte of the selected CS page. This Byte is ignored if the routine is not enabled.

The routine has been developed to support downloading of the ADC1 calibration parameters stored at the beginning of the first 100TP page (see **Table 6-4**) into the XRAM for an easy access but can be more generally used for all other CS user parameters. If the routine is enabled, firmware will wait for XRAM initialization completion before copying the data. Moreover, independent of startup setting, a similar routine is provided as NVM user routine (refer to **Section 6.3.6**)

### 3.1.7 User / BSL mode entry

Entry to user mode is determined by the No Activity Count (NAC) value which is defined in the user code.

If NVM double Bit error occurs when reading the NAC value, the system goes into endless loop.

Before exiting to user mode, the system clock frequency is switched to PLL output previously set by default to 24 MHz. In case PLL has not locked within 1 ms, the CPU clock source LP\_CLK (low precision clock running nominally at 20 MHz) will be used. All SFRs are reset to default values and the user internal ram is selected.

Note: User mode is entered jumping to NVM starting address. This can happen directly from startup routine, after a waiting time for possible BSL communication, or as a result of BSL commands. In all these cases, jump to user mode will only occur either (1) when NVM is not protected and NVM content at 0000<sub>H</sub> is not FF<sub>H</sub> or (2) when NVM is protected. In all other cases, firmware will put the device in sleep mode.

### 3.1.7.1 NAC definition

The NAC value specifies the duration of delay before jumping to user mode measured from the reset release. The Bit 7 of the NAC will determine which BSL mode to enter. In particular, the device will enter LIN BSL mode if the NAC Bit 7 is equal to zero and UART BSL mode if it is equal to one.

After ending the start up procedure, the program will detect any activities on the LIN bus / UART for a period of time, determined by (((NAC & 7F<sub>H</sub>) -1<sub>H</sub>) \* 5) ms reduced by the time already spent to perform the start up procedure. When nothing is detected on the LIN bus / UART and (((NAC & 7F<sub>H</sub>) -1<sub>H</sub>) \* 5) ms is passed from reset going high, the microcontroller will jump to user mode. Anyhow, if NAC is 1<sub>H</sub> or 81<sub>H</sub>, user mode is entered immediately.

NAC value is restricted to  $C_H$  as the first open WDT1 window is worst case 65 ms. The firmware has to either refresh the WDT within the 65 ms or jump to user mode. If NAC is not valid, BootROM code will switch off the WDT and wait for a LIN frame indefinitely.

Table 3-1 gives an overview of the action of the microcontroller with respect to No

Activity Count (NAC) values

Note: Timer 0 is initialized to have 5 ms overflow and is used to create the delay.

| Table 3-1                             | Type of ac               | tion w.r.t. No Activity Count (NAC) values            |

|---------------------------------------|--------------------------|-------------------------------------------------------|

| NAC Value                             |                          | Action                                                |

| 01 <sub>H</sub> , 81 <sub>H</sub>     |                          | 0 ms delay. Jump to user mode immediately             |

| 02 <sub>H</sub> , 82 <sub>H</sub>     |                          | 5 ms delay before jumping to user mode <sup>1)</sup>  |

| 03 <sub>H</sub> , 83 <sub>H</sub>     |                          | 10 ms delay before jumping to user mode <sup>1)</sup> |

| 04 <sub>H</sub> , 84 <sub>H</sub>     |                          | 15 ms delay before jumping to user mode <sup>1)</sup> |

| 05 <sub>H</sub> , 85 <sub>H</sub>     |                          | 20 ms delay before jumping to user mode <sup>1)</sup> |

| 06 <sub>H</sub> , 86 <sub>H</sub>     |                          | 25 ms delay before jumping to user mode <sup>1)</sup> |

| 07 <sub>H</sub> , 87 <sub>H</sub>     |                          | 30 ms delay before jumping to user mode <sup>1)</sup> |

| 08 <sub>H</sub> , 88 <sub>H</sub>     |                          | 35 ms delay before jumping to user mode <sup>1)</sup> |

| 09 <sub>H</sub> , 89 <sub>H</sub>     |                          | 40 ms delay before jumping to user mode <sup>1)</sup> |

| 0A <sub>H</sub> , 8A <sub>H</sub>     |                          | 45 ms delay before jumping to user mode <sup>1)</sup> |

| 0B <sub>H</sub> , 8B <sub>H</sub>     |                          | 50 ms delay before jumping to user mode <sup>1)</sup> |

| 0C <sub>H</sub> , 8C <sub>H</sub>     |                          | 55 ms delay before jumping to user mode <sup>1)</sup> |

| 0D <sub>H</sub> - 7F <sub>H</sub> , 0 | 0 <sub>H</sub> , Invalid | Wait forever for the first LIN frame                  |

| 8D <sub>H</sub> - FF <sub>H</sub> , 8 | 0 <sub>H</sub>           | Wait forever for the first UART frame                 |

<sup>1)</sup> If a LIN frame/UART frame is received within the delay period, the following actions occur; (1) the remaining delay is ignored, (2) it will not enter user mode anymore (3) it will process the LIN / UART frame accordingly

The NAC value is stored, together with the NAD value, in the last 4 Bytes of the linearly mapped NVM region. The Table 3-2 shows the addresses for the all the available family devices. To ensure the parameter validity, the 2 parameters actual values and their inverted values are checked. In case the stored value and inverted value are not consistent (value + inverted value + 1 not equal to 0) the parameter is considered to be invalid and the default value will be used.

| Table 3-2 NAC and NAD parameters details |                        |                                                                                                 |                 |  |

|------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------|-----------------|--|

| Address                                  | User Defined Value     | Criteria / Range                                                                                | Default         |  |

| YFFC <sub>H</sub> <sup>1)</sup>          | NAC                    | 01 <sub>H</sub> - 0C <sub>H</sub> for LIN BSL<br>81 <sub>H</sub> - 8C <sub>H</sub> for UART BSL | 7F <sub>H</sub> |  |

| YFFD <sub>H</sub> <sup>1)</sup>          | NAC                    | Inverted NAC value                                                                              |                 |  |

| YFFE <sub>H</sub> <sup>1)</sup>          | NAD (for LIN BSL only) | $01_{\text{H}}$ - FF <sub>H</sub> (00 <sub>H</sub> is reserved)                                 | 7F <sub>H</sub> |  |

| YFFF <sub>H</sub> <sup>1)</sup>          | NAD (for LIN BSL only) | Inverted NAD value                                                                              | -               |  |

### Table 3-2 NAC and NAD parameters details

<sup>1)</sup> Y is equal to 4, 7, A or E for the 24, 36, 48 or 64 kByte respectively

### 4 LIN BSL mode

LIN BSL is a LIN like protocol based on LIN 2.0 but for security reason the checksum is inverted for most of the supported modes. Standard LIN protocol can support a max. baud rate of 20 kBaud. FastLIN BSL protocol is an enhanced feature implemented in TLE983x device. This is introduced to support baud rates of 20 kBaud to 57.6 kBaud and 115.2 kBaud via a single-wire UART using UART BSL protocol (See Section 4.6).

### 4.1 LIN BSL features

Features that are implemented include:

- 1. Re-synchronization to the transfer speed (baud rate) of the communication partner upon receiving every frame

- 2. Using Diagnostic Frame (Master Request and Slave Response)

- 3. Usage of user values (NAD and NAC) stored in uppermost linearly mapped NVM

- 4. Non standard LIN checksum (Programming checksum, see Section 4.4.3.2)

- 5. Fast LIN BSL using UART protocol on single-wire UART (LIN)

### 4.2 LIN BSL mode overview

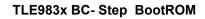

The LIN BSL mode consists of three functional phases described below:

- **Phase I**: To establish a connection with every frame (Master Request or Slave Response frame) received by automatically synchronizing to the transfer speed (baud rate) of the communication partner (host).

- **Phase II**: To execute the host specified command. In order to execute the commands, host needs to send a Master Request Header first, followed by a Command frame. The selected mode information is embedded in the Command frame.

- The possible modes are:

- Mode 0 (00<sub>H</sub>): Transfer a user program from the host to XRAM<sup>1</sup>)

- Mode 1 (01<sub>H</sub>): Execute a user program in the XRAM<sup>2)</sup>

- Mode 2 (02<sub>H</sub>): Transfer a user program from the host to NVM<sup>1</sup>)

- Mode 3 (03<sub>H</sub>): Execute a user program in the NVM<sup>2)</sup>

- Mode 4 (04<sub>H</sub>): Erase NVM<sup>1</sup>)

- Mode 6 (06<sub>H</sub>): NVM Protection mode enabling/disabling Scheme<sup>2)</sup>

- Mode 8 (08<sub>H</sub>): Transfer a user program from the host to XRAM using classic LIN checksum<sup>3</sup>)

- Mode 9 (09<sub>H</sub>): Execute a user program in the XRAM using classic LIN checksum<sup>4</sup>)

- Mode A (0A<sub>H</sub>): Get info (based on Option Byte)<sup>1)</sup>

<sup>1)</sup> The microcontroller returns to the beginning of Phase I/II and wait for the next command from the host

<sup>2)</sup> LIN BSL and serial communication are exited.

<sup>&</sup>lt;sup>3)</sup> Similar to mode 0. mode 8 uses classic LIN checksum instead of Programming checksum.

<sup>&</sup>lt;sup>4)</sup> Similar to mode 1. mode 9 uses classic LIN checksum instead of Programming checksum.

LIN BSL supports Fast Programming through modes 0, 2 and 8 with the selection of Fast Programming Option. Refer to **Section 4.4.4.2** for more details.

• **Phase III**: To send microcontroller status to host. In order to receive the microcontroller status, host needs to send a Slave Response Header first.

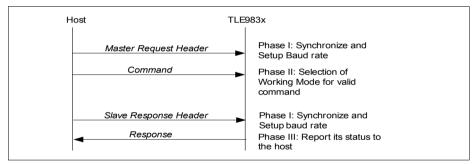

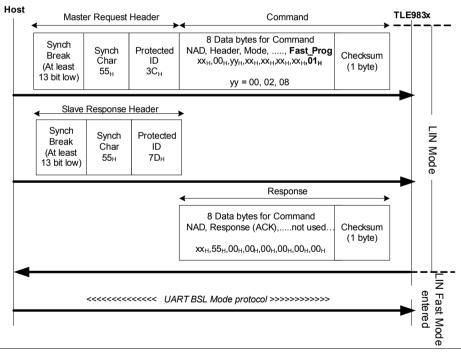

Re-synchronization and setup of baud rate (Phase I) are done at all times (before Phases II and III). Thus, different baud rates can be supported. Phase II is entered when its Master Request Header is received, otherwise Phase III is entered (Slave Response Header). The Master Request Header has a Protected ID of  $3C_H$  while the Slave Response Header has a Protected ID of  $7D_H$ . The Command and Response frames are identified as Diagnostic LIN frame which has a standard 8 data Byte structure (instead of 2 or 4).

**Figure 4-1** shows the relationship between the PC host and the microcontroller for the 3 phases, while **Figure 4-2** shows the Master Request Header, Slave Response Header, Command and Response frames.

Figure 4-1 LIN mode - Phases I, II and III

#### Figure 4-2 LIN mode - Frames

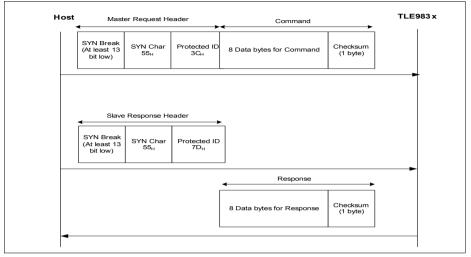

For all modes' entry, the Master Request Header is transmitted from host to microcontroller, followed by the command, which is the header block. The Slave Response Header is transmitted to check the status of the operation. For mode 0, 2 and 8, there is no need to send a Slave Response Header after every data block. The microcontroller supports multiple data block transfers (up to 256 data blocks) without sending a Slave Response Header, which saves overhead. As the commands are sent one after another without waiting for any status indication, a certain delay is required as shown in **Figure 4-3** to ensure sufficient time is provided for the microcontroller to execute the desired operations.

### Figure 4-3 Communication structure of the LIN BSL modes

### 4.3 Phase I: Automatic synchronization to the host

Upon entry to LIN mode, a connection is established. The transfer speed (baud rate) of the device is automatically synchronized to the serial communication partner (host) in the following steps:

- STEP 1: Initialize LIN interface for reception and timer 2 for baud rate measurement

- STEP 2: Wait for an incoming frame from host

- STEP 3: Synchronize the baud rate to the host

- STEP 4: Enter Phase II (for Master Request Frame) or Phase III (for Slave Response Frame)

- Note: Re-synchronization and setup of baud rate are always done for **every** Master Request Header or Slave Response Header frame.

#### 4.3.1 General description

The LIN baud rate detection feature provides the capability to detect the baud rate within the LIN protocol using timer 2. Initialization consists of:

Serial port of the microcontroller set to mode 1 (8-bit UART, variable baud rate) for communication

- baud rate range for detection, controlled by the field BGSEL of the BCON, set to "5.5 to 166.7 kBaud".

- · Capture Timer 2 data register contents on negative transition at pin T2EX

- Timer 2 external events are enabled (EXF2 flag is set when a negative transition occurs at pin T2EX)

- $f_{T2}=f_{PCLK}/8$  (T2PRE=011<sub>B</sub>)

As shown in Figure 4-2, the LIN Header frame consists of the:

- synch Break (13 Bits time low)

- synch Byte (55<sub>H</sub>)

- Protected ID field

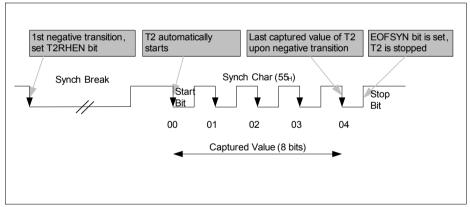

The Break is used to signal the beginning of a new frame and must be at least 13 Bits of dominant value. When negative transition is detected at pin T2EX at the beginning of Break, the Timer 2 External Start Enable Bit (T2MOD.T2RHEN) is set. This will automatically start Timer 2 at the next negative transition of pin T2EX. Finally, the end of synch Byte flag (LINST.EOFSYN) is polled. When this flag is set, Timer 2 is stopped. T2 Reload/Capture register (RC2H/L) is the time taken for 8 Bits. Then the LIN routine calculates the actual baud rate, sets the PRE and BG values and activates baud Rate Generator. The baud rate detection for LIN is shown in Figure 4-4

Figure 4-4 LIN autobaud rate detection

### 4.3.2 Calculation of BR\_VALUE and PRE values

To set up auto baud rate detection, the BG and PRE values must be calculated. As there are two unknown values, two formulas are therefore needed. Firstly, the correlation

between the baud rate (baud) and the reload value BR\_VALUE (stored in the registers BGL and BGH) depends on the internal peripheral frequency ( $f_{PCLK}$ ):

$$baud = \frac{f_{PCLK}}{16 \times PRE \times (BR_VALUE)}$$

[4.1]

The previous reported formula is valid in the hypothesis that the use of fractional divider is not required.

Secondly, the relation between the baud rate (baud) and the captured value of Timer 2 (T2) depends on the T2 peripheral frequency ( $f_{T2}$ ) and the number of received Bits ( $N_{\rm b}$ ):

baud =

$$\frac{f_{T2} \times N_b}{T2}$$

[4.2]

Combining Equation [4.1] and Equation [4.2] with  $N_b=8$ ,  $f_{T2}=f_{PCLK} / 8$  (T2PRE=011<sub>B</sub>) results in the following:

$$\frac{f_{PCLK}}{16 \times PRE \times (BR_VALUE)} = \frac{\frac{f_{PCLK}}{8} \times 8}{T2}$$

[4.3]

By simplifying **Equation** [4.3], the following is obtained:

$$PRE \times (BR_VALUE) = \frac{T2}{16}$$

[4.4]

After setting BR\_VALUE and PRE, the baud rate generator will then be enabled, and the subsequent Command frame or Response frame will follow this baud rate.

#### 115.2 kBaud for FAST LIN

To support FAST LIN with baud rate 115.2 kBaud, fractional divider needs to be enabled. The detection of 115.2 kBaud is determined by the T2 timing. If T2H and T2L is less than  $154_{\rm H}$  (i.e. baud rate roughly above 70 kBaud), baud rate will be set to 115.2 kBaud.

In such a case, the correlation between the baud rate, the reload value BR\_VALUE, the fractional divider setting and the internal peripheral frequency ( $f_{PCLK}$ ) is:

baud =

$$\frac{f_{PCLK}}{16 \times PRE \times \left(BR_VALUE + \frac{FDSEL}{32}\right)}$$

[4.5]

As a consequence, the settings for 115.2 kBaud are:

- BR\_VALUE = 13 (SFR BGL.BR\_VALUE = 101<sub>B</sub> and SFR BGH = 1<sub>H</sub>)

- PRE (SFR BCON.BRPRE) = 000<sub>B</sub>

- Read FD\_SEL value from configuration sector and store into SFR BGL. FD\_SEL

## 4.4 Phase II: LIN BSL communication protocol and the working modes

Once successful synchronization to the host is completed (with a Master Request Header), the routine enters Phase II. Here, the host communicates to the microcontroller the desired working mode.

A simple transfer protocol is defined for the communication between the host and TLE983x. The protocol data is performed in information blocks. The information block follows a specified block structure and termed transfer block. Each transfer block is 9 Bytes long. A transfer block has the following structure:

| NAD      | Block Type | Data Area   | Checksum   |

|----------|------------|-------------|------------|

| (1 byte) | (1 byte)   | (6 bytes)   | (1 byte)   |

| (1 5)(6) | (15)(6)    | (0 5 3 100) | (1 5 3 10) |

- NAD: Node Address for Diagnostic, specifies the address of the active slave node. See Section 4.4.1.

- Block Type: This field determines the type of the message (See Section 4.4.2).

- Data Area: This is the data of the block. The length is fixed at 6 Bytes.

- **Checksum**: This checksum is calculated based on the NAD, Block Type and Data Area. See Section 4.4.3.

### 4.4.1 Node Address for Diagnostic (NAD)

This field specifies the address of the active slave node. Only slave nodes have an address. The NAD address range supported in TLE983x is listed in Table 4-1.

| NAD Value                                                                | Description                                                                       |

|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| 00 <sub>H</sub>                                                          | Invalid Slave Address                                                             |

| 7F <sub>H</sub>                                                          | Default Address (NAD value is invalid or it is not programmed in NVM linear area) |

| 01 <sub>H</sub> to 7E <sub>H</sub><br>80 <sub>H</sub> to FF <sub>H</sub> | Valid Slave Address                                                               |

Table 4-1 NAD address range

Note: LIN block with Broadcast NAD (7F<sub>H</sub>) is ignored if valid NAD value is programmed in NVM linear area.

Note: For NAD address and details refer to Table 3-2.

### 4.4.2 Block type

This field determines the types of transfer blocks. There are 3 transfer block types shown in **Table 4-2**.

| Block Name                         | Block Type      | Description                                                                                                                                              |

|------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Header block                       | 00 <sub>H</sub> | Special information is contained in the data area of the block, which is used to select different working modes.                                         |

| Data block                         | 01 <sub>H</sub> | This block is used in working modes 0, 2 and 8 to transfer a portion of program code. The program code is in the data area of the block.                 |

| End of Transmission<br>(EOT) block | 02 <sub>H</sub> | This block is the last block in data transmission in working modes 0, 2 and 8. The last program code to be transferred is in the data area of the block. |

Table 4-2 Type of transfer block

### 4.4.3 Checksum

Diagnostic LIN frame always uses classic checksum where checksum calculation is over the data Bytes only. The Checksum is the last field of Command and Response LIN frames. For TLE983x, there are 2 types of checksum implemented, Classic (LIN) and Programming checksum. Both Programming and LIN Checksum are supported and are indicated in the respective modes.

### 4.4.3.1 Classic / LIN checksum

The classic checksum is a standard LIN checksum used for communication with LIN 2.0 slaves. The classic checksum contains the inverted eight Bits sum with carry<sup>1)</sup> over all data Bytes.

### 4.4.3.2 Programming checksum

The programming checksum, or Inverted Classic checksum is a non-LIN standard checksum. This is implemented in TLE983x to allow other slaves (not in TLE983x BSL mode) on the LIN bus to ignore this Programming frame. The inversion of the classic checksum yields the programming checksum.

<sup>&</sup>lt;sup>1)</sup> the checksum is calculated summing all values (8-bit sum with carry) and subtracting 255 every time the sum is greater or equal to 256 (which is not the same as modulo-255 or modulo-256).

An example of the calculation of the Programming checksum is provided in **Table 4-3**. For this example, data of  $4A_H$ ,  $55_H$ ,  $93_H$  and  $E5_H$  is considered. The calculated programming checksum is  $19_H$ . The classic checksum is an inversion of the programming checksum value (i.e.  $E6_H$ ).

| Addition of data                            | HEX               | Result          | CARRY | Addition with CARRY |

|---------------------------------------------|-------------------|-----------------|-------|---------------------|

| <b>4A</b> <sub>H</sub>                      | 4A <sub>H</sub>   | 4A <sub>H</sub> | 0     | 4A <sub>H</sub>     |

| (4A <sub>H</sub> ) + <b>55</b> <sub>H</sub> | 9F <sub>H</sub>   | 9F <sub>H</sub> | 0     | 9F <sub>H</sub>     |

| (9F <sub>H</sub> ) + <b>93</b> <sub>H</sub> | 0132 <sub>H</sub> | 32 <sub>H</sub> | 1     | 33 <sub>H</sub>     |

| (33 <sub>H</sub> ) + <b>E5</b> <sub>H</sub> | 0118 <sub>H</sub> | 18 <sub>H</sub> | 1     | 19 <sub>H</sub>     |

### Table 4-3 Programming checksum

### 4.4.4 Mode selection

When Phase II is entered, TLE983x waits for the Command frame and the header block from the host containing indication about the desired mode to be selected.

### 4.4.4.1 Receiving the header block

The header block is always the first transfer block to be sent by the host during each data communication process. It contains the mode number and special information on the related mode (referred to as "Mode Data"). The general structure of a header block is shown below.

|          | Block Type            |          | Checkeum  |          |

|----------|-----------------------|----------|-----------|----------|

| NAD      | <b>00<sub>н</sub></b> | Mode     | Mode Data | Checksum |

| (1 byte) | (Header Block)        | (1 byte) | (5 bytes) | (1 byte) |

Description:

- NAD: Node Address for Diagnostic. See Section 4.4.1

- Block Type 00<sub>H</sub>: The Block Type, which marks the block as a header block

- Mode: The mode to be selected. The implemented modes are covered in Section 4.2

- Mode Data: Five Bytes of special information to activate corresponding mode.

- Checksum: The programming or LIN checksum of the header block.

Note: Mode 8 and mode 9 support LIN checksum, while mode 0 - 4, 6, and A support Programming checksum.

### 4.4.4.2 The activation of working mode 0, 2 and 8

Mode 0, 2 and 8 are used to transfer a user program from host to microcontroller. Mode 0 and 8 allow XRAM transfers, while mode 2 allows NVM transfers.

The header block has the following structure:

#### The header block

|              |           |                                                                       |                                   | Mode Data (5 bytes)              |                                          |                         |                           |                      |  |

|--------------|-----------|-----------------------------------------------------------------------|-----------------------------------|----------------------------------|------------------------------------------|-------------------------|---------------------------|----------------------|--|

| NA<br>(1 byt | I (Header | 00 <sub>H</sub> /02 <sub>H</sub> /08 <sub>H</sub><br>(Mode 0/2/<br>8) | Start<br>Addr<br>High<br>(1 byte) | Start<br>Addr<br>Low<br>(1 byte) | No of Data<br>Blocks<br>Used<br>(1 byte) | Not<br>Used<br>(1 byte) | Fast_<br>Prog<br>(1 byte) | Checksum<br>(1 byte) |  |

Mode Data Description:

**Start Addr High, Low**: 16-bit Start Address, which determines where to copy the received program codes in the XRAM/NVM<sup>1)</sup>.

**No. of data blocks used:** Total number of data blocks to be sent, maximum 256 ( $FF_H$ ) for mode 0 and 8 and maximum 21 ( $15_H$ ) for mode 2. It is verified when EOT block is received. If number does not match, microcontroller will send a Block Type Error. PC host will then have to re-send the whole series of blocks (header, data and EOT blocks).

Not used: This Byte is not used and will be ignored in mode 0/2/8.

Fast\_Prog: Indication Byte to enter Fast LIN BSL<sup>2)</sup>

- 01<sub>H</sub>: Enter Fast LIN BSL

- Other values: Ignored. Fast LIN BSL is not entered.

Note: The programming of NVM in mode 2 will be started after 128 Bytes or EOT are received. All Bytes sent during the program operation will be lost.

When this Command frame (header block) is used for entering Fast LIN BSL, no other Master Request Header and Command frames (for data block or EOT block) should be sent. Instead, the microcontroller expects a Slave Response Header frame and sends a Response frame to Acknowledge receiving correct header block to enter Fast LIN BSL where UART BSL protocol is used. See Section 4.6

On successful receipt of the header block, the microcontroller enters mode 0/2/8, whereby the program code is transmitted from the host to the microcontroller by data block and EOT block, which are described below.

<sup>&</sup>lt;sup>1)</sup> NVM address should be aligned to the Page address (low Byte of the start address equal to 00<sub>H</sub> or 80<sub>H</sub>). If the data starts in a non-page address, PC host should fill up the beginning vacancies with 00<sub>H</sub> and provide the start address of that page address.

<sup>&</sup>lt;sup>2)</sup> In the case NVM is protected, entry to FastLIN BSL is not possible.

### The data block

|                 |                                                 | Data Area ( 6 bytes)      |                      |

|-----------------|-------------------------------------------------|---------------------------|----------------------|

| NAD<br>(1 byte) | <b>01<sub>н</sub></b><br>(Data Block<br>1 byte) | Program Code<br>(6 bytes) | Checksum<br>(1 byte) |

Data area Description:

Program Code: The program code has a fixed length of 6 Bytes per data block.

### The EOT block

| NAD<br>(1 byte) | <b>02</b> н<br>(EOT Block<br>1 byte) | Last_Code<br>length<br>(1 byte) |  | Not Used<br>( 6-1-Last_Codelength<br>bytes) | Checksum<br>(1 byte) |

|-----------------|--------------------------------------|---------------------------------|--|---------------------------------------------|----------------------|

Data area Description:

Last\_Codelength: This Byte indicates the length of the program code in this EOT block.

Program Code: The last program code (valid data) to be sent to the microcontroller.

**Not used**: The length is (6 - 1 - Last\_Codelength). These Bytes are not used and they can be set to any value.

Note:

- 1. NVM programming needs to be performed in multiples of page, 1 page is 128 Bytes. Host is expected to introduce a delay of 15 ms after 128 Bytes of program code are sent. Refer to example given below on mode 2 downloading.

- 2. To prevent external access, once the NVM is protected, modes 0, 2 and 8 are not accessible.

### Table 4-4 Example for 200 Bytes downloading using mode 0/8 and mode 2

|                                                           | ···· J··· J ···· · · · · · · ·                            |

|-----------------------------------------------------------|-----------------------------------------------------------|

| Mode 0/8 - (XRAM download)                                | Mode 2 - (NVM download)                                   |

| Send Master Request Header                                | Send Master Request Header                                |

| Send header block                                         | Send header block                                         |

| <ul> <li>No of data blocks used = 33</li> </ul>           | <ul> <li>No of data blocks used = 21</li> </ul>           |

| <ul> <li>Start address (e.g. F000<sub>H</sub>)</li> </ul> | <ul> <li>Start address (e.g. 0100<sub>H</sub>)</li> </ul> |

| Delay                                                     | Delay                                                     |

| Send Slave Response Header                                | Send Slave Response Header                                |

| Check for Acknowledge                                     | Check for Acknowledge                                     |

| Send 33 times (Master Request Header +                    | Send 21 times (Master Request Header +                    |

| data blocks)                                              | data blocks)                                              |

| (Delay after each data block required)                    | (Delay after each data block required)                    |

| Send Master Request Header                                | Send Master Request Header                                |

| Send EOT block                                            | Send EOT Block                                            |

| <ul> <li>Last_Codelength = 2</li> </ul>                   | <ul> <li>Last_Codelength = 2</li> </ul>                   |

| Delay                                                     | Delay                                                     |

| Send Slave Response Header                                | Send Slave Response Header                                |

| Check for Acknowledge                                     | Check for Acknowledge                                     |

|                                                           | Send Master Request Header                                |

|                                                           | Send header block                                         |

|                                                           | <ul> <li>No of data blocks used = 12</li> </ul>           |

|                                                           | <ul> <li>Start address (e.g. 0180<sub>H</sub>)</li> </ul> |

|                                                           | Delay                                                     |

|                                                           | Send Slave Response Header                                |

|                                                           | Check for Acknowledge                                     |

|                                                           | Send 12 times (Master Request Header +                    |

|                                                           | data blocks)                                              |

|                                                           | (Delay after each data block required)                    |

|                                                           | Send Master Request Header                                |

|                                                           | Send EOT block                                            |

|                                                           | <ul> <li>Last_Codelength = 0</li> </ul>                   |

|                                                           | Delay                                                     |

|                                                           | Send Slave Response Header                                |

|                                                           | Check for Acknowledge                                     |

|                                                           |                                                           |

#### 33 blocks \* 6 Bytes + 2 Bytes = 200 Bytes

### 4.4.4.3 The activation of working mode 1, 3 and 9

Mode 1, 3 and 9 are used to trigger execution of a user program by the microcontroller. Mode 1 and 9 trigger execution of user program in XRAM at address  $F000_{\text{H}}$ . Mode 3 triggers execution of user program in NVM at address  $0000_{\text{H}}$ . The header block for this working mode has the following structure:

#### The header block

| NAD      | 00 <sub>H</sub> | 01 <sub>H</sub> /03 <sub>H</sub> /09 <sub>H</sub> | Mode Data          | Checksum |

|----------|-----------------|---------------------------------------------------|--------------------|----------|

| (1 byte) | (Header Block)  | (Mode 1/3/9)                                      | Not Used (5 bytes) | (1 byte) |

Mode Data Description:

Not used: The five Bytes are not used and will be ignored in mode 1/3/9.

For modes 1, 3 and 9, the header block is the only transfer block to be sent by the host followed by a Slave Response Header. The microcontroller will send a response block (Acknowledgement code,  $55_{\rm H}$ ), exit the LIN BSL and jump to the XRAM address at F000<sub>H</sub> (mode 1 and mode 9) or jump to NVM address at 0000<sub>H</sub> (mode 3) respectively.

Note: For mode 3, jump to NVM will only occur either (1) when NVM is not protected and NVM content at  $0000_{\rm H}$  is not FF<sub>H</sub>; or (2) when NVM is protected. In all other cases, firmware will put the device in sleep mode.

### 4.4.4.4 The activation of working mode 4

Mode 4 is used to erase the NVM. 3 different options are supported:

- Option 00<sub>H</sub>: Page Erase

- Option 40<sub>H</sub>: Sector Erase

- Option C0<sub>H</sub>: Mass Erase

The header block for Option =  $00_{H}$  has the following structure:

#### The header block for page erase (Option = 00<sub>H</sub>)

|                 |                                            |                                   |                                 | Mode                            | e Data (5 b            | oytes)                  |                                                |                      |

|-----------------|--------------------------------------------|-----------------------------------|---------------------------------|---------------------------------|------------------------|-------------------------|------------------------------------------------|----------------------|

| NAD<br>(1 byte) | <b>00<sub>н</sub></b><br>(Header<br>Block) | <b>04<sub>H</sub></b><br>(Mode 4) | Addr<br>High<br>byte<br>(1byte) | Addr<br>Low<br>byte<br>(1 byte) | Not<br>Used<br>(1byte) | Not<br>Used<br>(1 byte) | <b>Option</b><br>= 00 <sub>H</sub><br>(1 byte) | Checksum<br>(1 byte) |

Mode Data Description:

Start Addr High, Low: 16-bit address of the NVM page to be erased.

Not used: This Byte is not used and will be ignored in mode 4.

**Option**: set to 00<sub>H</sub> to enable page erase.

When the Option Byte is  $00_{H}$ , the NVM page selected by the address provided in the Mode Data field is erased. The address should be aligned with the beginning of the chosen page.

### The header block for sector erase (Option = $40_{H}$ )

The header block for Option =  $40_{H}$  has the following structure:

|                 |                                            |                                   |                                  | Mode Data (5 bytes)             |                         |                         |                                                |                      |

|-----------------|--------------------------------------------|-----------------------------------|----------------------------------|---------------------------------|-------------------------|-------------------------|------------------------------------------------|----------------------|

| NAD<br>(1 byte) | <b>00<sub>н</sub></b><br>(Header<br>Block) | <b>04<sub>H</sub></b><br>(Mode 4) | Addr<br>High<br>byte<br>(1 byte) | Addr<br>Low<br>byte<br>(1 byte) | Not<br>Used<br>(1 byte) | Not<br>Used<br>(1 byte) | <b>Option</b><br>= 40 <sub>H</sub><br>(1 byte) | Checksum<br>(1 byte) |

Mode Data Description:

Start Addr High, Low: 16-bit address of the NVM sector to be erased.

Not used: This Byte is not used and will be ignored in mode 4.

**Option**: set to 40<sub>H</sub> to enable sector erase.

When the Option Byte =  $40_{\text{H}}$ , the NVM sector selected by the address provided in the Mode Data field is erased. The address should be aligned with the beginning of the chosen sector.

### The Header for mass erase (Option = C0<sub>H</sub>)

The header block for Option =  $C0_H$  has the following structure:

|                 |                                            |                         | Mode Data (5 bytes)   |                                         |                      |

|-----------------|--------------------------------------------|-------------------------|-----------------------|-----------------------------------------|----------------------|

| NAD<br>(1 byte) | <b>00<sub>н</sub></b><br>(Header<br>Block) | <b>04</b> н<br>(Mode 4) | Not Used<br>(4 bytes) | Option<br>= C0 <sub>H</sub><br>(1 byte) | Checksum<br>(1 byte) |

Mode Data Description:

Not used: This Byte is not used and will be ignored in mode 4.

**Option**: set to C0<sub>H</sub> to enable mass erase.

When the Option Byte =  $CO_H$ , mass erase on all the sectors in the NVM unit is performed.

Note: Not Used Bytes should be set to 0.

Note: When NVM is protected, mode 4 is not accessible and so NVM cannot be erased.

### 4.4.4.5 The activation of working mode 6

Mode 6 is used to enable or disable the NVM protection mode (read and write protection of the Linearly and Non-Linearly mapped sectors) via the given user-password. The header block for this working mode has the following structure:

#### The header block

| ſ |                 | 00 <sub>H</sub>   | 00                                | Mode                      | Chackeum              |          |

|---|-----------------|-------------------|-----------------------------------|---------------------------|-----------------------|----------|

|   | NAD<br>(1 byte) | (Header<br>Block) | <b>06<sub>н</sub></b><br>(Mode 6) | User-password<br>(1 byte) | Not Used<br>(4 bytes) | (1 byte) |

Mode Data Description

User-password: This Byte is given by user to enable or disable NVM protection mode.

Not used: The four Bytes are not used and will be ignored in mode 6.

In mode 6, the header block is the only transfer block to be sent by the host. If device is unprotected, the provided user-password will be set as NVM\_PASSWORD and internally stored. No further commands will be accepted until a power up or hardware reset. Afterwards, protection mode will be enabled.

However, if the NVM is already protected, the microcontroller will deactivate the Protection and erase the NVM if the user-password Byte matches the stored NVM\_PASSWORD Byte. If MSB of the NVM\_PASSWORD is 0, only NVM Linearly mapped sectors are erased. If the Bit is 1, both NVM Linearly and Non-linearly mapped regions are erased. No further commands will be accepted until a power up or hardware reset. Afterwards, protection mode will be disabled.

In case NVM is protected and the given user-password does not match the stored NVM\_PASSWORD, no actions will be triggered and a Protection Error Byte will be returned instead of Acknowledge.

Note:

- 1. Password value has to be different from  $00_H$  and  $FF_H$ .

- When disabling NVM protection, together with NVM, the NAC and NAD values are erased too. As a result, after next reset, default NAD will be used and chip waits for ever for the first BSL LIN frame.

### 4.4.4.6 The activation of working mode A

Mode A is used to get 4 Bytes Chip ID data, NVM page or CS page or mass NVM checksum check info depending on the Option Byte value in the header block.

Different options are supported:

- Option 00<sub>H</sub>: Get 4 Bytes Chip ID

- Option 10<sub>H</sub>: NVM page checksum check

- Option 18<sub>H</sub>: Mass NVM checksum check

- Option 50<sub>H</sub>: Configuration sector page checksum check

#### The header block - Get 4 Bytes Chip ID (Option = $00_{H}$ )

The header block for Option =  $00_{H}$  has the following structure:

|                |                      |                             | Mode Data (5 bytes)   |                                         |                      |

|----------------|----------------------|-----------------------------|-----------------------|-----------------------------------------|----------------------|

| NAD<br>(1 byte | e) (Header<br>Block) | 0A <sub>H</sub><br>(Mode A) | Not Used<br>(4 bytes) | Option<br>= 00 <sub>H</sub><br>(1 byte) | Checksum<br>(1 byte) |

Mode Data Description:

Not used: These Bytes are not used and will be ignored.

**Option**: set to 00<sub>H</sub> to enable get 4 Bytes Chip ID info.

When the Option Byte =  $00_{H}$ , the 4 Byte Chip ID Number will be returned (see **Chapter 4.5.3**).

#### The header block - NVM page checksum check (Option = $10_{H}$ )

The header block for Option =  $10_{H}$  has the following structure:

|                 |                                            |                         |                                   | Mode                             | <b>Data</b> (5 b                | oytes)                         |                                         |                      |

|-----------------|--------------------------------------------|-------------------------|-----------------------------------|----------------------------------|---------------------------------|--------------------------------|-----------------------------------------|----------------------|

| NAD<br>(1 byte) | <b>00<sub>н</sub></b><br>(Header<br>Block) | <b>0А</b> н<br>(Mode A) | Start<br>Addr<br>High<br>(1 byte) | Start<br>Addr<br>Low<br>(1 byte) | Exp<br>CHKS<br>High<br>(1 byte) | Exp<br>CHKS<br>Low<br>(1 byte) | Option<br>= 10 <sub>H</sub><br>(1 byte) | Checksum<br>(1 byte) |

Mode Data Description:

Start Addr High, Low: Address of the NVM page for checksum check. (Address should be page aligned).

Exp. CHKS High, Low: Expected checksum High/Low Byte.

**Option**: set to 10<sub>H</sub> to enable NVM page checksum check.

This option will trigger a checksum calculation (16 bits inverted XOR) over the whole page pointed by the address given in the header block and the result will then be compared with the expected checksum (provided as well by the user in the header

frame). The response frame will then return an Acknowledge followed by four data Bytes. These Bytes are, in sequential order, pass/fail indication ( $00_H$  if the calculated and expected checksum match,  $80_H$  if they differ), calculated checksum High Byte, calculated checksum Low Byte, and a final Byte equal to  $00_H$ .

The input address should always be aligned with a page. In case the provided address is not a valid NVM address, the microcontroller will return a Block Type Error ( $FF_H$ ) instead of an Acknowledge (55<sub>H</sub>) followed by no further Bytes.

#### The header block - Mass NVM checksum check (Option = $18_{H}$ )

The header block for Option =  $18_{H}$  has the following structure:

|                 |                                  |                         |                         | Mode                    | e Data (5 b                     | oytes)                         |                                         |                      |

|-----------------|----------------------------------|-------------------------|-------------------------|-------------------------|---------------------------------|--------------------------------|-----------------------------------------|----------------------|

| NAD<br>(1 byte) | <b>00</b> н<br>(Header<br>Block) | <b>0А</b> н<br>(Mode A) | Not<br>Used<br>(1 byte) | Not<br>Used<br>(1 byte) | Exp<br>CHKS<br>High<br>(1 byte) | Exp<br>CHKS<br>Low<br>(1 byte) | Option<br>= 18 <sub>H</sub><br>(1 byte) | Checksum<br>(1 byte) |

Mode Data Description:

Not used: These Bytes are not used and will be ignored.

Exp. CHKS High, Low: Expected checksum High/Low Byte.

**Option**: set to 18<sub>H</sub> to enable Mass NVM checksum check.

Checksum (16 Bits inverted XOR) on the whole linearly and non-linearly mapped sectors (configuration sector pages not included) is calculated and then compared with the expected values (provided as well as an input). The response frame will then give back a pass or fail indication plus the calculated checksum.

#### The header block - Configuration sector page checksum check (Option = 50<sub>H</sub>)

The header block for Option =  $50_{H}$  has the following structure:

|                 |                                            |                         |                        | Mode                    | <b>Data</b> (5 b                | oytes)                          |                                         |                      |

|-----------------|--------------------------------------------|-------------------------|------------------------|-------------------------|---------------------------------|---------------------------------|-----------------------------------------|----------------------|

| NAD<br>(1 byte) | <b>00<sub>н</sub></b><br>(Header<br>Block) | <b>0А</b> н<br>(Mode A) | CS<br>Page<br>(1 byte) | Not<br>Used<br>(1 byte) | Exp<br>CHKS<br>High<br>(1 byte) | Exp<br>CKSum<br>Low<br>(1 byte) | Option<br>= 50 <sub>H</sub><br>(1 byte) | Checksum<br>(1 byte) |

Mode Data Description:

**CS Page:** Selection of the CS Page to be checked (refer to **Figure 6-1**).

Not used: This Byte is not used and will be ignored.

Exp. CHKS High, Low: Expected checksum High/Low Byte.

**Option**: set to  $50_{\text{H}}$  to enable configuration sector page checksum check.

Checksum (16 Bits inverted XOR) on the selected configuration sector page is calculated and then compared with the expected values (provided as well as an input). The response frame will then give back a pass or fail indication plus the calculated checksum. In case the provided CS address is not valid, the microcontroller will return a Block Type Error (FF<sub>H</sub>) followed by no further Bytes.

For mode A, the header block is the only transfer block to be sent by the host followed by a Slave Response Header. In case of valid header block, the microcontroller will send a response block (Acknowledgement code,  $55_H$ ) followed by the 4 Bytes data. The response for mode A is described in **Section 4.5.3**.

### 4.5 Phase III: Response protocol to the host

The microcontroller status is sent to the host only when a Slave Response Header frame is received. The microcontroller status is always sent in a transfer block of 9 Bytes.

A typical transfer block consists of four parts:

| NAD      | Response | Response Data | Checksum |

|----------|----------|---------------|----------|

| (1 byte) | (1 byte) | (6 bytes)     | (1 byte) |

- NAD: Node Address for Diagnostic, specifies the address of the active slave node.

- Response: Response code indicating Acknowledge or Error status. See Table 4-7.

- Response Data: These 6 Bytes are generally not used and set to 00<sub>H</sub>. An exception is mode A response which is described in detail in Section 4.5.3.

- **Checksum**: The checksum is calculated based on NAD, Response and Response Data Bytes. All responses sent by microcontroller will adopt classic checksum. See **Section 4.4.3.1**.

### 4.5.1 Acknowledgement response

The Acknowledge response code  $(55_{\rm H})$  is sent by microcontroller to host to indicate that a block has been successfully received.

### 4.5.2 Error response

There are 3 error responses indicated by microcontroller.

### 4.5.2.1 Block Type Error (FF<sub>H</sub>)

This error can occur in the following conditions.

- 1. A Block Type other than the implemented ones was received. See Table 4-2.

- 2. An incorrect sequence of transfer blocks was received. For example, in mode 0 operation upon receiving a header block, a slave response request is expected. However, if another header block is received, this will result in a Block Type Error.

### 4.5.2.2 Checksum Error (FE<sub>H</sub>)

This error occurs when the checksum comparison fails. Microcontroller will reject the transfer block by sending back a Checksum Error code ( $FE_H$ ) to the host.

### 4.5.2.3 Protection Error (FD<sub>H</sub>)

This error occurs when selected NVM sectors, for programming or erasing, are protected. As the selected NVM sectors are protected, no programming or erasing is allowed. In this special error case, the LIN routine will abort current command and wait for the next header block from the host again.

#### 4.5.2.4 Response overview

**Table 4-5** shows a tabulated summary of the possible responses the device may transmit following the reception of a header, data or EOT block.

| Mode    | Header block                                                          | Data block                                          | EOT block                                           |

|---------|-----------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|

| 0, 2, 8 | Acknowledge, Block Type<br>Error, Checksum Error,<br>Protection Error | Acknowledge, Block<br>Type Error, Checksum<br>Error | Acknowledge, Block<br>Type Error,<br>Checksum Error |

| 1, 3, 9 | Acknowledge, Block Type<br>Error, Checksum Error                      |                                                     |                                                     |

| 4, 6    | Acknowledge, Block Type<br>Error, Checksum Error,<br>Protection Error |                                                     |                                                     |