### Laboratorio di Architetture e Programmazione dei Sistemi Elettronici Industriali

Prof. Luca Benini <luca.benini@unibo.it>

Simone Benatti <simone.benatti@unibo.it>

Filippo Casamassima<filippo.casamassima@unibo.it>

### #1 USART

## USART

- **USART** (Universal Synchronous-Asynchronous Receiver/Transmitter)

- The USART is the most used serial communication interface (eg. PC RS232 interface, IC communication interface, BT and WiFi module interface)

#### FEATURES:

- Full duplex, asynchronous communications

- Fractional baud rate generator systems

- A common programmable transmit and receive baud rates up to 4.5 MBits/s

- Programmable data word length (8 or 9 bits)

- Configurable stop bits support for 1 or 2 stop bits

- Transmitter clock output for synchronous transmission

- Single wire half duplex communication

- Configurable multibuffer communication using DMA (direct memory access)

- Buffering of received/transmitted bytes in reserved SRAM using centralized DMA

- Separate enable bits for Transmitter and Receiver

#### FLAGS:

- Receive buffer full

- Transmit buffer empty

- End of Transmission flags

- Parity control:

- Transmits parity bit

- Checks parity of received data byte

- Four error detection flags:

- Overrun error

- Noise error

- Frame error

- Parity error

- Ten interrupt sources with flags:

- CTS changes

- Transmit data register empty

- Transmission complete

- Receive data register full

- Idle line received

- Overrun error

- Framing error

- Noise error

- Parity error

- Multiprocessor communication enter into mute mode

- if address match does not occur

### USART

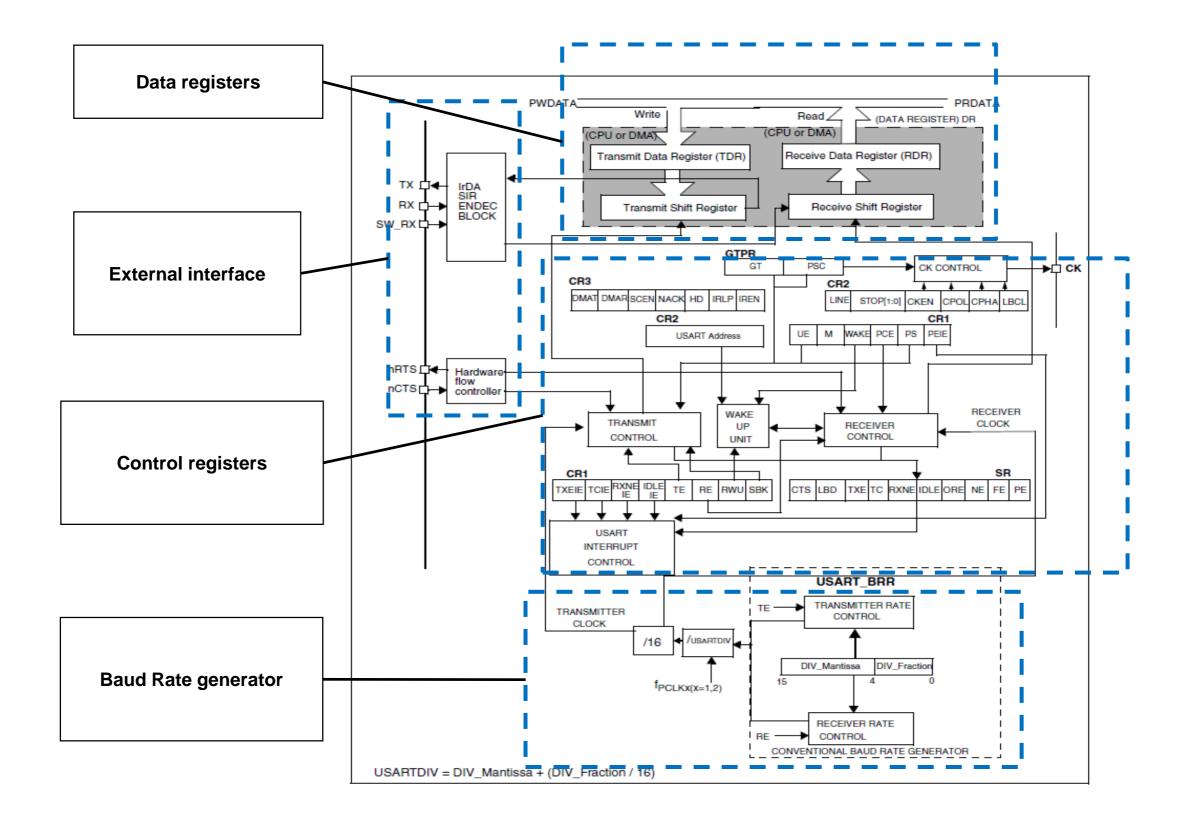

## USART Tx/Rx

#### <u>Transmitter</u>

The transmitter can send data words of either 8 or 9 bits depending on the M bit status.

When the transmit enable bit (TE) is set, the data in the transmit shift register is output on the TX pin and the corresponding clock pulses are output on the CK pin.

#### **Character transmission**

During a USART transmission, data shifts out least significant bit first on the TX pin. In this mode, the USART\_DR register consists of a buffer (TDR) between the internal bus and the transmit shift register

Every character is preceded by a start bit which is a logic level low for one bit period. The character is terminated by a configurable number of stop bits. The following stop bits are supported by USART: 0.5, 1, 1.5 and 2 stop bits.

Note:

1 The TE bit should not be reset during transmission of data. Resetting the TE bit during the

transmission will corrupt the data on the TX pin as the baud rate counters will get frozen.

The current data being transmitted will be lost.

2 An idle frame will be sent after the TE bit is enabled.

#### **Receiver**

The USART can receive data words of either 8 or 9 bits depending on the M bit in the USART\_CR1 register.

#### **Character reception**

During a USART reception, data shifts in least significant bit first through the RX pin. In this mode, the USART\_DR register consists of a buffer (RDR) between the internal bus and the received shift register.

### USART block diagram

# **USART** registers

|                    | Offset | Register    | 31<br>30<br>229<br>228<br>228<br>228<br>228<br>225<br>225<br>221<br>220<br>2119<br>117<br>117 | 9 10 12 13 14<br>9 10 12 12 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8 2 9                    | 0 <del>1</del> 0 <del>7</del> 0 <del>7</del> 0 |                                                                                                                       |

|--------------------|--------|-------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Status register    | 0x00   | USART_SR    | Reserved                                                                                      | CTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | LBD<br>TXE<br>TC         | RXNE<br>IDLE<br>ORE<br>NE<br>FE<br>PE          |                                                                                                                       |

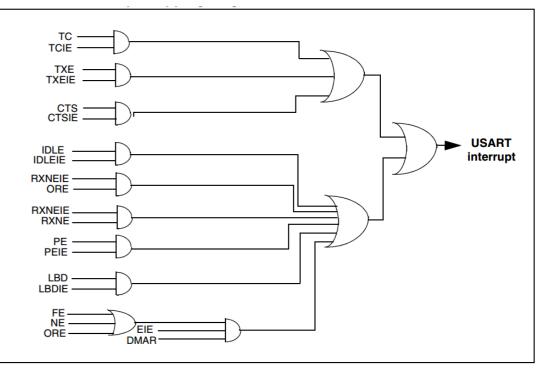

|                    |        | Reset value |                                                                                               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0 1 1                    | 0 0 0 0 0 0                                    | The USART interrupt events are connected to the Same                                                                  |

| Data register      | 0x04   | USART_DR    | Reserved                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                          | DR[8:0]                                        | interrupt routine                                                                                                     |

|                    |        | Reset value |                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0 0 0                    | 0 0 0 0 0 0                                    |                                                                                                                       |

| Baud Rate register | 0x08   | USART_BRR   | Reserved                                                                                      | DIV_Mantissa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | [15:4]                   | DIV_Fraction<br>[3:0]                          | <ul> <li>During transmission: Transmission Complete, Clear to Send or<br/>Transmit Data Register</li> </ul>           |

|                    |        | Reset value |                                                                                               | 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0 0 0                    | 0 0 0 0 0 0                                    | empty interrupt.                                                                                                      |

| Control register 1 | 0x0C   | USART_CR1   | Reserved                                                                                      | DE NAKE UE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | TXEIE<br>TCIE            | RXNEIE<br>IDLEIE<br>TE<br>RE<br>RWU<br>SBK     | While receiving: Idle Line detection, Overrun error, Receive                                                          |

|                    |        | Reset value |                                                                                               | 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0 0 0                    | 0 0 0 0 0 0                                    | •                                                                                                                     |

| Control register 2 | 0x10   | USART_CR2   | Reserved                                                                                      | STOP LINE<br>LINE<br>STOP LINE<br>STOP LINE<br>S | LBCL<br>sserved<br>LBDIE | ADD[3:0]                                       | Data register not empty,<br>Parity error, LIN break detection, Noise Flag (only in multi buffer                       |

|                    |        | Reset value |                                                                                               | 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0 🛱 0                    | 0 0 0 0 0                                      | communication) and                                                                                                    |

| Control register 3 | 0x14   | USART_CR3   | Reserved                                                                                      | CTSIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RTSE<br>DMAT<br>DMAR     | SCEN<br>NACK<br>HDSEL<br>IRLP<br>IREN<br>EIE   | Framing Error (only in multi buffer communication).<br>These events generate an interrupt if the corresponding Enable |

|                    |        | Reset value |                                                                                               | 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0 0 0                    | 0 0 0 0 0 0                                    | Control Bit is set.                                                                                                   |

| Prescaler register | 0x18   | USART_GTPR  | Reserved                                                                                      | GT[7:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                          | PSC[7:0]                                       |                                                                                                                       |

|                    |        | Reset value |                                                                                               | 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0 0 0                    | 0 0 0 0 0 0                                    |                                                                                                                       |

| Interrupt event                                                             | Event flag      | Enable<br>Control bit |  |

|-----------------------------------------------------------------------------|-----------------|-----------------------|--|

| Transmit data register empty                                                | TXE             | TXEIE                 |  |

| CTS flag                                                                    | CTS             | CTSIE                 |  |

| Transmission complete                                                       | TC              | TCIE                  |  |

| Received data ready to be read                                              | RXNE            | RXNEIE                |  |

| Overrun error detected                                                      | ORE             |                       |  |

| Idle line detected                                                          | IDLE            | IDLEIE                |  |

| Parity error                                                                | PE              | PEIE                  |  |

| Break flag                                                                  | LBD             | LBDIE                 |  |

| Noise flag, Overrun error and Framing error in multibuffer<br>communication | NE or ORE or FE | EIE <sup>(1)</sup>    |  |

# USART

#### **Procedure:**

- 1. Enable the USART by writing the UE bit in USART\_CR1 register to 1.

- 2. Program the M bit in USART\_CR1 to define the word length.

- 3. Program the number of stop bits in USART\_CR2.

**4**. Select DMA enable (DMAT) in USART\_CR3 if Multi buffer Communication is to take place. Configure the DMA register as explained in multibuffer communication.

- 5. Select the desired baud rate using the USART\_BRR register.

- 6. Set the TE bit in USART\_CR1 to send an idle frame as first transmission.

7. Write the data to send in the USART\_DR register (this clears the TXE bit). Repeat this for each data to be transmitted in case of single buffer.

8. After writing the last data into the USART\_DR register, wait until TC=1. This indicates that the transmission of the last frame is complete. This is required for instance when the USART is disabled or enters the Halt mode to avoid corrupting the last transmission.

#### Single byte communication

The TXE bit is always cleared by a write to the data register. The TXE bit is set by hardware and it indicates:

- The data has been moved from TDR to the shift register and the data transmission has started.

- The TDR register is empty.

• The next data can be written in the USART\_DR register without overwriting the previous data.

This flag generates an interrupt if the TXEIE bit is set.

### RX

#### **Procedure:**

- 1. Enable the USART by writing the UE bit in USART\_CR1 register to 1.

- 2. Program the M bit in USART\_CR1 to define the word length.

- 3. Program the number of stop bits in USART\_CR2.

**4**. Select DMA enable (DMAR) in USART\_CR3 if multibuffer communication is to take place. Configure the DMA register as explained in multibuffer communication.

5. Select the desired baud rate using the baud rate register USART\_BRR

6. Set the RE bit USART\_CR1. This enables the receiver which begins searching for a start bit

#### Single byte communication

• The RXNE bit is set. It indicates that the content of the shift register is transferred to the

RDR. In other words, data has been received and can be read (as well as its associated error flags).

- An interrupt is generated if the RXNEIE bit is set.

- The error flags can be set if a frame error, noise or an overrun error has been detected during reception.

• In multibuffer, RXNE is set after every byte received and is cleared by the DMA read to he Data Register.

• In single buffer mode, clearing the RXNE bit is performed by a software read to the USART\_DR register. The RXNE flag can also be cleared by writing a zero to it. The RXNE bit must be

## USART (what)

• I want to use an USART. What do I need to know?

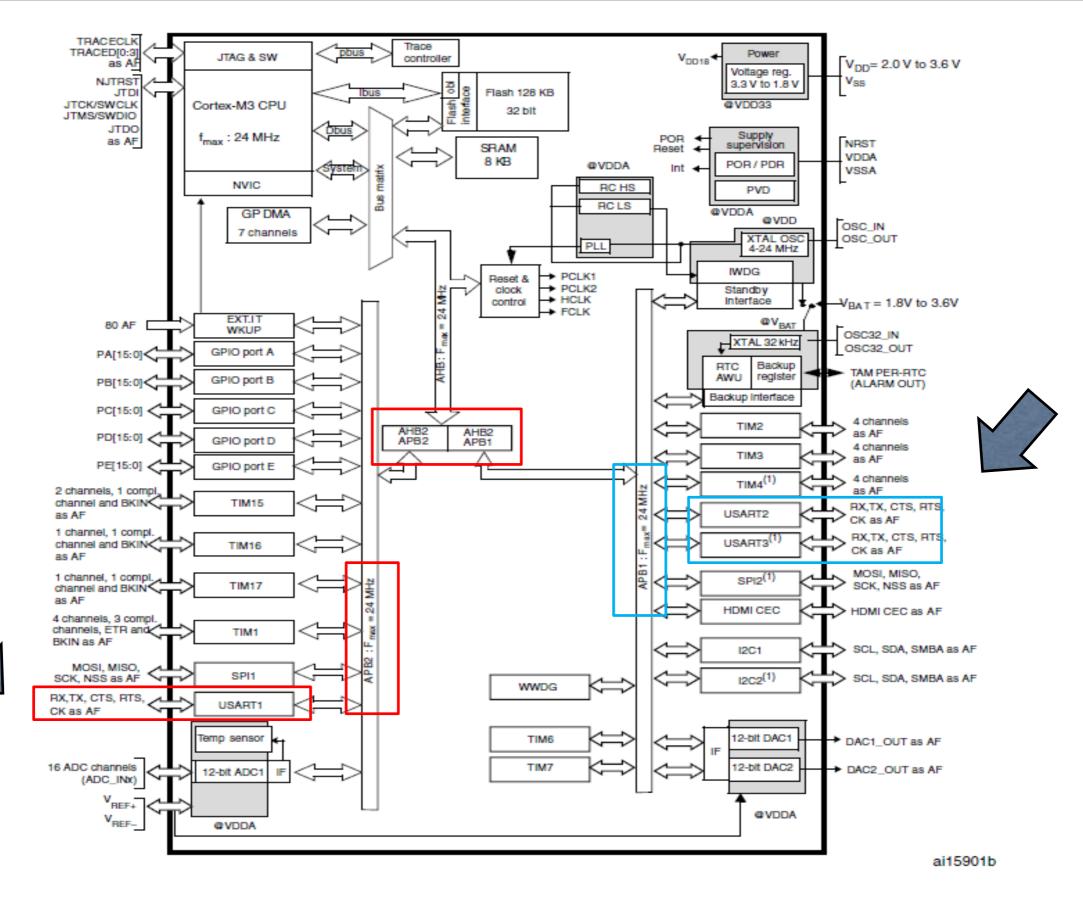

### Which bus USARTx are connected to?

$\rightarrow$  Look at the architecture diagram

### Which port are we going to use?

→ Look at the development board documentation

### What do I need to do with this USART? (input, output, ...)

→ Configure for 38400 / 8 N 1 (google this if you want to know more about the configurations)

## USART (where)

- I want to use an USART. Where can I gather these information?

- → The **datasheet** contains all the information we need

- → Look at the UM0919 User Manual

https://www1.elfa.se/data1/wwwroot/assets/datasheets/STM32\_discovery\_eng\_manual.pdf

### USART (code)

#### main.c

#include "stm32F10x.h"

#include "STM32vldiscovery.h"

//#include "stm32f10x\_exti.h"

#include "misc.h"

#include "stm32f10x\_gpio.h "

#include "stm32f10x\_usart.h"

#include <stdio.h>

typedef enum { FAILED = 0, PASSED = !FAILED} TestStatus;

/\* Private define -----\*/ #define RxBufferSize1 128 /\* Private macro -----\*/ #define countof(a) (sizeof(a) / sizeof(\*(a))) #define PUTCHAR\_PROTOTYPE int fputc(int ch, FILE \*f)

/\* Private variables -----\*/

uint8\_t RxBuffer1[RxBufferSize1]; \_\_IO uint8\_t RxCounter1 = 0x00; uint8\_t NbrOfDataToRead1 = RxBufferSize1; char c = 'r'; char received\_ch; /\* Private function prototypes ------\*/

void RCC\_Configuration(void); void GPIO\_Configuration(void); void NVIC\_Configuration(void); void USART\_Configuration(void); Function and variables prototypes

. . .

## USART(code)

/\* Private functions ----void RCC\_Configuration(void) /\* Enable GPIO clock \*/ RCC APB2PeriphClockCmd(RCC APB2Periph GPIOA | RCC APB2Periph AFIO, ENABLE); RCC\_APB2PeriphClockCmd(RCC\_APB2Periph\_USART1, ENABLE); void GPIO\_Configuration(void) GPIO\_InitTypeDef GPIO\_InitStructure; /\* Configure USARTy Rx as input floating \*/ GPIO InitStructure.GPIO Pin = GPIO Pin 10; GPIO\_InitStructure.GPIO\_Mode = GPIO\_Mode\_IN\_FLOATING; GPIO\_Init(GPIOA, &GPIO\_InitStructure); /\* Configure USARTy Tx as alternate function push-pull \*/ **INIT** functions GPIO\_InitStructure.GPIO\_Pin = GPIO\_Pin\_9; GPIO\_InitStructure.GPIO\_Speed = GPIO\_Speed\_50MHz; GPIO InitStructure.GPIO Mode = GPIO Mode AF PP; GPIO Init(GPIOA, &GPIO InitStructure); } void NVIC\_Configuration(void) NVIC InitTypeDef NVIC InitStructure; /\* Configure the NVIC Preemption Priority Bits \*/ NVIC\_PriorityGroupConfig(NVIC\_PriorityGroup\_0); /\* Enable the USARTy Interrupt \*/ NVIC\_InitStructure.NVIC\_IRQChannel = USART1\_IRQn; NVIC InitStructure.NVIC IRQChannelSubPriority = 0; NVIC\_InitStructure.NVIC\_IRQChannelCmd = ENABLE; NVIC\_Init(&NVIC\_InitStructure); }

## USART (code)

Interrupt enable (use in later exercise)

void USART\_Configuration(void)

USART\_InitTypeDef USART\_InitStructure; USART\_InitStructure.USART\_BaudRate = 9600; USART InitStructure.USART WordLength = USART WordLength 8b; USART\_InitStructure.USART\_StopBits = USART\_StopBits\_1; USART\_InitStructure.USART\_Parity = USART\_Parity\_No; USART\_InitStructure.USART\_HardwareFlowControl = USART\_HardwareFlowControl\_None; USART\_InitStructure.USART\_Mode = USART\_Mode\_Rx | USART\_Mode\_Tx;

/\* Configure USARTy \*/ USART\_Init(USART1, &USART\_InitStructure);

/\* Enable USARTy Receive and Transmit interrupts \*/ //USART\_ITConfig(USART1, USART\_IT\_RXNE, ENABLE); //USART\_ITConfig(USART1, USART\_IT\_TXE, ENABLE);

/\* Enable the USARTy \*/ USART\_Cmd(USART1, ENABLE);

}

int main(void) RCC\_Configuration(); NVIC\_Configuration(); GPIO\_Configuration(); USART\_Configuration(); USART\_SendData(USART1,c); Sending the character while(USART\_GetFlagStatus(USART1,USART\_FLAG\_TC) == RESET); while (1) { if (USART\_GetFlagStatus(USART1 , USART\_FLAG\_RXNE) != RESET) received\_ch = USART\_ReceiveData(USART1); Receiving the character received\_ch = received\_ch; }

### USART (code)

### stm32f10x\_it.c . . . void USART1\_IRQHandler(void) { if(USART\_GetITStatus(USART1, USART\_IT\_TXE) == SET) { //write interrupt code here //Remember to disable the transmission after the tx of last char } if(USART\_GetITStatus(USART1, USART\_IT\_RXNE) != RESET) {

/\* Read one byte from the receive data register \*/

// use the function USART receive data USART\_ReceiveData(USART1);

}

## USART (exercises)

### Exercise 1

Verify the TX and the RX of the char 'r' in the USART1 of the board, by a shortcircuit between the RX and TX pin. (Check the docs to decide which pins should be connected toghether)

### **Exercise 2**

Repeat exercise 1 using the interrupt TX and RX routine (Hint: use the debugger and breakpoints) (Hint 2: implement the two interrupt separately to verify your solution)

### **Exercise 3**

Repeat exercise 1 and 2 with TX and RX of the string "#yourname" instead of the byte 'r' (Hint: try the function "sprint" for a compact solution or use a for/while loop).

**Exercise 4**

Connect two board. Send a value from board 1 to board 2. After 3 second resend the (value+1) from board 2 to board 1. After 3 second restart with (value + 2)...etc...