# KL25 Analog-to-Digital Converter 16-bit SAR

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, t he Energy Efficient Solutions logo, mobileGT, PowerQUICC, QorlQ, StarCore and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeStack, ColdFire-, CoreNet, Flexis, Kinetis, MXO, Platform in a Package, Processor Expert, OorlQ Qonverge, Oorivva, QUICC Engine, SMARTINOS, TurboLink, VortiQa and Xtrinsis are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. ©2011 Freescale Semiconductor, Inc.

- 1. ADC Features overview

- 2. External signal connections

- 3. Configuration registers

- 4. ADC Hands-On explanation

- 5. Reference material

- 1. ADC Features overview

- 2. External signal connections

- 3. Configuration registers

- 4. ADC Hands-On explanation

- 5. Reference material

Freescale, the Freescale logo, AltiVec, C-5, Code TEST, Code Warrior, ColdFire, C-Ware, the Energy Efficient Solutions logo, mobileGT, PowerQUICC, QorlQ, StarCore and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Beeklt, BeeStack, ColdFire+, CoreNet, Flexis, Kinetis, MXC, Platformin a Package, Processor Expert, QorlQ Qonverge, Qorivae, QUICC Engine, SMARTMOS, TurboLink, VortiQa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other productor service names are the property of their respective owners. © 2011 Freescale Semiconductor, Inc.

# **ADC Features overview**

- ✓ Linear successive approximation algorithm with up to 16-bit resolution

- ✓ Up to four pairs of differential and 24 single-ended external analog inputs

- ✓ Output modes:

- Differential 16-bit, 13-bit, 11-bit, and 9-bit modes, in two's complement 16-bit sign-extended format

- Single-ended 16-bit, 12-bit, 10-bit, and 8-bit modes, in right-justified unsigned format

- ✓ Single or continuous conversion

- Configurable sample time and conversion speed/power

- Conversion complete and hardware average complete flag and interrupt

- ✓ Input clock selectable from up to four sources

Freescale, the Freescale logo, AltiVec, C-5, Code TEST, Code Warrior, ColdFire, C-Ware, the Energy Efficient Solutions logo, mobileGT, PowerQUICC, QorlQ, StarCore and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat, & Tm. Off. BeeKit, BeeStack, CodeFire+, CoreNet, Flexis, Kinetis, MXC, Platformin a Package, Processor Expert, QorlQ Qonverge, Qoriva, QUICC Engine, SMARTMOS, TurboLink, VorlQa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other productor service names are the property of their respective owners. © 2011 Freescale Semiconductor, Inc.

# **ADC Features overview (cont.)**

- Operation in low power modes for lower noise operation

- Asynchronous clock source for lower noise operation with option to output the clock

- Selectable asynchronous hardware conversion trigger with hardware channel select

- ✓ Automatic compare with interrupt for various programmable values

- ✓ Temperature sensor

- ✓ Hardware average function

- ✓ Selectable voltage reference

- ✓ Self-calibration mode

Freescale, the Freescale logo, AttiVec, C-5, Code/TEST, Code/Warrior, Cold/Fire, C-Ware, the Energy Efficient Solutions logo, mobileGT, PowerQUICC, QorlQ, StarCore and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeKit, BeeStatk, Code/Fire, CoreNet, Flexis, Kinetis, MXC, Platformin a Package, Processor Expert, QorlQ Qonverge, Qorivva, QUICC Engine, SMARTMOS, TurboLink, VortiQa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2011 Freescale Semiconductor, Inc.

1. ADC Features overview

#### 2. External signal connections

- 3. Configuration registers

- 4. ADC Hands-On explanation

- 5. Reference material

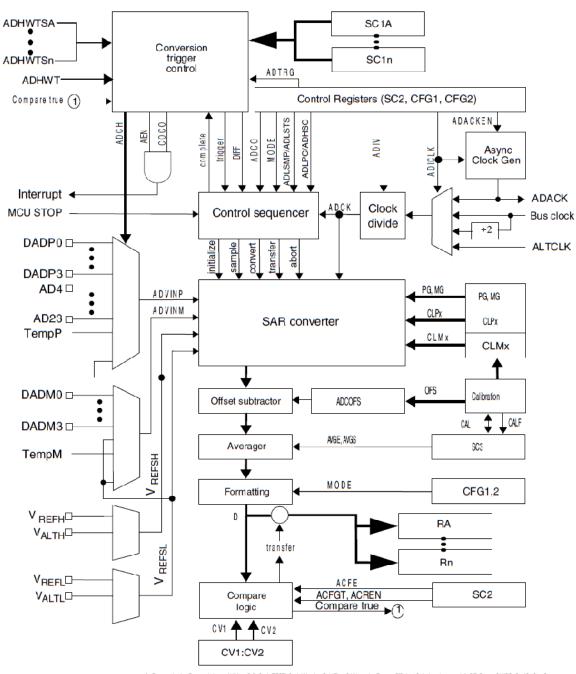

## **ADC Block Diagram**

| Signal      | Description                            |

|-------------|----------------------------------------|

| DADP3-DADP0 | Differential Analog Channel Inputs (+) |

| DADM3-DADM0 | Differential Analog Channel Inputs (-) |

| ADn         | Single-Ended Analog Channel Inputs     |

| VREFSH      | Voltage Reference Select High          |

| VREFSL      | Voltage Reference Select Low           |

| VDDA        | Analog Power Supply                    |

| VSSA        | Analog Ground                          |

Freescale, the Freescale logo, AltiVec, C-5, Code/TEST, Code/Warrior, ColdFire, C-Ware, the Energy Efficient, Solutions logo, mobileGT, PowerQUICC, QorlQ, StarCore and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S., Pat. & Tm. Off. BeeKit, BeeStack, ColdFirer, CoreNet, Flexis, Kinetis, MXC, Platformin a Package, Processor Expert, QorlQ Qonverge, Qorriva, QUICC Engine, SMARTIMOS, TurboLink, VortiQa and Xtinnsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. @2011 Freescale Semiconductor, Inc.

7

## **ADC Channel Assignment**

| ADC Channel<br>(SC1n[ADCH]) | Channel | Input signal<br>(SC1n[DIFF]= 1) | Input signal<br>(SC1n[DIFF]= 0) |

|-----------------------------|---------|---------------------------------|---------------------------------|

| 00000                       | DAD0    | ADC0_DP0 and ADC0_DM0           | ADC0_DP0/ADC0_SE0               |

| 00001                       | DAD1    | ADC0_DP1 and ADC0_DM1           | ADC0_DP1/ADC0_SE1               |

| 00010                       | DAD2    | ADC0_DP2 and ADC0_DM2           | ADC0_DP2/ADC0_SE2               |

| 00011                       | DAD3    | ADC0_DP3 and ADC0_DM3           | ADC0_DP3/ADC0_SE3               |

| 00100 <sup>1</sup>          | AD4a    | Reserved                        | ADC0_DM0/ADC0_SE4a              |

| 00101 <sup>1</sup>          | AD5a    | Reserved                        | ADC0_DM1/ADC0_SE5a              |

| 00110 <sup>1</sup>          | AD6a    | Reserved                        | ADC0_DM2/ADC0_SE6a              |

| 00111 <sup>1</sup>          | AD7a    | Reserved                        | ADC0_DM3/ADC0_SE7a              |

| 00100 <sup>1</sup>          | AD4b    | Reserved                        | ADC0_SE4b                       |

| 00101 <sup>1</sup>          | AD5b    | Reserved                        | ADC0_SE5b                       |

| 00110 <sup>1</sup>          | AD6b    | Reserved                        | ADC0_SE6b                       |

| 00111 <sup>1</sup>          | AD7b    | Reserved                        | ADC0_SE7b                       |

| 01000                       | AD8     | Reserved                        | ADC0_SE8                        |

| 01001                       | AD9     | Reserved                        | ADC0_SE9                        |

| 01010                       | AD10    | Reserved                        | Reserved                        |

| 01011                       | AD11    | Reserved                        | ADC0_SE11                       |

| 01100                       | AD12    | Reserved                        | ADC0_SE12                       |

| 01101                       | AD13    | Reserved                        | ADC0_SE13                       |

| 01110                       | AD14    | Reserved                        | ADC0_SE14                       |

| 01111                       | AD15    | Reserved                        | ADC0_SE15                       |

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFile, C-Ware, the Energy Efficient Solutions logo, mobileGT, PowerQUICC, QorlQ, StarCore and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeKit, BeeStack, ColdFile+, CoreNet, Flexis, Kinetis, MXC, Platformin a Package, Processor Expert, OorlQ Qonverge, Qorivag, QUICC Engine, SMARTIMOS, TurboLink, VortiQa and Xtinsic are trademarks of Freescale Semiconductor, Inc. All other productor service names are the property of their respective owners. © 2011 Freescale Semiconductor, Inc.

# **ADC Channel Assignment (cont.)**

| ADC Channel<br>(SC1n[ADCH]) | Channel | Input signal<br>(SC1n[DIFF]= 1) | Input signal<br>(SC1n[DIFF]= 0)  |  |  |

|-----------------------------|---------|---------------------------------|----------------------------------|--|--|

| 10000                       | AD16    | Reserved                        | Reserved                         |  |  |

| 10001                       | AD17    | Reserved                        | Reserved                         |  |  |

| 10010                       | AD18    | Reserved                        | Reserved                         |  |  |

| 10011                       | AD19    | Reserved                        | Reserved                         |  |  |

| 10100                       | AD20    | Reserved                        | Reserved                         |  |  |

| 10101                       | AD21    | Reserved                        | Reserved                         |  |  |

| 10110                       | AD22    | Reserved                        | Reserved                         |  |  |

| 10111                       | AD23    | Reserved                        | 12-bit DAC0 Output/<br>ADC0_SE23 |  |  |

| 11000                       | AD24    | Reserved                        | Reserved                         |  |  |

| 11001                       | AD25    | Reserved                        | Reserved                         |  |  |

| 11010                       | AD26    | Temperature Sensor (Diff)       | Temperature Sensor (S.E)         |  |  |

| 11011                       | AD27    | Bandgap (Diff) <sup>2</sup>     | Bandgap (S.E) <sup>2</sup>       |  |  |

| 11100                       | AD28    | Reserved                        | Reserved                         |  |  |

| 11101                       | AD29    | -VREFH (Diff)                   | VREFH (S.E)                      |  |  |

| 11110                       | AD30    | Reserved                        | VREFL                            |  |  |

| 11111                       | AD31    | Module Disabled                 | Module Disabled                  |  |  |

Freescale, the Freescale logo, AltiVec, C-5, Code TEST, CodeWarrior, ColdFire, C-Ware, the Energy Efficient Solutions logo, mobileGT, PowerQUICC, QorlQ, StarCore and Symphony are trademarks of Freescale Semiconductor, Inc., Reg, U.S. Pat. & Tm. Off. Beekit, BeeStack, ColdFire+, Coreket, Flexis, Kinetis, MXC, Platformin a Package, Processor Expert, QorlQ Qonverge, Qorivva, QUICC Engine, SMARTMOS, TurboLink, VortiQa and Xtinsic are trademarks of Freescale Semiconductor, Inc. All other productor service names are the property of their respective owners. © 2011 Freescale Semiconductor, Inc.

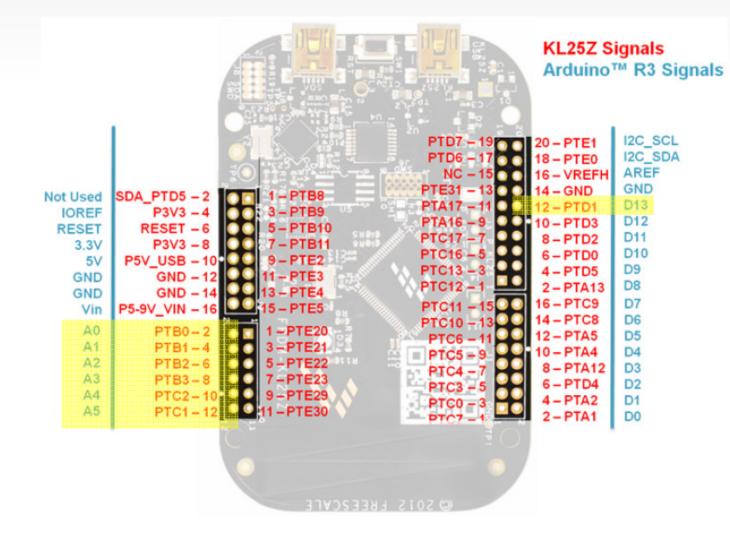

#### ADC Channels on FRDM-KL25Z board

*∳*freescale™

10

Freescale, the Freescale logo, AltiVec, C-5, Code/TEST, Code/Warrior, Cold/Fire, C-Ware, the Energy Efficient, Solutions logo, mobileGT, PowerQUICC, QorlQ, StarCore and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S., Pat. & Tm. Off. BeeKit, BeeStack, Cold/Fire+, CoreNet, Flexis, Kinetis, MXC, Platformin a Package, Processor Expert, QorlQ Qonverge, Qorivva, QUICC Engine, SMARTMOS, TurboLink, VortiQa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. @ 2011 Freescale Semiconductor, Inc.

- 1. ADC Features overview

- 2. External signal connections

## 3. Configuration registers

- 4. ADC Hands-On explanation

- 5. Reference material

Freescale, the Freescale logo, AltiVec, C-5, Code TEST, CodeWarrior, ColdFire, C-Ware, the Energy Efficient Solutions logo, mobileGT, PowerQUICC, QorlQ, StarCore and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeKit, BeeStack, ColdFire+, CoreNet, Flexis, Kinetis, MXC, Platformin a Package, Processor Expert, QorlQ Qonverge, Qorivva, QUICC Engine, SMARTMOS, TurboLink, VortiQa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other productor service names are the property of their respective owners. 6/2011 Freescale Semiconductor, Inc.

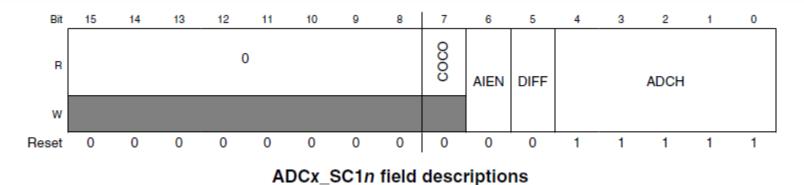

- Status and Control Registers 1

- ADC0\_SC1A, ADC0\_SC1B

- **COCO**: Conversion Complete flag, a 1 indicates when the ADC conversion has finished.

- **AIEN**: Enables the Conversion Complete interrupt when its value is 1; otherwise, interrupts will not be asserted.

- **DIFF**: If it is 0, single-ended mode is enabled. If it is 1, differential mode is enabled.

- **ADCH**: Indicates the channel that will be converted. When all bits are 1, the ADC module will be disabled.

Freescale, the Freescale logo, AttiVec, C-5, Code/TEST, Code/Warrior, ColdFire, C-Ware, the Energy Efficient Solutions logo, mobileGT, PowerQUICC, QorlQ, StarCore and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeKit, BeeStack, Code/Texe, CoreNet, Flexis, Kinetis, MXC, Platformin a Package, Processor Expert, QorlQ Qonverge, Qorivva, QUICC Engine, SMARTIMOS, TurboLink, VortiQa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. 02011 Freescale Semiconductor, Inc.

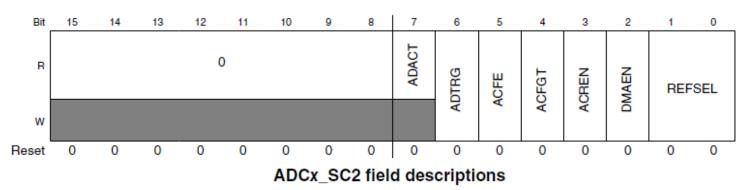

# Status and Control Register 2

ADC0\_SC2

- **ADACT**: This flag indicates that a conversion or hardware averaging is in progress.

- **ADTRG**: Selects the type of trigger used for initiating a conversion: 0 for software, 1 for hardware.

- ACFE: If it is 1, the compare function is enabled.

- **ACFGT**: Only has effect if the ACFE bit is 1. With a value of 0, configures the Less Than threshold. With a value of 1, configures the Greater Than threshold.

- ACREN: Enables the Range Comparison. If it is 0, just CV1 is compared. If it is 1, both CV1 and CV2 are compared.

- **DMAEN**: If it is 1, DMA-based conversion will be enabled.

- **REFSEL**: Selects the High and Low references: 0b00 for default reference pins (VREFH and VREFL). 0b01 for alternate pins (VALTH and VALTL). 0b10 and 0b11 are reserved.

Freescale, the Freescale logo, AltiVec, C-5, Code TEST, Code Warrior, ColdFire, C-Ware, the Energy Efficient Solutions logo, mobileGT, PowerQUICC, QorlQ, StarCore and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat, & Tm. Off. BeeKit, BeeStack, ColdFire+, CoreNet, Flexis, Kinetis, MXC, Platformin a Package, Processor Expert, QorlQ Qonverge, Qoriva, QUICC Engine, SMARTMOS, TurboLink, VortiQa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. Alt other product or service names are the property of their respective owners. @2011 Freescale Semiconductor, Inc.

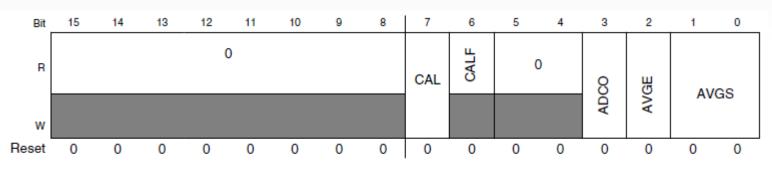

# Status and Control Register 3

ADC0\_SC3

ADCx\_SC3 field descriptions

- CAL: Begins the calibration sequence when set.

- **CALF**: If it is 0, calibration completed normally. If it is 1, calibration failed. It will fail if any ADC register is modified during calibration process.

- **ADCO**: If it is 0, single conversion is configured. If it is 1, continuous conversions are configured.

- AVGE: If it is 1, hardware average function is enabled; otherwise, average is disabled.

- **AVGS**: If AVGE bit is set, these bits select how many samples will be averaged: 0b00 for 4 samples. 0b01 for 8 samples. 0b10 for 16 samples. 0b11 for 32 samples.

Freescale, the Freescale logo, AttiVec, C-5, Code/TEST, Code/Warrior, ColdFire, C-Ware, the Energy Efficient Poslutions logo, mobileGT, PowerQUICC, QorlQ, StarCore and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeKit, BeeStack, ColdFire+, CoreNet, Flexis, Kinetis, MXC, Platformin a Package, Processor Expert, AorlQ Converge, Qoriva, QUICC Engine, SMARTMOS, Turbolink, VortiQa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2011 Freescale Semiconductor, Inc.

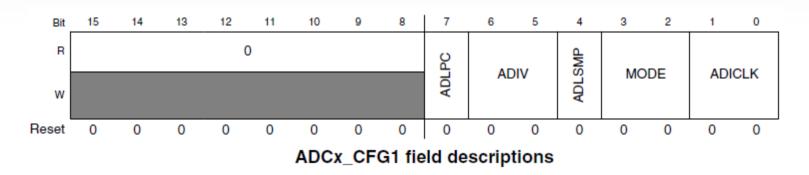

# Configuration Register 1

ADC0\_CFG1

- **ADLPC** : If it is 1, ADC low-power configuration is enabled.

- **ADIV**: Selects the divide ratio used by the ADC to generate the internal clock ADCK: 0b00 for divide by 1. 0b01 for divide by 2. 0b10 for divide by 4. 0b11 for divide by 8.

- **ADLSMP**: If it is 0, short sample time is configured. If it is 1, long sample time is configured.

- MODE: Selects the ADC resolution mode: 0b00 for 8-bit single-ended or 9-bit differential. 0b01 for for 12-bit single-ended or 13-bit differential. 0b10 for for 10-bit single-ended or 11-bit differential. 0b11 for for 16-bit single-ended or differential.

- ADICLK: Selects the input clock source to generate the ADC clock: 0b00 for Bus clock. 0b01 for Bus clock divided by 2. 0b10 for Alternate clock (ALTCLK). 0b11 for Asynchronous clock (ADACK).

Freescale, the Freescale logo, AttiVec, C-5, Code TEST, CodeWarrior, ColdFire, C-Ware, the Energy Efficient Solutions logo, mobileGT, PowerQUICC, QorlQ, StarCore and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeKit, BeeStack, ColdFire+, CoreNet, Flexis, Kinetis, MXC, Platformin a Package, Processor Expert, QorlQ Qonverge, Qorivva, QUICC Engine, SMARTMOS, TurboLink, VortiQa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other productor service names are the property of their respective owners. © 2011 Freescale Semiconductor, Inc.

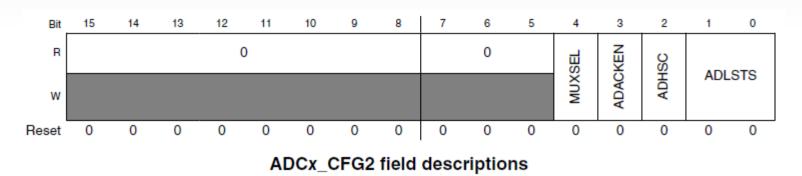

# Configuration Register 2

ADC0\_CFG2

- **MUXSEL**: Changes the ADC mux setting to select between alternate sets of ADC channels. If it is 0, ADxxa channels are selected. If it is 1, ADxxb channels are selected.

- **ADACKEN**: If it is 1, enables the asynchronous clock source and the clock source output regardless of the conversion and status of CFG1[ADICLK].

- **ADHSC**: If it is 1, High-Speed conversion sequence is selected. Otherwise, Normal conversion sequence is selected.

- ADLSTS: Selects between the extended sample times when long sample time is selected (CFG1[ADLSMP]=1). 0b00 for 20 extra cycles. 0b01 for 12 extra cycles. 0b10 for 6 extra cycles. 0b11 for 2 extra cycles.

Freescale, the Freescale logo, AltiVec, C-5, Code TEST, CodeWarrior, ColdFine, C-Ware, the Energy Efficient Solutions logo, mobileGT, PowerQUICC, QorlQ, StarCore and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat, & Tm. Off. BeeKit, BeeStack, ColdFire+, CoreNet, Flexis, Kinetis, MXC, Platformin a Package, Processor Expert, QorlQ Qonverge, Qoriva, QUICC Engine, SMARTMOS, TurboLink, VorliQa and Xitnisic are trademarks of Freescale Semiconductor, Inc. All other productor service names are the property of their respective owners.@2011 Freescale Semiconductor, Inc.

# Data Result Registers

#### • ADC0\_RA, ADC0\_RB:

Contain the result of an ADC conversion of the channel selected by the corresponding status and channel control register (SC1A:SC1n). For every status and channel control register, there is a corresponding data result register.

| Conversion<br>mode      | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Format                          |

|-------------------------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|---------------------------------|

| 16-bit differential     | S   | D   | D   | D   | D   | D   | D  | D  | D  | D  | D  | D  | D  | D  | D  | D  | Signed 2's<br>complement        |

| 16-bit single-<br>ended | D   | D   | D   | D   | D   | D   | D  | D  | D  | D  | D  | D  | D  | D  | D  | D  | Unsigned right justified        |

| 13-bit differential     | S   | S   | S   | S   | D   | D   | D  | D  | D  | D  | D  | D  | D  | D  | D  | D  | Sign-extended<br>2's complement |

| 12-bit single-<br>ended | 0   | 0   | 0   | 0   | D   | D   | D  | D  | D  | D  | D  | D  | D  | D  | D  | D  | Unsigned right-<br>justified    |

| 11-bit differential     | S   | S   | S   | S   | S   | S   | D  | D  | D  | D  | D  | D  | D  | D  | D  | D  | Sign-extended<br>2's complement |

| 10-bit single-<br>ended | 0   | 0   | 0   | 0   | 0   | 0   | D  | D  | D  | D  | D  | D  | D  | D  | D  | D  | Unsigned right-<br>justified    |

| 9-bit differential      | S   | S   | S   | S   | S   | S   | S  | S  | D  | D  | D  | D  | D  | D  | D  | D  | Sign-extended<br>2's complement |

| 8-bit single-<br>ended  | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | D  | D  | D  | D  | D  | D  | D  | D  | Unsigned right-<br>justified    |

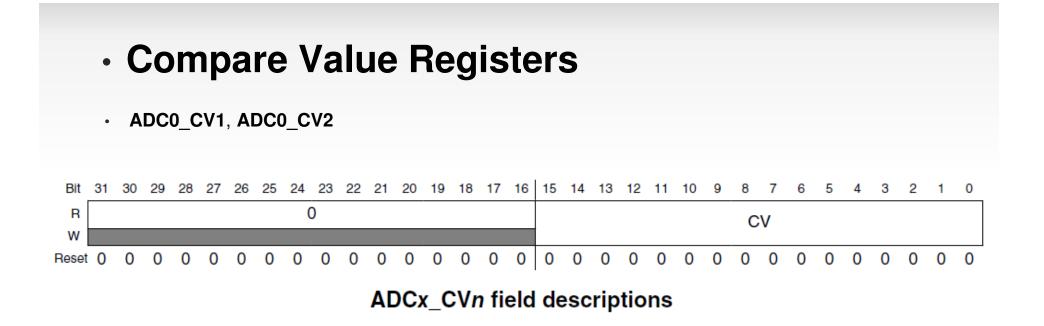

- CV: Contain a compare value used to compare the conversion result when the compare function is enabled (SC2[ACFE]=1).

- The compare value 2 register (CV2) is used only when the compare range function is enabled (SC2[ACREN]=1).

Freescale, the Freescale logo, AltiVec, C-5, Code/TEST, Code/Warrior, Cold/Fire, C-Ware, the Energy Efficient, Solutions logo, mobileGT, PowerQUICC, QorlQ, StarCore and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S., Pat. & Tm. Off. BeeKit, BeeStack, Code/Te+e, CoreNet, Flexis, Kinetis, MXC, Platformin a Package, Processor Expert, QorlQ Qonverge, Qoriva, QUICC Engine, SMARTIMOS, TurboLink, VortiQa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. @2011 Freescale Semiconductor, Inc.

- 1. ADC Features overview

- 2. External signal connections

- 3. Configuration registers

- 4. ADC Hands-On explanation

- 5. Reference material

Freescale, the Freescale logo, AlliVec, C-5, Code TEST, Code Warrior, ColdFire, C-Ware, the Energy Efficient Solutions logo, mobile GT, Power QUICC, QorlQ, StarCore and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeKit, BeeStack, ColdFire+, CoreNet, Flexis, Kinetis, MXC, Platformin a Package, Processor Expert, QorlQ Qonverge, Qorivva, QUICC Engine, SMARTMOS, TurboLink, VortiQa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other productor service names are the property of their respective owners. © 2011 Freescale Semiconductor, Inc.

# ADC Hands-On

• On this example, the ADC will be initialized to 16-bit single-ended mode for reading the 1.0V Bandgap reference voltage (channel AD27).

| 11010 | AD26 | Temperature Sensor (Diff)   | Temperature Sensor (S.E)   |

|-------|------|-----------------------------|----------------------------|

| 11011 | AD27 | Bandgap (Diff) <sup>2</sup> | Bandgap (S.E) <sup>2</sup> |

| 11100 | AD28 | Reserved                    | Reserved                   |

| 11101 | AD29 | -VREFH (Diff)               | VREFH (S.E)                |

| 11110 | AD30 | Reserved                    | VREFL                      |

| 11111 | AD31 | Module Disabled             | Module Disabled            |

1. ADCx\_CFG2[MUXSEL] bit selects between ADCx\_SEn channels a and b. Refer to MUXSEL description in ADC chapter for details.

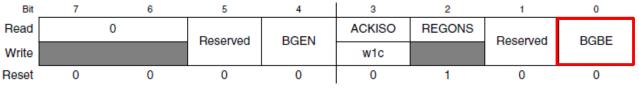

This is the PMC bandgap 1V reference voltage. Prior to reading from this ADC channel, ensure that you enable the bandgap buffer by setting the PMC\_REGSC[BGBE] bit. Refer to the device data sheet for the bandgap voltage (V<sub>BG</sub>) specification.

It is required to turn on the Bandgap buffer by setting the bit BGBE of PMC\_REGSC register; otherwise, conversions will return random values.

PMC\_REGSC field descriptions

Freescale, the Freescale logo, AltiVec, C-5, Code/TEST, Code/Warrior, ColdFire, C-Ware, the Energy Efficient Solutions logo, mobileGT, PowerQUICC, QorlQ, StarCore and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeKit, BeeStack, ColdFire+, CoreNet, Flexis, Kinetis, MXC, Platformin a Package, Processor Expert, QorlQ Qonverge, Qorivva, QUICC Engine, SMARTIMOS, TurboLink, VortiQa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other productor service names are the property of their respective owners. © 2011 Freescale Semiconductor, Inc.

### ADC Hands-On (cont.)

- Open Tera Term and ensure that the Serial Port is the "Open SDA CDC Serial Port", with a baud rate of 38400 bps.

- The raw data, the calculated Bandgap voltage (considering VDD = 3.3V), and the calculated VDD voltage (considering Bandgap = 1V) will be printed.

| Tera Term: New connection                                 | 🐸 COM82:38400baud - Tera Term VT                                                                                               |          |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|----------|

| © <u>T</u> CP/IP H <u>o</u> st: 192.168.1.3 ▼             | <u>F</u> ile <u>E</u> dit <u>S</u> etup C <u>o</u> ntrol <u>W</u> indow <u>H</u> elp                                           |          |

| TCP port#: 23 Protocol: UNSPEC -                          | This is the ADC example on FRDM-KL25Z!                                                                                         | <b>^</b> |

|                                                           | Raw result(0-65535): 19775<br>Bandgap Voltage (considering VDD=3.3V): 0.99V<br>Calculated VDD (considering Bandgap=1V): 3.31 V |          |

| ● <u>S</u> erial Port: COM82: OpenSDA - CDC Serial Port ▼ | Raw result(0-65535): 19814<br>Bandgap Voltage (considering VDD=3.3V): 0.99V<br>Calculated VDD (considering Bandgap=1V): 3.30 V |          |

| OK Cancel Help                                            | Raw result(0-65535): 19814<br>Bandgap Voltage (considering VDD=3.3V): 0.99V<br>Calculated VDD (considering Bandgap=1V): 3.30 V |          |

|                                                           | Raw result(0-65535): 19813                                                                                                     |          |

| Port: COM82 OK                                            | Bandgap Voltage (considering VDD=3.3V): 0.99V<br>Calculated VDD (considering Bandgap=1V): 3.30 V                               |          |

| <u>B</u> aud rate: <u>38400</u> ▼                         | Raw result (0-65535): 19811                                                                                                    |          |

| <u>D</u> ata: 8 bit → Cancel                              | Bandgap Voltage (considering VDD=3.3V): 0.99V<br>Calculated VDD (considering Bandgap=1V): 3.30 V                               |          |

| P <u>a</u> rity: none -                                   |                                                                                                                                |          |

| <u>S</u> top: 1 bit → <u>H</u> elp                        |                                                                                                                                |          |

| Elow control:                                             |                                                                                                                                |          |

| Transmit delay                                            |                                                                                                                                |          |

| 0 msec/ <u>c</u> har 0 msec/ <u>l</u> ine                 |                                                                                                                                |          |

|                                                           |                                                                                                                                | <b>•</b> |

21

Freescale, the Freescale logo, AltiVec, C-5, Code TEST, CodeWarrior, ColdFire, C-Ware, the Energy Efficient Solutions logo, mobileGT, PowerQUICC, QorlQ, StarCore and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeKit, BeeStack, ColdFire+, CoreNet, Flexis, Kinetis, MXC, Platformin a Package, Processor Expert, QorlQ Qonverge, Qorivva, QUICC Engine, SMARTIMOS, TurboLink, VortiQa and Xtinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2011 Freescale Semiconductor, Inc.

- 1. ADC Features overview

- 2. External signal connections

- 3. Configuration registers

- 4. ADC Hands-On explanation

- 5. Reference material

Freescale, the Freescale logo, AltiVec, C-5, Code TEST, CodeWarrior, ColdFire, C-Ware, the Energy Efficient Solutions logo, mobileGT, PowerQUICC, QorlQ, StarCore and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeKit, BeeStack, CodiFire+, CoreNet, Flexis, Kinetis, MXC, Platformin a Package, Processor Expert, QorlQ Qonverge, Qorivva, QUICC Engine, SMARTMOS, TurboLink, VortiQa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other productor service names are the property of their respective owners. © 2011 Freescale Semiconductor, Inc.

#### **Reference Material**

More information about using the temperature sensor available on AN3031 "*Temperature Sensor for the HCS08 Microcontroller Family*": <u>http://www.freescale.com/files/microcontrollers/doc/app\_note/AN3031.pdf</u>

Complete pin out description on FRDM-KL25Z User's Manual : <u>http://www.freescale.com/files/32bit/doc/user\_guide/FRDMKL25ZUM.zip</u>

Kinetis L Peripheral Module Quick Reference: <u>http://www.freescale.com/files/32bit/doc/quick\_ref\_guide/KLQRUG.pdf</u>

Freescale, the Freescale logo, AltiVec, C-5, Code/TEST, Code/Warrior, ColdFire, C-Ware, the Energy Efficient Solutions logo, mobileGT, PowerQUICC, QorlQ, StarCore and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeKit, BeeStack, ColdFire+, CoreNet, Flexis, Kinetis, MXC, Platformin a Package, Processor Expert, QorlQ Qonverge, Qorivva, QUICC Engine, SMARTMOS, TurboLink, VortiQa and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other productor service names are the property of their respective owners. Ø 2011 Freescale Semiconductor, Inc.