## Wide Operating Temperature

# COM-842E COM Express CPU Module

## User's Manual Version 1.1

2011.06 **CE**

| Tł | his page is intentionally left blank. |  |

|----|---------------------------------------|--|

|    |                                       |  |

|    |                                       |  |

|    |                                       |  |

|    |                                       |  |

|    |                                       |  |

|    |                                       |  |

|    |                                       |  |

|    |                                       |  |

|    |                                       |  |

|    |                                       |  |

|    |                                       |  |

|    |                                       |  |

|    |                                       |  |

|    |                                       |  |

| Table of Contents                       |    |

|-----------------------------------------|----|

| Chapter 1 - Introduction                | 1  |

| 1.1 Copyright Notice                    | 2  |

| 1.2 Declaration of Conformity           |    |

| 1.3 About This User's Manual            |    |

| 1.4 Warning                             |    |

| 1.5 Replacing the Lithium Battery       |    |

| 1.6 Technical Support                   | 4  |

| 1.7 Warranty                            | 4  |

| 1.8 Packing List                        | 5  |

| 1.9 Ordering Information                | 5  |

| 1.10 Specifications                     |    |

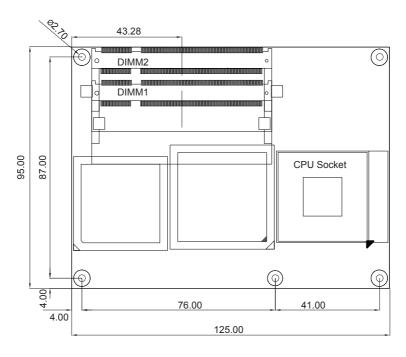

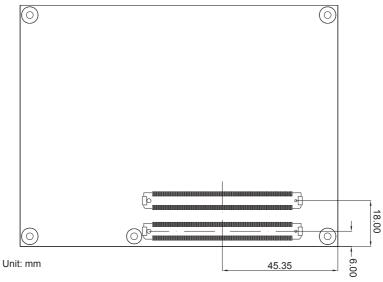

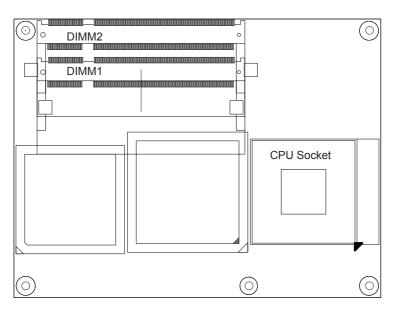

| 1.11 Board Dimensions                   | 7  |

| Chapter 2 - Installation                | 9  |

| 2.1 What is " COM Express "?            |    |

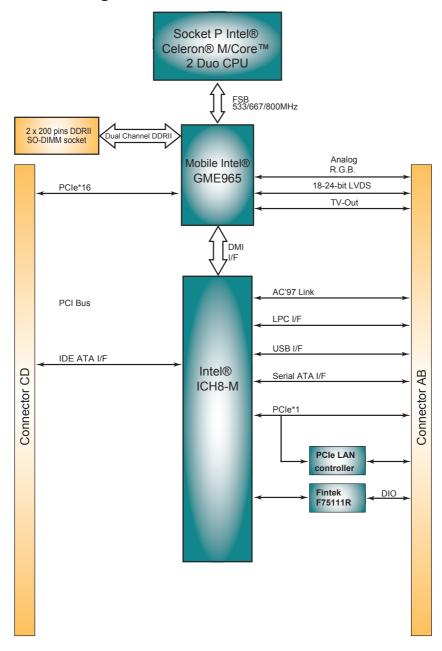

| 2.2 Block Diagram                       |    |

| 2.3 Jumpers and Connectors              | 12 |

| 2.4 COM Express AB Connector            | 13 |

| 2.5 COM Express CD Connector            |    |

| 2.6 The Installation Paths of CD Driver | 17 |

| Chapter 3 - BIOS                        | 19 |

| 3.1 BIOS Main Setup                     |    |

| 3.2 Advanced Settings                   | 21 |

| 3.2.1 CPU Configuration                 |    |

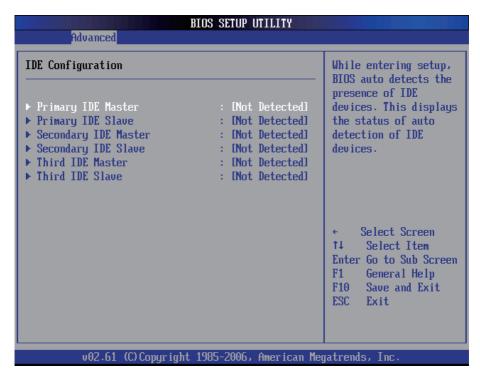

| 3.2.2 IDE Configuration                 | 24 |

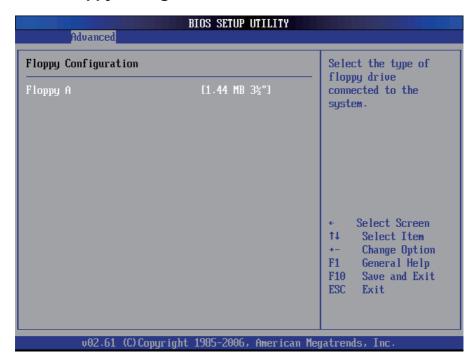

| 3.2.3 Floppy Configuration              |    |

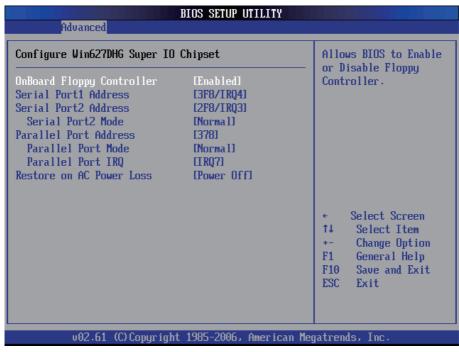

| 3.2.4 Super IO Configuration            | 26 |

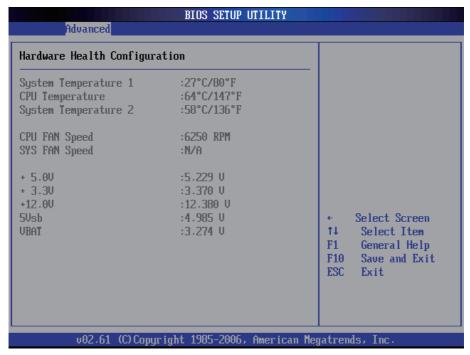

| 3.2.5 Hardware Health Configuration     | 28 |

| 3.2.6 ACPI Configuration                |    |

| 3.2.7 AHCI Configuration                |    |

| 3.2.8 APM Configuration                 | 31 |

| 3.2.9 MPS Configuration                 | 33 |

| 3.2.10 USB Configuration                | 34 |

| 3.2.11 Remote Access Configuration         | 36 |

|--------------------------------------------|----|

| 3.3 Advanced PCI/PnP Settings              | 37 |

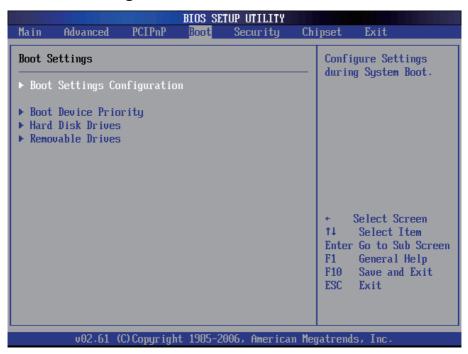

| 3.4 Boot Settings                          | 39 |

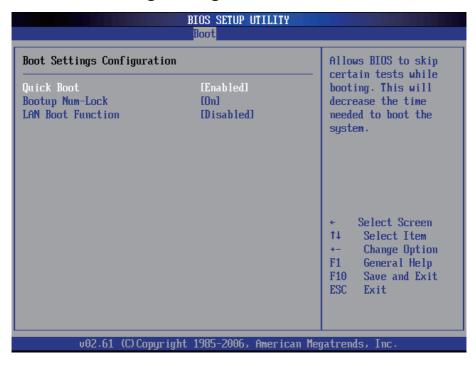

| 3.4.1 Boot Settings Configuration          | 40 |

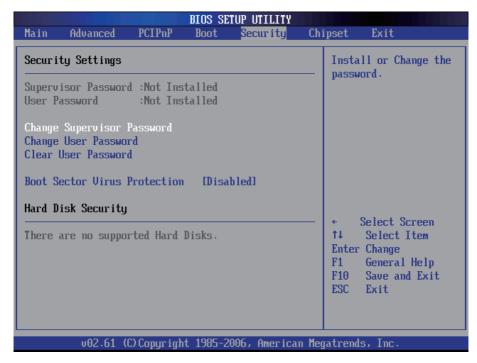

| 3.5 Security                               | 41 |

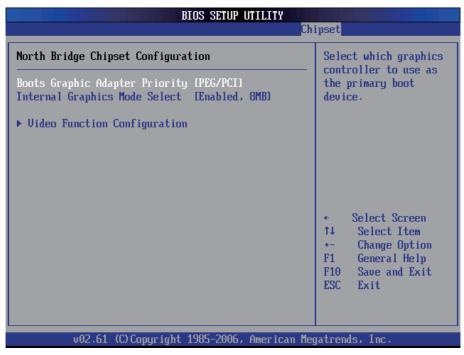

| 3.6 Advanced Chipset Settings              | 43 |

| 3.6.1 North Bridge Chipset Configuration   | 43 |

| 3.6.2 South Bridge Chipset Configuration   | 46 |

| 3.7 Exit Options                           | 48 |

| 3.8 Beep Sound codes list                  | 53 |

| 3.8.1 Boot Block Beep Codes                | 53 |

| 3.8.2 POST BIOS Beep Codes                 | 53 |

| 3.8.3 Troubleshooting POST BIOS Beep Codes | 54 |

| Appendix                                   | 67 |

| Appendix A: I/O Port Address Map           | 68 |

| Appendix B: BIOS Memory Map                | 69 |

| Appendix C: Interrupt Request Lines (IRQ)  | 70 |

| Appendix D: Digital I/O Setting            | 71 |

## Chapter 1

## Introduction

#### 1.1 Copyright Notice

All Rights Reserved.

The information in this document is subject to change without prior notice in order to improve the reliability, design and function. It does not represent a commitment on the part of the manufacturer.

Under no circumstances will the manufacturer be liable for any direct, indirect, special, incidental, or consequential damages arising from the use or inability to use the product or documentation, even if advised of the possibility of such damages.

This document contains proprietary information protected by copyright. All rights are reserved. No part of this manual may be reproduced by any mechanical, electronic, or other means in any form without prior written permission of the manufacturer.

#### 1.2 Declaration of Conformity

#### CE

This product has passed the CE test for environmental specifications when shielded cables are used for external wiring. This kind of cable is available from ARBOR. Please contact your local supplier for ordering information. Test conditions for passing included the equipment being operated within an industrial enclosure. In order to protect the product from being damaged by ESD (Electrostatic Discharge) and EMI leakage, we strongly recommend the use of CE-compliant industrial enclosure products.

#### **FCC Class A**

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) this device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.

#### **RoHS**

ARBOR Technology Corp. certifies that all components in its products are in compliance and conform to the European Union's Restriction of Use of Hazardous Substances in Electrical and Electronic Equipment (RoHS) Directive 2002/95/FC.

The above mentioned directive was published on 2/13/2003. The main purpose of the directive is to prohibit the use of lead, mercury, cadmium, hexavalent chromium, polybrominated biphenyls (PBB), and polybrominated diphenyl ethers (PBDE) in electrical and electronic products. Member states of the EU

are to enforce by 7/1/2006.

ARBOR Technology Corp. hereby states that the listed products do not contain unintentional additions of lead, mercury, hex chrome, PBB or PBDB that exceed a maximum concentration value of 0.1% by weight or for cadmium exceed 0.01% by weight, per homogenous material. Homogenous material is defined as a substance or mixture of substances with uniform composition (such as solders, resins, plating, etc.). Lead-free solder is used for all terminations (Sn(96-96.5%), Ag(3.0-3.5%) and Cu(0.5%)).

#### 1.3 About This User's Manual

This user's manual provides general information and installation instructions about the product. This User's Manual is intended for experienced users and integrators with hardware knowledge of personal computers. If you are not sure about any description in this booklet. please consult your vendor before further handling.

#### 1.4 Warning

Single Board Computers and their components contain very delicate Integrated Circuits (IC). To protect the Single Board Computer and its components against damage from static electricity, you should always follow the following precautions when handling it:

- 1. Disconnect your Single Board Computer from the power source when you want to work on the inside.

- 2. Hold the board by the edges and try not to touch the IC chips, leads or circuitry.

- 3. Use a grounded wrist strap when handling computer components.

- 4. Place components on a grounded antistatic pad or on the bag that comes with the Single Board Computer, whenever components are separated from the system.

#### 1.5 Replacing the Lithium Battery

Incorrect replacement of the lithium battery may lead to a risk of explosion.

The lithium battery must be replaced with an identical battery or a battery type recommended by the manufacturer.

Do not throw lithium batteries into the trash-can. It must be disposed of in accordance with local regulations concerning special waste.

#### 1.6 Technical Support

If you have any technical difficulties, please do not hesitate to call or e-mail our customer service.

http://www.arbor.com.tw

E-mail:info@arbor.com.tw

#### 1.7 Warranty

This product is warranted to be in good working order for a period of two years from the date of purchase. Should this product fail to be in good working order at any time during this period, we will, at our option, replace or repair it at no additional charge except as set forth in the following terms. This warranty does not apply to products damaged by misuse, modifications, accident or disaster.

Vendor assumes no liability for any damages, lost profits, lost savings or any other incidental or consequential damage resulting from the use, misuse of, or inability to use this product. Vendor will not be liable for any claim made by any other related party.

Vendors disclaim all other warranties, either expressed or implied, including but not limited to implied warranties of merchantability and fitness for a particular purpose, with respect to the hardware, the accompanying product's manual(s) and written materials, and any accompanying hardware. This limited warranty gives you specific legal rights.

Return authorization must be obtained from the vendor before returned merchandise will be accepted. Authorization can be obtained by calling or faxing the vendor and requesting a Return Merchandise Authorization (RMA) number. Returned goods should always be accompanied by a clear problem description.

#### 1.8 Packing List

1 x COM-842E COM Express CPU Module

1 x Driver CD

1 x Quick Installation Guide

If any of the above items is damaged or missing, contact your vendor immediately.

#### 1.9 Ordering Information

| COM-842E/L7500 | Intel® Core™ 2 Duo L7500 1.6GHz COM Express CPU Module |

|----------------|--------------------------------------------------------|

| PBE-1700       | COM Express evaluation board in ATX form factor        |

| HS-0842-F1     | Heat spreader (114 x 95 x 20.8mm)                      |

| CBK-04-1700-00 | Cable kit                                              |

#### 1.10 Specifications

| Form Factor          | COM Express Type 2 CPU Module                                                                  |

|----------------------|------------------------------------------------------------------------------------------------|

| CPU                  | Intel® Core™ 2 Duo processor, up to 800MHz FSB Intel® Celeron® M processor with 533/667MHz FSB |

| Chipset              | Intel® GME965 + Intel® ICH8M                                                                   |

| System Memory        | 2 x 200-pin DDR2 SO-DIMM sockets supporting 533/667MHz SDRAM up to 4GB                         |

| VGA/LCD Controller   | Integrated Intel® Graphics Media Accelerator X3100                                             |

| Ethernet             | 1 x RTL8111 PCle Gigabit Ethernet Controller                                                   |

| BIOS                 | AMI PnP Flash BIOS                                                                             |

| Serial ATA           | 3 x Serial ATA with 300MB/s HDD transfer rate                                                  |

| IDE Interface        | 1 x Ultra ATA, supports 2 IDE devices                                                          |

| Universal Serial Bus | 8 x USB 2.0                                                                                    |

| Digital Input/Output | 8-bit programmable Digital Input/Output                                                        |

| Expansion Interface  | 1 x PCI Express x16<br>5 x PCI Express x1<br>4 x PCI                                           |

| Operation Temp.      | -40°C ~ 85°C (-40°F ~ 185°F)                                                                   |

| Watchdog Timer       | 1 ~ 255 levels Reset                                                                           |

| Dimension (L x W)    | 125 x 95 mm (4.9" x 3.7")                                                                      |

#### 1.11 Board Dimensions

This page is intentionally left blank.

# Chapter 2

## Installation

#### 2.1 What is "COM Express"?

With more and more demands on small and embedded industrial boards, a multi-functioned COM (Computer-on-Module) is the great one of the solutions.

COM Express, board-to-board connectors consist of two rows of 220 pins each.

Row AB, which is required, provides pins for PCI Express, SATA, LVDS, LCD channel, LPC bus, system and power management, VGA, LAN, and power and ground interfaces.

Row CD, which is optional, provides SDVO and legacy PCI and IDE signals next to additional PCI Express, LAN and power and ground signals.

By the way, the target markets of COM will be focused on:

- Retail & Advertising

- Medical

- Test & Measurement

- Gaming & Entertainment

- Industrial & Automation

- Military & Government

- Security

#### 2.2 Block Diagram

#### 2.3 Jumpers and Connectors

#### 2.4 COM Express AB Connector

| B1         | GND                  | GND                   | A1  |

|------------|----------------------|-----------------------|-----|

| B2         | GBE0 ACT#            |                       | A2  |

| B3         | LPC_FRAME#           | GBE0 MDI3+            | A3  |

| B4         | I PC ADO             | GBE0 LINK100#         |     |

| B5         | LPC_AD0<br>LPC_AD1   | GBE0_LINK100#         |     |

| <br>D0     | LPC_ADT              |                       |     |

| <u>B6</u>  | LPC_AD2              | GBE0_MDI2-            | A6  |

| B7         | LPC_AD3<br>LPC_DRQ0# | GBE0_MDI2+            | A7  |

| B8         | LPC_DRQ0#            | GBE0_LINK#            |     |

| B9         | LPC_DRQ1#<br>LPC_CLK | GBE0_MDI1-            | A9  |

| B10        | LPC_CLK              | GBE0_MDI1+            | A10 |

| B11        | GND                  |                       | A11 |

| B12        | PWRBTN#              | GBE0_MDI0-            | A12 |

| B13        | SMB_CK               | GBE0_MDI0+            | A13 |

| B14        | SMB_DAT              | GBE0_CTREF            | A14 |

| B15        | SMB ALERT#           | SŪS S3#               | A15 |

| B16        | N/C                  | SATAO_TX+             | A16 |

| B17        | N/C                  |                       |     |

| B18        | SUS_STAT#            | SATA0_TX-<br>SUS_S4#  | A18 |

| B19        | N/C                  | SATAO RX+             | A19 |

| B20        | N/C                  | SATAO_RX-             |     |

| B21        | GND                  | GND                   | A21 |

| B22        | N/C                  | SATA2 TX+             | A22 |

| B23        | N/C                  | SATA2 TX-             | A23 |

| B24        | PWR_OK               | 0/1/2_1X-             |     |

| B25        | N/C                  | SUS_S5#<br>SATA2_RX+  | A25 |

| B26        | N/C                  | SATA2_RX-             | A26 |

| B27        | WDT                  | BATLOW#               |     |

| B28        |                      | ATA ACT#              |     |

| B29        | AC_SDIN2             | A/A_AC/#              | A20 |

|            | AC_SDIN1<br>AC_SDIN0 | AC_SYNC<br>AC_RST#    | A29 |

| B30<br>B31 | GND                  | GND                   | A30 |

| B32        | SPKR                 | AC DITCLY             | A31 |

|            |                      | AC_BITCLK<br>AC_SDOUT | A32 |

| B33        | I2C_CK<br>I2C_DAT    | PIOS DISABLE#         | A33 |

| B34        | TUDAT                | BIOS_DĪSABLE#         |     |

| B35        | THRM#                | THRMTRIP#             |     |

| B36        | USB7-                | USB6-                 |     |

| B37        | USB7+                | USB6+                 |     |

| B38        | USB_4_5_OC#          | USB_6_7_OC#           |     |

| B39        | USB5-                | USB4-                 | A39 |

| <u>B40</u> | USB5+                | USB4+                 |     |

| B41        | GND                  | GND                   |     |

| B42        | USB3-                |                       | A42 |

| B43        | USB3+                | USB2+                 |     |

| B44        | USB_0_1_OC#          | USB_2_3_OC#           |     |

| B45        | USB1-                | ŪSB0-                 |     |

| B46        | USB1+                | USB0+                 |     |

| B47        | EXCD1_PERST#         |                       | A47 |

| B48        | EXCD1_CPPE#          | EXCD0_PERST#          |     |

| B49        | SYS_RESET#           | EXCD0_CPPE#           |     |

| B50        | CB_RESET#            | LPC_SERIRQ            |     |

| B51        | GNĪD                 | - GND                 | A51 |

| B52        | N/C                  | N/C                   | A52 |

| B53        | N/C                  |                       | A53 |

| B54        | GPO1                 | GPI0 D54              | A54 |

| B55        | N/C                  | N/C                   | A55 |

|            |                      |                       | -   |

| B56        | N/C                                                                                             | N/C                           | A56        |

|------------|-------------------------------------------------------------------------------------------------|-------------------------------|------------|

| B57        | GPO2                                                                                            | GND                           | A57        |

| B58        | N/C                                                                                             | N/C                           | A58        |

| B59        | N/C                                                                                             | N/C                           | A59        |

| B60        | GND                                                                                             | GND                           | A60        |

| B61        | PCIE RX2+                                                                                       | PCIE TX2+                     | A61        |

| B62        | PCIE RX2-                                                                                       | PCIE TX2-                     | A62        |

| B63        | GPO3                                                                                            | GPI1                          | A63        |

| B64        | PCIE RX1+                                                                                       | PCIE TX1+                     | A64        |

| B65        | PCIE RX1-                                                                                       | PCIE TX1-                     | A65        |

| B66        | WAKE0#                                                                                          | GND                           | A66        |

| B67        | WAKE1#                                                                                          | GPI2                          | A67        |

| B68        | PCIE RX0+                                                                                       | PCIE_TX0+                     | A68        |

|            |                                                                                                 | PCIE TX0-                     |            |

| B69<br>B70 | PCIE_RX0-<br>GND                                                                                |                               | A69        |

| B71        | LVDS B0+                                                                                        | GND<br>LVDS_A0+               | A70<br>A71 |

|            |                                                                                                 |                               |            |

| B72        | LVDS_B0-                                                                                        | LVDS_A0-                      | A72        |

| B73        | LVDS_B1+                                                                                        | LVDS_A1+                      | A73        |

| B74        | LVDS_B1-                                                                                        | LVDS_A1-                      | A74        |

| B75        | LVDS_B2+                                                                                        | LVDS_A2+                      | A75        |

| B76        | LVDS_B2-                                                                                        | LVDS_A2-                      | A76        |

| B77        | N/C                                                                                             | LVDS_VDD_EN                   | A77        |

| B78        | N/C                                                                                             | N/C                           | A78        |

| B79        | LVDS_BKLT_EN                                                                                    | N/C                           | A79        |

| B80        | GND                                                                                             | GND                           | A80        |

| B81        | LVDS_B_CK+                                                                                      | LVDS_A_CK+                    | A81        |

| B82        | LVDS_B_CK-                                                                                      | LVDS_A_CK-                    | A82        |

| B83        | CKLVDS_BKLT_CTRL                                                                                | LVDS_I2C_CK                   | A83        |

| B84        | VCC_5V_SBY<br>VCC_5V_SBY<br>VCC_5V_SBY<br>VCC_5V_SBY                                            | LVDS_T2C_DAT                  | A84        |

| B85        | VCC_5V_SBY                                                                                      | GPI3                          | A85        |

| B86        | VCC_5V_SBY                                                                                      | KBD_RST#                      | A86        |

| B87        | VCC_5V_SBY                                                                                      | KBD_A20GATE                   | A87        |

| B88        | RSVD                                                                                            | PCIE0_CK_REF+                 | A88        |

| B89        | VGA_RED                                                                                         | PCIE0_CK_REF-                 | A89        |

| B90        | GND                                                                                             | GND                           | A90        |

| B91        | VGA_GRN                                                                                         | RSVD B91                      | A91        |

| B92        | VGA_BLU                                                                                         | RSVD                          | A92        |

| B93        | VGA_HSYNC                                                                                       | GPO0                          | A93        |

| B94        | VGA_VSYNC                                                                                       | RSVD                          | A94        |

| B95        | VGA_I2C_CK                                                                                      | RSVD                          | A95        |

| B96        | VGA_I2C_DAT                                                                                     | GND                           | A96        |

| B97        | TV_DAC_A                                                                                        | VCC_12V                       | A97        |

| B98        | TV_DAC_B                                                                                        | VCC_12V<br>VCC_12V            | A98        |

| B99        | TV_DAC_C                                                                                        | VCC_12V                       | A99        |

| B100       | GND                                                                                             | GND                           | A100       |

| B101       | VCC_12V                                                                                         | VCC_12V                       | A101       |

| B102       | VCC_12V                                                                                         | VCC_12V                       | A102       |

| B103       | VCC_12V                                                                                         | VCC_12V<br>VCC_12V            | A103       |

| B104       | VCC_12V                                                                                         | VCC_12V                       | A104       |

| B105       | VCC_12V                                                                                         | VCC_12V<br>VCC_12V<br>VCC_12V | A105       |

| B106       | VCC_12V                                                                                         | VCC_12V                       | A106       |

| B107       | VCC_12V                                                                                         | VCC 12V                       | A107       |

| B108       | VCC_12V                                                                                         | VCC_12V<br>VCC_12V            | A108       |

| B109       | VCC_12V<br>VCC_12V<br>VCC_12V<br>VCC_12V<br>VCC_12V<br>VCC_12V<br>VCC_12V<br>VCC_12V<br>VCC_12V | VCC_12V                       | A109       |

| B110       | GND                                                                                             | GND                           | A110       |

|            |                                                                                                 |                               |            |

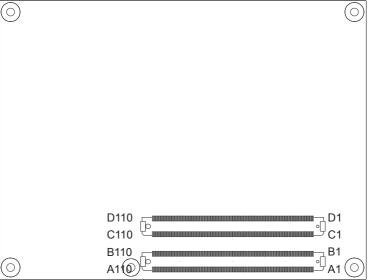

#### 2.5 COM Express CD Connector

| D1         | GND                      | GND                | C1         |

|------------|--------------------------|--------------------|------------|

| D2         | IDE D5                   | IDE D7             | C2         |

| D3         | IDE_D10                  | IDE D6             | C3         |

| D4         | IDE D11                  |                    | C4         |

| D5         | IDE D12                  | IDE_D3             | C5         |

|            |                          | IDE_D13            |            |

| <u>D6</u>  | IDE_D4                   |                    | C6         |

| D7         | IDE_D0                   | IDE_D9             | C7         |

| <u>D8</u>  | IDE_REQ                  | IDE_D2             | C8         |

| D9         | IDE_IOW#                 | IDE_D13            | <u>C9</u>  |

| D10        | IDE_ACK#                 | IDE_D1             | C10        |

| D11        | GND                      |                    | C11        |

| D12        | IDE_IRQ                  | IDE_D14            | C12        |

| D13        | IDE_A0                   | IDE_IORDY          | C13        |

| D14        | IDE_A1                   | IDE_IOR#           | C14        |

| D15        | IDE A2                   | PCI PME#           | C15        |

| D16        | IDE_CS1#                 | PCI_GNT2#          | C16        |

| D17        | IDF CS3#                 | PCI REQ2#          |            |

| D18        | IDE RESET#               | PCI GNT1#          | C18        |

| D19        | PCI_GNT3#                | PCI REQ1#          | C19        |

| D20        | PCI REQ3#                | PCI_GNT0#          |            |

| D21        | GND                      | GND                | C21        |

| D22        | PCI AD1                  | PCI REQ0#          | C21<br>C22 |

| D23        | PCI_AD1                  | PCI_RESET#         | C23        |

|            |                          |                    | C24        |

| D24<br>D25 | PCI_AD5                  | PCI_AD0<br>PCI_AD2 | C24        |

|            | PCI_AD7                  |                    | C25        |

| D26        | PCI_C/BE0#               | PCI_AD4            | C26        |

| D27        | PCI_AD9                  | PCI_AD6            | C27        |

| D28        | PCI_AD11                 |                    | C28        |

| D29        | PCI_AD13                 | PCI_AD10           | C29        |

| D30        | PCI_AD15                 | PCI_AD12           | C30        |

| D31        | GND                      | GND                | C31        |

| D32        | PCI_PAR                  | PCI_AD14           | C32        |

| D33        | PCI_SERR#                | PCI_C/BE1#         |            |

| D34        | PCI_STOP#                | PCĪ_PERR#          | C34        |

| D35        | PCI_TRDY#                | PCI_LOCK#          | C35        |

| D36        | PCI_FRAME#               | PCI_DEVSEL#        | C36        |

| D37        | PCI_AD16                 | PCI_IRDY#          | C37        |

| D38        | PCI_AD18                 | PCI_C/BE2#         | C38        |

| D39        | PCI_AD20                 | PCI_AD17           | C39        |

| D40        | PCI AD22                 | PCI AD19           | C40        |

| D41        | GND                      | - GND              | C41        |

| D42        | PCI_AD24                 | PCI AD21           | C42        |

| D43        | PCI AD26                 | PCI AD23           | C43        |

| D44        | PCT AD28                 | PCI C/BE3#         | C44        |

| D45        | PCI AD30                 | PCI AD25           | C45        |

| D46        | PCI_IRQC#                | PCI AD27           | C46        |

| D47        | PCI_IRQD#                | PCI_AD29           | C47        |

| D48        | PCI CLKRUN#              | PCI AD31           | C48        |

| D49        | PCI_M66EN                | PCI TRQA#          | C49        |

| D50        | PCI CLK                  | PCI_IRQB#          |            |

| D51        | GND<br>GND               | GND (FIXED)        | C51        |

| D51        | PEG_TX0+                 | PEG RX0+           | C52        |

| D52        | PEG_TX0+                 |                    | C52        |

| D53        | PEG_LANE_RV#             | TYPE0#             | C54        |

|            | PEG_LANL_KV#<br>PEG_TX1+ | PEG RX1+           |            |

| טטט        | I LU_IAIT                | FLG_RXIT           | 000        |

| D56  | PEG_TX1-                                                       | PEG RX1-                                                       | C56  |

|------|----------------------------------------------------------------|----------------------------------------------------------------|------|

| D57  | TYPE2#                                                         | TYPE1#                                                         |      |

| D58  | PEG_TX2+                                                       | PEG RX2+                                                       |      |

|      | PEG_TX2-                                                       | PEG RX2-                                                       |      |

| D60  | GND                                                            | GND                                                            |      |

|      | DEC TV2                                                        |                                                                |      |

| D61  | PEG_TX3+<br>PEG_TX3-                                           | PEG_RX3+                                                       |      |

| D62  | PEG_1X3-                                                       | PEG_RX3-                                                       |      |

| D63  | RSVD                                                           | RSVD                                                           |      |

| D64  | RSVD                                                           | RSVD                                                           |      |

| D65  | PEG_TX4+<br>PEG_TX4-                                           | PEG_RX4+                                                       |      |

| D66  | PEG_TX4-                                                       | PEG_RX4-                                                       |      |

| D67  | GND                                                            | RSVD                                                           |      |

| D68  | PEG_TX5+                                                       | PEG_RX5+                                                       | C68  |

| D69  | PEG_TX5-                                                       | PEG_RX5-                                                       | C69  |

| D70  | GND                                                            | GND                                                            | C70  |

| D71  | PEG_TX6+<br>PEG_TX6-                                           | PEG RX6+                                                       | C71  |

| D72  | PEG TX6-                                                       | PEG RX6-                                                       | C72  |

| D73  | SDVO CLK                                                       | SDVO_DATA                                                      | C73  |

| D74  | PEG TX7+                                                       | PEG RX7+                                                       | C74  |

| D75  | PEG_TX7+<br>PEG_TX7-                                           | PEG RX7-                                                       |      |

| D76  | GND                                                            | GND                                                            |      |

| D77  | IDE CBLID#                                                     | RSVD                                                           |      |

| D78  | DEC TYS+                                                       | PEG RX8+                                                       |      |

| D79  | PEG_TX8+<br>PEG_TX8-                                           | PEG RX8-                                                       |      |

| D80  | GND                                                            | GND                                                            |      |

| D81  | DEC TYOL                                                       | PEG RX9+                                                       |      |

| D82  | PEG_TX9+<br>PEG_TX9-                                           | PEG_RX9+                                                       |      |

| D83  | RSVD                                                           | RSVD                                                           |      |

| D83  | GND                                                            | GND                                                            |      |

| D85  | PEG TX10+                                                      | PEG RX10+                                                      | C85  |

| D86  | PEG_TX10-                                                      | PEG RX10-                                                      |      |

| D87  | GND                                                            | GND                                                            |      |

| D88  | PEG_TX11+                                                      | PEG RX11+                                                      |      |

| D89  | PEG_TX11-                                                      | PEG RX11-                                                      |      |

| D89  | GND                                                            | FEG_RXTI-<br>GND                                               |      |

| D90  | PEG_TX12+                                                      | PEG RX12+                                                      |      |

| D91  | PEC TV12                                                       |                                                                |      |

|      | PEG_TX12-                                                      | PEG_RX12-                                                      |      |

| D93  | GND<br>DEC TYAN                                                | GND                                                            |      |

| D94  | PEG_TX13+                                                      | PEG_RX13+                                                      | C94  |

| D95  | PEG_TX13-                                                      | PEG_RX13-                                                      |      |

| D96  | GND                                                            | GND                                                            |      |

| D97  | PEG_ENABLE#                                                    | RSVD                                                           |      |

| D98  | PEG_TX14+                                                      | PEG_RX14+                                                      |      |

| D99  | PEG_TX14-                                                      | PEG_RX14-                                                      | C99  |

| D100 | GND                                                            | GND                                                            |      |

| D101 | PEG_TX15+                                                      | PEG_RX15+                                                      |      |

| D102 | PEG_TX15-                                                      | PEG_RX15-                                                      | C102 |

| D103 | GND                                                            | GND                                                            | C103 |

| D104 | VCC_12V                                                        | VCC_12V                                                        | C104 |

| D105 | VCC_12V                                                        | VCC_12V                                                        | C105 |

| D106 | VCC_12V                                                        | VCC_12V                                                        | C106 |

| D107 | VCC_12V                                                        | VCC_12V                                                        | C107 |

| D108 | VCC_12V<br>VCC_12V<br>VCC_12V<br>VCC_12V<br>VCC_12V<br>VCC_12V | VCC_12V                                                        | C108 |

| D109 | VCC_12V                                                        | VCC_12V<br>VCC_12V<br>VCC_12V<br>VCC_12V<br>VCC_12V<br>VCC_12V | C109 |

| D110 | GND                                                            | GND                                                            | C110 |

#### 2.6 The Installation Paths of CD Driver

#### Windows 2000 & XP

| Driver  | Path                              |

|---------|-----------------------------------|

| CHIPSET | \CHIPSET\INF 9.11                 |

| LAN     | \ETHERNET\REALTEK\8111_WINXP_5764 |

| VGA     | \GRAPHICS\INTEL 2K XP 32\1432     |

#### Windows 7

| Driver  | Path                                                         |

|---------|--------------------------------------------------------------|

| CHIPSET | \CHIPSET\INF 9.11                                            |

| LAN     | Windows 7 built-in LAN driver                                |

| VGA     | \GRAPHICS\INTEL_WIN7_32\1930<br>\GRAPHICS\INTEL_WIN7_64\1930 |

This page is intentionally left blank.

# Chapter 3 BIOS

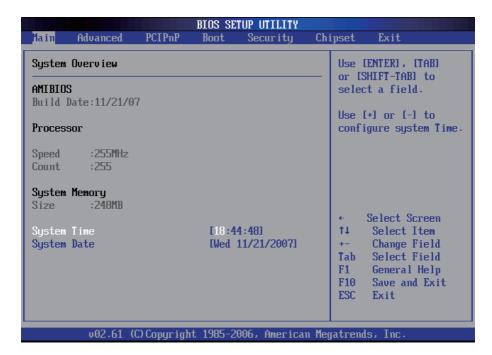

#### 3.1 BIOS Main Setup

The AMI BIOS provides a setup utility program for specifying the system configurations and settings. The BIOS ROM of the system stores the setup utility.

When you turn on the computer, the AMI BIOS is immediately activated. The Main displays system overview status. Use the left/right arrow keys to highlight a particular configuration screen from the top menu bar or use the down arrow key to access and configure the information below.

#### **System Time**

Set the system time.

The time format is: **Hour**: 00 to 23

Minute: 00 to 59 Second: 00 to 59

#### **System Date**

Set the system date. Note that the 'Day' automatically changes when you set

the date.

The date format is: Day: Sun to Sat

Month: 1 to 12 Date: 1 to 31

Year: 1999 to 2099

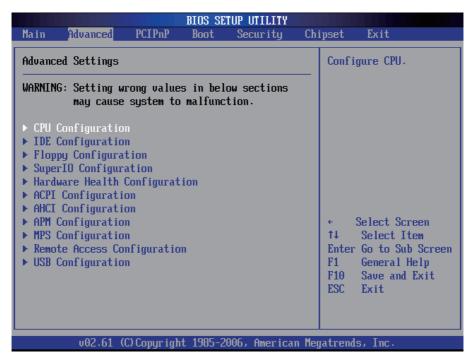

#### 3.2 Advanced Settings

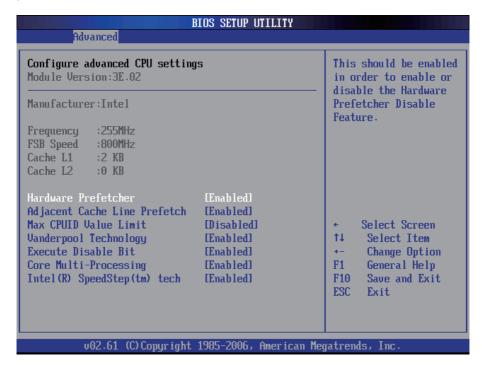

#### 3.2.1 CPU Configuration

The CPU Configuration setup screen varies depending on the installed processor.

#### **Hardware Prefetcher**

This should be enabled in order to enable or disable the Hardware Prefetcher Disable Feature.

Enable - Enable Hardware Prefetcher.

Disabled - Disable Hardware Prefetcher.

#### **Adjacent Cache Line Prefetch**

This should be enabled in order to enable or disable the cache Prefetcher Disable Feature.

The choice: Enabled, Disabled.

#### Cache L1 & L2

CPU Internal Cache & External Cache:

These two categories speed up memory access. However, it depends on CPU/chipset design.

Enable - Enable cache. Disabled - Disable cache

#### **Max CPUID Value Limit**

Disabled for Windows XP.

#### **Vanderpool Technology**

Enable this item will allow a platform to run multiple virtual operating systems and applications in independent partitions.

#### **Core Multi-Processing**

Enabled or disabled the multi-processing functionality of the Core processor.

#### Intel® SpeedStep™ Tech

Maximum: CPU speed is set to maximum. Minimum: CPU speed is set to minimum.

Automatic: CPU speed controlled by Operating system.

Disabled: Default CPU speed.

#### 3.2.2 IDE Configuration

#### Primary/Secondary/Third IDE Master/Slave

Select one of the hard disk drives to configure. Press <Enter> to access its sub menu.

#### 3.2.3 Floppy Configuration

Select the type of floppy disk drive installed in your system.

#### The choice:

None

360K 5.25"

1.2M 5.25"

720K 3.5"

1.44M 3.5"

2.88M 3.5"

#### 3.2.4 Super IO Configuration

#### **Onboard Floppy Controller**

Select "Enabled" if your system has a floppy disk controller (FDC) installed on the system board and you wish to use it. If you didn't install an FDC or the system has no floppy drive, select Disabled in this field.

The Choice: Enabled, Disabled

#### Serial Port1 / Port2 Address

Select an address and corresponding interrupt for the first and second serial ports.

The choice:

3F8/IRQ4

2E8/IRQ3

3E8/IRQ4

2F8/IRQ3

Disabled

Auto

#### **Serial Port2 Mode**

Allows BIOS to select mode for serial Port2.

#### **Parallel Port Address**

Select an address for the parallel port.

The choice:

3BC

378

278

Disabled

#### **Parallel Port Mode**

Select an operating mode for the onboard parallel port. Select Normal, Compatible or SPP unless you are certain both of your hardware and software support one of the other available modes.

The choice:

SPP

**EPP**

ECP

ECP + EPP

Normal

#### **Parallel Port IRQ**

Select an interrupt for the parallel port.

The choice:

IRQ5

IRQ7

#### Restore on AC Power Loss by IO

This item allows you to select if you want to power on the system after power failure.

#### 3.2.5 Hardware Health Configuration

#### System/ CPU Temperature 1

Displays the current System / CPU fan temperature.

#### **CPU / System Fan Speed**

Shows the current CPU / System Fan operating speed.

#### **Vcore**

Displays the voltage level of CPU (Vcore).

#### +5.0V / +3.3V / +12.0V / 5Vsb / VBAT

Shows the voltage level of the +3.3V, +5.0V, +12.0V, +5V standby and battery.

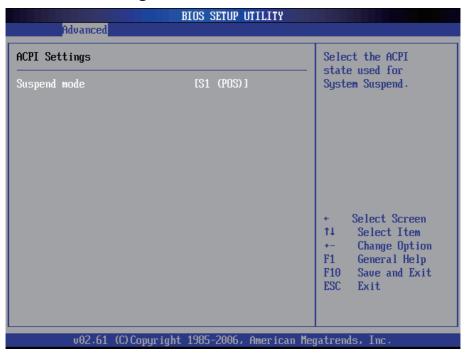

#### 3.2.6 ACPI Configuration

#### Suspend mode

Select the ACPI state used for System Suspend.

The Choice: S1 (POS)

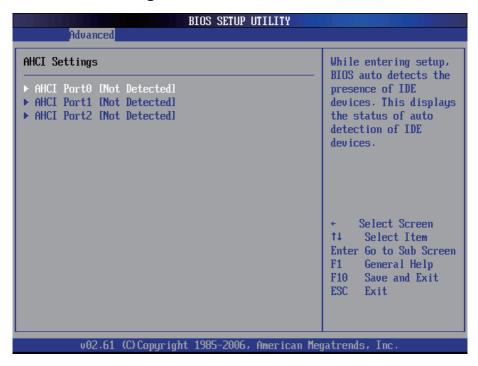

#### 3.2.7 AHCI Configuration

#### AHCI Port 0 / Port 1 / Port 2

While entering setup, BIOS auto detects the presence of IDE devices. This displays the status of auto detection of IDE devices.

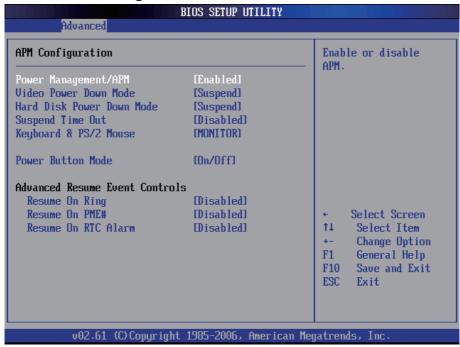

#### 3.2.8 APM Configuration

#### **Power Management/APM**

This category allows you to select the type (or degree) of power saving and is directly related to the following modes:

- 1. HDD Power Down

- 2. Doze Mode

- 3. Suspend Mode

#### Video Power Down Mode

This option defines the level of power-saving mode requires in to power down the video display. As a default, the video powers down both in suspend mode and standby mode.

The Choice: Enabled, Disabled

#### **Hard Disk Power Down Mode**

Power Down Hard Disk in Suspend or Standby Mode.

The Choice: Enabled, Disabled

#### **Suspend Time Out**

Go into Suspend in the specified time.

The Choice: Enabled, Disabled

#### **Keyboard & PS/2 Mouse**

Monitor KBC ports 60/64.

#### **Power Button Mode**

Pressing the power button for more than 4 seconds forces the system to enter the Soft-Off state when the system has "hang".

The Choice: Delay 4 Sec, On/Off

### Advanced Resume Event Controls Resume On Ring

An input signal on the serial Ring Indicator (RI) line (in other words an incoming call on the modem) awakens the system from a soft off state.

The Choice: Enabled, Disabled

#### Resume On PME#

An input signal from a PME on the PCI card awakens the system from a soft off state.

The Choice: Enabled, Disabled

#### **Resume On RTC Alarm**

When "Enabled", you can set the date and time at which the RTC (real-time clock) alarm awakens the system from Suspend mode.

The Choice: Enabled, Disabled

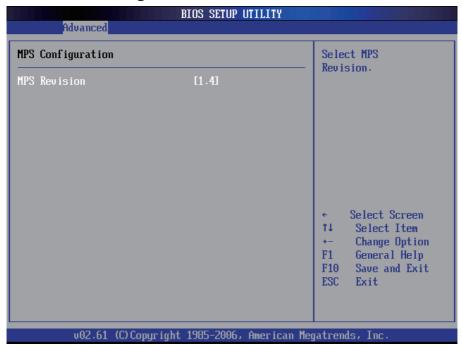

## 3.2.9 MPS Configuration

#### **MPS Revision**

Select the operating system that is Multi-Processors Version Control for OS.

The Choice: 1.4, 1.1.

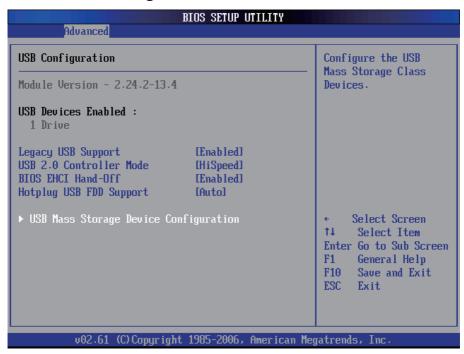

## 3.2.10 USB Configuration

#### **Legacy USB Support**

Enables support for legacy USB. AUTO option disables legacy support if no USB devices are connected.

#### **USB 2.0 Controller Mode**

Configures the USB 2.0 controller in High Speed (480Mbps) or Full Speed (12MBPS).

#### **BIOS EHCI Hand-Off**

This is a work around for OSs without EHCI hand-Off support. The EHCI ownership change should be claimed by EHCI driver.

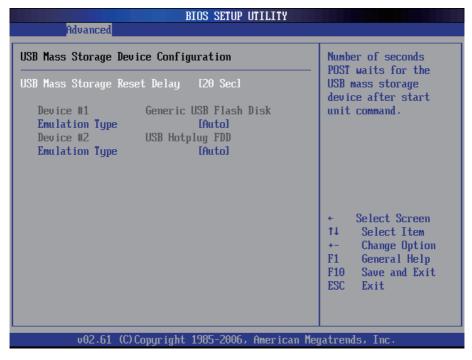

#### **USB Mass Storage Reset Delay**

Number of seconds POST waits for the USB mass storage device after start unit command.

## **Emulation Type**

If Auto, USB devices less than 530MB will be emulated as Floppy and remaining as hard drive. Forced FDD option can be used to force a HDD formatted drive to BOOT as FDD. (Ex. ZIP drive).

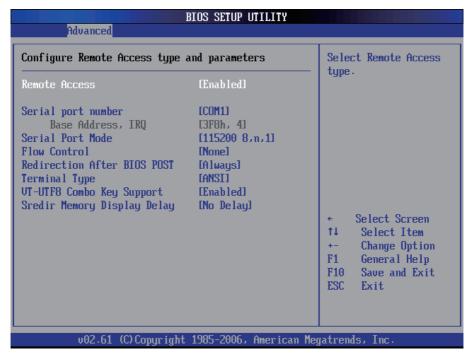

#### 3.2.11 Remote Access Configuration

#### **Remote Access**

Configure Remote Access type and parameters.

The Choice: Enabled, Disabled.

#### Serial port number

Select Serial Port for console redirection. Make sure the selected port is enabled.

The Choice: COM1, COM2.

#### Base Address, IRQ

Select Serial Port for console redirection. Make sure the selected port is enabled. The Choice:

3F8, IRQ4

2E8, IRQ3

3E8, IRQ4

2F8, IRQ3

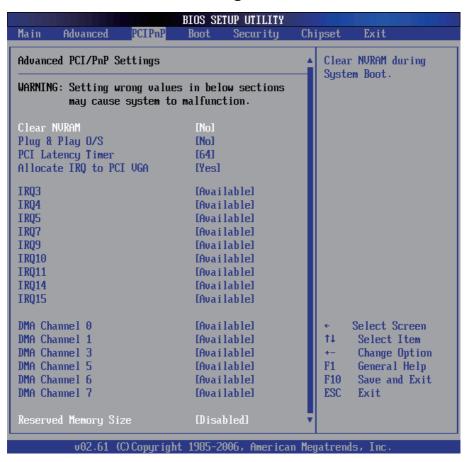

## 3.3 Advanced PCI/PnP Settings

#### **Clear NVRAM**

Clear NVRAM during System BOOT.

The Choice: Yes, No.

#### Plug & Play O/S

No: Lets the BIOS configure all the devices in the system.

Yes: lets the operating system configure Plug and Play (PnP) devices not required for BOOT if your system has a Plug and Play operating system.

#### **PCI Latency Timer**

Value in units of PCI clocks for PCI device latency timer register.

#### Allocate IRQ to PCI VGA

Yes: Assigns IRQ to PCI VGA card if card requests IRQ.

No: Does not assign IRQ to PCI VGA card even if card requests an IRQ.

#### **IRQ3 - IRQ15**

Available: Specified IRQ is available to be used by PCI/PnP devices. Reserved: Specified IRQ is reserved for use by Legacy ISA devices.

#### DMA Channel 0 - DMA Channel 7

Available: Specified DMA is available to be used by PCI/PnP devices. Reserved: Specified DMA is reserved for use by Legacy ISA devices.

#### **Reserved Memory Size**

Size of memory block to reserve for legacy ISA devices.

## 3.4 Boot Settings

#### **Boot Device Priority**

Press Enter and it shows Bootable add-in devices.

#### Hard Disk Drives

Press Enter and it shows Bootable and Hard Disk drives.

#### Removable Drives

Press Enter and it shows Bootable and Removable drives.

## 3.4.1 Boot Settings Configuration

#### **Quick Boot**

Allows BIOS to skip certain tests while booting. This will decrease the time needed to boot the system.

#### **Bootup Num-Lock**

Set this value to allow the Number Lock setting to be modified during boot up.

#### **LAN Boot Function**

Set this option to LAN add-on Boot ROM function.

## 3.5 Security

#### Supervisor Password & User Password

You can set either supervisor or user password, or both of then. The differences between are:

Set **Supervisor Password**: Can enter and change the options of the setup menus.

Set *User Password*: Just can only enter but do not have the right to change the options of the setup menus. When you select this function, the following message will appear at the center of the screen to assist you in creating a password.

#### ENTER PASSWORD:

Type the password, up to eight characters in length, and press <Enter>. The password typed now will clear any previously entered password from CMOS memory. You will be asked to confirm the password. Type the password again and press <Enter>. You may also press <ESC> to abort the selection and not enter a password.

To disable a password, just press <Enter> when you are prompted to enter the password. A message will confirm the password will be disabled. Once the password is disabled, the system will boot and you can enter Setup freely.

#### PASSWORD DISABLED.

When a password has been enabled, you will be prompted to enter it every time you try to enter Setup. This prevents an unauthorized person from changing any part of your system configuration.

Additionally, when a password is enabled, you can also require the BIOS to request a password every time your system is rebooted. This would prevent unauthorized use of your computer.

You determine when the password is required within the BIOS Features Setup Menu and its Security option. If the Security option is set to "System", the password will be required both at boot and at entry to Setup. If set to "Setup", prompting only occurs when trying to enter Setup.

#### **Boot Sector Virus Protection**

Enable/Disable Boot Sector Virus Protection.

## 3.6 Advanced Chipset Settings

## 3.6.1 North Bridge Chipset Configuration

#### **Boots Graphic Adapter Priority**

Select which graphics controller to use as the primary boot device.

#### **Internal Graphic Mode Select**

Select the amount of system memory used by the Internal graphics device.

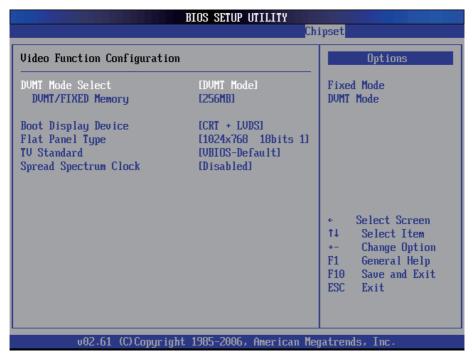

#### **Video Function Configuration**

#### **DVMT Mode Select**

The Choice: FIXED, DVMT (Default), Both.

## **DVMT/FIXED Memory**

The Choice: 64MB, 128MB (Default), 224MB.

#### **Boot Display**

The Choice: CRT + LVDS (Default).

## **Flat Panel Type**

It allows you to select the LCD Panel type as below ---

The Choice: 640x480

800x600

1024x768 18bits 1 (Default)

1280x1024 1400x1050 1400x1050 1600x1200 1280x768 1680x1050 1920x1200

#### **TV Standard**

The Choice: VBIOS-Default

#### **Spread Spectrum Clock**

It sets the value of the spread spectrum. It is for CE testing use only.

The Choice: Disabled (Default), Enabled.

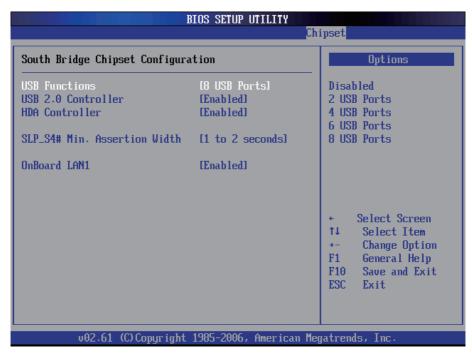

## 3.6.2 South Bridge Chipset Configuration

#### **USB Funtion**

This item allows you to active USB ports.

#### The Choice:

Disabled

2 USB Ports

4 USB Ports

6 USB Ports

8 USB Ports

10 USB Ports

#### **USB 2.0 Controller**

Select "Enabled" if your system contains a Universal Serial Bus 2.0 (USB 2.0) controller and you have USB peripherals.

The Choice: Enabled, Disabled.

#### **HDA Controller**

This item allows you to select the chipset family to support High Definition Audio Controller.

The Choice: Enabled, Disabled.

#### SLP\_S4# Min. Assertion Width

The item allows you to select the assertion width of SLP\_S4#. The Choice:

4 to 5 Seconds.

3 to 4 Seconds.

2 to 3 Seconds.

1 to 2 Seconds.

#### **Onboard LAN1**

Select "Enabled" if your system has a LAN device installed on the system board and you wish to use it.

The Choice: Enabled, Disabled.

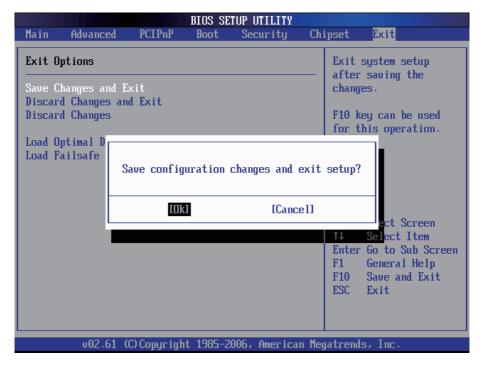

# 3.7 Exit Options

## Save Changes and Exit

Pressing <Enter> on this item asks for confirmation:

Save configuration changes and exit setup?

Pressing <OK> stores the selection made in the menus in CMOS - a special section of memory that stays on after you turn your system off. The next time you boot your computer, the BIOS configures your system according to the Setup selections stored in CMOS. After saving the values the system is restarted again.

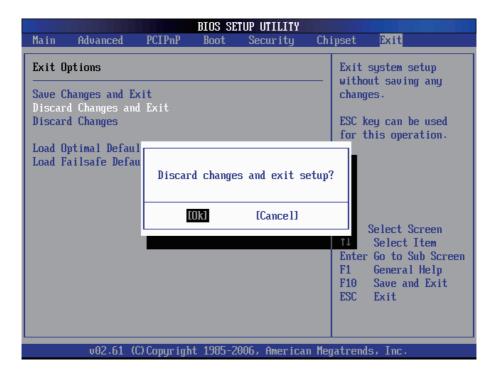

#### **Discard Changes and Exit**

Exit system setup without saving any changes. <ESC> key can be used for this operation.

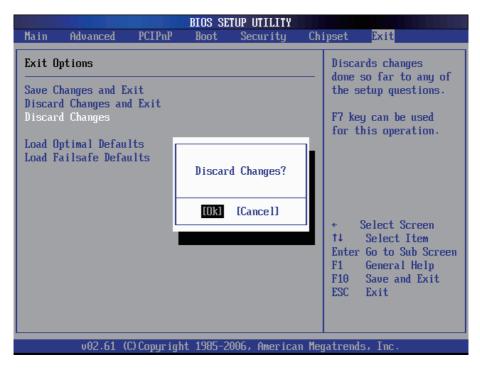

#### **Discard Changes**

Discards changes done so far to any of the setup questions. <F7> can be used for this operation.

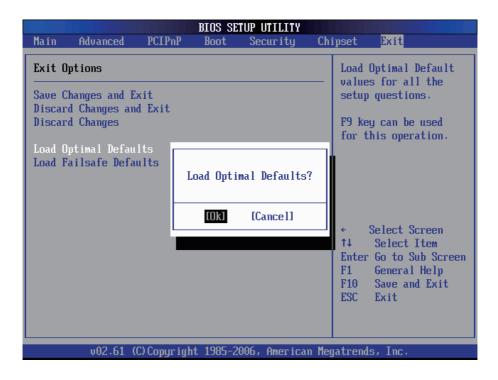

#### **Load Optimal Defaults**

When you press <Enter> on this item you get a confirmation dialog box with a message:

Load Optimal Defaults? [OK] [Cancel]

Pressing [OK] loads the BIOS Optimal Default values for all the setup questions.

<F9> key can be used for this operation.

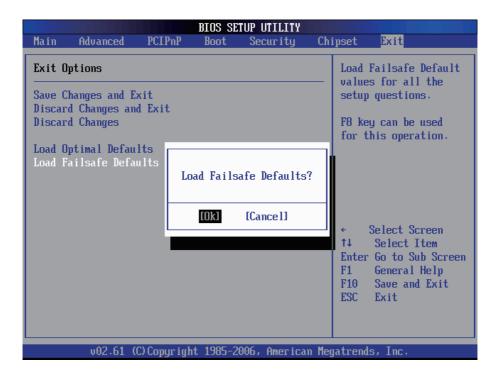

#### **Load Failsafe Defaults**

When you press <Enter> on this item you get a confirmation dialog box with a message:

Load Failsafe Defaults? [OK] [Cancel]

Pressing [OK] loads the BIOS Failsafe Default values for all the setup questions.

<F8> key can be used for this operation.

## 3.8 Beep Sound codes list

## 3.8.1 Boot Block Beep Codes

| Number of Beeps | Description                                                                        |

|-----------------|------------------------------------------------------------------------------------|

| 1               | Insert diskette in floppy drive A:                                                 |

| 2               | 'AMIBOOT.ROM' file not found in root directory of diskette in A:                   |

| 4               | Flash Programming successful                                                       |

| 5               | Floppy read error                                                                  |

| 6               | Keyboard controller BAT command failed                                             |

| 7               | No Flash EPROM detected                                                            |

| 8               | Floppy controller failure                                                          |

| 9               | Boot Block BIOS checksum error                                                     |

| 10              | Flash Erase error                                                                  |

| 11              | Flash Program error                                                                |

| 12              | 'AMIBOOT.ROM' file size error                                                      |

| 13              | BIOS ROM image mismatch (file layout does not match image present in flash device) |

## 3.8.2 POST BIOS Beep Codes

| Number of Beeps | Description                                                   |

|-----------------|---------------------------------------------------------------|

| 1               | Memory refresh timer error.                                   |

| 2               | Parity error in base memory (first 64KB block)                |

| 4               | Motherboard timer not operational                             |

| 5               | Processor error                                               |

| 6               | 8042 Gate A20 test error (cannot switch to protected mode)    |

| 7               | General exception error (processor exception interrupt error) |

| 8               | Display memory error (system video adapter)                   |

| 9               | AMIBIOS ROM checksum error                                    |

| 10              | CMOS shutdown register read/write error                       |

| 11              | Cache memory test failed                                      |

# 3.8.3 Troubleshooting POST BIOS Beep Codes

| Number of Beeps | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2 or 3       | Reseat the memory, or replace with known good modules.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4-7, 9-11       | Fatal error indicating a serious problem with the system. Consult your system manufacturer. Before declaring the motherboard beyond all hope, eliminate the possibility of interference by a malfunctioning add-in card. Remove all expansion cards except the video adapter.  • If beep codes are generated when all other expansion cards are absent, consult your system manufacturer's technical support.  • If beep codes are not generated when all other expansion cards are absent, one of the add-in cards is causing the malfunction. Insert the cards back into the system one at a time until the problem |

| 8               | If the system video adapter is an add-in card, replace or reset the video adapter. If the video adapter is an integrated part of the system board, the board may be faulty.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

## 3.9 AMI BIOS Checkpoints

## 3.9.1 Bootblock Initialization Code Checkpoints

The Bootblock initialization code sets up the chipset, memory and other components before system memory is available. The following table describes the type of checkpoints that may occur during the bootblock initialization portion of the BIOS (Note):

| Checkpoint | Description                                                                                                                                                                                                                                                                                     |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Before D0  | If boot block debugger is enabled, CPU cache-as-RAM functionality is enabled at this point. Stack will be enabled from this point.                                                                                                                                                              |

| D0         | Early Boot Strap Processo (BSP) initialization like microcode update, frequency and other CPU critical initialization. Early chipset initialization is done.                                                                                                                                    |

| D1         | Early super I/O initialization is done including RTC and keyboard controller. Serial port is enabled at this point if needed for debugging. NMI is disabled. Perform keyboard controller BAT test. Save power-on CPUID value in scratch CMOS. Go to flat mode with 4GB limit and GA20 enabled.  |

| D2         | Verify the boot block checksum. System will hang here if checksum is bad.                                                                                                                                                                                                                       |

| D3         | Disable CACHE before memory detection. Execute full memory sizing module. If memory sizing module is not executed, start memory refresh and do memory sizing in Boot block code. Do additional chipset initialization. Re-enable CACHE. Verify that flat mode is enabled.                       |

| D4         | Test base 512KB memory. Adjust policies and cache first 8MB. Set stack.                                                                                                                                                                                                                         |

| D5         | Bootblock code is copied from ROM to lower system memory and control is given to it. BIOS now executes out of RAM. Copy compressed boot block code to memory in right segments. Copy BIOS from ROM to RAM for faster access. Perform main BIOS checksum and update recovery status accordingly. |

| D6                 | Both key sequence and OEM specific method are checked to determine if BIOS recovery is forced. If BIOS recovery is necessary, control flows tocheckpoint E0. See <i>Bootblock Recovery Code Checkpoints</i> section of document for more information. |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7                 | Restore CPUID value back into register. The Bootblock-<br>Runtime interface module is moved to system memory and<br>control is given to it. Determine whether to execute serial<br>flash.                                                             |

| D8                 | The Runtime module is uncompressed into memory. CPUID information is stored in memory.                                                                                                                                                                |

| D9                 | Store the Uncompressed pointer for future use in PMM. Copying Main BIOS into memory. Leaves all RAM below 1MB Read-Write including E000 and F000 shadow areas but closing SMRAM.                                                                      |

| DA                 | Restore CPUID value back into register. Give control to BIOS POST (ExecutePOSTKernel). See POST Code Checkpoints section of document for more information.                                                                                            |

| DC                 | System is waking from ACPI S3 state                                                                                                                                                                                                                   |

| E1 - E8<br>EC - EE | OEM memory detection/configuration error. This range is reserved for chipset vendors & system manufacturers. The error associated with this value may be different from one platform to the next.                                                     |

## 3.9.2 Bootblock Recovery Code Checkpoints

The Bootblock recovery code gets control when the BIOS determines that a BIOS recovery needs to occur because the user has forced the update or the BIOS checksum is corrupt. The following table describes the type of checkpoints that may occur during the Bootblock recovery portion of the BIOS (Note):

| Checkpoint | Description                                                                                                                                                                              |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E0         | Initialize the floppy controller in the super I/O. Some interrupt vectors are initialized. DMA controller is initialized. 8259 interrupt controller is initialized. L1 cache is enabled. |

| E9         | Set up floppy controller and data. Attempt to read from floppy.                                                                                                                          |

| EA         | Enable ATAPI hardware. Attempt to read from ARMD and ATAPI CDROM.                                                                                                                        |

| EB         | Disable ATAPI hardware. Jump back to checkpoint E9.                                                                                                                                      |

| EF         | Read error occurred on media. Jump back to checkpoint EB.                                                                                                                                |

| F0         | Search for pre-defined recovery file name in root directory.                                                                                                                             |

| F1         | Recovery file not found.                                                                                                                                                                 |

| F2         | Start reading FAT table and analyze FAT to find the clusters occupied by the recovery file.                                                                                              |

| F3         | Start reading the recovery file cluster by cluster.                                                                                                                                      |

| F5         | Disable L1 cache.                                                                                                                                                                        |

| FA         | Check the validity of the recovery file configuration to the current configuration of the flash part.                                                                                    |

| FB         | Make flash write enabled through chipset and OEM specific method. Detect proper flash part. Verify that the found flash part size equals the recovery file size.                         |

| F4         | The recovery file size does not equal the found flash part size.                                                                                                                         |

| FC | Erase the flash part.                                                                                                                                                       |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FD | Program the flash part.                                                                                                                                                     |

| FF | The flash has been updated successfully. Make flash write disabled. Disable ATAPI hardware. Restore CPUID value back into register. Give control to F000 ROM at F000:FFF0h. |

## 3.9.3 POST Code Checkpoints

The POST code checkpoints are the largest set of checkpoints during the BIOS pre-boot process. The following table describes the type of checkpoints that may occur during the POST portion of the BIOS (Note):

| Checkpoint | Description                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 03         | Disable NMI, Parity, video for EGA, and DMA controllers. Initialize BIOS, POST, Runtime data area. Also initialize BIOS modules on POST entry and GPNV area. Initialized CMOS as mentioned in the Kernel Variable "wCMOSFlags."                                                                                                                                                                    |

| 04         | Check CMOS diagnostic byte to determine if battery power is OK and CMOS checksum is OK. Verify CMOS checksum manually by reading storage area. If the CMOS checksum is bad, update CMOS with power-on default values and clear passwords. Initialize status register A. Initializes data variables that are based on CMOS setup questions. Initializes both the 8259 compatible PICs in the system |

| 05         | Initializes the interrupt controlling hardware (generally PIC) and interrupt vector table.                                                                                                                                                                                                                                                                                                         |

| 06         | Do R/W test to CH-2 count reg. Initialize CH-0 as system timer.Install the POSTINT1Ch handler. Enable IRQ-0 in PIC for system timer interrupt. Traps INT1Ch vector to "POSTINT1ChHandlerBlock."                                                                                                                                                                                                    |

| 07         | Fixes CPU POST interface calling pointer.                                                                                                                                                                                                                                                                                                                                                          |

| 08         | Initializes the CPU. The BAT test is being done on KBC. Program the keyboard controller command byte is being done after Auto detection of KB/MS using AMI KB-5.                                                                                                                                                                                                                                   |

| C0         | Early CPU Init Start Disable Cache – Init Local APIC                                                                                                                                                                                                                                                                                                                                               |

| C1         | Set up boot strap processor Information                                                                                                                                                                                                                                                                                                                                                            |

| C2         | Set up boot strap processor for POST                                                                                                                                                                                                                                                                                                                                                               |

| C5         | Enumerate and set up application processors                                                                                                                                                                                                                                                                                                                                                        |

| C6         | Re-enable cache for boot strap processor                                                                                                                                                                                                                                                                                                                                                           |

|            |                                                                                                                                                                                                                                                                                                                                                                                                    |

| C7 | Early CPU Init Exit                                                                                                                                                                                                                              |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0A | Initializes the 8042 compatible Key Board Controller.                                                                                                                                                                                            |

| 0B | Detects the presence of PS/2 mouse.                                                                                                                                                                                                              |

| 0C | Detects the presence of Keyboard in KBC port.                                                                                                                                                                                                    |

| 0E | Testing and initialization of different Input Devices. Also, update the Kernel Variables. Traps the INT09h vector, so that the POST INT09h handler gets control for IRQ1. Uncompress all available language, BIOS logo, and Silent logo modules. |