# » Kontron User's Guide «

## PRELIMINARY

## **KTA75/Flex**

KTD-N0876-0

## » Table of Contents «

| 1          | Introduction 5                                                  |

|------------|-----------------------------------------------------------------|

| 2          | Installation Procedure 6                                        |

| 2.1        | Installing the Board6                                           |

| 2.2        | Requirements IEC609507                                          |

| 3          | System Specifications 8                                         |

| 3.1        | Component main data8                                            |

| 3.2        | KTA75/Flex Block Diagram14                                      |

| 3.3        | USB ports overview                                              |

| 4          | Connectors Locations 18                                         |

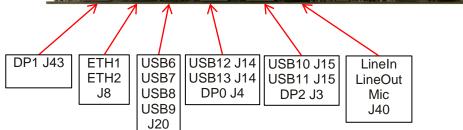

| 4.1        | KTA75/Flex Topview                                              |

| 5          | Connector Signal Definitions 19                                 |

| 6          | Rear IO Connectors 20                                           |

| 6.1        | DisplayPort (DP0/DP1/DP2) ( J3/J4/J44)                          |

| 6.2        | USB3.0 Connectors (USB10/USB11/USB12/USB13) (J15/J15/J14/J14)23 |

| 6.3        | Ethernet Connectors (ETH1/ETH2) (J8)25                          |

| 6.4        | USB x4 Stack Connector (USB6/USB7/USB8/USB9) (J20)26            |

| 6.5        | Audio Interface (J40)                                           |

| 7          | Pin Connectors 29                                               |

| 7.3        | Audio Header Connector (J41)                                    |

| 7.4        | USB4/5 Connector (J16)                                          |

| 7.5        | Jumper area (J34, J35, J36, J37)34                              |

| 7.6        | SPI Connector (J21)                                             |

| 7.7        | COM1/COM2 (J23/J22)                                             |

| 7.8        | LPC Connector (J29)                                             |

| 7.9        | Front Panel Connector (J5)                                      |

| 7.10       | CPU/System Fan Connectors (J25, J24)40                          |

| 7.11       | Feature Connector (J26)                                         |

| 7.12       | KBD/MSE (J27)                                                   |

| 8<br>msama | Slot Connectors (PCI-Express, miniPCIe, PCI, SATA,<br>A)        |

| 8.1        | PCIex16 (in x16 slot) (J7)                                      |

| 8.2        | PCIex4 (J6)                                                     |

| 8.3        | mPCIe connector (J38)                                           |

| 8.4        | mpcle connector (J38)                                           |

| 0.4        | MUSAIA/MILOTE CONNECTOR (043)                                   |

| 8.5         | PCI sl | ot conn | ectors | (J18 & | J28)  |         | • • • • • •     |           |     | •••• | ••••    | ••• | 53 |

|-------------|--------|---------|--------|--------|-------|---------|-----------------|-----------|-----|------|---------|-----|----|

| 8.6<br>J39) |        | SATA1,  | SATA2, | SATA3, | SATA4 | & SATAS | 5 (J12 <b>,</b> | J13,      | J9, | J11, | J10     | ŵ   |    |

| Apper       | ndix:  | Matin   | g Conr | nector | s     | •••••   | • • • • •       | • • • • • |     | •••• | • • • • | •   | 58 |

| Apper       | ndix:  | OS Se   | tup    | ••••   |       |         |                 |           |     |      |         | •   | 59 |

## Document Revision History

| Rev. | Date                      | Ву  | Comment                           |

|------|---------------------------|-----|-----------------------------------|

|      |                           |     |                                   |

| 0    | Mar 21 <sup>th</sup> 2013 | MLA | Preliminary version ofKTA75/Flex. |

## Copyright Notice

Copyright  $\ensuremath{\mathbb{C}}$  2013, KONTRON Technology A/S, ALL RIGHTS RESERVED.

No part of this document may be reproduced or transmitted in any form or by any means, electronically or mechani- cally, for any purpose without the express written permission of KONTRON Technology A/S.

#### KTA75/Flex Users Guide

## Trademark Acknowledgement

Brand and product names are trademarks or registered trademarks of their respective owners.

## Disclaimer

KONTRON Technology A/S reserves the right to make changes without notice to any product, including circuits and/or software described or contained in this manual in order to improve design and/or performance.

Specifications listed in this manual are subject to change without notice. KONTRON Technology assumes no responsibility or liability for the use of the described product(s), conveys no license or title under any patent, copyright or mask work rights to these products and makes no representations or warranties that these products are free from patent, copyright or mask work right infringement unless otherwise specified. Applications that are described in this manual are for illustration purposes only. KONTRON Technology A/S makes no representation or warranty that such application will be suitable for the specified use without further testing or modification.

### Life Support Policy

KONTRON Technology'S PRODUCTS ARE NOT FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT EXPRESS WRITTEN APPROVAL OF THE GENERAL MANAGER OF KONTRON Technology A/S.

#### As used herein:

Life support devices or systems are devices or systems which (a) are intended for surgical implant into body or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labelling can be reasonably expected to result in significant injury to the user.

A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

## KONTRON Technology Technical Support

If you have questions about installing or using your KONTRON Technology Product, then check this User's Manual first - you will find answers to most questions here. To obtain support please contact your local Kontron Sales Partner or Kontron Field Application Engineer (FAE).

**Before Contacting Support:** Please be prepared to provide as much information as possible:

• CPU Board

1. Type and P/N (Part Number), find label like:

Prod.code:A4Q S/N:

2.S/N (Serial Number), find label like:

- Configuration (if relevant)

- 1.CPU Type and Clock speed

- 2.DRAM Type and Size.

- 3.BIOS Revision (find the version info in the BIOS Setup Menu).4.BIOS Settings different than *Default* Settings.

- System (if relevant)

1.OS (Operating System) Make and Version.

2.Driver Version numbers: Graphics, Network, and Audio etc.

3.Attached Hardware: Harddisks, CD-Rom, Display Panels etc.

#### KTA75/Flex Users Guide

### Warranty

KONTRON Technology warrants its products to be free from defects in material and workmanship during the warranty period. If a product proves to be defective in material or workmanship during the warranty period KONTRON Technology will, at its sole option, repair or replace the product with a similar product.

Page 4

Replacement Product or parts may include remanufactured or refurbished parts or components.

#### The warranty does not cover:

1. Damage, deterioration or malfunction resulting from:

- A. Accident, misuse, neglect, fire, water, lightning or other acts of nature, unauthorized product modification or failure to follow instructions supplied with the product.

- B. Repair or attempted repair by anyone not authorized by KONTRON Technology.

- C. Causes external to the product, such as electric power fluctuations or failure.

- D. Normal wear and tear.

- E. Any other causes which does not relate to a product defect.

- 2.Removal, installation and set-up service charges.

#### Exclusion of damages:

KONTRON TECHNOLOGY LIABILITY IS LIMITED TO THE COST OF REPAIR OR REPLACEMENT OF THE PRODUCT. KONTRON TECHNOLOGY SHALL NOT BE LIABLE FOR:

1.DAMAGE TO OTHER PROPERTY CAUSED BY ANY DEFECTS IN THE PRODUCT, DAMAGES BASED UPON INCON- VENIENCE, LOSS OF USE OF THE PRODUCT, LOSS OF TIME, LOSS OF PROFITS, LOSS OF BUSINESS OPPORTUNITY, LOSS OF GOODWILL, INTERFERENCE WITH BUSINESS RELATIONSHIPS OR OTHER COMMERCIAL LOSS, EVEN IF ADVISED OF THEIR POSSIBILITY OF SUCH DAMAGES.

2. ANY OTHER DAMAGES, WHETHER INCIDENTAL, CONSEQUENTIAL OR OTHERWISE.

3. ANY CLAIM AGAINST THE CUSTOMER BY ANY OTHER PARTY.

## 1 Introduction

This manual describes the KTA75/Flex family of boards made by KONTRON Technology A/S. These board will also be denoted KTA75 within this Users Guide.

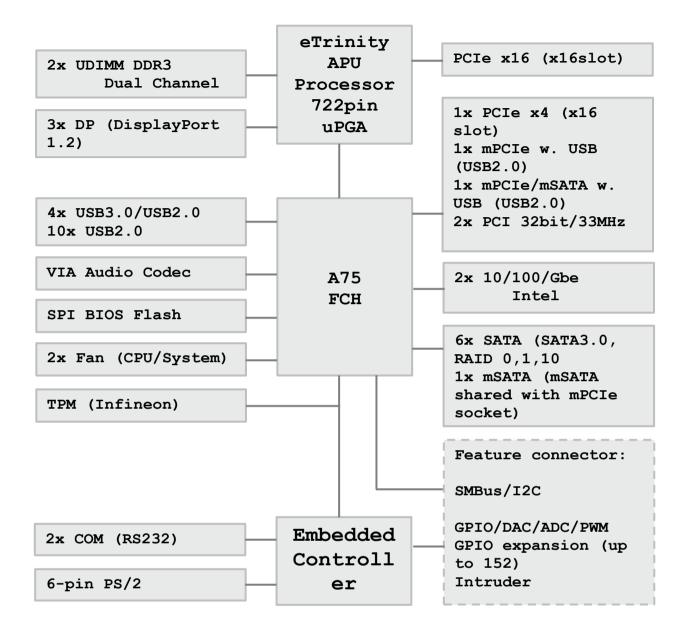

The KTA75 is designed to support the listed APU variants (uPGA 722pin processors) and AMD A75 Fusion Controller Hub (FCH) A75 on a Flex form factor. See the chapter *System Specifications* for more specific details.

| APU variants | AMD PN         | Processor data            |

|--------------|----------------|---------------------------|

| R-464L       | RE464LDEC44HJE | 2.3 GHz - Quad Core - 35W |

| R-460H       | RE460HDEC44HJE | 1.9 GHz - Quad Core - 35W |

| R-272F       | RE272FDEC23HJE | 2.7 GHz - Dual Core - 35W |

| R-268D       | RE268DDEC23HJE | 2.5 GHz - Dual Core - 35W |

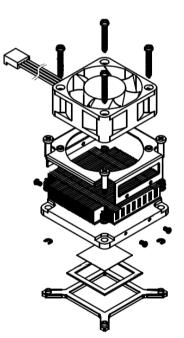

The 4 versions have the same type of active CPU cooler (the cooler is by default not premounted, but can be ordered with this obtion).

Use of this Users Guide implies a basic knowledge of PC-AT hard- and software. This manual is focused on describing the KTA75 board's special features and is not intended to be a standard PC-AT textbook.

New users are recommended to study the *Installation Procedure* stated in the following chapter before switching-on the power.

All configuration and setup of the CPU board is either done automatically or manually by the user via the BIOS setup menus. Only exceptions are the *Clear CMOS jumper* and the *Always On jumper*.

## 2 Installation Procedure

#### 2.1 Installing the Board

To get the board running, follow these steps. If the board shipped from KONTRON has already components like RAM mounted, then relevant steps below can be skipped.

#### 1. Turn off the PSU (Power Supply Unit)

Warning: Turn off PSU (Power Supply Unit) befor configuring the board and do not hot plug power supply, otherwise

#### 2. Insert the DDR3 UDIMM 240 Pin module(s)

Be careful to push it in the slot(s) before locking the tabs.

#### 3. Connecting Interfaces and PSU

Insert all external cables for hard disk, keyboard etc. A display/monitor must be connected in order to be able to change BIOS settings. Connect a standard ATX/BTX PSU to the board by the inserting power cables into 24-pin ATX and the 4-pin ATX+12V PWR plugs connectors.

#### 4. Power Button

Turn on mains power to the PSU. If board doesn't boot, then PWRBTN\_IN must be toggled; this is done by shorting pins 16 (PWRBTN\_IN) and pin 18 (GND) on the FRONTPNL connector (see Connector description), by use of a "normally open" switch etc.

#### 5. BIOS Setup

Enter the BIOS setup by pressing the <Del> key during boot up. Enter Exit Menu and Load Optimal Defaults. Refer to the "BIOS Configuration / Setup" section of this manual for details on BIOS setup.

Note: To clear all BIOS settings, including Password protection, activate *Clear CMOS* Jumper for ~10 sec (without power connected).

#### 6. Mounting the board to chassis

It is recommended using screws with integrated washer and having diameter of approx. 7mm.

Warning: please notice that the board contains components on both sides of the PCB which can easily be damaged if board is handled without reasonable care. A damaged component can result in malfunction or no function at all. Do not use

## Page 7

### 2.2 Requirements IEC60950

Users of KTA75 should take care when designing chassis interface connectors in order to fulfil the IEC60950 standard.

When an interface or connector has a VCC (or other power) pin which is directly connected to a power plane like the VCC plane: To protect the external power lines of the peripheral devices the customer has to take care about:

- That the wires have suitable rating to withstand the maximum available power.

- That the enclosure of the peripheral device fulfils the fire protecting requirements of IEC60950.

#### Lithium battery precautions

| CAUTION!                                                                                                                                                                                                                                             | VORSICHT!                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Danger of explosion if battery is<br>incorrectly re- placed. Replace only<br>with same or equivalent type<br>recommended by manufacturer. Dispose<br>of used batteries according to the<br>manufacturer's instruc- tions.                            | Explosionsgefahr bei unsachgemäßem<br>Austausch der Batterie. Ersatz nur<br>durch den selben oder einen vom<br>Hersteller empfohlenen gleichwertigen<br>Typ. Entsorgung gebrauchter Batterien<br>nach Anga- ben des Herstellers.           |

| ATTENTION!                                                                                                                                                                                                                                           | PRECAUCION!                                                                                                                                                                                                                                |

| Risque d'explosion avec l'échange<br>inadéquat de la batterie. Remplacement<br>seulement par le même ou un type<br>équivalent recommandé par le<br>producteur. L'évacuation des batteries<br>usagées conformément à des indications<br>du fabricant. | Peligro de explosión si la batería se<br>sustituye incorrectamente. Sustituya<br>solamente por el mismo o tipo<br>equivalente recomendado por el<br>fabricante. Disponga las baterías<br>usadas según las instrucciones del<br>fabricante. |

|                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                            |

| ADVARSEL!                                                                                                                                                                                                                                            | ADVARSEL!                                                                                                                                                                                                                                  |

| ADVARSEL!<br>Lithiumbatteri – Eksplosionsfare ved<br>fejlagtig håndtering. Udskiftning må<br>kun ske med batteri af samme fabrikat<br>og type. Levér det brugte batteri<br>tilbage til leverandøren.                                                 | ADVARSEL!<br>Eksplosjonsfare ved feilaktig skifte av<br>batteri. Benytt samme batteritype eller<br>en tilsvarende type anbefalt av<br>apparatfabrikanten. Brukte batterier<br>kasseres i henhold til fabrikantens<br>instruksjoner.        |

| Lithiumbatteri – Eksplosionsfare ved<br>fejlagtig håndtering. Udskiftning må<br>kun ske med batteri af samme fabrikat<br>og type. Levér det brugte batteri                                                                                           | Eksplosjonsfare ved feilaktig skifte av<br>batteri. Benytt samme batteritype eller<br>en tilsvarende type anbefalt av<br>apparatfabrikanten. Brukte batterier<br>kasseres i henhold til fabrikantens                                       |

KTA75/Flex Users Guide

## 3 System Specifications

## 3.1 Component main data

The table below summarizes the features of the KTA75/Flex embedded motherboards.

| Form    | Flex: 190,5 x 228,6 mm / 7,5 x 9,0"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| factor  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ocessor | <ul> <li>AMD eTrinity FP2 processor:</li> <li>Quad-Core 2.3 GHZ with R-464L APU 35W</li> <li>Quad Core 1.9 GHz with R-460H APU 35W</li> <li>Dual Core 2.7 GHz with R-272F APU 35W</li> <li>Dual Core 2.5 GHz with R-268D APU 35W</li> <li>Compatible with Existing 32-Bit x86 and 64-bit AMD64 Code Base</li> <li>AMD64 64-bit ISA</li> <li>High Performance Floating-Point Unit</li> <li>SSE 4.1 &amp; 4.2, AVX 1.0 &amp;1.1, AES, XOP, FMA4</li> <li>Secure advanced Virtualization Features</li> <li>64-bit DDR3 SDRAM Controller (1333MT/s, 666MHz): PC3-10600 / (1600MT/s, 800MHz): PC3-12800</li> <li>Compliant with JEDEC DDR3 1.5V and LV-DDR3 1.35V/1.25V SDRAM specification. Note:LV-DDR3 modules not validated</li> <li>PCIe@ Technology</li> <li>Integrated Memory Controller</li> <li>Integrated Graphics AMD Radeon™ HD 7000G Series graphics.</li> <li>Dedicated graphics memory controller</li> <li>2D Acceleration Features</li> <li>Open GL 4.2 &amp; 2.0</li> <li>DirectX® 11 compliant 3D Acceleration Features</li> <li>Adaptive Anti Aliasing, Shader Model 5</li> <li>Motion Video Acceleration Features</li> <li>Dedicated hardware (UVD 3) for H.264</li> <li>VC-1, DivX and MPEG2 decode</li> <li>HDCP (High-bandwidth Digital Content Protection) supported on DisplayPort Interface.</li> <li>Display Port 1.2</li> <li>Support DVI/HDMI via passive adapter.</li> </ul> |

KTD-N0876-0

#### Page 9

| Companion  | AMD A75 (Hudson)Fusion Controller Hub                          |

|------------|----------------------------------------------------------------|

| Device     | • Unified Media Interface (UMI) (5.0 GT/s)                     |

|            | • PCI Express® 2.0 Controller                                  |

|            | • PCI Host Bus Controller                                      |

|            |                                                                |

|            | • USB Controllers with up to 14 USB ports                      |

|            | • SMBus Controller                                             |

|            | <ul> <li>SATA Controller with RAID 0,1,10 support</li> </ul>   |

|            | High Definition Audio                                          |

|            | • Real Time Clock (RTC)                                        |

|            | • Integrated Clock controller                                  |

|            | • ACPI 3.0 compliant                                           |

|            | ACFI 5.0 COMPTIANC                                             |

|            |                                                                |

| Memory     | Memory controller is integrated in the AMD eTrinity FS1r2      |

|            | uPGA 722pin processor.                                         |

|            | Features are:                                                  |

|            | • Compliant with JEDEC DDR3 1.5V and (LV-DDR3 1.35V /          |

|            | 1.25 SDRAM, not verified) specifications                       |

|            | • Supports DDR3 UDIMM 240pin Using up to 8GB DRAM              |

|            | technology                                                     |

|            |                                                                |

|            | • DDR3 1333/1600MT/s (PC3-10600/PC3-12800)                     |

|            | <ul> <li>From 1GB to 2x 8GB maximum (16GB in total)</li> </ul> |

|            | Notes: Less than 4GB displayed in System                       |

|            | Properties using 32bit OS                                      |

|            | (Shared Video Memory/PCI                                       |

|            | resources is subtracted)                                       |

|            | ECC not supported                                              |

|            | Lee not supported                                              |

| TI h       | 20Mbit ODT Black for dual Quater DIOQ                          |

| Flash      | 32Mbit SPI Flash for dual System BIOS.                         |

| (BIOS)     |                                                                |

| Security   | Intel® Integrated TPM 1.2 support                              |

|            | Infineon TPM SLB9635TT1.2 (FW 3.17)                            |

|            |                                                                |

| IT8516E    | KT Feature Connector.                                          |

| Embedded   | 15 Multiplexed (GPIO, DAC, ADC, PWM & TIMER)                   |

| Controlle  | Possible 152 GPIO expansion.                                   |

|            | -                                                              |

| r          | Software Watchdog.                                             |

|            |                                                                |

| Audio      | Audio, 7.1 Channel High Definition Audio Codec using the       |

| Codec      | VIA VT1708S codec                                              |

|            |                                                                |

| Seriel     | 6x SATA port J9 - J13 & J39, SATA 3.0                          |

| ATA        | 1x mSATA J39 (mechanically sharing space with mPCIe slot       |

|            | J38), SATA 3.0                                                 |

|            | <ul> <li>RAID 0,1,10 support</li> </ul>                        |

| Exertisers |                                                                |

| Frontpane  | 2xUSB, HDD-LED, SYSRST#, SUSLED, PWRBTN#, AUDIO Line/MIC       |

| 1          | output.                                                        |

|            |                                                                |

| PCI        | 2x PCI slots (PCI Local Bus Specification revision 2.3         |

|            | 32bit/33MHz)                                                   |

|            |                                                                |

|            |                                                                |

|            |                                                                |

| PCIe<br>DisplayPo<br>rt | <pre>1x PCI Express x16 Slot<br/>1x PCI Express x4 Slot (in mechanically x16 slot)<br/>1x mPCIe Slot J38<br/>1x mPCIe/mSATA J43 (mechanically sharing between mSATA and<br/>mPCIe) The mSATA interface will be selected when a mSATA<br/>card are inserted into the mPCIe socket (J43)<br/>3x DisplayPort connector ( in REAR-IO area)<br/>DP1 J43<br/>DP2 J3<br/>DP0 J4<br/>Optionally Add-On card with 1x DisplayPort</pre> |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LVDS                    | Optionally Add-On card (TBD)                                                                                                                                                                                                                                                                                                                                                                                                  |

| Audio<br>Jack           | 3x Audiojacks stack J40 (in REAR-IO area)<br>Blue Line-In<br>Green Speaker<br>Pink Mic                                                                                                                                                                                                                                                                                                                                        |

| Audio                   | Audio Pin header J41<br>Line-out<br>Line-in<br>Surround output: SIDE, LFE, CEN, BACK and FRONT<br>Microphone: MIC1<br>SPDIF-OUT (electrical Interface only)                                                                                                                                                                                                                                                                   |

| LAN                     | <ul> <li>Two RJ45 connectors J8 (in REAR-IO area)</li> <li>2x 10/100/1000Mbits/s LAN (ETH1/ETH2) using Intel®<br/>Pearsonville xGB PCI Express Ethernet controller<br/>(WGI211ATSLJXZ).</li> <li>PXE Netboot supported.</li> <li>Wake On LAN (WOL) supported</li> </ul>                                                                                                                                                       |

| USB                     | <pre>14x USB ports (9x USB2.0 &amp; 4x USB2.0/USB3.0):<br/>2x USB2.0 in Frontpanel Connector J5<br/>2x USB2.0 in USB Internal USB Connector J16<br/>4x USB2.0, USB stack J20 (in REAR-IO area)<br/>2x USB 2.0/USB3.0, Right USB stack J14 ( in REAR-IO<br/>area)<br/>2x USB 2.0/USB3.0, left USB stack J15 (in REAR-IO<br/>area)<br/>1x USB 2.0 in mPCIe socket J38<br/>1x USB 2.0 in mSATA/mPCIe socket J43</pre>            |

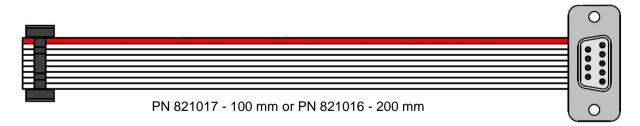

| Serial<br>port          | 2x RS232 pin header (+12V, -12V supply generated by driver<br>circuit)<br>COM1 2x 5 Pin row J23<br>COM2 2x 5 Pin row J22                                                                                                                                                                                                                                                                                                      |

| LPC                     | LPC connector J29                                                                                                                                                                                                                                                                                                                                                                                                             |

#### Page 11

| FAN            | CPUFAN 4 pin row J25 12V PWM<br>SYSFAN 4 pin row J24 12V PWM                                                                                                                                                                         |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

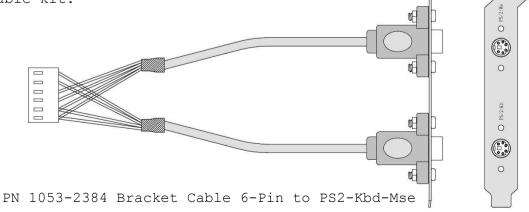

| PS2<br>Kbd/Mse | 1x 6 Pin row Keyboard / Mouse PS2 cable kit interface J27                                                                                                                                                                            |

| Power<br>Plug  | <pre>1x 4 pole Internal connector J19 ATX core power<br/>(+12V Single Supply , Max 260W)<br/>1x 24 pole connector J17 ATX/BTX power</pre>                                                                                            |

| Battery        | Exchangeable 3.0V Lithium battery for on-board Real Time Clock and CMOS RAM.                                                                                                                                                         |

|                | Manufacturer Panasonic / Part-number CR-2032L/BN,<br>CR2032N/BN or CR-2032L/BE.                                                                                                                                                      |

|                | Approximate 6 years retention.                                                                                                                                                                                                       |

|                | Current draw is 4 $\mu A$ when PSU is disconnected and 0 $\mu A$ in S0 - S5.                                                                                                                                                         |

|                | CAUTION: Danger of explosion if the battery is incorrectly<br>replaced. Replace only with the same or equivalent type<br>recommended by the manufacturer. Dispose of used batteries<br>according to the manufacturer's instructions. |

| Speaker        | On-board Speaker Piezo<br>On-board speaker (Electromagnetic Sound Generator like<br>Hycom HY-05LF)                                                                                                                                   |

| Entri nonme       | Operating                                                                                                                                                                                                                                                                               |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Environme<br>ntal | Operating:<br>0°C - 60°C operating temperature (forced cooling). It is<br>the customer's responsibility to provide sufficient<br>airflow around each of the components to keep them within<br>allowed temperature range.                                                                |

|                   | 10% - 90% relative humidity (non-condensing)                                                                                                                                                                                                                                            |

|                   | <pre>Storage:<br/>-20°C - 70°C; lower limit of storage temperature is defined<br/>by specification restriction of on-board CR2032 battery.<br/>Board with battery has been verified for storage<br/>temperature down to -40°C by Kontron.</pre>                                         |

|                   | 5% - 95% relative humidity (non-condensing)                                                                                                                                                                                                                                             |

|                   | Electro Static Discharge (ESD) / Radiated Emissions (EMI):<br>All Peripheral interfaces intended for connection to<br>external equipment are ESD/ EMI protected.<br>EN 61000-4-2:2000 ESD Immunity<br>EN55022:1998 class B Generic Emission Standard.                                   |

|                   | Safety:<br>EN 60950-1: 2006/ A11:2009/ A1:2010/A12:2011<br>IEC 60950-1(ed.2)<br>CSA C22.2 No. 60950-1<br>Product Category: Information Technology Equipment<br>Including Electrical Business Equipment<br>Product Category CCN: NWGQ2, NWGQ8<br>File number: E194252 (E194252-A21-CB-1) |

|                   | Theoretical MTBF:<br>314.614 / 153.436 hours @ 40°C / 60°C                                                                                                                                                                                                                              |

|                   | Restriction of Hazardous Substances (RoHS):<br>All boards in the KTA75 family are RoHS/RoHS-II compliant.                                                                                                                                                                               |

|                   | Capacitor utilization:<br>No Tantalum capacitors on board<br>Only Japanese brand Solid capacitors rated for 100 °C used<br>on board                                                                                                                                                     |

| BIOS              | AMI EFI<br>SPI Connector J21 (for BIOS Recovery)<br>Clear CMOS J34<br>Always On J37                                                                                                                                                                                                     |

| OS<br>(planned) | Windows 7 (32 and 64bit)<br>Windows 8 (32 and 64bit)<br>Windows XP (32 bit)<br>DOS |

|-----------------|------------------------------------------------------------------------------------|

|                 | Windows Embedded 7                                                                 |

### 3.2 KTA75/Flex Block Diagram

#### 3.3 USB ports overview

The KTA75 board contains two pairs of EHCI (Enhanced Host Controller Interface) and OHCI (Open Host Controller Interface) in order to support up to 10 USB1.1/USB2.0 devices and further more two xHCI (Extensible Host Controller Interface) to support up to 4 USB3.0 devices.

The OHCI controllers support USB1.1, Full-Speed (12Mbps) and Low-Speed (1.5Mbps).

The EHCI controllers support USB2.0, High-Speed (480Mbps).

The xHCI controllers support USB3.0, USB2.0 and USB 1.1, Super-Speed (5.0Gbps), High-Speed (480Mbps), Full-Speed (12Mbps) and Low-Speed (1.5Mbps)

Legacy Keyboard/Mouse and wakeup from sleep states are supported. Over-current detection on all USB ports except USB2.

| USB<br>#                     | USB standard             | Connector<br>location                         | HCI         | Note                            |

|------------------------------|--------------------------|-----------------------------------------------|-------------|---------------------------------|

| USBO<br>USB1                 | USB2.0 /USB1.1           | Frontpanel (J5)                               | OHCI1/EHCI1 |                                 |

| USB2                         | USB2.0 /USB1.1           | mPCIe (J38)                                   | OHCI1/EHCI1 | No over<br>current<br>detection |

| USB3                         | USB2.0 /USB1.1           | mSATA/mPCIe (J43)                             | OHCI1/EHCI1 | No over<br>current<br>detection |

| USB4                         | USB2.0 /USB1.1           | Pin row (J16)                                 | OHCI1/EHCI1 |                                 |

| USB5                         | USB2.0 /USB1.1           | Pin row (J16)                                 | OHCI2/EHCI2 |                                 |

| USB6<br>USB7<br>USB8<br>USB9 | USB2.0 /USB1.1           | USB quad stack<br>(J20)<br>Rear IO            | OHCI2/EHCI2 |                                 |

| USB1<br>0<br>USB1<br>1       | USB3.0/USB2.0/US<br>B1.1 | USB3.0 dual stack<br>(J15)<br>Left - Rear IO  | xHCI1       |                                 |

| USB1<br>2<br>USB1<br>3       | USB3.0/USB2.0/US<br>B1.1 | USB3.0 dual stack<br>(J14)<br>Right - Rear IO | xHCI2       |                                 |

Notes: In order to meet the requirements of USB standard, the 5V input supply must be at least 5.00V.

The contacts for USB devices are protected and suitable to supply USB devices with a maximum input current of 1000mA.

Do not supply external USB devices with higher power dissipation through these pinsTo protect the external power lines of peripheral devices make sure that - the wires have the right diameter to withstand the maximum available current.

- to enclosure of the peripheral device fulfills the fire-protecting conditions of IEC/EN 60950.

Page 17

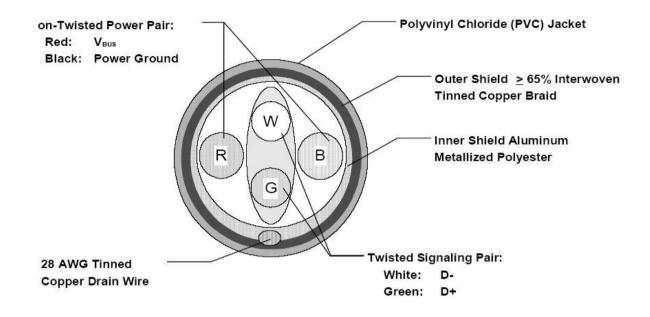

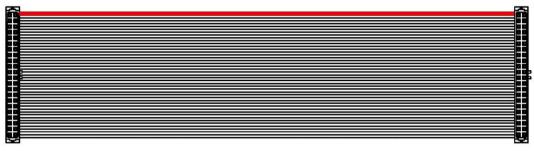

For USB2.0 cabling it is required to use only HiSpeed USB cable, specified in USB2.0 standard:

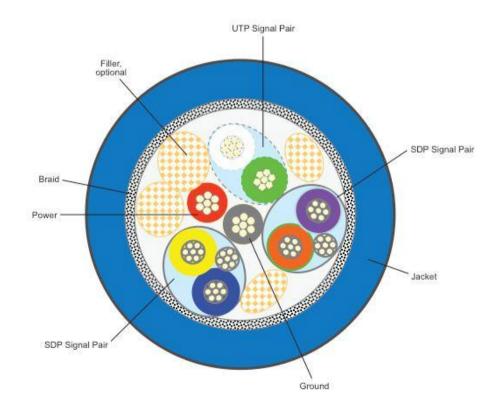

For USB3.0 cabling it is required to use only HiSpeed USB cable, specified in USB3.0 standard:

KTA75/Flex Users Guide

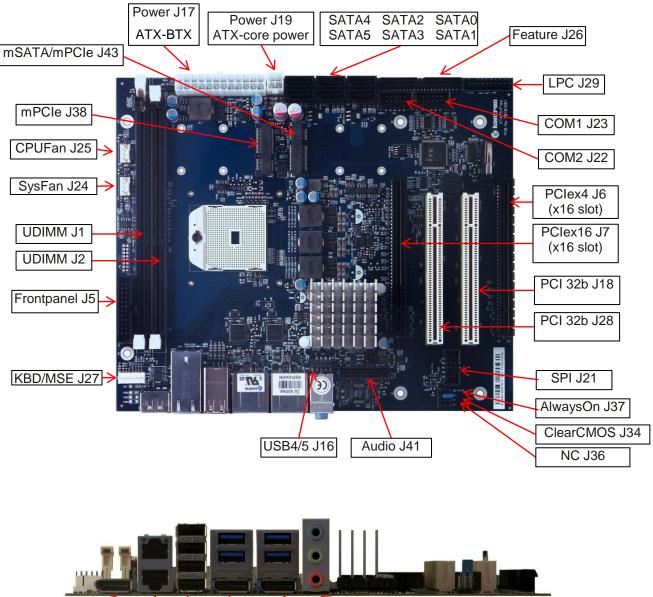

## 4 Connectors Locations

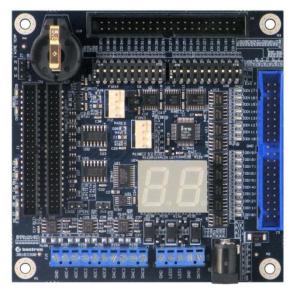

### 4.1 KTA75/Flex Topview

## 5 Connector Signal Definitions

The following sections provide pin definitions and detailed description of all onboard connectors.

The connector definitions follow the following notation:

| Column<br>Name | Description                                                                                                                    |  |  |  |  |  |  |  |  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Pin            | Shows the pin numbers in the connector.                                                                                        |  |  |  |  |  |  |  |  |

| Signal         | The mnemonic name of the signal at the current pin. The notation "#" states that the signal is active low.                     |  |  |  |  |  |  |  |  |

| Туре           | AI: <u>A</u> nalogue <u>I</u> nput                                                                                             |  |  |  |  |  |  |  |  |

|                | AO: <u>A</u> nalogue <u>O</u> utput                                                                                            |  |  |  |  |  |  |  |  |

|                | I: Digital <u>I</u> nput                                                                                                       |  |  |  |  |  |  |  |  |

|                | IO: Digital <u>I</u> nput / <u>O</u> utput                                                                                     |  |  |  |  |  |  |  |  |

|                | IOD: <u>I</u> nput / <u>O</u> pen <u>D</u> rain output                                                                         |  |  |  |  |  |  |  |  |

|                | 0: Digital <u>O</u> utput                                                                                                      |  |  |  |  |  |  |  |  |

|                | DSO: <u>D</u> ifferential <u>S</u> ignaling <u>O</u> utput with complementary                                                  |  |  |  |  |  |  |  |  |

|                | signals on two paired wires                                                                                                    |  |  |  |  |  |  |  |  |

|                | DSI: <u>D</u> ifferential <u>S</u> ignaling <u>I</u> nput with complementary                                                   |  |  |  |  |  |  |  |  |

|                | signals on two paired wires                                                                                                    |  |  |  |  |  |  |  |  |

|                | DSIO: <u>D</u> ifferential <u>S</u> ignaling <u>I</u> nput / <u>O</u> utput (combined DSO and DSI)                             |  |  |  |  |  |  |  |  |

|                | PWR: <u>PoWeR</u> supply or ground reference pins                                                                              |  |  |  |  |  |  |  |  |

|                | NC: Pin <u>N</u> ot <u>C</u> onnected                                                                                          |  |  |  |  |  |  |  |  |

|                | Additional notations:                                                                                                          |  |  |  |  |  |  |  |  |

|                | -5.0 +5.0V signal voltage level, e.g. I-5.0                                                                                    |  |  |  |  |  |  |  |  |

|                | -3.3 +3.3V signal voltage level, e.g. 0-3.3                                                                                    |  |  |  |  |  |  |  |  |

|                | -1.8 +1.8V signal voltage level, e.g. IO-1.8                                                                                   |  |  |  |  |  |  |  |  |

| Ioh/Iol        | Ioh: Typical current in mA flowing out of an output pin<br>through a grounded load while the output voltage has high<br>level. |  |  |  |  |  |  |  |  |

|                | Iol: Typical current in mA flowing into an output pin from a VCC connected load while the output voltage has low level.        |  |  |  |  |  |  |  |  |

The abbreviation tbd is used for specifications which are not available yet or which are not sufficiently specified by the component vendors.

## 6 Rear IO Connectors

## 6.1 DisplayPort (DP0/DP1/DP2) ( J3/J4/J44)

The DP (DisplayPort) connectors are based on standard DP type Foxconn 3VD11203-H7AB-4H or similar.

|    | 1<br>9 | 1<br>7 | 1<br>5 | 1<br>3 | 1      | 9 7 | 5   | 3 1 |

|----|--------|--------|--------|--------|--------|-----|-----|-----|

| 20 | 1<br>8 | 1<br>6 | 1<br>4 | 1<br>2 | 1<br>0 | 8   | 6 4 | 2   |

| Pin | Signal        | Description                      | Туре | Note                                                                                                                                                   |

|-----|---------------|----------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Lane 0<br>(p) |                                  | LVDS |                                                                                                                                                        |

| 2   | GND           |                                  | PWR  |                                                                                                                                                        |

| 3   | Lane O<br>(n) |                                  | LVDS |                                                                                                                                                        |

| 4   | Lane 1<br>(p) |                                  | LVDS |                                                                                                                                                        |

| 5   | GND           |                                  | PWR  |                                                                                                                                                        |

| 6   | Lane 1<br>(n) |                                  | LVDS |                                                                                                                                                        |

| 7   | Lane 2<br>(p) |                                  | LVDS |                                                                                                                                                        |

| 8   | GND           |                                  | PWR  |                                                                                                                                                        |

| 9   | Lane 2<br>(n) |                                  | LVDS |                                                                                                                                                        |

| 10  | Lane 3<br>(p) |                                  | LVDS |                                                                                                                                                        |

| 11  | GND           |                                  | PWR  |                                                                                                                                                        |

| 12  | Lane 3<br>(n) |                                  | LVDS |                                                                                                                                                        |

| 13  | Config1       | Aux or DDC<br>selection          | I    | Internally pull down (1Mohm).<br>Aux channel on pin 15/17 selected as<br>default (when NC)<br>DDC channel on pin 15/17, If HDMI<br>adapter used (3.3V) |

| 14  | Config2       | (Not used)                       | 0    | Internally connected to GND                                                                                                                            |

| 15  | Aux Ch<br>(p) | Aux Channel<br>(+) or DDC<br>Clk |      | AUX (+) channel used by DP<br>DDC Clk used by HDMI                                                                                                     |

| 16  | GND           |                                  | PWR  |                                                                                                                                                        |

| 17 | Aux Ch<br>(n) | Aux Channel<br>(-) or DDC<br>Data |     | AUX (-) channel used by DP<br>DDC Data used by HDMI      |

|----|---------------|-----------------------------------|-----|----------------------------------------------------------|

| 18 | Hot<br>Plug   |                                   | I   | Internally pull down (100Kohm).                          |

| 19 | Return        |                                   | PWR | Same as GND                                              |

| 20 | 3.3V          |                                   | PWR | Fused by 1.5A resetable PTC fuse, common for DPO and DP1 |

| Note: To protect the external power lines of peripheral devices make sure that  |

|---------------------------------------------------------------------------------|

| - the wires have the right diameter to withstand the maximum available current. |

| - to enclosure of the peripheral device fulfills the fire-protecting conditions |

| of IEC/EN 60950.                                                                |

The 3 DisplayPorts (DP0, DP1 and DP2) can be used in 3 independt display configurations. By use of DP Adapter Converters it is possible to implement a mix of DP, VGA, HDMI and DVI-D outputs and still support 3 independt display configuration.

Available DP adapters:

DP to VGA PN 1045-5779

DP to HDMI PN 1045-5781

DP to DVI-D PN 1045-5780

DP Extention Cable:

In order to prevent mechanical conflicts the above DP adapters can be connected to DP#0, DP#1 and DP#2 via the 1051-7619 Cable DP Extender cable 200mm.

The DP to VGA adapter is an "active" converter, meaning that seen from the graphics controller it looks like a DP. The HDMI and DVI converters are passive converters, meaning that they inform the graphics controller about its type and the graphics controller then replace the DP signals with TMDS signals (used in HDMI and DVI).

The HDMI interface supports the HDMI 1.4a specification including audio codec. Limitations to the resolution apply: 2048x1536 (VGA), 1920x1200 (HDMI and DVI).

4 independt (simultaneously) displays (without using PCIe Graphics cards) is a possible configuration under the following conditions:

- 1. A PCIe-DP passive card must be used in the outermost PCIe slot.

- 2. All DP must be converted to DP-DVI-D or DP-HDMI via passive adapters like above adapters. (Restriction, only one adapter can be HDMI type)

- 3. Two of the panels must have the same timing (meaning two display monitors have to be exact same type).

#### 6.2 USB3.0 Connectors (USB10/USB11/USB12/USB13) (J15/J15/J14/J14)

The USB3.0 connectors are based on standard USB3.0 connectors type Lotes ABA-USB-104-K01 or similar.

Thease 4 USB3.0 ports are controlled by the xHCI controllers supporting USB3.0, USB2.0 and USB 1.1, Super-Speed (5.0Gbps), High-Speed (480Mbps), Full-Speed (12Mbps) and Low-Speed (1.5Mbps)

USB Ports 10 and 11 (mounted on top of the DP#2 port):

| Note | Туре     | Signal  | I     | PIN    | 1    |     | Signal | Туре  | Note |

|------|----------|---------|-------|--------|------|-----|--------|-------|------|

|      | DSIO-3.3 | U       | τ     | USB10+ |      |     | DSIO-  |       |      |

|      |          |         |       |        |      |     |        | 3.3   |      |

| 1    | PWR      | 5V/SB5V | 1 2   |        | 3    | 4 ( | GND    | PWR   |      |

|      | DSIO-3.3 | RX10- 5 | 6     | 7      | 8    | 9   | TX10+  | DSIO- |      |

|      |          |         |       |        |      |     |        | 3.3   |      |

|      | DSIO-3.3 | RX      | K10+  |        | ΤX   | 10- |        | DSIO- |      |

|      |          |         |       |        |      |     |        | 3.3   |      |

|      | PWR      |         | 0     | SNE    | )    |     |        |       |      |

|      |          |         |       |        |      |     |        |       |      |

|      | DSIO-3.3 | U       | SB11- | τ      | JSB: | 11+ |        | DSIO- |      |

|      |          |         |       |        |      |     |        | 3.3   |      |

| 1    | PWR      | 5V/SB5V | 1 2   |        | 3    | 4 ( | GND    | PWR   |      |

|      | DSIO-3.3 | RX11- 5 | 6     | 7      | 8    | 9   | TX11+  | DSIO- |      |

|      |          |         |       |        |      |     |        | 3.3   |      |

|      | DSIO-3.3 | RX      | K11+  |        | ΤX   | 11- |        | DSIO- |      |

|      |          |         |       |        |      |     |        | 3.3   |      |

|      | PWR      |         | 0     | GNE    | )    |     |        |       |      |

| Signal                          | Description                                                                                                                                                                   |  |  |  |  |  |  |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| USB10+<br>USB10-<br>RX10+ RX10- |                                                                                                                                                                               |  |  |  |  |  |  |

| TX10+ TX10-                     | Differential pair works as Data (Address (Command Bus                                                                                                                         |  |  |  |  |  |  |

| USB11+<br>USB11-                | Differential pair works as Data/Address/Command Bus.                                                                                                                          |  |  |  |  |  |  |

| RX11+ RX11-                     |                                                                                                                                                                               |  |  |  |  |  |  |

| TX11+ TX11-                     |                                                                                                                                                                               |  |  |  |  |  |  |

| 5V/SB5V                         | 5V supply for external device. SB5V is supplied during powerdown to allow wakeup on device activity. Protected by current limited power distribution switch,1A for each port. |  |  |  |  |  |  |

USB Ports 12 and 13 (mounted on top of the DP#0 port):

| Note | Туре     | Signal P |       |     | I      |      | Signal | Туре  | Note |

|------|----------|----------|-------|-----|--------|------|--------|-------|------|

|      | DSIO-3.3 | USB12-   |       |     | USB12+ |      |        | DSIO- |      |

|      |          |          |       |     |        |      |        | 3.3   |      |

| 1    | PWR      | 5V/SB5V  | 1 2   |     | 3      | 4    | GND    | PWR   |      |

|      | DSIO-3.3 | RX12- 5  | 56    | 7   | 8      | 9    | TX12+  | DSIO- |      |

|      |          |          |       |     |        |      |        | 3.3   |      |

|      | DSIO-3.3 | R        | X12+  |     | ТΣ     | K12- | -      | DSIO- |      |

|      |          |          |       |     |        |      |        | 3.3   |      |

|      | PWR      |          | 0     | GNE | )      |      |        |       |      |

|      |          |          |       |     |        |      |        |       |      |

|      | DSIO-3.3 | U        | SB13- | Ţ   | JSB    | 13+  |        | DSIO- |      |

|      |          |          |       |     |        |      |        | 3.3   |      |

| 1    | PWR      | 5V/SB5V  | 1 2   |     | 3      | 4    | GND    | PWR   |      |

|      | DSIO-3.3 | RX13- 5  | 56    | 7   | 8      | 9    | TX13+  | DSIO- |      |

|      |          |          |       |     |        |      |        | 3.3   |      |

|      | IO       | R        | X13+  |     | TΣ     | K13- | -      | DSIO- |      |

|      |          |          |       |     |        |      |        | 3.3   |      |

|      | PWR      |          | 0     | GNE | )      |      |        |       |      |

| Signal                                                                                                                | Description                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB12+<br>USB12-<br>RX12+<br>RX12-<br>TX12+<br>TX12-<br>USB13+<br>USB13-<br>RX13+<br>RX13-<br>TX13+<br>TX13+<br>TX13- | Differential pair works as Data/Address/Command Bus.                                                                                                                                   |

| 5V/SB5V                                                                                                               | 5V supply for external device. SB5V is supplied during<br>powerdown to allow wakeup on device activity. Protected<br>by current limited power distribution switch,1A for each<br>port. |

Notes: In order to meet the requirements of USB standard, the 5V input supply must be at least 5.00V.

The contacts for USB devices are protected and suitable to supply USB devices with a maximum input current of 1000mA.

Do not supply external USB devices with higher power dissipation through these pinsTo protect the external power lines of peripheral devices make sure that - the wires have the right diameter to withstand the maximum available current.

- to enclosure of the peripheral device fulfills the fire-protecting conditions of IEC/EN 60950.

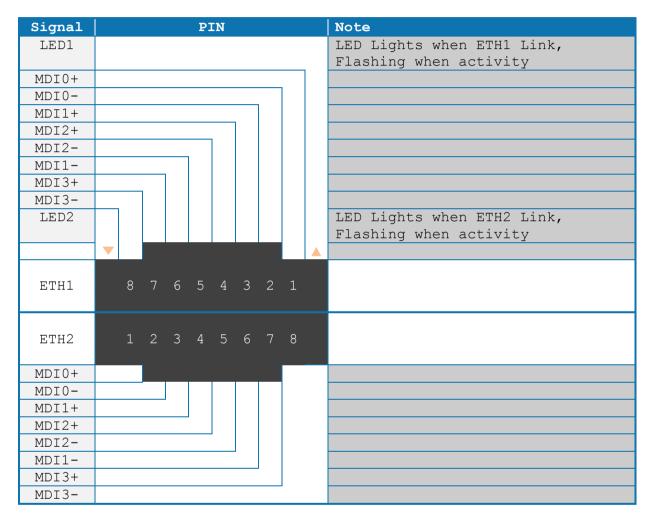

### 6.3 Ethernet Connectors (ETH1/ETH2) (J8)

The KTA75 supports two 10/100/1000Mb Ethernet RJ45 connetors in a stacked dual LAN connector, type Ude RMT-123AGF1F or sililar. Both ports are driven by Intel® Pearsonville WGI211AT PCI Express controller.

Ethernet connector 1 (ETH1) is mounted above Ethernet connector 2 (ETH2).

In order to achieve the specified performance of the Ethernet port, Category 5 twisted pair cables must be used with 10/100MB and Category 5E, 6 or 6E with 1Gb LAN networks.

| Signal       | Description                                                                                                                                                                                      |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MDI[0]+      | <pre>MDI mode: first pair in 1000Base-T (i.e. the BI_DA+/- pair),<br/>transmit pair in 10/100Base-T.<br/>MDI crossover mode: acts as the BI_DB+/- pair, receive pair<br/>in 10/100Base-TX.</pre> |

|              | 111 10/100Base=1A.                                                                                                                                                                               |

| MDI[1]+<br>/ | MDI mode: second pair in 1000Base-T (i.e. the BI_DB+/- pair), receive pair in 10/100Base-T.                                                                                                      |

| MDI[1]-                 | MDI crossover mode: acts as the BI_DA+/- pair, transmit pair in 10/100Base-T.                                   |

|-------------------------|-----------------------------------------------------------------------------------------------------------------|

|                         | MDI mode: third pair in 1000Base-T (i.e. the BI_DC+/- pair).<br>MDI crossover mode: acts as the BI_DD+/- pair.  |

| MDI[3]+<br>/<br>MDI[3]- | MDI mode: fourth pair in 1000Base-T (i.e. the BI_DD+/- pair).<br>MDI crossover mode: acts as the BI_DC+/- pair. |

Note: MDI = Media Dependent Interface.

### 6.4 USB x4 Stack Connector (USB6/USB7/USB8/USB9) (J20)

USB Ports 6, 7, 8 and 9 are mounted in a single stack in the IO Area type Foxconn UB11123-Q8DF-4F or similar. The USB ports are controlled by a single set of OHCI and EHCI controllers (also shared by USB5).

The OHCI controllers support USB1.1, Full-Speed (12Mbps) and Low-Speed (1.5Mbps).

The EHCI controllers support USB2.0, High-Speed (480Mbps).

| Note | Туре     | Signal  | PIN |   |   | Signal | Туре  | Note     |  |

|------|----------|---------|-----|---|---|--------|-------|----------|--|

|      | PWR      | 5V/SB5V | 1   | 2 | 3 | 4      | GND   | PWR      |  |

|      | DSIO-3.3 | USB6-   |     |   |   |        | USB6+ | DSIO-3.3 |  |

|      |          |         |     |   |   |        |       |          |  |

|      | PWR      | 5V/SB5V | 1   | 2 | 3 | 4      | GND   | PWR      |  |

|      | DSIO-3.3 | USB7-   |     |   |   |        | USB7+ | DSIO-3.3 |  |

|      |          |         |     |   |   |        |       |          |  |

|      | PWR      | 5V/SB5V | 1   | 2 | 3 | 4      | GND   | PWR      |  |

|      | DSIO-3.3 | USB8-   |     |   |   |        | USB8+ | DSIO-3.3 |  |

|      |          |         |     |   |   |        |       |          |  |

|      | PWR      | 5V/SB5V | 1   | 2 | 3 | 4      | GND   | PWR      |  |

|      | DSIO-3.3 | USB9-   |     |   |   |        | USB9+ | DSIO-3.3 |  |

| Signal                     | Description                                                                                                                                           |  |  |  |  |  |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| USB6+ USB6-<br>USB7+ USB7- | Differential pair works as Data/Address/Command Bus.                                                                                                  |  |  |  |  |  |

| USB8+ USB8-<br>USB9+ USB9- | billelenetat patt works as baca/Address/command bus.                                                                                                  |  |  |  |  |  |

| 5V/SB5V                    | 5V supply for external devices. SB5V is supplied during powerdown to allow wakeup on USB device activity. Protected by individual resettable 1A fuse. |  |  |  |  |  |

Notes: In order to meet the requirements of USB standard, the 5V input supply must be at least 5.00V.

The contacts for USB devices are protected and suitable to supply USB devices with a maximum input current of 1000mA.

Do not supply external USB devices with higher power dissipation through these

#### KTA75/Flex Users Guide

pinsTo protect the external power lines of peripheral devices make sure that - the wires have the right diameter to withstand the maximum available current.

- to enclosure of the peripheral device fulfills the fire-protecting conditions of IEC/EN 60950.

### 6.5 Audio Interface (J40)

The on-board Audio circuit, based on Via VT1708S, implements 7.1+2 Channel High Definition Audio with UAA (Universal Audio Architecture), featuring five 24-bit stereo DACs and three 20-bit stereo ADCs. The Following Audio connector is available in IO Area.

Audio Speakers, Line-in and Microphone are available in the stacked audiojack connector type Lotes ABA-JAK-028-K03

|        | Signal      | Туре | Note |

|--------|-------------|------|------|

|        |             |      |      |

| TIP    | LINE1-L     | IA   |      |

| RING   | LINE1-R     | IA   |      |

| SLEEVE | GND         | PWR  |      |

|        |             |      |      |

| TIP    | FRONT-OUT-L | OA   |      |

| RING   | FRONT-OUT-R | OA   |      |

| SLEEVE | GND         | PWR  |      |

|        |             |      |      |

| TIP    | MIC1-L      | IA   |      |

| RING   | MIC1-R      | IA   |      |

| SLEEVE | GND         | PWR  |      |

|        |             |      |      |

| Signal      | Description                            | Note                     |

|-------------|----------------------------------------|--------------------------|

| FRONT-OUT-L | Front Speakers (Speaker<br>Out Left).  |                          |

| FRONT-OUT-R | Front Speakers (Speaker<br>Out Right). |                          |

| MIC1-L      | Microphone 1 - Left                    | Shared with Audio Header |

| MIC1-R      | Microphone 1 - Right                   | Shared with Audio Header |

| LINE1-L     | Line 1 signal - Left                   | Shared with Audio Header |

| LINE1-R     | Line 1 signal - Right                  | Shared with Audio Header |

### 7 Pin Connectors

#### 7.1 DC Power ATX-BTX Connector (J17)

The KTA75 boards are designed to be supplied from a standard ATX (or BTX) power supply. Use of BTX supply is not required for operation, but may be required to drive high-power PCIe cards.

| Header | Note | Туре | Signal | P  | EN | Signal | Туре | Note |

|--------|------|------|--------|----|----|--------|------|------|

|        |      | PWR  | 3V3    | 12 | 24 | GND    | PWR  |      |

| 200%   |      | PWR  | +12V   | 11 | 23 | 5V     | PWR  |      |

|        |      | PWR  | +12V   | 10 | 22 | 5V     | PWR  |      |

| 밑밀     |      | PWR  | SB5V   | 9  | 21 | 5V     | PWR  |      |

|        |      | I    | P_OK   | 8  | 20 | -5V    | PWR  | 1    |

|        |      | PWR  | GND    | 7  | 19 | GND    | PWR  |      |

|        |      | PWR  | 5V     | 6  | 18 | GND    | PWR  |      |

|        |      | PWR  | GND    | 5  | 17 | GND    | PWR  |      |

|        |      | PWR  | 5V     | 4  | 16 | PSON#  | OC   |      |

|        |      | PWR  | GND    | 3  | 15 | GND    | PWR  |      |

| -002   |      | PWR  | 3V3    | 2  | 14 | -12V   | PWR  |      |

|        |      | PWR  | 3V3    | 1  | 13 | 3V3    | PWR  |      |

ATX-BTX Power Connector (J17):

Note 1: -5V supply is not used on-board.

See chapter "Power Consumption" regarding input tolerances on 3.3V, 5V, SB5V, +12 and -12V (also refer to ATX specification version 2.2).

| Signal | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P_OK   | P_OK is a power good signal and should be asserted high by the power supply<br>to indicate that the +5VDC and +3.3VDC outputs are above the undervoltage<br>thresholds of the power supply. When this signal is asserted high, there<br>should be sufficient energy stored by the converter to guarantee continuous<br>power operation within specification. Conversely, when the output voltages<br>fall below the undervoltage threshold, or when mains power has been removed<br>for a time sufficiently long so that power supply operation is no longer<br>guaranteed, P_OK should be de-asserted to a low state. The recommended<br>electrical and timing characteristics of the P_OK (PWR_OK) signal are<br>provided in the ATX12V Power SupplyDesign Guide. |

|        | It is strongly recommended to use an ATX or BTX supply in order to implement the supervision of the 5V and 3V3 supplies. These supplies are not supervised on-board.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PS_ON# | Active low open drain signal from the board to the power supply to turn on the power supply outputs. Signal must be pulled high by the power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

### 7.2 DC Power Internal Connector (J19)

The KTA75/Flex has an internal power input connector for supplying voltage in the range from +11.4V to +12.6V. The power connector is a 4 pin 12V ATX connector type Lotes ABA-POW-003-K02 or similar.

| Header | Pin | Signal | Description          |

|--------|-----|--------|----------------------|

|        | 1   | GND    | Ground               |

|        | 2   | GND    | Ground               |

| 2 1    | 3   | 12V    | Power supply<br>+12V |

|        | 4   | 12V    | Power supply<br>+12V |

Warning: Hot Plugging power supply is not supported. Hot plugging might damage the board.

**Note 1:** Use of the 4-pin ATX+12V Power Connector is required for operation of all KTQ67 board versions.

Notes: To protect the external power lines of peripheral devices make sure that - the wires have the right diameter to withstand the maximum available current. - to enclosure of the peripheral device fulfills the fireprotecting conditions of IEC/EN 60950. Alternatively the DC Power External Connector can be used

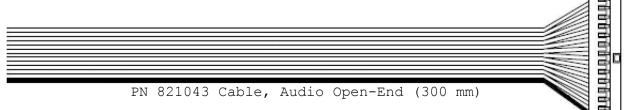

## 7.3 Audio Header Connector (J41)

The Audio Header connector is a 26 pin connector type Molex  $87832\mathchar`-2620$  or similar.

| Note | Туре | Signal      | PIN |    | Signal      | Туре | Note |

|------|------|-------------|-----|----|-------------|------|------|

|      | AO   | LFE-OUT     | 1   | 2  | CEN-OUT     | AO   |      |

|      | PWR  | AAGND       | 3   | 4  | AAGND       | PWR  |      |

| 1    | AO   | FRONT-OUT-L | 5   | 6  | FRONT-OUT-R | AO   | 1    |

|      | PWR  | AAGND       | 7   | 8  | AAGND       | PWR  |      |

|      | AO   | REAR-OUT-L  | 9   | 10 | REAR-OUT-R  | AO   |      |

|      | AO   | SIDE-OUT-L  | 11  | 12 | SIDE-OUT-R  | AO   |      |

|      | PWR  | AAGND       | 13  | 14 | AAGND       | PWR  |      |

| 1    | AI   | MIC1-L      | 15  | 16 | MIC1-R      | AI   | 1    |

|      | PWR  | AAGND       | 17  | 18 | AAGND       | PWR  |      |

| 1    |      | LINE1-L     | 19  | 20 | LINE1-R     |      | 1    |

|      | NC   | NC          | 21  | 22 | AAGND       | PWR  |      |

|      | PWR  | GND         | 23  | 24 | NC          | NC   |      |

|      | 0    | SPDIF-OUT   | 25  | 26 | GND         | PWR  |      |

Note 1: Shared with Audio Stack connector (in Rear IO area).

| Signal      | Description                               |

|-------------|-------------------------------------------|

| FRONT-OUT-L | Front Speakers (Speaker Out Left).        |

| FRONT-OUT-R | Front Speakers (Speaker Out Right).       |

| REAR-OUT-L  | Rear Speakers (Surround Out Left).        |

| REAR-OUT-R  | Rear Speakers (Surround Out Right).       |

| SIDE-OUT-L  | Side speakers (Surround Out Left)         |

| SIDE-OUT-R  | Side speakers (Surround Out Right)        |

| CEN-OUT     | Center Speaker (Center Out channel).      |

| LFE-OUT     | Subwoofer Speaker (Low Freq. Effect Out). |

| NC          | No connection                             |

| MIC1        | MIC Input 1                               |

| LINE1       | Line 1 signals                            |

| F-SPDIF-OUT | S/PDIF Output                             |

| AAGND       | Audio Analogue ground                     |

Available cable kit:

### 7.4 USB4/5 Connector (J16)

USB Ports 4 and 5 are available via Pin Row connector type Foxconn  $\rm HS1105F\text{-}RNP9$  or similar.

The USB4 port is controlled by a set of OHCI and EHCI controllers (also shared by USB0/1/2). The USB5 port is controlled by a set of OHCI and EHCI controllers (also shared by USB6/7/8/9).

The OHCI controllers support USB1.1, Full-Speed (12Mbps) and Low-Speed (1.5Mbps). The EHCI controllers support USB2.0, High-Speed (480Mbps).

| Header | Pin                                                    | Signa<br>1  | Description                                          | Туре         |

|--------|--------------------------------------------------------|-------------|------------------------------------------------------|--------------|

| 1002   | 1                                                      | 5V/SB<br>5V | 5V (always) protected by separate 1A resettable fuse | PWR          |

|        | 2                                                      | 5V/SB<br>5V | 5V (always) protected by separate 1A resettable fuse | PWR          |

|        | 3                                                      | USB4-       | Differential pair 4 -                                | DSIO-<br>3.3 |

|        | 4                                                      | USB5-       | Differential pair 5 -                                | DSIO-<br>3.3 |

|        | 5USB4+Differential pair 4 +6USB4+Differential pair 5 + |             | DSIO-<br>3.3                                         |              |

|        |                                                        |             | DSIO-<br>3.3                                         |              |

|        | 7                                                      | GND         | Ground                                               | PWR          |

|        | 8                                                      | GND         | Ground                                               | PWR          |

|        | -                                                      |             | (pin not mounted -Used for keying)                   |              |

|        | 10                                                     | KEY         |                                                      | NC           |

Notes: In order to meet the requirements of USB standard, the 5V input supply must be at least 5.00V.