# Describing Synthesizable RTL in SystemC

Version 1.0, May 2001

# **Trademarks and Copyright**

Synopsys and CoCentric are a registered trademarks of Synopsys, Inc. with further information at http://synopsys.com.

All other product or company names may be trademarks of their respective owners.

Copyright © 2001 Synopsys, Inc.

# Contents

|    | About This Guide                                                                                 | ×                        |

|----|--------------------------------------------------------------------------------------------------|--------------------------|

|    | SystemC Training                                                                                 | Xi                       |

|    | Information About Synopsys SystemC Synthesis Products                                            | хi                       |

| 1. | SystemC RTL Synthesis Overview                                                                   |                          |

|    | System-Level Design                                                                              | 1-2                      |

|    | System-Level Design Challenges                                                                   | 1-2<br>1-2               |

|    | Tool Interoperability                                                                            | 1-3<br>1-3               |

|    | SystemC                                                                                          | 1-4                      |

|    | Why Synthesis From SystemC?  Interpretation Errors.  Verification Reuse  Increased Productivity. | 1-5<br>1-5<br>1-6<br>1-6 |

|    | About This Manual                                                                                | 1-7                      |

# 2. Creating SystemC Modules for RTL Synthesis

| Defining Modules and Processes     | 2-2  |

|------------------------------------|------|

| Modules                            | 2-2  |

| Processes                          | 2-3  |

| Registering a Process              | 2-3  |

| Triggering Execution of a Process  | 2-4  |

| Reading and Writing Processes      | 2-4  |

| Types of Processes                 | 2-4  |

| Creating a Module                  | 2-5  |

| Module Header File                 | 2-5  |

| Module Syntax                      | 2-6  |

| Module Ports                       | 2-6  |

| Port Syntax                        | 2-7  |

| Port Data Types                    | 2-8  |

| Signals                            | 2-8  |

| Signal Syntax                      | 2-9  |

| Signal Data Types                  | 2-9  |

| Data Member Variables              | 2-10 |

| Creating a Process in a Module     | 2-11 |

| Defining the Sensitivity List      | 2-12 |

| Defining a Level-Sensitive Process | 2-12 |

| Incomplete Sensitivity Lists       | 2-13 |

| Defining an Edge-Sensitive Process | 2-13 |

| Limitations for Sensitivity Lists  | 2-14 |

| Member Functions                   | 2-15 |

| Module Constructor                 | 2-15 |

| Implementing the Module            | 2-15 |

|      | Reading and Writing Ports and Signals              | 2-16 |

|------|----------------------------------------------------|------|

|      | Reading and Writing Bits of Ports and Signals      | 2-16 |

|      | Signal and Port Assignments                        | 2-17 |

|      | Variable Assignment                                | 2-18 |

| С    | reating a Module With a Single SC_METHOD Process   | 2-20 |

| С    | reating a Module With Multiple SC_METHOD Processes | 2-22 |

| С    | reating a Hierarchical RTL Module                  | 2-26 |

|      | The Basics of Hierarchical Module Creation         | 2-26 |

|      | Hierarchical RTL Module Example                    | 2-28 |

| 3. U | sing the Synthesizable Subset                      |      |

| С    | converting to a Synthesizable Subset               | 3-2  |

|      | SystemC and C++ Synthesizable Subsets              | 3-2  |

|      | Nonsynthesizable SystemC Constructs                | 3-3  |

|      | Nonsynthesizable C/C++ Constructs                  | 3-4  |

| R    | efining Data                                       | 3-7  |

|      | Nonsynthesizable Data Types                        | 3-8  |

|      | Recommended Data Types for Synthesis               | 3-8  |

|      | Using SystemC Data Types                           | 3-11 |

|      | Bit Vector Data Type Operators                     | 3-11 |

|      | Fixed and Arbitrary Precision Data Type Operators  | 3-12 |

|      | Using Enumerated Data Types                        | 3-13 |

|      | Using Aggregate Data Types                         | 3-13 |

|      | Using C++ Data Types                               | 3-13 |

|      | Data Members of a Module                           | 3-14 |

|    | Recommendations About Refinement for Synthesis      | 3-16 |

|----|-----------------------------------------------------|------|

| 4. | RTL Coding Guidelines                               |      |

|    | Register Inference                                  | 4-2  |

|    | Flip-Flop Inference                                 | 4-2  |

|    | Simple D Flip-flop                                  | 4-2  |

|    | D Flip-Flop With an Active-High Asynchronous Set or |      |

|    | Reset                                               | 4-4  |

|    | D Flip-Flop With an Active-Low Asynchronous Set or  |      |

|    | Reset                                               | 4-5  |

|    | D Flip-Flop With Synchronous Set or Reset           | 4-8  |

|    | Inferring JK Flip-Flops                             | 4-10 |

|    | Inferring Toggle Flip-Flops                         | 4-13 |

|    | Latch Inference                                     | 4-16 |

|    | Inferring a D Latch From an If Statement            | 4-16 |

|    | Inferring an SR Latch                               | 4-17 |

|    | Avoiding Latch Inference                            | 4-19 |

|    | Inferring a Latch From a Switch Statement           | 4-21 |

|    | Active-Low Set and Reset                            | 4-25 |

|    | Active-High Set and Reset                           | 4-27 |

|    | D Latch With an Asynchronous Set and Reset          | 4-28 |

|    | D Latch With an Asynchronous Set                    | 4-29 |

|    | D Latch With an Asynchronous Reset                  | 4-30 |

|    | Three-State Inference                               | 4-32 |

|    | Simple Three-State Inference                        | 4-32 |

|    | Registered Three-State Drivers                      | 4-34 |

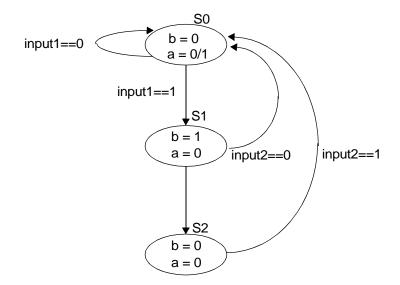

| State Machines                                    | <br>4-37 |

|---------------------------------------------------|----------|

| State Machine With a Common Computation Process   | <br>4-39 |

| State Machine With Separate Computation Processes | <br>4-41 |

| Moore State Machine                               | 4-43     |

# **Preface**

This preface includes the following sections:

- About This Guide

- SystemC Training

- Information About Synopsys SystemC Synthesis Products

# **About This Guide**

The *Describing Synthesizable RTL in SystemC* describes how to develop a SystemC RTL model for synthesis.

For information about SystemC, see the Open SystemC Community web site at http://www.systemc.org.

#### **Related Publications**

For information about the SystemC language and syntax, see the SystemC User's Manual available from the Open SystemC Community web site at http://www.systemc.org.

#### **Comments About This Document**

E-mail your comments about this document to techpubs-sld@synopsys.com.

# **Typographical Conventions**

Courier font is used in this document to distinguish SystemC code examples.

# **SystemC Training**

For information about SystemC training and private workshops, contact

Willamette HDL

http://www.whdl.com

Three-day SystemC for High-Level Synthesis

Three-day Modeling With SystemC

Transfer

http://www.transfer.nt

Three-day Modeling With SystemC

Fraunhofer IIS-A

http://www.iis.fhg.de

Three-day SystemC Training Classes

Doulos

Five-day Comprehensive SystemC Training Class

http://www.doulos.com

• Blue Pacific Computing

http://www.bluepc.com

Three-Day SystemC Workshop

# **Information About Synopsys SystemC Synthesis Products**

For information about Synopsys SystemC synthesis products, contact your local Synopsys sales office or

- Go to the Synopsys Web page at http://www.synopsys.com

- In the Synopsys Products field, choose CoCentric™ SystemC Compiler

1

# SystemC RTL Synthesis Overview

This chapter describes how RTL synthesis from SystemC fits into the system-level design flow. It contains the following sections:

- System-Level Design

- System-Level Design Challenges

- SystemC

- Why Synthesis From SystemC?

# **System-Level Design**

System-level design involves specifying the system, verifying its functionality, and determining optimum system architecture by evaluating design alternatives. Today's complex systems have significant software content and are integrated into a system on a chip (SoC).

System-level design can help with the growing complexity of both the hardware and software. An effective system-level design strategy minimizes late design iterations and increases design team productivity, which enables you to deliver a high quality product on time.

# **System-Level Design Challenges**

Developing an effective system-level design strategy presents several challenges that can be solved by using SystemC.

# **Component Integration**

Component reuse is a widely implemented strategy for handling complexity, but many of the components are provided from various sources.

Because component models are written in different languages and styles, integrating the models into the system design is often so difficult the system designers avoid doing it, eliminating the important task of specification and functional verification.

# **Tool Interoperability**

Although system modeling tools are available, each tool uses a proprietary model format, which makes a model developed for one tool unsuitable for use with another tool. This lack of tool interoperability and model compatibility also prevents using more than one tool in a design flow.

# **Design Team Collaboration**

During system architecture design, designers choose the processor(s), bus, and peripherals, and decide what to implement in hardware and software. Effective architecture design requires participation of the hardware and software design teams for creating models and influencing architectural decisions, which is called hardware-software co-design. Furthermore, as the hardware and software design teams participate in architecture design concurrently, communication and consensus is reached early in the design cycle. The results of this collaboration must be validated and corrections can be made early in the design cycle. This prevents surprises when the hardware and software are integrated much later in the design cycle. To further complicate the situation, the system designers, hardware designers, and software engineers often apply different design languages. A common design language is needed to increase understanding, communication, and productivity, and to bring these teams together during the system architecture design phase.

# **SystemC**

SystemC is the foundation for design tools and methodologies that address the above mentioned the system-level design challenges of tool interoperability, team communication, and component model creation and distribution.

SystemC is based on C++, the most popular language with system designers and software engineers. The SystemC classes add the necessary constructs to C++ for modeling systems and hardware at various levels of abstraction—from the abstract untimed models to cycle-accurate RTL models. The software content of the system can be written in C++, without the need for additional constructs.

SystemC, by itself, solves only a few of the system-level design challenges. You can use SystemC for creating an executable specification to verify the system functionality and architecture, but analysis and architecture design tools are needed and IP vendors need to provide SystemC models.

The power of SystemC is that it can be used as a common language by system designers, software engineers, and hardware designers. SystemC allows exchange of IP models, creation of an interoperable tool infrastructure, and development of a concept-to-implementation design methodology. The same benefits derived from the standardization of Verilog and VHDL in RTL design can now be achieved in the system design space with SystemC.

# Why Synthesis From SystemC?

Hardware design has the well-established Verilog and VHDL hardware description languages with tools and design flows based on them. Why should you bother to understand how to use SystemC, a system design language, for hardware design and synthesis?

Consider a scenario where a system designer has created an architectural model of a SoC in SystemC and you are a hardware designer. The architectural model contains a variety of models, including processor models, abstract bus models, and peripheral models. The peripheral models capture the full functionality and interface of the peripherals, although at a high level of abstraction. This allows the system designer to hand you the peripheral models as an executable specification, along with written requirements for the area, speed, and power consumption for the peripherals.

# **Interpretation Errors**

You need to implement the peripherals and verify the implementation in the context of the entire system. If you use a Verilog or VHDL synthesis tool, you need to rewrite the peripheral models in Verilog or VHDL, which is a time-consuming and error-prone process. Or you can synthesize the peripheral models from SystemC. Instead of throwing away the work done at the system level and recoding the design, you can take the abstract, non-synthesizable peripheral models and refine them into synthesizable models.

# **Verification Reuse**

As an added advantage, you can use the system-level verification environment to check the correctness of your implementation as you refine it.

# **Increased Productivity**

If a hardware designer receives a SystemC executable specification, implementation from SystemC gives higher designer productivity than recoding it in Verilog or VHDL. Higher designer productivity comes from two sources—refinement is faster than recoding, and verifying a refined design is faster than verifying a recoded HDL design.

Refinement is faster than recoding, because hardware functionality is envisioned as either an algorithm or a finite state machine and data path, even if the description is abstract. Algorithmic models can be synthesized using behavioral synthesis techniques, and finite state machines and data paths can be synthesized by using RTL synthesis techniques. The primary refinement tasks are staying within the synthesizable subset and adding the implementation details and the hardware structure that were not included in the abstract model. You can reduce the refinement effort by ensuring that the system designer minimizes violations in the abstract model.

Verifying a refined SystemC design is faster than verifying a recoded HDL design, because refinement changes fewer lines of code and has fewer opportunities to introduce interpretation mistakes. Therefore, you typically spend less time debugging and verifying the hardware design.

Design engineers can achieve greater productivity by refining a SystemC executable specification. Design teams can fully deploy the productivity of system-level design by using a SystemC synthesis tool that supports both behavioral and RTL styles. This designer productivity improvement can reduce time-to-market.

# **About This Manual**

As with VHDL and Verilog, SystemC has modeling rules and a synthesizable subset of those rules. This manual describes the modeling rules and synthesizable subset for describing RTL in SystemC.

# 2

# Creating SystemC Modules for RTL Synthesis

This chapter explains the SystemC and C/C++ language elements that are important for RTL synthesis. It contains the following sections:

- Defining Modules and Processes

- Creating a Module

- Creating a Module With a Single SC\_METHOD Process

- Creating a Module With Multiple SC\_METHOD Processes

- Creating a Hierarchical RTL Module

# **Defining Modules and Processes**

This modeling guide explains how to develop SystemC RTL modules for synthesis. It assumes that you are knowledgeable about the C/C++ language and the SystemC Class Library available from the Open SystemC Community Web site at http://www.systemc.org.

#### **Modules**

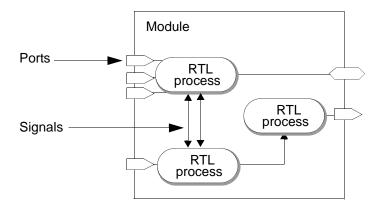

The basic building block in SystemC is the module. A SystemC module is a container in which processes and other modules are instantiated. A typical module can have

- Single or multiple RTL processes to specify combinational or sequential logic

- Multiple RTL modules to specify hierarchy

- One or more member functions that are called from within an instantiated process or module

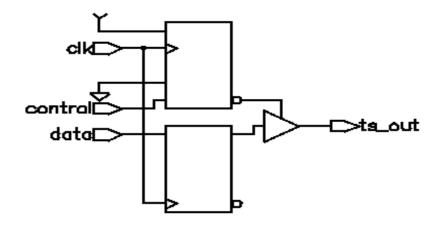

Figure 2-1 shows a module with several RTL processes. The processes within a module are concurrent, and they execute whenever one of their sensitive inputs changes.

Figure 2-1 Module

#### **Processes**

SystemC provides processes to describe the parallel behavior of hardware systems. This means processes execute concurrently rather than sequentially like C++ functions. The code within a process, however, executes sequentially.

# **Registering a Process**

Defining a process is similar to defining a C++ function. A process is declared as a member function of a module class and registered as a process in the module's constructor. Registering a process means that it is recognized as a SystemC process rather than as an ordinary member function.

You can register multiple different processes, but it is an error to register more than one instance of the same process. To create multiple instances of the same process, enclose the process in a module and instantiate the module multiple times.

# **Triggering Execution of a Process**

You define a sensitivity list that identifies which input ports and signals trigger execution of the code within a process. You can define level-sensitive inputs to specify combinational logic or edge-sensitive inputs to specify sequential logic.

# **Reading and Writing Processes**

A process can read from and write to ports, internal signals, and internal variables.

Processes use signals to communicate with each other. One process can cause another process to execute by assigning a new value to a signal that interconnects them. Do not use data variables for communication between processes, because the processes execute in random order and it can cause nondeterminism (order dependencies) during simulation.

# **Types of Processes**

SystemC provides three process types—SC\_METHOD, SC\_CTHREAD, and SC\_THREAD—that execute whenever their sensitive inputs change. For simulation, you can use any of the process types. For RTL synthesis, you can use only the SC\_METHOD process.

The SC\_METHOD process is sensitive to either changes in signal values (level-sensitive) or to particular transitions (edges) of the signal (edge-sensitive) and executes when one of its sensitive inputs changes.

# **Creating a Module**

It is a recommended coding practice to describe a module by using a separate header file (*module\_name*.h) and an implementation file (*module\_name*.cpp or *module\_name*.cc).

#### **Module Header File**

Each module header file contains

- Port declarations

- Internal signal variable declarations

- Internal data variable declarations

- Process declarations

- Member function declarations

- Module constructor

# **Module Syntax**

Declare a module, using the syntax shown in bold in the following example:

SC\_MODULE and SC\_CTOR are C++ macros defined in the SystemC Class library.

### **Module Ports**

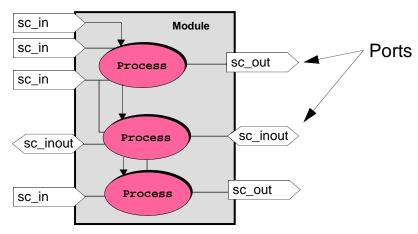

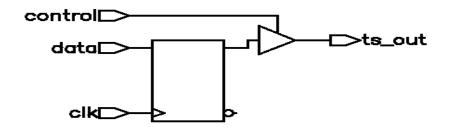

Each module has any number of input, outputs, and inout ports (see Figure 2-2), which determine the direction of data into or out of the module.

Figure 2-2 Module Ports

A port is a data member of SC\_MODULE. You can declare any number of sc\_in, sc\_out, and sc\_inout ports. To read from an output port, declare it as an sc\_inout rather than an sc\_out port.

# **Port Syntax**

Declare ports by using the syntax shown in bold in the following example:

# **Port Data Types**

Ports connect to signals and have a data type associated with them. For synthesis, declare each port as one of the synthesizable data types described in "Converting to a Synthesizable Subset" on page 3-2.

# **Signals**

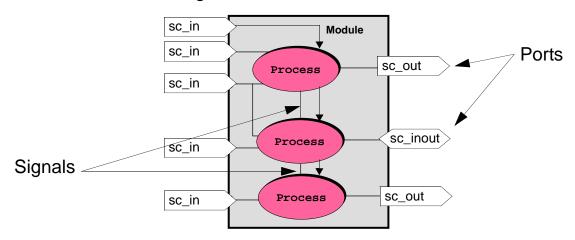

Modules use ports to communicate with other modules. In hierarchical modules, use signals to communicate between the ports of instantiated modules. Use internal signals for peer-to-peer communication between processes within the same module, as shown in Figure 2-3.

Figure 2-3 Processes and Signals

# **Signal Syntax**

Declare signals by using the syntax shown in bold in the following example:

```

SC_MODULE (module_name) {

//Module port declarations

sc_in<port_type> port_name;

sc_out<port_type> port_name;

sc_in<port_type>port_name;

//Internal signal variable declarations

sc_signal<signal_type> signal_name;

sc_signal<signal_type> signal1, signal2;

//Data variable declarations

//Process declarations

//Member function declarations

//Module constructor

SC_CTOR (module_name) {

//Register processes

//Declare sensitivity list

};

```

# **Signal Data Types**

A signal's bit-width is determined by its corresponding data type. Specify the data type as any of the synthesizable SystemC or C++ data types listed in "Converting to a Synthesizable Subset" on page 3-2. Signals and the ports they connect must have the same data types.

#### **Data Member Variables**

Inside a module, you can define data member variables of any synthesizable SystemC or C++ type. These variables can be used for internal storage in the module. Recommendations about using data member variables for synthesis are provided in "Data Members of a Module" on page 3-14. Declare internal data variables by using the syntax shown in bold in the following example:

```

SC MODULE (module name) {

//Module port declarations

sc_in<port_type> port_name;

sc_out<port_type> port_name;

sc_in port_name;

//Internal signal variable declarations

sc_signal<signal_type> signal_name;

//Data member variable declarations

int count_val;

//Internal counter

sc_int<8> mem[1024]; //Array of sc_int

//Process declarations

//Member function declaration

//Module constructor

SC CTOR (module name) {

//Register processes

//Declare sensitivity list

};

```

#### Note:

Do not use data variables for peer-to-peer communication in a module. This can cause pre- and post-synthesis simulation mismatches and nondeterminism (order dependency) in your design.

# **Creating a Process in a Module**

SystemC processes are declared in the module body and registered as processes inside the constructor of the module, as shown in bold in Example 2-1.

You must declare a process with a return type of void and no arguments, which is also shown in bold in Example 2-1.

To register a function as an SC\_METHOD process, you need to use the SC\_METHOD macro that is defined in the SystemC class library. The SC\_METHOD macro takes one argument, the name of the process.

#### Example 2-1 Creating a Method Process in a Module

```

SC_MODULE(my_module) {

// Ports

sc in<int> a;

sc in<bool> b;

sc out<int> x;

sc_out<int> y;

// Internal signals

sc_signal<bool>c;

sc_signal<int> d;

// process declaration

void my method proc();

// module constructor

SC_CTOR(my_module) {

// register process

SC_METHOD(my_method_proc);

// Define the sensitivity list

};

```

# **Defining the Sensitivity List**

An SC\_METHOD process reacts to a set of signals called its sensitivity list. You can use the sensitive(), sensitive\_pos(), or sensitive\_neg() functions or the sensitive, sensitive\_pos, or sensitive\_neg streams in the sensitivity declaration list.

# **Defining a Level-Sensitive Process**

For combinational logic, define a sensitivity list that includes all input ports, inout ports, and signals used as inputs to the process. Use the sensitive method to define the level-sensitive inputs. Example 2-2 shows in bold a stream-type declaration and a function-type declaration. Specify any number of sensitive inputs for the stream-type declaration, and specify only one sensitive input for the function-type declaration. You can call the sensitive function multiple times with different inputs.

# Example 2-2 Defining a Level-Sensitive Sensitivity List

```

SC_MODULE(my_module) {

// Ports

sc in<int> a;

sc in<bool> b;

sc out<int> x;

sc_out<int> y;

// Internal signals

sc_signal<bool>c;

sc signal<int> d;

sc_signal<int> e;

// process declaration

void my method proc();

// module constructor

SC_CTOR(my_module) {

// register process

SC METHOD(my method proc);

// declare level-sensitive sensitivity list

sensitive << a << c << d; // Stream declaration</pre>

```

```

sensitive(b); //Function declaration

sensitive(e); //Function declaration

}

};

```

# **Incomplete Sensitivity Lists**

To eliminate the risk of pre- and post-synthesis simulation mismatches, include all the inputs to the combinational logic process in the sensitivity list of the method process. Example 2-3 shows an incomplete sensitivity list.

#### Example 2-3 Incomplete Sensitivity List

```

//method process

void comb_proc () {

out_x = in_a & in_b & in_c;

}

SC_CTOR( comb_logic_complete ) {

// Register method process

SC_METHOD( comb_proc);

sensitive << in_a << in_b; // missing in_c

}</pre>

```

# **Defining an Edge-Sensitive Process**

For sequential logic, define a sensitivity list of the input ports and signals that trigger the process. Use the sensitive\_pos, sensitive\_neg, or both the sensitive\_pos and sensitive\_neg methods to define the edge-sensitive inputs that trigger the process. Declare ports and the edge-sensitive inputs as type sc\_in<book\_income sensitive inputs.

Define the sensitivity list by using either the function or the stream syntax. Example 2-4 shows in bold an example of a stream-type declaration for two inputs and a function-type declaration for the clock input.

#### Example 2-4 Defining an Edge-Sensitive Sensitivity List

```

SC_MODULE(my_module){

// Ports

sc in<int> a;

sc in<bool> b;

sc_in<bool> clock;

sc_out<int> x;

sc_out<int> y;

sc in<bool> reset;

// Internal signals

sc signal<bool>c;

sc_signal<int> d;

// process declaration

void my_method_proc();

// module constructor

SC_CTOR(my_module) {

// register process

SC_METHOD(my_method_proc);

// declare sensitivity list

sensitive_pos (clock); //Function delaration

sensitive_neg << b << reset; // Stream declaration</pre>

};

```

# **Limitations for Sensitivity Lists**

When you define a sensitivity list, adhere to the following limitations:

- You cannot specify both edge-sensitive and level-sensitive inputs in the same process for synthesis.

- You cannot declare an sc\_logic type for the clock or other edge-sensitive inputs. You can declare only an sc\_in<br/>bool> data type.

#### **Member Functions**

You can declare member functions in a module that are not processes. This type of member function is not registered as a process in the module's constructor. It can be called from a process. Member functions can contain any synthesizable C++ or SystemC statement allowed in a SC\_METHOD process.

A member function that is not a process can return any synthesizable data type.

#### **Module Constructor**

For each module you need to create a constructor, which is used to

- Register processes

- Define a sensitivity list for an SC\_METHOD process

For synthesis, other statements are not allowed in the constructor. See Example 2-4.

# Implementing the Module

In the module implementation file, define the functionality of each SC\_METHOD process and member function. Example 2-5 shows a minimal implementation file.

# Example 2-5 Module Implementation File

```

#include "systemc.h"

#include "my_module.h"

void my_module::my_method_proc() {

// describe process functionality as C++ code

}

```

# **Reading and Writing Ports and Signals**

In the module implementation description, you can read from or write to a port or signal by using the read and write methods or by assignment.

When you read or write a port, as a recommended coding practice, use the read() and write() methods. Use the assignment operator for variables. Example 2-6 shows in bold how to use the read and write methods for ports and signals, and it shows assignment operators for variables.

## Example 2-6 Using Assignment and read() and write() Methods

# Reading and Writing Bits of Ports and Signals

You read or write all bits of a port or signal. You cannot read or write the individual bits, regardless of the type. To do a bit-select on a port or signal, read the value into a temporary variable and do a bit-select on the temporary variable. Example 2-7 shows in bold how to write a bit by using a temporary variable.

### Example 2-7 Reading and Writing Bits of a Variable

```

//...

sc_signal <sc_int<8> > a;

sc_int<8> b;

bool c;

b = a.read();

c = b[0];

// c = a[0]; /Does not work in SystemC

```

Example 2-7 reads the value of signal a into temporary variable b, and bit 0 of b is assigned to c. You cannot read a bit from signal a, because this operation is not allowed in SystemC.

### **Signal and Port Assignments**

When you assign a value to a signal or port, the value on the right side is not transferred to the left side until the process ends. This means the signal value as seen by other processes is not updated immediately, but it is deferred.

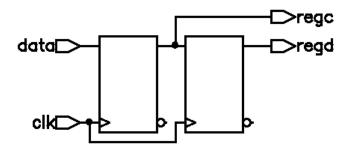

Example 2-8 shows a serial register implementation with signal assignment, and Figure 2-4 shows the resulting schematic.

### Example 2-8 Signal Assignment

```

#include "systemc.h"

SC_MODULE(rtl_nb) {

sc_in<bool> clk;

sc_in<bool> data;

sc_inout<bool> regc, regd;

void reg_proc() {

regc.write(data.read());

regd.write(regc.read());

}

```

```

SC_CTOR(rtl_nb) {

SC_METHOD(reg_proc);

sensitive_pos << clk;

}

};</pre>

```

Figure 2-4 Signal Assignment Schematic

### **Variable Assignment**

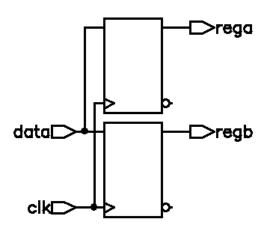

When you assign a value to a variable, the value on the right side is immediately transferred to the left side of the assignment statement.

Example 2-9 uses a variable assignment, where the implementation assigns the value of data to rega and regb, as the resulting schematic in Figure 2-5 indicates.

### Note:

This example is only an illustration of variable assignment. You can write the same behavior more efficiently by removing the rega\_v and regb\_v variables and writing the ports directly.

### Example 2-9 Variable Assignment

```

#include "systemc.h"

SC_MODULE(rtl_b) {

sc_in<bool> clk;

sc_in<bool> data;

sc_out<bool> rega, regb;

bool rega_v, regb_v;

void reg_proc() {

rega_v = data.read();

regb_v = rega_v;

rega.write(rega_v);

regb.write(regb_v);

}

SC_CTOR(rtl_b) {

SC_METHOD(reg_proc);

sensitive_pos << clk;

}

};</pre>

```

Figure 2-5 Variable Assignment Schematic

### Creating a Module With a Single SC\_METHOD Process

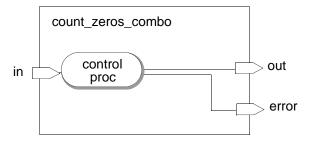

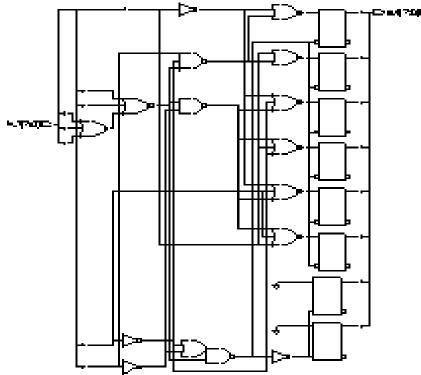

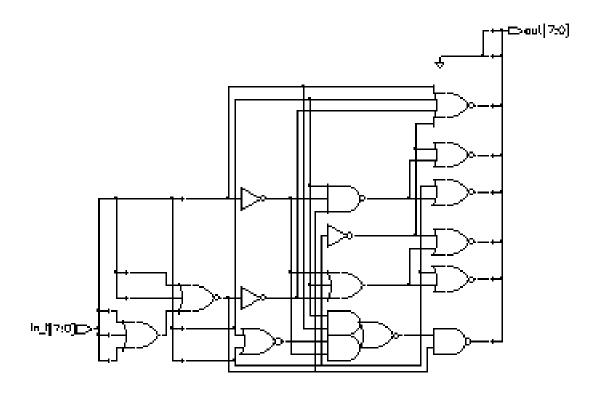

Example 2-10 is a complete example of an RTL description of a count zeros circuit that contains one SC\_METHOD process, control\_proc(), and two member functions, legal() and zeros(). The circuit determines in one cycle if an 8-bit value on the input port is valid (no more than one sequence of zeros) and how many zeros the value contains. The circuit produces two outputs, the number of zeros found and an error indication. Figure 2-6 illustrates the module and its ports.

Figure 2-6 Count Zeros Combinational Module

### Example 2-10 Count Zeros Combinational Version

```

/****count_zeros_comb.h file***/

#include "systemc.h"

SC_MODULE(count_zeros_comb) {

sc_in<sc_uint<8> > in;

sc_out<sc_uint<4> > out;

sc_out<bool> error;

bool legal(sc_uint<8> x);

sc_uint<4> zeros(sc_uint<8> x);

void control_proc();

SC_CTOR(count_zeros_comb) {

SC_METHOD(control_proc);

sensitive << in;

}

};</pre>

```

```

/****count_zeros_comb.cpp file****/

#include "count_zeros_comb.h"

void count_zeros_comb::control_proc() {

sc_uint<4> tmp_out;

bool is_legal = legal(in.read());

error.write(! is_legal);

is_legal ? tmp_out = zeros(in.read()) : tmp_out = 0;

out.write(tmp_out);

bool count_zeros_comb::legal(sc_uint<8> x) {

bool is_legal = 1;

bool seenZero = 0;

bool seenTrailing = 0;

for (int i=0; i <=7; ++i) {

if (seenTrailing && (x[i] == 0)) {

is_legal = 0;

break;

} else if (seenZero && (x[i] == 1)) {

seenTrailing = 1;

else if (x[i] == 0) {

seenZero = 1;

}

return is_legal;

sc_uint<4> count_zeros_comb::zeros(sc_uint<8> x) {

int count = 0;

for (int i=0; i <= 7; ++i) {

if (x[i] == 0)

++count;

}

return count;

```

# Creating a Module With Multiple SC\_METHOD Processes

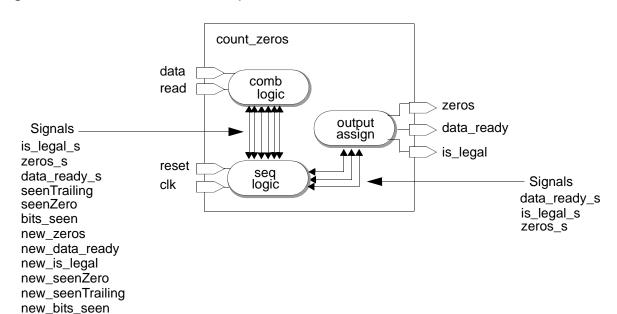

Example 2-11 on page 2-23 shows a sequential description of the same count zeros circuit described in "Creating a Module With a Single SC\_METHOD Process" on page 2-20.

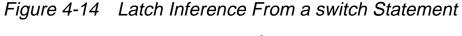

In this sequential version, there are three SC\_METHOD processes and several signals for communication between the processes, as shown in Figure 2-7. The comb\_logic() and output\_assign() processes are level-sensitive, and the seq\_logic() process is sensitive to the positive edge of the clk and reset inputs. The set\_defaults() member function is called at the beginning of the comb\_logic() process.

This example does not show typical simulation-specific code that you might include for debugging purposes.

Figure 2-7 Count Zeros Sequential Module

### Example 2-11 Count Zeros Sequential Version

```

/****count_zeros_seq.h file****/

#include "systemc.h"

#define ZEROS_WIDTH 4

#define MAX_BIT_READ 7

SC_MODULE(count_zeros_seq) {

sc_in<bool> data, reset, read, clk;

sc_out<bool> is_legal, data_ready;

sc_out<sc_uint<ZEROS_WIDTH> > zeros;

sc_signal<bool> new_data_ready, new_is_legal, new_seenZero, new_seenTrailing;

sc_signal<bool> seenZero, seenTrailing;

sc_signal<bool> is_legal_s, data_ready_s;

sc_signal<sc_uint<ZEROS_WIDTH> > new_zeros, zeros_s;

sc_signal<sc_uint<ZEROS_WIDTH - 1> > bits_seen, new_bits_seen;

// Processes

void comb logic();

void seq_logic();

void assign_outputs();

// Helper functions

void set_defaults();

SC_CTOR(count_zeros_seq) {

SC_METHOD(comb_logic);

sensitive << data << read << is_legal_s << data_ready_s;</pre>

sensitive << seenTrailing << seenZero << zeros_s << bits_seen;</pre>

SC_METHOD(seq_logic);

sensitive_pos << clk << reset;</pre>

SC METHOD(assign outputs);

sensitive << is_legal_s << data_ready_s << zeros_s;</pre>

};

```

```

/****count_zeros_seq.cpp file****/

#include "count_zeros_seq.h"

* SC_METHOD: comb_logic()

finds a singular run of zeros and counts them

* /

void count_zeros_seq::comb_logic() {

set_defaults();

if (read.read()) {

if (seenTrailing && (data.read() == 0)) {

new_is_legal = false;

new_zeros = 0;

new data ready = true;

} else if (seenZero && (data.read() == 1)) {

new seenTrailing = true;

} else if (data.read() == 0) {

new_seenZero = true;

new_zeros = zeros_s.read() + 1;

}

if (bits_seen.read() == MAX_BIT_READ)

new_data_ready = true;

else

new_bits_seen = bits_seen.read() + 1;

}

}

* SC_METHOD: seq_logic()

All registers have asynchronous resets

void count zeros seq::seq logic() {

if (reset) {

zeros_s = 0;

bits_seen = 0;

seenZero = false;

seenTrailing = false;

is_legal_s = true;

data_ready_s = false;

} else {

zeros_s = new_zeros;

bits_seen = new_bits_seen;

seenZero = new seenZero;

seenTrailing = new_seenTrailing;

is_legal_s = new_is_legal;

data_ready_s = new_data_ready;

```

```

}

* SC_METHOD: assign_outputs()

* Zero time assignments of signals to their associated outputs

* /

void count_zeros_seq::assign_outputs() {

zeros = zeros_s;

is_legal = is_legal_s;

data_ready = data_ready_s;

method: set_defaults()

sets the default values of the new_* signals for the comb_logic

process.

* /

void count_zeros_seq::set_defaults() {

new_is_legal = is_legal_s;

new_seenZero = seenZero;

new_seenTrailing = seenTrailing;

new_zeros = zeros_s;

new_bits_seen = bits_seen;

new_data_ready = data_ready_s;

}

```

### **Creating a Hierarchical RTL Module**

You can create a hierarchical module with multiple instantiated modules.

### The Basics of Hierarchical Module Creation

To create a hierarchical module,

- 1. Create data members in the top-level module that are pointers to the instantiated modules.

- 2. Allocate the instantiated modules inside the constructor of the top-level module, giving each instance a unique name.

- 3. Bind the ports of the instantiated modules to the ports or signals of the top-level module. Use either binding by position or binding by name coding style, which is illustrated in bold in Example 2-12.

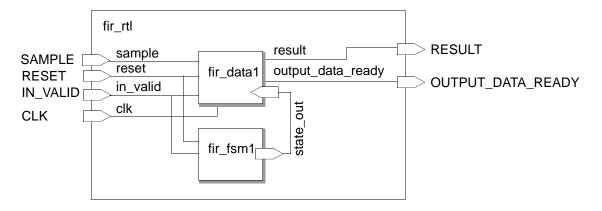

Example 2-12 shows the partial source code of two modules, fir\_fsm and fir\_data, instantiated within the fir\_top module. The relevant code is highlighted in bold.

### Example 2-12 Hierarchical Module With Multiple RTL Modules

```

sc_out<bool>

OUTPUT_DATA_READY;

sc out<int>

RESULT;

sc_signal<unsigned> state_out; //Communication between

//two peer modules

// Create data members - pointers to instantiated

// modules

fir fsm *fir fsm1;

fir_data *fir_data1;

SC_CTOR(fir_top) {

// Create new instance of fir_fsm module

fir_fsm1 = new fir_fsm("FirFSM");

// Binding by name

fir_fsm1->clock(CLK);

fir fsm1->reset(RESET);

fir fsm1->in valid(IN VALID);

fir_fsm1->state_out(state_out);

// Binding by position alternative

//fir_fsm1 (CLK, RESET, IN_VALID, state_out);

// Create new instance

// of fir_data module and bind by name

fir_data1 = new fir_data("FirData");

fir data1->reset(RESET);

fir_data1->state_out(state_out);

fir data1->sample(SAMPLE);

fir_data1->result(RESULT);

fir_data1->output_data_ready(OUTPUT_DATA_READY);

fir data1->clk(CLK);

. . .

};

/***fir fsm.h***/

SC_MODULE(fir_fsm) {

sc in<bool>

clock;

sc_in<bool>

reset;

sc_in<bool>

in_valid;

```

### **Hierarchical RTL Module Example**

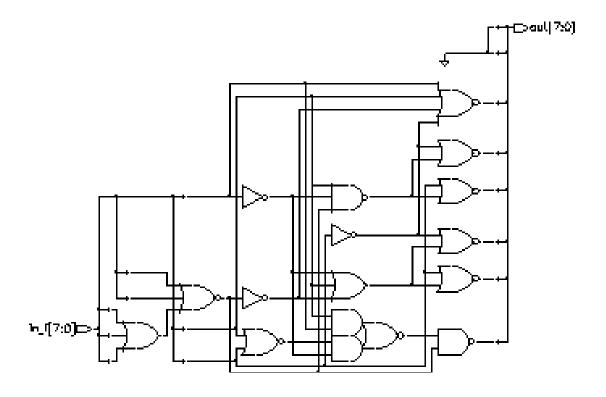

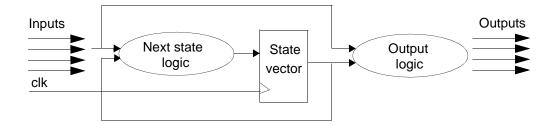

Example 2-13 on page 2-29 shows a complete example of the hierarchical RTL finite impulse response (FIR) filter description. This is a typical sequential logic description that separates the controlling FSM (Example 2-14 on page 2-30) and the data path (Example 2-15 on page 2-32) into two separate modules. Figure 2-8 illustrates the modules, the port binding, and their interconnecting signals.

In the top-level fir\_rtl module, data member pointers to the fir\_fsm and fir\_data modules are declared, new instances of the two modules (fir\_fsm1 and fir\_data1) are created, and the port bindings are defined. A signal, state\_out, is defined to connect the fir\_fsm1 and fir\_data1 state\_out ports.

Coding guidelines for state machines are described in "State Machines" on page 4-37.

Figure 2-8 FIR RTL Modules

### Example 2-13 FIR Top-Level Module

```

/****fir_rtl.h file****/

#include <systemc.h>

#include "fir_fsm.h"

#include "fir_data.h"

SC_MODULE(fir_rtl) {

sc_in<bool>

clk;

sc in<bool>

reset;

sc_in<bool>

in_valid;

sc_in<int>

sample;

sc_out<bool>

output_data_ready;

sc_out<int>

result;

sc_signal<unsigned> state_out;

fir_fsm *fir_fsm1;

fir_data *fir_data1;

SC_CTOR(fir_rtl) {

fir_fsm1 = new fir_fsm("FirFSM");

fir_fsm1->clock(clk);

fir_fsm1->reset(reset);

```

```

fir_fsml->in_valid(in_valid);

fir_fsml->state_out(state_out);

fir_datal = new fir_data("FirData");

fir_datal->state_out(state_out);

fir_datal->sample(sample);

fir_datal->clock(clk);

fir_datal->result(result);

fir_datal->output_data_ready(output_data_ready);

};

```

### Example 2-14 FIR FSM Module

```

/***fir_fsm.h file***/

SC_MODULE(fir_fsm) {

sc in<bool>

clock;

sc in<bool>

reset;

sc_in<bool>

in_valid;

sc_out<unsigned> state_out;

// defining the states of the ste machine

enum {reset_s, first_s, second_s, third_s, output_s,

wait_s} state;

SC_CTOR(fir_fsm)

SC_METHOD(entry);

sensitive_pos(clock);

void entry();

};

/***fir_fsm.cpp file****/

#include <systemc.h>

#include "fir_fsm.h"

```

```

void fir_fsm::entry() {

sc_uint<3> state_tmp;

// reset behavior

if(reset.read()==true) {

state = reset s;

// main state machine

switch(state) {

case reset_s:

state = wait_s;

state_tmp = 0;

state_out.write(state_tmp);

break;

case first_s:

state = second_s;

state_tmp = 1;

state_out.write(state_tmp);

break;

case second_s:

state = third_s;

state\_tmp = 2;

state_out.write(state_tmp);

break;

case third_s:

state = output_s;

state_tmp = 3;

state_out.write(state_tmp);

break;

case output_s:

state = wait_s;

state_tmp = 4;

state_out.write(state_tmp);

break;

default:

if(in_valid.read()==true) {

state = first_s;

};

state_tmp = 5;

state_out.write(state_tmp);

```

```

break;

}

```

### Example 2-15 FIR Data Module

```

/***fir data.h file***/

SC_MODULE(fir_data) {

sc_in<unsigned> state_out;

sc_in<int>

sample;

sc_out<int> result;

sc_out<bool> output_data_ready;

sc_in<bool>

clock;

sc_int<19> acc;

sc_int<8> shift[16];

sc_int<9> coefs[16];

SC_CTOR(fir_data)

SC_METHOD(entry);

sensitive_pos(clock);

void entry();

};

/****fir_data.cpp file****/

#include <systemc.h>

#include "fir_data.h"

void fir_data::entry()

#include "fir_const_rtl.h"

sc_int<8> sample_tmp;

sc_uint<3> state = state_out.read();

```

```

switch (state) {

case 0:

sample\_tmp = 0;

acc = 0;

for (int i=0; i<=15; i++) {

shift[i] = 0;

result.write(0);

output_data_ready.write(false);

break;

case 1:

sample_tmp = sample.read();

acc = sample_tmp*coefs[0];

acc += shift[14]* coefs[15];

acc += shift[13]*coefs[14];

acc += shift[12]*coefs[13];

acc += shift[11]*coefs[12];

output_data_ready.write(false);

break;

case 2:

acc += shift[10]*coefs[11];

acc += shift[9]*coefs[10];

acc += shift[8]*coefs[9];

acc += shift[7]*coefs[8];

output_data_ready.write(false);

break;

case 3:

acc += shift[6]*coefs[7];

acc += shift[5]*coefs[6];

acc += shift[4]*coefs[5];

acc += shift[3]*coefs[4];

output_data_ready.write(false);

break;

case 4:

acc += shift[2]*coefs[3];

acc += shift[1]*coefs[2];

acc += shift[0]*coefs[1];

for(int i=14; i>=0; i--) {

shift[i+1] = shift[i];

};

shift[0] = sample.read();

result.write(acc);

```

```

output_data_ready.write(true);

break;

case 5 :

// This state waits for valid input

output_data_ready.write(false);

break;

default :

output_data_ready.write(false);

result.write(0);

}

```

# 3

## Using the Synthesizable Subset

This chapter explains the subset of the SystemC and C/C++ language elements and data types that are used for RTL synthesis. It contains the following sections:

- Converting to a Synthesizable Subset

- Refining Data

- Recommendations About Refinement for Synthesis

### **Converting to a Synthesizable Subset**

To prepare for synthesis, you need to convert all nonsynthesizable code into synthesizable code. This is required only for functionality that is to be synthesized.

Although you can use any SystemC class or C++ construct for simulation and other stages of the design process, only a subset of the language can be used for synthesis. You can use #ifdef and #endif to comment out code that is needed only for simulation. For example, you can exclude trace and print statements with these compiler directives.

### SystemC and C++ Synthesizable Subsets

The synthesizable subsets of SystemC and C++ are provided in the sections that follow. Wherever possible, a recommended corrective action is indicated for converting nonsynthesizable constructs into synthesizable constructs. For many nonsynthesizable constructs, there is no obvious recommendation for converting them into synthesizable constructs or there are numerous ways to convert them. In such cases, a recommended corrective action is not indicated. Familiarize yourself with the synthesizable subset and use it as much as possible in your pure C/C++ or high-level SystemC models to minimize the refinement effort for synthesis.

You can use any SystemC or C++ construct for a testbench. You do not need to restrict your code to the synthesizable subset in the testbench.

### **Nonsynthesizable SystemC Constructs**

The SystemC constructs listed in Table 3-1 are not supported for RTL synthesis.

Table 3-1 Nonsynthesizable SystemC Constructs for RTL Synthesis

| Category            | Construct                               | Comment                                                               | Corrective action          |

|---------------------|-----------------------------------------|-----------------------------------------------------------------------|----------------------------|

| Thread process      | SC_THREAD                               | Used for modeling a testbench but not supported for synthesis.        |                            |

| CTHREAD<br>process  | SC_CTHREAD                              | Used for simulation and modeling at the behavioral level.             |                            |

| Main function       | sc_main()                               | Used for simulation.                                                  |                            |

| Clock<br>generators | sc_start()                              | Used for simulation.                                                  | Use only in sc_main( ).    |

| Global watching     | watching()                              | Not supported for RTL synthesis                                       |                            |

| Local watching      | W_BEGIN,<br>W_END,<br>W_DO,<br>W_ESCAPE | Not supported.                                                        |                            |

| Tracing             | sc_trace,<br>sc_create*<br>trace_file   | Creates waveforms of signals, channels, and variables for simulation. | Comment out for synthesis. |

### **Nonsynthesizable C/C++ Constructs**

The C and C++ constructs listed in Table 3-2 are not supported for RTL synthesis.

Table 3-2 Nonsynthesizable C/C++ Constructs

| Category                         | Construct                                       | Comment                                                                              | Corrective action                               |

|----------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------|

| Local class declaration          |                                                 | Not allowed.                                                                         | Replace.                                        |

| Nested class declaration         |                                                 | Not allowed.                                                                         | Replace.                                        |

| Derived class                    |                                                 | Only SystemC modules and processes supported.                                        | Replace.                                        |

| Dynamic<br>storage<br>allocation | malloc(),<br>free(), new,<br>new[],<br>delete[] | malloc(), free(), new, new[], delete, and delete[] are not supported.                | Use static memory allocation.                   |

| Exception handling               | try, catch,<br>throw                            | Not allowed.                                                                         | Comment out.                                    |

| Recursive function call          |                                                 | Not allowed.                                                                         | Replace with iteration.                         |

| Function overloading             |                                                 | Not allowed (except the classes overloaded by SystemC).                              | Replace with unique function calls.             |

| C++ built-in functions           |                                                 | Math library, I/O library, file I/O, and similar built-in C++ functions not allowed. | Replace with synthesizable functions or remove. |

| Virtual function                 |                                                 | Not allowed.                                                                         | Replace with a nonvirtual function.             |

| Inheritance                      |                                                 | Not allowed.                                                                         | Create an independent SC_MODULE.                |

| Multiple<br>inheritance          |                                                 | Not allowed.                                                                         | Create independent modules.                     |

Table 3-2 Nonsynthesizable C/C++ Constructs (Continued)

| Category                                        | Construct                                   | Comment                                                                         | Corrective action                                                                |

|-------------------------------------------------|---------------------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Member access control specifiers                | public,<br>protected,<br>private,<br>friend | Allowed in code but ignored for synthesis. All member access is public.         |                                                                                  |

| Accessing struct members with the (->) operator | -> operator                                 | Not allowed, except for module instantiation.                                   | Replace with access using the period (.) operator.                               |

| Static member                                   |                                             | Not allowed.                                                                    | Replace with nonstatic member variable.                                          |

| Dereference operator                            | * and & operators                           | Not allowed.                                                                    | Replace dereferencing with array accessing.                                      |

| for loop comma operator                         | , operator                                  | The comma operator is not allowed in a for loop definition.                     | Remove the comma operators.                                                      |

| Operator overloading                            |                                             | Not allowed (except the classes overloaded by SystemC).                         | Replace overloading with unique function calls.                                  |

| Operator, sizeof                                | sizeof                                      | Not allowed.                                                                    | Determine size statically for use in synthesis.                                  |

| Pointer                                         | *                                           | Pointers are allowed only in hierarchical modules to instantiate other modules. | Replace all other pointers with access to array elements or individual elements. |

| Pointer type conversions                        |                                             | Not allowed.                                                                    | Do not use pointers.<br>Use explicit variable<br>reference.                      |

| this pointer                                    | this                                        | Not allowed.                                                                    | Replace.                                                                         |

| Reference, C++                                  | &                                           | Allowed only for passing parameters to functions.                               | Replace in all other cases.                                                      |

Table 3-2 Nonsynthesizable C/C++ Constructs (Continued)

| Category                                    | Construct | Comment                                                                                                                                               | Corrective action                                                     |

|---------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| Reference conversion                        |           | Reference conversion is supported for implicit conversion of signals only.                                                                            | Replace in all other cases.                                           |

| User-defined template class                 |           | Only SystemC templates classes such as sc_int<> are supported.                                                                                        | Replace.                                                              |

| Type casting at runtime                     |           | Not allowed.                                                                                                                                          | Replace.                                                              |

| Type identification at runtime              |           | Not allowed.                                                                                                                                          | Replace.                                                              |

| Explicit<br>user-defined<br>type conversion |           | The C++ built-in types and SystemC types are supported for explicit conversion.                                                                       | Replace in all other cases.                                           |

| Unconditional branching                     | goto      | Not allowed.                                                                                                                                          | Replace.                                                              |

| Unions                                      |           | Not allowed.                                                                                                                                          | Replace with structs.                                                 |

| Global variable                             |           | Not supported for synthesis.                                                                                                                          | Replace with local variables.                                         |

| Member<br>variable                          |           | Member variables accessed by two or more SC_METHOD processes are not supported. However, access to member variables by only one process is supported. | Use signals instead of variables for communication between processes. |

| Volatile variable                           |           | Not allowed.                                                                                                                                          | Use only nonvolatile variables.                                       |

### **Refining Data**

A pure C/C++ model or a high-level SystemC model typically uses native C++ types or aggregates (structures) of such types. Native C++ types such as int, char, bool, and long have fixed, platform-dependent widths, which are often not the correct width for efficient hardware. For example, you might need only a 6-bit integer for a particular operation, instead of the native C++ 32-bit integer. In addition, C++ does not support four-valued logic vectors, operations such as concatenation, and other features that are needed to efficiently describe hardware operations.

SystemC provides a set of limited-precision and arbitrary-precision data types that allows you to create integers, bit vectors, and logic vectors of any length. SystemC also supports all common operations on these data types.

To refine a SystemC model for RTL synthesis, you need to evaluate all variable declarations, formal parameters, and return types of all functions to determine the appropriate data type and the appropriate widths of each data type. Selecting the data widths is a design decision, and it is typically a tradeoff between the cost of hardware and the required precision. This decision is, therefore, left to you.

### **Synthesizable Data Types**

C++ is a strongly typed language. Every constant, port, signal, variable, function return type, and parameter is declared as a data type, such as bool or sc\_int<*n*>, and can hold or return a value of that type. Therefore, it is important that you use the correct data types in expressions.

### **Nonsynthesizable Data Types**

All SystemC and C++ data types can be used for RTL synthesis, except the following types:

- Floating-point types such as float and double

- Fixed-point types sc\_fixed, sc\_ufixed, sc\_fix, and sc\_ufix

- Access types such as pointers

- File types such as FILE

- I/O streams such as stdout and cout

### **Recommended Data Types for Synthesis**

For best synthesis, use appropriate data types and bit-widths so unnecessary hardware is not built during RTL synthesis.

The following are some general recommendations about data type selections:

- For a single-bit variable, use the native C++ type bool.

- For variables with a width of 64 bits or less, use sc\_int or sc\_uint data types. Use sc\_uint for all logic and unsigned arithmetic operations. Use sc\_int for signed arithmetic operations as well as for logic operations. These types produce the fastest simulation runtimes of the SystemC types.

- For variables larger than 64 bits, use sc\_bigint or sc\_biguint if you want to do arithmetic operations with these variables.

- Use sc\_logic or sc\_lv only when you need to model three-state signals or buses. When you use these data types, avoid comparison with X and Z values in your synthesizable code, because such comparisons are not synthesizable.

- Use native C++ integer types for loop counters.

- Use the native C++ data types with caution, because their size is platform-dependent. For example, on most platforms, a char is 8 bits wide, a short is 16 bits wide, and both an int and long are 32 bits wide. An int, however, can be 16, 32, or 64 bits wide.

To restrict bit size for synthesis, use the recommended SystemC data types summarized in Table 3-3 in place of the equivalent C++ native type. For example, change an int type to an sc\_int<*n*> type.

Table 3-3 Synthesizable Data Types

| SystemC and C++ type   | Description                                                                                                     |

|------------------------|-----------------------------------------------------------------------------------------------------------------|

| sc_bit                 | A single-bit true or false value. Supported but not recommended. Use the bool data type.                        |

| sc_bv< <i>n</i> >      | Arbitrary-length bit vector. Use sc_uint< <i>n</i> > when possible.                                             |

| sc_logic               | A single-bit 0, 1, X, or Z.                                                                                     |

| sc_lv< <i>n</i> >      | Arbitrary-length logic vector.                                                                                  |

| sc_int< <i>n</i> >     | Fixed-precision integers restricted in size up to 64 bits and 64 bits of precision during operations.           |

| sc_uint< <i>n</i> >    | Fixed-precision integers restricted in size up to 64 bits and 64 bits of precision during operations, unsigned. |

| sc_bigint< <i>n</i> >  | Arbitrary-precision integers recommended for sizes over 64 bits and unlimited precision.                        |

| sc_biguint< <i>n</i> > | Arbitrary-precision integers recommended for sizes over 64 bits and unlimited precision, unsigned.              |

Table 3-3 Synthesizable Data Types (Continued)

| SystemC and C++ type | Description                                                                  |

|----------------------|------------------------------------------------------------------------------|

| bool                 | A single-bit true or false value.                                            |

| int                  | A signed integer, typically 32 or 64 bits, depending on the platform.        |

| unsigned int         | An unsigned integer, typically 32 or 64 bits, depending on the platform.     |

| long                 | A signed integer, typically 32 bits or longer, depending on the platform.    |

| unsigned long        | An unsigned integer, typically 32 bits or longer, depending on the platform. |

| char                 | 8 bits, signed character, platform-dependent.                                |

| unsigned char        | 8 bits, unsigned character, platform-dependent.                              |

| short                | A signed short integer, typically 16 bits, depending on the platform.        |

| unsigned short       | An unsigned short integer, typically 16 bits, depending on the platform.     |

| struct               | A user-defined aggregate of synthesizable data types.                        |

| enum                 | A user-defined enumerated data type associated with an integer constant.     |

### **Using SystemC Data Types**

Use the SystemC data type operators to access individual bits of a value.

### **Bit Vector Data Type Operators**

Table 3-4 lists the operators available for the SystemC sc\_bv data type.

Table 3-4 SystemC Bit Vector Data Type Operators

# Ditwise &(and), |(or), ^(xor), and ~(not) Bitwise <<(shift left) and >>(shift right) Assignment =, &=, |=, and ^= Equality ==, != Bit selection [x] Part selection range (x-y) Concatenation (x,y) Reduction: and\_reduce(), or\_reduce(), and xor\_reduce() Type conversion: to\_uint() and to\_int()

### **Fixed and Arbitrary Precision Data Type Operators**

Table 3-5 lists the operators available for the SystemC sc\_int and sc\_uint fixed-precision and sc\_bigint and sc\_biguint arbitrary-precision integer data types.

Table 3-5 SystemC Integer Data Type Operators

# Ditwise &(and), |(or), ^(xor), and ~(not) Bitwise <<(shift left) and >>(shift right) Assignment =, &=, |=, ^=, +=, -=, \*=, /=, and %= Equality ==, != Relational <, <=, >, and >= Autoincrement ++ and autodecrement - Bit selection [x] Part selection range (x-y) Concatenation (x,y) Type conversion: to\_uint() and to\_int()

### Note:

The reduction and\_reduce(), or\_reduce(), and xor\_reduce() operators are not supported for the fixed- and arbitrary-precision data types.

### **Using Enumerated Data Types**

Systemc supports enumerated (enum) data types and interprets an enum data type the same was a C++ compiler interprets it. Example 3-1 shows an enum definition.

### Example 3-1 Enumerated Data Type

```

enum command_t{

NONE,

RED,

GREEN,

YELLOW

};

```

### **Using Aggregate Data Types**

To group data types into a convenient aggregate type, define them as a struct type similar to Example 3-2. You need to use all synthesizable data types in a struct for the struct to be synthesizable.

### Example 3-2 Aggregate Data Type

```

struct package {

sc_uint<8> command;

sc_uint<8> address;

sc_uint<12> data;

}

```

### **Using C++ Data Types**

The native C++ data types, such as bool, char, int, long, short, unsigned char, unsigned int, unsigned long, and unsigned short, have a platform-specific size, which will be used during synthesis.

### **Data Members of a Module**

Do not use data members for interprocess communication, because it can lead to nondeterminism (order dependencies) during simulation and it can cause mismatches between the results of preand post-synthesis simulation. Instead of a data member for interprocess communication, use an sc\_signal for this purpose.

Example 3-3 shows (in bold) a data member variable named count that is incorrectly used to communicate between the do\_count() and outregs() processes. A value is written to the count variable in the do\_count() process, and a value is read from the same variable in the outregs() process. The order in which the two processes execute cannot be predicted—therefore, you cannot determine whether writing to the count variable is happening before or after count is incremented.

Example 3-3 Incorrect Use of a Data Member Variable for Interprocess Communication

```

void do_count() {

if (reset.read() == 0)

count = 0;

else

count++;

}

void outregs() {

if (reset.read() == 0)

count_out.write(0);

else

count_out.write(count);

}

```

To eliminate the nondeterminism of count in Example 3-3, change count to an sc\_signal, as shown in bold in Example 3-4. Notice that the only change in the code is the type declaration of count.

### Example 3-4 Correct Use of a Signal for Interprocess Communication

```

/****mem_var_good.h****/

#include "systemc.h"

SC_MODULE(counter) {

sc in<bool> clk;

sc in<bool> reset z;

sc_out<sc_uint<4> > count_out;

// Signal for interprocess communication

sc_signal<sc_uint<4> > count;

SC_CTOR(counter) {

SC_METHOD(do_count);

sensitive pos << clk;

sensitive_neg << reset_z;</pre>

SC_METHOD(outregs);

sensitive_pos << clk;

sensitive_neg << reset_z;</pre>

}

```

```

void do_count() {

if (reset.read() == 0)

count = 0;

else

count++;

}

void outregs() {

if (reset.read() == 0)

count_out.write(0);

else

count_out.write(count);

}

```

### **Recommendations About Refinement for Synthesis**

The following practices are recommended during refinement:

- After each step in refinement, reverify your design to ensure that you did not introduce errors during that step.

- Although it is recommended that you thoroughly refine at each refinement stage, it is not necessary. For example, during data refinement, you can refine one data type at a time and evaluate the impact on synthesizability and the quality of results. Similarly, you might want to replace one nonsynthesizable construct with a synthesizable construct and reverify the design before replacing the next nonsynthesizable construct.

4

## **RTL Coding Guidelines**

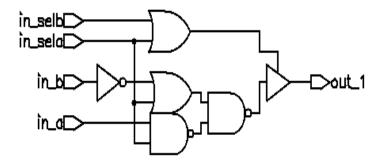

This chapter provides SystemC RTL coding guidelines.

It contains the following sections:

- Register Inference

- Three-State Inference

- State Machines

### **Register Inference**

Register inference allows you to use sequential logic in your designs and keep your designs technology-independent. A register is an array of 1-bit memory devices. A latch is a level-sensitive memory device, and a flip-flop is an edge-triggered memory device. Use the coding guidelines in this section to control flip-flop and latch inference.

As a recommended design practice, whenever you infer registers, ensure that the clock and data inputs to the registers can be directly controlled from the ports of the design. This ensures that you can initialize your design easily during simulation as well as in the actual circuit. You can, of course, infer registers with set and reset, which makes the task of register initialization easier and is highly recommended.

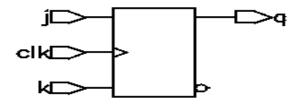

### Flip-Flop Inference

RTL synthesis can infer D flip-flops, JK flip-flops, and toggle flip-flops. The following sections provide details about each of these flip-flop types.

### Simple D Flip-flop

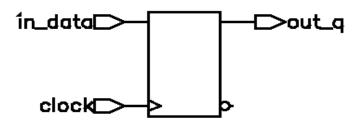

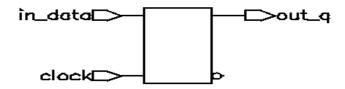

To infer a simple D flip-flop, make the SC\_METHOD process sensitive to only one edge of the clock signal. To infer a positive-edge-triggered flip-flop, make the process sensitive to the positive edge of the clock, and make the process sensitive to the negative edge to infer a negative-edge-triggered flip-flop.

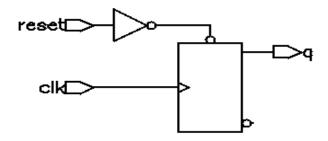

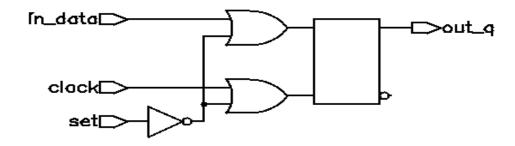

RTL synthesis creates flip-flops for all the variables that are assigned values in the process. Example 4-1 is a common SC\_METHOD process description that infers a flip-flop. Figure 4-1 shows the inferred flip-flop.

## Example 4-1 Inferring a Positive-Edge-Triggered Flip-Flop

```

/* Positive edge-triggered DFF */

#include "systemc.h"

SC_MODULE (dff1) {

sc_in<bool> in_data;

sc_out<bool> out_q;

sc in<bool> clock;

// clock port

// Method for D-flip-flop

void do_dff_pos ();

// Constructor

SC_CTOR (dff1) {

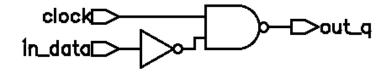

SC_METHOD (do_dff_pos);

sensitive_pos << clock;</pre>

};

void dff1::do_dff_pos()

out_q.write(in_data.read());

```

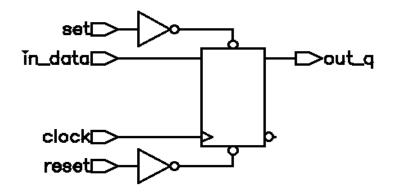

Figure 4-1 Inferred Positive-Edge-Triggered Flip-Flop

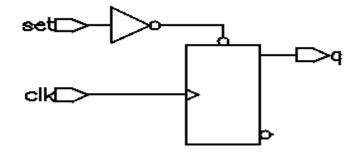

# D Flip-Flop With an Active-High Asynchronous Set or Reset

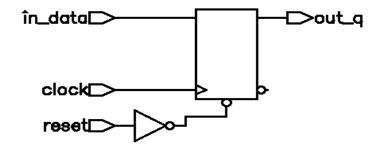

To infer a D flip-flop with an asynchronous set or reset, include edge expressions for the clock and the asynchronous signals in the sensitivity list of the SC\_METHOD process constructor. Specify the asynchronous signal conditions with an if statement in the SC\_METHOD process definition. Example 4-2 shows a typical asynchronous specification. Specify the asynchronous branch conditions before you specify the synchronous branch conditions.

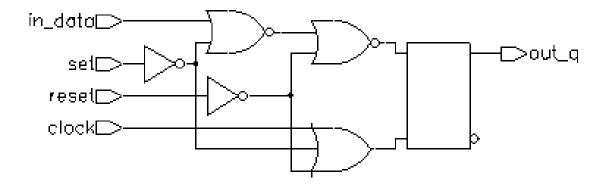

Example 4-2 is a the SystemC description for a D flip-flop with an active-high asynchronous reset. Figure 4-2 shows the inferred flip-flop.

#### Example 4-2 D Flip-Flop With an Active-High Asynchronous Reset

```

/* Positive edge-triggered DFF */

#include "systemc.h"

SC MODULE (dff3) {

sc_in<bool> in_data, reset;

sc_out<bool> out_q;

sc_in<bool> clock; // clock port

void do_dff_pos ();

// Constructor

SC_CTOR (dff3) {

SC_METHOD (do_dff_pos);

sensitive pos << clock << reset;

};

void dff3::do_dff_pos () {

if (reset.read())

out_q.write(0);

else

```

```

out_q.write(in_data.read());

}

```

Figure 4-2 D Flip-Flop With an Active-High Asynchronous Reset

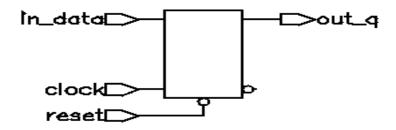

# D Flip-Flop With an Active-Low Asynchronous Set or Reset

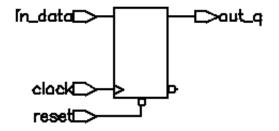

Example 4-3 is a SystemC description for a D flip-flop with an active-low asynchronous reset. Figure 4-3 shows the inferred flip-flop.

## Example 4-3 D Flip-Flop With an Active-Low Asynchronous Reset

```

/* Positive edge-triggered DFF

with active low reset */

#include "systemc.h"

SC_MODULE (dff3a) {

sc_in<bool> in_data, reset;

sc_out<bool> out_q;

sc_in<bool> clock; // clock port

void do_dff_pos ();

// Constructor

SC_CTOR (dff3a) {

```

```

SC_METHOD (do_dff_pos);

sensitive_pos << clock;

sensitive_neg << reset;

}

};

void dff3a::do_dff_pos () {

if (reset.read() == 0)

out_q.write(0);

else

out_q.write(in_data.read());

}</pre>

```

Figure 4-3 D Flip-Flop With an Active-Low Asynchronous Reset

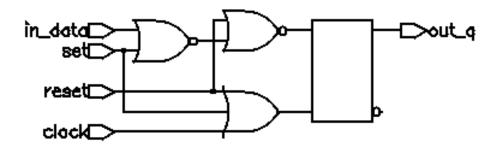

#### D Flip-Flop With Active-High Asynchronous Set and Reset.

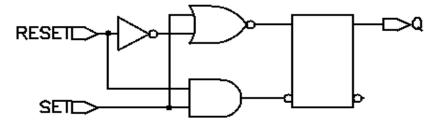

Example 4-4 is a SystemC description for a D flip-flop with active-high asynchronous set and reset ports. Figure 4-4 shows the inferred flip-flop.

An implied priority exists between set and reset, and reset has priority. This priority is not guaranteed, because it can be implemented differently in various technology libraries. To ensure the correct behavior, assign a high value to either the set or reset at one time, but not to both at the same time.

#### Example 4-4 Flip-Flop With Asynchronous Set and Reset

```

/* Positive edge-triggered DFF */

#include "systemc.h"

SC MODULE (dff4) {

sc_in<bool> in_data, reset, set;

sc out<bool> out q;

sc_in<bool> clock; // clock port

void do_dff_pos ();

// Constructor

SC_CTOR (dff4) {

SC METHOD (do dff pos);

sensitive_pos << clock << reset << set;</pre>

}

};

void dff4::do_dff_pos () {

if (reset.read())

out_q.write(0);

else if (set.read())

out_q.write(1);

else

out_q.write(in_data.read());

```

Figure 4-4 Flip-Flop With Asynchronous Set and Reset

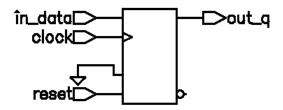

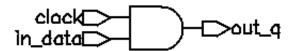

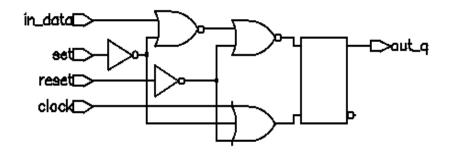

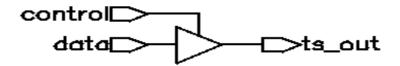

# D Flip-Flop With Synchronous Set or Reset

The previous examples illustrated how to infer a D flip-flop with asynchronous controls — one way to initialize or control the state of a sequential device. You can also synchronously reset or set a flip-flop.

If the target technology library does not have a D flip-flop with a synchronous reset, a D flip-flop with synchronous reset logic as the input to the D pin of the flip-flop is inferred. If the reset (or set) logic is not directly in front of the D pin of the flip-flop, initialization problems can occur during gate-level simulation of the design.

To specify a synchronous set or reset input, do not include it in the sensitivity list. Describe the synchronous set or reset test and action in an if statement. Example 4-5 is a SystemC description for a D flip-flop with synchronous reset. Figure 4-5 shows the inferred flip-flop.

## Example 4-5 D Flip-Flop With Synchronous Reset

```

/* Positive edge-triggered DFF */

#include "systemc.h"

SC_MODULE (dff5) {

sc_in<bool> in_data, reset;

sc_out<bool> out_q;

sc_in<bool> clock;

// clock port

// Method for D-flip-flop

void dff ();

// Constructor

SC_CTOR (dff5) {

SC_METHOD (dff);

sensitive_pos << clock;</pre>

};

void dff5::dff()

if (reset.read())

out_q.write(0);

else

out_q.write(in_data.read());