# PCI 703 Series

# PCI PnP Analog Board User's Manual

PCI703-16/A, PCI703-32/A PCI703-64/A PCI703S-8/A, PCI703S-16/A

Eagle Technology – Cape Town, South Africa Copyright © 2001-2002 www.eagle.co.za

# **Analog Boards**

Data Acquisition and Process Control

© Eagle Technology 31-35 Hout Street • Cape Town • South Africa Phone +27 21 423 4943 • Fax +27 21 424 4637 Email eagle@eagle.co.za

#### Copyright

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or any means, electronic, mechanical, by photographing, recording, or otherwise without prior written permission.

Copyright © Eagle Technology, South Africa July 2002 Revision 1.6

Information furnished in this manual is believed to be accurate and reliable; however no responsibility is assumed for its use, or any infringements of patents or other rights of third parties, which may result from its use.

Trademarks and Logos in this manual are the property of their respective owners.

#### **Product Warranty**

Eagle Technology, South Africa, warrants its products from defect in material and workmanship from confirmed date of purchase for a period of one year if the conditions listed below are met. The product warranty will call the Eagle Technology Data Acquisition Device short as **ETDAQD**.

- The warranty does not apply to an ETDAQD that has been previously repaired, altered, extended by any other company or individual outside the premises of Eagle Technology.

- That a qualified person configure and install the ETDAQD, and damages caused to a

device during installation shall make the warranty void and null.

- The warranty will not apply to conditions where the ETDAQD has been operated in a manner exceeding its specifications.

Eagle Technology, South Africa, does not take responsibility or liability of consequential damages, project delays, damaging of equipment or capital loss as a result of its products.

Eagle Technology, South Africa, holds the option and final decision to repair or replace any **ETDAQD.** Proof of purchase must be supplied when requesting a repair.

### **TABLE OF CONTENTS**

| 1. INTRODUCTION                                                                                                                                                                                                                                                                 | 1                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Features                                                                                                                                                                                                                                                                        | 1                                      |

| Applications                                                                                                                                                                                                                                                                    | 2                                      |

| Key Specifications                                                                                                                                                                                                                                                              | 2                                      |

| Software Support                                                                                                                                                                                                                                                                | 2                                      |

| Contact Details                                                                                                                                                                                                                                                                 | 2                                      |

| 2. INSTALLATION                                                                                                                                                                                                                                                                 | 3                                      |

| Package                                                                                                                                                                                                                                                                         | 3                                      |

| Operating System Support                                                                                                                                                                                                                                                        | 3                                      |

| Hardware Installation                                                                                                                                                                                                                                                           | 3                                      |

| Software Installation Windows 98/2000/ME Post installation Windows NT                                                                                                                                                                                                           | <b>4</b><br>4<br>7<br>9                |

| Accessories                                                                                                                                                                                                                                                                     | 9                                      |

| 3. INTERCONNECTIONS                                                                                                                                                                                                                                                             | 10                                     |

| External Connectors<br>PCI703-16/A                                                                                                                                                                                                                                              | <b>10</b><br>10                        |

| Connector Pin Assignments PCI703-16/A PCI703-32/64/A PCI703S-8/16/A                                                                                                                                                                                                             | <b>11</b><br>11<br>11<br>11            |

| Cable Pin Assignments Y-Cable 1 (PCI 703-16/A) Analog -DB37 F Y-Cable 1, Y-Cable 3, Y-Cable 4 (PCI 703-16/64/S/A) Digital -DB37 F                                                                                                                                               | 12<br>12<br>12                         |

| Signal Definitions                                                                                                                                                                                                                                                              | 13                                     |

| Pin Descriptions  Analog Input (ACH0-63)  Analog Input Sensing (AISENSE)  Analog Input Ground (AIGND)  Analog Output Ground (AOGND)  Analog Outputs (DAC0-1)  Digital Input/Outputs (DIO0-7)  Multi Function Digital Input/Outputs (PIO0-7)  TRIG1  Frequency Output (FREQ_OUT) | 13 13 13 13 13 13 13 13 13 13 13 13 13 |

| ADC Scan Clock (SCANCLK) Counters (GPCTR0-1) +5V Power Pin (+5V) | 13<br>13<br>14  |  |  |  |  |

|------------------------------------------------------------------|-----------------|--|--|--|--|

| Digital Ground (DGND)                                            | 14              |  |  |  |  |

| <b>Analog Input Connections</b>                                  | 14              |  |  |  |  |

| Analog Input Connections - SAMPLE-AND-HOLD                       |                 |  |  |  |  |

| Differential Input Pairing                                       | 14              |  |  |  |  |

| 4. PROGRAMMING GUIDE                                             | 15              |  |  |  |  |

| EDR Enhanced API                                                 | 15              |  |  |  |  |

| Digital Inputs/Outputs                                           | 16              |  |  |  |  |

| Reading the Digital Inputs                                       | 16              |  |  |  |  |

| Writing to the Digital Outputs                                   | 16              |  |  |  |  |

| Counters                                                         | 17              |  |  |  |  |

| Writing the initial counter value Configuring a counter          | 17<br>17        |  |  |  |  |

| Controlling the counter gate                                     | 18              |  |  |  |  |

| Analog Output                                                    | 19              |  |  |  |  |

| Writing to a DAC channel                                         | 19              |  |  |  |  |

| Generating a Waveform                                            | 19              |  |  |  |  |

| Analog Input                                                     | 21              |  |  |  |  |

| Reading a single voltage from a channel                          | 21              |  |  |  |  |

| Configuring the ADC subsystem for scanning                       | 21              |  |  |  |  |

| Digital triggering Analog triggering                             | 22<br>22        |  |  |  |  |

| Starting and Stopping the ADC process                            | 24              |  |  |  |  |

| Getting data from the driver buffer                              | 24              |  |  |  |  |

| Querying the ADC subsystem                                       | 25              |  |  |  |  |

| Query Codes                                                      | 26              |  |  |  |  |

| How to use query codes                                           | 26              |  |  |  |  |

| API Call<br>ActiveX Call                                         | 26<br>26        |  |  |  |  |

| How to change the hardware FIFO depth                            | 26              |  |  |  |  |

| How to check for available data                                  | 27              |  |  |  |  |

| How to get the driver buffer size                                | 27              |  |  |  |  |

| How to get the number of ADC channels                            | 27              |  |  |  |  |

| How to check the status of the driver buffer                     | 27              |  |  |  |  |

| 5. CALIBRATION                                                   | 28              |  |  |  |  |

| Requirements                                                     | 28              |  |  |  |  |

| A. SPECIFICATIONS                                                | 29              |  |  |  |  |

| Maximum Transfer Bandwidth – PCI703/S                            | 29              |  |  |  |  |

|                                                                  |                 |  |  |  |  |

| Analog Input Characteristics – PCI703 Input Characteristics      | <b>29</b><br>29 |  |  |  |  |

| Conversion Characteristics                                       | 29              |  |  |  |  |

| Differential Input Amplifier Characteristics (AD620BR)                                         | 29              |

|------------------------------------------------------------------------------------------------|-----------------|

| Analog Input Characteristics – PCI703S  Differential Input Amplifier Characteristics (AD620BR) | <b>30</b><br>30 |

| Sample and Hold Amplifier Characteristics (AD684)                                              | 30              |

| Programmable Gain Amplifier Characteristics                                                    | 30              |

| Input Characteristics                                                                          | 30              |

| Conversion Characteristics                                                                     | 30              |

| Analog Output Characteristics                                                                  | 31              |

| Output Characteristics                                                                         | 31              |

| Conversion Characteristics (Calibrated)                                                        | 31              |

| Voltage Output Characteristics                                                                 | 31              |

| Digital Input/Output Characteristics                                                           | 31              |

| Multifunction Input/Output Characteristics                                                     | 31              |

| Timing Input/Output Characteristics                                                            | 32              |

| Other                                                                                          | 32              |

| B. CONFIGURATION CONSTANTS                                                                     | 33              |

| Query Codes                                                                                    | 33              |

| Error Codes                                                                                    | 33              |

| Digital I/O Codes                                                                              | 33              |

| Analog Input Gain Codes – PCI703-16/32/64/A                                                    | 33              |

| Analog Input Gain Codes – PCI703S-8/16/A                                                       | 33              |

| Analog Input Range Codes – PCI703-16/32/64/A                                                   | 33              |

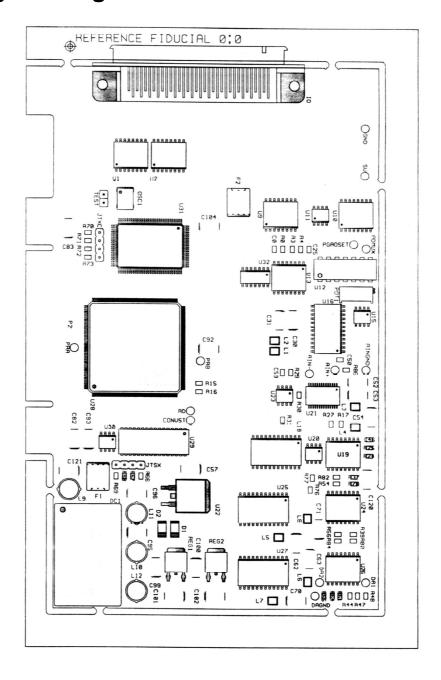

| C. LAYOUT DIAGRAM                                                                              | 35              |

| D. ORDERING INFORMATION                                                                        | 36              |

# **Table of Figures**

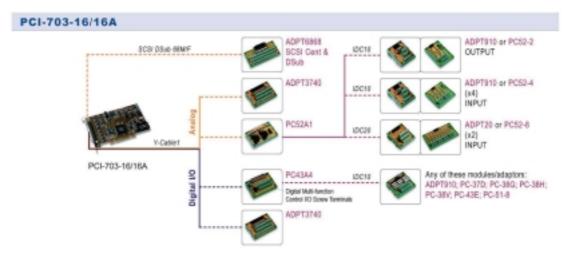

| Figure 3-A PCI 703 Interconnections | . 10 |

|-------------------------------------|------|

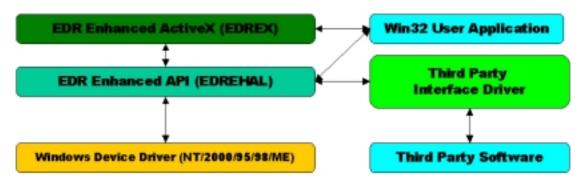

| Figure 4-A EDR Enhanced Design      | . 15 |

### **Table of Tables**

| Table 1-1 PCI703 16/32/64 Versions                                   | 1  |

|----------------------------------------------------------------------|----|

| Table 1-2 PCI703S Versions                                           | 2  |

| Table 2-1 Operating System Support                                   | 3  |

| Table 3-1 Pinouts for PCI703-16/A (External Connector – SCSI 68)     |    |

| Table 3-2 Pinouts for PCI703-32/64/A (External Connector - SCSI 100) | 11 |

| Table 3-3 Pinouts for PCI703S-8/16/A (External Connector – SCSI 68)  | 12 |

| Table 3-4 Y-Cable 1 Analog Connector                                 | 12 |

| Table 3-5 Y-Cable 1,3,4 Digital Connector                            | 12 |

| Table 3-6 Differential Channel Assignment                            |    |

| Table 4-1 Counter Assignment                                         | 17 |

| Table 4-2 Counter Configuration                                      | 18 |

| Table 4-3 Gate Configuration                                         | 18 |

| Table D-1 Ordering Information                                       | 36 |

### 1. Introduction

The PCI703 series are 32-bit PCI bus architecture data acquisition boards. They are available in four models, the 16, 32 and 64 channels analog input board and the sample-and-hold version. The PCI703 contains digital input and output ports, onboard counters, a frequency generator, analog-in and analog-out sub-systems. The PCI703 is a multi-purpose analog board that can be used in many applications.

#### **Features**

The PCI703 does have some very unique features and are short listed below:

- 32-bit PCI bus Revision 2.2 compliant at 33MHz.

- PCI Bus 3.3V compatible.

- PCI Bus Master DMA.

- Fully individually programmable analog-in channels.

- Analog-out waveform generation support.

- Sample-and-hold option.

| Feature                                                                                                                                                                    |                                                                                                                        | PCI703-XX                    |           |   |            | PCI703-XXA                                   |            |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------|-----------|---|------------|----------------------------------------------|------------|--|

| Number of analog input                                                                                                                                                     | PCI703-16                                                                                                              | PCI703-32                    | PCI703-64 | П | PCI703-16A | PCI703-32A                                   | PCI703-64A |  |

| channels                                                                                                                                                                   | 16                                                                                                                     | 32                           | 64        |   | 16         | 32                                           | 64         |  |

| Number of analog output channels A/D resolution @ 400 KHz A/D FIFO depth A/D channel list depth D/A resolution @ 100 KHz D/A FIFO depth D/A waveform generation capability |                                                                                                                        | 0<br>14<br>4096<br>4096<br>- |           |   | 10         | 2<br>14<br>4096<br>4096<br>14<br>4096<br>YES |            |  |

| Triggering capability                                                                                                                                                      | Internal, External.  Analog & Digital.  Post & Pre-Trigger  Internal, External.  Analog & Digital.  Post & Pre-Trigger |                              |           |   |            | l.                                           |            |  |

| Counters                                                                                                                                                                   |                                                                                                                        | 3 3                          |           |   |            |                                              |            |  |

| Frequency generation                                                                                                                                                       | 1                                                                                                                      |                              |           |   | 1          |                                              |            |  |

| Number of digital input/output lines                                                                                                                                       | 8                                                                                                                      |                              |           |   |            |                                              |            |  |

| Number of multi function digital I/O lines                                                                                                                                 | 10 10                                                                                                                  |                              |           |   |            |                                              |            |  |

Table 1-1 PCI703 16/32/64 Versions

| Feature                                    | PCI 703S-8          | PCI 703S-8A         | PCI 703S-16         | PCI 703S-16A        |

|--------------------------------------------|---------------------|---------------------|---------------------|---------------------|

| Number of analog input channels            | 8                   | 16                  | 16                  | 16                  |

| Number of analog output channels           | 0                   | 2                   | 0                   | 2                   |

| A/D resolution @ 400 KHz                   | 14                  |                     | 14                  | 14                  |

| A/D FIFO depth                             | 4096                | 4096                | 4096                | 4096                |

| A/D channel list depth                     | 4096                | 4096                | 4096                | 4096                |

| D/A resolution @ 100 KHz                   | -                   | 14                  | -                   | 14                  |

| D/A FIFO depth                             | -                   | 4096                | -                   | 4096                |

| D/A waveform generation capability         | -                   | YES                 | -                   | YES                 |

| Triggering capability                      | Internal, External. | Internal, External. | Internal, External. | Internal, External. |

|                                            | Analog & Digital.   | Analog & Digital.   | Analog & Digital.   | Analog & Digital.   |

|                                            | Post & Pre-Trigger  | Post & Pre-Trigger  | Post & Pre-Trigger  | Post & Pre-Trigger  |

| Counters                                   | 3                   | 3                   | 3                   | 3                   |

| Frequency generation                       | 1                   | 2                   | 1                   | 1                   |

| Number of digital input/output lines       | 8                   | 8                   | 8                   | 8                   |

| Number of multi function digital I/O lines | 10                  | 10                  | 10                  | 10                  |

Table 1-2 PCI703S Versions

#### **Applications**

The PCI703 can be used in the following applications:

- Vibration monitoring.

- Transducer monitoring.

- Automation and test equipment.

- Signal generation.

- Laboratory training.

- Medical applications.

#### **Key Specifications**

- 14-bit analog input @ 400 KHz.

- Fully programmable sample-and-hold analog input system with triggering.

- 14-bit analog output @ 400 KHz.

- · Independent waveform generation capability.

#### **Software Support**

The PCI703 is supported by EDR Enhanced and comes with an extensive range of examples. The software will help you to get your hardware going very quickly. It also makes it easy to develop complicated control applications quickly. All operating system drivers, utility and test software are supplied on the Eagle Technology CD-Rom. The latest drivers can also be downloaded from the Eagle Technology website. For further support information see the Contact Details section.

#### **Contact Details**

Below are the contact details of Eagle Technology.

#### **Eagle Technology**

PO Box 4376 Cape Town 8000 South Africa Telephone +27 (021) 423 4943 Fax +27 (021) 424 4637 E-Mail eagle@eagle.co.za

Website <a href="http://www.eagledaq.com">http://www.eagledaq.com</a>

### 2. Installation

This chapter describes how to install and configure the PCI703 for the first time. Minimal configuration is necessary; almost all settings are done through software. The PCI BIOS or operating system will take care of all resource assignments.

#### **Package**

PCI703 package will contain the following:

- PCI703 PCI board

- Software CD-Rom

#### **Operating System Support**

PCI703 support the following operating systems

| Board Type     | Revision   | Operating Systems     | Driver Type     |

|----------------|------------|-----------------------|-----------------|

| PCI703-16/A    | Revision 1 | Windows NT/2000       | NT Sys          |

| PCI703-16/A    | Revision 2 | Windows NT/2000/98/ME | NT Sys, WDM PnP |

| PCI703-64/A    | Revision 2 | Windows NT/2000/98/ME | NT Sys, WDM PnP |

| PCI703S-8/16/A | Revision 1 | Windows NT/2000/98/ME | NT Sys, WDM PnP |

**Table 2-1 Operating System Support**

#### Hardware Installation

This section will describe how to install your PCI board into your computer.

• Switch off the computer and disconnect from power socket.

Failure to disconnect all power cables can result in hazardous conditions, as there may be dangerous voltage levels present in externally connected cables.

- Remove the cover of the PC.

- Choose any open PCI slot and insert PCI board

- Insert bracket screw and ensure that the board sits firmly in the PCI socket.

- Replace the cover of the PC.

- Reconnect all power cables and switch the power on.

- The hardware installation is now completed.

#### **Software Installation**

#### Windows 98/2000/ME

Installing the Windows 98/2000 device driver is a very straightforward task. Because it is plug and play Windows will auto detect the PCI board as soon as it is installed. No setup is necessary. You simply have to supply Windows with a device driver.

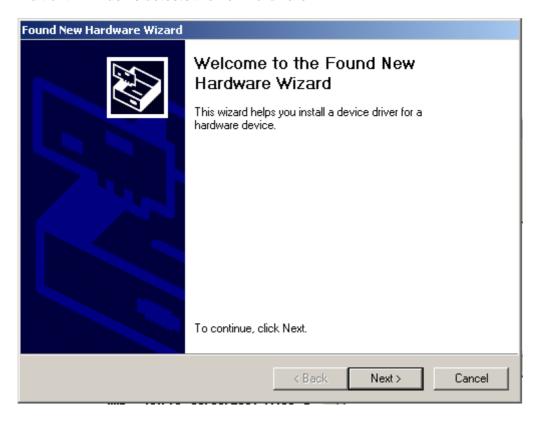

#### Wait until Windows detects the new hardware

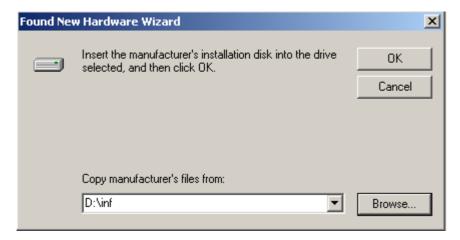

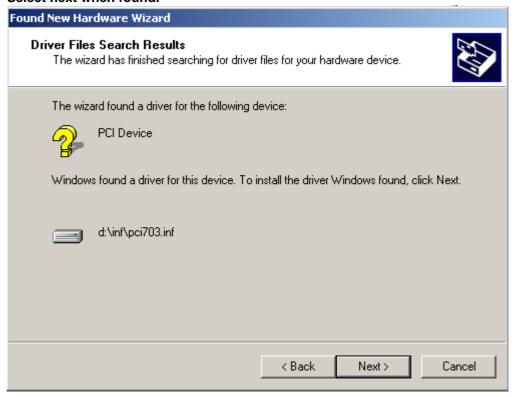

#### **Select Next**

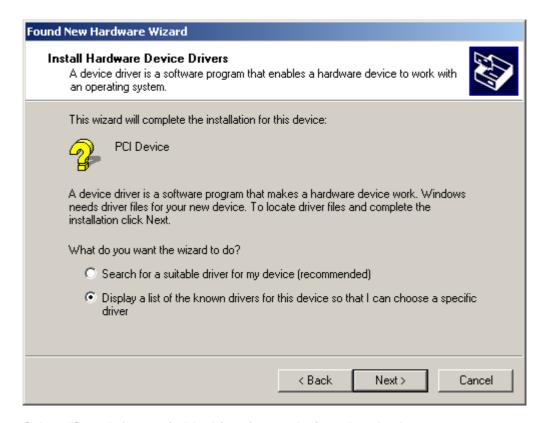

Select "Search for a suitable driver for my device..." and select next

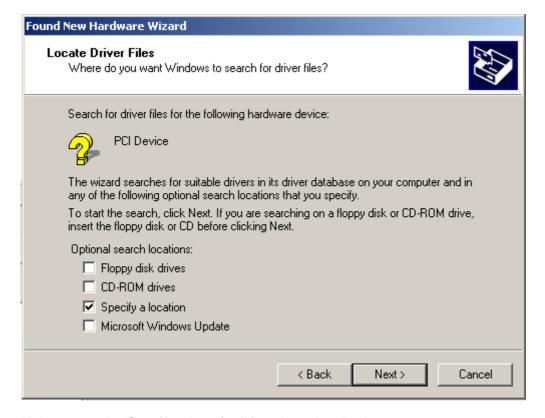

Make sure only "Specify a location" is selected and select next

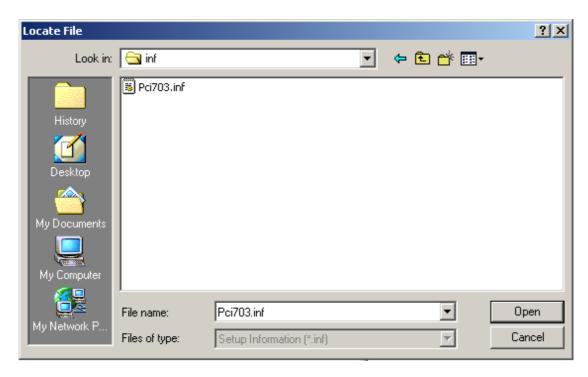

Select the browse button and search for the PCI703.inf file on the Eagle CD-Rom.

The driver is normally located in the <CDROM>:\EDRE\DRIVERS\WDM\PCI703 directory.

The PCI703/16/64 use the same driver. However the PCI703S has a different driver. Please sure that you use the appropriate driver for your board.

#### Select next when found.

#### Select next again.

When done you might have to restart your computer.

#### Post installation

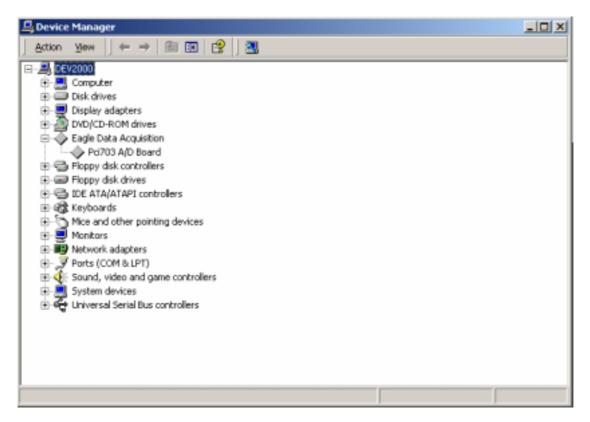

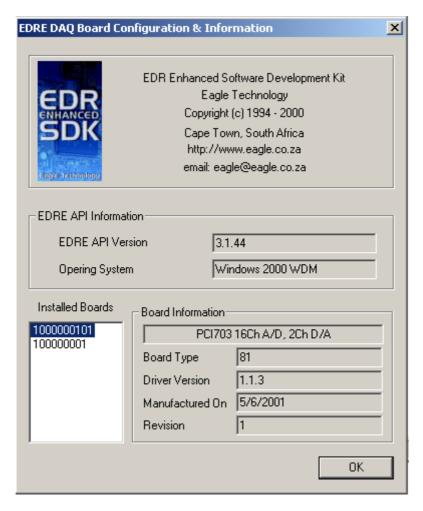

When done with the driver installation the device manager can be open to make sure the installation was a success.

- First make sure that the driver is working properly by opening the *Device Manager*.

- Check under the Eagle Data Acquisition list if your board is listed and working properly. See picture below.

- Clearly you can see that the PCI device is listed and working properly.

- Further open the control panel and then the *EagleDAQ* folder. This dialog should list all installed hardware. Verify your board's properties on this dialog. See picture below

Now the first part of your installation has been completed and ready to install the EDR Enhanced Software Development Kit.

Run edreapi.exe found on the Eagle CD-Rom and follow the on screen instructions

#### **Windows NT**

Windows NT does not require any special setup procedure. The Windows NT driver does not support plug and play. If Windows 2000 detects a new device simply install a default driver, or so called placeholder. This will disable the device in the plug and play manager.

To install the Windows NT drivers simply run *edrewinnt.exe* on the Eagle CD-Rom. This will automatically install the device drivers. Restart your computer when done. Open the *EagleDAQ* folder in the control panel to check if your installation was successful.

#### **Accessories**

The PCI703 has got a wide variety of accessories that it can be connected too. See the Eagle Technology catalog for more information.

### 3. Interconnections

The PCI703 has got one external connector that includes connections for analog-in, analog-out, digital I/O, counters and power. All connections are made through this connector situated on the card's bracket.

A wide variety of genuine accessories available from Eagle Technology also make interfacing to the PCI703 very easy. Accessories are available in the form of cables, screw terminals and application modules.

#### **External Connectors**

#### PCI703-16/A

The PCI703-16/A has a SCSI female centronics 68-way connector. Two types of cables are available, 68-way SCSI-II D-Sub (F) to (M) screened cable connecting to an adaptor ADPT6868 and a Y-Cable 68-way SCSI-II D-Sub (F) to 2 x DB37 (F) connection to application modules and adaptors. Application modules include the PC43A4 and PC52A1. Adaptors would be the ADPT3740. See diagram below.

Figure 3-A PCI 703 Interconnections

#### **Connector Pin Assignments**

#### PCI703-16/A

| Pin | Name       | Pin | Name     | Pin | Name         | Pin | Name    |

|-----|------------|-----|----------|-----|--------------|-----|---------|

| 1   | FREQ_OUT   | 18  | DGND     | 35  | DGND         | 52  | DIO0    |

| 2   | GPCTR0     | 19  | DIO4     | 36  | DGND         | 53  | DGND    |

| 3   | PFI9       | 20  | RESERVED | 37  | PFI8         | 54  | AOGND   |

| 4   | DGND       | 21  | DAC1     | 38  | PFI7         | 55  | AOGND   |

| 5   | PFI6       | 22  | DAC0     | 39  | DGND         | 56  | AIGND   |

| 6   | PFI5       | 23  | ACH15    | 40  | GPCTR1       | 57  | ACH7    |

| 7   | DGND       | 24  | AIGND    | 41  | PFI4         | 58  | ACH14   |

| 8   | +5V        | 25  | ACH6     | 42  | PFI3/CPCTR1  | 59  | AIGND   |

| 9   | DGND       | 26  | ACH13    | 43  | PFI2/CONVERT | 60  | ACH5    |

| 10  | PFI1       | 27  | AIGND    | 44  | DGND         | 61  | ACH12   |

| 11  | PFI0/TRIG1 | 28  | ACH4     | 45  | RESERVED     | 62  | AISENSE |

| 12  | DGND       | 29  | AIGND    | 46  | SCANCLK      | 63  | ACH11   |

| 13  | DGND       | 30  | ACH3     | 47  | DIO3         | 64  | AIGND   |

| 14  | +5V        | 31  | ACH10    | 48  | DIO7         | 65  | ACH2    |

| 15  | DGND       | 32  | AIGND    | 49  | DIO2         | 66  | ACH9    |

| 16  | DIO6       | 33  | ACH1     | 50  | DGND         | 67  | AIGND   |

| 17  | DIO1       | 34  | ACH8     | 51  | DIO5         | 68  | ACH0    |

Table 3-1 Pinouts for PCI703-16/A (External Connector - SCSI 68)

The following cables can be used with this connector.

- Y-Cable 1

- SCSI D-Sub 68 M/F

#### PCI703-32/64/A

| Pin | Name    | Pin | Name              | Pin | Name     | Pin | Name  |

|-----|---------|-----|-------------------|-----|----------|-----|-------|

| 1   | AIGND   | 26  | DIO4              | 51  | ACH16    | 76  | AIGND |

| 2   | AIGND   | 27  | DIO1              | 52  | ACH24    | 77  | ACH36 |

| 3   | ACH0    | 28  | DIO5              | 53  | ACH17    | 78  | ACH44 |

| 4   | ACH8    | 29  | DIO2              | 54  | ACH25    | 79  | ACH37 |

| 5   | ACH1    | 30  | DIO6              | 55  | ACH18    | 80  | ACH45 |

| 6   | ACH9    | 31  | DIO3              | 56  | ACH26    | 81  | ACH38 |

| 7   | ACH2    | 32  | DIO7              | 57  | ACH19    | 82  | ACH46 |

| 8   | ACH10   | 33  | DGND              | 58  | ACH27    | 83  | ACH39 |

| 9   | ACH3    | 34  | +5V               | 59  | ACH20    | 84  | ACH47 |

| 10  | ACH11   | 35  | +5V               | 60  | ACH28    | 85  | ACH48 |

| 11  | ACH4    | 36  | SCANCLK           | 61  | ACH21    | 86  | ACH56 |

| 12  | ACH12   | 37  | EXTSTROBE         | 62  | ACH29    | 87  | ACH49 |

| 13  | ACH5    | 38  | PFI0/TRIG1        | 63  | ACH22    | 88  | ACH57 |

| 14  | ACH13   | 39  | PFI1/TRIG2        | 64  | ACH30    | 89  | ACH50 |

| 15  | ACH6    | 40  | PFI2/CONVERT      | 65  | ACH23    | 90  | ACH58 |

| 16  | ACH14   | 41  | PFI3/GPCTR1_SRC   | 66  | ACH31    | 91  | ACH51 |

| 17  | ACH7    | 42  | PFI4/GPCTR1_GATE  | 67  | ACH32    | 92  | ACH59 |

| 18  | ACH15   | 43  | GPCTR1_OUT        | 68  | ACH40    | 93  | ACH52 |

| 19  | AISENSE | 44  | PFI5/UPDATE       | 69  | ACH33    | 94  | ACH60 |

| 20  | DAC0OUT | 45  | PFI6/WFTRIG       | 70  | ACH41    | 95  | ACH53 |

| 21  | DAC10UT | 46  | PFI7/STARTSCAN    | 71  | ACH34    | 96  | ACH61 |

| 22  | EXTREF  | 47  | PFI8/ GPCTR0_SRC  | 72  | ACH42    | 97  | ACH54 |

| 23  | AOGND   | 48  | PFI9/ GPCTR0_GATE | 73  | ACH35    | 98  | ACH62 |

| 24  | DGND    | 49  | GPCTR0_OUT        | 74  | ACH43    | 99  | ACH55 |

| 25  | DIO0    | 50  | FREQ_OUT          | 75  | AISENSE2 | 100 | ACH63 |

Table 3-2 Pinouts for PCI703-32/64/A (External Connector - SCSI 100)

The following cable can be used with this connector

- Y-Cable 3

- SCSI D-Sub 100 M/M

#### PCI703S-8/16/A

| Pin | Name   | Pin | Name  | Pin | Name   | Pin | Name  |

|-----|--------|-----|-------|-----|--------|-----|-------|

| 1   | AIGND  | 18  | ACH0+ | 35  | AIGND  | 52  | ACH1+ |

| 2   | ACH14- | 19  | DAC0  | 36  | ACH15- | 53  | DAC1  |

| 3   | ACH14+ | 20  | AOGND | 37  | ACH15+ | 54  | AOGND |

| 4   | ACH12- | 21  | DGND  | 38  | ACH13- | 55  | DGND  |

| 5  | ACH12+ | 22 | FREQ_OUT     | 39 | ACH13+ | 56 | NC             |

|----|--------|----|--------------|----|--------|----|----------------|

| 6  | ACH10- | 23 | GPCTR0       | 40 | ACH11- | 57 | GPCTR1         |

| 7  | ACH10+ | 24 | PFI8         | 41 | ACH11+ | 58 | PFI9           |

| 8  | ACH8-  | 25 | PFI6         | 42 | ACH9-  | 59 | PFI7/STARTSCAN |

| 9  | ACH8+  | 26 | PFI4         | 43 | ACH9+  | 60 | PFI5           |

| 10 | AIGND  | 27 | PFI2/CONVERT | 44 | AIGND  | 61 | PFI3           |

| 11 | ACH6-  | 28 | PFI0/TRIG1   | 45 | ACH7-  | 62 | PFI1           |

| 12 | ACH6+  | 29 | +5V          | 46 | ACH7+  | 63 | +5V            |

| 13 | ACH4-  | 30 | DGND         | 47 | ACH5-  | 64 | DGND           |

| 14 | ACH4+  | 31 | DIO6         | 48 | ACH5+  | 65 | DIO7           |

| 15 | ACH2-  | 32 | DIO4         | 49 | ACH3-  | 66 | DIO5           |

| 16 | ACH2+  | 33 | DIO2         | 50 | ACH3+  | 67 | DIO3           |

| 17 | ACH0-  | 34 | DIO0         | 51 | ACH1-  | 68 | DIO1           |

Table 3-3 Pinouts for PCI703S-8/16/A (External Connector - SCSI 68)

The following cable can be used with this connector.

- SCSI D-Sub M/F-S

- Y-Cable 4

#### **Cable Pin Assignments**

#### Y-Cable 1 (PCI 703-16/A) Analog -DB37 F

| Pin | Name  | Pin | Name    |

|-----|-------|-----|---------|

| 1   | AIGND | 20  | ACH0    |

| 2   | ACH1  | 21  | AIGND   |

| 3   | ACH2  | 22  | ACH3    |

| 4   | AIGND | 23  | ACH4    |

| 5   | ACH5  | 24  | AIGND   |

| 6   | ACH6  | 25  | ACH7    |

| 7   | AIGND | 26  | ACH8    |

| 8   | ACH9  | 27  | AIGND   |

| 9   | ACH10 | 28  | ACH11   |

| 10  | AIGND | 29  | ACH12   |

| 11  | ACH13 | 30  | AIGND   |

| 12  | ACH14 | 31  | ACH15   |

| 13  | AIGND | 32  | AISENSE |

| 14  | AIGND | 33  | NC      |

| 15  | l NC  | 34  | NC      |

| 16  | AOGND | 35  | EXTREF  |

| 17  | AOGND | 36  | DAC0    |

| 18  | AOGND | 37  | DAC1    |

| 19  | AOGND |     |         |

Table 3-4 Y-Cable 1 Analog Connector

#### Y-Cable 1, Y-Cable 3, Y-Cable 4 (PCI 703-16/64/S/A) Digital -DB37 F

|      | _            |     |            |

|------|--------------|-----|------------|

| _Pin | Name         | Pin | _Name      |

| 1    | DGND         | 20  | DIO0       |

| 2    | DIO1         | 21  | DGND       |

| 3    | DIO2         | 22  | DIO3       |

| 4    | DGND         | 23  | DIO4       |

| 5    | DIO5         | 24  | DGND       |

| 6    | DIO6         | 25  | DIO7       |

| 7    | DGND         | 26  | +5V        |

| 8    | DGND         | 27  | SCANCLK    |

| 9    | EXTSTROBE    | 28  | PFI0/TRIG1 |

| 10   | DGND         | 29  | +5V        |

| 11   | DGND         | 30  | PFI1/TRIG2 |

| 12   | PFI2/CONVERT | 31  | PFI3       |

| 13   | DGND         | 32  | PFI4       |

| 14   | PFI5         | 33  | PFI6       |

| 15   | DGND         | 34  | GPCTR1     |

| 16   | PFI7         | 35  | PFI8       |

| 17   | DGND         | 36  | PFI9       |

| 18   | GPCTR0       | 37  | FREQ_OUT   |

| 19   | GND          |     |            |

Table 3-5 Y-Cable 1,3,4 Digital Connector

#### **Signal Definitions**

This sections deal with all the signals abbreviations.

| Signal   | Description                                        |  |

|----------|----------------------------------------------------|--|

| ACH0-63  | Analog inputs                                      |  |

| AIGND    | Analog input ground                                |  |

| AOGND    | Analog output ground                               |  |

| AISENSE  | Analog input sensing                               |  |

| DAC0-1   | Analog outputs                                     |  |

| DIO0-7   | Digital inputs/outputs                             |  |

| PFI0-9   | Programmable multi function digital inputs/outputs |  |

| TRIG1    | Digital trigger pin                                |  |

| FREQ_OUT | Frequency generator                                |  |

| SCANCLK  | A/D external convert                               |  |

| GPCTR0-1 | Counters                                           |  |

| +5V      | Power output                                       |  |

| DGND     | Digital ground                                     |  |

**Table 3-2 Signal definitions**

#### **Pin Descriptions**

#### **Analog Input (ACH0-63)**

This is the analog input-channels. Depending on the version there are either 16/64 single ended input channels or 8/32 differential input channels.

#### **Analog Input Sensing (AISENSE)**

This input is used as a reference analog input ground. This is normally used where the measurement point is very far from the PCI703 connector.

#### **Analog Input Ground (AIGND)**

This is the analog reference used by single ended analog inputs.

#### **Analog Output Ground (AOGND)**

This is the analog reference used by analog outputs.

#### **Analog Outputs (DAC0-1)**

The A version of the PCI703 has two analog outputs, DAC0 and DAC1.

#### **Digital Input/Outputs (DIO0-7)**

The DIO0-7 pins are the pins for the digital I/O system.

#### Multi Function Digital Input/Outputs (PIO0-7)

These pins are digital I/O, but can also be used for some other functions. They represent the same function as the digital I/O pins.

#### TRIG1

This pin is used for digital triggering.

#### Frequency Output (FREQ OUT)

This is the output pin of the frequency generator system.

#### **ADC Scan Clock (SCANCLK)**

This input is used to externally clock the ADC system.

#### **Counters (GPCTR0-1)**

These are the outputs of the two user counters.

#### +5V Power Pin (+5V)

This is a +5 volt fused power pin.

#### **Digital Ground (DGND)**

All digital ground signals should be connected to this pin.

#### **Analog Input Connections**

#### **WARNING!!**

All unused analog inputs must be connected to analog ground. The analog input system of the PCI703 can be damaged or become unstable when scanning channels that is left floating.

#### **Analog Input Connections - SAMPLE-AND-HOLD**

#### **WARNING!!**

Don't feed any voltage into the PCI703S while the computer is switched off. This will damage the analog input cicuitry. The sample-and-hold devices will be damaged parmanently and result in multfunctioning of the board.

#### **Differential Input Pairing**

The table below shows the differential channel pairing. This is for the PCI703-16/32/64 boards. Please note that if any channel is assigned as a differential input, the paired channel will automatically become unavailable. The positive channel is the channel that needs to be configured.

| Channel<br>Number | Positive<br>Channel | Negative<br>Channel | Channel<br>Number | Positive<br>Channel | Negative<br>Channel |

|-------------------|---------------------|---------------------|-------------------|---------------------|---------------------|

| 0                 | 0                   | 8                   | 16                | 32                  | 40                  |

| 1                 | 1                   | 9                   | 17                | 33                  | 41                  |

| 2                 | 2                   | 10                  | 18                | 34                  | 42                  |

| 3                 | 3                   | 11                  | 19                | 35                  | 43                  |

| 4                 | 4                   | 12                  | 20                | 36                  | 44                  |

| 5                 | 5                   | 13                  | 21                | 37                  | 45                  |

| 6                 | 6                   | 14                  | 22                | 38                  | 46                  |

| 7                 | 7                   | 15                  | 23                | 39                  | 47                  |

| 8                 | 16                  | 24                  | 24                | 48                  | 56                  |

| 9                 | 17                  | 25                  | 25                | 49                  | 57                  |

| 10                | 18                  | 26                  | 26                | 50                  | 58                  |

| 11                | 19                  | 27                  | 27                | 51                  | 59                  |

| 12                | 20                  | 28                  | 28                | 52                  | 60                  |

| 13                | 21                  | 29                  | 29                | 53                  | 61                  |

| 14                | 22                  | 30                  | 30                | 54                  | 62                  |

| 15                | 23                  | 31                  | 31                | 55                  | 63                  |

**Table 3-6 Differential Channel Assignment**

### 4. Programming Guide

The PCI703 is supplied with a complete software development kit. EDR Enhanced (EDRE SDK) comes with drivers for many operating systems and a common application program interface (API). The API also serves as a hardware abstraction layer (HAL) between the control application and the hardware. The EDRE API makes it possible to write an application that can be used on all hardware with common sub-systems.

The PCI703 can also be programmed at register level, but it is not recommended. A detailed knowledge of the PCI703 is needed and some knowledge about programming Plug and Play PCI devices. We recommend that you only make use of the software provided by Eagle Technology.

#### **EDR Enhanced API**

The EDR Enhanced SDK comes with both ActiveX controls and a Windows DLL API. Examples are provided in many different languages and serve as tutorials. EDRE is also supplied with a software manual and user's guide.

The EDRE API hides the complexity of the hardware and makes it really easy to program the PCI703. It has got functions for each basic sub-system and is real easy to learn.

Figure 4-A EDR Enhanced Design

#### **Digital Inputs/Outputs**

The PCI703 has got 8 digital I/O lines and 10 multi I/O lines that can all be used for digital control purposes. The EDRE API supports auto direction configuration. By writing to or reading from a port, it is automatically configured as an output or input. A port is defined as a collection of simultaneous configurable entities. Thus in the case of the PCI703 each port is only 1-bit wide. In total the PCI703 has got 18 digital ports that can be configured in any direction. Some of which has got more than one function when configured as an input.

#### **Reading the Digital Inputs**

A single call is necessary to read a digital I/O port.

#### **API-CALL**

#### Long EDRE\_DioRead(ulng Sn, ulng Port, ulng \*Value)

The serial number, port, and a pointer to variable to hold the result must be passed by the calling function. A return code will indicate if any errors occurred.

#### **ACTIVEX CALL**

#### Long EDREDioX.Read(long Port)

Only the port-number needs to be passed and the returned value will either hold an error or the value read. If the value is negative an error did occur.

#### Writing to the Digital Outputs

A single call is necessary to write to a digital I/O port.

#### **API-CALL**

#### Long EDRE\_DioWrite(ulng Sn, ulng Port, ulng Value)

The serial number, port, and a value must be passed by the calling function. A return code will indicate if any errors occurred.

#### **ACTIVEX CALL**

#### Long EDREDioX.Write(long Por, ulng Value)

The port number and value to be written needs to be passed and the returned value holds an error or the value read. If the value is negative an error did occur.

#### **Counters**

The counter sub-system is supported by functions to Write, Configure and controlling the gate. There are 3 counters and 1 frequency generator. Only the first two counters and the frequency generator are available for the user. See the table below that shows the relation of the counters and their assigned numbers.

| Counter | Assigned Number     | Description           |

|---------|---------------------|-----------------------|

| 0       | 0                   | Counter 0             |

| 1       | 1                   | Counter 1             |

| 2       | <not used=""></not> | A/D Timing            |

| 3       | 2                   | Frequency Out Counter |

**Table 4-1 Counter Assignment**

#### Writing the initial counter value

A single call is necessary to write a counter's initial load value.

#### **API-CALL**

#### Long EDRE\_CTWrite(ulng Sn, ulng Ct, ulng Value)

The serial number, counter-number, and a value must be passed by the calling function. A return code will indicate if any errors occurred.

#### **ACTIVEX CALL**

#### Long EDRECTX.Write(long Port, ulng Value)

The port number and value to be written needs to be passed and the returned value holds an error or the value read. If the value is negative an error did occur.

#### Configuring a counter

A single call is necessary to configure a counter.

#### **API-CALL**

### Long EDRE\_CTConfig(ulng Sn, ulng Ct, ulng Mode, ulng Type, ulng ClkSrc, ulng GateSrc)

The serial number, counter-number, mode, type, clock source and gate source is needed to specify a counter's configuration. A return code will indicate if any errors occurred.

#### **ACTIVEX CALL**

#### Long EDRECTX.Configure(long ct, long mode, long type, ulng source, ulng gate)

The counter-number, mode, type, clock source and gate source is needed to specify a counter's configuration. A return code will indicate if any errors occurred.

Only the counter mode, clock source and type parameters are used by the PCI703. The table below shows the options for each parameter.

| Parameter | Description                                                              |

|-----------|--------------------------------------------------------------------------|

| Sn        | Serial Number                                                            |

| Ct        | Counter Number:                                                          |

|           | 0 : Counter 0                                                            |

|           | 1 : Counter 1                                                            |

|           | 2 : Frequency Out Counter                                                |

| Mode      | 0:PULSE                                                                  |

|           | 1: TOGGLE                                                                |

|           | Invalid parameter for counter 2                                          |

| Type      | Interrupt on TC:                                                         |

|           | 0 : Disabled                                                             |

|           | 1 : Enabled                                                              |

|           | This bit will only generate a interrupt at the interrupt sub-system. The |

|           | interrupt sub-system must also be setup to generate a PCI Bus            |

|           | interrupt.                                                               |

| Source    | 0 : 20MHz internal clock                                                 |

|           | 1: 100KHz internal clock                                                 |

|           | 2 : External clock <invalid 2="" counter=""></invalid>                   |

| Gate | <not use=""></not> |

|------|--------------------|

|------|--------------------|

**Table 4-2 Counter Configuration**

#### Controlling the counter gate

A single call is necessary to setup/control a counter's gate. This function call is invalid for the frequency generator (counter 2). Counter 2 does not have a gate.

#### **API-CALL**

#### Long EDRE\_CTSoftGate(ulng Sn, ulng Ct, ulng Gate)

The serial number, counter-number and gate are needed to control a counter's gate. A return code will indicate if any errors occurred.

#### **ACTIVEX CALL**

#### Long EDRECTX.SoftGate(ulng Sn, ulng Ct, ulng Gate)

The counter-number and mode is needed to control a counter's gate. A return code will indicate if any errors occurred.

These values are acceptable as a gate source.

| Value | Description   |

|-------|---------------|

| 0     | Gate disabled |

| 1     | Gate enabled  |

**Table 4-3 Gate Configuration**

#### **Analog Output**

The PCI703-X/A version has got 2 DAC channels that support single write and waveform generation. The DAC subsystem uses the onboard counters for timing and a FIFO for data transfer. Data is transfer either by I/O writes or bus master DMA. The DAC subsystem is control via 3 functions: SingleWrite, Control and Configure.

#### Writing to a DAC channel

A single call is necessary to set a voltage on a DAC channel.

#### **API-CALL**

#### Long EDRE\_DAWrite (ulng Sn, ulng Channel, long uVoltage)

The serial number, DAC channel and micro-voltage is needed to set a DAC channel's voltage. A return code will indicate if any errors occurred.

#### **ACTIVEX CALL**

#### Long EDREDAX.Write (ulng Channel, long uVoltage)

The DAC channel and micro-voltage is needed to set a DAC channel's voltage. A return code will indicate if any errors occurred.

#### **Generating a Waveform**

Generating a waveform is basically a two-step process. First configure a channel then start and stop it. Two modes are available, FIFO non-loop mode and pattern mode. The FIFO non-loop mode is continuously updated from software, where pattern only resides inside the FIFO. FIFO non-loop mode is a streaming process. Please note that the frequency is not the total frequency of the waveform, but the update rate of the DAC channel.

# API-CALL Long EDRE\_DAConfig (ulng Sn, ulng Channel, ulng Frequency, ulng ClkSrc, ulng GateSrc, ulng Continuous, ulng Length, long \*uVoltage)

|            |                          | To                                |

|------------|--------------------------|-----------------------------------|

| Parameter  | Type                     | Description                       |

| Sn         | Unsigned long            | Board's serial number             |

| Channel    | Unsigned long            | Channel                           |

|            |                          | 0: DAC Channel 0                  |

|            |                          | 1: DAC Channel 1                  |

| Frequency  | Unsigned long            | Actual value written to counter   |

| ClkSrc     | Unsigned long            | Clock source                      |

|            |                          | 0: Internal 20 MHz                |

|            |                          | 1: Internal 100 KHz               |

|            |                          | 2: External Clock                 |

| GateSrc    | Unsigned long            | Gate Source – Ignored             |

| Continuous | Unsigned long            | Mode                              |

| Length     | Unsigned long            | Buffer length                     |

| uVoltage   | Pointer to a long buffer | Buffer filled with micro voltages |

| Return     | Long                     | Error Code                        |

#### **ACTIVEX CALL**

Long EDRDAX.Configure (long Channel, long Frequency, long ClkSrc, long GateSrc, long Continuous, long Length, long \*uVoltage)

| Parameter | Туре | Description                     |

|-----------|------|---------------------------------|

| Channel   | Long | Channel                         |

|           | 1 -  | 0: DAC Channel 0                |

|           |      | 1: DAC Channel 1                |

| Frequency | Long | Actual value written to counter |

| ClkSrc    | Long | Clock source                    |

|           |      | 0: Internal 20 MHz              |

| GateSrc<br>Continuous<br>Length | Long Long Long Pointer to a long buffer | 1: Internal 100 KHz 2: External Clock Gate Source – Ignored Mode Number of samples in buffer Buffer filled with micro voltages |

|---------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| uVoltage                        | Pointer to a long buffer                | Buffer filled with micro voltages                                                                                              |

| Return                          | Long                                    | Error Code                                                                                                                     |

API-CALL Long EDRE\_DAControl (ulng Sn, ulng Channel, ulng Command)

| Parameter | Туре          | Description           |

|-----------|---------------|-----------------------|

| Sn        | Unsigned long | Board's serial number |

| Channel   | Unsigned long | Channel               |

|           |               | 0: DAC Channel 0      |

|           |               | 1: DAC Channel 1      |

| Command   | Unsigned long | Command Code          |

|           |               | 0: NULL               |

|           |               | 1: Start process      |

|           |               | 2: Stop process       |

|           |               | 3: Pause process      |

|           |               | 4: Continue process   |

| Return    | Long          | Error Code            |

# ACTIVEX CALL Long EDREDAX.Control (long Channel, long Command)

| Parameter | Туре | Description         |

|-----------|------|---------------------|

| Channel   | Long | Channel             |

|           | _    | 0: DAC Channel 0    |

|           |      | 1: DAC Channel 1    |

| Command   | Long | Command Code        |

|           | _    | 0: NULL             |

|           |      | 1: Start process    |

|           |      | 2: Stop process     |

|           |      | 3: Pause process    |

|           |      | 4: Continue process |

| Return    | Long | Error Code          |

#### **Analog Input**

The PCI703 has got a very unique A/D subsystem and is fully configurable. Configuration includes dynamic range, gain, reference and differential or single ended. Each of these settings can be applied to an individual channel while scanning.

Please not that although the PCI703 and PCI703S is similar in operation and uses the same functions, not all parameters apply to the PCI703S. This is because the PCI703S only supports bipolar-differential mode. The frequency is also implemented differently. Where the frequency is the timer tic for the ADC on the PCI703, it is the total frequency on the PCI703S.

#### Reading a single voltage from a channel

To read a single ADC channel you need to know the voltage range and gain.

API-CALL

Long EDRE\_ADSingle (ulng Sn, ulng Channel, ulng Gain, ulng Range, plong uVoltage)

| F | Parameter | Туре              | Description                          |

|---|-----------|-------------------|--------------------------------------|

|   | Sn        | Unsigned long     | Board's serial number                |

|   | Channel   | Unsigned long     | ADC Channel                          |

|   | Gain      | Unsigned long     | Gain code. See appendix for details  |

|   | Range     | Unsigned long     | Range code. See appendix for details |

|   | uVoltage  | Pointer to a long | Voltage read from channel            |

|   | Return    | Long              | Error Code                           |

# ACTIVEX CALL Long EDREADX.SingleRead (long Channel)

| Parameter | Туре | Description                    |

|-----------|------|--------------------------------|

| Channel   | Long | ADC Channel                    |

| Return    | Long | Voltage returned from channel. |

Make sure to set the *Gain* and *Range* properties of the ADC ActiveX control. This will in turn set the range and gain when reading the ADC channel.

#### Configuring the ADC subsystem for scanning

This is the most complicated part of configuring the PCI703 for auto scanning. Make sure that you use the correct format when applying the channel list configuration. There are many loopholes and care should be taken when implementing code to configure the PCI703.

#### **API-CALL**

### Long EDRE\_ADConfig (ulng Sn, pulng Freq, ulng ClkSrc, ulng Burst, ulng Range, pulng ChanList, pulng GainList, ulng ListSize)

The following parameters must be specified when configuring the ADC sub-system.

| Parameter | Туре                           | Description         |                                                                                         |  |  |  |  |  |  |  |

|-----------|--------------------------------|---------------------|-----------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Sn        | Unsigned long                  | Board's serial num  | ber.                                                                                    |  |  |  |  |  |  |  |

| Freq      | Pointer to an<br>unsigned long | Sampling frequenc   | Sampling frequency. The actual sampling frequency will be returned with this parameter. |  |  |  |  |  |  |  |

| ClkSrc    | Unsigned long                  | This parameter is u | ised to configure the clocking system of the ADC.                                       |  |  |  |  |  |  |  |

|           |                                | Format              |                                                                                         |  |  |  |  |  |  |  |

|           |                                | Offset (bits)       | Description                                                                             |  |  |  |  |  |  |  |

|           |                                | 0                   | Clock Source (C0-C7)                                                                    |  |  |  |  |  |  |  |

|           |                                |                     | 0: Undefined                                                                            |  |  |  |  |  |  |  |

|           |                                |                     | 1: Internal                                                                             |  |  |  |  |  |  |  |

|           |                                |                     | 2: External – PIN PFI2/CONVERT                                                          |  |  |  |  |  |  |  |

|           |                                | 8                   | Trigger Source (T0-T3)                                                                  |  |  |  |  |  |  |  |

|           |                                |                     | 0: Internal                                                                             |  |  |  |  |  |  |  |

|           |                                |                     | 1: Reference – DAC CHAN 1 (NOT SUPPORTED BY PCI 703S)                                   |  |  |  |  |  |  |  |

|           |                                |                     | 2: External – PIN TRIG1                                                                 |  |  |  |  |  |  |  |

|                                        |                                                                                     |                             | 12                                           |                                      | 0: Pi<br>1: N<br>2: R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ger Mo<br>ositive<br>egative<br>ising<br>alling   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Only ap                                                                                          | oplies t                                                                                                   | o the re                                            | eferend              | ce trigg       | er sou  | rce. (M | 10-M3) |        |             |

|----------------------------------------|-------------------------------------------------------------------------------------|-----------------------------|----------------------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------|----------------|---------|---------|--------|--------|-------------|

|                                        |                                                                                     | Exam<br>15                  | ole La                                       | yout:<br>13                          | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11                                                | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9                                                                                                | 0                                                                                                          | T -                                                 | Ι,                   |                |         | 1       | 1      | 1      | _           |