The following document contains information on Cypress products. Although the document is marked with the name "Spansion" and "Fujitsu", the company that originally developed the specification, Cypress will continue to offer these products to new and existing customers.

#### **Continuity of Specifications**

There is no change to this document as a result of offering the device as a Cypress product. Any changes that have been made are the result of normal document improvements and are noted in the document history page, where supported. Future revisions will occur when appropriate, and changes will be noted in a document history page.

#### **Continuity of Ordering Part Numbers**

Cypress continues to support existing part numbers. To order these products, please use only the Ordering Part Numbers listed in this document.

#### For More Information

Please contact your local sales office for additional information about Cypress products and solutions.

#### **About Cypress**

Cypress (NASDAQ: CY) delivers high-performance, high-quality solutions at the heart of today's most advanced embedded systems, from automotive, industrial and networking platforms to highly interactive consumer and mobile devices. With a broad, differentiated product portfolio that includes NOR flash memories, F-RAM™ and SRAM, Traveo™ microcontrollers, the industry's only PSoC® programmable system-on-chip solutions, analog and PMIC Power Management ICs, CapSense® capacitive touch-sensing controllers, and Wireless BLE Bluetooth® Low-Energy and USB connectivity solutions, Cypress is committed to providing its customers worldwide with consistent innovation, best-in-class support and exceptional system value.

#### Colophon

The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for any use that includes fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for any use where chance of failure is intolerable (i.e., submersible repeater and artificial satellite). Please note that Spansion will not be liable to you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products. Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions. If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Law of Japan, the US Export Administration Regulations or the applicable laws of any other country, the prior authorization by the respective government entity will be required for export of those products.

#### Trademarks and Notice

The contents of this document are subject to change without notice. This document may contain information on a Spansion product under development by Spansion. Spansion reserves the right to change or discontinue work on any product without notice. The information in this document is provided as is without warranty or guarantee of any kind as to its accuracy, completeness, operability, fitness for particular purpose, merchantability, non-infringement of third-party rights, or any other warranty, express, implied, or statutory. Spansion assumes no liability for any damages of any kind arising out of the use of the information in this document.

Copyright © 2013 Spansion Inc. All rights reserved. Spansion<sup>®</sup>, the Spansion logo, MirrorBit<sup>®</sup>, MirrorBit<sup>®</sup> Eclipse<sup>TM</sup>, ORNAND<sup>TM</sup> and combinations thereof, are trademarks and registered trademarks of Spansion LLC in the United States and other countries. Other names used are for informational purposes only and may be trademarks of their respective owners.

# F<sup>2</sup>MC-16FX FAMILY 16-BIT MICROCONTROLLER MB96340, MB88121

# INTERFACING MB96340 TO MB88121

**APPLICATION NOTE**

# **Revision History**

| Date       | Issue                    |

|------------|--------------------------|

| 2008-03-25 | V1.0, MSt<br>First draft |

|            |                          |

This document contains 38 pages.

# Warranty and Disclaimer

To the maximum extent permitted by applicable law, Fujitsu Microelectronics Europe GmbH restricts its warranties and its liability for **all products delivered free of charge** (eg. software include or header files, application examples, target boards, evaluation boards, engineering samples of IC's etc.), its performance and any consequential damages, on the use of the Product in accordance with (i) the terms of the License Agreement and the Sale and Purchase Agreement under which agreements the Product has been delivered, (ii) the technical descriptions and (iii) all accompanying written materials. In addition, to the maximum extent permitted by applicable law, Fujitsu Microelectronics Europe GmbH disclaims all warranties and liabilities for the performance of the Product and any consequential damages in cases of unauthorised decompiling and/or reverse engineering and/or disassembling. **Note, all these products are intended and must only be used in an evaluation laboratory environment**.

- 1. Fujitsu Microelectronics Europe GmbH warrants that the Product will perform substantially in accordance with the accompanying written materials for a period of 90 days form the date of receipt by the customer. Concerning the hardware components of the Product, Fujitsu Microelectronics Europe GmbH warrants that the Product will be free from defects in material and workmanship under use and service as specified in the accompanying written materials for a duration of 1 year from the date of receipt by the customer.

- 2. Should a Product turn out to be defect, Fujitsu Microelectronics Europe GmbH's entire liability and the customer's exclusive remedy shall be, at Fujitsu Microelectronics Europe GmbH's sole discretion, either return of the purchase price and the license fee, or replacement of the Product or parts thereof, if the Product is returned to Fujitsu Microelectronics Europe GmbH in original packing and without further defects resulting from the customer's use or the transport. However, this warranty is excluded if the defect has resulted from an accident not attributable to Fujitsu Microelectronics Europe GmbH, or abuse or misapplication attributable to the customer or any other third party not relating to Fujitsu Microelectronics Europe GmbH.

- 3. To the maximum extent permitted by applicable law Fujitsu Microelectronics Europe GmbH disclaims all other warranties, whether expressed or implied, in particular, but not limited to, warranties of merchantability and fitness for a particular purpose for which the Product is not designated.

- 4. To the maximum extent permitted by applicable law, Fujitsu Microelectronics Europe GmbH's and its suppliers' liability is restricted to intention and gross negligence.

#### NO LIABILITY FOR CONSEQUENTIAL DAMAGES

To the maximum extent permitted by applicable law, in no event shall Fujitsu Microelectronics Europe GmbH and its suppliers be liable for any damages whatsoever (including but without limitation, consequential and/or indirect damages for personal injury, assets of substantial value, loss of profits, interruption of business operation, loss of information, or any other monetary or pecuniary loss) arising from the use of the Product.

Should one of the above stipulations be or become invalid and/or unenforceable, the remaining stipulations shall stay in full effect

#### Interfacing MB96340 TO MB88121 Contents

# Contents

| R | EVISI           | ON HIST    | ORY        |                                                 | 2  |

|---|-----------------|------------|------------|-------------------------------------------------|----|

| W | ARRA            | ANTY AN    | ND DISCL   | AIMER                                           | 3  |

| C | ONTE            | NTS        |            |                                                 | 4  |

| 1 | INTR            | ODUCT      | ION        |                                                 | 6  |

| 2 |                 |            |            | PLE MB96F348RS – MB88121B                       |    |

|   |                 |            |            |                                                 |    |

| 3 |                 |            |            |                                                 |    |

|   | 3.1             |            |            | ode                                             |    |

|   | 3.3             |            |            | eration mode                                    |    |

|   | 3.4             |            | •          | the external bus interface                      |    |

|   | J. <del>T</del> | 3.4.1      |            | Bus Mode register (EBM)                         |    |

|   |                 | 3.4.2      |            | Bus Clock and Function register                 |    |

|   |                 | 3.4.3      |            | Bus Address output Enable registers (EBAE[2:0]) |    |

|   |                 | 3.4.4      |            | Bus Control Signal register (EBCS)              |    |

|   |                 | 3.4.5      |            | Area Configuration registers (EACH/EACL[5:0])   |    |

|   |                 | 3.4.6      |            | s EAS[5:2]                                      |    |

|   |                 | 3.4.7      | •          | in file start.asm                               |    |

|   |                 | 3.4.8      | _          | s interface functions at pins on MB96F348RS     |    |

|   | 3.5             | Simplifi   |            | diagram of MB88121B                             |    |

|   |                 | 3.5.1      | MB8812     | 1 read timing                                   | 27 |

|   |                 | 3.5.2      | MB8812     | 1 write timing                                  | 28 |

|   | 3.6             | Initialisa | ation sequ | ence of MB88121                                 | 29 |

|   | 3.7             | Interrup   | ts         |                                                 | 30 |

|   |                 | 3.7.1      | CC interr  | rupt                                            | 30 |

|   |                 | 3.7.2      | MCU ext    | ernal interrupt                                 | 31 |

|   |                 |            | 3.7.2.1    | External interrupt configuration registers      | 31 |

|   |                 |            | 3.7.2.2    | I/O port register DDR and PIER                  | 32 |

|   |                 |            | 3.7.2.3    | Interrupt vector table                          | 33 |

|   | 3.8             | Debugg     | jing suppo | ort                                             | 35 |

|   | 3.9             | Stop W     | atch pin   |                                                 | 35 |

| 4 | REF             | ERENCE     |            |                                                 | 36 |

| 5 | APP             | ENDIX      |            |                                                 | 37 |

|   | 5.1             |            |            |                                                 |    |

|   |                 |            |            |                                                 |    |

#### Interfacing MB96340 TO MB88121 Contents

#### 1 Introduction

FUJITSU Microelectronics Europe GmbH offers a stand alone FlexRay Communication Controller, MB88121 series, which supports parallel and serial connectivity to Host MCU. The MB88121 series supports a parallel Bus interface modes, 16-bit multiplexed mode, especially for Fujitsu 16FX MCU. The 16FX MCU MB96340 series is supporting a 16-bit multiplexed bus interface. The following discusses Hardware and Software requirement based on MB96F348RS series.

#### Note:

Not all MB96300 devices support an multiplexed external bus interface.

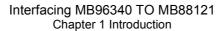

# 2 Connection example MB96F348RS – MB88121B

A connection example is summarized in the following table. All pins of the communication controller (CC) are divided into 7 categories:

- External bus interface: CC pins in connection with MCU pins

- · CC mode pins

- · CC debug pins

- · CC stop watch trigger pin

- CC pins in connection with physical layer transceiver

- CC power supply pins

- CC external clock pin

#### Note:

- 1. The connection of the interrupt pins is application-specific. The table here shows only an example.

- 2. The CC reset pin can be controlled by MCU reset pin or by an independent circuitry.

- 3. In this application note external bus area 2 is configured for MB88121B. Other areas can also be used.

- 4. For the power supply it should be noticed that MB88121B is a single voltage supply chip. All power supply pins should have the same supply voltage between 3.3V and 5V.

#### Interfacing MB96340 TO MB88121 Chapter 2 Connection example MB96F348RS – MB88121B

|                 | Exte                  | rnal bus interface: C | C pins in conn | ection with MCU p | ins                          |

|-----------------|-----------------------|-----------------------|----------------|-------------------|------------------------------|

| CC pin Nr       | Name                  | Functi                | on             | MCU pin Nr        | Name                         |

| 53              | AD10                  |                       |                | 87                | P01_2/AD10                   |

| 54              | AD9                   |                       |                | 86                | P01_1/AD09                   |

| 55              | AD8                   |                       |                | 85                | P01_0/AD08                   |

| 56              | AD7                   |                       |                | 84                | P00_7/AD07                   |

| 57              | AD6                   | Address/da            | ita hus        | 83                | P00_6/AD06                   |

| 58              | AD5                   | MCU⇔                  |                | 82                | P00_5/AD05                   |

| 59              | AD4                   |                       |                | 81                | P00_4/AD04                   |

| 60              | AD3                   |                       |                | 80                | P00_3/AD03                   |

| 61              | AD2                   |                       |                | 79                | P00_2/AD02                   |

| 62              | AD1                   | 1                     |                | 78                | P00_1/AD01                   |

| 63              | AD0                   | 1                     |                | 77                | P00_0/AD00                   |

| CC pin Nr       | Name                  | Function              | on             | MCU pin Nr        | Name                         |

| 46              | D15                   |                       |                | 96                | P01_7/AD15                   |

| 47              | D14                   | Data b                | 119            | 95                | P01_6/AD14                   |

| 50              | D13                   | MCU⇔                  |                | 94                | P01_5/AD13                   |

| 51              | D12                   |                       |                | 89                | P01_4/AD12                   |

| 52              | D11                   |                       |                | 88                | P01_3/AD11                   |

| CC pin Nr       | Name                  | Function              | on             | MCU pin Nr        | Name                         |

| 10              | INT0 <sup>1</sup>     |                       |                | 46                | P07_1/INT1                   |

| 34              | INT1                  | Interrupt o           | outout         | 47                | P07_2/INT2                   |

| 35              | INT2                  | CC=>M                 | -              | 48                | P07_3/INT3                   |

| 36              | INT3                  | -                     |                | 49                | P07_4/INT4                   |

| 37              | INT4                  |                       |                | 50                | P07_5/INT5                   |

| CC pin Nr       | Name                  | Functi                | on             | MCU pin Nr        | Name                         |

| 6               | $\overline{RST}^{-2}$ | Reset                 |                | 1                 | 1                            |

| 15              | BCLK                  | Bus clock             | 1              | 12                | P03_7/ECLK                   |

| 19              | $\overline{CS}$       | Chip select           |                | 72                | P09_5/CS2 <sup>3</sup>       |

| 20              | $\overline{RD}$       | Read enable           | MCU=>CC        | 6                 | P03_1/RDX                    |

| 21              | WR                    | Write enable          | -              | 7                 | P03_2/WRLX/WRX               |

| 22              | ALE                   | Address latch enable  | -              | 5                 | P03_0/ALE                    |

| 27              | RDY                   | Ready signal          | 00 . 11017     | 11                | P03_6/RDY                    |

| 31              | DMA_REQ               | DMA request           | CC=>MCU        | 55                | P07_6/INT6                   |

|                 | 1                     | C                     | C mode pins    |                   |                              |

|                 |                       | - ··                  | I/O type       | 1                 | ogic value                   |

| CC pin Nr       | Name                  | Function              | i/O type       |                   | ogic value                   |

| CC pin Nr<br>64 | Name<br>MD2           | Mode selection        | I/O type       | 1                 | 16bit parallel bus interface |

|                                                       | <u> </u>                                                      |                                                                                                                                                                                                                         | VID90F346K3 — IVID0012                                                                                                                                                                            | ,                                                         |  |

|-------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--|

| 5                                                     | MD0                                                           |                                                                                                                                                                                                                         |                                                                                                                                                                                                   | <u> </u>                                                  |  |

| _                                                     |                                                               |                                                                                                                                                                                                                         | 0                                                                                                                                                                                                 |                                                           |  |

| 28                                                    | MDE2                                                          | Extended mode                                                                                                                                                                                                           | 0                                                                                                                                                                                                 | Multiplexed mode                                          |  |

| 29                                                    | MDE1                                                          | selection                                                                                                                                                                                                               | 0                                                                                                                                                                                                 | for 16FX                                                  |  |

| 30                                                    | MDE0                                                          |                                                                                                                                                                                                                         | 1                                                                                                                                                                                                 |                                                           |  |

|                                                       |                                                               | CC debug                                                                                                                                                                                                                | -                                                                                                                                                                                                 |                                                           |  |

| CC pin Nr                                             | Name                                                          | Function                                                                                                                                                                                                                | I/O type                                                                                                                                                                                          | Configuration register                                    |  |

| 7                                                     | SDS                                                           | Start of dynamic segmen                                                                                                                                                                                                 | nt OUT                                                                                                                                                                                            |                                                           |  |

| 8                                                     | CYCS0                                                         | Cycle 0 start                                                                                                                                                                                                           | OUT                                                                                                                                                                                               |                                                           |  |

| 14                                                    | CYCS                                                          | Cycle start                                                                                                                                                                                                             | OUT                                                                                                                                                                                               |                                                           |  |

| 23                                                    | MT                                                            | Macrotick start                                                                                                                                                                                                         | OUT                                                                                                                                                                                               | Debug support register                                    |  |

| 38                                                    | MBSU_TX1                                                      |                                                                                                                                                                                                                         |                                                                                                                                                                                                   | DBGS                                                      |  |

| 39                                                    | MBSU_RX1                                                      | Message buffer status updat                                                                                                                                                                                             | te port OUT                                                                                                                                                                                       |                                                           |  |

| 44                                                    | MBSU_TX2                                                      | Message buller status upuat                                                                                                                                                                                             | le port OO1                                                                                                                                                                                       |                                                           |  |

| 45                                                    | MBSU_RX2                                                      |                                                                                                                                                                                                                         |                                                                                                                                                                                                   |                                                           |  |

|                                                       |                                                               | CC stop watch                                                                                                                                                                                                           | trigger pin                                                                                                                                                                                       |                                                           |  |

| CC pin Nr                                             | Name                                                          | I/O type                                                                                                                                                                                                                | Function                                                                                                                                                                                          |                                                           |  |

| 9                                                     | STPW                                                          | IN captures actu                                                                                                                                                                                                        | After stop watch is triggered (rising or falling edge), register STF captures actual cycle counter and macrotick value, register STF captures slot counter values for channel A and B.            |                                                           |  |

|                                                       |                                                               | capti                                                                                                                                                                                                                   | ures slot counter values f                                                                                                                                                                        | or channel A and B.                                       |  |

|                                                       | C                                                             | capti<br>C pins in connection with p                                                                                                                                                                                    |                                                                                                                                                                                                   |                                                           |  |

| CC pin Nr                                             | Name                                                          | -                                                                                                                                                                                                                       |                                                                                                                                                                                                   |                                                           |  |

| CC pin Nr                                             |                                                               | C pins in connection with p                                                                                                                                                                                             | hysical layer transceive                                                                                                                                                                          | r                                                         |  |

|                                                       | Name                                                          | C pins in connection with p                                                                                                                                                                                             | hysical layer transceive                                                                                                                                                                          | r                                                         |  |

| 11                                                    | Name<br>TXDA                                                  | Function  Data transmission                                                                                                                                                                                             | hysical layer transceive I/O type OUT                                                                                                                                                             | r<br>Connection                                           |  |

| 11                                                    | Name TXDA  TXENA                                              | Function  Data transmission ena                                                                                                                                                                                         | hysical layer transceive  I/O type  OUT  able  OUT                                                                                                                                                | r<br>Connection                                           |  |

| 11<br>12<br>13                                        | TXDA  TXENA  RXDA                                             | Function  Data transmission ena  Data reception                                                                                                                                                                         | hysical layer transceive  I/O type  OUT  able  IN  IN                                                                                                                                             | r<br>Connection                                           |  |

| 11<br>12<br>13<br>24                                  | TXDA  TXENA  RXDA  RXDB                                       | Function  Data transmission ena  Data reception  Data reception                                                                                                                                                         | hysical layer transceive  I/O type  OUT  able  OUT  IN  IN                                                                                                                                        | Connection  Channel A transceiver                         |  |

| 11<br>12<br>13<br>24<br>25                            | TXDA  TXENA  RXDA  RXDB  TXENB                                | EC pins in connection with pine Function  Data transmission  Channel transmission enain Data reception  Data reception  Channel transmission enain Data reception                                                       | hysical layer transceive  I/O type  OUT  Able  IN  IN  Able  OUT  OUT  OUT                                                                                                                        | Connection  Channel A transceiver                         |  |

| 11<br>12<br>13<br>24<br>25                            | TXDA  TXENA  RXDA  RXDB  TXENB                                | Function  Data transmission ena  Data reception  Data reception  Channel transmission ena  Data reception  Data reception  Data transmission ena  Data reception                                                        | hysical layer transceive  I/O type  OUT  Able  IN  IN  Able  OUT  OUT  OUT                                                                                                                        | Connection  Channel A transceiver                         |  |

| 11<br>12<br>13<br>24<br>25<br>26                      | TXDA  TXENA  RXDA  RXDB  TXENB  TXDB                          | Function  Data transmission ena  Data reception  Data reception  Channel transmission ena  Data reception  Data reception  Data transmission ena  Data reception                                                        | hysical layer transceive  I/O type  OUT  able OUT  IN  IN  able OUT  OUT                                                                                                                          | Connection  Channel A transceiver                         |  |

| 11 12 13 24 25 26 CC pin Nr                           | Name TXDA  TXENA  RXDA  RXDB  TXENB  TXDB                     | Function  Data transmission ena  Data reception  Data reception  Channel transmission ena  Data reception  Channel transmission ena  Channel transmission ena  Channel transmission ena  Channel transmission  CC power | hysical layer transceive  I/O type  OUT  able OUT  IN  IN  able OUT  OUT  r pins  Function                                                                                                        | Channel A transceiver  Channel B transceiver              |  |

| 11 12 13 24 25 26 CC pin Nr 1,17,33,49                | Name TXDA  TXENA  RXDA  RXDB  TXENB  TXDB  Name VSS           | Function  Data transmission ena  Data reception  Data reception  Channel transmission ena  Data reception  Channel transmission ena  Channel transmission ena  Channel transmission ena  Single pow                     | hysical layer transceive  I/O type  OUT  able OUT  IN  IN  able OUT  OUT  OUT  r pins  Function  OV Ground                                                                                        | Channel A transceiver  Channel B transceiver  3.3v and 5v |  |

| 11 12 13 24 25 26 CC pin Nr 1,17,33,49 16, 32, 48     | Name TXDA  TXENA  RXDA  RXDB  TXENB  TXDB  Name VSS  VCC 4    | Function  Data transmission ena  Data reception  Data reception  Channel transmission ena  Data reception  Channel transmission ena  Channel transmission ena  Channel transmission ena  Single pow                     | hysical layer transceive  I/O type  OUT  able OUT  IN  IN  able OUT  OUT  rpins  Function OV Ground  ver supply input between apply stabilization capacito                                        | Channel A transceiver  Channel B transceiver  3.3v and 5v |  |

| 11 12 13 24 25 26 CC pin Nr 1,17,33,49 16, 32, 48     | Name TXDA  TXENA  RXDA  RXDB  TXENB  TXDB  Name VSS  VCC 4    | Function  Data transmission ena  Data reception  Data reception  Channel transmission ena  Data reception  Channel transmission ena  Data transmission ena  Data transmission  CC power  Single pow  Power sup          | hysical layer transceive  I/O type  OUT  able OUT  IN  IN  able OUT  OUT  rpins  Function OV Ground  ver supply input between apply stabilization capacito                                        | Channel A transceiver  Channel B transceiver  3.3v and 5v |  |

| 11 12 13 24 25 26  CC pin Nr 1,17,33,49 16, 32, 48 18 | Name TXDA  TXENA  RXDA  RXDB  TXENB  TXDB  Name VSS  VCC 4  C | Function  Data transmission ena  Data reception  Data reception  Channel transmission ena  Data reception  Channel transmission ena  Data transmission ena  Data transmission  CC power  Single pow  Power sup          | hysical layer transceive  I/O type  OUT  Able OUT  IN  IN  Able OUT  OUT  OUT  Ppins  Function  OV Ground  Ver supply input between a copy stabilization capacito  Clock pin  Function  4MHz, 5MI | Connection  Channel A transceiver  Channel B transceiver  |  |

#### Interfacing MB96340 TO MB88121 Chapter 2 Connection example MB96F348RS – MB88121B

# 3 Configuration

This chapter introduces the concrete configuration of MB96F348RS series

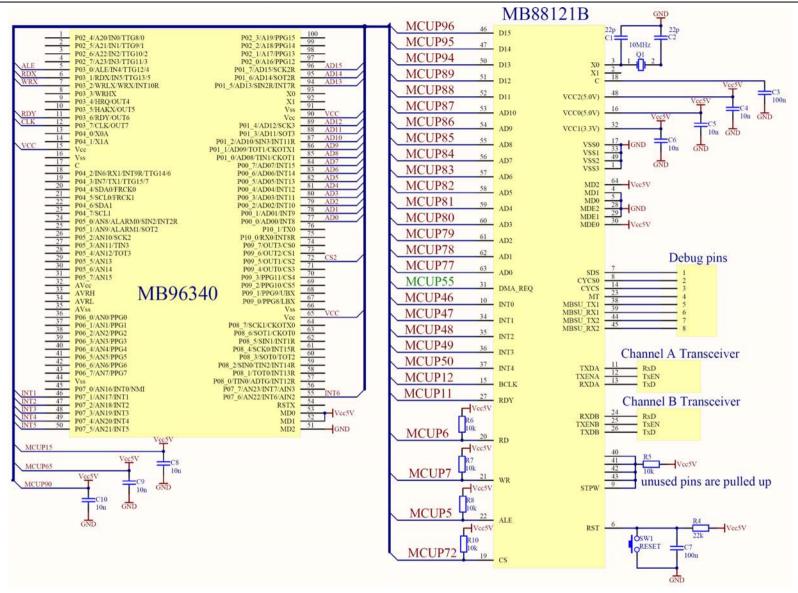

#### 3.1 MB96340 series

MB96340 series is based on Fujitsu's 16FX architecture. Some features of this MCU family are listed below.

| Flash/ROM                  | RAM       | MB96340 series                                      |

|----------------------------|-----------|-----------------------------------------------------|

| 128KB                      | 6KB       | MB96344R,MB96344Y                                   |

| 288KB                      | 16KB      | MB96F346R, MB96346R, MB96F346Y, MB96346Y, MB96F346A |

| 416KB                      | 16KB      | MB96F347R, MB96347R, MB96F347Y, MB96347Y, MB96F347A |

| 544KB                      | 24KB      | MB96F348R, MB96F348Y, MB96F348A                     |

| Main Flash<br>544KB        |           | MB96F348C, MB96F348H, MB96F348T                     |

| Satellite<br>Flash<br>32KB | 24KB      | WIDSOT 340C, WIDSOT 34011, WIDSOT 3401              |

| External in                | terrupts  | 16 channels                                         |

| External bus               | interface | Multiplexed mode                                    |

| Chip selec                 | t signal  | 6                                                   |

Table 3-1 MB96340 feature

Figure 3-1 Block diagram of the MB96340 series

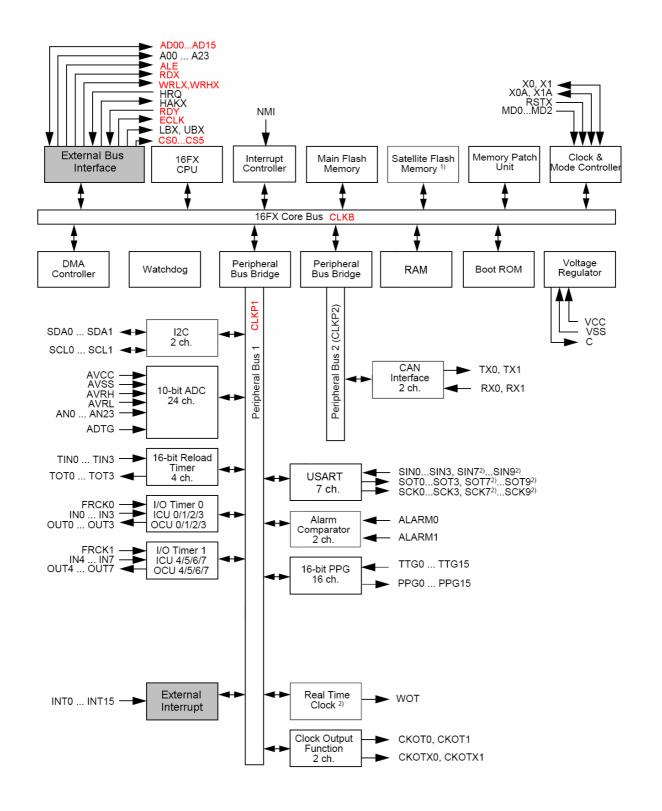

#### 3.2 MCU operation mode

The MCU operates in the internal ROM external bus mode. That means the internal Flash is accessible and in addition the external bus interface might be enabled during initialization phase of the MCU

The configuration of mode pins and file start.asm are listed below.

| Mode pin setting | Operation<br>mode | Description                                                                                 |

|------------------|-------------------|---------------------------------------------------------------------------------------------|

| MD2=0            | Internal          | The heat vector (upor program start address) is read from                                   |

| MD1=1            | vector<br>mode    | The boot vector (user program start address) is read from internal memory address 0xFFFFDC. |

| MD0=1            | mode              |                                                                                             |

Table 3-2 Configuration of internal ROM external bus mode

```

; 4.1 Controller Series, Device

SERIES MB96340

#set

DEVICE MB96348R

; 4.14 Boot Vector

BOOT VECTOR BOOT VECTOR TABLE

#if BOOT_VECTOR == BOOT_VECTOR_TABLE

.SECTION

RESVECT, CONST, LOCATE=H'FFFFDC

.DATA.E _start

.SECTION BOOT_SELECT, CONST, LOCATE=H'DF0030

.DATA.L OxFFFFFFF

#endif

; 6.1 Import external symbols

.IMPORT _main

; user code entrance

.EXPORT start

; 6.2 Program start (the boot vector should point here)

:-----

start:

```

The memory map of this operation mode is illustrated in the next page.

Figure 3-2 Memory map of internal RAM external bus mode

# 3.3 MB88121 CC operation mode

The mode pins MD[2:0] and MDE[2:0] select between different bus types. The multiplexed mode is fixed encoded.

| MD2 | MD1 | MD0 | Mode           | MDE2 | MDE1 | MDE0 | Mode exter      | nsion         |   |   |   |                 |

|-----|-----|-----|----------------|------|------|------|-----------------|---------------|---|---|---|-----------------|

|     |     | 0   |                | 0    | 0    | 0    | Multiplexed bus | FR460         |   |   |   |                 |

| 1   | 0   |     | 16bit parallel | 0    | 0    | 1    |                 | 16FX          |   |   |   |                 |

|     |     |     |                |      |      |      |                 | communication | 1 | 0 | 0 | Non-multiplexed |

|     |     |     |                | 1    | 1    | 0    | bus             | FR360         |   |   |   |                 |

Table 3-3 Mode selection input of the communication controller

#### 3.4 Configuration of the external bus interface

MB96340 has 6 chip select areas. The configuration registers are listed in the table.

| Address  | +0                                          | +1                                                    |  |  |  |  |  |  |

|----------|---------------------------------------------|-------------------------------------------------------|--|--|--|--|--|--|

|          | External bus area [5:0]                     | configuration register                                |  |  |  |  |  |  |

| 0x0006E0 | EACL0                                       | EACH0                                                 |  |  |  |  |  |  |

| 0x0006E2 | EACL1                                       | EACH1                                                 |  |  |  |  |  |  |

| 0x0006E4 | EACL2                                       | EACH2                                                 |  |  |  |  |  |  |

| 0x0006E6 | EACL3                                       | EACH3                                                 |  |  |  |  |  |  |

| 0x0006E8 | EACL4                                       | EACH4                                                 |  |  |  |  |  |  |

| 0x0006EA | EACL5                                       | EACH5                                                 |  |  |  |  |  |  |

|          | External bus area [5                        | :2] select register                                   |  |  |  |  |  |  |

| 0x0006EC | EAS2                                        | EAS3                                                  |  |  |  |  |  |  |

| 0x0006EE | EAS4                                        | EAS5                                                  |  |  |  |  |  |  |

| 0x0006F0 | EBM<br>(external bus mode register)         | EBCF<br>(external bus clock and function<br>register) |  |  |  |  |  |  |

|          | External bus address o                      | utput enable register                                 |  |  |  |  |  |  |

| 0x0006F2 | EBAE0                                       | EBAE1                                                 |  |  |  |  |  |  |

| 0x0006F4 | EBAE2                                       | EBCS<br>(external bus control signal<br>register)     |  |  |  |  |  |  |

|          | Gray Settings used for MB88121 connectivity |                                                       |  |  |  |  |  |  |

Table 3-4 External bus interface registers

The MB88121 CC requires a minimum address range of 2K (0 - 0x7FF).

That means that CS0 cannot be used due to insufficient address range. In this example CS2 is used.

# 3.4.1 External Bus Mode register (EBM)

Register EBM defines the bus mode of the external bus interface. Bit function is listed below.

| Bit | Name |   | Function                                                                         |

|-----|------|---|----------------------------------------------------------------------------------|

| 7   | NMS  | 0 | Multiplexed bus mode for all external areas (parameter ADDRESSMODE in start.asm) |

|     |      | 1 | Non-multiplexed bus mode for all external areas                                  |

| 6   | ERE  | 0 | Internal ROM mode (parameter BUSMODE in start.asm)                               |

|     |      | 1 | External ROM mode                                                                |

| 5   | EAE5 | 0 | External area 5 is disabled (parameter CHIP_SELECT5 in start.asm)                |

|     |      | 1 | External area 5 is enabled                                                       |

| 4   | EAE4 | 0 | External area 4 is disabled (parameter CHIP_SELECT4 in start.asm)                |

|     |      | 1 | External area 4 is enabled                                                       |

| 3   | EAE3 | 0 | External area 3 is disabled (parameter CHIP_SELECT3 in start.asm)                |

|     |      | 1 | External area 3 is enabled                                                       |

| _   |      | 0 | External area 2 is disabled                                                      |

| 2   | EAE2 | 1 | External area 2 is enabled (parameter CHIP_SELECT2 in start.asm)                 |

| 1   | EAE1 | 0 | External area 1 is disabled (parameter CHIP_SELECT1 in start.asm)                |

|     |      | 1 | External area 1 is enabled                                                       |

| 0   | EAE0 | 0 | External area 0 is disabled (parameter CHIP_SELECTO in start.asm)                |

|     |      | 1 | External area 0 is enabled                                                       |

|     |      |   | Gray Settings used for MB88121 connectivity                                      |

Table 3-5 Register EBM

#### 3.4.2 External Bus Clock and Function register

Register EBCF controls the external bus clock, the external READY and HOLD function. Bit function is listed below.

| Bit  | Name     |   | Function                                                                                                                                            |

|------|----------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 15   | 15 HDE   |   | HOLD function disabled (parameter HOLD_REQ in start.asm)                                                                                            |

|      |          | 1 | HOLD function enabled                                                                                                                               |

|      |          | 0 | READY function disabled                                                                                                                             |

| 14   | RYE      | 1 | READY function enabled (parameter EXT_READY in start.asm)                                                                                           |

|      | 2        | 0 | External bus clock output disabled                                                                                                                  |

| 13   | CKE      | 1 | External bus clock output enabled (parameter EXT_CLOCK_ENABLE in start.asm)                                                                         |

|      | 12 CKI   |   | External bus clock is not inverted the inactive level of ECLK is '0' and the rising edge is the active edge                                         |

| 12   |          |   | External bus clock is inverted the inactive level of ECLK is '1' and the falling edge is the active edge  (parameter EXT_CLOCK_INVERT in start.asm) |

| 11   | CSM      | 0 | External bus clock is always output (parameter EXT_CLOCK_SUSPEND in start.asm)                                                                      |

|      |          | 1 | External bus clock is only output during transfer                                                                                                   |

| 10:8 | DIV[2:0] |   | External bus clock (ECLK) divider (parameter EXT_CLOCK_DIVISION in start.asm)                                                                       |

|      |          |   | Gray Settings used for MB88121 connectivity                                                                                                         |

Table 3-6 Register EBCF

| DIV2 | DIV1                                        | DIV0 | External bus clock (ECLK) divider setting |  |  |  |  |  |

|------|---------------------------------------------|------|-------------------------------------------|--|--|--|--|--|

| 0    | 0                                           | 0    | CLKB (CPU clock)                          |  |  |  |  |  |

| 0    | 0                                           | 1    | CLKB/2                                    |  |  |  |  |  |

| 0    | 1                                           | 0    | CLKB/4                                    |  |  |  |  |  |

| 0    | 1                                           | 1    | CLKB/8                                    |  |  |  |  |  |

| 1    | 0                                           | 0    | CLKB/16                                   |  |  |  |  |  |

| 1    | 0                                           | 1    | CLKB/32                                   |  |  |  |  |  |

| 1    | 1                                           | 0    | CLKB/64                                   |  |  |  |  |  |

| 1    | 1                                           | 1    | CLKB/128                                  |  |  |  |  |  |

|      | Gray Settings used for MB88121 connectivity |      |                                           |  |  |  |  |  |

Table 3-7 Bit DIV[2:0] of register EBCF

#### Note:

- 1. All operations of the external bus are based on ECLK even if the output of this clock is disabled.

- 2. CSM=0, ECLK is always output, also in HOLD state.

The 16FX MCU offers two methods to extend the read/write access to an external device: the auto wait function (bits EACL\_R[2:0]) and the READY function through RDY pin (bit EBCF\_RYE). They enable the access to low-speed memory and peripheral circuits.

The auto wait function can insert 1 to 32 wait cycles to extend the data cycle. By READY function the data cycle is extended as long as pin RDY =0.

#### 3.4.3 External Bus Address output Enable registers (EBAE[2:0])

Registers EBAE[2:0] control the output function of each address line.

0: disable the address line

1: enable the address line

| Address  | Bit7                                        | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | Corresponding parameter in file start.asm |  |

|----------|---------------------------------------------|------|------|------|------|------|------|------|-------------------------------------------|--|

| 0x0006F2 | A7                                          | A6   | A5   | A4   | A3   | A2   | A1   | A0   | ADDR PINS 7 0                             |  |

| (EBAE0)  | 1                                           | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 11001(_1110/_0                            |  |

| 0x0006F3 | A15                                         | A14  | A13  | A12  | A11  | A10  | A9   | A8   | ADDR PINS 15 8                            |  |

| (EBAE1)  | 1                                           | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 11551(_11115_15_6                         |  |

| 0x0006F4 | A23                                         | A22  | A21  | A20  | A19  | A18  | A17  | A16  | ADDR PINS 23 16                           |  |

| (EBAE2)  | 0                                           | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 11221(_11110_20_10                        |  |

|          | Gray Settings used for MB88121 connectivity |      |      |      |      |      |      |      |                                           |  |

Table 3-8 Register EBAE[2:0]

In the multiplexed bus mode register EBAE0 and EBAE1 control the address output of the pins AD15—AD00.

As the 16-bit multiplexed mode is used AD00 .. AD15 needs to be enabled.

# 3.4.4 External Bus Control Signal register (EBCS)

Register EBCS enables/disables the control signals of the external bus.

| Bit | Name  |   | Function                                                            | Corresponding parameter in file start.asm |  |  |

|-----|-------|---|---------------------------------------------------------------------|-------------------------------------------|--|--|

| 15  | 1     |   | ١                                                                   | \                                         |  |  |

| 14  | ASL   | 0 | Address strobe is low active ( $\overline{AS}$ function)            | ADDRESS STROBE LVL                        |  |  |

|     | 7.02  | 1 | Address strobe is high active (ALE function)                        |                                           |  |  |

| 13  | ASE   | 0 | Address strobe output (ALE/ $\overline{AS}$ ) disabled              | ADDRESS STROBE                            |  |  |

|     | 7.02  | 1 | Address strobe output (ALE/ $\overline{AS}$ ) enabled               |                                           |  |  |

| 12  | RDE   | 0 | Read strobe output ( $\overline{RD}$ ) disabled                     | READ STROBE                               |  |  |

|     | .2    |   | Read strobe output ( $\overline{RD}$ ) enabled                      | _                                         |  |  |

| 11  | WRHE  | 0 | Write strobe output ( $\overline{WRH}$ ) disabled                   | HIGH WRITE STROBE                         |  |  |

|     |       |   | Write strobe output ( $\overline{WRH}$ ) enabled                    |                                           |  |  |

| 10  | WRLE  | 0 | Write strobe output ( $\overline{WRL}$ / $\overline{WR}$ ) disabled | LOW WRITE STROBE                          |  |  |

|     | ***** | 1 | Write strobe output ( $\overline{WRL}$ / $\overline{WR}$ ) enabled  |                                           |  |  |

| 9   | UBE   | 0 | Byte select output ( $\overline{\textit{UB}}$ ) disabled            | HIGH BYTE SIGNAL                          |  |  |

|     | o obl |   | Byte select output ( $\overline{U\!B}$ ) enabled                    |                                           |  |  |

| 8   | LBE   |   | Byte select output ( $\overline{LB}$ ) disabled                     | LOW BYTE SIGNAL                           |  |  |

|     |       | 1 | Byte select output ( $\overline{LB}$ ) enabled                      |                                           |  |  |

|     | •     | ı | Gray Settings used for MB88121 connectivity                         | 1                                         |  |  |

Table 3-9 Register EBCS

#### 3.4.5 External Area Configuration registers (EACH/EACL[5:0])

Function of register EACH and EACL is listed below. In this application note external area 2 is used. The corresponding parameter is CS2\_CONFIG.

| Register EACH2 |                |                    |                                                               |  |  |  |  |  |

|----------------|----------------|--------------------|---------------------------------------------------------------|--|--|--|--|--|

| Bit            | Name           |                    | Function                                                      |  |  |  |  |  |

| 15:14          | 1              |                    | \                                                             |  |  |  |  |  |

| 13             | ATL            | 0                  | Code and data read possible                                   |  |  |  |  |  |

|                | AIL.           | 1                  | Only data read possible                                       |  |  |  |  |  |

| 12             | CSL            | 0                  | Chip select signal is low active ( $\overline{\mathit{CS}}$ ) |  |  |  |  |  |

|                |                | 1                  | Chip select signal is high active (CS)                        |  |  |  |  |  |

| 11             | CSE            | 0                  | Chip select output disabled                                   |  |  |  |  |  |

| ''             | COL            | 1                  | Chip select output enabled                                    |  |  |  |  |  |

| 10:8           | EASZ[2:0]      | External area size |                                                               |  |  |  |  |  |

|                | Register EACL2 |                    |                                                               |  |  |  |  |  |

| 7              | BW             | 0                  | 16bit data bus width                                          |  |  |  |  |  |

| '              |                | 1                  | 8bit data bus width                                           |  |  |  |  |  |

| 6              | ES             | 0                  | Little-endian                                                 |  |  |  |  |  |

|                | LO             | 1                  | Big-endian                                                    |  |  |  |  |  |

| 5              | WSF            | 0                  | $\overline{WRL}$ write strobe is activated                    |  |  |  |  |  |

|                | ****           | 1                  | $\overline{WR}$ write strobe is activated                     |  |  |  |  |  |

| 4              | STS            | 0                  | Strobe timing scheme 0 is selected                            |  |  |  |  |  |

| _              | 010            | 1                  | Strobe timing scheme 1 is selected                            |  |  |  |  |  |

| 3              | ACE            | 0                  | Address cycle is not extended                                 |  |  |  |  |  |

|                |                |                    | Address cycle is extended by one ECLK cycle                   |  |  |  |  |  |

| 2:0            | R[2:0]         |                    | Automatic wait cycles                                         |  |  |  |  |  |

| _              | _              | Gray Se            | ttings used for MB88121 connectivity                          |  |  |  |  |  |

Table 3-10 Register EACH/EACL

#### Note:

- 1. Bit ACE decides the length of the address cycle in multiplexed bus mode

- 2. Bit STS selects the timing of the signal ALE,  $\overline{WR}$  and  $\overline{RD}$  (for details please see the hardware manual of MB96300 series)

| EASZ2 | EASZ1 | EASZ0 | Area size | Valid bit of register EAS |

|-------|-------|-------|-----------|---------------------------|

| 0     | 0     | 0     | 64KB      | EAS_A[7:0]                |

| 0     | 0     | 1     | 128KB     | EAS_A[7:1]                |

| 0     | 1     | 0     | 256KB     | EAS_A[7:2]                |

| 0     | 1     | 1     | 512KB     | EAS_A[7:3]                |

| 1     | 0     | 0     | 1MB       | EAS_A[7:4]                |

| 1     | 0     | 1     | 2MB       | EAS_A[7:5]                |

| 1     | 1     | 0     | 4MB       | EAS_A[7:6]                |

| 1     | 1     | 1     | 8MB       | EAS_A[7]                  |

Table 3-11 EASZ[2:0] of register EACH

| R2 | R1 | R0 | Automatic wait cycles |

|----|----|----|-----------------------|

| 0  | 0  | 0  | No wait cycle         |

| 0  | 0  | 1  | 1 cycle               |

| 0  | 1  | 0  | 2 cycle               |

| 0  | 1  | 1  | 3 cycle               |

| 1  | 0  | 0  | 4 cycle               |

| 1  | 0  | 1  | 8 cycle               |

| 1  | 1  | 0  | 16 cycle              |

| 1  | 1  | 1  | 32 cycle              |

Table 3-12 R[2:0] of register EACL

#### 3.4.6 Registers EAS[5:2]

MB96340 series support 6 external bus areas. Among them area 0 and area 1 have fixed address range.

| External area | Address range          |

|---------------|------------------------|

| CS0           | 0x0000F0—0x0000FF      |

| CS1           | 0x000C00—(RAM_start-1) |

Table 3-13 address range of area 0 and area 1

| Device                 | RAM size | RAM_start |

|------------------------|----------|-----------|

| MB96344                | 6KB      | 0x006A40  |

| MB96(F)346, MB96(F)347 | 16KB     | 0x004240  |

| MB96F348               | 24KB     | 0x002240  |

Table 3-14 RAM start address of different devices

The address range of area 2 to area 5 is programmable through register EAS[5:2] and register EACH[5:2].

| External area | Available address area | Corresponding register |

|---------------|------------------------|------------------------|

| CS2           |                        | EAS2, EACH2_EASZ       |

| CS3           | 0x100000—0xFFFFF       | EAS3, EACH3_EASZ       |

| CS4           | SX100000 OXITITI       | EAS4, EACH4_EASZ       |

| CS5           |                        | EAS5, EACH5_EASZ       |

Table 3-15 Configuration registers for area range

Register EAS defines the upper 8-bit address (start bank) of the external bus area. Together with bits EASZ[2:0] of register EACH the address range of each external bus area can be specified.

The configurations in file start.asm are listed below. Area 2 is modified for MB88121B. Area 3/4/5 are not used.

| EAS register                    | EACH register                            | Area range                  |  |  |

|---------------------------------|------------------------------------------|-----------------------------|--|--|

| EAS2=0x10 (parameter CS2_START) | EACH2_EASZ[2:0]=0 (parameter CS2_CONFIG) | 0x100000—0x10FFFF<br>(64KB) |  |  |

| EAS3=0x40 (parameter CS3_START) | EACH3_EASZ[2:0]=6 (parameter CS3_CONFIG) | 0x400000—0x7FFFFF<br>(4MB)  |  |  |

| EAS4=0x80 (parameter CS4_START) | EACH4_EASZ[2:0]=6 (parameter CS4_CONFIG) | 0x800000—0xBFFFFF<br>(4MB)  |  |  |

| EAS5=0xC0 (parameter CS5_START) | EACH5_EASZ[2:0]=6 (parameter CS5_CONFIG) | 0xC00000—0xFFFFFF<br>(4MB)  |  |  |

Table 3-16 Configurations of area range in file start.asm

#### 3.4.7 Settings in file start.asm

FUJITSU Microelectronics Europe GmbH offers Software examples for MB96340 series, including a template project. The start.asm file is used to initialise the MCU. All settings are done via defines, according to the selected defines a code content is generetade during compilation.

Following find the required bus interface settings for start.asm file using MB96340 and Mb88121 series.

```

; 4.8 Clock Selection

:-----

CRYSTAL

#set

FREQ 4MHZ

#set

CPU_48MHZ_CLKP2_16MHZ

0x08

CLOCK SPEED CPU_48MHZ_CLKP2_16MHZ

#set

; 4.10 External Bus Interface

:-----

#set

BUSMODE INTROM EXTBUS ; bus mode

ADDRESSMODE MULTIPLEXED ; address-mode

#set

#set CHIP_SELECT2 ON ; enable chip select area

HOLD REQ

OFF ; HOLD function

#set

#set EXT_READY ON ; Ready function

EXT CLOCK ENABLE ON ; external bus clock output

#set

EXT CLOCK INVERT ON ; clock inversion

#set

EXT CLOCK SUSPEND OFF ;

#set

#set

ADDR PINS 23 16 B'00000000 ; select used address lines

#set

ADDR PINS 15 8 B'11111111

; A10..A0

#set

ADDR PINS 7 0 B'11111111 ;

#set

LOW_BYTE_SIGNAL OFF ;

#set

#set

HIGH BYTE SIGNAL

OFF ;

LOW WRITE STROBE ON ; write strobe signal WRLX/WRX

#set

HIGH WRITE STROBE OFF ;

#set

READ STROBE ON ; read strobe signal RDX

#set

ADDRESS_STROBE ON ; address strobe signal ALE/ASX

#set

ADDRESS STROBE LVL OFF ; address strobe active low

#set

CS2 CONFIG B'0000100000111010 ; Chip Select Area 2 configuration

#set

CS2_START 0x10 ; start bank of chip select area2

#set

```

```

; 6.6 Set external bus configuration

:-----

EBCF, #((HOLD_REQ << 7) | (EXT_READY << 6) | (EXT_CLOCK_ENABLE << 5) |

(EXT CLOCK INVERT << 4) | (EXT CLOCK SUSPEND << 3) | EXT CLOCK DIVISION)

MOV EBAEO, #ADDR PINS 7 0

MOV EBAE1, #ADDR PINS 15 8

MOV EBAE2, #ADDR PINS 23 16

MOV EBCS, #((ADDRESS STROBE LVL << 6) | (ADDRESS STROBE << 5) | (READ STROBE <<

4) | (HIGH WRITE STROBE << 3) | (LOW WRITE STROBE << 2) | (HIGH BYTE SIGNAL <<

1) | LOW BYTE SIGNAL)

MOVW EACL2, #CS2 CONFIG

MOV EAS2, #CS2 START

#((ADDRESSMODE << 7) | ((BUSMODE-1) << 6) | (CHIP SELECT5 << 5) |

(CHIP SELECT4 << 4) | (CHIP SELECT3 << 3) | (CHIP SELECT2 << 2) | (CHIP SELECT1

<< 1) | CHIP SELECTO)

MOV PIER00, #0xFF; MCU port 0

MOV PIER01, #0xFF; MCU port 1

SETB PIER03:6

; READY function

ROMM CONFIG .EQU ((MIRROR_BANK << 4) | (MIRROR_SIZE << 1) | (ROMMIRROR))

MOV ROMM, #ROMM CONFIG

```

#### 3.4.8 Used bus interface functions at pins on MB96F348RS

All the used pins of the external bus interface are listed below. Data output function of pins AD[15:00] is automatically enabled. Pin ALE is used to distinguish value on the address/data lines. Pin RDY is used by slow external devices to insert wait cycles. The initial value of register DDR (data direction register) and PIER (port input enable register) is 0.

| MCU pin  | Description                 | Register PIER              | Register DDR       | Other registers |

|----------|-----------------------------|----------------------------|--------------------|-----------------|

| RDY      | ready signal                | PIER03_IE6=1               | DDR03_D6=0         | EBCF_RYE        |

|          | address output              | \                          | \                  | EBAE[2:0]       |

| AD[15:0] | data output                 | \                          | \                  | 1               |

|          | data input                  | PIER00=0xFF<br>PIER01=0xFF | DDR00=0<br>DDR01=0 | \               |

| ALE      | address latch enable signal | \                          | 1                  | EBCS_ASE        |

| CS2      | chip select signal          | 1                          | \                  | EACH_CSE        |

| RDX      | read signal                 | 1                          | \                  | EBCS_RDE        |

| WRX      | Write signal                | 1                          | 1                  | EBCS_WRLE       |

#### Interfacing MB96340 TO MB88121 Chapter 3 Configuration

| MCU pir | Description        | Register PIER | Register DDR | Other registers |

|---------|--------------------|---------------|--------------|-----------------|

| ECLK    | external bus clock | \             | /            | EBCF_CKE        |

Table 3-17 Configuration registers of I/O port function

MB96348RS provides maximal 24bit address-line and 16bit data-line for the external bus interface. Since the communication controller MB88121B has 11bit address-line and 16bit data-line, the bus width is fixed.

- 16bit data bus: MCU pins AD[15:00].

- E-Ray registers are 16bit addressed from 0x0000 to 0x07FC. Each register is 32bit long and begins at even address. Since the data bus is restricted to 16bit, the high order 16bit data and low order 16bit data are distinguished by address bit A[1]. The first five bits and the last bit of a 16bit address are always zero. The 11bit address bus (MCU pins AD[10:00]) is shown below. Address A[23:16] are not used.

MCU port 0 and port 1 are reused for data and address bus.

| 0 | 0   | 0     | 0   | 0 | Χ | Χ | Χ | Χ    | Χ      | Χ     | Χ | Х | Χ | Χ    | 0    |

|---|-----|-------|-----|---|---|---|---|------|--------|-------|---|---|---|------|------|

|   | Alv | ays z | ero |   |   |   |   | Addr | ess A[ | 10:2] |   |   |   | A[1] | A[0] |

Table 3-18 11bit address line

#### 3.5 Simplified timing diagram of MB88121B

The below shown timing diagram is required to achieve a correct access to MB88121. The settings discussed for the bus interface register will generate this timing. Depending on PCB layout the number of wait states may differ. This needs to be rechecked and optimised case by case.

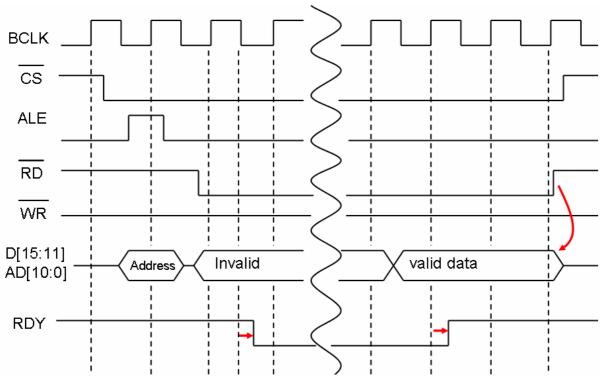

#### 3.5.1 MB88121 read timing

Figure 3-3 Read operation

#### Operation sequence:

- 1. The address is latched by the falling edge of ALE pin.

- 2. The RD pin (signal RD) becomes low level, the output data on pins D[15:11] and AD[10:0] is invalid.

- 3. After that the RDY pin becomes low level at the next falling edge of the clock signal BCLK (pin BCLK), which causes the MCU to wait.

- 4. After several wait cycles the RDY pin becomes high level at the rising edge of the BCLK pin and the valid data is output from the pins D[15:11] and AD[10:0].

- 5. When the RD pin becomes high level again, the read access is finished. Pins D[15:11] and AD[10:0] become Hi-Z.

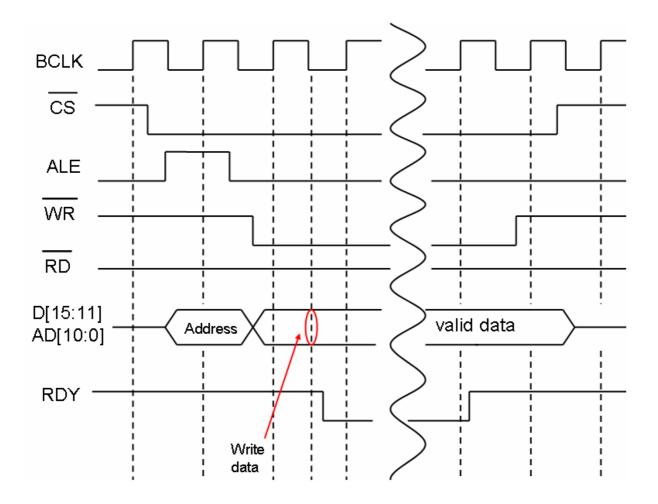

#### 3.5.2 MB88121 write timing

Figure 3-4 Write operation

#### Operation sequence:

- 1. The address is latched by the falling edge of ALE pin.

- 2. The WR pin (signal  $\overline{WR}$ ) becomes low level. At the next falling edge of the BCLK signal the data on pins D[15:11] and AD[10:0] is written to a temporary register and the RDY pin becomes low level, which causes the MCU to wait.

- 3. The data in the temporary register is written to the addressed register. The RDY pin becomes high level again.

#### Note:

Details about RDY wait cycle and byte ordering are located in the MB88121 data sheet.

#### 3.6 Initialisation sequence of MB88121

After the proper setup of the bus interface MB88121 is visual in the MCU address range starting at 0x10.0000.

The MB88121 requires internal operation frequency of 80 MHz. This frequency is generated via the internal PLL of the MB88121.

First access to MB88121 should setup the PLL. The PLL is set in the CLOCK CONTROL REGISTER (CCNT) (Address 0x04 => 0x10.0004).

The example is using a 10 MHz crystal. The PLL must be setup to multiplication ratio x8 (PMUL[1:0]) to achieve the 80 MHz. The PLL must be enabled via PON bit. To supply the FlexRay CC with clock the STOP bit needs to be set to '0'.

Other bits shall be set to '0'.

The stabilisation time of the PLL is 600us. After this time the MB88121 The PLL clock usage can be selected via the CCNT.SEEL bit ( set to '1').

The wait time can be assured using a reload timer of the MCU.

The MB88121 is operating with 80 MHz. It is now possible to initialise the MB88121 with the FlexRay bus parameter settings.

```

/* THIS SAMPLE CODE IS PROVIDED AS IS AND IS SUBJECT TO ALTERATIONS. */

/* FUJITSU MICROELECTRONICS ACCEPTS NO RESPONSIBILITY OR LIABILITY FOR */

/* ANY ERRORS OR ELIGIBILITY FOR ANY PURPOSES.

(C) Fujitsu Microelectronics Europe GmbH

#define CCNT ((uint32 t *)0x100004) /* address of CCNT ERAY Register */

void start rldtmr 3 (void) {

/* start count operation */

TMCSR3 TRG = 1;

}

/* setup of reload timer 3 */

TMRLR3 = 600;

/* set reload value */

TMCSR3 = 0x0802;

/* set MB88121 Clock */

*CCNT = 0x0000000D; /* enable PLL, PLLx8 */

/* start wait time */

start rldtmr 3();

/* PLL stabilization wait time */

while (!TMCSR3 UF);

*CCNT = 0x0000000F;

/* switch to PLL clock */

```

#### 3.7 Interrupts

The MB88121 FlexRay CC is supporting also interrupt events. These events are available at pins and can be connected to MCU external interrupt pins.

#### 3.7.1 CC interrupt

CC interrupt pins signal different interrupt request. For details please refer to the document "MB88121B preliminary data sheet" and "E-Ray user manual".

| CC pin | Interrupt type                    |

|--------|-----------------------------------|

| INT0   | E-Ray interrupt line0 (eray_int0) |

| INT1   | E-Ray interrupt line1 (eray_int1) |

| INT2   | E-Ray timer0 interrupt            |

| INT3   | E-Ray timer1 interrupt            |

| INT4   | Low voltage detection interrupt   |

Table 3-19 CC interrupt output by 16bit multiplexed mode

After power-on / Reset these pins are set to output driving Low level. Interrupt requests are indicated by High Level output at the pins.

To enable the output of the signals INT2 to INT 4 the INT (Interrupt register) at offset address 0x0C (Address 0x10.000C in our example configuration) must be used. The dedicated E-Ray timer interrupts are indication a request just a few Macroticks, It is recommended to use rising edge detection for the external interrupts.

The INTO and INT1 pins are connected to the Eray\_intO and Eray\_int1 interrupts. The functions are configured with the E-Ray interrupt registers. In case of an interrupt request the pins output High-level and remaining the level until the Interrupt Flag is clear in the corresponding register.

Following interrupt registers are available:

- Error Interrupt Register (EIR): indicates an error interrupt request

- Status Interrupt Register (SIR): indicates a status interrupt request

- Error Interrupt Line Select (EILS): Selects which error interrupt is output at which eray\_int (0 or 1) line.

- Status Interrupt Line Select (SILS): Selects which status interrupt is output at which eray int (0 or 1) line.

- Error Interrupt Enable Set / Reset (EIES, EIER): Enable / disable error interrupts

- Status Interrupt Enable Set / Reset (SIES, SIER): Enable / disable status interrupts