# **FireBird**

# **Hardware Manual**

v1.2

# Disclaimer

While every precaution has been taken in the preparation of this manual, Active Silicon assumes no responsibility for errors or omissions. Active Silicon reserves the right to change the specification of the product described within this manual and the manual itself at any time without notice and without obligation of Active Silicon to notify any person of such revisions or changes.

# **Copyright Notice**

Copyright © 2011-2014 Active Silicon. All rights reserved. This document may not in whole or in part, be reproduced, transmitted, transcribed, stored in any electronic medium or machine readable form, or translated into any language or computer language without the prior written consent of Active Silicon.

# Trademarks

All trademarks and registered trademarks are the property of their respective owners.

# **Part Information**

Part Number: FBD-MAN-HW

# **Contact Details**

| Web:<br>Sales:<br>Support: | <u>www.activesilicon.com</u><br><u>sales@activesilicon.com</u><br><u>techsupport@activesilicon.com</u>                               |  |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|

| Europe:                    | Active Silicon Ltd.<br>Pinewood Mews, Bond Close, Iver,<br>Bucks, SL0 0NA, UK.<br>Tel: +44 (0)1753 650600<br>Fax: +44 (0)1753 651661 |  |

| North<br>America:          | Active Silicon, Inc.<br>479 Jumpers Hole Road, Suite 301,<br>Severna Park, MD 21146, USA.<br>Tel: +1 410-696-7642                    |  |

Fax: +1 410-696-7643

# **Revision History**

| Version          | Comments                                                                                                                                      |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| v1.0 14-Sep-2011 | First release.                                                                                                                                |

| v1.1 24-Jun-2014 | CoaXPress LEDs updated to reflect the v1.1 CoaXPress standard. Additional guidance information added to the I/O section.                      |

| v1.2 16-Dec-2014 | Additional information on the mating connector for the 50 way I/O header.<br>Added information about the bus hold function of the TTL inputs. |

# **Table of Contents**

| Disc  | laime        | er                                         | 3  |

|-------|--------------|--------------------------------------------|----|

| Сору  | yrigh        | t Notice                                   | 3  |

| Trad  | emar         | rks                                        | 3  |

| Part  | Infor        | mation                                     | 3  |

|       |              |                                            |    |

| Cont  | act L        | Details                                    | 3  |

| Revi  | sion         | History                                    | 4  |

| Table | e of (       | Contents                                   | 5  |

| 1.    | Intro        | oduction                                   | 7  |

|       | 1.1.         | Scope                                      | 7  |

|       | 1.2.         | Document Structure                         | 7  |

|       | 1.3.         | Conventions                                | 7  |

|       | 1.4.         | Related Documentation                      | 7  |

| 2.    | Boai         | rds                                        | 8  |

|       | 2.1.         | FireBird CoaXPress PCI Express x8 Boards   | 8  |

|       |              | 2.1.1. Connectors                          | 8  |

|       |              | 2.1.2. LEDs                                | 10 |

|       |              | 2.1.3. Jumpers                             | 12 |

|       | 2.2.         | FireBird Camera Link PCI Express x8 Boards |    |

|       |              | 2.2.1. Connectors                          |    |

|       |              | 2.2.2. LEDs                                |    |

|       |              | 2.2.3. Jumpers                             | 16 |

| 3.    | Fire         | Bird I/O Connector                         | 18 |

|       | 3.1.         | Pinout                                     | 18 |

|       | 3.2.         | Signal Functions                           | 19 |

|       |              | 3.2.1. Opto-Isolated Signals               | 19 |

|       |              | 3.2.2. RS-422 Signals                      |    |

|       |              | 3.2.3. TTL Signals                         |    |

|       |              | 3.2.4. +12V                                | 22 |

|       |              | 3.2.5. GND                                 | 22 |

| 4.    | Coa          | XPress Connector                           | 23 |

|       | 4.1.         | Cables                                     | 23 |

|       | 4.2.         | Power over CoaXPress (PoCXP)               | 23 |

|       | 4.3. General |                                            |    |

| 5. | Camera Link Connector |                               | 24 |

|----|-----------------------|-------------------------------|----|

|    | 5.1.                  | Cables                        | 24 |

|    | 5.2.                  | Power over Camera Link (PoCL) | 24 |

|    | 5.3.                  | Pinout                        | 24 |

|    | 5.4.                  | General                       | 24 |

| 6. | PCI                   | Express Graphics Connector    | 25 |

|    | 6.1.                  | Cable Identification          | 25 |

|    | 6.2.                  | Pinout                        | 26 |

| 7. | Not                   | es on PCI Express Slots       | 27 |

# 1. Introduction

### 1.1. Scope

This document describes the hardware features of FireBird boards, including connectors and jumper settings.

### 1.2. Document Structure

The document is broken down into the following major sections:

#### **Product-Specific Information.**

Each FireBird product has a section giving a layout drawing and description of each user connector, jumper and LED.

#### FireBird I/O (Input/Output) Connector.

This connector is common across the range, and the pinout, characteristics and example circuits are given.

#### **CoaXPress Connector Information.**

Information on the industry standard CoaXPress connector is given.

#### Camera Link Connector Information.

Information on the industry standard Camera Link connector is given.

#### PCI Express Graphics Connector Information.

This connector is used on all FireBird CoaXPress boards, and is described in detail in this section.

#### **PCI Express Information.**

Some general information on PCI Express slots is given.

#### 1.3. Conventions

The following conventions are used in this document:

Blue italic: A hyperlink to the relevant section of the document.

#### 1.4. Related Documentation

FireBird User Manual:

FBD-MAN-USER.

# 2. Boards

# 2.1. FireBird CoaXPress PCI Express x8 Boards

This includes the boards with the following part numbers, which only differ in the number of CoaXPress BNC connectors fitted:

AS-FBD-1xCXP6-2PE8, AS-FBD-2xCXP6-2PE8, AS-FBD-4xCXP6-2PE8.

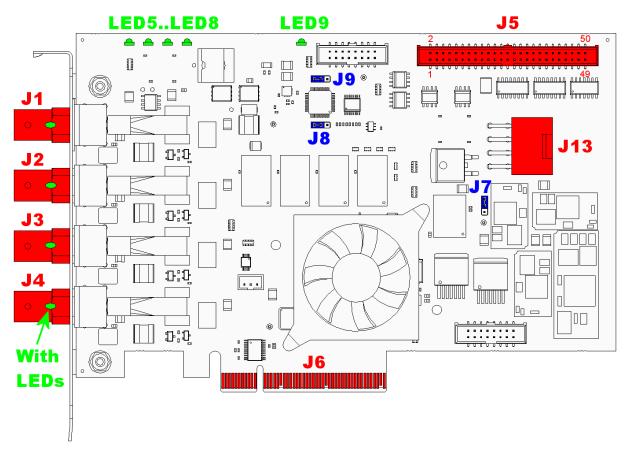

#### Figure 1: FireBird CoaXPress PCI Express x8 Board Layout

The following sections describe the features shown in color.

#### 2.1.1. Connectors

These are shown in red in Figure 1. Note that connectors not listed are for factory use only.

#### J1 CoaXPress Input 1

This is the first CoaXPress input. See CoaXPress Connector (page 23) for more details.

#### J2 CoaXPress Input 2

This is the second CoaXPress input on four input boards. See *CoaXPress Connector* (page 23) for more details.

#### J3 CoaXPress Input 3

This is the third CoaXPress input on four input boards, or the second on two input boards. See *CoaXPress Connector* (page 23) for more details.

Boards

This is the fourth CoaXPress input on four input boards. See *CoaXPress Connector* (page 23) for more details.

#### J5 FireBird I/O Connector

This is the standard 50 way FireBird I/O (input/output) connector. See *FireBird I/O Connector* (page 18) for more details.

#### J6 PCI Express Connector

This is a PCI Express x8 connector that supports the faster Gen 2 operational speed. Check the computer's documentation to identify a suitable slot. See *Notes on PCI Express Slots* (page 27) for additional information.

#### J13 Power Connector for PoCXP

This connector supplies 12V to the *Power over CoaXPress* (PoCXP) power supply on FireBird. It is only needed when cameras requiring PoCXP are used. See *PCI Express Graphics Connector* (page 25) for additional information, including **important** information on identifying the correct cables in a computer to connect to J13.

Boards

### 2.1.2. LEDs

These are shown in green in Figure 1.

# LEDs in BNC Connectors J1..J4

These show the CoaXPress status as defined in the CoaXPress specification v1.1:

| State                                                                     | Indication                                                                                                                  |

|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| No power                                                                  | Off                                                                                                                         |

| FireBird booting                                                          | Solid orange                                                                                                                |

| FireBird ready, but nothing connected                                     | Slow pulse red                                                                                                              |

| Link detection in progress, PoCXP active                                  | Fast flash alternate green / orange<br>Shown for a minimum of 1s even if<br>the link detection is faster                    |

| Link detection in progress, PoCXP not in use                              | Fast flash orange<br>Shown for a minimum of 1s even if<br>the link detection is faster                                      |

| Device / Host incompatible, PoCXP active                                  | Slow flash alternate red / green                                                                                            |

| Device / Host incompatible, PoCXP not in use                              | Slow flash alternate red / orange                                                                                           |

| PoCXP over-current                                                        | Solid red                                                                                                                   |

| Device / Host connected, but no data being transferred                    | Solid green                                                                                                                 |

| Device / Host connected, waiting for event (e.g. trigger, exposure pulse) | Slow pulse orange                                                                                                           |

| Device / Host connected, data being transferred                           | Fast flash green                                                                                                            |

| Error during data transfer<br>(e.g. CRC error, single bit error detected) | 500ms red pulse<br>In case of multiple errors, there are at<br>least two green pulses before the<br>next error is indicated |

| System error (e.g. internal error)                                        | Fast flash red                                                                                                              |

| Indication | Timing                     |

|------------|----------------------------|

| Fast flash | 12.5Hz (20ms on, 60ms off) |

| Slow flash | 0.5Hz (1s on, 1s off)      |

| Slow pulse | 1Hz (200ms on, 800ms off)  |

#### LED5

To be defined.

#### LED6

To be defined.

#### LED7

To be defined.

#### LED8

This is solid green, but blinks off for each PCIe access, both register read/write and DMA.

#### **LED9 FPGA Configuration Status**

This shows<sup>1</sup> the status of the main chip on the board, the FPGA:

| Indication                                  | Meaning                                                                                                                                                                                                                                    |

|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Off                                         | No power.                                                                                                                                                                                                                                  |

| Solid green, with single pulse off at 1.2Hz | Normal operation, with the FPGA configured from the User Design.                                                                                                                                                                           |

| Solid green, with double pulse off at 1.2Hz | This indicates that the FPGA has configured from the Factory Design. If<br>this occurs with J8 in its default position this indicates that the User<br>Design is corrupt and needs re-loading using the FireBird configuration<br>utility. |

| Flashing                                    | Indicates the FPGA is not configured. Should normally only occur in factory modes, so check the setting of jumper J9. If J9 is correct, contact FireBird support.                                                                          |

| Solid green                                 | Indicates the FPGA is configured in a special factory mode. Check the setting of jumper J9. If J9 is correct, contact FireBird support.                                                                                                    |

Note that these LED indications are not valid if jumpers J8 or J9 are moved after the FPGA has configured.

Boards

<sup>&</sup>lt;sup>1</sup> Note – Very early FireBird CoaXPress boards do not have this LED fitted.

### 2.1.3. Jumpers

These are shown in green in Figure 1, which also shows the default settings of the jumpers.

# J7 Write Protect (WP)

| Position        | Meaning                                                                                   |  |

|-----------------|-------------------------------------------------------------------------------------------|--|

| Upper (default) | The factory FPGA design can be updated by software.                                       |  |

| Lower           | <i>Write Protect</i> . This stops the factory FPGA design from being updated by software. |  |

#### J8 Factory / User Control (FF)

| Position       | Meaning                                                                                                                                                                                                                                                                           |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Left (default) | The FPGA will configure from the User Design. If this fails to load, the factory design will be loaded.                                                                                                                                                                           |

| Right          | <i>Force Factory</i> . The FPGA will configure from the Factory Design. This mode may be needed if the User Design is corrupt, and the extra time taken to try to load the User Design, and then to load the Factory Design, means that the computer does not recognize FireBird. |

### J9 For Factory Use Only

| Position       | Meaning                                             |  |

|----------------|-----------------------------------------------------|--|

| Left (default) | The FPGA will configure based on the setting of J8. |  |

| Right          | 1st. This mode is for factory use only.             |  |

Boards

# 2.2. FireBird Camera Link PCI Express x8 Boards

This includes the boards with the following part numbers, which only differ in the number of Camera Link connectors fitted:

AS-FBD-1xCLD-2PE8, AS-FBD-2xCLD-2PE8.

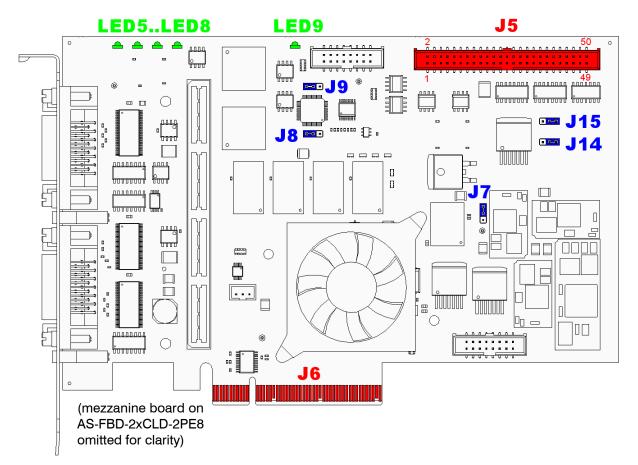

Figure 2: FireBird Camera Link Deca PCI Express x8 Board Layout

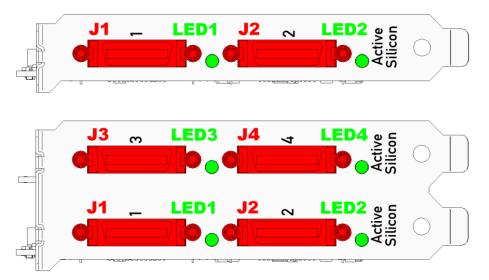

Figure 3: FireBird Camera Link Deca PCI Express x8 End Brackets

The following sections describe the features shown in color.

#### 2.2.1. Connectors

These are shown in red in Figure 2 and Figure 3. Note that connectors not listed are for factory use only.

#### J1 Camera Link Input 1

This is the first Camera Link input. It can be used for Base configuration, or for the primary connection in conjunction with J2 in Medium, Full and Deca (80 bit) configurations. See *Camera Link Connector* (page 24) for more details.

#### J2 Camera Link Input 2

This is the second Camera Link input. It can be used in conjunction with J1 for the secondary connection in Medium, Full and Deca (80 bit) configurations. See *Camera Link Connector* (page 24) for more details.

#### J3 Camera Link Input 3

This is the third Camera Link input, only available on boards with four Camera Link connectors. It can be used for Base configuration, or for the primary connection in conjunction with J4 in Medium, Full and Deca (80 bit) configurations. See *Camera Link Connector* (page 24) for more details.

#### J4 Camera Link Input 4

This is the fourth Camera Link input, only available on boards with four Camera Link connectors. It can be used in conjunction with J3 for the secondary connection in Medium, Full and Deca (80 bit) configurations. See *Camera Link Connector* (page 24) for more details.

#### J5 FireBird I/O Connector

This is the standard 50 way FireBird I/O (input/output) connector. See *FireBird I/O Connector* (page 18) for more details.

#### J6 PCI Express Connector

This is a PCI Express x8 connector that supports the faster Gen 2 operational speed. Check the computer's documentation to identify a suitable slot. See *Notes on PCI Express Slots* (page 27) for additional information.

### 2.2.2. LEDs

These are shown in green in Figure 2 and Figure 3.

#### LED1, LED2, LED, LED4

These show the Camera Link status. LED1 shows the status for J1, LED2 for J2, LED3 for J3, and LED4 for J4. LED3 and LED 4 are only present on boards with four Camera Link connectors.

| State                                                                     | Indication                                                                        |

|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| No power                                                                  | Off                                                                               |

| FireBird booting                                                          | Solid orange                                                                      |

| FireBird ready, but nothing connected                                     | Slow pulse red                                                                    |

| Link detection in completed, PoCL active                                  | Fast flash green<br>Shown for a minimum of 1s                                     |

| Link detection in completed, PoCL not in use                              | Fast flash orange<br>Shown for a minimum of 1s                                    |

| PoCL over-current                                                         | Solid red                                                                         |

| Device / Host connected, but no data being transferred                    | Slow pulse green                                                                  |

| Device / Host connected, waiting for event (e.g. trigger, exposure pulse) | Slow pulse orange                                                                 |

| Device / Host connected, data being transferred                           | Solid green whenever data<br>transferred (i.e. blinks<br>synchronously with data) |

| System error (e.g. internal error)                                        | Fast flash red                                                                    |

| Indication | Timing                     |

|------------|----------------------------|

| Fast flash | 12.5Hz (20ms on, 60ms off) |

| Slow flash | 0.5Hz (1s on, 1s off)      |

| Slow pulse | 1Hz (200ms on, 800ms off)  |

#### LED5

To be defined.

LED6

To be defined.

LED7 To be defined.

#### LED8

This is solid green, but blinks off for each PCIe access, both register read/write and DMA.

#### **LED9 FPGA Configuration Status**

This shows the status of the main chip on the board, the FPGA:

| Indication                                  | Meaning                                                                                                                                                                                                                                    |  |  |  |

|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Off                                         | No power.                                                                                                                                                                                                                                  |  |  |  |

| Solid green, with single pulse off at 1.2Hz | Normal operation, with the FPGA configured from the User Design.                                                                                                                                                                           |  |  |  |

| Solid green, with double pulse off at 1.2Hz | This indicates that the FPGA has configured from the Factory Design. If<br>this occurs with J8 in its default position this indicates that the User<br>Design is corrupt and needs re-loading using the FireBird configuration<br>utility. |  |  |  |

| Flashing                                    | Indicates the FPGA is not configured. Should normally only occur in factory modes, so check the setting of jumper J9. If J9 is correct, contact FireBird support.                                                                          |  |  |  |

| Solid green                                 | Indicates the FPGA is configured in a special factory mode. Check the setting of jumper J9. If J9 is correct, contact FireBird support.                                                                                                    |  |  |  |

Note that these LED indications are not valid if jumpers J8 or J9 are moved after the FPGA has configured.

### 2.2.3. Jumpers

These are shown in green in Figure 2, which also shows the default settings of the jumpers.

#### J7 Write Protect (WP)

| Position        | Meaning                                                                           |

|-----------------|-----------------------------------------------------------------------------------|

| Upper (default) | The factory FPGA design can be updated by software.                               |

| Lower           | Write Protect. This stops the factory FPGA design from being updated by software. |

#### J8 Factory / User Control (FF)

| Position       | Meaning                                                                                                                                                                                                                                                                           |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Left (default) | The FPGA will configure from the User Design. If this fails to load, the factory design will be loaded.                                                                                                                                                                           |

| Right          | <i>Force Factory</i> . The FPGA will configure from the Factory Design. This mode may be needed if the User Design is corrupt, and the extra time taken to try to load the User Design, and then to load the Factory Design, means that the computer does not recognize FireBird. |

#### J9 For Factory Use Only

| Position       | Meaning                                             |  |  |

|----------------|-----------------------------------------------------|--|--|

| Left (default) | The FPGA will configure based on the setting of J8. |  |  |

| Right          | 1st. This mode is for factory use only.             |  |  |

Boards

# J14 S6A Write Protect (WP)

| Position        | Meaning                                                                                                                                |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Right (default) | The secondary FPGA design for the Camera Link interface on J1 and J2 can be updated by software.                                       |

| Left            | <i>Write Protect</i> . This stops the secondary FPGA design for the Camera Link interface on J1 and J2 from being updated by software. |

# J15 S6B Write Protect (WP)

This is only present on boards with four Camera Link connectors.

| Position        | Meaning                                                                                                                                |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Right (default) | The secondary FPGA design for the Camera Link interface on J3 and J4 can be updated by software.                                       |

| Left            | <i>Write Protect</i> . This stops the secondary FPGA design for the Camera Link interface on J3 and J4 from being updated by software. |

# 3. FireBird I/O Connector

FireBird I/O (Input / Output) uses a 2mm pitch header that connects to a standard IDC ribbon cable. Example mating connector: Don Connex A05b-50-BSB1-G. If sourcing equivalent parts, check that the overall length does not exceed 54.1mm. Parts from some manufacturers are longer.

It may be easier to buy complete cables, e.g. Samtec TCSD-25-D-xx.xx-01-F-N where "xx.xx" is the cable length in inches. A six inch cable is a standard stock item at Digi-Key, code SAM8549-ND.

# 3.1. Pinout

The pinout is as follows, with corner pin numbers indicated on board layout figures in this document, and on the board itself.

| Pin | Signal      | Pin | Signal      |

|-----|-------------|-----|-------------|

| 1   | OPTO_OUT_1+ | 2   | OPTO_OUT_1- |

| 3   | OPTO_OUT_2+ | 4   | OPTO_OUT_2- |

| 5   | OPTO_OUT_3+ | 6   | OPTO_OUT_3- |

| 7   | OPTO_OUT_4+ | 8   | OPTO_OUT_4- |

| 9   | OPTO_IN_1+  | 10  | OPTO_IN_1-  |

| 11  | OPTO_IN_2+  | 12  | OPTO_IN_2-  |

| 13  | OPTO_IN_3+  | 14  | OPTO_IN_3-  |

| 15  | OPTO_IN_4+  | 16  | OPTO_IN_4-  |

| 17  | +12V        | 18  | +12V        |

| 19  | GND         | 20  | GND         |

| 21  | 422_OUT_1+  | 22  | 422_OUT_1-  |

| 23  | 422_OUT_2+  | 24  | 422_OUT_2-  |

| 25  | 422_OUT_3+  | 26  | 422_OUT_3-  |

| 27  | 422_OUT_4+  | 28  | 422_OUT_4-  |

| 29  | GND         | 30  | GND         |

| 31  | 422_IN_1+   | 32  | 422_IN_1-   |

| 33  | 422_IN_2+   | 34  | 422_IN_2-   |

| 35  | 422_IN_3+   | 36  | 422_IN_3-   |

| 37  | 422_IN_4+   | 38  | 422_IN_4-   |

| 39  | GND         | 40  | GND         |

| 41  | TTL_OUT5V_1 | 42  | TTL_OUT5V_2 |

| 43  | TTL_OUT5V_3 | 44  | TTL_OUT5V_4 |

| 45  | TTL_IN5V_1  | 46  | TTL_IN5V_2  |

| 47  | TTL_IN5V_3  | 48  | TTL_IN5V_4  |

| 49  | GND         | 50  | GND         |

Opto-isolated signals are shown in red; RS-422 signals in blue; TTL in green.

# 3.2. Signal Functions

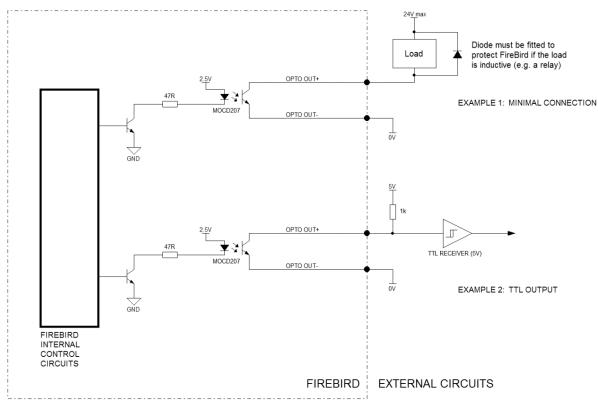

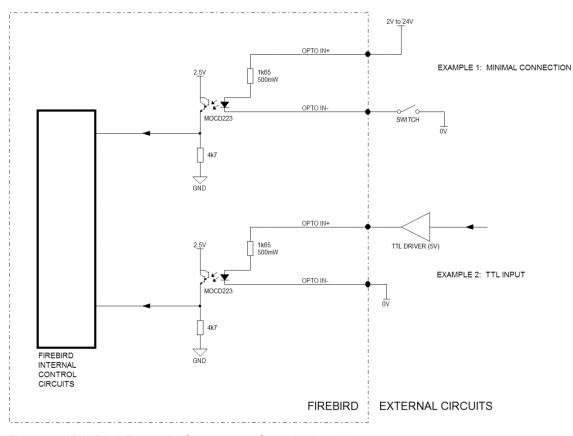

#### 3.2.1. Opto-Isolated Signals

Opto-isolated signals can be good in factory environments; however the maximum speed is much lower than RS-422 and may not be sufficient for fast line triggers. Note that slow edges on optical signals can easily result in false multiple edges. The appropriate trigger filter (see the *FireBird Programmer's Manual*) can be used to prevent these resulting in multiple triggers.

Note that the opto-isolators on FireBird do not provide safety isolation. Therefore it is recommended to keep the ground potential between the opto-isolated signals and FireBird's ground to under 50V. Some form of ground link may be needed – maybe via a resistor – to prevent the grounds drifting apart.

### OPTO\_OUT\_n+/-

Each OPTO\_OUT\_n+ signal connects to the emitter of an opto-isolated transistor, and each OPTO\_OUT\_n- signal connects to the corresponding collector.

| Parameter                                   | Value                                                   |  |  |

|---------------------------------------------|---------------------------------------------------------|--|--|

| Output current                              | 21mA maximum                                            |  |  |

| Collector - emitter saturation voltage (on) | 0.5V maximum                                            |  |  |

| Allowable collector – emitter voltage (off) | 24V maximum in normal operation<br>27V absolute maximum |  |  |

| Rise time                                   | 1.6μs typical                                           |  |  |

| Fall time                                   | 2.2μs typical                                           |  |  |

| Turn-on time                                | 3.0μs typical                                           |  |  |

| Turn-off time                               | 2.8μs typical                                           |  |  |

Transistor parameters are:

#### OPTO\_IN\_n+/-

Each OPTO\_IN\_n+ signal connects to the LED anode of an opto-isolator via a 1.65k $\Omega$  resistor, and each OPTO\_IN\_n- signal connects to the corresponding cathode.

Input parameters are:

| Parameter                                   | Value                                                   |  |  |

|---------------------------------------------|---------------------------------------------------------|--|--|

| Input voltage                               | 24V maximum in normal operation<br>27V absolute maximum |  |  |

| Minimum input voltage to detect 'on' state  | 2.0V minimum                                            |  |  |

| Maximum input voltage to detect 'off' state | 0.8V maximum                                            |  |  |

| Turn-on time                                | 3.5μs typical                                           |  |  |

| Turn-off time                               | 95µs typical (darlington transistor)                    |  |  |

Example circuits to use the opto-isolated inputs and outputs are shown on the next page, along with a simplified representation of the circuit on FireBird:

Figure 4: FireBird Example Circuits for Opto-Isolated Output

Figure 5: FireBird Example Circuits for Opto-Isolated Input

### 3.2.2. RS-422 Signals

Active Silicon recommends that RS-422 is used to receive or drive I/O outside the PC containing FireBird. This is because RS-422 is a differential signal with a relatively wide voltage range, and with good common mode voltage immunity. Therefore it is ideal for electrically noisy environments such as in factories. This is particularly important for higher speed signals such as shaft encoders for line triggers.

Note that while RS-422 can cope with several volts of common mode offset, for reliable operation the ground of FireBird must be connected to the ground of the remote system.

#### 422\_OUT\_n+/-

Each 422\_OUT\_n+/- signal comes from a standard RS-422 driver, and should be connected to a standard RS-422 receiver. For more than a short cable length, a  $100\Omega$  terminating resistor is recommended at the receiver between the + and – pins.

High speed protection devices are fitted to guard against transients.

#### 422\_IN\_n+/-

Each 422\_IN\_n+/- signal connects to a standard RS-422 receiver, and should be driven by a standard RS-422 driver. A 100 $\Omega$  terminating resistor is connected at the receiver between the + and – pins.

High speed protection devices are fitted to guard against transients.

### 3.2.3. TTL Signals

TTL is ideal to connect to a separate control board inside a PC. However Active Silicon does not recommend that TTL I/O is used outside the PC because of the very low noise immunity inherent in TTL. Note that ringing following a falling edge TTL trigger can easily result in a false positive edge. The appropriate trigger filter (see the *FireBird Programmer's Manual*) can be used to prevent these resulting in multiple triggers.

Note that the low noise immunity of TTL means that for reliable operation there must be a very good connection between the ground of FireBird and the ground of the remote system.

#### TTL\_OUT5V\_n

Each TTL\_OUT5V\_n signal comes from a 5V TTL driver with the following characteristics:

| Parameter                 | Value                                                 |  |  |

|---------------------------|-------------------------------------------------------|--|--|

| High level output voltage | 3.0V minimum at 3mA load<br>2.0V minimum at 32mA load |  |  |

| Low level output voltage  | 0.55V maximum at 64mA load                            |  |  |

| High level output current | 64mA maximum                                          |  |  |

| Low level output current  | -32mA maximum                                         |  |  |

High speed protection devices are fitted to guard against transients.

### TTL\_IN5V\_n

Each TTL IN5V n signal connects to a 5V tolerant<sup>2</sup> TTL receiver with the following characteristics:

| Parameter                | Value                        |  |  |

|--------------------------|------------------------------|--|--|

| High level input voltage | 2.0V minimum<br>5.5V maximum |  |  |

| Low level input voltage  | 0.8V maximum                 |  |  |

High speed protection devices are fitted to guard against transients.

The inputs use a "bus hold" device, so if an input is disconnected, it will retain the last level it was driven to. Approximately  $20\mu$ A is needed to overdrive the held level to make the device switch state.

### 3.2.4. +12V

This is a nominal 12V from the computer's power supply, and is provided to allow convenient use of the opto-isolated input and outputs in designs where they are used to provide higher voltage switching but isolation is not required.

The 12V output is short-circuit protected via a 200mA resettable fuse to provide compliance with safety regulations.

### 3.2.5. GND

This is the GND for the 422\_OUT\_n+/- , 422\_IN\_n+/-, TTL\_OUT5V\_n, TTL\_IN5V\_n and +12V signals. Note that there is no electrical connection between this GND and the OPTO\_OUT\_n+/- or OPTO\_IN\_n+/- signals.

This signal is the internal GND for FireBird, and is connected to the computer chassis.

<sup>&</sup>lt;sup>2</sup> Note – Some very early FireBird boards supplied in Q2, Q3 and Q4 2011 have a 4.5V maximum input voltage.

# 4. CoaXPress Connector

# 4.1. Cables

FireBird uses a high quality  $75\Omega$  BNC connector for CoaXPress.

Example mating cable: Active Silicon AS-CBL-VDM230-xxM where "xx" is the length in meters.

For reliable operation only good quality CoaXPress cables should be used. Cable quality is most critical at high bit rates and with long cables.

# 4.2. Power over CoaXPress (PoCXP)

A single BNC on FireBird can supply a nominal 24V to power cameras, up to the 17W limit allowed in the CoaXPress specification. Note that the camera is allowed up to 13W; the difference is to allow for losses in long cables. 24V is not output by FireBird if the connected camera is not identified as supporting PoCXP, according to the CoaXPress specification, and can be forced off under software control.

# 4.3. General

Although CoaXPress can automatically detect multiple cameras regardless of the order that the BNCs are connected, there may be significant benefits in OEM applications if a fixed connection order is defined so that a given software *handle* always connects to the same camera.

For full details of CoaXPress, see the specification available from the *Japan Industrial Imaging Association (JIIA)*, <u>http://jiia.org/</u>.

# 5. Camera Link Connector

# 5.1. Cables

FireBird uses the standard "MDR" type Camera Link connectors.

Example mating cable: Active Silicon AS-CBL-CL-MP-D-xxM where "xx" is the length in meters.

For reliable operation only good quality Camera Link cables should be used. Cable quality is most critical in Full and Deca modes at or near the 85 MHz upper frequency limit, and with long cables.

# 5.2. Power over Camera Link (PoCL)

A single Camera Link connector on FireBird can supply a nominal 12V to power cameras, up to the 4W limit allowed in the Camera Link specification. 12V is not output by FireBird if the connected camera is not identified as supporting PoCL, according to the SafePower protocol.

# 5.3. Pinout

FireBird follows the industry standard Camera Link pinout shown below, with corner pin numbers indicated on the board itself.

| Pin | Base Mode or<br>Primary<br>Connector | Secondary<br>Connector | Pin | Base Mode or<br>Primary<br>Connector | Secondary<br>Connector |

|-----|--------------------------------------|------------------------|-----|--------------------------------------|------------------------|

| 1   | PoCL Power                           | PoCL Power             | 14  | Power Return                         | Power Return           |

| 2   | CC4-                                 | Z3+                    | 15  | CC4+                                 | Z3-                    |

| 3   | CC3+                                 | Zclk+                  | 16  | CC3-                                 | Zclk-                  |

| 4   | CC2-                                 | Z2+                    | 17  | CC2+                                 | Z2-                    |

| 5   | CC1+                                 | Z1+                    | 18  | CC1-                                 | Z1-                    |

| 6   | SerTFG+                              | Z0+                    | 19  | SerTFG-                              | Z0-                    |

| 7   | SerTC-                               | Spare                  | 20  | SerTC+                               | Spare                  |

| 8   | X3+                                  | Y3+                    | 21  | Х3-                                  | Y3-                    |

| 9   | Xclk+                                | Yclk+                  | 22  | Xclk-                                | Yclk-                  |

| 10  | X2+                                  | Y2+                    | 23  | X2-                                  | Y2-                    |

| 11  | X1+                                  | Y1+                    | 24  | X1-                                  | Y1-                    |

| 12  | X0+                                  | Y0+                    | 25  | X0-                                  | Y0-                    |

| 13  | Power Return                         | Power Return           | 26  | PoCL Power                           | PoCL Power             |

High speed signals are shown in red; low speed signals in blue.

Note that when connected to a non-PoCL camera, the "PoCL Power" and "PoCL Return" signals all become signal return lines.

# 5.4. General

For full details of Camera Link, see the specification available from the AIA (formerly *Automated Imaging Association*), <u>http://www.visiononline.org/</u>.

# 6. PCI Express Graphics Connector

This connector supplies 12V to the *Power over CoaXPress* (PoCXP) power supply on FireBird. It is only needed when cameras requiring PoCXP are used. Computers may have many superficially similar cables, so it is **important** that the following section is used to identify the correct cable for FireBird.

# 6.1. Cable Identification

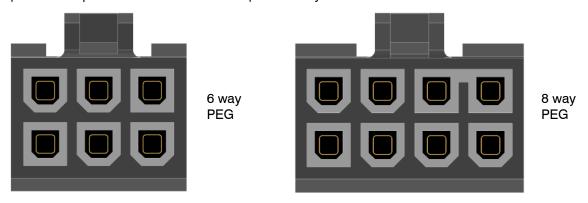

The correct power supply cable is one intended for PCI Express Graphics (PEG) cards, and may have 6 or 8 ways. To distinguish it from other similar connectors in the computer, the connector should be black and may be marked "PCI-E" or "PEG". Similar connectors that are not PEG should be white. However this is often not the case, so the cables should be carefully checked for the pattern of squares and chamfers on the plastic body of the connector at the end of the cable:

#### Figure 6: PCI Express Graphics Connectors

Also, the wires should be black on the side with the connector clip, and colored (often yellow or blue) on the side opposite the connector clip.

# If the connector does not match those shown above, DO NOT attempt to force it into FireBird as this could result in serious damage.

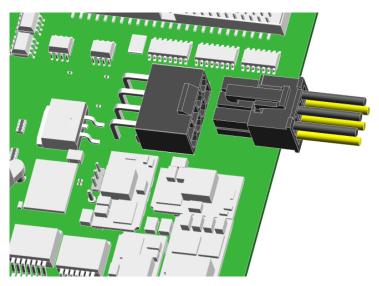

If a 6 way connector is plugged into FireBird, it should be aligned at the upper 6 ways of the 8 way FireBird connector as shown below:

Figure 7: 6 Way PCI Express Graphics Connector Alignment

PEG cable splitters, PEG to SATA adapters and PEG to "Molex" adapters are available from Active Silicon and are included in the optional cable starter kit.

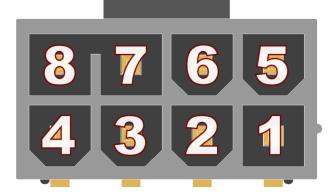

#### 6.2. Pinout

For OEMs that need to make cables to connect to non-PC power supplies, the pinout is:

Figure 8: PCI Express Graphics Pinout (view into J13)

| Pin | Signal     | Pin | Signal     |

|-----|------------|-----|------------|

| 1   | +12V       | 5   | GND        |

| 2   | +12V       | 6   | No connect |

| 3   | +12V       | 7   | GND        |

| 4   | No connect | 8   | GND        |

In a general case the power supply needs to provide 12V at approximately 70W to allow for four cameras at maximum power, however in a closed system with known cameras a much lower wattage may be usable.

6 way connectors are currently more widely available than 8 way ones. A suitable 6 way mating connector is Molex 0455590002.

# 7. Notes on PCI Express Slots

It is best to check your computer's documentation to choose the appropriate PCI Express slot because there are several issues to consider:

- FireBird will automatically drop to Gen 1 speed if plugged into a Gen 1 slot in the computer, however this may not give sufficient bandwidth for many applications.

- Most x16 slots will support x8 operation, but this is not always the case.

- Some x16 slots are dedicated for graphics card use, and may not work at all, or may work slowly, with any other type of board such as FireBird.

- Some computers, including many Apple Macs, use x16 connectors even if the slot only supports x1 operation.

- Some computers, including some Apple Macs, require a configuration utility to be run to set the slot width.

- At Gen 2 speeds, ribbon cable style PCI Express extenders as supplied with many small form factor computers are unlikely to work reliably, if at all.

This page intentionally blank.