# PROGRAMMING

IsoMax<sup>TM</sup> is a programming language based on Finite State Machine (FSM) concepts applied to software, with a procedural language (derived from Forth) underneath it. The closest description to the FSM construction type is a "One-Hot" Mealy type of Timer Augmented Finite State Machines. More on these concepts will come later.

## QUICK OVERVIEW

What is IsoMax<sup>TM</sup>? IsoMax<sup>TM</sup> is a real time operating system / language.

How do you program in IsoMax<sup>TM</sup>? You create state machines that can run in a virtually parallel architecture.

| Step | Programming Action                         | Syntax                                                                                                                                              |

|------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Name a state machine                       | MACHINE <name></name>                                                                                                                               |

| 2    | Select this state                          | ON-MACHINE <name></name>                                                                                                                            |

| 3    | Name any states appended on the machine    | APPEND-STATE <name><br/>APPEND-STATE <name><br/></name></name>                                                                                      |

| 4    | Describe transitions from states to states | IN-STATE<br><state><br/>CONDITION<br/><boolean><br/>CAUSES<br/><action><br/>THEN-STATE<br/><state><br/>TO-HAPPEN</state></action></boolean></state> |

| 5    | Test and Install                           | {as required}                                                                                                                                       |

What do you have to write to make a state machine in IsoMax<sup>TM</sup>? You give a machine a name, and then tell the system that's the name you want to work on. You append any number of states to the machine. You describe any number of transitions between states. Then you test the machine and when satisfied, install it into the machine chain.

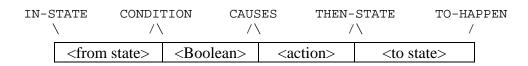

What is a transition? A transition is how a state machine changes states. What's in a transition? A transition has four components; 1) which state it starts in, 2) the condition necessary to leave, 3) the action to take when the condition comes true, and 4) the state to go to next time. Why are transitions so verbose? The structure makes the transitions easy to read in human language. The constructs IN-STATE, CONDITION, CAUSES, THEN-STATE and TO-HAPPEN are like the five brackets around a table of four things.

In a transition description the constructs IN-STATE, CONDITION, CAUSES, THEN-STATE and TO-HAPPEN are always there (with some possible options to be set out later). The "meat slices" between the "slices of bread" are the hearty stuffing of the description. You will fill in those portions to your own needs and liking. The language provides "the bread" (with only a few options to be discussed later).

So here you have learned a bit of the syntax of IsoMax<sup>TM</sup>. Machines are defined, states appended. The transitions are laid out in a pattern, with certain words surrounding others. Procedural parts are inserted in the transitions between the standard clauses.

The syntax is very loose compared to some languages. What is important is the order or sequence these words come in. Whether they occur on one line or many lines, with one space or many spaces between them doesn't matter. Only the order is important.

### **THREE MACHINES**

Now let's take a first step at exploring IsoMax<sup>™</sup> the language by looking at some very simple examples. We'll explore the language with what we've just tested earlier, the LED words. We'll add some machines that will use the LED's as outputs, so we can visually "see" how we're coming along.

### REDTRIGGER

First let's make a very simple machine. Since it is so short, at least in V0.3 and later, it's presented first without detailed explanation, entered and tested. Then we will explain the language to create the machine step by step

MACHINE REDTRIGGER ON-MACHINE REDTRIGGER APPEND-STATE RT IN-STATE RT CONDITION PA7 OFF? CAUSES REDLED ON THEN-STATE RT TO-HAPPEN RT SET-STATE ( INSTALL REDTRIGGER EVERY 50000 CYCLES SCHEDULE-RUNS REDTRIGGER There you have it, a complete real time program in two lines of IsoMax<sup>TM</sup>, and few additional lines to install it. A useful virtual machine is made here with one state and one transition.

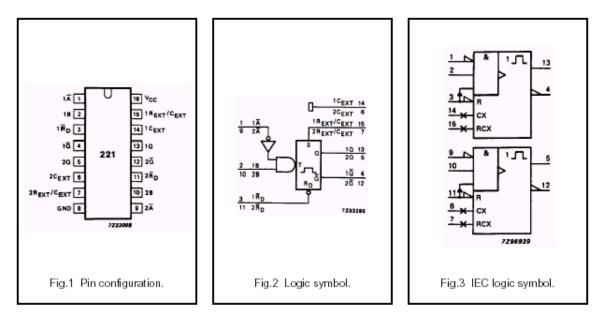

This virtual machine acts like a non-retriggerable one-shot made in hardware. (NON-RETRIGGERABLE ONE-SHOT TIMER: Produces a preset timed output signal on the occurrence of an input signal. The timed output response may begin on either the leading edge or the trailing edge of the input signal. The preset time (in this case: infinity) is independent of the duration of the input signal.) For an example of a hardware non-retriggerable one-shot, see <a href="http://www.philipslogic.com/products/hc/pdf/74hc221.pdf">http://www.philipslogic.com/products/hc/pdf/74hc221.pdf</a>.

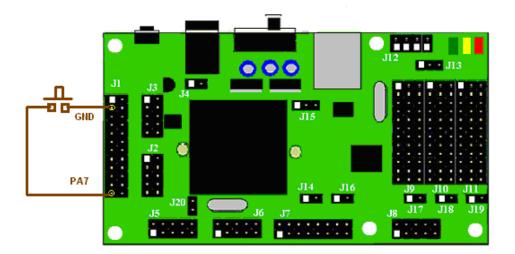

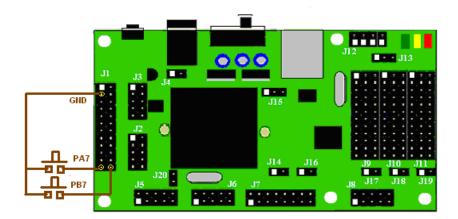

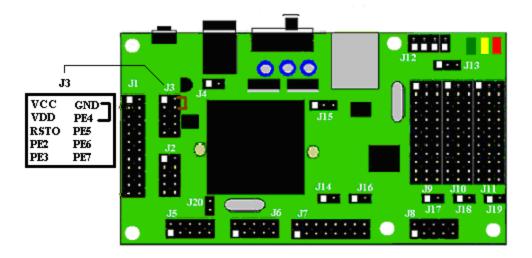

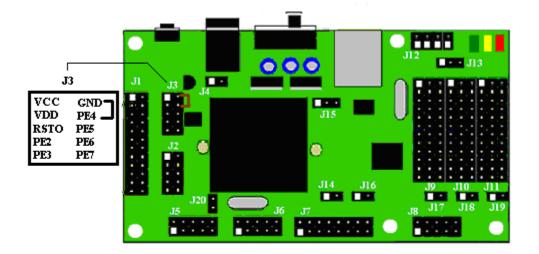

If PA7 goes low briefly, the red LED turns on and stays on even if PA7 then changes. PA7 normally has a pull up resistor that will keep it "on", or "high" if nothing is attached. So attaching push button from PA7 to ground, or even hooking a jumper test lead to ground and pushing the other end into contact with the wire lead in PA7, will cause PA7 to go "off" or "low", and the REDLED will come on.

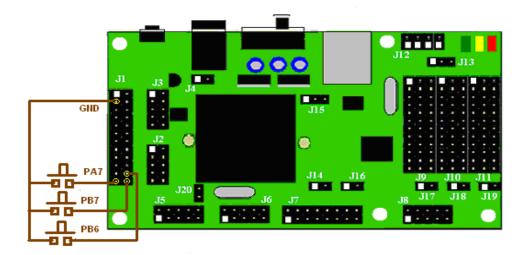

(In these examples, any port line that can be an input could be used. PA7 here, PB7 and PB6 later, were chosen because they are on  $\underline{J1}$  and the easy to access.)

Now if you want, type these lines shown above in. (If you are reading this manual electronically, you should be able to highlight the text on screen and copy the text to the clipboard with Cntl-C. Then you may be able to paste into your terminal program. On <u>MaxTerm</u>, the command to down load the clipboard is Alt-V. On other windows programs it might be Cntl-V.)

Odds are your red LED is already on. When the ServoPod-USB<sup>TM</sup> powers up, it's designed to have the LED's on, unless programmed otherwise by the user. So to be useful we must reset this one-shot. Enter:

REDLED OFF

Now install the REDTRIGGER by installing it in the (now empty) machine chain.

RT SET-STATE (INSTALL REDTRIGGER EVERY 50000 CYCLES SCHEDULE-RUNS REDTRIGGER

Ground PA7 with a wire or press the push button, and see the red LED come on. Remove the ground or release the push button. The red LED does not go back off. The program is still running, even though all visible changes end at that point. To see that, we'll need to manually reset the LED off so we can see something happen again. Enter.

REDLED OFF

If we ground PA7 again, the red LED will come back on, so even though we are still fully interactive with the ServoPod-USB<sup>TM</sup> able to type commands like REDLED OFF in manually, the REDTRIGGER machine is running in the background.

Now let's go back through the code, step-by-step. We'll take it nice and easy. We'll take the time explain the concepts of this new language we skipped over previously.

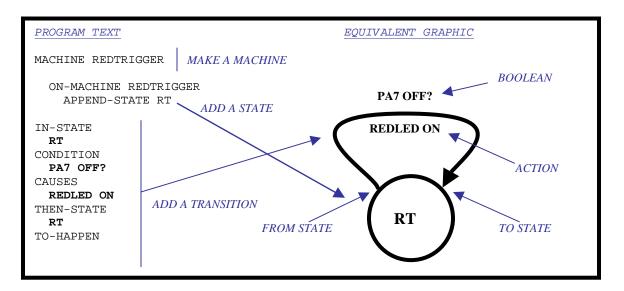

Here in this box, the code for REDTRIGGER "pretty printed" so you can see how the elements of the program relate to a state machine diagram. Usually you start to learn a language by learning the syntax, or how and where elements of the program must be placed. The syntax of the IsoMax<sup>TM</sup> language is very loose. Almost anything can go on any line with any amount of white space between them as long as the sequence remains the same. So in the pretty printing, most things are put on a separate line and have spaces in front of them just to make the relationships easy to see. Beyond the basic language syntax, a few words have a further syntax associated to them. They must have new names on the same line as them. In this example, MACHINE, ON-MACHINE and APPEND-STATE require a name following. You will see that they do. More on syntax will come later.

In this example, the first program line, we tell IsoMax<sup>TM</sup> we're making a new virtual machine, named REDTRIGGER. (Any group of characters without a space or a backspace or return will do for a name. You can be very creative. Use up to 32 characters. Here the syntax is MACHINE followed by the chosen name.)

#### MACHINE REDTRIGGER

That's it. We now have a new machine. This particular new machine is named REDTRIGGER. It doesn't do anything yet, but it is part of the language, a piece of our program.

For our second program line, we'll identify REDTRIGGER as the machine we want to append things to. The syntax to do this is to say ON-MACHINE and the name of the

machine we want to work on, which we named REDTRIGGER so the second program line looks like this:

ON-MACHINE REDTRIGGER

(Right now, we only have one machine installed. We could have skipped this second line. Since there could be several machines already in the ServoPod-USB<sup>TM</sup> at the moment, it is good policy to be explicit. Always use this line before appending states. When you have several machines defined, and you want to add a state or transition to one of them, you will need that line to pick the machine being appended to. Otherwise, the new state or transition will be appended to the last machine worked on.)

All right. We add the machine to the language. We have told the language the name of the machine to add states to. Now we'll add a state with a name. The syntax to do this is to say APPEND-STATE followed by another made-up name of our own. Here we add one state RT like this:

APPEND-STATE RT

States are the fundamental parts of our virtual machine. States help us factor our program down into the important parts. A state is a place where the computer's outputs are stable, or static. Said another way, a state is place where the computer waits. Since all real time programs have places where they wait, we can use the waits to allow other programs to have other processes. There is really nothing for a computer to do while its outputs are stable, except to check if it is time to change the outputs.

(One of the reasons IsoMax<sup>TM</sup> can do virtually parallel processing, is it never allows the computer to waste time in a wait, no backwards branches allowed. It allows a check for the need to leave the state once per scheduled time, per machine.)

To review, we've designed a machine and a sub component state. Now we can set up something like a loop, or jump, where we go out from the static state when required to do some processing and come back again to a static wait state.

The rules for changing states along with the actions to do if the rule is met are called transitions. A transition contains the name of the state the rule applies to, the rules called the condition, what to do called the action, and "where to go" to get into another state. (We have only one state in this example, so the last part is easy. There is no choice. We go back into the same state. In machines with more than one state, it is obviously important to have this final piece.)

There's really no point in have a state in a machine without a transition into or out of it. If there is no transition into or out of a state, it is like designing a wait that cannot start, cannot end, and cannot do anything else either.

On the other hand, a state that has no transition into it, but does have one out of it, might be an "initial state" or a "beginning state". A state that has a transition into it, but doesn't have one out of it, might be a "final state" or an "ending state". However, most states will have at least one (or more) transition entering the state and one (or more) transition leaving the state. In our example, we have one transition that leaves the state, and one that comes into the state. It just happens to be the same one.

Together a condition and action makes up a transition, and transitions go from one specific state to another specific state. So there are four pieces necessary to describe a transition; 1) The state the machine starts in. 2) the condition to leave that state 3) the action taken between states and 4) the new state the machine goes to.

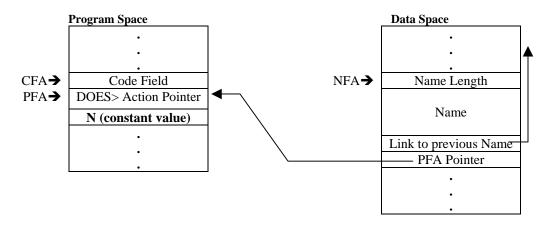

Looking at the text box with the graphic in it, we can see the transitions four elements clearly labeled. In the text version, these four elements are printed in bold. In the equivalent graphic they are labeled as "FROM STATE", "BOOLEAN", "ACTION" and "TO STATE".

The "FROM STATE" is RT. The "BOOLEAN" is a simple phrase checking I/O PA7 OFF?. The "ACTION" is REDLED ON. The "TO STATE" is again RT.

So to complete our state machine program, we must define the transition we need. The syntax to make a transition, then, is to fill in the blanks between this form: IN-STATE <name> CONDITION <Boolean> CAUSES <action> THEN-STATE <name> TO-HAPPEN.

Whether the transition is written on one line as it was at first:

IN-STATE RT CONDITION PA7 OFF? CAUSES REDLED ON THEN-STATE RT TO-HAPPEN

Or pretty printed on several lines as it was in the text box:

```

IN-STATE

RT

CONDITION

PA7 OFF?

CAUSES

REDLED ON

THEN-STATE

RT

TO-HAPPEN

```

The effect is the same. The five bordering words are there, and the four user supplied states, condition and action are in the same order and either way do the same thing.

After the transition is added to the program, the program can be tested and installed as shown above.  $\bullet$

State machine diagrams (the graphic above being an example) are nothing new. They are widely used to design hardware. They come with a few minor style variations, mostly related to how the outputs are done. But they are all very similar. The figure to the right is a hardware Quadrature design with four states.

While FSM diagrams are also widely known in programming as an abstract computational element, there are few instances where they are used to design software. Usually, the tools for writing software in state machines are very hard to follow. The programming style doesn't seem to resemble the state machine design, and is often a slow, table-driven "read, process all inputs, computation and output" scheme.

IsoMax<sup>™</sup> technology has overcome this barrier, and gives you the ability to design software that looks "like" hardware and runs "like" hardware (not quite as fast of course, but in the style, or thought process, or "paradigm" of hardware) and is extremely efficient. The Virtually Parallel Machine Architecture lets you design many little, hardware-like, machines, rather than one megalith software program that lumbers through layer after layer of if-then statements. (You might want to refer to the IsoMax Reference Manual to understand the language and its origins.)

### ANDGATE1

Let's do another quick little machine and install both machines so you can see them running concurrently.

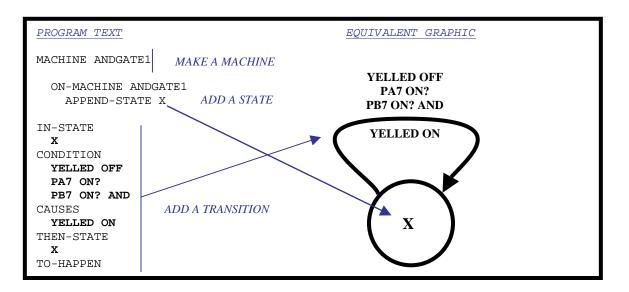

MACHINE ANDGATE1 ON-MACHINE ANDGATE1 APPEND-STATE X IN-STATE X CONDITION YELLED OFF PA7 ON? PB7 ON? AND CAUSES YELLED ON THEN-STATE X TO-HAPPEN

X SET-STATE ( INSTALL ANDGATE1 MACHINE-CHAIN CHN1 REDTRIGGER ANDGATE1 END-MACHINE-CHAIN EVERY 50000 CYCLES SCHEDULE-RUNS CHN1

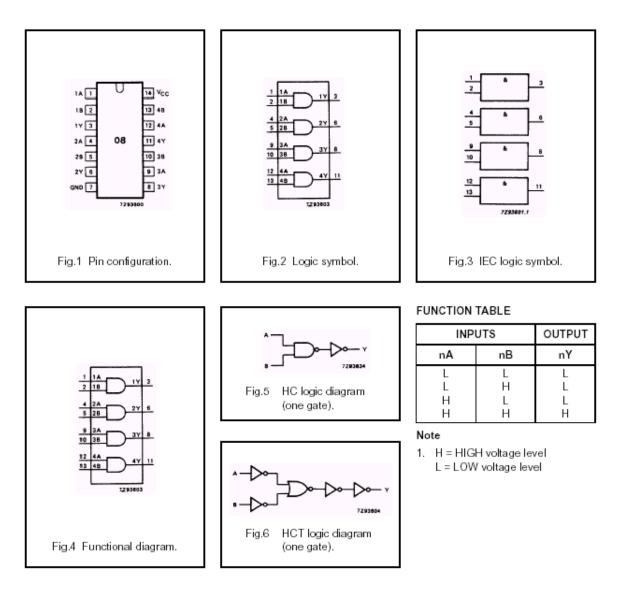

There you have it, another complete real time program in three lines of IsoMax<sup>™</sup>, and one additional line to install it. A useful virtual machine is made here with one state and one transition. This virtual machine acts (almost) like an AND gate made in hardware. For example: <u>http://www.philipslogic.com/products/hc/pdf/74hc08.pdf</u>

Both PA7 and PB7 must be on, or high, to allow the yellow LED to remain on (most of the time). So by attaching push buttons to PA7 and PB7 simulating micro switches this little program could be used like an interlock system detecting "cover closed".

(Now it is worth mentioning, the example is a bit contrived. When you try to make a state machine too simple, you wind up stretching things you shouldn't. This example could have acted exactly like an AND gate if two transitions were used, rather than just one. Instead, a "trick" was used to turn the LED off every time in the condition, then turn it on only when the condition was true. So a noise spike is generated a real "and" gate doesn't have. The trick made the machine simpler, it has half the transitions, but it is less functional. Later we'll revisit this machine in detail to improve it.)

Notice both machines share an input, but are using the opposite sense on that input. ANDGATE1 looks for PA7 to be ON, or HIGH. The internal pull up will normally make PA7 high, as long as it is programmed for a pull up and nothing external pulls it down.

Grounding PA7 enables REDTRIGGER's condition, and inhibits ANDGATE1's condition. Yet the two machines coexist peacefully on the same processor, even sharing the same inputs in different ways.

To see these machines running enter the new code, if you are still running REDTRIGGER, reset (toggle the DTR line on the terminal, for instance, Alt-T twice in <u>MaxTerm</u> or cycle power) and download the whole of both programs.

Initialize REDTRIGGER for action by turning REDLED OFF as before. Grounding PA7 now causes the same result for REDTRIGGER, the red LED goes on, but the opposite effect for the yellow LED, which goes off while PA7 is grounded. Releasing PA7 turns the yellow LED back on, but the red LED remains on.

Again, initialize REDTRIGGER by turning REDLED OFF. Now ground PB7. This has no effect on the red LED, but turns off the yellow LED while grounded. Grounding both PA7 and PB7 at the same time also turns off the yellow LED, and turns on the red LED if not yet set.

Notice how the tightly the two machines are intertwined. Perhaps you can imagine how very simple machines with combinatory logic and sharing inputs and feeding back outputs can quickly start showing some complex behaviors. Let's add some more complexity with another machine sharing the PA7 input.

### BOUNCELESS

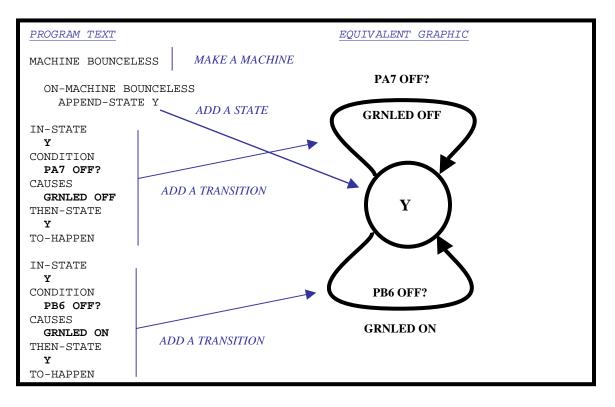

We have another quick example of a little more complex machine, one with one state and two transitions.

MACHINE BOUNCELESS ON-MACHINE BOUNCELESS APPEND-STATE Y IN-STATE Y CONDITION PA7 OFF? CAUSES GRNLED OFF THEN-STATE Y TO-HAPPEN IN-STATE Y CONDITION PB6 OFF? CAUSES GRNLED ON THEN-STATE Y TO-HAPPEN Y SET-STATE ( INSTALL BOUNCELESS MACHINE-CHAIN 3EASY REDTRIGGER ANDGATE BOUNCELESS END-MACHINE-CHAIN EVERY 50000 CYCLES SCHEDULE-RUNS 3EASY

There you have yet another complete design, initialization and installation of a virtual machine in four lines of IsoMax<sup>TM</sup> code.

Another name for the machine in this program is "a bounceless switch".

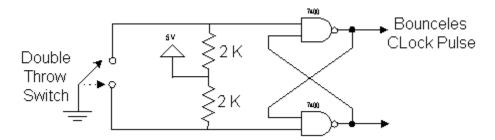

Bounceless switches filter out any noise on their input buttons, and give crisp, one-edge output signals. They do this by toggling state when an input first becomes active, and remaining in that state. If you are familiar with hardware, you might recognize the two gates feed back on each other as a very elementary flip-flop. The flip-flop is a bistable on/off circuit is the basis for a memory cell. The bounceless switch flips when one input is grounded, and will not flip back until the other input is grounded.

By attaching push buttons to PA7 and PB6 the green LED can be toggled from on to off with the press of the PA7 button, or off to on with the press of the PB6. The PA7 button acts as a reset switch, and the PB6 acts as a set switch.

You can see here, in IsoMax<sup>TM</sup>, you can simulate hardware machines and circuits, with just a few lines of code. Here we created one machine, gave it one state, and appended two transitions to that state. Then we installed the finished machine along with the two previous machines. All run in the background, freeing us to program more virtual machines that can also run in parallel, or interactively monitor existing machines from the foreground.

Notice all three virtual hardware circuits are installed at the same time, they operate virtually in parallel, and the ServoPod-USB<sup>TM</sup> is still not visibly taxed by having these machines run in parallel. Further, all three machines share one input, so their behavior is strongly linked.

## SYNTAX AND FORMATTING

Let's talk a second about pretty printing, or pretty formatting. To go a bit into syntax again, you'll need to remember the following. Everything in  $IsoMax^{TM}$  is a word or a number. Words and numbers are separated spaces (or returns).

Some words have a little syntax of their own. The most common cases for such words are those that require a name to follow them. When you add a new name, you can use any combinations of characters or letters except (obviously) spaces and backspaces, and carriage returns. So, when it comes to pretty formatting, you can put as much on one line as will fit (up to 80 characters). Or you can put as little on one line as you wish, as long as you keep your words whole. However, some words will require a name to follow them, so those names will have to be on the same line.

In the examples you will see white space (blanks) used to add some formatting to the source text. MACHINE starts at the left, and is followed by the name of the new machine being added to the language. ON-MACHNE is indented right by two spaces. APPEND-STATE x is indented two additional spaces. This is the suggested, but not mandatory, offset to achieve pretty formatting. Use two spaces to indent for levels. The transitions are similarly laid out, where the required words are positioned at the left, and the user programming is stepped in two spaces.

# MULTIPLE STATES/MULTIPLE TRANSITIONS

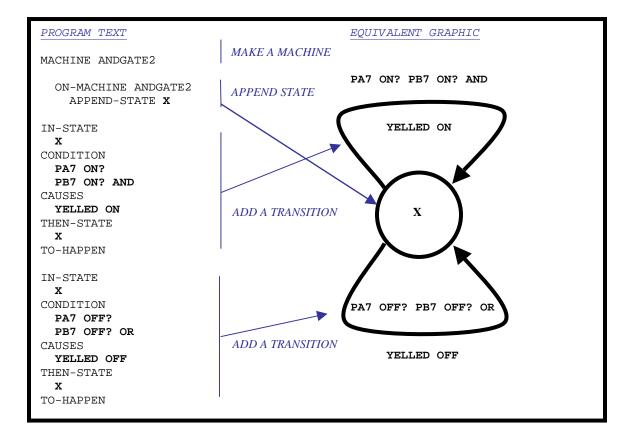

Before we leave the previous "Three Machines", let's review the AND machine again, since it had a little trick in it to keep it simple, just one state and one transition. The trick does simplify things, but goes too far, and causes a glitch in the output. To make an AND gate which is just like the hardware AND we need at least two transitions. The previous example, BOUNCELESS was the first state machine with more than one transition. We'll follow this precedent and redo ANDGATE2 with two transitions.

# ANDGATE2

MACHINE ANDGATE2

```

ON-MACHINE ANDGATE2

APPEND-STATE X

IN-STATE

Х

CONDITION

PA7 ON?

PB7 ON? AND

CAUSES

YELLED ON

THEN-STATE

Х

TO-HAPPEN

IN-STATE

Х

CONDITION

PA7 OFF?

PB7 OFF? OR

CAUSES

YELLED OFF

THEN-STATE

Х

TO-HAPPEN

```

#### X SET-STATE ( INSTALL ANDGATE2

EVERY 50000 CYCLES SCHEDULE-RUNS ANDGATE2

Compare the transitions in the two ANDGATE's to understand the trick in ANDGATE1. Notice there is an "action" included in the ANDGATE1 condition clause. See the **YELLED OFF** statement (highlighted in bold) in ANDGATE1, not present in ANDGATE2? Further notice the same phrase **YELLED OFF** appears in the second transition of ANDGATE2 as the object action of that transition.

| TRANSITION COMPARISON |             |             |  |

|-----------------------|-------------|-------------|--|

| ANDGATE1              | ANDO        | GATE2       |  |

| IN-STATE              | IN-STATE    | IN-STATE    |  |

| Х                     | Х           | Х           |  |

| CONDITION             | CONDITION   | CONDITION   |  |

| YELLED OFF            |             |             |  |

| PA7 ON?               | PA7 ON?     | PA7 OFF?    |  |

| PB7 ON? AND           | PB7 ON? AND | PB7 OFF? OR |  |

| CAUSES                | CAUSES      | CAUSES      |  |

| YELLED ON             | YELLED ON   | YELLED OFF  |  |

| THEN-STATE            | THEN-STATE  | THEN-STATE  |  |

| Х                     | Х           | Х           |  |

| TO-HAPPEN             | TO-HAPPEN   | TO-HAPPEN   |  |

The way this trick worked was by using an action in the condition clause, every time the scheduler ran the chain of machines, it would execute the conditions clauses of all transitions on any active state. Only if the condition was true, did any action of a transition get executed. Consequently, the trick used in ANDGATE1 caused the action of the second transition to happen when conditionals (only) should be running. This meant it was as if the second transition of ANDGATE2 happened every time. Then if the condition found the action to be a "wrong" output in the conditional, the action of ANDGATE1 ran and corrected the situation. The brief time the processor took to correct the wrong output was the "glitch" in ANDGATE1's output.

Now this AND gate, ANDGATE2, is just like the hardware AND, except not as fast as most modern versions of AND gates implemented in random logic on silicon. The latency of the outputs of ANDGATE2 are determined by how many times ANDGATE2 runs per second. The programmer determines the rate, so has control of the latency, to the limits of the CPU's processing power.

The original ANDGATE1 serves as an example of what not to do, yet also just how flexible you can be with the language model. Using an action between the CONDITION and CAUSES phrase is not prohibited, but is considered not appropriate in the paradigm of Isostructure.

An algorithm flowing to determine a single Boolean value should be the only thing in the condition clause of a transition. Any other action there slows the machine down, being executed every time the machine chain runs.

Most of the time, states wait. A state is meant to take no action, and have no output. They run the condition only to check if it is time to stop the wait, time to take an action in a transition.

The actions we have taken in these simple machines if very short. More complex machines can have very complex actions, which should only be run when it is absolutely necessary. Putting actions in the conditional lengthens the time it takes to operate waiting machines, and steals time from other transitions.

Why was it necessary to have two transitions to do a proper AND gate? To find the answer look at the output of an AND gate. There are two possible mutually exclusive outputs, a "1" or a "0". Once action cannot set an output high or low. One output can set a bit high. It takes a different output to set a bit low. Hence, two separate outputs are required.

## ANDOUT

Couldn't we just slip an action into the condition spot and do away with both transitions? Couldn't we just make a "thread" to do the work periodically? Yes, perhaps, but that would break the paradigm. Let's make a non-machine definition. The output of our conditional is in fact a Boolean itself. Why not define:

: ANDOUT PA7 ON? PB7 ON? AND IF YELLED ON ELSE YELLED OFF THEN ;

Why not forget the entire "machine and state" stuff, and stick ANDOUT in the machine chain instead? There are no backwards branches in this code. It has no Program Counter Capture (PCC) Loops. It runs straight through to termination. It would work.

This, however, is another trick you should avoid. Again, why? This code does one of two actions every time the scheduler runs. The actions take longer than the Boolean test and transfer to another thread. The system will run slower, because the same outputs are being generated time after time, whether they have changed or not. While the speed penalty in this example is exceedingly small, it could be considerable for larger state machines with more detailed actions.

A deeper reason exists that reveals a great truth about state machines. Notice we have used a state machine to simulate a hardware gate. What the AND gate outputs next is completely dependent on what the inputs are next. An AND gate has an output which has no feedback. An AND gate has no memory. State machines can have memory. Their future outputs depend on more than the inputs present. A state machine's outputs can also depend on the history of previous states. To appreciate this great difference between state machines and simple gates, we must first look a bit further at some examples with multiple states and multiple transitions.

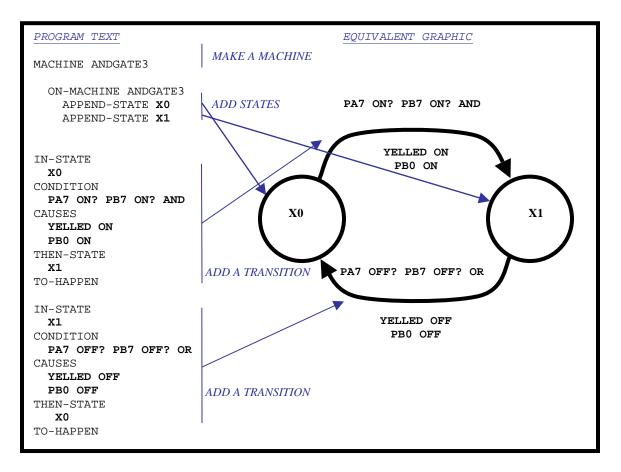

### ANDGATE3

We are going to do another AND gate version, ANDGATE3, to illustrate this point about state machines having multiple states. This version will have two transitions and two states. Up until now, our machines have had a single state. Machines with a single state in general are not very versatile or interesting. You need to start thinking in terms of machines with many states. This is a gentle introduction starting with a familiar problem. Another change is in effect here. We have previously first written the code so as to make the program small in terms of lines. We used this style to emphasize small program length. From now on, we are going to pretty print it so it reads as easily as possible, instead.

```

MACHINE ANDGATE3

ON-MACHINE ANDGATE3

APPEND-STATE X0

APPEND-STATE X1

IN-STATE

X0

CONDITION

PA7 ON? PB7 ON? AND

CAUSES

YELLED ON

PB0 ON

THEN-STATE

X1

TO-HAPPEN

IN-STATE

X1

CONDITION

PA7 OFF? PB7 OFF? OR

CAUSES

YELLED OFF

PB0 OFF

THEN-STATE

X0

TO-HAPPEN

XO SET-STATE ( INSTALL ANDGATE3

EVERY 50000 CYCLES SCHEDULE-RUNS ANDGATE3

```

Notice how similar this version of an AND gate, ANDGATE3, is to the previous version, ANDGATE2. The major difference is that there are two states instead of one. We also added some "spice" to the action clauses, doing another output on PB0, to show how actions can be more complicated.

# INTER-MACHINE COMMUNICATIONS

Now imagine ANDGATE3 is not an end unto itself, but just a piece of a larger problem. Now let's say another machine needs to know if both PA7 and PB7 are both high? If we had only one state, it would have to recalculate the AND phrase, or read back what ANDGATE3 had written as outputs. Rereading written outputs is sometimes dangerous, because there are hardware outputs which is cannot be read back. If we use different states for each different output, the state information itself stores which state is active. All an additional machine has to do to discover the status of PA7 and PB7 AND'ed together is check the stored state information of ANDGATE3. To accomplish this, simply query the state this way.

X0 IS-STATE?

A Boolean value will be returned that is TRUE if either PA7 and PB7 are low. This Boolean can be part of a condition in another state. On the other hand:

X1 IS-STATE?

will return a TRUE value only if PA7 and PB7 are both high.

# STATE MEMORY

So you see, a state machine's current state is as much as an output as the outputs PB0 ON and YELLOW LED ON are, less likely to have read back problems, and faster to check. The current state contains more information than other outputs. It can also contain history. The current state is so versatile, in fact, it can store all the pertinent history necessary to make any decision on past inputs and transitions. This is the deep truth about state machines we sought.

### 9-2 THE FINITE-STATE MODEL -- BASIC DEFINITION

The behavior of a finite-state machine is described as a sequence of events that occur at discrete instants, designated t = 1, 2, 3, etc. Suppose that a machine *M* has been receiving inputs signals and has been responding by producing output signals. If now, at time t, we were to apply an input signal x(t) to M, its response z(t) would depend on x(t), as well as the past inputs to *M*.

From: SWITCHING AND FINITE AUTOMATA THEORY, KOHAVI

No similar solution is possible with short code threads. While variables can indeed be used in threads, and threads can again reference those variable, using threads and variables leads to deeply nested IF ELSE THEN structures and dreaded spaghetti code which often invades and complicates real time programs.

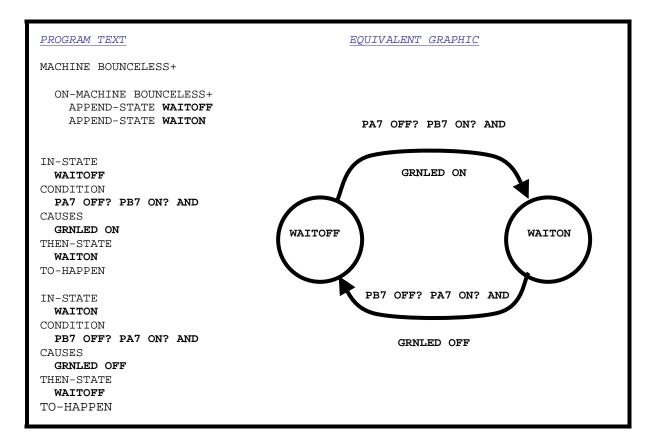

### **BOUNCELESS+**

To put the application of state history to the test, let's revisit our previous version of the machine BOUNCELESS. Refer back to the code for transitions we used in BOUNCELESS.

| STATE Y    |            |  |

|------------|------------|--|

| IN-STATE   | IN-STATE   |  |

| Y          | Y          |  |

| CONDITION  | CONDITION  |  |

| PA7 OFF?   | PB6 OFF?   |  |

| CAUSES     | CAUSES     |  |

| GRNLED OFF | GRNLED ON  |  |

| THEN-STATE | THEN-STATE |  |

| Y          | Y          |  |

| TO-HAPPEN  | TO-HAPPEN  |  |

This code worked fine, as long as PA7 and PB6 were pressed one at a time. The green LED would go on and off without noise or bounces between states. Notice however, PA7 and PB6 being low at the same time is not excluded from the code. If both lines go low at the same time, the output of our machine is not well determined. One state output will take precedence over the other, but which it will be cannot be determined from just looking at the program. Whichever transition gets first service will win.

Now consider how BOUNCELESS+ can be improved if the state machines history is integrated into the problem. In order to have state history of any significance, however, we must have multiple states. As we did with our ANDGATE3 let's add one more state. The new states are WAITON and WAITOFF and run our two transitions between the two states. At first blush, the new machine looks more complicated, probably slower, but not significantly different from the previous version. This is not true however. When the scheduler calls a machine, only the active state and its transitions are considered. So in the previous version each time Y was executed, two conditionals on two transitions were tested (assuming no true condition). In this machine, two conditionals on *only* one transition are tested. As a result this machine runs slightly faster.

Further, the new BOUNCELESS+ machine is better behaved. (In fact, it is better behaved than the original hardware circuit shown!) It is truly bounceless, even if both switches are pressed at once. The first input detected down either takes us to its state or inhibits the release of its state. The other input can dance all it wants, as long as the one first down remains down. Only when the original input is released can a new input cause a change of state. In the rare case where both signals occur at once, it is the history, the existing state, which determines the status of the machine.

| STATE WAITOFF        | STATE WAITON         |

|----------------------|----------------------|

| IN-STATE             | IN-STATE             |

| WAITOFF              | WAITON               |

| CONDITION            | CONDITION            |

| PA7 OFF? PB7 ON? AND | PB7 OFF? PA7 ON? AND |

| CAUSES               | CAUSES               |

| GRNLED ON            | GRNLED OFF           |

| THEN-STATE           | THEN-STATE           |

| WAITON               | WAITOFF              |

| TO-HAPPEN            | TO-HAPPEN            |

# DELAYS

Let's say we want to make a steady blinker out of the green LED. In a conventional procedural language, like BASIC, C, FORTH, or Java, etc., you'd probably program a loop blinking the LED on then off. Between each loop would be a delay of some kind, perhaps a subroutine you call which also spins in a loop wasting time.

| Assem | bler       | BASIC        | C JAVA                    | FORTH   |

|-------|------------|--------------|---------------------------|---------|

| LOOP1 | LDX # 0    | FOR I=1 TO N | While ( 1 )               | BEGIN   |

| LOOP2 |            | GOSUB DELAY  | { delay(x);               | DELAY   |

|       | BNE LOOP2  |              |                           |         |

|       | ldaa #1    | LET PB=TRUE  | <pre>out(1,portA1);</pre> | LED-ON  |

|       | STAA PORTA |              |                           |         |

|       | LDX # 0    |              |                           |         |

| LOOP3 | DEX        | GOSUB DELAY  | delay(x);                 | DELAY   |

|       | BNE LOOP3  |              |                           |         |

|       | LDAA #N    | Let PB=FALSE | <pre>out(0,portA1);</pre> | LED-OFF |

|       | STAA PORTA |              |                           |         |

| JMP LOOP1 | NEXT | } | AGAIN |

|-----------|------|---|-------|

|-----------|------|---|-------|

Here's where IsoMax<sup>TM</sup> will start to look different from any other language you're likely to have ever seen before. The idea behind Virtually Parallel Machine Architecture is constructing virtual machines, each a little "state machine" in its own right. But this IsoStructure requires a limitation on the machine, themselves. In IsoMax<sup>TM</sup>, there are no program loops, there are no backwards branches, there are no calls to time wasting delays allowed. Instead we design machines with states. If we want a loop, we can make a state, then write a transition from that state that returns to that state, and accomplish roughly the same thing. Also in IsoMax<sup>TM</sup>, there are no delay loops.

### The whole point of having a state is to allow "being in the state" to be "the delay".

Breaking this restriction will break the functionality of IsoStructure, and the parallel machines will stop running in parallel. If you've ever programmed in any other language, your hardest habit to break will be to get away from the idea of looping in your program, and using the states and transitions to do the equivalent of looping for you.

A valid condition to leave a state might be a count down of passes through the state until a 0 count reached. Given the periodicity of the scheduler calling the machine chain, and the initial value in the counter, this would make a delay that didn't "wait" in the conventional sense of backwards branching.

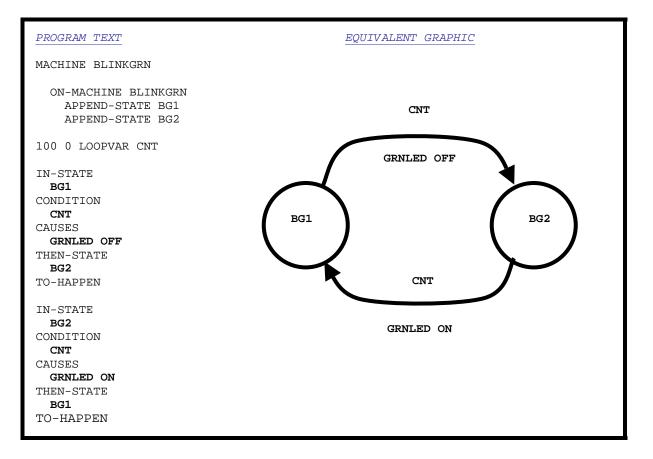

### BLINKGRN

Now for an example of a delay using the count down to zero, we make a machine BLINKGRN. Reset your ServoPod-USB<sup>TM</sup> so it is clean and clear of any programs, and then begin.

```

MACHINE BLINKGRN

ON-MACHINE BLINKGRN

APPEND-STATE BG1

APPEND-STATE BG2

```

The action taken when we leave the state will be to turn the LED off and reinitialize the counter. The other half of the problem in the other state we go to is just the reversed. We delay for a count, then turn the LED back on.

Since we're going to count, we need two variables to work with. One contains the count, the other the initial value we count down from. Let's add a place for those variables now, and initialize them

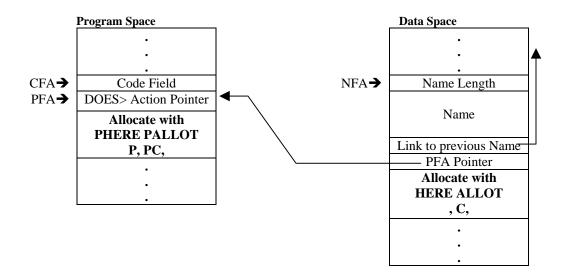

```

: -LOOPVAR <BUILDS HERE P, 1- DUP , , DOES>

P@ DUP @ 0= IF DUP 1 + @ SWAP ! TRUE ELSE 1-! FALSE THEN ;

100 -LOOPVAR CNT

```

IN-STATE BG1 CONDITION CNT CAUSES GRNLED OFF THEN-STATE BG2 TO-HAPPEN IN-STATE BG2 CONDITION CNT CAUSES GRNLED ON THEN-STATE BG1 TO-HAPPEN

Above, the two transitions are "pretty printed" to make the four components of a transition stand out. As discussed previously, as long as the structure is in this order it could just as well been run together on a single line (or so) per transition, like this

IN-STATE BG1 CONDITION CNT CAUSES GRNLED OFF THEN-STATE BG2 TO-HAPPEN

IN-STATE BG2 CONDITION CNT CAUSES GRNLED ON THEN-STATE BG1 TO-HAPPEN

Finally, the new machine must be installed and tested

**BG1 SET-STATE** ( INSTALL BLINKGRN EVERY 50000 CYCLES SCHEDULE-RUNS BLINKGRN

The result of this program is that the green LED blinks on and off. Every time the scheduler runs the machine chain, control is passed to whichever state BG1 or BG2 is active. The -LOOPVAR created word CNT is decremented and tested. When the CNT reaches zero, it is reinitialize back to the originally set value, and passes a Boolean on to be tested by the transition. If the Boolean is TRUE, the action is initiated.

The GRNLED is turned ON of OFF (as programmed in the active state) and the other state is set to happen the next control returns to this machine.

### SPEED

You've seen how to write a machine that delays based on a counter. Let's now try a slightly less useful machine just to illustrate how fast the ServoPod-USB<sup>TM</sup> can change state. First reset your machine to get rid of the existing machines.

### ZIPGRN

MACHINE ZIPGRN

```

ON-MACHINE ZIPGRN

APPEND-STATE ZIPON

APPEND-STATE ZIPOFF

```

IN-STATE ZIPON CONDITION TRUE CAUSES GRNLED OFF THEN-STATE ZIPOFF TO-HAPPEN

```

IN-STATE ZIPOFF CONDITION TRUE CAUSES GRNLED ON THEN-STATE ZIPON TO-HAPPEN

```

ZIPON SET-STATE

Now rather than install our new machine we're going to test it by running it "by hand" interactively. Type in:

ZPON SET-STATE ZIPGRN

ZIPGRN should cause a change in the green LED. The machine runs as quickly as it can to termination, through one state transition, and stops. Run it again. Type:

ZIPGRN

Once again, the green LED should change. This time the machine starts in the state with the LED off. The always TRUE condition makes the transition's action happen and the next state is set to again, back to the original state. As many times as you run it, the machine will change the green LED back and forth.

Now with the machine program and tested, we're ready to install the machine into the machine chain. The phrase to install a machine is :

EVERY n CYCLES SCHEDULE-RUNS word

So for our single machine we'd say:

ZIPON SET-STATE EVERY 5000 CYCLES SCHEDULE-RUNS ZIPGRN

Now if you look at your green LED, you'll see it is slightly dimmed.

That's because it is being turned off half the time, and is on half the time. But it is happening so fast you can't even see it.

### REDYEL

Let's do another of the same kind. This time lets do the red and yellow LED, and have them toggle, only one on at a time. Here we go:

MACHINE REDYEL

ON-MACHINE REDYEL APPEND-STATE REDON APPEND-STATE YELON

IN-STATE REDON CONDITION TRUE CAUSES REDLED OFF YELLED ON THEN-STATE YELON TO-HAPPEN

```

IN-STATE YELON CONDITION TRUE CAUSES REDLED ON YELLED OFF THEN-STATE REDON TO-HAPPEN

```

Notice we have more things happening in the action this time. One LED is turned on and one off in the action. You can have multiple instructions in an action.

Test it. Type:

```

REDON SET-STATE

REDYEL

REDYEL

REDYEL

REDYEL

```

See the red and yellow LED's trade back and forth from on to off and vice versa.

All this time, the ZIPGRN machine has been running in the background, because it is in the installed machine chain. Let's replace the installed machine chain with another. So we define a new machine chain with both our virtual machines in it, and install it.

```

MACHINE-CHAIN CHN2

ZIPGRN

REDYEL

END-MACHINE-CHAIN

REDON SET-STATE

EVERY 5000 CYCLES SCHEDULE-RUNS CHN2

```

With the new machine chain installed, all three LED's look slightly dimmed.

Again, they are being turned on and off a thousand times a second. But to your eye, you can't see the individual transitions. Both our virtual machines are running in virtual parallel, and we still don't see any slow down in the interactive nature of the ServoPod-USB<sup>TM</sup>.

So what was the point of making these two machines? Well, these two machines are running faster than the previous ones. The previous ones were installed with 50,000 cycles between runs. That gave a scan-loop repetition of 100 times a second. Fine for many mechanical issues, on the edge of being slow for electronic interfaces. These last examples were installed with 5,000 cycles between runs. The scan-loop repetition was 1000 times a second. Fine for many electronic interfaces, that is fast enough. Now let's change the timing value. Redo the installation with the SCHEDULE-RUNS command.

The scan-loop repetition is 10,000 times a second.

EVERY 500 CYCLES SCHEDULE-RUNS CHN2

Let's see if we can press our luck.

EVERY 100 CYCLES SCHEDULE-RUNS CHN2

Even running two machines 50,000 times a second in high-level language, there is still time left over to run the foreground routine. This means, two separate tasks are being started and running a series of high-level instructions 50,000 times a second. This shows the ServoPod-USB<sup>TM</sup> is running more than four hundred thousand high-level instructions per second. The ServoPod-USB<sup>TM</sup> performance is unparalleled in any small computer available today.

# TRINARIES

With the state machine structures already given, and a simple input and output words many useful machines can be built. Almost all binary digital control applications can be written with the trinary operators.

As an example, let's consider a digital thermostat. The thermostat works on a digital input with a temperature sensor that indicates the current temperature is either above or below the current set point. The old style thermostats had a coil made of two dissimilar metals, so as the temperature rose, the outside metal expanded more rapidly than the interior one, causing a mercury capsule to tip over. The mercury moving to one end of the capsule or the other made or broke the circuit. The additional weight of mercury caused a slight feedback widening the set point. Most heater systems are digital in nature as well.

They are either on or off. They have no proportional range of heating settings, only heating and not heating. So in the case of a thermostat, everything necessary can be programmed with the machine format already known, and a digital input for temperature and a digital output for the heater, which can be programmed with trinaries.

Input trinary operators need three parameters to operate. Using the trinary operation mode of testing bits and masking unwanted bits out would be convenient. This mode requires: 1) a mask telling which bits in to be checked for high or low settings, 2) a mask telling which of the 1 possible bits are to be considered, and 3) the address of the I/O port you are using. The keywords which separate the parameters are, in order: 1) SET-MASK, 2) CLR-MASK and 3) AT-ADDRESS. Finally, the keyword FOR-INPUT finishes the defining process, identifying the trinary operator in effect.

```

DEFINE <name> TEST-MASK <mask> DATA-MASK <mask> AT-ADDRESS <address> FOR-INPUT

```

Putting the keywords and parameters together produces the following lines of IsoMax<sup>TM</sup> code. Before entering hexadecimal numbers, the keyword HEX invokes the use of the hexadecimal number system. This remains in effect until it is change by a later command. The numbering system can be returned to decimal using the keyword DECIMAL:

HEX DEFINE TOO-COLD? TEST-MASK 01 DATA-MASK 01 AT-ADDRESS 0FB1 FOR-INPUT DEFINE TOO-HOT? TEST-MASK 01 DATA-MASK 00 AT-ADDRESS 0FB1 FOR-INPUT DECIMAL

Output trinary operators also need three parameters. In this instance, using the trinary operation mode of setting and clearing bits would be convenient. This mode requires: 1) a mask telling which bits in the output port are to be set, 2) a mask telling which bits in the output port are to be cleared, and 3) the address of the I/O port. The keywords which proceed the parameters are, in order: 1) SET-MASK, 2) CLR-MASK and 3) AT-ADDRESS. Finally, the keyword FOR-OUTPUT finishes the defining process, identifying which trinary operator is in effect.

DEFINE <name> AND-MASK <mask> XOR-MASK <mask> AT-ADDRESS <address> FOR-OUTPUT DEFINE <name> CLR-MASK <mask> SET-MASK <mask> AT-ADDRESS <address> FOR-OUTPUT

A single output port line is needed to turn the heater on and off. The act of turning the heater on is unique and different from turning the heater off, however. Two actions need to be defined, therefore, even though only one I/O line is involved. PA1 was selected for the heater control signal.

When PA1 is high, or set, the heater is turned on. To make PA1 high, requires PA1 to be set, without changing any other bit of the port. Therefore, a set mask of 02 indicates the next to least significant bit in the port, corresponding to PA1, is to be set. All other bits are to be left alone without being set. A clear mask of 00 indicates no other bits of the port are to be cleared.

When PA1 is low, or clear, the heater is turned off. To make PA1 low, requires PA1 to be cleared, without changing any other bit of the port. Therefore, a set mask of 00 indicates no other bits of the port are to be set. A clear mask of 02 indicates the next to least significant bit in the port, corresponding to PA1, is to be cleared. All other bits are to be left alone without being cleared.

Putting the keywords and parameters together produces the following lines of IsoMax<sup>TM</sup> code:

```

HEX

DEFINE HEATER-ON SET-MASK 02 CLR-MASK 00 AT-ADDRESS 0FB0 FOR-OUTPUT

DEFINE HEATER-OFF SET-MASK 00 CLR-MASK 02 AT-ADDRESS 0FB0 FOR-OUTPUT

DECIMAL

```

Only a handful of system words need to be covered to allow programming at a system level, now.

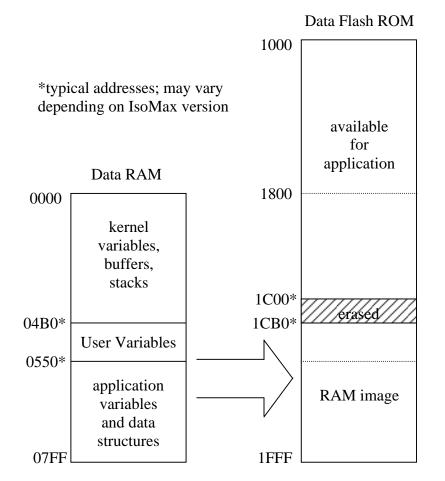

# FLASH AND AUTOSTARTING

Here's everything you need to copy an application to Flash and to autostart it. Here, briefly, are the steps:

1. You should start with a clean Servopod, by doing SCRUB. This will erase the Program Flash and remove any previous autostart patterns.

2. In the program file, each Forth word should be followed by EEWORD. This applies to colon definitions, CODE and CODE-SUB words, constants, variables, "defined" words (those created with <BUILDS..DOES>), and objects (those created with OBJECT).

3. If IMMEDIATE is used, it must come \*before\* EEWORD (i.e., you must do IMMEDIATE EEWORD and \*not\* EEWORD IMMEDIATE).

4. For IsoMax code the following rules apply:

a. MACHINE <name> must be followed by EEWORD.

b. APPEND-STATE <name> must be followed by EEWORD.

c. IN-STATE ... TO-HAPPEN (or THIS-TIME or NEXT-TIME) must be followed by IN-EE.

d. MACHINE-CHAIN ... END-MACHINE-CHAIN must be followed by EEWORD. e. ON-MACHINE <name> is \*not\* followed by any EE command.

[Note that we can make EEWORD and IN-EE automatic, if you want all state machines to be built in Flash and never in RAM.]

5. When the application is complete, you must use SAVE-RAM to preserve the state machine variables in Data Flash. (This does \*not\* save kernel variables.)

### 6. Finally you can set the autostart vector in Program Flash. AUTOSTART <wordname> E.g., AUTOSTART MAIN

<address> AUTOSTART <wordname> (from V0.3 to V0.62 ) E.g., HEX 3C00 AUTOSTART MAIN

The board should now reset into the application program.

# **ISOMAX GLOSSARY**

Stack comments use the following notation:

- n a signed 16-bit value, -32768..+32767.

- u an unsigned 16-bit value, 0..65535.

- +n a signed, positive 16-bit value, 0..+32767.

- w a generic16-bit value.

- 16b a generic 16-bit value.

- addr an address (16 bits).

c a character. (Note: stored as 16 bits on the ServoPod-USB<sup>TMTM</sup>)

- 8b a generic 8-bit value. (Note: stored as 16 bits on the ServoPod-USB<sup>TMTM</sup>)

- d a signed 32-bit value, -2,147,483,648..+2,147,483,647.

- ud an unsigned 32-bit value, 0..4,294,967,295.

- wd a generic 32-bit value.

- 32b a generic 32-bit value.

r a floating-point (real) value.

flag a logical flag, zero = false, -1 (all ones) = true.

Values on the stack before and after execution of a word are given as follows:

| (before after)     | normal integer data stack                        |

|--------------------|--------------------------------------------------|

| (F: before after ) | floating-point data stack                        |

| (C: before after ) | compile-time behavior of the integer data stack. |

Stack comments in italics also refer to compile-time behavior.

# Integer Arithmetic

| Word  | Stack Effect       | Description                                         |

|-------|--------------------|-----------------------------------------------------|

| *     | ( w1 w2 w3 )       | Multiplies w2 by w1 and leaves the product w3 on    |

|       |                    | the stack.                                          |

| */    | ( n1 n2 n3 n4 )    | Multiplies n2 by n1 and divides the product by n3.  |

|       |                    | The quotient, n4 is placed on the stack.            |

| */MOD | ( n1 n2 n3 n4 n5 ) | n1 is multiplied by n2 producing a product which is |

|       |                    | divided by n3. The remainder, n4 and the quotient,  |

|       |                    | n5 are then placed on the stack.                    |

| +     | (w1 w2 w3 )        | Adds w2 and w1 then leaves the sum, w3 on the       |

|       |                    | stack.                                              |

| +!    | ( w1 addr )        | Adds w1 to the value at addr then stores the sum at |

|       |                    | addr replacing its previous value.                  |

| -     | ( w1 w2 w3 )       | Subtracts w2 from w1 and leaves the result, w3 on   |

|       |                    |                                                     |

|          |                        | the stack.                                                                                                                             |

|----------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| /        | ( n1 n2 n3 )           | Divides n1 by n2 and leaves the quotient n3 on the stack.                                                                              |

| /MOD     | ( n1 n2 n3 n4 )        | Divides n1 by n2 then leaves on the stack the remainder n3 and the quotient n4.                                                        |

| 1+       | (w1 w2)                | Adds 1 to w1 then leaves the sum, w2 on the stack.                                                                                     |

| 1+!      | ( addr )               | Adds one to the value at addr and stores the result at addr.                                                                           |

| 1-       | ( w1 w2 )              | Subtract 1 from w1 then leaves the difference, w2 on the stack.                                                                        |

| 1-!      | ( addr )               | Subtracts one from the value at addr and stores the result at addr.                                                                    |

| 2*       | (w1w2)                 | Multiplies w1 by 2 to give w2.                                                                                                         |

| 2+       | (w1 w2)                | Adds two to w1 and leaves the sum, w2 on the stack.                                                                                    |

| 2-       | ( w1 w2 )              | Subtracts two from w1 and leaves the result, w2 on the stack.                                                                          |

| 2/       | (n1 n2)                | Divides n1 by 2, giving n2 as the result.                                                                                              |

| $\times$ | ( 8b1/8b2<br>8b2/8b1 ) | Swaps the upper and lower bytes of the value on the stack.                                                                             |

| ABS      | ( n u )                | Leaves on the stack the absolute value, u of n.                                                                                        |

| MAX      | ( n1 n2 n3 )           | Leaves the greater of n1 and n2 as n3.                                                                                                 |

| MIN      | ( n1 n2 n3 )           | Leaves the lesser of n1 and n2 as n3.                                                                                                  |

| MOD      | ( n1 n2 n3 )           | Divides n1 by n2 and leaves the remainder n3.                                                                                          |

| NEGATE   | (n1 n2)                | Leaves the two's complement n2 of n1.                                                                                                  |

| UM*      | ( u1 u2ud )            | Multiplies u1 and u2 returning the double length product ud.                                                                           |

| UM/MOD   | ( ud u1 u2 u3 )        | Divides the double length unsigned number ud by u1<br>and returns the single length remainder u2 and the<br>single length quotient u3. |

# Logical and Comparison

| Word       | Stack Effect    | Description                                        |

|------------|-----------------|----------------------------------------------------|

| 0<         | ( n flag )      | Leaves a true flag if n is less than zero.         |

| 0=         | ( w flag )      | Leaves a true flag if w is equal to zero.          |

| 0>         | ( n flag )      | Leaves a true flag if n is greater than zero.      |

| <          | ( n1 n2 flag )  | Leaves a true flag on stack if n1 is less than n2. |

| =          | ( w1 w2 flag )  | Returns a true flag if w1 is equal to w2.          |

| >          | ( n1 n2 flag )  | Returns a true flag if n1 is greater than n2.      |

| AND        | (16b1 16b2      | Leaves the bitwise logical AND of 16b1 and         |

|            | 16b3)           | 16b2 as 16b3.                                      |

| CLEAR-BITS |                 | Clears bits at addr corresponding to 1s in mask b. |

| INVERT     | (16b1 16b2)     | Leaves the one's complement 16b2 of 16b1.          |

| NOT        | ( flag1 flag2 ) | Leaves the logical inverse flag2 of flag1. flag2   |

|            |                 | is false if flag1 was true, and vice versa.        |

| OR         | ( 16b1 16b2     | Leaves the inclusive-or 16b3 of 16b1 an 16b2.      |

|             | 16b3)         |                                                  |

|-------------|---------------|--------------------------------------------------|

| SET-BITS    | ( b addr )    | Sets bits at addr corresponding to 1s in mask b. |

| TOGGLE-BITS | ( b addr )    | Toggles bits at addr corresponding to 1s in mask |

|             |               | b.                                               |

| U<          | ( u1 u2flag ) | Returns a true flag if u1 is less then u2.       |

| XOR         | (16b1 16b2    | Performs a bit-by-bit exclusive or of 16b1 with  |

|             | 16b3)         | 16b2 to give 16b3.                               |

# **Double-Precision Operations**

| Word             | Stack Effect                            | Description                                                              |

|------------------|-----------------------------------------|--------------------------------------------------------------------------|

| 2CONSTANT        | ( 32b )                                 | Creates a double length constant for a <name>. When</name>               |

| <name></name>    | (20h)                                   | <name> is executed, 32b is left on the stack.</name>                     |

| 2DROP            | (32b )                                  | Removes 32b from the stack.                                              |

| 2DUP             | ( 32b 32b<br>32b )                      | Duplicates 32b.                                                          |

| 20VER            | ( 32b1 32b2<br>32b1 32b2 32b3<br>)      | 32b3 is a copy of 32b1                                                   |

| 2ROT             | ( 32b1 32b2<br>32b3 32b2<br>32b3 32b1 ) | Rotates 32b1 to the top of the stack.                                    |

| 2SWAP            | ( 32b1 32b2<br>32b2 32b1 )              | Swaps 32b1 and 32b2 on the stack.                                        |

| <b>2VARIABLE</b> | ()                                      | Creates double-length variable for <name>. when <name></name></name>     |

| <name></name>    |                                         | is executed, its parameter field address is placed on the stack.         |

| D*               | ( d1 d2 d3 )                            | Multiplies d1 by d2 and leaves the product d3 on the stack.              |

| D+               | ( wd1 wd2<br>wd3 )                      | Adds wd1 and wd2 and leaves the result, wd3 on stack.                    |

| D-               | ( wd1 wd2 wd3                           | Subtracts wd2 from wd1 and returns the dif- ference wd3.                 |

| D/               | ( d1 d2 d3 )                            | Divides d1 by d2 and leaves the quotient d3 on the stack.                |

| D0=              | ( wd flag )                             | Returns a true flag if wd is equal to zero.                              |

| D2/              | ( d1 d2 )                               | Divides d1 by 2 and gives quotient d2.                                   |

| D<               | ( d1 d2 flag )                          | Leaves a true flag if d1 is less than d2; otherwise leaves a false flag. |

| D=               | ( wd1 wd2<br>flag )                     | Returns a true flag if wd1 is equal to wd2.                              |

| DABS             | (d ud)                                  | Returns the absolute value of d as ud.                                   |

| DCONSTANT        | (32b )                                  | Creates a double length constant for a <name>. When</name>               |

| <name></name>    |                                         | <name> is executed, 32b is left on the stack. Same as 2CONSTANT.</name>  |

| DDROP            | ( 32b )                                 | Removes 32b from the stack. Same as 2DROP.                               |

| DDUP             | ( 32b 32b<br>32b )                      | Duplicates 32b. Same as 2DUP.                                            |

| DMAX<br>DMIN<br>DMOD<br>DNEGATE<br>DOVER | ( d1 d2 d3 )<br>( d1 d2 d3 )<br>( d1 d2 d3 )<br>( d1 d2 )<br>( 32b1 32b2<br>32b1 32b2 32b3 | Returns d3 as the greater of d1 or d2.<br>Returns d3 as the lesser of d1 or d2.<br>Divides d1 by d2 and leaves the remainder d3.<br>Leaves the two's complement d2 of d1.<br>32b3 is a copy of 32b1. Same as 20VER. |

|------------------------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DROT                                     | )<br>( 32b1 32b2<br>32b3 32b2<br>22b2 22b1 )                                               | Rotates 32b1 to the top of the stack. Same as 2ROT.                                                                                                                                                                 |

| DSWAP                                    | 32b3 32b1 )<br>( 32b1 32b2<br>32b2 32b1 )                                                  | Swaps 32b1 and 32b2 on the stack. Same as 2SWAP.                                                                                                                                                                    |

| DU<                                      | ( ud1 ud2<br>flag )                                                                        | Returns a true flag if ud1 is less than ud2.                                                                                                                                                                        |

| DVARIABLE <name></name>                  | ()                                                                                         | Creates double-length variable for <name>. when <name> is executed, its parameter field address is placed on the stack. Same as 2VARIABLE.</name></name>                                                            |

| S->D                                     | ( n d )                                                                                    | Sign extend single number to double number.                                                                                                                                                                         |

# Floating-point Operations

| Word<br>2**X | <b>Stack Effect</b><br>(F: r1 r2) | <b>Description</b><br>Raise 2 to the r1 power giving r2.                      |

|--------------|-----------------------------------|-------------------------------------------------------------------------------|

| D>F          | (d ) (F - r)                      | R is the floating-point equivalent of d.                                      |

| e            | (F: r1)                           | Put natural value e (= $2.718282$ ) on the floating-<br>point stack as r1.    |

| F!           | (addr ) (F:r )                    | Store r at addr.                                                              |

| F*           | (F:r1 r2 r3)                      | Multiply r1 by r2 giving r3.                                                  |

| F**          | (F:r1 r2 r3)                      | Raise r1 to the r2 power giving r3.                                           |

| F+           | (F:r1 r2 r3)                      | Add r1 to r2, giving r3.                                                      |

| F,           | (F:r )                            | Store r as a floating-point number in the next available dictionary location. |

| F-           | (F:r1 r2 r3)                      | Subtract r2 from r1, giving r3.                                               |

| F/           | (F:r1 r2 r3)                      | Divide r1 by r2, giving r3.                                                   |

| F0<          | (F:r ) ( flag)                    | flag is true if r is less than zero.                                          |

| F0=          | (F:r ) ( flag)                    | flag is true if r is equal to zero.                                           |

| F2*          | (F:r1 r2)                         | Multiply r1 by 2 giving r2.                                                   |

| F2/          | (F:r1 r2)                         | Divide r1 by 2 giving r2.                                                     |

| F<           | (F:r1 r2 )(<br>flag)              | flag is true if r1 is less than r2.                                           |

| F>D          | (F:r )( d)                        | Convert r to d.                                                               |

| F@           | (addr )(F: r)                     | r is the value stored at addr.                                                |

| FABS         | (F:r1 r2)                         | R2 is the absolute value of r1.                                               |

| FALOG        | (F:r1 r2)                         | Raise 10 to the power r1, giving r2.                                          |

| FATAN        | (F:r1 r2)                         | R2 is the principal radian whose tangent is r1.                               |

| FATAN2<br>FCONSTANT | (F:r1 r2 r3 )<br>(F:r )                                                    | R3 is the radian angle whose tangent is $r1/r2$ .<br>Define a constant <name> with value r.</name> |

|---------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| <name></name>       |                                                                            |                                                                                                    |

| FCOS                | (F:r1 r2)                                                                  | r2 is the cosine of the radian angle r1.                                                           |

| FDEPTH              | ( +n)                                                                      | +n is the number of values contained on separate                                                   |

|                     |                                                                            | floating point stack.                                                                              |

| FDROP               | (F:r )                                                                     | Remove r from the floating-point stack.                                                            |

| FDUP                | (F:r r r)                                                                  | Duplicate r.                                                                                       |

| FEXP                | (F:r1 r2)                                                                  | Raise e to the power r1, giving r2.                                                                |

| FLN                 | (F:r1 r2)                                                                  | R2 is the natural logarithm of r1.                                                                 |

| FLOAT+              | (addr1 addr2)                                                              | Add the size of a floating-point value to addr1.                                                   |

| FLOATS              | (n1 n2)                                                                    | n2 is the size, in bytes, of n1 floating-point numbers.                                            |

| FLOG                | (F:r1 r2)                                                                  | R2 is the base 10 logarithm of r1.                                                                 |

| FLOOR               | (F:r1 r2)                                                                  | Round r1 using the "round to negative infinity"                                                    |

|                     | (= ··· =)                                                                  | rule, giving r2.                                                                                   |

| FMAX                | (F:r1 r2 r3)                                                               | r3 is the maximum of r1 and r2.                                                                    |

| FMIN                | (F:r1 r2 r3)                                                               | r3 is the minimum of r2 and r3.                                                                    |

| FNEGATE             | (F:r1 r2)                                                                  | r2 is the negation of r1.                                                                          |

| FNIP                | (F:r1 r2 r2)                                                               | Remove second number down from floating-point                                                      |

| EQUED               | $(\mathbf{E}, \mathbf{r}, 1, \mathbf{r}, 2, \mathbf{r}, 1, \mathbf{r}, 2)$ | stack.                                                                                             |

| FOVER               | (F:r1 r2 r1 r2                                                             | Place a copy of r1 on top of the floating-point stack.                                             |

| EDOUND              | $(\mathbf{F}_{r1}, \mathbf{r}_{2})$                                        |                                                                                                    |

| FROUND              | (F:r1 r2)                                                                  | Round r1 using the ";round to even"; rule, giving r2.                                              |

| FSIN                | (F:r1 r2)                                                                  | R2 is the sine of the radian angle r1.                                                             |

| FSQRT               | (F:r1 r2)                                                                  | R2 is the square root of r1.                                                                       |

| FSWAP               | (F:r1 r2 r2 r1)                                                            | Exchange the top two floating-point stack items.                                                   |

| FTAN                | (F:r1 r2)                                                                  | R2 is the tangent of the radian angle r1.                                                          |

| FVARIABLE           | ()                                                                         | Create a floating-point variable <name>. Reserve</name>                                            |

| <name></name>       |                                                                            | data memory in the dictionary sufficient to hold a                                                 |

|                     |                                                                            | floating-point value.                                                                              |

| LOG2                | (F:r1 r2)                                                                  | R2 is the base 2 logarithm of r1.                                                                  |

| ODD-POLY            | (F: r1)(addr )                                                             | Evaluate odd-polynomial giving r1.                                                                 |

| PI                  | (F: r1)                                                                    | Put the numerical value of pi on the floating- point                                               |

|                     |                                                                            | stack as r1.                                                                                       |

| POLY                | (F: r1)(addr )                                                             | Evaluate polynomial giving r1.                                                                     |

| S>F                 | (n)(F: r)                                                                  | R is the floating-point equivalent of n.                                                           |

| SF!                 | (addr )(F:r )                                                              | Store the floating point number r as a 32 bit IEEE                                                 |

|                     |                                                                            | single precision number at addr.                                                                   |

| SF@                 | ( addr )(F: r)                                                             | Fetch the 32-bit IEEE single precision number                                                      |

|                     |                                                                            | stored at addr to the floating-point stack as r in the                                             |

|                     |                                                                            | internal representation.                                                                           |

|                     |                                                                            |                                                                                                    |

## Stack Operations

| Word  | Stack Effect                          | Description                                                                         |

|-------|---------------------------------------|-------------------------------------------------------------------------------------|

| -ROLL | ( n )                                 | Removes the value on the top of stack and inserts it                                |

|       | · · ·                                 | into the nth place from the top of stack.                                           |

| >R    | (16b )                                | Removes 16b from user stack and place it onto return stack.                         |

| ?DUP  | (16b 16b 16b ),<br>(0 0)              | Duplicates 16b if it is a non-zero.                                                 |

| DEPTH | (+n)                                  | Returns count +n of numbers on the data stack.                                      |

| DROP  | (16b )                                | Removes 16b from the data stack.                                                    |

| DUP   | (16b 16b 16b )                        | Duplicates 16b.                                                                     |

| OVER  | (16b1 16b2<br>16b1 16b2 16b3 )        | 16b3 is a copy of 16b1.                                                             |

| PICK  | ( +n 16b )                            | Copies the data stack's +nth item onto the top.                                     |

| R>    | ( 16b)                                | 16b is removed from the return stack and placed onto the data stack.                |

| R@    | ( 16b)                                | 16b is a copy of the top of the return stack.                                       |

| ROLL  | (+n )                                 | Removes the stack's nth item and places it onto the top of stack.                   |

| ROT   | (16b1 16b2 16b3<br>- 16b2 16b3 16b1 ) | Rotates 16b1 to the top of the stack.                                               |