# PrPMC8005E Processor PMC Module

**Installation and Use**

6806800A42B

September 2008 Edition

© Copyright 2008 Emerson

All rights reserved.

#### **Trademarks**

Emerson, Business-Critical Continuity, Emerson Network Power and the Emerson Network Power logo are trademarks and service marks of Emerson Electric Co. © 2008 Emerson Electric Co.

All other trademarks are the property of their respective owners.

PICMG<sup>®</sup>, CompactPCI<sup>®</sup>, AdvancedTCA<sup>™</sup> and the PICMG, CompactPCI and AdvancedTCA logos are registered trademarks of the PCI Industrial Computer Manufacturers Group.

#### **Notice**

While reasonable efforts have been made to assure the accuracy of this document, Emerson assumes no liability resulting from any omissions in this document, or from the use of the information obtained therein. Emerson reserves the right to revise this document and to make changes from time to time in the content hereof without obligation of Emerson to notify any person of such revision or changes.

Electronic versions of this material may be read online, downloaded for personal use, or referenced in another document as a URL to a Emerson website. The text itself may not be published commercially in print or electronic form, edited, translated, or otherwise altered without the permission of Emerson,

It is possible that this publication may contain reference to or information about Emerson products (machines and programs), programming, or services that are not available in your country. Such references or information must not be construed to mean that Emerson intends to announce such Emerson products, programming, or services in your country.

#### Limited and Restricted Rights Legend

If the documentation contained herein is supplied, directly or indirectly, to the U.S. Government, the following notice shall apply unless otherwise agreed to in writing by Emerson.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (b)(3) of the Rights in Technical Data clause at DFARS 252.227-7013 (Nov. 1995) and of the Rights in Noncommercial Computer Software and Documentation clause at DFARS 252.227-7014 (Jun. 1995).

#### **Contact Address**

Emerson Network Power - Embedded Computing 2900 South Diablo Way, Suite 190 Tempe, AZ 85282 USA

#### **Safety Summary**

The following general safety precautions must be observed during all phases of operation, service, and repair of this equipment. Failure to comply with these precautions or with specific warnings elsewhere in this manual could result in personal injury or damage to the equipment.

The safety precautions listed below represent warnings of certain dangers of which Emerson is aware. You, as the user of the product, should follow these warnings and all other safety precautions necessary for the safe operation of the equipment in your operating environment.

#### Ground the Instrument.

To minimize shock hazard, the equipment chassis and enclosure must be connected to an electrical ground. If the equipment is supplied with a three-conductor AC power cable, the power cable must be plugged into an approved three-contact electrical outlet, with the grounding wire (green/yellow) reliably connected to an electrical ground (safety ground) at the power outlet. The power jack and mating plug of the power cable meet International Electrotechnical Commission (IEC) safety standards and local electrical regulatory codes.

#### Do Not Operate in an Explosive Atmosphere.

Do not operate the equipment in any explosive atmosphere such as in the presence of flammable gases or fumes. Operation of any electrical equipment in such an environment could result in an explosion and cause injury or damage.

#### Keep Away From Live Circuits Inside the Equipment.

Operating personnel must not remove equipment covers. Only Factory Authorized Service Personnel or other qualified service personnel may remove equipment covers for internal subassembly or component replacement or any internal adjustment. Service personnel should not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, such personnel should always disconnect power and discharge circuits before touching components.

#### Use Caution When Exposing or Handling a CRT.

Breakage of a Cathode-Ray Tube (CRT) causes a high-velocity scattering of glass fragments (implosion). To prevent CRT implosion, do not handle the CRT and avoid rough handling or jarring of the equipment. Handling of a CRT should be done only by qualified service personnel using approved safety mask and gloves.

#### Do Not Substitute Parts or Modify Equipment.

Do not install substitute parts or perform any unauthorized modification of the equipment. Contact your local Emerson representative for service and repair to ensure that all safety features are maintained.

#### **Observe Warnings in Manual.**

Warnings, such as the example below, precede potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed. You should also employ all other safety precautions which you deem necessary for the operation of the equipment in your operating environment.

To prevent serious injury or death from dangerous voltages, use extreme caution when handling, testing, and adjusting this equipment and its components.

#### **Flammability**

All Emerson PWBs (printed wiring boards) are manufactured with a flammability rating of 94V-0 by UL-recognized manufacturers.

#### **EMI Caution**

This equipment generates, uses and can radiate electromagnetic energy. It may cause or be susceptible to electromagnetic interference (EMI) if not installed and used with adequate EMI protection.

## **Lithium Battery Caution**

This product contains a lithium battery to power the clock and calendar circuitry. Only qualified personnel should replace lithium batteries.

Danger of explosion if battery is replaced incorrectly. Replace battery only with the same or equivalent type recommended by the equipment manufacturer. Dispose of used batteries according to the manufacturer's instructions.

Il y a danger d'explosion s'il y a remplacement incorrect de la batterie. Remplacer uniquement avec une batterie du même type ou d'un type équivalent recommandé par le constructeur. Mettre au rebut les batteries usagées conformément aux instructions du fabricant.

Explosionsgefahr bei unsachgemäßem Austausch der Batterie. Ersatz nur durch denselben oder einen vom Hersteller empfohlenen Typ. Entsorgung gebrauchter Batterien nach Angaben des Herstellers.

## **CE Notice (European Community)**

This is a Class A product. In a domestic environment, this product may cause radio interference, in which case the user may be required to take adequate measures.

Emerson products with the CE marking comply with the EMC Directive (89/336/EEC). Compliance with this directive implies conformity to the following European Norms:

EN55022 "Limits and Methods of Measurement of Radio Interference Characteristics of Information Technology Equipment"; this product tested to Equipment Class A

EN 300 386 V.1.2.1 "Electromagnetic compatibility and radio spectrum matters (ERM); Telecommunication network equipment; Electromagnetic compatibility (EMC) requirements"

Board products are tested in a representative system to show compliance with the above mentioned requirements. A proper installation in a CE-marked system will maintain the required EMC/safety performance.

In accordance with European Community directives, a "Declaration of Conformity" has been made and is on file within the European Union. The "Declaration of Conformity" is available on request. Please contact your sales representative.

The product has been designed to meet the directive on the restriction of the use of certain hazardous substances in electrical and electronic equipment (RoHS) Directive 2002/95/EC.

# **Contents**

| ۸۲ | oout This Manual                                           | VV.   |

|----|------------------------------------------------------------|-------|

| AL |                                                            |       |

|    | Overview of Contents                                       |       |

|    | Summary of Changes                                         |       |

|    | Comments and Suggestions                                   |       |

|    | Conventions Used in This Manual                            | .xvii |

| 1  | Preparation and Installation                               | 1     |

|    | Introduction                                               | 1     |

|    | PrPMC800 Description                                       | 1     |

|    | Monarch and Non-Monarch PrPMCs                             | 2     |

|    | Carrier Board Requirements                                 | 2     |

|    | System Enclosure                                           | 2     |

|    | Overview of Start-Up Procedures                            | 3     |

|    | Unpacking the Hardware                                     |       |

|    | Preparing the Hardware                                     |       |

|    | PrPMC800 Configuration                                     |       |

|    | Harrier Power-Up Configuration Header                      |       |

|    | Installation                                               |       |

|    | ESD Precautions                                            | 6     |

|    | Installation of PrPMC800 on a VME or CompactPCI Board      |       |

| 2  | Operating Instructions                                     | 9     |

| _  |                                                            |       |

|    | Introduction                                               |       |

|    | Applying Power                                             |       |

|    | Status LEDs and Port Connections                           |       |

|    | Status Indicators                                          |       |

|    | Debug Serial Port                                          | . 11  |

|    | Ethernet Port Adapter Cable                                | . 11  |

| 3  | Functional Description                                     | . 13  |

|    | Introduction                                               | 13    |

|    | Features                                                   |       |

|    | General Description                                        |       |

|    | Block Diagram                                              |       |

|    | ·                                                          |       |

|    | Processor                                                  |       |

|    | Harrier System Memory Controller / PCI Host Bridge ASIC    |       |

|    | Hamer Ovaletti Methory Controller / F.O. Float DHUUE MOICH | . 10  |

| Harrier Power-Up Configuration        | 17 |

|---------------------------------------|----|

| Arbitration                           | 19 |

| Flash Memory                          | 19 |

| Onboard Bank A Flash                  | 20 |

| Optional Bank B Flash                 | 20 |

| ECC Memory                            | 20 |

| Onboard SDRAM                         | 20 |

| SROM                                  | 20 |

| 10BaseT/100BaseTX Ethernet Channel    | 21 |

| Miscellaneous Control and Status      | 21 |

| Timers                                | 21 |

| 32-Bit Timers                         | 21 |

| Watchdog Timers                       | 22 |

| Interrupt Routing and Generation      |    |

| Asynchronous Serial Port              |    |

| Clock Generator                       |    |

| PrPMC800 Power Supplies               |    |

| Module Reset Logic                    |    |

| PCI Interface                         |    |

| PRESENT# Signal                       |    |

| MONARCH# Signal                       |    |

| INTA#-INTD# Signals                   |    |

| IDSELB, REQB#, and GNTB# Signals      |    |

| M66EN Signal                          |    |

| RESETOUT_L Signal                     |    |

| EREADY Signal                         |    |

| PCI Signaling Voltage Level           |    |

| Debug Header                          |    |

| ABORT# and RESET# Signals             |    |

| Harrier Power-Up Configuration Header |    |

| On-Board LEDs                         |    |

| Memory Maps                           |    |

| · · · · · · · · · · · · · · · · · · · |    |

| onnector Pin Assignments              | 29 |

| -                                     |    |

| troduction                            |    |

| CI Mezzanine Card (PMC) Connectors    |    |

| Signal Description for P14            |    |

| hernet Adapter Connector              |    |

| ebug Header                           |    |

| Signal Description for J1             |    |

| arrier Power-Up Configuration Header  |    |

| ebug Serial Port Cable                | 38 |

| 2CP us                                | 20 |

| PCBug                                 | 39 |

| verview                               | 39 |

5

|   | PPCBug Basics                                        |      |

|---|------------------------------------------------------|------|

|   | PPCBug Implementation                                | . 40 |

|   | MPU, Hardware, and Firmware Initialization           | . 40 |

|   | Using PPCBug                                         | . 42 |

|   | Debugger Commands                                    | . 42 |

|   | Diagnostic Tests                                     | . 45 |

|   |                                                      |      |

| 6 | Modifying the Environment                            | . 49 |

|   | Overview                                             | . 49 |

|   | CNFG – Configure Board Information Block             | . 49 |

|   | ENV – Set Environment                                | . 50 |

|   | Configuring the PPCBug Parameters                    | . 50 |

|   |                                                      |      |

| A | Specifications                                       | . 57 |

|   | Specifications                                       | . 57 |

|   | Mechanical Characteristics                           | . 57 |

|   | Electrical Characteristics                           | . 57 |

|   | Environmental Characteristics                        | . 58 |

|   | EMC Compliance                                       | . 58 |

| _ |                                                      |      |

| В | Thermal Validation                                   | . 59 |

|   | Overview                                             | . 59 |

|   | Thermally Significant Components                     | . 59 |

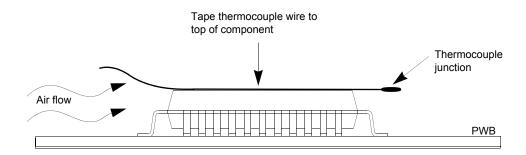

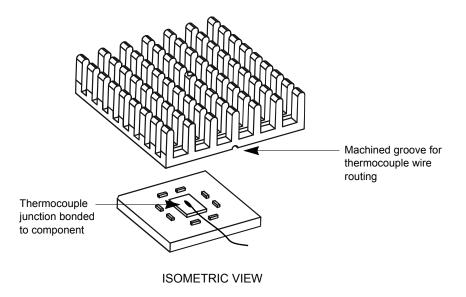

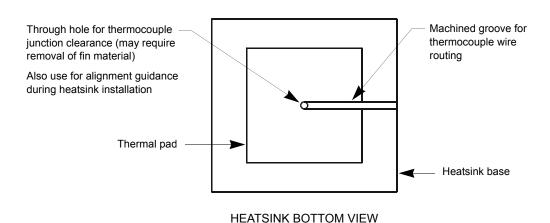

|   | Component Temperature Measurement                    |      |

|   | Preparation                                          |      |

|   | Measuring Junction Temperature                       |      |

|   | Measuring Case Temperature                           |      |

|   | Measuring Local Air Temperature                      | . 63 |

| С | Related Documentation                                | . 65 |

| - |                                                      |      |

|   | Emerson Network Power - Embedded Computing Documents |      |

|   | Manufacturers' Documents                             |      |

|   | Kelaleo Soeciicalions                                | n/   |

# List of Tables

| Table 1-1. PrPMC8005E Models/Configurations                          | . <b>x</b> v |

|----------------------------------------------------------------------|--------------|

| Table 1-1. Start-Up Overview                                         | 3            |

| Table 1-2. J2 Harrier Power-Up Configuration Header Pin Assignments  | 4            |

| Table 3-3. PrPMC800 Features                                         | . 13         |

| Table 3-4. Harrier Power-Up Configuration Settings                   | . 17         |

| Table 3-5. PPC to PCI Clock Ratios                                   | . 22         |

| Table 3-6. Reset Source Functions                                    | . 23         |

| Table 4-7. PMC Connector P11 Pin Assignments                         | . 29         |

| Table 4-8. PMC Connector P12 Pin Assignments                         | . 30         |

| Table 4-9. PMC Connector P13 Pin Assignments                         | . 31         |

| Table 4-10. PMC Connector P14 Pin Assignments                        | . 32         |

| Table 4-11. J3 Ethernet Adapter Connector Pin Assignments            | . 35         |

| Table 4-12. J1 Debug Header Pin Assignments                          | . 36         |

| Table 4-13. J2 Harrier Power-Up Configuration Header Pin Assignments | . 37         |

| Table 4-14. PrPMC Cable-001 Termination                              | . 38         |

| Table 5-1. Debugger Commands                                         | . 42         |

| Table 5-2. Diagnostic Test Groups                                    | . 46         |

| Table A-3. Power Requirements for PrPMC800                           | . 57         |

| Table A-4. PrPMC800 Environmental Specifications                     | . 58         |

| Table B-5. Thermally Significant Components                          | . 60         |

| Table C-6. Emerson Network Power - Embedded Computing Publications   | . 65         |

| Table C-7. Manufacturers' Documents                                  | . 66         |

| Table C-8. Related Specifications                                    | . 67         |

# List of Figures

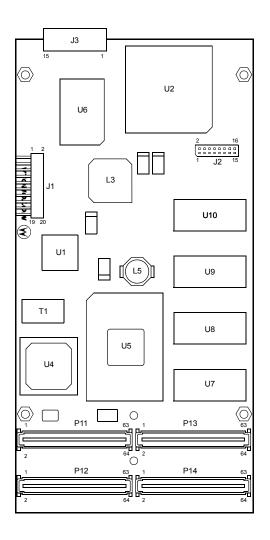

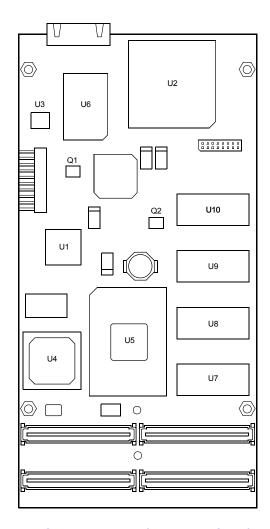

| Figure 1-1. | PrPMC800 Headers, Connectors and Components       | . 5 |

|-------------|---------------------------------------------------|-----|

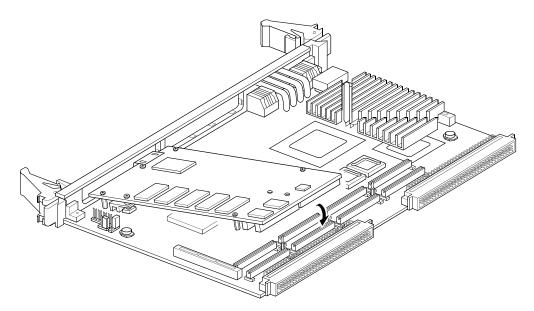

| Figure 1-2. | Installing a PrPMC800 on a VMEmodule              | . 7 |

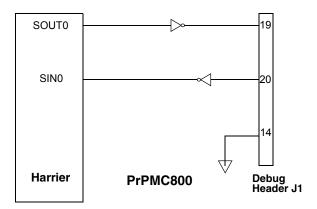

| Figure 2-3. | PrPMC800 Debug Serial Port Configuration          | 11  |

| Figure 3-4. | PrPMC800 Block Diagram                            | 15  |

| Figure 3-5. | PrPMC800 Reset Block Diagram                      | 24  |

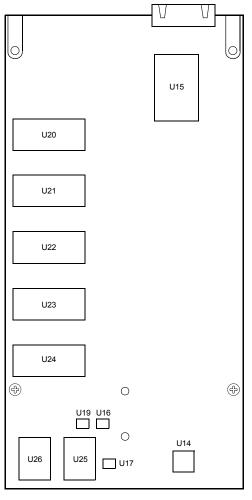

| Figure B-1. | Thermally Significant Components (Primary Side)   | 61  |

| Figure B-2. | Thermally Significant Components (Secondary Side) | 62  |

| Figure B-3. | Measuring Local Air Temperature                   | 63  |

| Figure B-4. | Mounting a Thermocouple Under a Heatsink          | 64  |

## About This Manual

The PrPMC8005E Processor PMC Module Installation and Use provides information for installation and configuration of the PrPMC8005E board, including jumper settings and installation procedures. It also includes descriptions of various components' functions, connector pinout information, and a general description of the PPCBug firmware used with the board. Hereafter, the PrPMC8005E will be referred to as the PrPMC800.

Information in this manual applies to Emerson boards that are compatible with the PowerPC<sup>™</sup> instruction set architecture and that use PPCBug as their resident debugger program. The majority of these boards, including most Processor PMC, VME, CompactPCI<sup>®</sup> and ATX form factors, are equipped with PPCBug.

This document is limited to the installation and use instructions. For programming information, refer to the *Harrier ASIC Programmer's Reference Guide* and the *PrPMC800 Processor PMC Module Programmer's Reference Guide*.

The following table lists the various model numbers and configurations for the PrPMC800. Note that some of the models listed below qualify as Class B devices. If you require a Class B device, contact your Emerson sales representative for specific models and configurations that meet those requirements.

**Table 1-1. PrPMC8005E Models/Configurations**

| Model Number     | Processor /<br>Speed | L2<br>Cache | Memory | Ethernet | PCI Bus<br>Speed  |

|------------------|----------------------|-------------|--------|----------|-------------------|

| PrPMC8005E-1261  | MPC7410/<br>450 MHz  | 2MB         | 256MB  | Front    | 33 MHz            |

| PrPMC8005E-1259  | MPC7410/<br>450 MHz  | 2MB         | 128MB  | Rear     | 33 MHz            |

| PrPMC8005E-1269  | MPC7410/<br>450 MHz  | 2MB         | 256MB  | Rear     | 33 MHz            |

| PrPMC8005E-2261  | MPC7410/<br>450 MHz  | 2MB         | 256MB  | None     | 66 MHz<br>Capable |

| PrPMC800C5E-2261 | MPC7410/<br>450 MHz  | 2MB         | 256MB  | None     | 66 MHz<br>Capable |

| PrPMC8005E-2271  | MPC7410/<br>450 MHz  | 2MB         | 512MB  | None     | 66 MHz<br>Capable |

## **Overview of Contents**

Chapter 1, Preparation and Installation, provides a general description of the PrPMC800 including a summary of the basic features and architecture. It also includes a brief discussion of the monarch and non-monarch use of this board, and the carrier board requirements when the PrPMC800 is being used as a monarch. The remainder of the chapter includes an overview of the start-up procedures, general information on unpacking and hardware preparation, and installation instructions.

Chapter 2, Operating Instructions, contains a section on applying power, a brief description of status LEDs and debug serial ports.

Chapter 3, Functional Description, provides a list of the main features of the PrPMC800. It also provides a general description of the board, a block diagram, and subsections on all of the major components on the board, including configuration settings for the Harrier ASIC. In addition, it also describes various key functions such as arbitration, setting flash memory, memory size settings and system registers.

Chapter 4, Connector Pin Assignments, includes tables of pin assignments for all connectors and headers on the board.

Chapter 5, PPCBug, includes a general discussion of PPCBug, the initialization process and steps, and a brief summary of the use of PPCBug with a list of current commands. A list of the current Diagnostic Test Groups is also included.

Chapter 6, Modifying the Environment, provides a general overview of how to change various parameters within PPCBug firmware. It discusses two main commands: ENV and CNFG.

Appendix A, Specifications, provides basic mechanical, electrical and environmental specifications for the PrPMC800, as well as a section on Thermal Validation offering information on thermally significant components and an overview of how to measure various junction and case temperatures.

Appendix B, Thermal Validation, provides systems integrators with information which can be used to conduct thermal evaluations of the board in their specific system configuration.

Appendix C, Related Documentation, provides a list of other Emerson Embedded Computing related documents, applicable Manufacturer's (vendor) documents, and a list of related specifications. Comments and Suggestions

## **Summary of Changes**

See the table below for manual revisions and changes.

| Part Number | Date           | Description                                                          |

|-------------|----------------|----------------------------------------------------------------------|

| 6806800A42B | September 2008 | Update document to Emerson style (logo, copyright, trademarks, etc.) |

## **Comments and Suggestions**

We welcome and appreciate your comments on our documentation. We want to know what you think about our manuals and how we can make them better.

Mail comments to us by filling out the following online form: http://www.emersonnetworkpowerembeddedcomputing.com/ > Contact Us > Online Form

In "Area of Interest" select "Technical Documentation". Be sure to include the title, part number, and revision of the manual and tell us how you used it.

## **Conventions Used in This Manual**

The following typographical conventions are used in this document:

#### bold

is used for user input that you type just as it appears. Bold is also used for commands, options and arguments to commands, and names of programs, directories and files.

italic

is used for names of variables to which you assign values. Italic is also used for comments in screen displays and examples, and to introduce new terms.

courier

is used for system output (for example, screen displays, reports), examples, and system prompts.

```

<Enter>, <Return> or <CR>

```

<CR> represents the carriage return or Enter key.

#### **CTRL**

represents the Control key. Execute control characters by pressing the Ctrl key and the letter simultaneously, for example, **Ctrl-d**.

|

separates two or more items from which to choose (one only)

[]

encloses an optional item that may not occur at all, or may occur once.

{}

encloses an optional item that may not occur at all, or may occur one or more times.

A character precedes a data or address parameter to specify the numeric format, as follows (if not specified, the format is hexadecimal):

\$ dollar

a hexadecimal character.

0x Zero-x

% percent a binary number. & a decimal number. ampersand

Data and address sizes are defined as follows:

A byte is eight bits, numbered 0 through 7, with bit 0 being the least significant.

A half-word is 16 bits, numbered 0 through 15, with bit 0 being the least significant.

A word is 32 bits, numbered 0 through 31, with bit 0 being the least significant.

The MPU on the board is programmed to big-endian byte ordering. Any attempt to use littleendian byte ordering will immediately render the debugger unusable.

**Note:** All references to processor bus support via the Harrier ASIC relate specifically to the MPC60x-class bus mode. They do not imply support of any other PowerPC-architecture bus mode.

## Introduction

This chapter provides a brief description of the PrPMC8005E Processor PMC Module and instructions for preparing and installing the hardware.

In this manual, the name PrPMC800 refers to all models of the PrPMC8005E series boards, unless otherwise specified. These are add-on modules intended for use with any host carrier board that accepts a PMC or PrPMC module.

## **PrPMC800 Description**

The PrPMC800 is a single-width, standard-length and standard-height Processor PCI Mezzanine Card (PrPMC) board. It is compatible with the PowerPlus III architecture and consists of an MPC7410 processor and the Harrier PCI-Host bridge/system memory controller ASIC. The PrPMC800 features 2MB of L2 cache, 32MB of flash memory (a second bank of flash can be located on the baseboard and accessed through the PMC P14 connector), one bank of SDRAM (128MB to 256MB) onboard, a 10BaseT/100BaseTX Ethernet channel based on the Intel 82559ER/82551IT device and an RS-232 transceiver providing debug capabilities through one of the Harrier UART channels.

Four 64-pin PMC connectors on the PrPMC800 are used to connect the PrPMC800 to the host board. One right-angle 20-pin connector located on the primary side of the PrPMC800 provides an interface to the asynchronous serial port and the processor JTAG/COP port, along with the RESET# and ABORT# signals used for debug support. The serial port and JTAG/COP interfaces, along with the ABORT\_L signal, are also routed to the PMC P14 connector for host board access.

Connectivity to the Ethernet channel is provided either by a front panel connector or by rear I/O via the P14 connector. The build option determines the connection method. Models of this board configured for Ethernet routing via the Pn4 do not have a front bezel.

The PrPMC800 module can operate as a monarch (master) for the baseboard, or as a slave processor PMC, depending on the state of the MONARCH# signal from the PMC P12 connector. When configured as the monarch, the PrPMC800 enumerates the PCI bus, and monitors and services the four PCI interrupts. If configured to operate in the non-monarch mode, the PrPMC800 module does not enumerate the bus or service interrupts, but it may generate a PCI interrupt. The following section describes these modes of operation in greater detail.

#### Monarch and Non-Monarch PrPMCs

The traditional concept of host/master and slave/target processors changes with the inception of the PrPMC because of the arbiter and clock source. Traditionally located on the host board, these functions are not part of the PrPMC800. The VITA 32 specification defines the terms monarch and non-monarch to refer to these two modes of operation for PrPMCs. A monarch PrPMC is defined as the main PCI bus PrPMC (or CPU) that performs PCI bus enumeration at power-up or reset and acts as the PCI interrupt handler. The non-monarch is a slave/target processor that does not perform bus enumeration and does not service PCI interrupts but may generate a PCI interrupt to the host processor.

A system may have one monarch PrPMC800 and/or one or more non-monarch PrPMC800s, creating a loosely coupled multiprocessing system. A PrPMC800 operating as a monarch may be mated to a carrier board with slave processors, PCI, and other I/O devices. A PrPMC800 operating as a non-monarch may be installed on a carrier with a host processor and other PCI devices, such as an CPCI-6065 board. PPCBug does not support all of the operating characteristics of a PrPMC800 operating as a non-monarch. Consequently, another operating system, such as a Real-Time Operating System, may be required.

The PrPMC800 firmware PPCBug is configured to operate as either a monarch or non-monarch by reading the state of the MONARCH# pin on the PrPMC800. This pin is either grounded or left open on the carrier board to enable the desired mode of operation. Refer to the MONARCH# signal explanation on page 25 of this manual for more information.

#### **Carrier Board Requirements**

A carrier board must provide the standard PCI interface, including +3.3V and +5V power (the PrPMC800 only requires +3.3V), PCI address/control, a PCI clock, and two PCI arbiter REQ/GNT pairs (refer to the VITA-32-199x specification for more information). The carrier board must also ground the MONARCH# pin to enable the monarch operating mode. Leaving the MONARCH# pin open enables the non-monarch mode. Additionally, board models PrPMC8005E-2261 and PrPMC8005E -2271 may be configured for 66 MHz PCI operation. To enable this mode, the M66EN pin must be pulled up on the baseboard.

## **System Enclosure**

The system enclosure requirements are determined by the configuration and architecture of the baseboard (either VME, CompactPCI, or custom). Only a single slot is necessary for both the baseboard and the attached PrPMC800 in a VME or CompactPCI chassis.

## **Overview of Start-Up Procedures**

The following table lists the things you need to do before you can use this board and tells where to find the information you need to perform each step. Be sure to read this entire chapter, including all Cautions and Warnings, before you begin.

**Table 1-1. Start-Up Overview**

| What you need to do                                                | Refer to                                                                                                                                                 | On page |

|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Unpack the hardware.                                               | Unpacking the PrPMC800 Hardware                                                                                                                          | 3       |

| Make any settings or adjustments                                   | Preparing the PrPMC800 Hardware                                                                                                                          | 4       |

| on the PrPMC800 module.                                            | PrPMC800 Configuration Considerations                                                                                                                    | 4       |

| Prepare any other optional devices or equipment you will be using. | devices or equipment you will be equipment, refer to the documentation                                                                                   |         |

| Install the PrPMC800 on the baseboard.                             | Installation of a PrPMC800 on a VME or CompactPCI board                                                                                                  | 6       |

| Connect any other optional                                         | Connector Pin Assignments                                                                                                                                | 29      |

| devices or equipment you will be using.                            | For more information on optional devices and equipment, refer to the documentation provided with that equipment.                                         |         |

| Power up the system.                                               | Status Indicators                                                                                                                                        | 10      |

|                                                                    | You may also wish to obtain the <i>PPCBug Diagnostics Manual</i> , listed in Appendix C, <i>Related Documentation</i> .                                  | 65      |

| Examine the environmental                                          | ENV - Set Environment                                                                                                                                    | 50      |

| parameters and make any changes needed.                            | You may also wish to obtain the <i>PPCBug Firmware Package User's Manual</i> , listed in Appendix C, <i>Related Documentation</i> .                      | 65      |

| Program the PrPMC800 module                                        | Preparing the PrPMC800 Hardware                                                                                                                          | 4       |

| and PMCs as needed for your applications.                          | You may also wish to obtain the <i>PrPMC800 Processor PMC Module Programmer's Reference Guide</i> , listed in Appendix C, <i>Related Documentation</i> . | 65      |

# **Unpacking the Hardware**

**Note** If the shipping carton(s) is/are damaged upon receipt, request that the carrier's agent be present during the unpacking and inspection of the equipment.

Unpack the equipment from the shipping carton(s). Refer to the packing list(s) and verify that all items are present. Save the packing material for storing and reshipping of equipment.

Avoid touching areas of integrated circuitry; static discharge can damage these circuits.

## **Preparing the Hardware**

To produce the desired configuration and ensure proper operation of the PrPMC800, you may need to carry out certain modifications before and after installing the modules.

The following paragraphs discuss the preparation of the PrPMC800 hardware components prior to installing them into a chassis and connecting them.

## **PrPMC800 Configuration**

The PrPMC800 provides software control over most options. By setting bits in control registers, after installing the PrPMC800 in a system, you can modify its configuration. Refer to *Table 1-2 on page 4* for information on the Harrier Power-Up Configuration header, which provides access for configuration control. The PrPMC800 control registers are described in detail in the *PrPMC800 Processor PMC Module Programmer's Reference Guide* and the *Harrier ASIC Programmer's Reference Guide* as listed in *Appendix C, Related Documentation*.

Figure 1-1 on page 5 shows the placement of headers, connectors, and components on the PrPMC800. The PrPMC800 was factory tested and is shipped with the configurations described in the following sections. It contains a factory-installed debug monitor, PPCBug, which operates with those factory settings.

## **Harrier Power-Up Configuration Header**

A 2mm, 16-pin low profile header located on side 1 of the PrPMC800 provides the means to change some of the Harrier power-up configuration settings. The pin assignments for this header, along with the power-up setting with the jumper on or off, are as follows (boards are shipped with all jumpers off):

Table 1-2. J2 Harrier Power-Up Configuration Header Pin Assignments

| J2    | Jumper On                                         | Jumper Off                            |

|-------|---------------------------------------------------|---------------------------------------|

| 1-2   | PUST0 = 0<br>Harrier PUST Bit 0 in GCSR Register. | PUST0 = 1                             |

| 3-4   | PUST1 = 0<br>Harrier PUST Bit 1 in GCSR Register  | PUST1 = 1                             |

| 5-6   | PUST2 = 0<br>Harrier PUST Bit 2 in GCSR Register  | PUST2 = 1                             |

| 7-8   | PUST3 = 0<br>Harrier PUST Bit 2 in GCSR Register  | PUST3 = 1                             |

| 9-10  | Hold off Configuration Space access               | Configuration Space access enabled    |

| 11-12 | Processor held in reset at power-up               | Processor enabled at power-up         |

| 13-14 | Class Code set for I2O Controller"                | Class Code set for<br>"Bridge Device" |

| 15-16 | Xport 1uses normal data byte ordering             | Xport 1 uses Hawk data byte ordering  |

Figure 1-1. PrPMC800 Headers, Connectors and Components

## Installation

The following instructions tell how to install the PrPMC800 on a typical VME or CompactPCI single board computer. The PrPMC800 can also be installed on an ATX form factor carrier board that is equipped with industry standard PMC slots.

#### **ESD Precautions**

Use ESD

**Wrist Strap**

Emerson strongly recommends that you use an antistatic wrist strap and a conductive foam pad when installing or upgrading a system. Electronic components, such as disk drives, computer boards, and memory modules, can be extremely sensitive to ESD. After removing the component from the system or its protective wrapper, place the component flat on a grounded, static-free surface (and, in the case of a board, component side up). Do not slide the component over any surface.

If an ESD station is not available, you can avoid damage resulting from ESD by wearing an antistatic wrist strap (available at electronics stores) that is attached to an active electrical ground. Note that a system chassis may not be grounded if it is unplugged.

#### Installation of PrPMC800 on a VME or CompactPCI Board

To install a PrPMC800 mezzanine on an VMEmodule or CompactPCI board, refer to *Figure 1-2* and perform the following steps:

- 1. Attach an ESD strap to your wrist. Attach the other end of the ESD strap to an electrical ground. (Note that the system chassis may not be grounded if it is unplugged) The ESD strap must be secured to your wrist and to ground throughout the procedure.

- 2. Perform an operating system shutdown. Turn the AC or DC power off and remove the AC cord or DC power lines from the system. Remove the chassis or system cover(s) as necessary to gain access to the VMEmodule or CompactPCI board.

Inserting or removing modules with power applied may result in damage to module components.

Carefully remove the VMEmodule or CompactPCI board from its card slot and place it

on a clean and adequately protected working surface (preferably an ESD mat) with the

backplane connectors facing you.

Avoid touching areas of integrated circuitry; static discharge can damage circuits.

4. Place the PrPMC800 mezzanine module on top of the VMEmodule, or CompactPCI board, with the four PMC connectors on the PrPMC800 aligned with the four corresponding connectors on the baseboard. Connectors P11, P12, P13, and P14 at the bottom edge of the PrPMC800 should connect smoothly with the corresponding connectors on the VMEmodule or CompactPCI board.

Figure 1-2. Installing a PrPMC800 on a VMEmodule

- 5. Align the standoffs on the PrPMC800 mezzanine with the VMEmodule or CompactPCI board. Install the Phillips-head screws through the holes in the baseboard and the spacers. Tighten the screws.

- 6. Install the VME or CompactPCI assembly in its proper card slot. Ensure the module is seated properly in the backplane connectors. Do not damage or bend connector pins.

- 7. Replace the chassis or system cover(s) and connect the system to the AC or DC power source. Turn the equipment power on.

## Introduction

This chapter provides information about powering up the PrPMC800 system, and functionality of the status indicators, and I/O ports on the PrPMC800 module.

## **Applying Power**

After you have verified that all necessary hardware preparation has been done, that all connections have been made correctly, and that the installation is complete, you can power up the system. The MPU, hardware and firmware initialization process is performed by the PPCBug firmware at power-up or system reset. The firmware initializes the devices on the PrPMC800 module in preparation for booting the operating system.

The firmware, PPCBug, is shipped from the factory with an appropriate set of defaults. In most cases there is no need to modify the firmware configuration before you boot the operating system. However, if you choose to do so, refer to *Chapter 6, Modifying the Environment* for further information about modifying these defaults.

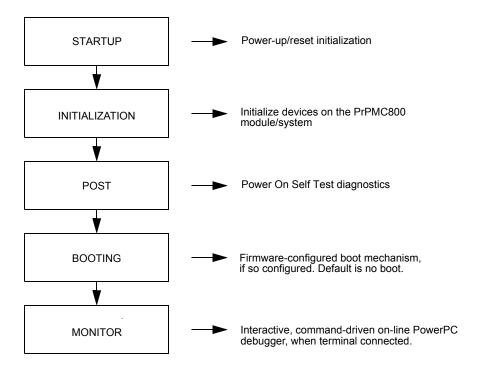

The following flowchart shows the basic initialization process that takes place during PrPMC800 system start-up.

For further information on PPCBug, refer to *Chapter 5, PPCBug*, or to the PPCBug documentation listed in *Appendix C, Related Documentation*.

## Status LEDs and Port Connections

The PrPMC800's status indicators (LEDs), Debug Serial port and Ethernet Port adapter cable are described in the following subsections.

#### **Status Indicators**

There are two LED (light-emitting diode) status indicators located on the secondary side of the PrPMC800, BDFL and CPU.

#### BDFL

The yellow fail LED is lit when the Harrier Board fail bit (**BDFL**) in the Miscellaneous Control and Status register is active (software controlled). This LED is illuminated at reset and then turned off after PPCBug has successfully completed initialization.

#### **CPU**

The green CPU LED is lit when the DBB# (Data Bus Busy) signal line on the processor bus is active (hardware controlled).

#### **Debug Serial Port**

A three-wire debug serial RS-232 port (TXD, RXD, GND) is available on the 2mm, 20-pin right-angle header (J1) located on the primary side of the PrPMC800. Refer to *Figure 2-3* for pin definitions. An optional J1-to-DB9 adapter cable is available from Emerson. Contact your local Emerson Sales Office or Distributor for more information or to order cable part number: PrPMC-CABLE-001. The pinout description for this cable is defined in *Debug Serial Port Cable on page 38*.

The debug port may be used for connecting a terminal to the PrPMC800 to serve as the firmware console for the factory installed debugger, PPCBug. The port is configured as follows:

- 8 bits per character

- 1 stop bit per character

- □ Parity disabled (no parity)

- Baud rate = 9600 baud (default baud rate at power-up)

After power-up, the baud rate of the debug port can be reconfigured by using the debugger's Port Format (**PF**) command. Refer to *Chapter 5, PPCBug* and *Chapter 6, Modifying the Environment* for information about PPCBug.

Figure 2-3. PrPMC800 Debug Serial Port Configuration

## **Ethernet Port Adapter Cable**

An Ethernet port adapter cable is available for those models with front panel Ethernet. The cable provides the capability to adapt the low profile Ethernet connector (J3) to a standard RJ45 receptacle. Contact your local Emerson Sales Office to order cable part number: PRPMC-Cable-003.

## Introduction

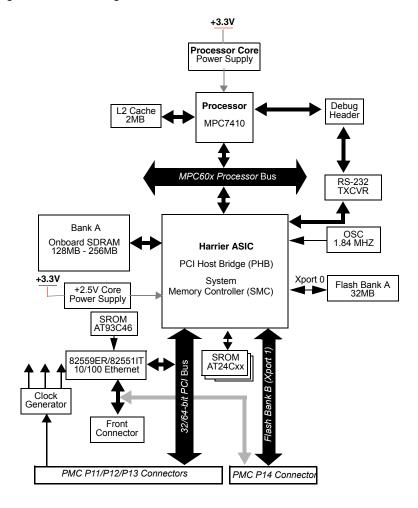

This chapter describes the PrPMC800 Processor PMC Module on a block diagram level. The *General Description* provides an overview of the PrPMC800, followed by a detailed description of several blocks of circuitry. *Figure 3-4 on page 15* shows a block diagram of the overall board architecture.

Detailed descriptions of other PrPMC800 blocks, including programmable registers in the ASIC and peripheral chips, can be found in the *PrPMC800 Processor PMC Module Programmer's Reference Guide* and the *Harrier ASIC Programmer's Reference Guide*, *listed in Appendix C, Related Documentation*. Refer to those documents for a more comprehensive set of functional descriptions.

## **Features**

The following table summarizes the features of the PrPMC800 processor module.

Table 3-3. PrPMC800 Features

| Feature              | Description                                                                                                                                                                                       |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Processor            | Single MPC7410 processor Core frequencies of 450Mhz for MPC7410 Bus clock frequency of 100 MHz. Address and data bus parity                                                                       |

| L2 Cache             | Backside L2 Cache using pipeline burst-mode SRAMS: 2MB for the MPC7410 Data bus parity                                                                                                            |

| Flash Memory         | Bank A: 32MB soldered on-board using two 128 Mbit devices.  Bank B: Second bank of flash can be located on host board and accessed through the PMC P14 connector.                                 |

| SDRAM                | Double-Bit-Error detect, Single-Bit-Error correct across 72 bits Single bank of 16-bit wide devices onboard provide 128MB to 256MB SDRAM.                                                         |

| Memory Controller    | Harrier's SMC (System Memory Controller).                                                                                                                                                         |

| PCI Host Bridge      | Harrier's PHB (PCI Host Bridge).                                                                                                                                                                  |

| Interrupt Controller | Harrier's MPIC (Multi-Processor Interrupt Controller).                                                                                                                                            |

| PCI Interface        | 32/64-bit Data 33 MHz minimum, 66 MHz capable on certain models +3.3V/+5V universal signaling compatible interface P11, P12, P13 and P14 PMC connectors Address/data parity per PCI specification |

Table 3-3. PrPMC800 Features (continued)

| Feature                     | Description                                                                                                                                                                         |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ethernet Interface          | 10BaseT/100BaseTX interface based on the Intel<br>82559ER/82551IT device<br>AT93C46 SROM for 82559ER/82551IT configuration                                                          |

| SROM                        | Two 8K byte dual-address I <sup>2</sup> C serial EEPROM devices for Vital Product Data, user configuration data One 256 byte standard I <sup>2</sup> C serial EEPROM for memory SPD |

| Debug Support               | Two 16550-compatible async serial ports (in Harrier) with RS-232 interface Processor JTAG/COP Interface RESET and ABORT signals Signals routed to 2mm header and PMC connector P14  |

| Input Power<br>Requirements | 3.3V ± 5%                                                                                                                                                                           |

| Form Factor                 | Single-width, standard-length PMC (74mm x 149mm) with 10mm board-to-board stacking height. Standard (3.5mm) side 2 height                                                           |

## **General Description**

The PrPMC800 is a Emerson processor PMC module compatible with the PowerPlus III architecture. It consists of an MPC7410 processor and:

- Harrier System Memory Controller/PCI Host Bridge ASIC

- 32MB of flash memory

- □ 128MB TO 256MB of ECC-protected SDRAM on board with memory expansion capability

- □ 10BaseT/100BaseTX Ethernet controller

- Debug serial port

The PrPMC800 module interfaces to the host board PCI bus via the PMC P11, P12 and P13 connectors. These provide a 64-bit PCI interface (that is, 33 MHz/66 MHz capable) between the host board and the PrPMC800. The PrPMC module draws +3.3V through the PMC connectors. The onboard Processor Core Power Supply derives the core voltage from the +3.3V power. The clock generator derives all of the required onboard clocks from the PCI clock input on P11.

The PrPMC800 module has a 2mm header onboard to support module debug operations. This header provides the interface to the debug serial RS-232 port and an interface to the processor JTAG/COP port.

The PrPMC800 module can function as a system controller (monarch mode) for the host board or as a slave processor (non-monarch) PMC, depending on the state of the MONARCH# signal from the PMC connector. When configured as the monarch, the PrPMC800's PPCBug enumerates the PCI bus as well as monitor and service the four PCI interrupts.

# **Block Diagram**

The following figure is a block diagram of the PrPMC800's overall architecture

Figure 3-4. PrPMC800 Block Diagram

#### **Processor**

The PrPMC800 board can be ordered with 450 MHz MPC7410-class, low-power/low care voltage processor chip.

#### L2 Cache

The PrPMC800 utilizes a backside L2 cache structure via the MPC7410 processor chip family. The L2 cache is implemented with an on-chip, 2-way set-associative tag memory and external direct-mapped synchronous SRAMs for data storage. The external SRAMs are accessed through a dedicated 72-bit wide (64 bits of data and 8 bits of parity) L2 cache port. The MPC7410 processor can support up to 2MB. The L2 cache can operate in copyback or write-through modes and supports system cache coherency through snooping. Data parity generation and checking can be disabled by programming the processor's L2 cache control register accordingly. The MPC7410 processor also supports direct mapping of the SRAM memory, in conjunction with normal L2 cache operation. In this mode, a portion of the SRAM memory space may be mapped to appear as a private memory space in the memory map. Refer to the processor data sheet for additional information.

The L2 cache data SRAM for the PrPMC800 is implemented using two 128K x 36 or 256K x 36 synchronous pipelined burst SRAMs providing a total of 2MB of L2 cache.

## Harrier System Memory Controller / PCI Host Bridge ASIC

The Harrier ASIC provides the bridge function between the PPC60x bus, the system memory, and the PCI Local Bus. The Harrier ASIC incorporates the following key features:

- 100 MHz PowerPC-compatible bus interface

- □ SDRAM interface supporting up to eight banks of 512MB each, with ECC

- □ 32/64-bit REV2.1 compliant PCI bus interface capable of running up to 66 MHz

- Single channel DMA controller

- Message passing unit supporting I2O and generic functions

- □ Two internal 16550-type UARTs

- □ Two I<sup>2</sup>C bus master interfaces

- □ MPIC compliant interrupt controller

- Four Xport channels for interfacing to flash or other external registers/devices

Refer to the Harrier Programmer's Guide for additional information and programming details.

#### **Harrier Power-Up Configuration**

The Harrier ASIC XAD30-XAD0 pins provide configuration information for Harrier at power-up reset time. The following table lists the default power-up reset state of these pins for the PrPMC800 module. The **Select Option** column indicates whether the power-up setting can be changed by jumper, or if the setting is fixed and cannot be changed. The **Default Power-Up Setting** column indicates the default values for the standard PrPMC800 product. Default settings for jumper options indicate power-up values with jumpers not installed.

**Table 3-4. Harrier Power-Up Configuration Settings**

| Harrier<br>XAD<br>Bus<br>Signal | Select<br>Option        | Default<br>Power-<br>Up<br>Setting | Function/<br>Register Bit                                         | Description                                                                                                                                                                                                                                                                                   |

|---------------------------------|-------------------------|------------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XAD[30]                         | Jumper J2<br>pins 15-16 | 1                                  | Hawk data mode<br>XCSR.XPGC.HDM                                   | Enable/Disable (1/0) Hawk 16-bit data ordering mode for Xports configured for Hawk addressing mode. Xport 1 (flash bank B) is configured for Hawk compatibility mode. If disabled, use Harrier byte ordering mode.                                                                            |

| XAD[29]                         | Fixed                   | 0                                  | UART clock select                                                 | Select external clock source for UART.                                                                                                                                                                                                                                                        |

| XAD[28]                         | Jumper J2<br>pins 9-10  | 0                                  | PCI slave<br>configuration holdoff<br>XCSR.BPCS.CSH               | Enable/disable (1/0) configuration space hold off. If enabled, accesses to the PCI configuration space from another PCI master results in a disconnect retry. Local PrPMC800 software must clear this register bit to enable access after inbound address and attribute fields have been set. |

| XAD[27]                         | Fixed                   | 0                                  | PCI slave<br>configuration mask<br>XCSR.BPCS.CSM                  | All of Harrier's PCI configuration registers are visible from PCI space.                                                                                                                                                                                                                      |

| XAD[26]                         | Jumper J2<br>pins11-12  | 0                                  | Processor holdoff<br>XCSR.BXCS                                    | Enable/disable (1/0)<br>processor hold off at power-<br>up. If enabled, processor is<br>held in reset.                                                                                                                                                                                        |

| XAD[25]                         | Fixed                   | 0                                  | SDRAM external register XCSR.SDTC.SDER                            | There are no external buffers in series with the BAx, RAx, WE, RAS or CAS signals.                                                                                                                                                                                                            |

| XAD[24]                         | Fixed                   | 1                                  | Response to<br>unmapped address-<br>only cycles<br>XCSR.GCSR.AOAO | Harrier responds to unmapped address only cycles.                                                                                                                                                                                                                                             |

**Table 3-4. Harrier Power-Up Configuration Settings (continued)**

| Harrier<br>XAD<br>Bus<br>Signal | Select<br>Option                                                     | Default<br>Power-<br>Up<br>Setting | Function/<br>Register Bit                               | Description                                                                                                           |

|---------------------------------|----------------------------------------------------------------------|------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| XAD[23]                         | Jumper J2<br>pins 7-8                                                | 1                                  | Generic power up<br>status bit 3<br>XCSR.GCSR.PUST<br>3 | Software readable header bit 3                                                                                        |

| XAD[22]                         | Jumper J2<br>pins 5-6                                                | 1                                  | Generic power up<br>status bit 2<br>XCSR.GCSR.PUST<br>2 | Software readable header bit 2                                                                                        |

| XAD[21]                         | Jumper J2<br>pins 3-4                                                | 1                                  | Generic power up<br>status bit 1<br>XCSR.GCSR.PUST<br>1 | Software readable header bit 1                                                                                        |

| XAD[20]                         | Jumper J2<br>pins 1-2                                                | 1                                  | Generic power up<br>status bit 0<br>XCSR.GCSR.PUST<br>0 | Software readable header bit 0                                                                                        |

| XAD[19]                         | Jumper J2<br>pins 13-14                                              | 0                                  | I2O IOP agent                                           | Set PCI Configuration<br>register CLAS to present<br>class code for "bridge<br>device" (0) or "I2O<br>Controller" (1) |

| XAD[18]                         | Fixed                                                                | 0                                  | Internal PCI arbiter                                    | Disable internal PCI arbiter                                                                                          |

| XAD[17]                         | Fixed                                                                | 1                                  | Internal processor arbiter                              | Enable internal Processor arbiter                                                                                     |

| XAD<br>[16:15]                  | Fixed                                                                | 00                                 | XCSR register group base address                        | Set XCSR register group base address to \$FEFF0000                                                                    |

|                                 | On board<br>logic sets<br>ratio<br>depending<br>on state of<br>M66EN | 000                                | reserved                                                |                                                                                                                       |

| XAD<br>[14-12]                  |                                                                      | 001                                | 3:2                                                     | Set PPC-to-PCI clock ratio to 3:2                                                                                     |

|                                 |                                                                      | 010                                | 2:1                                                     | Set PPC-to-PCI clock ratio to 2:1                                                                                     |

|                                 |                                                                      | 011                                | 5:2                                                     | Set PPC-to-PCI clock ratio to 5:2                                                                                     |

|                                 |                                                                      | 100                                | 1:1                                                     | Set PPC-to-PCI clock ratio to 1:1                                                                                     |

|                                 |                                                                      | 101                                | reserved                                                |                                                                                                                       |

|                                 |                                                                      | 110                                | 3:1                                                     | Set PPC-to-PCI clock ratio to 3:1                                                                                     |

|                                 |                                                                      | 111                                | reserved                                                |                                                                                                                       |

| XAD<br>[11:10]                  | Fixed                                                                | 01                                 | Xport channel 0<br>data width<br>XCSR.XPAT0.DW          | Set flash bank A to 16-bit width                                                                                      |

**Table 3-4. Harrier Power-Up Configuration Settings (continued)**

| Harrier<br>XAD<br>Bus<br>Signal | Select<br>Option | Default<br>Power-<br>Up<br>Setting | Function/<br>Register Bit                      | Description                                                                                                         |

|---------------------------------|------------------|------------------------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| XAD[9]                          | BankB_SE<br>L    | х                                  | Xport channel 0 reset vector source            | Enable/Disable (1/0) Xport channel 0 (flash bank A) as reset vector source, depending on state of baseboard jumper. |

| XAD<br>[8:7]                    | Fixed            | 11                                 | Xport channel 1<br>data width<br>XCSR.XPAT1.DW | Set Xport channel 1 (flash bank B) to 16-bit width, Hawk addressing mode.                                           |

| XAD[6]                          | Fixed            | 1                                  | Xport channel 1 reset vector source            | Enable Xport channel 1 (flash bank B) as reset vector source if Xport channel 0 is disabled.                        |

| XAD<br>[5:4]                    | Fixed            | xx                                 | Xport channel 2<br>data width<br>XCSR.XPAT2.DW | Unused.                                                                                                             |

| XAD[3]                          | Fixed            | 0                                  | Xport channel 2 reset vector source            | Disable Xport channel 2 as<br>Reset Vector source                                                                   |

| XAD<br>[2:1]                    | Fixed            | xx                                 | Xport channel 3<br>data width<br>XCSR.XPAT2.DW | Unused.                                                                                                             |

| XAD[0]                          | Fixed            | 0                                  | Xport Channel 3<br>Reset Vector Source         | Disable Xport channel 3 as<br>Reset Vector source                                                                   |

#### **Arbitration**

The Harrier ASIC contains arbiters for the PPC bus (60x bus mode only) and the PCI bus. The PPC arbiter is used to arbitrate between the processor and the Harrier PPC bus master for ownership of the PPC bus. The processor is connected to the Harrier arbiter CPU0\_REQ/CPU0\_GNT signal pair (XARB3/XARB0).

The Harrier PCI bus arbiter is disabled in the standard board configuration. Per the VITA-32 199x Processor PMC Standard, the PCI bus arbitration must be provided by the baseboard.

## **Flash Memory**

The PrPMC800 supports two banks of flash memory. Bank A is onboard flash, while bank B is optional flash located on the host board and accessed through the PMC P14 connector.

#### **Onboard Bank A Flash**

The PrPMC800 contains one bank of 32MB of flash memory on Xport 0 configured for 16-bit mode. Bank A consists of two Intel StrataFlash (28F128J3D) +3.3 volt devices configured to operate in 8-bit mode. These Intel StrataFlash devices support page read mode operations with an 8-byte page size per device.

#### **Optional Bank B Flash**

The signal interface for the Harrier Xport 1, configured to operate in Hawk 16-bit address/data mode, is routed to the PMC P14 connector to support an optional 16-bit flash bank B on the baseboard. The address multiplexing of the Hawk mode can address up to 512MB, but device loading may restrict this size to less than that. The reset vector may be sourced by either bank A or bank B depending on the state of the Harrier Xport reset vector control bits (*RVEN0/RVEN1*). When the *RVEN0* bit is set, address range \$FFF00000-\$FFFFFFF maps to bank A. When *RVEN0* bit is cleared and the *RVEN1* bit is set, the address range \$FFF00000-\$FFFFFFF maps to bank B. The default state uses bank A for the reset vector. Bank B may be selected by connecting the BANKB\_SEL pin on P14 to +3.3V.

Xport 1 may be configured to operate in the normal data byte ordering mode where the data alternates every byte instead of every forth byte (Hawk data mode). The data ordering mode is controlled by one of the onboard jumpers.

## **ECC Memory**

The PrPMC800 supports onboard ECC SDRAM configured as explained below.

#### Onboard SDRAM

The PrPMC800 onboard ECC SDRAM memory, bank A, is configured as one bank of nine 8-bit wide, +3.3V SDRAM devices in 54-pin TSOPII packages. The total onboard memory size can be 64MB, 128MB, 256MB, or 512MB depending on the memory type used. The SDRAM memory is controlled by the Harrier ASIC which provides single-bit error correction and double-bit error detection. ECC is calculated over 72-bits. Refer to the *Harrier ASIC Programmer's Reference Guide* for additional information and programming details. The SDRAM memory bus operates at the same speed as the processor bus.

#### **SROM**

The PrPMC800 module contains two 8Kb serial EEPROM devices (AT24C64A) and one 256 byte serial EEPROM device (AT24C02) onboard. One 8Kb serial EEPROM provides for Vital Product Data (VPD) storage of the module hardware configuration, and the other 8Kb device provides storage for user configuration data. The contents of the devices are accessed by providing a two-byte address with the same device ID, instead of the standard one-byte address as used in the 256 byte devices. The 256 byte device provides for Serial Presence Detect (SPD) memory configuration information. The Serial EEPROM's are accessed through I<sup>2</sup>C port 0 in the Harrier ASIC. Refer to Appendix B of the *PrPMC800 Processor PMC Module Programmer's Reference Guide* for information on the contents of the VPD and SPD.

Harrier I<sup>2</sup>C port 0 is also routed to pins on the P14 PMC user I/O connector. The connection to the PMC connector provides a means to interface to an optional configuration SROM on the baseboard. This allows the PrPMC800 to determine hardware configuration information from the baseboard. Refer to the *Harrier ASIC Programmer's Reference Guide* for SROM device address assignments.

#### 10BaseT/100BaseTX Ethernet Channel

The PrPMC800 module uses an Intel GD82559ER/82551IT Ethernet controller to implement a 10BaseT/100BaseTX Ethernet channel. The GD82559ER/82551IT is a lower power, lower cost version of the GD82559 without the wake-on-LAN features. The GD82559ER/82551IT consists of both the Media Access Controller (MAC) and the physical layer (PHY) in a single integrated package. A Pulse H0013 low profile transformer is used to supply the external magnetics. The module will support a front panel Ethernet connection via a low profile PC card style connector mounted at the front of the module (on models -12x1 and -52x1). Optional rear I/O Ethernet is provided by routing the Ethernet transmit and receive signal pairs to P14 connector (on model PrPMC880-1279).

The 82559ER/82551IT interfaces to an AT93C46 serial EEPROM device that provides power-up configuration information for the 82559ER/82551IT. This is a 1Kb device organized as 64 16-bit words. Refer to the corresponding table in the VPD appendix of the *PrPMC800 Processor PMC Module Programmer's Reference Guide*, for the contents of this device.

#### **Miscellaneous Control and Status**

The Harrier ASIC contains a Miscellaneous Control and Status register that provides the PrPMC800 module with the module fail LED control, PrPMC EREADY# pin status, PrPMC MONARCH# pin status, module reset control, and processor timebase enable control. Refer to the *Harrier ASIC Programmer's Reference Guide* for additional details.

#### **Timers**

Timers on the PrPMC800 board are provided by the Harrier ASIC. Refer to the Harrier ASIC documents for programming details on these timers.

#### 32-Bit Timers

Four 32-bit timers are provided by Harrier (MPIC) that may be used for system timing or to generate periodic interrupts. Each timer is driven by a divide-by-eight prescaler which is synchronized to the Power PC processor clock. For a 100 MHz processor bus, the timer frequency would be 12.5 MHz.

#### **Watchdog Timers**

The Harrier ASIC contains two Watchdog timers, WDT0 and WDT1. Each timer is functionally equivalent but independent. These timers continuously decrement until they reach a count of 0 or are reloaded by software. The time-out period is programmable from 1 microsecond up to 32 minutes. If the timer count reaches 0, a timer output signal is asserted. The output of Watchdog Timer 0 is routed to an MPIC interrupt. The output of Watchdog Timer 1 is connected to the Harrier AUXRST, which will generate RESETOUT\_L.

Following a Harrier device reset, WDT0 is enabled with a default time-out of 8 seconds and WDT 1 is enabled with a default time-out of 16 seconds. Each timer must be disabled or reloaded by software to prevent a time-out. Software may reload a new timer value or force the timer to reload a previously loaded value. To disable or load/reload a timer requires a two step process.

## **Interrupt Routing and Generation**

External interrupts routed to the Harrier MPIC include the four PCI interrupts INTA#-INTD#, four host board interrupts from PMC connector P14, and the output from the watchdog timers. The PrPMC800 has the ability to generate any one of the PCI interrupts INTA#-INTD# by using the Harrier Generic Outbound Doorbell register or the I2O controller. The desired PCI interrupt is selected by programming the PCI Interrupt Mapping bits in the Harrier Bridge PCI Control and Status register.

## **Asynchronous Serial Port**

The PrPMC800 module provides a two-wire asynchronous serial interface (TXD and RXD) for use as a serial debug port. UART0 in the Harrier ASIC provides the 16550 compatible UART controller. The UART0 port SIN0 and SOUT0 signals are wired to an external RS-232 transceiver which interfaces to the 2mm debug header and the P14 connector. An onboard 1.8432 MHz oscillator provides the baud rate clock for the UART.

#### Clock Generator

The PrPMC800 module clock generator uses a Z9972 PLL clock driver to provide the clocks for the processor, the Harrier ASIC and the SDRAMs. All clocks are referenced to the PCI clock input on PMC connector P11. The PrPMC800 supports the PPC-to-PCI clock ratios listed in the following table. Onboard logic uses the state of the PMC M66EN pin to determine whether the maximum PCI clock frequency will be 33 MHz or 66 MHz.

Table 3-5. PPC to PCI Clock Ratios

| M66EN Pin | PPC Clock<br>Frequency<br>(MHz) | PCI Clock<br>Frequency<br>(MHz) | Ratio<br>(PPC:PCI) | Harrier PCI<br>Clock Divisor<br>(N) |

|-----------|---------------------------------|---------------------------------|--------------------|-------------------------------------|

| Low       | 100                             | 33.33                           | 3:1                | 12                                  |

| High      | 100                             | 66.67                           | 3:2                | 6                                   |

### **PrPMC800 Power Supplies**

The PrPMC800 module requires only a +3.3V input voltage. The processor core voltage and the Harrier core voltage are generated on the module from the +3.3V input using the LTC1702 dual synchronous switching regulator. In addition to the Harrier core voltage, the +2.5V supply provides the processor, Harrier, and L2 cache I/O voltages.

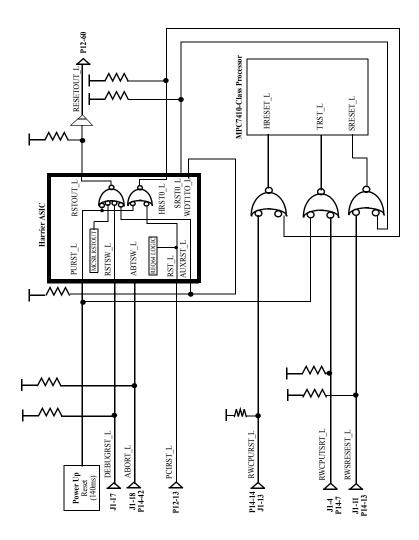

## **Module Reset Logic**

A block diagram of the PrPMC800 module reset logic appears in Figure 3-5 on page 24.

There are five standard sources of reset on the PrPMC800. They are:

- 1. Power-Up reset

- 2. PMC PCI RST#

- 3. Watchdog Timer reset via the Harrier Watchdog 1 Timer output

- 4. Software generated module reset from Harrier RSTOUT control bit

- 5. Debug RESET\_L signal from debug header

The following table describes the function of each reset source. A module reset includes the processor, Harrier and Ethernet. The RESETOUT\_L pin must be tied into the baseboard reset logic, which drives PCIRST# in order to produce module reset.

**Table 3-6. Reset Source Functions**

| Reset Source Type | Module Reset | PrPMC RESETOUT_L Active |

|-------------------|--------------|-------------------------|

| Power-Up Reset    | х            | Х                       |

| PMC PCI RST#      | х            |                         |

| WDT1 Timer Output |              | Х                       |

| SW Reset          |              | х                       |

| Debug Reset       |              | Х                       |

Figure 3-5. PrPMC800 Reset Block Diagram

#### **PCI** Interface

The PrPMC800 module contains four EIA-E700 AAAB connectors that provide a 32/64-bit PCI interface to an IEEE P1386.1 PMC compliant baseboard. Connectors P11-P13 provide the 32/64-bit 66 MHz capable PCI interface while P14 provides an I/O path from the module to the baseboard. Signals routed to P14 include the I<sup>2</sup>C bus, the RS-232 debug port, the processor JTAG/COP and the Xport 1.

PCI bus pullup resistors required by the PCI Revision 2.1 Specification (for motherboards), including 64-bit expansion signals, must be supplied by the baseboard. This is required if the PrPMC800 is operating as a monarch or non-monarch module.

The following special function processor PMC pins, as defined by the draft *Processor PMC Standard VITA-32-199x*, are implemented on the PrPMC800 as described in the following sections.

#### **PRESENT# Signal**

The PRESENT# signal on the PrPMC800 module is grounded to indicate to the baseboard that the module is installed.

#### **MONARCH# Signal**