# *Uncle (Unified NCL Environment)*

Robert B. Reese

December 2011

**Electrical & Computer Engineering Department**

Mississippi State University

Abstract: Uncle (Unified NCL Environment) is a toolset for creating dual-rail asynchronous designs using NULL Convention Logic (NCL). Both data-driven and control-driven (i.e., Balsa-style) styles are supported. The specification level is RTL, which means that the designer is responsible for creating both datapath (registers and compute blocks) and control (finite state machines, sequencers). Designs are specified in Verilog RTL, and a commercial synthesis tool is used to synthesize to a netlist of D-flip-flops, latches, combinational logic, and special gates known by the toolset. The Uncle toolset converts this netlist to an NCL netlist by single-rail to dual-rail conversion, and then generates the acknowledge network to make the NCL netlist live and safe. The resulting gate level netlist can then be simulated in a Verilog simulator or serve as the input netlist to a VLSI environment for transistor level simulation. Performance optimization via latch movement to balance data/acks delays is supported. An internal simulator is included that reports gate orphans/cycle time and includes NLDM timing. The toolset has a regression suite that includes several examples from both design styles. A transistor-level library of all gates is included in the release.

OTHER CONTRIBUTORS: RYAN A. TAYLOR

NOTE: THIS WORK PARTIALLY FUNDED BY NSF-CCF-1116405.

# **Contents**

| U | ncle (L                   | Inified NCL Environment)                                                  | 1  |  |

|---|---------------------------|---------------------------------------------------------------------------|----|--|

| 1 | Inst                      | tallation and Requirements                                                |    |  |

| 2 | Met                       | hodology Introduction                                                     | 5  |  |

|   | 2.1                       | Justification/Goals                                                       | 5  |  |

|   | 2.2                       | Uncle Flow Overview                                                       | 6  |  |

|   | 2.3                       | Dual Rail Combinational Logic in NCL                                      | 7  |  |

|   | 2.4                       | Data-driven vs. Control-driven Design Styles                              | 8  |  |

|   | 2.5                       | Data-driven Control and Registers                                         | 8  |  |

|   | 2.6                       | Control-driven Control and Registers                                      | 10 |  |

| 3 | Data                      | a-driven Examples                                                         | 11 |  |

|   | 3.1                       | RTL Constructs                                                            | 12 |  |

|   | 3.2                       | RTL Restrictions                                                          | 13 |  |

|   | 3.3                       | First example: clk_up_counter.v to ncl_up_counter.v walkthrough           | 13 |  |

|   | 3.4                       | Second Example: GCD16 (clkspec_gcdsimple.v)                               | 22 |  |

| 4 | 1 Control-driven Examples |                                                                           | 26 |  |

|   | 4.1                       | First control-driven example: up_counter.v to ncl_up_counter.v            | 26 |  |

|   | 4.2                       | While-loops, choice                                                       | 30 |  |

|   | 4.3                       | GCD control-driven example: gcd16bit.v to uncle_gcd16bit.v                | 34 |  |

|   | 4.4                       | Control-driven divider circuit – two methods (contrib. by Ryan A. Taylor) | 36 |  |

| 5 | 5 Optimizations           |                                                                           | 40 |  |

|   | 5.1                       | Net Buffering                                                             | 40 |  |

|   | 5.2                       | Latch Balancing                                                           | 41 |  |

|   | 5.3                       | Relaxation                                                                | 44 |  |

|   | 5.4                       | Cell Merging                                                              | 45 |  |

| 6 | 6 Miscellaneous Examples  |                                                                           | 45 |  |

|   | 6.1                       | A simple ALU, use of demuxes and merge gates                              | 45 |  |

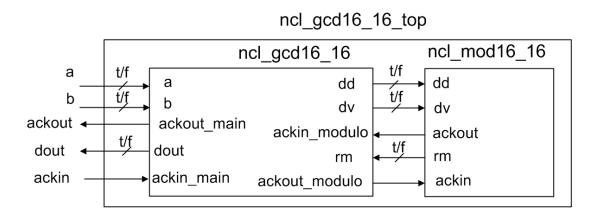

|   | 6.2                       | Multi-block Design: clkspec_gcd16_16.v, clkspec_mod16_16.v                | 50 |  |

|   | 63                        | A simple CPIT use of register files                                       | 58 |  |

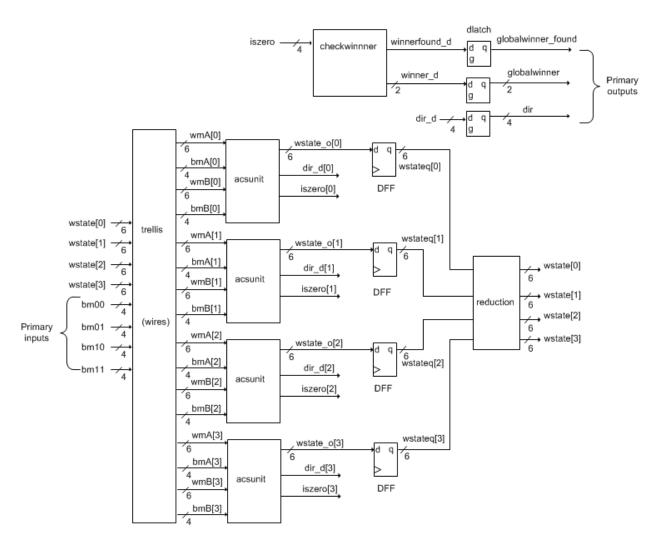

|     | 6.4  | Viterbi Decoder, mixing of control-driven and data-driven styles       | 60 |

|-----|------|------------------------------------------------------------------------|----|

| 7   | Ar   | bitration                                                              | 65 |

|     | 7.1  | Arbitration support in Uncle                                           | 66 |

|     | 7.2  | Arbiter Example: clkspec_arbtst_2shared.v, clkspec_arbtst_client.v     | 67 |

|     | 7.3  | Arbiter Example: clkspec_v2arbtst_2shared.v, clkspec_v2arbtst_client.v | 72 |

|     | 7.4  | Arbiter Example: clkspec_forktst.v                                     | 75 |

| 8   | Ac   | k Network Generation                                                   | 76 |

|     | 8.1  | Basic algorithm                                                        | 76 |

|     | 8.2  | Complications (demux and merge gates)                                  | 77 |

|     | 8.3  | Illegal Topologies                                                     | 78 |

|     | 8.4  | Early Completion Ack Network                                           | 78 |

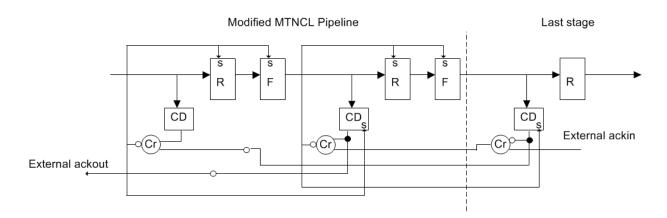

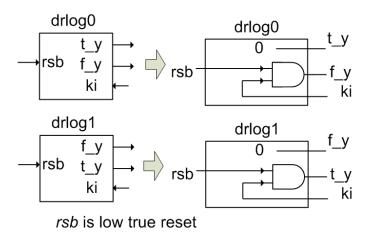

|     | 8.5  | Multi-threshold NCL (MTNCL), aka Sleep Convention Logic (SCL)          | 79 |

| 9   | Tr   | ansistor-level Simulation, Gate Characterization                       | 80 |

|     | 9.1  | Transistor-level Simulation                                            | 80 |

|     | 9.2  | Gate Characterization                                                  | 82 |

| 1(  | )    | Tech Files                                                             | 83 |

|     | 10.1 | L common.ini Variables                                                 | 84 |

| 1:  | 1    | Acknowledgements, Comments/Questions                                   | 86 |

| 12  | 2    | Appendix                                                               | 86 |

|     | 12.1 | L Debugging Tips                                                       | 86 |

|     | 12.2 | Notes on Synopsys synthesis                                            | 86 |

|     | 12.3 | Notes on Cadence synthesis                                             | 87 |

|     | 12.4 | 1 Constant Logic                                                       | 87 |

|     | 12.5 | doregress.py Scripts                                                   | 88 |

| 13  | 3    | Change Log                                                             | 90 |

|     | 13.1 | Change log for 0.2.xx                                                  | 90 |

|     | 13.2 | Change log for 0.1.xx                                                  | 90 |

| 1 4 | 1    | References                                                             | 93 |

## 1 Installation and Requirements

#### What do you need to use this toolset?

- A Linux environment to run the tools

- A commercial synthesis tool (Synopsys Design Compiler or Cadence RTL is currently supported).

- A Verilog simulator (the gate level models have been tested with Modelsim (both Linux and Windows), Cadence ncsim, and Synopsys SCS).

#### What is provided in the toolset?

- Linux 32-bit/64-bit binaries of the tools

- Verilog gate level models of the NCL gates (functional only, unit timing) and other support gates

- Sample designs with self-checking testbenches

- A user manual with tutorial examples

#### What are the usage restrictions?

At this time, there are no usage restrictions, the toolset can be used for research, educational, or commercial purposes. It is requested that you give appropriate credit for any published designs created using this toolset. Be aware that there are patent issues regarding commercialization of NCL designs (see Camgian Microsystems, Wave Semiconductor).

#### Level of NULL Convention Logic (NCL) knowledge required?

This document assumes that that reader has a working knowledge of NCL, which is a threshold logic design style used by Theseus Logic in the 1995-2005 (approximately) time frame for several ASICs. Some background references for NCL are [1][2][3]. An excellent introduction to NCL design is found at [4].

#### Is the code source available?

Source code is available to collaborators for toolset improvement.

#### How do I install the toolset?

The compressed tar archive should be unpacked into the directory that will serve as the final home for the tools. The *README.txt* file at the top level of the archive will have the latest installation instructions.

#### Why should I even care about asynchronous design?

Because it is fun? This document makes no attempt to justify this style of asynchronous design or asynchronous design in general; either it fulfills a need or it does not.

### 2 Methodology Introduction

### 2.1 Justification/Goals

Uncle's goal is to provide a methodology for *RTL* specification of complete dual-rail asynchronous systems based on NCL with significant tool assistance provided in generation of the final netlist. The justification is simple; there is currently no readily available toolset that accomplishes this goal. Clocked designers have had support for RTL specification of clocked systems for many years. A well known, mature toolset that also generates NCL-based dual-rail asynchronous systems is Balsa [5][6] (Balsa can also generate other types of dual-rail logic in addition to systems that use encodings other than dual-rail). Balsa has both advantages and disadvantages when compared to Uncle. One significant advantage is that Balsa's input specification (a custom language) can be directly simulated before a gate level implementation is generated. In Uncle, the RTL specification must first be transformed to a gate-level netlist via Uncle's tool flow before it can be simulated. Balsa is a higher level synthesis tool than Uncle in that it generates the control for the user based on the input specification, and also dictates the datapath style (control-driven, to be defined later). Balsa users do specify the registers and datapath operations, so Balsa synthesis is above RTL but below advanced high-level synthesis tools in the clocked world that generate registers/datapath elements to meet a user constraint based on a total number of clock cycles for the target computation

The RTL specification used by Uncle requires the designer to specify both datapath and control (same as in the clocked world), giving the designer more freedom, but also more responsibility. The Uncle flow does perform significant assistance to the user in terms of automated dual-rail expansion and ack network generation, along with performance and area driven optimizations, so it is a non-trival step-up from manual netlisting. The extra freedom (and responsibility) in the Uncle RTL specification means that a knowledgeable designer can perhaps create higher quality designs in terms of cycle times, transistor counts and energy usage than produced by higher level synthesis tool such as Balsa (the author's experience to date is that Uncle generated-netlists can compare favorably in these areas against Balsa designs). Using an RTL specification does mean that a designer will have to work harder to produce those designs than in a higher level synthesis toolset such as Balsa. However, the designer will understand in detail exactly how each register/compute element is used as well as the exact control scheme, since the designer has responsibility for specifying all of those elements. A user of a higher level synthesis tool may never quite understand the magic netlist that is produced by a higher level synthesis toolset, and thus may be at a loss as to how to improve that netlist if there is a shortcoming. The author believes this extra freedom given by an RTL specification is an advantage that Uncle has over Balsa, but understands that others may assert that this is a step backwards. Another viewpoint is that the Uncle RTL specification methodology fills a void for those designers that prefer this level of control over their designs. It should be noted that either approach (RTL or higher-level synthesis) also heavily depends upon the designer's skill and expertise with the language/toolset in terms of producing a quality design.

A naïve designer can produce low-performing designs using either approach. Balsa is a good toolset that offers significant capability to the asynchronous designer, but so does the Uncle toolset, albeit in different ways.

Table 2-1 compares features of both Uncle and Basla as that is another evaluation method for selecting a toolset. The toolset choice becomes easy if a designer requires a feature that is not present in a particular toolset.

|                               | Uncle                             | Balsa                          |

|-------------------------------|-----------------------------------|--------------------------------|

| Input-language spec           | No                                | Yes (custom simulator          |

| simulation                    |                                   | shipped with toolset)          |

| Gate-level netlist simulation | Via external Verilog              | Via external Verilog simulator |

|                               | simulator, and also by internal   |                                |

|                               | simulator that reports cycle time |                                |

|                               | (uses NLDM timing), orphan        |                                |

|                               | detection, and illegal dual-rail  |                                |

|                               | assertions.                       |                                |

| Timing model for simulation   | Internal simulator uses NLDM      | Fixed gate delay               |

|                               | timing (table lookup, input       |                                |

|                               | transition time/output cap load   |                                |

|                               | gives output transition time,     |                                |

|                               | output delay).                    |                                |

| Gate Level Performance        | Automated latch movement          | None                           |

| optimization                  | for data/ack delay balancing      |                                |

|                               | (data-driven style blocks only).  |                                |

|                               | Also, automated net               |                                |

|                               | buffering to meet transition time |                                |

|                               | spec.                             |                                |

| Gate level area optimization  | Relaxation, area-driven           | None                           |

| Control-driven style support  | Yes                               | Yes                            |

| Data-driven style support     | Yes (full support in both         | Limited to half-latches in     |

|                               | linear pipelines and FSMs)        | combinational blocks           |

| Automated generation of       | No                                | Yes                            |

| control                       |                                   |                                |

Table 2-1 Uncle versus Balsa Feature Comparison

#### 2.2 Uncle Flow Overview

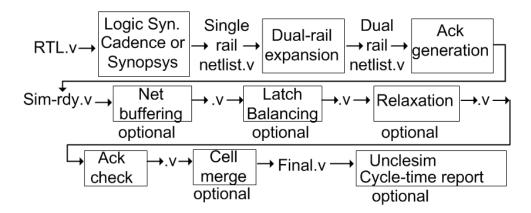

Figure 2-1 shows the Uncle tool flow. The flow is controlled by python scripts that invoke the various tools in the flow. The input RTL is transformed to a gate level netlist using commercial synthesis tools (both Synopsys Design Compiler and Cadence RTL Encounter are supported). The input Verilog RTL file contains a mixture of behavioral and gate-level statements that describes a mixture of combinational and control logic. The gate-level statements are necessary for instantiating elements that support the

asynchronous paradigm and which cannot be inferred from behavioral RTL statements. Parameterized modules are available from an Uncle-provided library and are used to reduce the code footprint of these constructs, reducing the RTL coding burden on the designer.

Figure 2-1 Uncle Synthesis Flow

The target library read by the commercial synthesis tool contains *and2*, *xor2*, *or2*, *inverter*, D-flip-flop (DFF), D-latch (DLAT), and other gates that are either black boxes for special use (such as T-,S- elements, discussed later), or are complex gates that have been mapped to an optimized NCL implementation (i.e., a full adder). These gates have unit delays for timing, and area figures that are relatively proportional to their transistor counts. The single-rail netlist is then expanded to a dual-rail netlist with gates and registers expanded to their actual dual-rail implementations. The ack network is then generated, at which point the gate level netlist is simulation-ready. The steps after this point are optional optimizations and checking. The ack checker is a tool that reverse engineers the ack network to mechanically check its correctness. This is primarily included as a check for coding errors in the ack generation tool when new approaches in ack network generation are tested.

The various components of this flow will be discussed in more detail in later sections of this document.

### 2.3 Dual Rail Combinational Logic in NCL

The asynchronous methodology supported by Uncle is dual-rail, four-phase, with fine-grain gates. The combinational logic in the *single\_rail\_netlist.v* file of Figure 2-1 contains basic two-input gates such as AND2, OR2, XOR2, and INV which are expanded to their dual-rail versions implemented in NCL gates. NCL is used instead of some other style such as DIMS as it produces logic with fewer transistors and lower delays. For example, a dual-rail AND2 (DRAND2) requires 31 transistors implemented in NCL versus 56 transistors in DIMS. Three-input (and higher) basic Boolean gates are not used as their dual-rail expansions are generally not as efficient as the two-input versions ([7] has a good discussion on dual-rail expansion of combinational logic to NCL). The combinational logic also has a few complex gates, such the full-adder and mux2, that have direct NCL implementations that are far more efficient than by representing these gates as primitive two-input gates and then dual-rail expanding these gates. These complex cells are expanded to their NCL implementations during the flow of Figure 2-1. One of the

future goals of the Uncle toolset is to offer better logic synthesis in terms of direct NCL implementation of complex gates rather than using primitive gates that are later expanded to dual-rail logic.

#### A note on the NCL full-adder cell

The NCL full-adder cell [4] is very efficient implementation in terms of transistor count and speed, but it has the property that the carry-out (CO) is not input-complete (its t/f rails do not depend on all of the t/f rails of the A, B, CI inputs). However, as long as the CO is used as the carry-input (CI) of another full-adder cell, input completeness of the sum bits are preserved. This means that if you want to use the most-significant carry-out of a ripple-chain, then you need to use XOR3 gating in order to have an input complete output. Sometimes, the Synopsys/Cadence synthesis tools will use a full-adder cell as an XOR3 gate (only the CO output is used, the SUM output is unconnected). During the mapping process, Uncle detects this condition and replaces the full-adder with a dual-rail XOR3.

### 2.4 Data-driven vs. Control-driven Design Styles

A complete digital system also needs registers and a sequencing mechanism in addition to combinational logic. Uncle supports two distinct design styles for registers/control: data-driven and control-driven (i.e., Balsa-style). These terms are more fully defined in the following sections, but some guidelines on the usage of these styles are given here as this is a basic choice that a designer must make before implementing their module (or sub-module within a larger design).

- The data-driven style is the best choice in terms of performance for linear pipelines. For transistor count/energy, the better choice (data-driven/control-driven) is design dependent.

- The data-driven style is generally the best choice in terms of performance for a block that has feedback (i.e. accumulators, finite state machine) if ALL registers, ALL ports are read/written each compute cycle. This assumes that the block is performance-optimized using the automated delay balancing tool available in the tool flow. If minimal energy/transistor count is required, then the control-driven style is generally better.

- The control-driven style is the better choice in terms of transistor count/energy for blocks that have registers with conditional read/writes, and/or ports with conditional activity. It can also be better in performance than the data-driven implementation, but it depends on the block.

Uncle supports designs that mix sub-modules that use different styles (the Viterbi example in the \$UNCLE/designs/ directory is an example of this). The data-driven style currently has more support in the Uncle flow in terms of optimizations because the first version of Uncle only supported this style, but it is envisioned that future versions of Uncle will also support a variety of optimizations for the control-driven style.

### 2.5 Data-driven Control and Registers

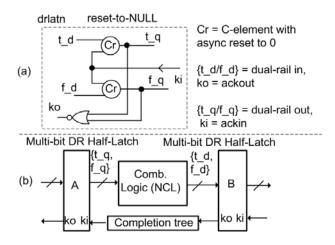

Figure 2-2a shows a data-driven dual-rail half-latch (the term half-latch is used because in a FIFO arrangement, two of these are required for each bit stored in the FIFO). In this system, the acknowledge signals *ki*, *ko* are at logic 1 when the data rails are at NULL. Because of this, an asynchronous reset signal is required in the C-element to force its output to NULL during system reset. This is a reset-to-NULL half-

latch as both outputs are reset to 0 during a system reset. In Uncle, a dual rail signal has  $t_f$  prefixes for true/false rails, respectively. The transistor level implementation of the half-latch used in Uncle is somewhat different from that shown in Figure 2-2a in that it isolates the  $t_f/f_g$  output loads from ko signal generation. It does this by using internal signals taken before the final inverter stage in the C-gates as inputs to an AND2 gate that then drives the ko output load. This costs four more transistors (34 transistors versus 30 transistors for the design of Figure 2-2a) but produces a faster ko path when  $t_g/f_g$  are loaded.

Figure 2-2 Data-driven Half-latch

Figure 2-2b shows how the acknowledge signals are used to control data transfer between two of these half-latches in the familiar micro pipeline arrangement. The ackin (*ki*) of a bit in latch A is tied to the output of a C-element completion tree whose inputs are the B-latch ackouts (*ko*) of all the destinations of that bit. The data sequencing between bits in the registers is controlled by arrival of data waves, NULL waves at the half-latch and by the ack network.

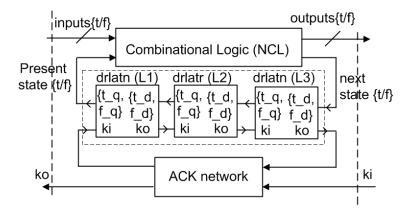

A finite state machine with feedback requires a different form of latch element. If the C-element of Figure 2-2a that drives the  $t_q$  output is replaced with a C-element that resets to 1, then this becomes a reset-to-DATA1 (drlats) half-latch (the latch outputs have a dual-rail DATA1 at system reset). Conversely, a reset-to-DATA0 (drlatr) half-latch is formed by replacing the C-element driving the  $f_q$  output with a C-element that resets to 1. Figure 2-3 shows a finite state machine implementation with state registers implemented as three half-latches, with the middle half-latch containing initial data. This forms a three half-latch ring which is the minimum required for data cycling [4], and the initial data in the middle half-latch is required in order to insert a data token on this loop. This register type is expensive in terms of transistors (and associated energy), requiring 3\*34 = 102 transistors per bit. This register type is termed a dual-rail data-driven register in this document.

Figure 2-3 Finite State Machine

This document refers to a system using this style of registers/control as data-driven, since there is no separate control network other than the ack network. In this data-driven style, all ports and all registers are read and written every compute cycle (port/register activity can be further restricted in a data-driven design, but requires extra effort in terms of additional gates; examples are given later in this document).

### 2.6 Control-driven Control and Registers

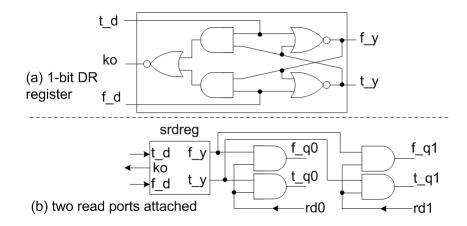

Conversely, this paper refers to a *control-driven* system as one that has registers with selective read/writes and a control network that is separate from the datapath such as that implemented by Balsa. Figure 2-4a shows a dual-rail register based on an SR-latch (this register has a low-true *ko*; Balsa uses a register with high-true *ko*). Any number of read ports can be easily added to the register by placing AND2 gates on the dual-rail outputs, with each port enabled by a single-rail control signal as shown in Figure 2-4b. A write operation is triggered by data arrival, while a read is triggered by assertion of the associated read line with a port. This provides a selective read/write control capability for the register. With one readport, the register in Figure 2-4a requires only 28 transistors per bit, compared with the 102 registers per bit of the register in Figure 2-3 or the 34 transistors per bit for the half-latch of Figure 2-2a. Generally, control-driven designs will have lower transistor counts and lower energy than data-driven designs. Note that the register of Figure 2-2a has no initialization capability; Uncle provides reset-to-0 and reset-to-1 versions as well.

Figure 2-4 Dual-rail register based on an SR latch.

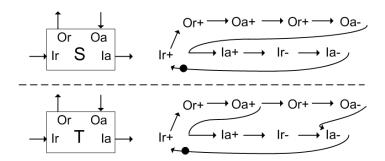

Balsa uses handshaking modules known as S-elements and T-elements [9] to implement the separate control channel for control-driven transfers. These elements have elegant implementations that are small and fast; the signal transition graphs for these two elements are shown in Figure 2-5. Typical use is to connect a chain of these elements to form a sequencer, with the *la* output of one element connected to the *lr* input of the next element. The *Or* output is typically used to trigger a read on one or more registers, with the *Oa* input connected to the output of the ack network for the destination registers. The T-element offers more concurrency than the S-element as it asserts *la+* (starts next sequencer element) when *Oa+* occurs, thus beginning the next datapath action while the current datapath action is returning to NULL. Balsa uses clever configurations of these elements with additional gating to accomplish various control structures such a *loop-while*, *if-else*, etc. Example usage of these elements in Uncle designs are provided later in this document.

Figure 2-5 S-element, T-element STGs.

## 3 Data-driven Examples

This section gives examples of data-driven designs; all examples are available in the *designs/* subdirectory of the Uncle distribution.

#### 3.1 RTL Constructs

All behavorial RTL examples in this document are given in Verilog. The native Uncle tools themselves can only parse Verilog gate-level netlists (named port association only), and rely on a commercial synthesis tool such Synopsys Design Compiler or Cadence RTL Compiler to synthesize behavioral RTL to the gate-level netlist that enters the Uncle tool flow. You could also use VHDL as the initial RTL, as long as the final gate netlist was in Verilog. Regression test examples in the Uncle toolset are all in Verilog RTL, and the majority have been tested with both Synopsys and Cadence.

Combinational logic in Uncle designs are specified using standard Verilog constructs. For arithmetic blocks, RTL operators such as '+', '<' etc. can be used, but Uncle examples often used parameterized modules that directly instantiate complex gates such as a full-adder to give full control over the structure used for the arithmetic operator instead of relying on the synthesis tool's choice. An important file in the Uncle distribution is:

\$UNCLE/mapping/tech/models/verilog/src/gatelib/parm\_modules.v

This file contains numerous parameterized macros that are used in several examples. This file is only used for synthesis purposes, and is automatically read by the scripts used for Synopsys/Cadence synthesis. We will point out the use of these macros as the examples are discussed.

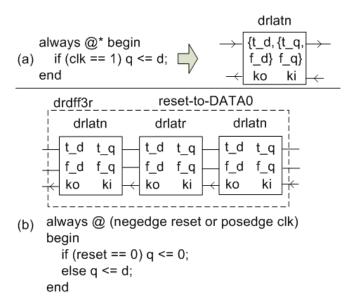

Figure 3-1a shows how to infer a half-latch from a behavioral Verilog statement. The behavioral Verilog generates a D-latch in the single-rail gate-level netlist, which is transformed during the mapping process into a dual rail half latch (a *drlatn* cell, which is a reset-to-NULL half-latch). Note that a clock signal needs to be present in the module's interface in order to infer this latch; this signal is dropped during the mapping process. Figure 3-1b shows how to infer a DATAO register from a behavioral Verilog statement. This infers a DFF (D-flip-flop) with a low-true reset in the single-rail gate-level netlist, which is transformed to the three half-latch structure (data-driven register) during the mapping process. Note that the middle latch is a reset-to-DATAO half-latch. If the statement q<=0 is replaced with q<=1 then the middle half-latch becomes a reset-to-DATA1 half-latch. If the always block of Figure 3-1b is modified to drop the asynchronous reset, then the DFF that is generated in the single rail netlist will not have a reset input. However, this DFF will still be mapped to the structure of Figure 3-1b during dual-rail expansion and a default reset input added, as all data-driven registers are assumed to have initial data.

Figure 3-1 Data-driven half-latch/register inference from RTL.

#### 3.2 RTL Restrictions

There are a few restrictions on the RTL that can be used for Uncle designs:

- Clock signal: For the flattened top-level module, all input to output paths must go through at least a half-latch; there can be no combinational-through paths. This also implies that in a data-driven design, the top-level design must have a clock signal in order to infer DFFs/D-latches. A control-driven design does not require a clock signal as these registers are manually instantiated by the user. There can be no gating logic on the clock signal.

- Asynchronous reset: An asynchronous reset line is not required in a data-driven netlist but all final NCL netlists will have one, so a low-true asynchronous reset with a default name is generated if one is not specified. Control-driven RTL is required to have a low-true asynchronous reset at the top-level module as one of the required gates needs this input. There can be no gating other than buffers/inverters on the asynchronous reset, and the asynchronous reset can only be used as the reset for DFFs or latches, and not in general logic. Buffering to meet a user-specified transition constraint is added to the asynchronous reset network during the mapping process; this is discussed later.

## 3.3 First example: *clk\_up\_counter.v* to *ncl\_up\_counter.v* walkthrough

The first example is *clk\_up\_counter.v* and is found in:

\$UNCLE/designs/regress/syn/rtl/clk up counter.v

Uncle's example directory structure uses the convention that commercial synthesis is done in the *syn*/ directory, NCL netlist mapping in the *map*/ directory, and Verilog simulation in the *sim*/ directory. For the rest of this example, many directory references are relative to \$UNCLE/designs/regress/.

The Verilog code is shown in (this example was grabbed off the web from a popular Verilog tutorial site). It is a standard up counter with an asynchronous low-true *reset*, and synchronous *enable*, *clr* signals.

```

☐ module clk_up_counter

1

2

, // Output of the counter

3

enable , // enable for counter

, // clock Input

4

clk

5

clr

, //synchronous clear

// asynchronous clear

6

reset

L);

7

8

//-----Output Ports-----

9

output [7:0] out;

10

//-----Input Ports-----

input enable, clk, reset,clr;

//-----Internal Variables-----

12

13

reg [7:0] out;

//-----Code Starts Here-----

14

15

16

□always @(posedge clk or negedge reset) begin

17

☐ if (reset == 0) begin

18

out <= 8'b0;

19

end else begin

20

if (clr) begin

21

22

out <= 8'b0;

23

end else if (enable) begin

24

out <= out + 1;

25

end

26

end

27

L end

endmodule

28

29

```

Figure 3-2 clk\_up\_counter.v RTL

The author's naming conventions for examples tends to stray somewhat, but generally 'clk\_', 'clkspec\_' or no prefix is used on input RTL, with 'ncl\_' or 'uncle\_' prefix used for verilog files that result from the mapping process. In this particular case, you can simulate this clocked RTL and you will get the same inputs/outputs on a compute cycle basis as you will get from the mapped NCL netlist. So this is a case where the input RTL can be simulated before mapping. However, for many other examples (including all of the control-driven style examples), this will not be possible. The top-level module name has to match the name of the input file without the .v extension.

To run the complete synthesis/mapping process for this example, execute the following command in the *\$UNCLE/designs/regress* directory (this assumes that Cadence RTL Encounter and the Cadence Verilog simulator is on your path):

python doregress.py up\_counter cadence default.ini -syntool cadence

This runs the complete flow including a regression test simulation. However, the design is typically created in three major steps: a) RTL-to-single-rail netlist synthesis, b) single-rail netlist to NCL netlist mapping, c) simulation of the NCL netlist. This corresponds to the *syn/*, *map/*, and *sim/* subdirectories under the *\$UNCLE/designs/regress* directory. The rest of this section discusses how to run these separate steps (more information on the regression script can be found in the appendix).

#### RTL Synthesis to gate-level single-rail netlist

To perform the RTL-to-single-rail netlist synthesis, change to the \$UNCLE/designs/regress/syn directory and execute the command:

```

synrc_design.py default_cadence.template %TOP%=clk_up_counter

```

This synthesizes the *syn/rtl/clk\_up\_counter.v* file to a gate-level netlist stored in file *syn/andor2\_rc/clk\_up\_counter.v* using Cadence RTL Encounter. This file is shown in Figure 3-3; observe that the combinational gates are primitive two-input gates.

The default cadence.template file is a synthesis template script that synthesizes for a minimum area contained \$UNCLE/mapping/tech/cadence constraint and is in the directory. mindelay cadence.template file synthesizes for a minimum delay constraint and may result in a faster design for designs with complex combinational blocks (or it may not, since longest path delays in asynchronous dual-rail netlists can be data-dependent, and furthermore, the gate-delays specified in the .lib file used for synthesis only contains unit-delays. This is an area that needs further improvement). A current limitation is that the *mindelay cadence.template* file can only be used for data-driven designs and not for control-driven designs because how the script is written to look for dff/Dlatch-to-dff/Dlatch paths (this restriction will be removed in a future release).

Use the following command if you wish to use Synopsys dc\_shell for synthesis:

```

syndc design.py default synopsys.template %TOP%=clk up counter

```

The resulting gate-level netlist is placed in the syn/andor2\_dc/clk\_up\_counter.v file.

```

module clk_up_counter(out, enable, clk, clr, reset);

input enable, clk, clr, reset;

5

6

output [7:0] out;

7

wire enable, clk, clr, reset;

8

wire [7:0] out;

9

wire logic_1_1_net, n_1, n_2, n_4, n_5, n_8, n_10, n_12;

wire n_14, n_17, n_18, n_19, n_22, n_25, n_26, n_27;

10

11

wire n_29, n_42, n_43, n_44, n_45, n_46, n_47, n_48;

12

wire n_49, n_50, n_51, n_52, n_53, n_54, n_55;

dffsr \out_reg[7] (.rb (reset), .sb (logic_1_1_net), .ck (clk), .d(n_29), .q (out[7]));

dffsr \out_reg[6] (.rb (reset), .sb (logic_1_1_net), .ck (clk), .d(n_27), .q (out[6]));

13

14

15

and2 g129(.a (n_43), .b (n_26), .y (n_29));

16

dffsr \out_reg[5] (.rb (reset), .sb (logic_1_1_net), .ck (clk), .d(n_25), .q (out[5]));

and2 g131(.a (n_45), .b (n_26), .y (n_27));

17

dffsr \setminus out\_reg[4] \ (.rb \ (reset), \ .sb \ (logic\_1\_1\_net), \ .ck \ (clk), \ .d(n\_22), \ .q \ (out[4]));

18

and2 g134(.a (n_47), .b (n_26), .y (n_25));

19

20

and2 g137(.a (n_49), .b (n_26), .y (n_22));

21

dffsr \out_reg[3] (.rb (reset), .sb (logic_1_1_net), .ck (clk), .d(n_17), .q (out[3]));

22

and2 g145(.a (n_18), .b (out[6]), .y (n_19));

\label{logic_1_1_net} $$ dffsr \operatorname{\out_reg[2] (.rb (reset), .sb (logic_1_1_net), .ck (clk), .d(n_14), .q (out[2])); $$ $$ dffsr \operatorname{\out_reg[2] (.rb (reset), .sb (logic_1_1_net), .ck (clk), .d(n_14), .q (out[2])); $$ $$ $$ dffsr \operatorname{\out_reg[2] (.rb (reset), .sb (logic_1_1_net), .ck (clk), .d(n_14), .q (out[2])); $$ $$ $$ $$ dffsr \operatorname{\out_reg[2] (.rb (reset), .sb (logic_1_1_net), .ck (clk), .d(n_14), .q (out[2])); $$ $$ $$ dffsr \operatorname{\out_reg[2] (.rb (reset), .sb (logic_1_1_net), .ck (clk), .d(n_14), .q (out[2])); $$ $$ $$ dffsr \operatorname{\out_reg[2] (.rb (reset), .sb (logic_1_1_net), .ck (clk), .d(n_14), .q (out[2])); $$ $$ $$ dffsr \operatorname{\out_reg[2] (.rb (reset), .sb (logic_1_1_net), .ck (clk), .d(n_14), .q (out[2])); $$ $$ $$ dffsr \operatorname{\out_reg[2] (.rb (reset), .sb (logic_1_1_net), .ck (clk), .d(n_14), .q (out[2])); $$ $$ $$ dffsr \operatorname{\out_reg[2] (.rb (reset), .sb (logic_1_1_net), .ck (clk), .d(n_14), .d (out[2])); $$ $$ $$ dffsr \operatorname{\out_reg[2] (.rb (reset), .sb (logic_1_1_net), .ck (clk), .d (out[2])); $$ $$ dffsr \operatorname{\out_reg[2] (.rb (reset), .sb (logic_1_1_net), .ck (clk), .d (out[2])); $$ $$ $$ dffsr \operatorname{\out_reg[2] (.rb (reset), .sb (logic_1_1_net), .ck (clk), .d (out[2])); $$ $$ dffsr \operatorname{\out_reg[2] (.rb (reset), .sb (logic_1_1_net), .d (out[2])); $$ $$ dffsr \operatorname\out_reg[2] (.rb (reset), .sb (logic_1_1_net), .d (out[2])); $$ $$ dffsr \out_reg[2] (.rb (reset), .sb (logic_1_1_net), .d (out[2])); $$ $$ dffsr \out_reg[2] (.rb (reset), .sb (logic_1_1_net), .d (out[2]), .d (out[2])); $$ $$ dffsr \out_reg[2] (.rb (reset), .sb (logic_1_1_net), .d (out[2]), .d (out[2])); $$ $$ dffsr \out_reg[2] (.rb (reset), .sb (logic_1_1_net), .d (out[2]), .d (o

23

24

and2 g141(.a (n_51), .b (n_26), .y (n_17));

and2 g146(.a (n_53), .b (n_26), .y (n_14));

25

26

dffsr \out_reg[1] (.rb (reset), .sb (logic_1_1_net), .ck (clk), .d(n_10), .q (out[1]));

27

and2 g150(.a (n_12), .b (out[5]), .y (n_18));

and2 g151(.a (n_55), .b (n_26), .y (n_10));

28

29

and2 g154(.a (n_8), .b (out[4]), .y (n_12));

dffsr \out_reg[0] (.rb (reset), .sb (logic_1_1_net), .ck (clk), .d(n_4), .q (out[0]));

31

and2 g158(.a (n_5), .b (out[3]), .y (n_8));

32

and2 g159(.a (n_1), .b (n_26), .y (n_4));

33

and2 g161(.a (n_2), .b (out[2]), .y (n_5));

34

xor2 g162(.a (out[0]), .b (enable), .y (n_1));

and2 g164(.a (out[0]), .b (out[1]), .y (n_2));

35

inv g165(.a (clr), .y (n_26));

36

xor2 g2(.a (n_42), .b (out[7]), .y (n_43));

37

38

and2 g3(.a (enable), .b (n_19), .y (n_42));

xor2 g174(.a (n_44), .b (out[6]), .y (n_45));

39

40

and2 g175(.a (enable), .b (n_18), .y (n_44));

41

xor2 g176(.a (n_46), .b (out[5]), .y (n_47));

42

and2 g177(.a (enable), .b (n_12), .y (n_46));

43

xor2 g178(.a (n_48), .b (out[4]), .y (n_49));

44

and2 g179(.a (enable), .b (n_8), .y (n_48));

45

xor2 g180(.a (n_50), .b (out[3]), .y (n_51));

46

and2 g181(.a (enable), .b (n_5), .y (n_50));

47

xor2 g182(.a (n_52), .b (out[2]), .y (n_53));

and2 g183(.a (enable), .b (n_2), .y (n_52));

49

xor2 g184(.a (n_54), .b (out[1]), .y (n_55));

50

and2 g185(.a (enable), .b (out[0]), .y (n_54));

51

logic_1 tie_1_cell(.y (logic_1_1_net));

endmodule

```

Figure 3-3 clk\_up\_counter.v single-rail netlist

#### Gate-level single-rail netlist to NCL netlist mapping

For NCL mapping, first copy the *syn/andor2\_rc/clk\_up\_counter.v* netlist to the *map/* directory. Then, edit the *clk\_up\_counter.v* file and change the module name from *clk\_up\_counter* to *ncl\_up\_counter*. This is needed as this module name is passed to the Uncle tool as the top-level module, and it also forms the basis for the output file name. If you do many of these designs, you will probably write a script to automate this step to your personal preferences (as is done automatically during the *doregress.py* regression script). **CHANGE version 2.6**: With version 2.6 and later, it is no longer necessary to edit the Verilog file and manually change the module name – the top module name of the Uncle Verilog file will be the second argument passed on the Uncle command line.

Execute the following command in the map/directory to map the netlist to an NCL netlist:

#### uncle clk\_up\_counter.v ncl\_up\_counter default.ini

After many lines of status output is produced, the NCL netlist is written to <code>ncl\_up\_counter.v</code>. The <code>uncle</code> command is a python script that expects three arguments: 1) input file name, 2) top module name, and 3) options file. The <code>default.ini</code> file is an options file the executes the default flow (see the chapter on technology files for an explanation of some of the options in a <code>.ini</code> file, these reside in the <code>\$UNCLE/mapping/tech</code> directory). The only performance optimization in the default flow is a net-buffering step, that buffers heavily loaded nets to meet a global transition time constraint (see the net-buffering section later in this document). The only area optimization performed in the default flow is a cell merging step that merges adjacent cells with no fanout to more complex gates.

During the mapping process, several intermediate netlists are produced in the *tmp/* subdirectory. Some of these files are (the entire *tmp/* directory can be deleted after mapping if desired):

- modname\_dr0.v after dual-rail expansion.

- modname\_dr1.v after inverter removal (inverters are replaced by assignment statements that swap the rails).

- modname dr2.v after netlist flattening of dual-rail gates to threshold gates.

- modname\_safe0.v after ack network generation. This is a complete NCL implementation, and

is a good file to use for detailed debugging as the DFFs have not yet been flattened to three halflatch implementations, and so there are fewer signals to deal with. Also, simulate this file if you

suspect a problem due to either relaxation or merging.

- modname\_safe1.v DFFs flattened to half-latch implementations.

- *modname*\_nbuf0.v the netlist after net buffering has been done.

- modname merge1.v after gate merging this can cause nets to be deleted.

- modname\_cleanup0.v a cleaned up version of the netlist with dead gates removed. This is the

netlist that is used by the acknetwork checker that checks for structural correctness of the ack

network.

- modname.v This is the final netlist, and is written to the current directory. This netlist has been cleaned of all verilog attributes that have been added during various stages of the transformation process.

Files produced in the current working directory other than the final netlist of modname.v are:

- modname\_stats.txt netlist statistics at the various transformation stages (the only one that

you are generally interested in is the total\_area statistic at the end of the file that is the total

number of transistors, and the output\_cycle\_average\_time if the uncle\_sim tool has been run).

- modname\_acks.txt information on the acknowledgement networks that are generated, useful

if your final netlist does not cycle and you are trying to debug it.

A portion of the  $ncl\_up\_counter.v$  netlist is shown in Figure 3-4. Note that the port names now have ' $t\_$ ' and ' $f\_$ ' as prefixes except for the asynchronous reset, and new ports named ackout, ackin have been added. Any gates with cqateN instance names are part of the ack network. Any gates with instance

names of *cmrg\_N* names have been merged by the cell merger. Any gates with instance names of *buffcomp\_N* names have been added during net buffering.

```

//The Netlist from Uncle

module ncl_up_counter ( t_out , f_out , t_enable , f_enable , t_clr , f_clr , reset , ackout , ackin );

output ackout;

5

input reset :

input f_clr

input t_clr

input f_enable ;

9

input t enable ;

10

output [7:0] f_out ;

11

output [7:0] t_out ;

12

13

assign ackout = acknet14;

assign f_n_26 = t_clr;

14

15

assign t_n_26 = f_clr ;

16

th22x4 cgate7 (.a ( ackin ) , .b ( acknet14 ) , .y ( acknet15 ));

17

th22 cgate6 (.a ( acknet13 ) , .b ( acknet12 ) , .y ( acknet14 ));

th44 cgate5 (.a (acknet2), .b (acknet6), .c (acknet3), .d (acknet7), .y (acknet13)); th44 cgate4 (.a (acknet4), .b (acknet1), .c (acknet5), .d (acknet0), .y (acknet12));

18

19

thand0 g185_U (.y ( f_n_54 ) , .d ( t_out[0] ) , .c ( bufnet_0 ) , .b ( f_out[0] ) , .a ( bufnet_2 )); th22 g185_U_0 (.y ( t_n_54 ) , .b ( t_out[0] ) , .a ( bufnet_0 ));

20

21

th24comp g184_U (.y (t_n_55), .d (f_n_54), .c (f_out[1]), .b (t_out[1]), .a (t_n_54));

th24comp g184_U 0 (.y (f_n_55), .d (f_n_54), .c (t_out[1]), .b (f_out[1]), .a (t_n_54));

thand0 g183_U (.y (f_n_52), .d (t_n_2), .c (bufnet_0), .b (f_n_2), .a (bufnet_2));

th22 g183_U 0 (.y (t_n_52), .b (t_n_2), .a (bufnet_0));

22

23

24

25

th24comp g182 U (.y ( t_n 53 ) , .d ( f_n 52 ) , .c ( f_o out[2] ) , .b ( t_o out[2] ) , .a ( t_n 52 )); th24comp g182 U (.y ( f_n 53 ) , .d ( f_n 52 ) , .c ( t_o out[2] ) , .b ( f_o out[2] ) , .a ( t_n 52 )); thand0 g181 U (.y ( f_n 50 ) , .d ( t_n 5 ) , .c ( bufnet 0 ) , .b ( f_n 5 ) , .a ( bufnet 2 )); th22 g181 U 0 (.y ( t_n 50 ) , .b ( t_n 5 ) , .a ( bufnet 0 ));

26

27

28

29

th24comp g180_U (.y ( t_n_51 ) , .d ( f_n_50 ) , .c ( f_out[3] ) , .b ( t_out[3] ) , .a ( t_n_50 )); th24comp g180_U (.y ( f_n_51 ) , .d ( f_n_50 ) , .c ( t_out[3] ) , .b ( f_out[3] ) , .a ( t_n_50 )); thand0 g179_U (.y ( f_n_48 ) , .d ( t_n_8 ) , .c ( bufnet_0 ) , .b ( f_n_8 ) , .a ( bufnet_2 )); th22 g179_U 0 (.y ( t_n_48 ) , .b ( t_n_8 ) , .a ( bufnet_0 )); th24comp g178_U (.y ( t_n_49 ) , .d ( f_n_48 ) , .c ( f_out[4] ) , .b ( t_out[4] ) , .a ( t_n_48 ));

30

31

32

33

```

Figure 3-4 Part of ncl\_up\_counter.v

#### NCL netlist simulation using uncle sim

Before using an external Verilog simulator to verify the netlist, you can use the internal Uncle simulator to do some basic checking (this is done in the regression test). Execute the following command line to apply random inputs for 100 output cycles:

```

uncle_sim ncl_up_counter.v default.ini -top ncl_up_counter -maxcycles 100

Stats given at the end of this simulation is (time is in picoseconds):

```

```

Finish time: 534076, Number of data output cycles: 100, Average output cycle time: 5340, Transitions per cycle: 179, Switched capacitance per cycle: 3.658548e-13,

```

By default, the internal simulator reads NLDM characterization information from the file (this file specified by an option in the *default.ini* file):

```

$UNCLE/mapping/tech/timing65nm.def

```

This timing characterization data was produced from pre-layout transistor-level gate models using Cadence Ultrasim, with transistor models from a commercial 65nm process. Transistor-level simulations using Cadence Ultrasim of the final NCL netlists have shown about a 5% agreement with predicted cycle

time. The Uncle simulator is an event-driven simulator that supports '0', '1', and 'X' values. The simulator uses the *function* property in the Uncle cell definition files for evaluating generic Boolean and NCL combinational gates. Special purpose gates such the mutex and various register cells have custom models built into the simulator, with the *ncl\_func* cell property used to identify the type of cell to the simulator.

The Uncle simulator also reports three unusual/failure conditions (a waveform file named module\_name.vcd is produced by the simulator and can be viewed by the freely-available Linux tool gtkwave to help debug these conditions):

- Failure to cycle: An error is reported if the netlist fails to cycle. This can either be due to designer error in the original RTL or because of incorrect netlist generation due to a tool error. See the debugging chapter for hints on debugging dead netlists.

- 'X' values after reset: Unclesim holds reset asserted with primary inputs at NULL until the netlist is settled, then releases reset and either applies random inputs or user-specified stimulus. An error is reported and the simulator is exited if any 'X' (unknown) values are detected on gate outputs once reset is settled. Check the .vcd waveform file to determine the cause of these 'X' nets.

- Orphan or glitch detected: This is a warning, and means that a net transition that fanned out to at least one NCL gate did not cause a corresponding transition in at least one of the fanout gates. In general, the dual-rail expansion methodology used in Uncle does not cause gate orphans in combinational logic, and the ack generation strives to not generate gate orphans. Long chains of gate orphans may cause timing problems in NCL. It is possible that something the designer has done using demux or merge gates can cause orphans. Orphans are an unusual condition, and should be checked by the designer. The —ignore\_orphan netname option can be specified to the simulator to specifically ignore orphans that the design knows are 'safe'. Generally speaking, the netlists produced by Uncle should be orphan free. Obviously, the orphan/glitch detection is only valid for the random vectors produced during the simulation run, and does not guarantee that your design is orphan-free for all possible input vectors. Note: some definitions of the term gate orphan use a timing constraint that do not report orphaned signal transitions unless they have the potential to cause a logic error by persisting long enough so that it collides with the next data wave. The Uncle simulator does not do any timing analysis for the orphan/glitches that are reported.

- Simultaneous assertion of dual-rail nets: This indicates that both rails of a dual-rail net have been simultaneously asserted, and always indicates some serious error with the netlist. This condition should never occur, and indicates either a tool error during the mapping process, or a designer error in the original RTL. These should always be investigated.

The uncle simulator can also read external vector files instead of using random vectors; look at the file:

\$UNCLE/design/regress/map/gcdsimple.vecs

for an example of the input format, and the regression test labeled as <code>gcdsimple\_t2</code> in the <code>\$UNCLE/design/regress/doregress.py</code> file for command line options needed for <code>uncle\_sim</code>. Because the input vector format is a primitive one, it is best to have the external verilog simulator testbench produce this file during its testing, as the following Verilog testbench does:

\$UNCLE/design/regress/sim/src/uncle\_gcdsimple/tb\_uncle\_gcdsimple.v

#### NCL netlist simulation using an external Verilog simulator

An external verilog simulator is required to fully test the NCL gate level design. The regression tests in the distribution have Makefiles that are compatible with Synopsys, Cadence, and Mentor (*modelsim*) simulators. The gate-level models are in \$UNCLE/mapping/tech/models/verilog/src/gatelib and use unit delays (the Uncle simulator with its NLDM timing model is intended for more accurate prediction of netlist performance).

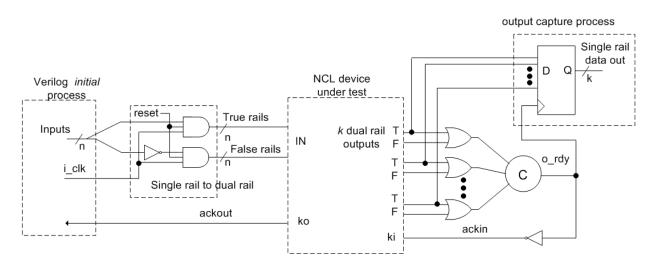

During mapping, a skeleton testbench file is also created named tb\_modname.v (i.e.,  $tb_ncl_up_counter.v$ ). The testbench structure is shown in Figure 3-5. All input vectors are supplied as single-rail vectors using the original single-rail port names via code placed in the *initial* process; a helper process translates these to dual-rail signals. A helper task named  $ncl_clk$  is used to assert  $i_clk$  to apply the data wave, waits for the falling edge of ackout that indicates the data wave was consumed, negates  $i_clk$  to apply the null wave, and then waits for the rising edge of ackout that indicates the NCL block is ready for new data.

Figure 3-5 NCL Testbench structure

A snippet of Verilog testbench code for the initial process is shown in Figure 3-6. Lines 40-45 initialize input signals and applies reset. Lines 49-53 is a loop that enables the counter, and then lets the counter count for 511 data/null waves. Lines 53-56 disables the counters for a few data/null waves, and then lines 57-58 clears the counter.

```

38

initial begin

39

//add user code here

40

i clk = 0;

41

enable = 0;

42

clr = 0;

43

state reached = 0;

44

reset = 1; //low true

45

#100 reset = 0; //assert async reset

#100 reset = 1; //negate async reset

46

47

48

//at this point, data is ready

49

enable = 1;

for (i=0; i < 511; i = i + 1) begin

50

ncl_clk;

51

52

end

53

enable = 0;

54

ncl clk; //hold

55

ncl clk;

ncl clk;

56

57

clr = 1;

ncl clk;

58

```

Figure 3-6 Part of the initial process.

Figure 3-7 shows a portion of the output capture process that captures the true rails of the output once they are ready and prints the value to the console.

Figure 3-7 Testbench output capture/display.

Simulation is done in the *sim/src* directory. Once the *map/ncl\_up\_counter.v* file is produced, copy it to the *sim/src/ncl\_up\_counter* directory (this directory already contains the fleshed-out testbench just discussed). Compile the *ncl\_up\_counter* directory by executing:

```

gmake -f ncl_up_counter/Makefile TOOLSET=simchoice

```

where *simchoice* is either *qhdl* (Mentor modelsim), *cadence* (Cadence/ncsim) or *synopsys* (Synopsys/vcs). To simulate, execute:

```

gmake -f ncl_up_counter/Makefile TOOLSET=simchoice dosim

```

The *dosim* target in the *Makefile* runs the simulation in batch mode for the default *SIMTIME* specified in the *Makefile*, with simulator output logged to *sim/src/ncl\_up\_counter/sim.log*.

A portion of the simulator output is shown in Figure 3-8. The counter is enabled for lines 535-540, held in lines 541-544, cleared 545-547 (*clr* takes precedence), and enabled in lines 548-551.

```

535

# Time:

13335/ enable=1 clr=0 out=11111001

# Time:

536

13361/ enable=1 clr=0 out=11111010

537

# Time:

13387/ enable=1 clr=0 out=11111011

# Time:

538

13413/ enable=1 clr=0 out=111111100

# Time:

539

13439/ enable=1 clr=0 out=111111101

540

# Time:

13465/ enable=1 clr=0 out=11111110

541

# Time:

13491/ enable=0 clr=0 out=11111111

542

# Time:

13519/ enable=0 clr=0 out=11111111

# Time:

543

13547/ enable=0 clr=0 out=11111111

544

# Time:

13575/ enable=0 clr=1 out=11111111

545

# Time:

13601/ enable=0 clr=1 out=00000000

546

# Time:

13627/ enable=1 clr=1 out=00000000

547

# Time:

13653/ enable=1 clr=1 out=00000000

548

# Time:

13679/ enable=1 clr=0 out=00000000

549

# Time:

13705/ enable=1 clr=0 out=00000001

# Time:

13731/ enable=1 clr=0 out=00000010

550

# Time:

13757/ enable=1 clr=0 out=00000011

551

```

Figure 3-8 A portion of the simulator output.

### 3.4 Second Example: GCD16 (clkspec\_gcdsimple.v)

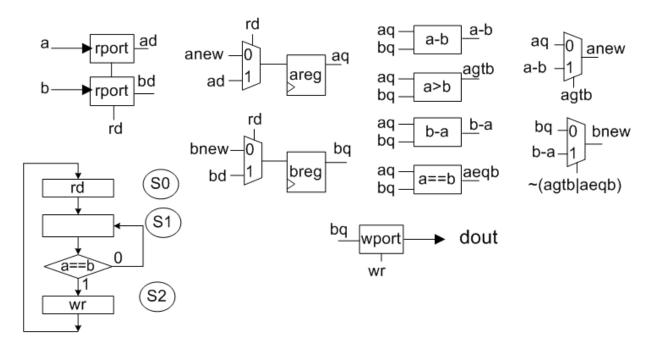

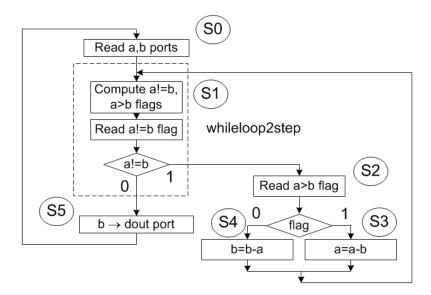

The file \$UNCLE/designs/regress/syn/rtl/clkspec\_gcdsimple.v implements the GCD algorithm shown in Figure 3-9 using 16-bit values.

```

1 def gcd (a,b):

2 while (a != b):

3 if (a > b):

4 a = a - b

6 b else:

6 b = b - a

7 return b

```

Figure 3-9 GCD using successive subtraction.

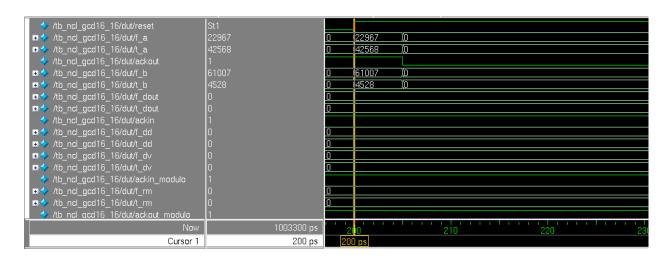

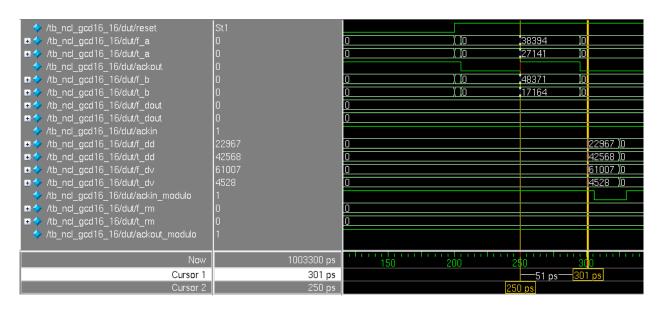

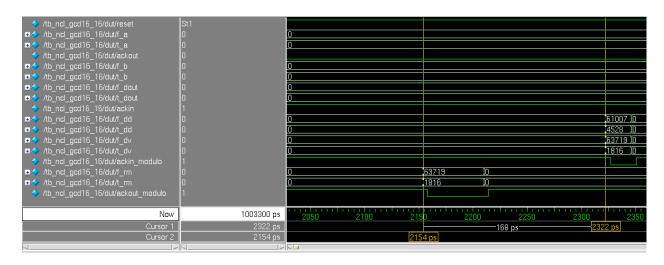

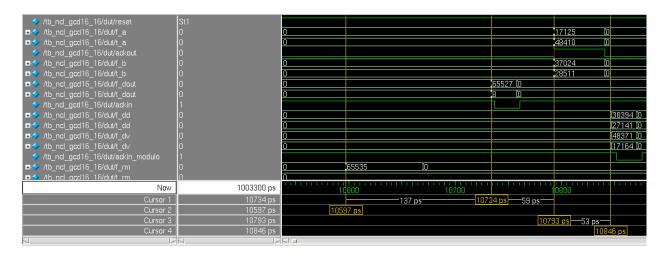

Two different regression tests are available in \$UNCLE/designs/regress/doregress.py for this design using the command lines shown below executed from the \$UNCLE/designs/regress directory (these command lines omit the synthesis step). The <code>gcdsimple\_t1</code> test runs Unclesim with random vectors, while the <code>gcdsimple\_t2</code> runs runs Unclesim with a user specified vector file.

```

python doregress.py gcdsimple_t1 cadence default.ini

python doregress.py gcdsimple_t2 cadence default.ini

```

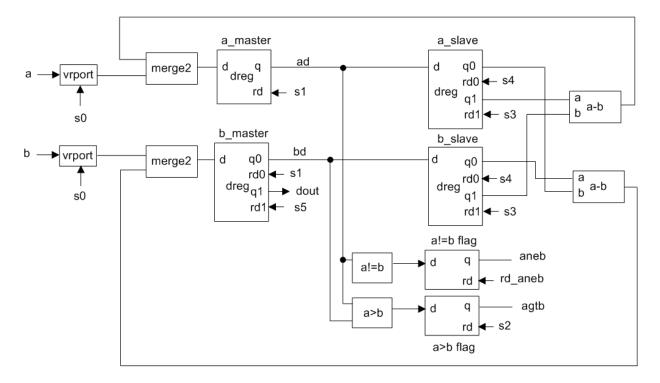

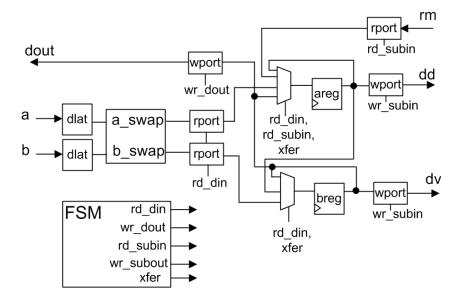

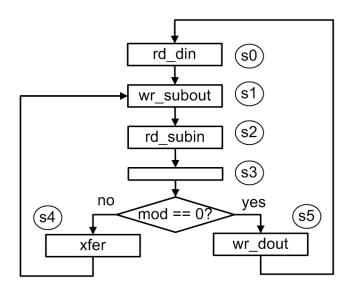

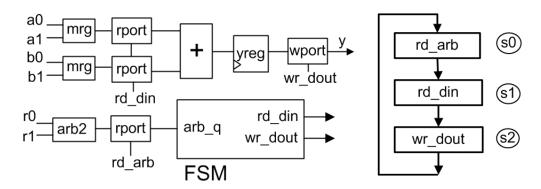

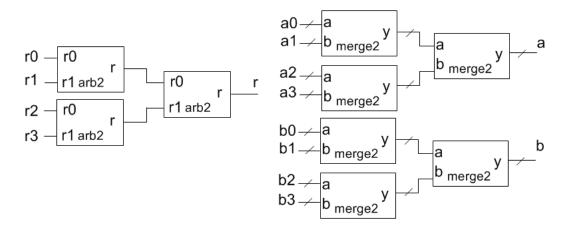

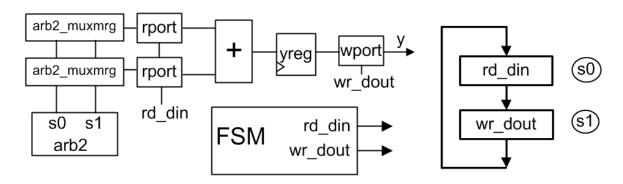

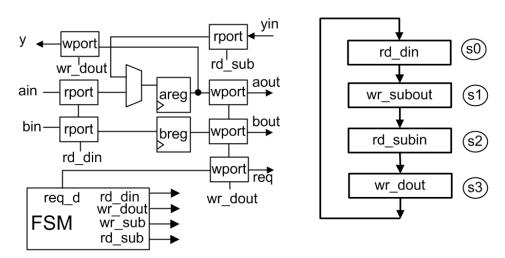

The datapath and finite state machine (FSM) for the *gcdsimple* example are shown Figure 3-10. There is no attempt at power savings, all muxes are Boolean. The GCD block has the property that it should only accept new input when it requires new input, which is during state S0. The *rport* box is a *read port* module, and is used to control input port activity to meet this requirement. Similarly, the DOUT output port should only be active when output value is ready, which is during state S2. The *wport* box is a *write port* module, and is used to control output port activity in this manner. In a data-driven design, having

conditional port activity costs extra gates in terms of read port/write port wrappers. These will be explained in more detail later in this section.

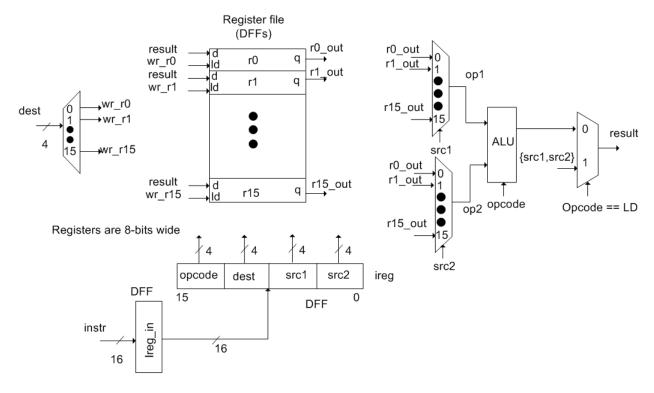

Figure 3-10 GCD Datapath/FSM.

Code excerpts will be shown from  $clkspec\_gcdsimple.v$  to illustrate how the elements of Figure 3-10 are implemented in RTL. Figure 3-11 shows RTL that implements the computational and mux elements of the datapath. Even though you can use arithmetic operators such as '<', '==', '-', etc., this code uses parameterized modules from parm\_modules.v to ensure user-controlled architectures for these operations. The use of the  $mux2\_n$  parameterized module is important as the mux2 cell has a very efficient NCL implementation.

```

// assign a_lt_b = (aq < bq);

33

34

// assign a_eq_b = (aq == bq);

35

compare_16 compmod (.a(aq),.b(bq),.agb(a_gt_b),.aeqb(a_eq_b));

36

assign a lt b = \sim(a gt b | a eq b);

37

38

wire [15:0] sub_a_b, sub_b_a;

39

subripple_n #(.WIDTH(16)) subcompa (.s(sub_a_b),.a(aq),.b(bq));

40

subripple_n #(.WIDTH(16)) subcompb (.s(sub_b_a),.a(bq),.b(aq));

41

42

43

// assign aq_val = (a_gt_b) ? (sub_a_b) : aq;

44

// assign bq val = (a lt b) ? (sub b a) : bq;

45

mux2 n #(.WIDTH(16)) u mux0 (.y(aq_val),.a(sub_a_b),.b(aq),.s(a_gt_b));

mux2_n #(.WIDTH(16)) u_mux1 (.y(bq_val),.a(sub_b_a),.b(bq),.s(a_lt_b));

46

47

48

wire [15:0] aq_rd, bq_rd;

49

mux2_n #(.WIDTH(16)) u_mux2 (.y(aq_rd),.a(ad),.b(aq_val),.s(rd));

50

mux2_n #(.WIDTH(16)) u_mux3 (.y(bq_rd),.a(bd),.b(bq_val),.s(rd));

```

Figure 3-11 Datapath RTL.

Figure 3-12 shows the RTL that implements the registers and FSM logic; this is written in essentially the same manner as for a clocked system. State S0 activates the read port, state S1 performs the iterative computation, and state S2 activates the write port.

```

□ always @(posedge clk or negedge reset) begin

52

53

if (reset == 0) begin

pstate <= `s0;</pre>

54

55

aq <= 0; bq <= 0;

56

end

else begin

57

58

pstate <= nstate;</pre>

59

aq <= aq_rd; bq <= bq_rd;

60

61

end //end always

62

63

//fsm logic

□always @(*) begin

64

65

wr = 0; rd = 0;

66

nstate = pstate;

case (pstate)

67

68

s0: begin

69

rd = 1;

70

nstate = `s1;

71

end

72

s1: begin

73

if (a eq b) nstate = `s2;

74

end

75

s2: begin

76

wr = 1;

77

nstate = `s0;

78

79

default: nstate = `s0;

80

endcase

end // end always

81

```

Figure 3-12 Register/FSM RTL.

#### **Read port operation**

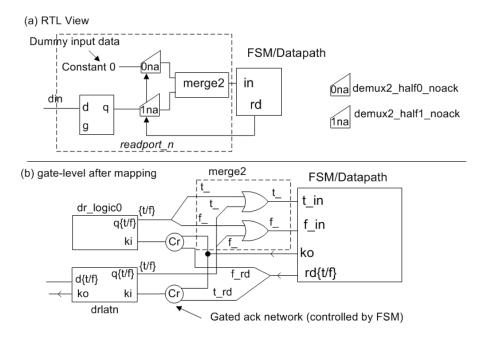

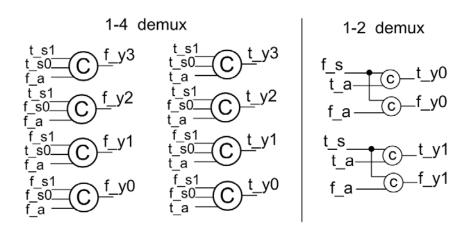

The *rport* box of Figure 3-10 is a *read port*, and is used to conditionally provide data to a data-driven design. A data-driven design requires data/null waves every compute cycle, and the read port's function is to provide data from an external port when its read line is asserted, and provides dummy data when its read line is negated. Figure 3-13a shows the RTL implementation of the read port macro. The input port goes to a D-latch, whose output goes to a *black-box* component named *demux2\_half1\_noack*. A black-box component has no logic function defined in the Cadence/Synopsys .lib file, and so the synthesis tool simply keeps it unchanged in the netlist. Black-box components in Uncle are used to implement either special gating that implements an asynchronous capability, or serves as virtual annotation in the netlist that causes the mapping process to manipulate this portion of the netlist in some manner. The output of the *demux2\_half1\_noack* gate goes to a *merge* gate, whose other input is from a *demux2\_half0\_noack* gate that is fed by a constant 0 (this is the dummy data when the readport is not selected). Both noack gates have select lines; one can view the *half1\_noack* output as having active data when its select line is logic 0. The merge gate is also a black box component, that maps in the dual rail netlist to

an OR2 gate that ORs the false rails together, and an OR2 gate that ORs the true rails together (this is typically called an asynchronous mux, and only one of the true/false rail pairs are assumed to have active data in any cycle). Note that select inputs of the  $half_noack$  components is tied to a line named rd (read) from the FSM; when rd=1 the external port data is gated to the FSM/datapath, when rd=0 the dummy data is gated to the FSM/datapath.

Figure 3-13 Read port details.

Figure 3-13b shows how the RTL is translated to gates in the final netlist by the mapping process. The  $half\_noack$  components act as virtual instructions to the ack network generator, and the ack generator creates a gated ack network as shown. Note the ki (ackin) input to the drlatn cell is only a '1' (request-for-data) if rd=1 ( $t\_rd$  is asserted). Similarly, the ki input to the dual-rail logic 0 generator is only a '1' (request-for-data) if rd=0 ( $f\_rd$  is asserted). The C-gates connected to the  $t\_rd/f\_rd$  signals are reset-to-null C-gates since during reset, the  $t\_rd/f\_rd$  signals will both be null, while the ko (ackout) of the FSM/datapath will be a '1', thus requiring a C-gate with a reset line.

The RTL for instantiating the read ports in the RTL for the GCD design is given below:

```

readport_n #(.WIDTH(16)) rp_x (.clk(clk),.d(a),.q(ad), .rd(rd));

readport_n #(.WIDTH(16)) rp_y (.clk(clk),.d(b),.q(bd), .rd(rd));

```

#### Write port operation

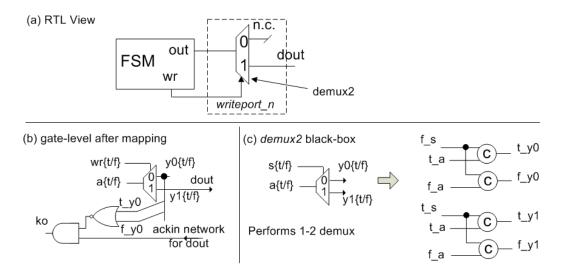

The wport box of Figure 3-10 is a write port, and is used to conditionally provide data to the output port of data-driven design. Figure 3-14a shows that the RTL view of a write port is just a demux2 black-box component with the y0 output unconnected. The y0 port of a demux2 copies the input data if the select line is false, and the y1 port copies the input data if the select line is true as shown in Figure 3-14c. The purpose of the unconnected output port of the demux2 is to consume the output data by providing a self-ack for this port as shown in Figure 3-14b. If your design is such that you know that the

FSM/datapath output will always be consumed by some destination (that is, an ack will be provided), then the *demux2* component can be replaced by a *demux2\_half1* component that only implements the y1 output (this saves the cost of the self-ack gating).

Figure 3-14 Write port details.

The RTL for instantiating the read ports in the RTL for the GCD design is given below:

```

writeport_n #(.WIDTH(16)) wp0 (.d(bq),.q(dout), .wr(wr));

```

## 4 Control-driven Examples

This section gives examples of control-driven designs; all examples are available in the *designs/* subdirectory of the Uncle distribution. The control-driven design methodology is taken from the Balsa synthesis toolset by examination of the Balsa generated netlists and through published articles on Balsa control; the author's contribution is to make this methodology available in a Verilog RTL form and to provide some optimizations to it such as C-gate sharing in ack networks.

## 4.1 First control-driven example: *up\_counter.v* to *ncl\_up\_counter.v*

The first control-driven example is *up\_counter.v* and is found in:

\$UNCLE/designs/regress\_dreg/syn/rtl/up\_counter.v

The regression test for this example can be run in the \$UNCLE/designs/regress\_dreg/ directory using the command:

python doregress.py up\_counter cadence default.ini -syntool cadence

Control-driven designs requires more designer effort at the RTL level than data-driven designs, as each register in data driven RTL (a DFF) most probably needs to be split into master/slave latches in the control-driven RTL, with each latch accessed in a different state of the control-driven sequencer. The control logic has to be instantiated manually as a network of S/T elements. There are some modules in the *parm\_modules.v* file that can somewhat reduce the RTL overhead of specifying a control-driven sequencer; these will be discussed when encountered in example designs.

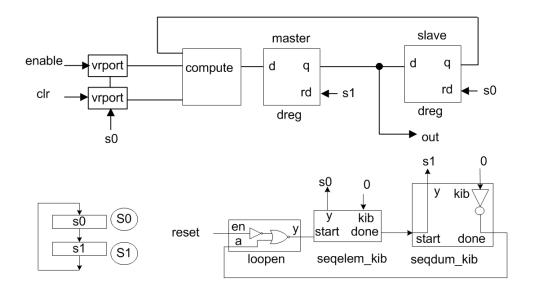

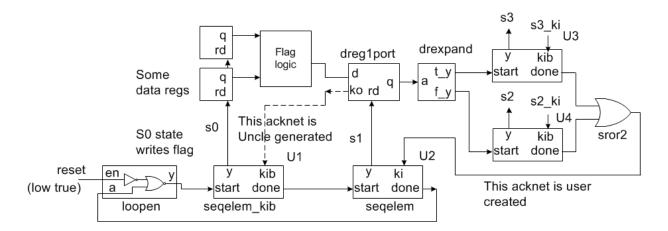

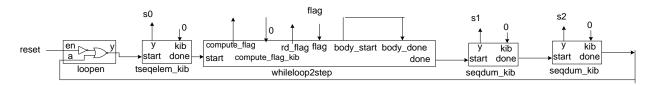

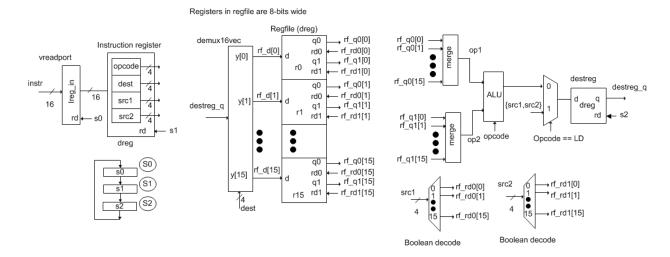

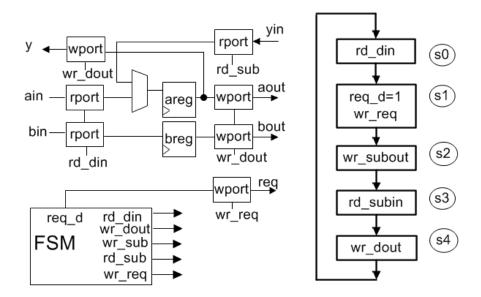

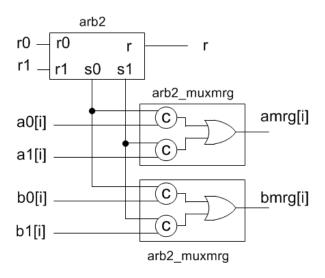

Figure 4-1 shows the RTL view of the control-driven *up\_counter* example. The register is implemented as separate master, slave latches that are controlled by a two-state sequencer. State SO gates the external inputs, reads the slave register, and updates the master register with the new counter value base on the slave register value and the external inputs. State S1 writes the slave register, and places the counter value on the *out* terminals. The *vrport* black box component is a virtual read port (module name is *vreadport*) used by control-driven designs for conditional access of external inputs. It differs from the read port module previously discussed in that it does not provide dummy values when its select line is false, and it does not actually contain a register. It serves as a virtual instruction to the ack network generator and causes a gated ack network to be placed on the *ackout* primary output in the final netlist (see Figure 4-2).

The two-state sequencer is implemented using three modules from parm\_modules.v: loopen, seqelem\_kib, and seqdum\_kib. The loopen component implements the logic shown, and is used to form a repeated sequence of actions. State S0 is implemented with the seqelem\_kib component (an Selement), with the terminals of Figure 2-5 renamed as start == Ir, y == Or, kib == Oa (+ inverter), done == la. The kib terminal is typically tied to the auto-generated ack network. The letter b in kib is used to indicate that this comes from a low-true ack network such as generated by the data registers, and has to be inverted inside of the seqelem\_kib component (there is also available a seqelem component that expects a high-true ack, and has a terminal named ki). In the RTL, the kib terminal is tied to logic '0' as Uncle expects all inputs to components in the starting netlist to be connected; during the mapping process this is replaced by the auto-generated ack network. Typically, ackin/ackout terminals are not exposed on black-box modules used in RTL, but they are in the case of S/T-elements as there is a need to manually connect these in some cases (to be discussed later). The seqdum\_kib is simply wires and one inverter as shown Figure 4-1; the last S/T element in a loop can be replaced by wires instead of using gating.

Figure 4-1 RTL view of the control-driven up\_counter example.

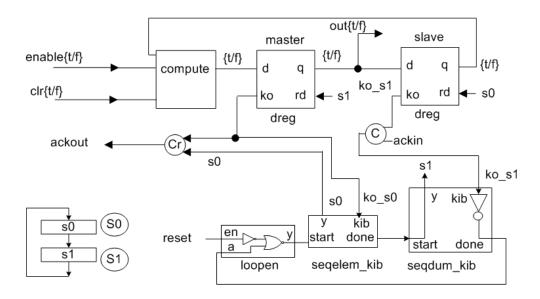

Figure 4-2 shows the final gate-level view of the up\_counter example. Note that a gated ack network is generated for the ackout signal, and that the ack inputs of the two sequencer elements have been connected to the appropriate ack networks. There is also one other important difference in this netlist when compared to the data-driven netlist – not all RTL signals have been expanded to dual-rail signals. Control-driven RTL has both single-rail and dual-rail components. Sequencer elements are single-rail components, and thus all signals connected to them all single-rail signals. Usage of single/dual rail signals will be expanded on in later examples.

Figure 4-2 Gate-level view of the control-driven up\_counter example.

Figure 4-3 shows the datapath RTL that instantiates the virtual read ports, the latches, and the compute block. Modules for control-driven registers are contained *parm\_modules.v* with versions that have 1, 2, 3 read ports and also a variable number of read ports.

```

14

//read ports for inputs

15

vreadport rdport en (.d(enable),.q(enable port),.rd(s0));

16

vreadport rdport_clr (.d(clr),.q(clr_port),.rd(s0));

17

//registers

18

19

dreg1port n #(.WIDTH(8)) dout master (.q(out),.rd(s1),.d(next out));

20

dreg1port_n #(.WIDTH(8)) dout_slave (.q(out_now),.rd(s0),.d(out));

21

//computation

22

23

24

□always @* begin

25

next out = out now;

26

if (enable port) next out = out now + 1;

27

if (clr_port) next_out = 0;

28

L end

```

Figure 4-3 Datapath RTL for up\_counter example.

Figure 4-4 shows the RTL that implements the sequencer; this is a straight-forward instantiation of the logic shown in Figure 4-1.

```

31

wire s0_start, s1_start, s1_done;

32

wire log0;

33

34

assign log0=0;

35

36

//enable for loop

37

loopen g0 (.y(s0_start),.en(reset),.a(s1_done));

38

39

//State s0

40

seqelem_kib u1 (.start(s0_start), .done(s1_start), .y(s0), .kib(log0));

41

42

//state s1

43

seqdum_kib u2 (.start(s1_start), .done(s1_done), .y(s1), .kib(log0));

44

```

Figure 4-4 Control RTL for up\_counter example.

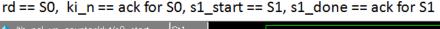

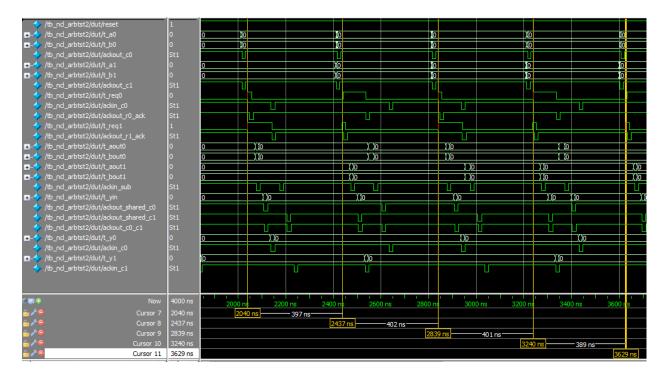

Figure 4-5 shows a simulation for the final netlist. Because synthesis does not always preserve net names used in the RTL, the mapping of gate-level net names to RTL names is given at the top of the timing simulation. This simulation uses the same test bench as used for the data-driven up counter example, which is as it should be, as data-driven versus control-driven should not change the module's interface. The time marked as point A shows the ack assertion (after the internal inverter in the seqelement\_kib component) in response to the SO assertion; note that this causes SO to be negated, which then triggers the ack negation. Observe that s1\_start assertion occurs after the SO ack is negated.

Figure 4-5 Timing for up counter done using Balsa style components (uses an S-element).

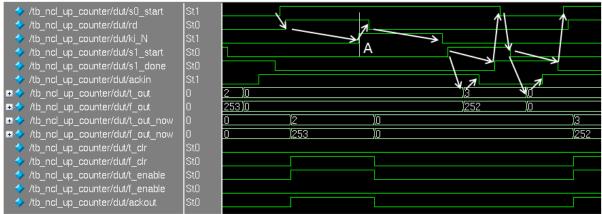

Figure 4-6 shows a simulation for the up counter in which the S-element has been replaced with a T-element (this example can be found in \$UNCLE/designs/regress/syn/rtl/clk\_up\_counterv2.v). Observe that the s1\_start assertion is now triggered by the S0 ack assertion and not by its negation. This overlaps the return-to-null action of S0 with the data wave of S1, resulting in a faster cycle time.

Figure 4-6 Timing for up\_counter done using Balsa style components (uses a T-element).

## 4.2 While-loops, choice

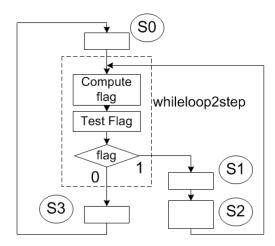

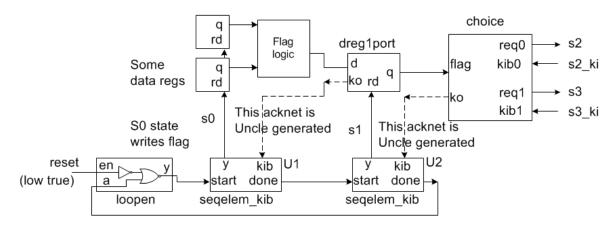

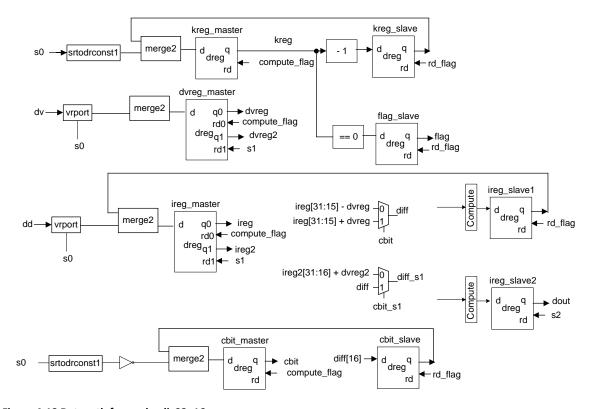

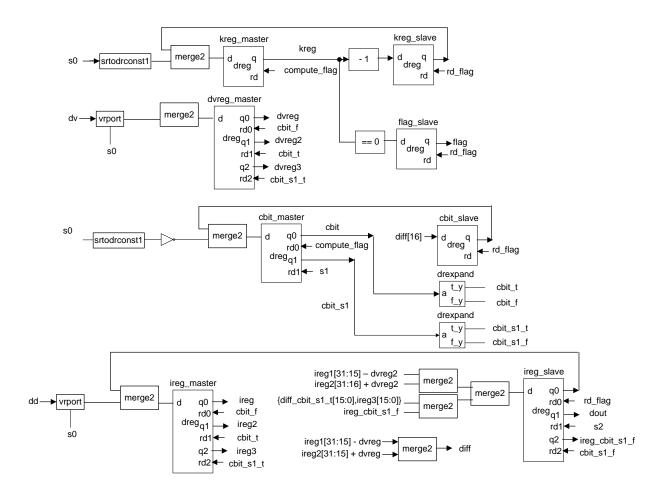

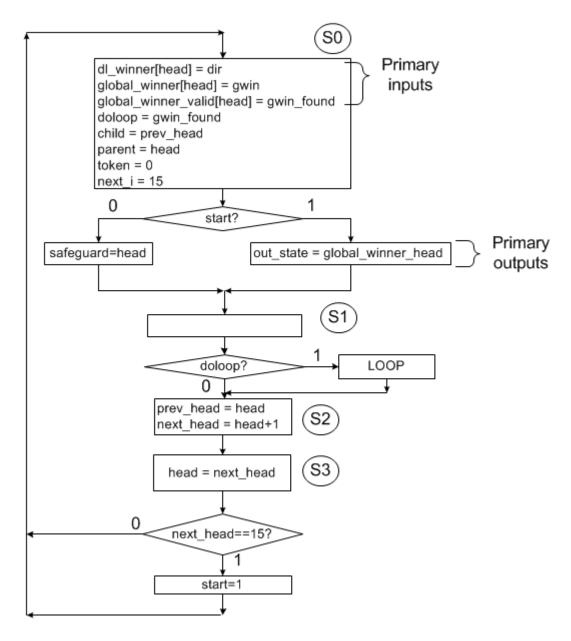

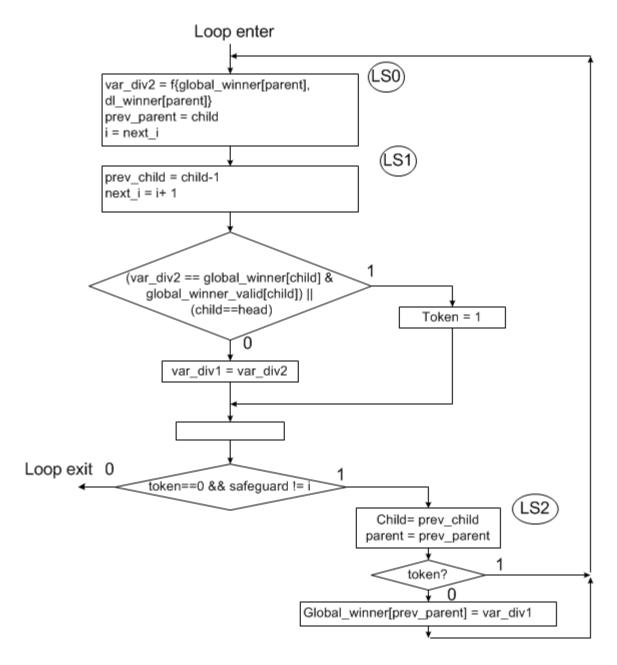

The previous example had a two-state sequencer with no conditional execution. Figure 4-7 shows a sequencer with a while-loop. State SO reads external ports, followed by states in the dotted box that compute a flag, then test flag the flag, with states S1, S2 executed if the flag test is true. State S3 is executed on loop exit, which returns back to SO on completion.

Figure 4-7 Sequencer with while loop.

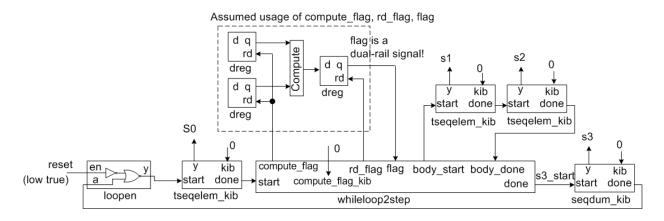

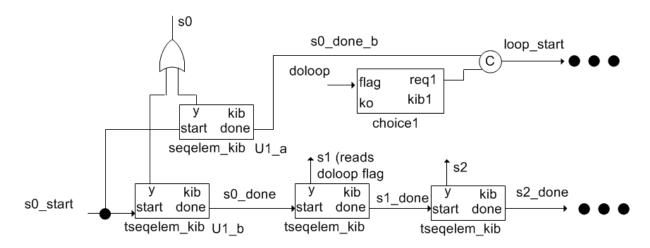

Figure 4-8 gives the RTL view of the control for the sequencer of Figure 4-7. The key component is the *whileloop2step* component, which is a module that is available in *parm\_modules.v*. The *whileloop2step* module first computes the flag that is used to control the loop execution, then reads/test the flag, and conditionally executes the loop body. All of the signals connected to the whileloop2 module are single-rail signals, except for the *flag* signal, which is dual-rail. It is assumed that the *compute\_flag* signal is used to compute the flag that is written to a single bit latch, whose read port is connected to the *rd\_flag* signal, and whose output is connected to the *flag* input. The *tseqelem* components are just place holders and can be replaced by S/T elements as desired.

Figure 4-8 RTL view of control for sequencer with while loop.

Figure 4-9 gives the *whileloop2step* module implementation details. A *seqelem* component is used to control a two-state sequencer that implements the compute flag and read flag steps. The *drexpand* module is a black box component that is used to access the individual  $t_f$  rails of a dual-rail signal at the RTL level. The input to a *drexpand* component is a dual-rail signal, while the two output signals are both single rail, making them suitable for connection to sequencer component inputs. Observe that the  $f_f$  signal is connected to the ki input of the seqelem component. This is an example of requiring a control element with a non-inverted ki input, and also a case where the designer provides the net

connection for the *ki* input instead being connected during the mapping process to an ack network. In terms of operation the two-state sequencer remains operational as long as the *t\_flag* signal is asserted during the flag read state.

Figure 4-9 whileloop2step module details.

An optimization can be applied to this while loop if the while body only has one state. This implies that the while-body will be implemented with a wired-sequential element, a *seqdum* component, which also means that the last *tseqelem* element of Figure 4-9 can be replaced with a *seqdum* component as well.

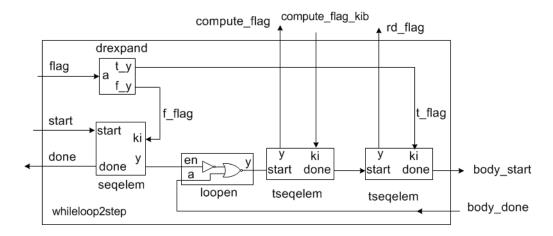

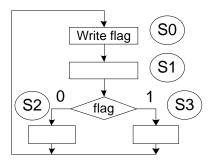

Figure 4-10 shows a sequencer with choice. State S2 is executed if the flag is false, else State S3 is executed.

Figure 4-10 Sequencer with choice.

Figure 4-12 shows one method of implementing the control of Figure 4-10 using sequencer elements. Sequencer element U1 implements state S0 (writes the flag), while element U2 implements state S1 (reads the flag). The  $t_f$  rails of the flag are used to trigger sequencer elements that control states S3/S2 respectively. The sror2 black-box component is a single-rail OR2; since only one sequencer element (U3 or U4) is activated, this gate combines the done signals of these two components to a single done signal that is then used as the ack for sequencer element U2.

Figure 4-11 One way to implement choice.

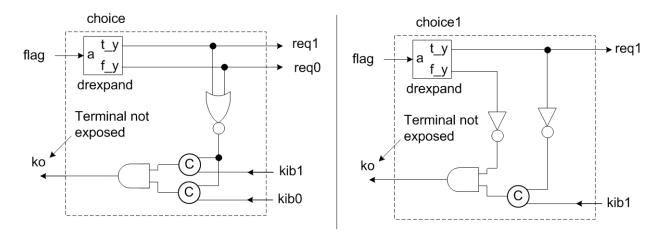

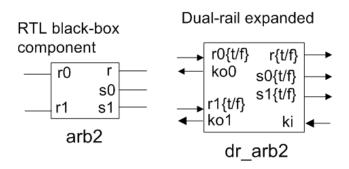

Figure 4-12 shows the control of Figure 4-10 implemented using the *choice* module available in *parm\_modules.v*. Depending on the application, this can be more efficient than the implementation of Figure 4-11. The *choice* module has a hidden ackout (*ko*) terminal that is low-true (like all Uncle ackout terminals) that will be automatically connected during mapping. Because the choice *ko* terminal is low-true, sequencer that gates the flag to choice element must have a low-true ackin. The exposed ackin terminals (*kib0*, *kib1*) on the choice element are also low-true, and are expected to come from completion networks tied to datapath elements.

Figure 4-12 Using the choice component.

The implementation of the choice component is shown in Figure 4-13. The flag signal is a dual-rail signal, expanded internally to  $t_f$  rails within the choice module. All ackins/ackout are low-true. The choice component can be used to implement  $if\{f\}/else\{f\}$  within a sequencer. Also shown in Figure 4-13 is a *choice1* module, which is useful for implementing an  $if\{f\}$  capability within a sequencer.

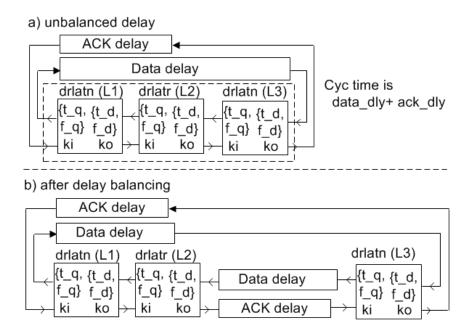

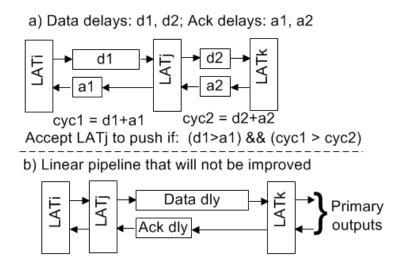

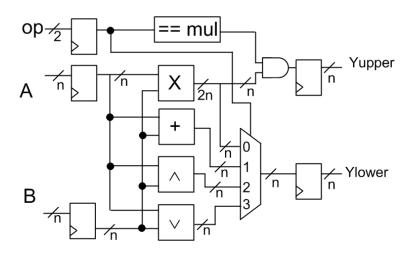

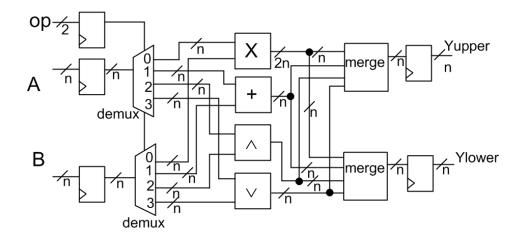

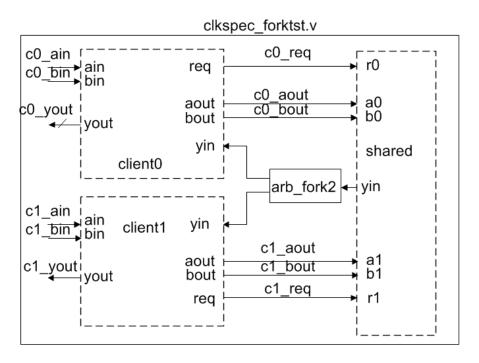

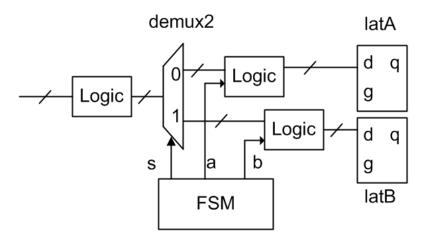

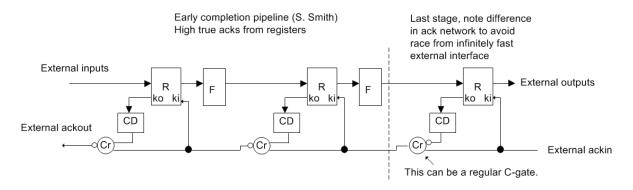

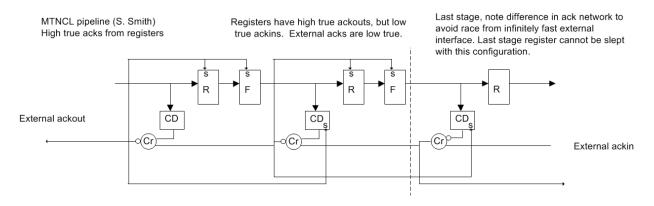

Figure 4-13 Implementation details for the choice/choice1 components.