## Design and VLSI Implementation of High Performance Face Recognition System

A report submitted to department of Electrical & Electronic Engineering, BRAC University in partial fulfillment of the requirements for thesis work.

Priyanka Das Dewan - 10221078

Tasnim Harun Shamma – 09221032

Afifa Abbas - 10221073

Raktim Kumar Mondol - 09221232

**April 2013**

#### **Declaration**

We do hereby declare that the thesis titled "Design and VLSI Implementation of High Performance Face Recognition System" is submitted to the Department of Electrical and Electronics Engineering of BRAC University in partial fulfillment of the Bachelor of Science in Electronics and Electrical Engineering. This is our original work and was not submitted elsewhere for the award of any other degree or any other publication.

| Date:      |  |  |

|------------|--|--|

| Supervisor |  |  |

|            |  |  |

Professor Dr. A. B. M Harun- Ur- Rashid

(Priyanka Das Dewan) Student's ID: 10221078 priyanka.bracu@gmail.com

(Tasnim Harun Shamma) Student ID: 09221032 tasnim.h.shamma@gmail.com

(Afifa Abbas) Student ID: 10221073 afifa.abbas118@gmail.com

(Raktim Kumar Mondol) Student ID: 09221232

raktim.live@gmail.com

#### **Abstract:**

In this paper, we have proposed a novel hardware architecture for face-recognition system. In order to make the system cost effective we have used a simple yet efficient algorithm of face-recognition system. We have designed, implemented and verified the algorithm in a cyclone III Field Programmable Gate Array (FPGA) chip. Altera DE0 development board which contains a cyclone III chip on it have been used for debugging purpose. We have also ensured for low power consumption such that the chip could be used universally in a wide range of security systems.

To develop a simple yet efficient face recognition algorithm (such as PCA, FFT etc.) on digital hardware, we have researched on various face recognition algorithms using Matlab codes and studied their detection efficiency under various posture and background and also the complexity of the algorithm. To save hardware resource and at the same time to obtain an acceptable level of recognition we have chosen to use Fast Fourier Transform.

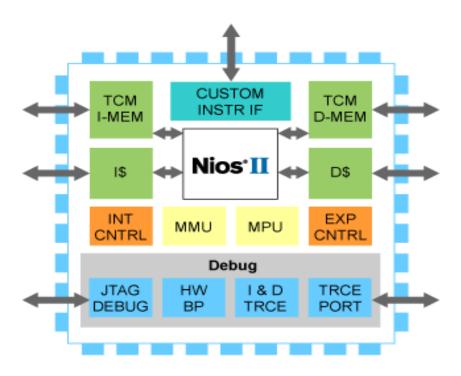

The search database is developed by taking pictures of BRAC University students in various background and postures and used them to evaluate the developed face recognition system. Images were captured using TRDB\_D5M camera module and digital data from the camera was transferred to the SDRAM of the DE0 board using GPIO interface. A NIOS2 microprocessor was synthesized in the cyclone III chip which controlled the total recognition system and the communication between the FFT core, SDRAM and On-chip memory. The performance of the hardware is now under evaluation.

## **Keywords:**

FFT, FPGA, Face Recognition, Nios2, TRDB\_D5M.

#### **Preface:**

One of the most important reasons for choosing this task as our undergraduate thesis is that it gave us the possibility to use the theory and knowledge that we have gained over the years to make something useful and practical. We also believed that the design task would be good preparation for the future challenges. We have always been fascinated by electronics and the wide area of application this technology presents. Since our interest include both VLSI and working with FPGA, this project became a great opportunity to combine our interest and education.

The reason behind choosing FPGA is that in our country very few people worked with this board and we took it as a challenge. This challenge was the most effective way to learn new things. We have learned a lot about image processing, DE0 board, TRDB\_D5M camera, Quartus12.0 and NIOSII. The Altera DE0 platform was a very good platform to work with. Many projects can be implemented using this board.

#### **Acknowledgements:**

This thesis is submitted to BRAC University in partial fulfillment of the requirements for the degree of bachelor in Electrical and Electronic Engineering.

We are thankful to our Almighty Allah for his blessings upon us and bestowing us courage to go with such task, and also our parents for their support, love and patience.

This project would not have been possible without all the help and the support we have received. We would like to thank our supervisor, Professor Dr. A. B. M Harun- Ur- Rashid (Bangladesh University of Engineering and Technology) for all the help, support, fresh perspectives we have got. We are also thankful to Sir Jahangir Alam, Lecturer of BRAC University for his constant guidance, when we were stuck. We highly appreciate the assistance and guidance of Shafiur Rahman, student of BUET and Ahsan Ashfaq, an Alumni of Halmstad University, Sweden, throughout the process.

April 13, 2013.

| Abstract                                                         | 3     |

|------------------------------------------------------------------|-------|

| Preface                                                          | 4     |

| Acknowledgement                                                  | 5     |

| Table of Contents                                                |       |

| Table List                                                       |       |

| Figure List.                                                     |       |

| rigure Dist                                                      | ••••• |

| <b>Table of Contents</b>                                         |       |

| Chapter 1                                                        |       |

| Introduction                                                     | 10    |

| 1.1 Background                                                   |       |

| 1.2 Motivation and objectives                                    |       |

| 1.3 Research Goal                                                | 11    |

| 1.4 Problem Formulation                                          | 12    |

| Chapter 2                                                        |       |

| 2.1 Algorithms for Face Recognition                              | 13    |

| 2.1.1 Principle Component Analysis(PCA)                          |       |

| 2.1.2 Linear Discriminant Analysis (LDA)                         |       |

| 2.1.3 Independent Component Analysis (ICA)                       |       |

| 2.1.4 Trace Transform                                            | 23-24 |

| 2.1.5 Neural Network.                                            |       |

| 2.2 Fast Fourier Transform (FFT).                                |       |

| 2.3 How does FFT works.                                          |       |

| 2.4 FFT algorithms.                                              |       |

| 2.4.1 FFT Implementation in NIOS II using Cooley-tukey algorithm |       |

| 2.5 Applying FFT on an image                                     |       |

| 2.6 Applications                                                 |       |

| 2.7 Benefits of using FFGA                                       |       |

| Chapter 3                                                        | 20    |

| MATLAB Implementation                                            |       |

| 3.1 Basic Approach                                               |       |

| 3.3 Functions used in Matlab.                                    |       |

|                                                                  | 43    |

| Chapter 4                                                        | 47    |

| DE0 board and TRDB_D5M Specifications                            |       |

| 4.1 Introduction to FPGA                                         |       |

| 4.2 Cyclone III FPGA: Architecture                               |       |

| 4.4 Cyclone III FPGA: Applications                               |       |

| 4.5 Altera Cyclone III 3C16 FPGA device                          |       |

| 4.6 Camera Module Pixel Array Structure                          |       |

| 4.7 I2C Protocol                                                 |       |

| 4.8 Camera Image Acquisition System.                             |       |

| 4.8.1 Frame Valid.                                               |       |

| 4.8.2 Line Valid                                            | 52 |

|-------------------------------------------------------------|----|

| 4.9 Bayer to RGB conversion in FPGA                         | 53 |

| 4.9.1 RGB Conversion.                                       | 53 |

| Chapter 5                                                   |    |

| Hardware Implementation                                     | 55 |

| 5.1 External Bus to Avalon Bridge                           | 57 |

| 5.2 SDRAM Controller                                        | 59 |

| 5.3 Phase Locked Loop (PLL)                                 | 62 |

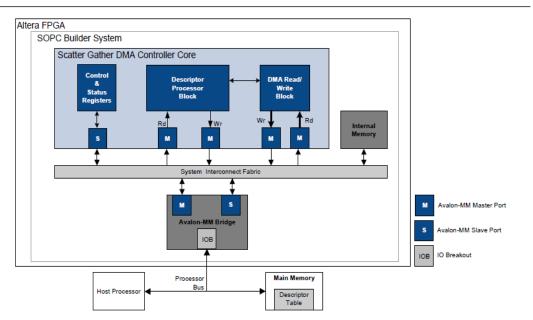

| 5.4 Scatter Gather DMA (Direct Memory Access)               |    |

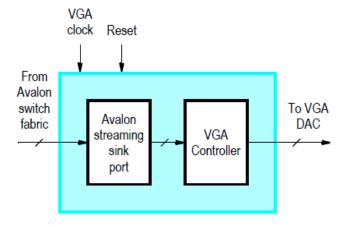

| 5.5 VGA Controller                                          |    |

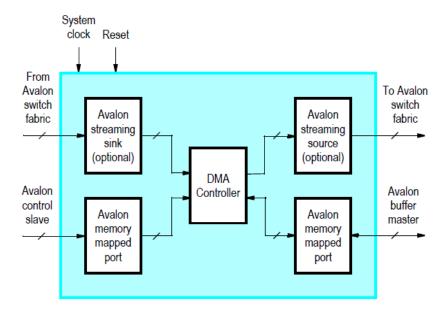

| 5.6 Video DMA Controller                                    |    |

| 5.7 Fast Fourier Transform (FFT) Generated from Mega wizard |    |

| 5.8 Creating FFT block in Qsys.                             |    |

| 5.9 On-chip Memory (RAM or ROM)                             |    |

| 5.10 NIOS II Processor.                                     |    |

| 5.11 Hardware Abstraction Layer.                            |    |

| Chapter 6                                                   |    |

| Results and Discussion                                      |    |

| 6.1 Software.                                               |    |

| 6.2 Hardware                                                |    |

| 6.3 Limitations.                                            |    |

| 6.3.1 Software.                                             |    |

| 6.3.2 Hardware                                              |    |

| 6.4 Future work                                             |    |

| 6.5 Conclusion.                                             |    |

| Chapter 7                                                   |    |

| References                                                  |    |

| Chapter 8                                                   | 87 |

| Appendix                                                    | 87 |

| 8.1 FFT Matlab code.                                        |    |

| 8.2 PCA based Face Recognition Matlab Code.                 |    |

| 8.3 FPGA Code                                               | 89 |

| 8.3.1 Storing Data from Camera Module to SDRAM              | 89 |

| 8.3.2 Interfacing Qsys Components with FPGA                 | 90 |

| 8.3.3 Creating SDRAM Allocation                             | 91 |

| 8.4 Code for SGDMA                                          |    |

| 8.5 Code for Recognition in C (NIOS II)                     | 92 |

| Table List                                 |    |

|--------------------------------------------|----|

| Table 5.1: Description of SDRAM Parameters | 61 |

| Table 5.2: PLL Calculation.                | 62 |

| Table 5.3: Function List.                  | 66 |

## Figure List

| Figure 2.1: Face Recognition Approaches                         | 25 |

|-----------------------------------------------------------------|----|

| Figure 2.2: Time Domain Decomposition                           | 27 |

| Figure 2.3: Rearrangement Pattern Required                      | 27 |

| Figure 2.4: Time domain to frequency domain                     | 28 |

| Figure 2.5: FFT Synthesis Flow Diagram                          | 29 |

| Figure 2.6: Result of Cooley- Tukey                             | 31 |

| Figure 2.7: The Magnitude calculated from the complex result    | 34 |

| Figure 2.8: Magnitude after logarithmic transform               | 35 |

| Figure 2.9: The Phase of FFT                                    | 35 |

| Figure 2.10: Magnitude and phase of a Fourier image             | 36 |

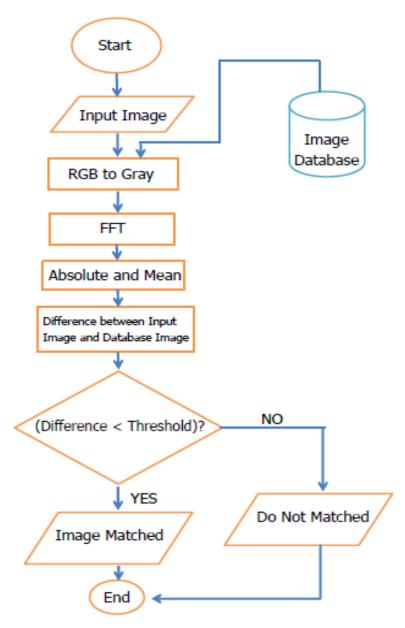

| Figure 3.1: Flowchart of FFT based Face Recognition             | 39 |

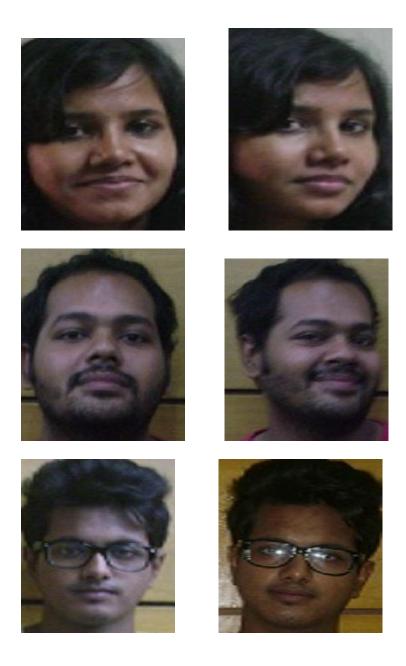

| Figure 3.2: Train Database                                      | 40 |

| Figure 3.3: Test Database Image                                 |    |

| Figure 4.1: Cyclone III Device Architecture Over view Floorplan | 47 |

| Figure 4.2: Cyclone III FPGA                                    | 47 |

| Figure 4.3: Cyclone III logic elements                          | 48 |

| Figure 4.4: DE0 FPGA Specifications                             | 49 |

| Figure 4.5: DE0 FPGA Components                                 | 50 |

| Figure 4.6: Pixel Array Description.                            | 51 |

| Figure 4.7: Default Pixel Output Timing                         | 52 |

| Figure 4.8: Bayer Pattern Filter                                | 53 |

| Figure 4.9: Bayer Image Pixels                                  | 53 |

| Figure 4.10: RGB Pixel from Bayer Format                        | 54 |

| Figure 5.1: Block Diagram of Our Proposed Architecture          | 55 |

| Figure 5.2: RTL Viewer                                          | 57 |

| Figure 5.3: External Bus to Avalon Bridge.                      |    |

| Figure 5.4: NIOS II Processor.                                  | 73 |

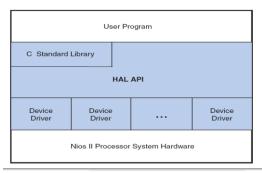

| Figure 5.5: HAL Architecture                                    | 74 |

| Figure 5.6: Nios II HAL Project Structure.                      |    |

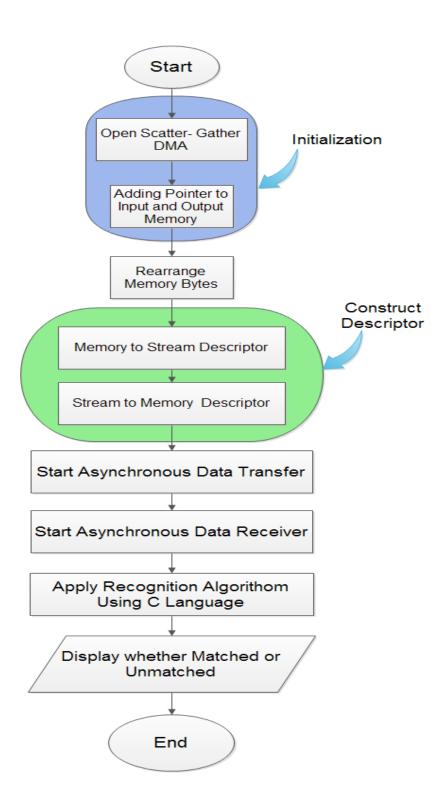

| Figure 5.7: Flowchart for Nios II Instruction.                  | 76 |

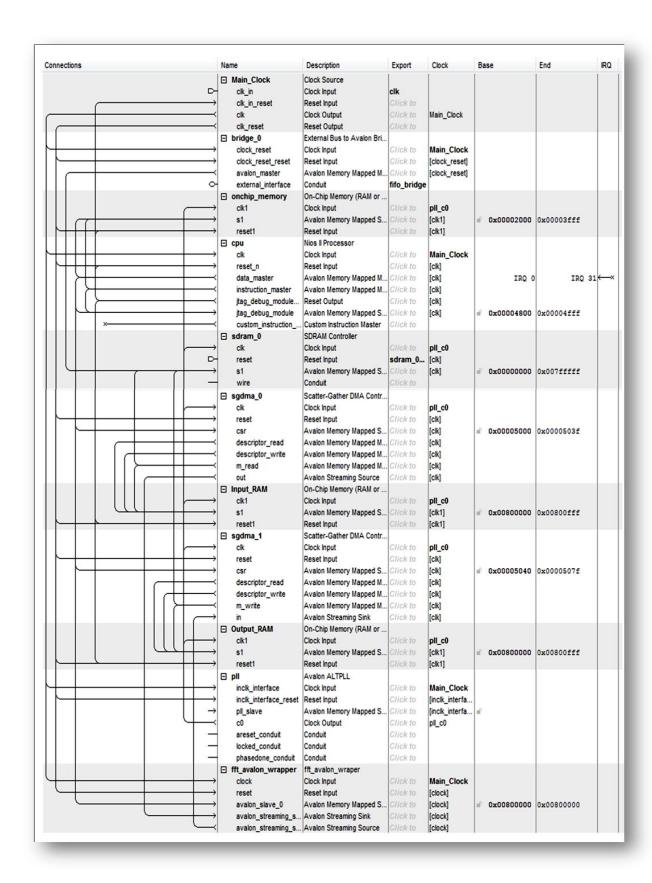

| Figure 5.8: Qsys System Content.                                | 77 |

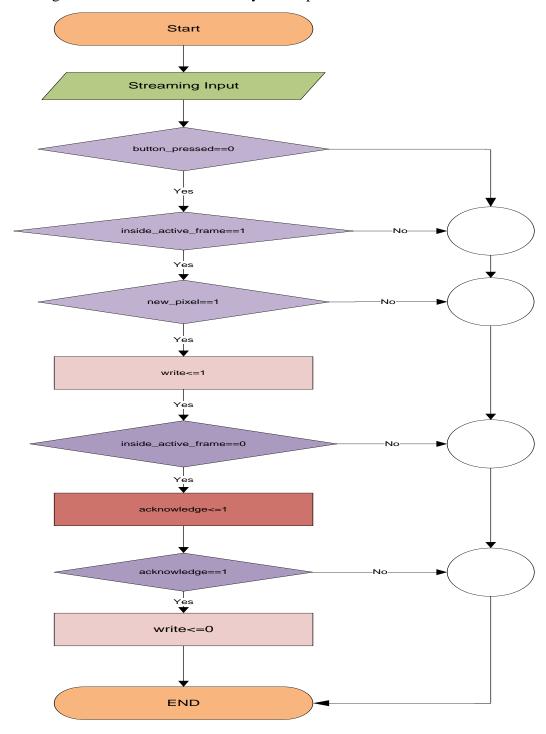

| Figure 5.9: Flowchart for Valid Frame Capture                   |    |

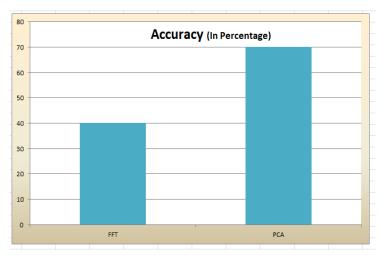

| Figure 6.1: Accuracy rate of Face Recognition for PCA and FFT   | 80 |

| Figure 6.2: Recognition Result with FFT based Algorithm         | 81 |

| Figure 6.3: Recognition Result with PCA based Algorithm.        | 82 |

## Chapter 1

#### **Introduction:**

#### 1.1 Background

A facial recognition system is a computer application for automatically identifying or verifying a person from digital image or a video frame from a video source. Therefore there are two types of approaches for face recognition. One is image based and another one is video- based. There are more classifications to it now. One is partially automated systems and the other is fully automates systems.

Face Recognition has become a well-liked and popular area of research in image analysis, understanding and in computer vision as well. This topic has raised curiosity among computer science researchers, neurologists and psychologists.

Basically, face recognition in our case is given still images of a person; it can verify and identify one or more persons using a stored database of faces. For the research help purpose already many databases have been created. As for example AT&T face database, Yale face databases etcetera comprising of different poses and illumination conditions. Many universities and institutions have shown interest in this image processing and recognition systems from very early time and still aspire to excel in this field.

Recognition algorithms is divided into two main categories or approached in two different ways. One is geometric another one is photometric. Geometric approach focuses on distinguished features of a face and photometric approaches statistically, that distils an image into some values and these values are compared with some templates so that variances are eliminated.

The researches' directions include recognition from outdoor images, non-frontal facial images, increased understanding of the effects of demographic factors on the performance, develop improved models for predicting identification performance on very large galleries and many more [1].

#### 1.2 Motivation and objectives:

After extensive research in the field of face recognition [35] [36], we discovered that none of the projects included FFT as a face recognition algorithm. We have designed the hardware architecture from a new perspective. Most of the available algorithms are implemented in software .As a result, the recognition speed is not as expected. On the other hand, hardware implementation has many promises. Therefore, we emphasized on hardware implementation. The improvement includes robustness of the speed and accuracy of the system. An FPGA can provide us necessary resources to achieve such improvements in face recognition. The resources includes built in blocks, various communication interfaces, millions of logic gates, scopes to run C codes into the digital hardware circuitry, high level design tools, performance, long term maintenance, reliability etcetera.

The objective of our project is to work with still image based algorithm and to implement it on a cyclone III FPGA chip from Altera Inc. The cyclone chip is relatively cheaper and includes ROM. DE0 board has been chosen as a tool for debugging process. We have emphasized on using FFT. Since FPGA implementation itself is a huge challenge, we will start with a simpler function that is FFT (Fast Fourier Transform). We have used the Cooley-Tukey algorithm for FFT. In addition, we have gone through for a hardware/software codesign approach. Our aim was to do the whole recognition in Matlab using FFT and PCA, verified that if they had worked properly, then we compared the algorithms. After that we focused on implementing FFT first on the board using Nios2 processors, SDRAM, on chip memory, DMA blocks etcetera.

#### 1.3 Research Goal:

Our research goal is to get acquainted with FPGA board, to learn how to use it. On the other hand, our goal was to enter into the huge area of image processing. Combining these two fields together can definitely broaden our knowledge. One of the prime concerns of our research is to start with the simpler algorithm, to confirm that it is possible to implement any other algorithm using FPGA, so that we can work on it in future. FPGA itself is complex device. Therefore we couldn't take our goal to the benchmark. Hopefully we will learn from mistakes and can go for further algorithms.

#### 1.4 Problem Formulation:

The first approach we had was to create our own small database with the images of our university students comprising different facial expressions. Then we attempted to apply some of the recognized algorithms on our database using MATLAB. Then we used our proposed algorithm using Fast Fourier Transform to assess the feasibility of using FFT as a face recognition algorithm. We afterwards moved towards hardware part which was our main interest. We used the FPGA board with the digital camera that is compatible with the board. We took images and stored them in the board's SDRAM. We then took these images from the memory and applied FFT on them and kept the transformed images to the SDRAM again. The next step was to compare between the values of the transformed images to verify if our algorithm was working.

## Chapter 2

## 2.1 Algorithms for face recognition

#### 2.1.1 Principle component Analysis:

Principle component Analysis (PCA) was invented in 1901 by Karl Pearson. This algorithm consists extracting relevant information in a face image which is called the principle component and encode that information in a suitable data structure. For recognition it takes the sample image and encodes it in the same way and compares it with the set of encoded images. In mathematical terms we want to find Eigen vectors and Eigen values of a covariance matrix of images, where one image is just a single point in high dimensional space [n \*n], where n\*n are the dimensions of an image. There can be many Eigen vectors for a covariance matrix but very few of them are principle one's. Each Eigen vector can be used for finding different amount of variations among the face image. However we are emphasizing only in principle Eigen vectors because these can show account for substantial variations among a bunch of images. They can show the most significant relationship between the data dimensions. Eigenvectors with highest Eigen values are the principle component of the image set. We may lose some information if we ignore components of lesser significance. But if the Eigen values are small then we won't lose much. Using those set of Eigen vectors we can construct Eigen faces.

The goal of PCA is to reduce the dimensionality of the data while retaining as much as possible of the variation present in the original dataset. PCA allows us to compute a linear transformation that maps data from high dimensional space to low dimensional sub-space. [1] [2].

$$b_1 = t_{11}a_1 + t_{12}a_2 + \dots + t_{1n}a_N$$

$$b_2 = t_{21}a_1 + t_{22}a_2 + \dots + t_{2n}a_N$$

$$\vdots$$

$$b_K = t_{K1}a_1 + t_{K2}a_2 + \dots + t_{KN}a_N$$

or  $y = Tx$  where  $T = \begin{bmatrix} t_{11} & t_{12} & \dots & t_{1N} \\ t_{21} & t_{22} & \dots & t_{2N} \\ \dots & \dots & \dots & \dots \\ t_{K1} & t_{K2} & \dots & t_{KN} \end{bmatrix}$

- Lower dimensionality basis

- Approaximate vectors by finding a basis in an approapriate lower dimensional space.

- (1) Higher dimensional space representation:

$$x = a_1 v_1 + a_2 v_2 + \cdots + a_N v_N$$

$v_1, v_2, ..., v_N$  is a basis of the N-dimensional space

(2)Lower dimensional space representation:

$$\hat{x} = b_1 u_1 + b_2 u_2 + \dots + b_K u_K$$

$u_1, u_2, ..., u_K$  is a basis of the K-dimensional space

- Note: if both bases have the same size (N = K), then  $x = \hat{x}$

Example:

$$v_1 = \begin{bmatrix} 1 \\ 0 \\ 0 \end{bmatrix}, v_2 = \begin{bmatrix} 0 \\ 1 \\ 0 \end{bmatrix}, v_3 = \begin{bmatrix} 0 \\ 0 \\ 1 \end{bmatrix} \text{ (standard basis)}$$

$$x_v = \begin{bmatrix} 3 \\ 3 \\ 3 \end{bmatrix} = 3v_1 + 3v_2 + 3v_3$$

$$u_1 = \begin{bmatrix} 1 \\ 0 \\ 0 \end{bmatrix}, u_2 = \begin{bmatrix} 1 \\ 1 \\ 0 \end{bmatrix}, u_3 = \begin{bmatrix} 1 \\ 1 \\ 1 \end{bmatrix} \text{ (some other basis)}$$

$$x_u = \begin{bmatrix} 3 \\ 3 \\ 3 \end{bmatrix} = 0u_1 + 0u_2 + 3u_3$$

thus,  $x_v = x_u$

- Methodology

- Suppose  $x_1, x_2, ..., x_M$  are  $N \times 1$  vectors

Step 1:

$$\bar{x} = \frac{1}{M} \sum_{i=1}^{M} x_i$$

Step 2: subtract the mean:  $\Phi_i = x_i - \bar{x}$

Step 3: form the matrix  $A = [\Phi_1 \ \Phi_2 \cdots \Phi_M]$  (NxM matrix), then compute:

$$C = \frac{1}{M} \sum_{n=1}^{M} \Phi_n \Phi_n^T = AA^T$$

(sample **covariance** matrix, NxN, characterizes the *scatter* of the data)

Step 4: compute the eigenvalues of  $C: \mathbf{\lambda}_1 > \mathbf{\lambda}_2 > \cdots > \mathbf{\lambda}_N$

Step 5: compute the eigenvectors of  $C: u_1, u_2, \ldots, u_N$

- Since C is symmetric,  $u_1, u_2, \dots, u_N$  form a basis, (i.e., any vector x or actually  $(x - \overline{x})$ , can be written as a linear combination of the eigenvectors):

$$x - \bar{x} = b_1 u_1 + b_2 u_2 + \dots + b_N u_N = \sum_{i=1}^{N} b_i u_i$$

Step 6: (dimensionality reduction step) keep only the terms corresponding to the K largest eigenvalues:

$$\hat{x} - \overline{x} = \sum_{i=1}^{K} b_i u_i$$

where  $K \ll N$

- The representation of  $\hat{x} - \bar{x}$  into the basis  $u_1, u_2, ..., u_K$  is thus

$$\begin{bmatrix} b_1 \\ b_2 \\ \dots \\ b_K \end{bmatrix}$$

- Linear transformation implied by PCA

- The linear transformation  $\stackrel{N}{R} \to \stackrel{K}{R}$  that performs the dimensionality reduction is:

$$\begin{bmatrix} b_1 \\ b_2 \\ \dots \\ b_K \end{bmatrix} = \begin{bmatrix} u_1^T \\ u_2^T \\ \dots \\ u_K^T \end{bmatrix} (x - \bar{x}) = U^T (x - \bar{x})$$

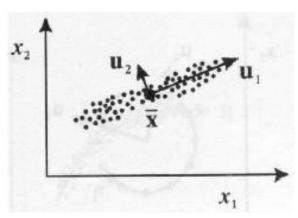

- Geometric Interpretation:

- PCA projects the data along the directions where the data varies the most.

- These directions are determined by the eigenvectors of the covariance matrix corresponding to the largest Eigenvalues.

- The magnitude of the Eigenvalues corresponds to the variance of the data along the eigenvector directions.

- Main Idea behind Eigenfaces:

- Suppose  $\Gamma$  is an  $N^2$ x1 vector, corresponding to an NxN face image I.

- The idea is to represent  $\Gamma$  ( $\Phi$ = $\Gamma$  mean face) into a low-dimensional space:

$$\hat{\Phi}-mean=w_1u_1+w_2u_2+\cdots w_Ku_K\,(K<< N^2)$$

• Computaion of the eigenfaces:

Step 1: obtain face images  $I_1, I_2, ..., I_M$  (training faces)

(very important: the face images must be centered and of the same size)

Step 2: represent every image  $I_i$  as a vector  $\Gamma_i$

Step 3: compute the average face vector  $\Psi$ :

$$\Psi = \frac{1}{M} \sum_{i=1}^{M} \Gamma_i$$

Step 4: subtract the mean face:

$$\Phi_i = \Gamma_i - \Psi$$

Step 5: compute the covariance matrix C:

$$C = \frac{1}{M} \sum_{n=1}^{M} \Phi_n \Phi_n^T = AA^T \quad (N^2 \times N^2 \text{ matrix})$$

where

$$A = [\Phi_1 \ \Phi_2 \cdots \Phi_M]$$

$(N^2 \times M \text{ matrix})$

Step 6: compute the eigenvectors  $u_i$  of  $AA^T$

The matrix  $AA^T$  is very large --> not practical !!

Step 6.1: consider the matrix  $A^T A (MxM \text{ matrix})$

Step 6.2: compute the eigenvectors  $v_i$  of  $A^T A$

$$A^T A v_i = \mu_i v_i$$

What is the relationship between  $us_i$  and  $v_i$ ?

$$A^T A v_i = \mu_i v_i \Longrightarrow A A^T A v_i = \mu_i A v_i \Longrightarrow$$

$$CAv_i = \mu_i Av_i$$

or  $Cu_i = \mu_i u_i$  where  $u_i = Av_i$

Thus,  $AA^T$  and  $A^TA$  have the same eigenvalues and their eigenvectors are related as follows:  $u_i = Av_i$ !!

Note 1:  $AA^T$  can have up to  $N^2$  eigenvalues and eigenvectors.

Note 2:  $A^T A$  can have up to M eigenvalues and eigenvectors.

Note 3: The M eigenvalues of  $A^TA$  (along with their corresponding eigenvectors) correspond to the M largest eigenvalues of  $AA^T$  (along with their corresponding eigenvectors).

Step 6.3: compute the M best eigenvectors of  $AA^T$ :  $u_i = Av_i$

(**important:** normalize  $u_i$  such that  $||u_i|| = 1$ )

Step 7: keep only K eigenvectors (corresponding to the K largest eigenvalues)

- Representing faces on to this basis

- Each face (minus the mean)  $\Phi_i$  in the training set can be represented as a linear combination of the best K eigenvectors:

$$\hat{\Phi}_i - mean = \sum_{j=1}^K w_j u_j, \ (w_j = u_j^T \Phi_i)$$

(we call the  $u_i$ 's eigenfaces)

- Each normalized training face  $\Phi_i$  is represented in this basis by a vector:

$$\Omega_i = \begin{bmatrix} w_1^i \\ w_2^i \\ \dots \\ w_K^i \end{bmatrix}, \quad i = 1, 2, \dots, M$$

- Face Recognition Using Eigenfaces

- Given an unknown face image Γ (centered and of the same size like the training faces) follow these steps:

Step 1: normalize  $\Gamma$ :  $\Phi = \Gamma - \Psi$

Step 2: project on the eigenspace

$$\hat{\Phi} = \sum_{i=1}^K w_i u_i \quad (w_i = u_i^T \Phi)$$

Step 3: represent

$$\Phi$$

as:  $\Omega = \begin{bmatrix} w_1 \\ w_2 \\ ... \\ w_K \end{bmatrix}$

Step 4: find  $e_r = \min_l ||\Omega - \Omega^l||$

Step 5: if  $e_r < T_r$ , then  $\Gamma$  is recognized as face l from the training set.

- The distance  $e_r$  is called <u>distance within the face space (difs)</u>

- Comment: we can use the common Euclidean distance to compute  $e_r$ , however, it has been reported that the *Mahalanobis distance* performs better:

$$\|\Omega - \Omega^k\| = \sum_{i=1}^K \frac{1}{\lambda_i} (w_i - w_i^k)^2$$

(variations along all axes are treated as equally significant)

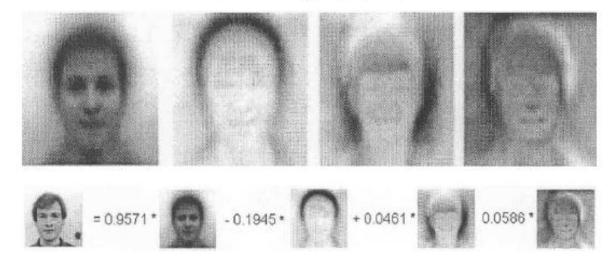

In the recognition phase, a subject face is normalized with respect to the average face and then projected onto face space using the eigenvector matrix. Next, the Euclidean distance is computed between this projection and all known projections. The minimum value of these comparisons is selected ans compared with the threshold calculated during the training phase. Based on this, if the value is greater than the threshold, the face is new. Otherwise, it is a known face.

#### 2.1.2 LDA:

Linear discriminant analysis (LDA) is another effective algorithm for face recognition. It is closely related to PCA and factor analysis in that they both look for linear combination of varaibles whice best explain the data. LDA explicitly attempts to model the difference between the classes of data. PCA on the other hand doesnot take into account any difference in class, and factor analysis builds the feature combinations based on differences rather than similarities. The face space created in LDA gives higher weight to the variations between individuals than those of the same individual. LDA is less sensitive than the phase spectrum. Indeed, it is the phase spectrum that contains information which humans use to identify faces. [4].

#### 2.1.3 ICA:

As PCA considers the 2<sup>nd</sup> order moments only it lacks information on higher order statistics. The Independent Component Analysis (ICA) accounts for higher order statistics and it identifies the independent source components from their linear mixtures. ICA thus provides a more powerful data representation than PCA [5] as its goal is that of providing an independent image rather than uncorrelated image decomposition and representation. ICA of a random vector searches for a linear transformation which minimizes the statistical dependence between its components [6]. ICA represents the input as an n-dimensional random vector. This random vector is then reduced using PCA, without losing the higher order statistics. Then, the ICA algorithm finds the covariance matrix of the result and obtain its factorized form. Finally, whitening, rotation and normalization are performed to obtain the Independent components that constitute the fce space of the individuals. Since the higher order relationships between pixels are used, ICA is robust in the presence of noise. Thus, recognition is less sensitive to "lighting conditions, changes in hair, make-up and facial ecxpressions" [7].

#### 2.1.4 Trace Transform:

The Trace transform [8], a generalization of the Radon transform, is a new tool for image processing which can be used for recognition objects under transformations, rotations, translation and scaling. To produce the Trace Transform one computes a functional along tracing lines of an image. Each line is characterized by two parameters, namely its distance

from the centre of the axes and the orientation. The trace transform is a global transform, applicable to full images. If we are going to use it to recognize faces, we must consider the local version of it. One of the key properties of the Trace transform is that it can be used to construct features invariant to rotation, translation and scaling. We should point out that invariance to rotation and scaling is harder to achieve than invariance to translation. It is assumed that an object is subjected to linear distortions like rotations, translations, and scaling. It is equivalent to saying that the image remains the same but viewed from the linearly distorted coordinate system.

#### 2.1.5 Neural Network:

A Neural Network is a system of programs and data structures that approximates the operation of the human brain. A neural network usually involves a large number of processors operating in parallel, each with its small sphere of knowledge and access to data in its local memory. Typically, a neural network is initially trained or fed large amounts of data and rules according to the data. A program can tell the network how to behave in response to an external stimulus or can initiate activity on its own. The main disadvantage of neural networks is that there is no clear method to find the initial topologies. The training takes long time. For face recognition, a neural network must be trained to recognize an individual. That is time consuming and not well suited for real-time applications [9].

#### Different Approaches For

#### **Face Recognition**

- Geometric Or Template based approaches.

- Piecemeal Or Wholistic approach.

- Appearance based Or Model based approaches.

- Template Or Statistical Or Neural network approaches.

# Statistical approaches for Face recognition

- Principal Component Analysis.(PCA)

- Discrete Cosine Transform.

- Linear Discriminant Analysis.

- Locality Preserving Projections.

- Gabor Wavelet.

- Independent Component Analysis.(ICA)

- Kernel PCA.

- Genetic Algorithms.

- Bayesian Network.

- Bi-dimensional regression, Ensemble based and other Boosting methods.

- Neural Network

#### Template matching And Neural Network approaches for Face recognition

- Adaptive appearance models.

- Neural networks with Gabor Filters.

- Neural networks and hidden Markov models.

- Fuzzy Neural netowks.

FIGURE 2.1: Face Recognition approaches

#### 2.2 FFT:

The fasr fourier transform (FFT) is simply a fast (computationally efficient) way to calculate the Discrete Fouries Transform.FFT algorithm was first published by Cooley and Tukey in 1965. This is a clever algorithm which can be used to transform a signal from time domain to fequency domain. The FFT greatly reduces the amount of calculation. It also reduces the noise of a signal that are present in time domain.

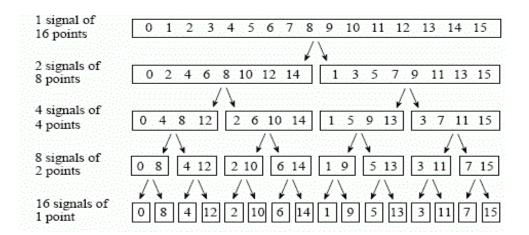

Functionally, the FFT decomposes the set of data to be transformed into a series of smaller data sets to be transformed. Then, it decomposes those smaller sets into even smaller sets. At each stage of preocessing, the results of previous stages are combined in special way. Finally, it calculates the DFT of each small data set. For example, an FFT of size 32 is broken into 2

FFTs of size 16, which are broken into broken 4 FFTs of size 8, which are broken into 8 FFTs of size 4, which are broken into 16 FFTs of size 2. [10]

The number of complex multiplication and addition operations required by the simple forms both the Discrete Fourier Transform (DFT) and Inverse Fourier Transform(IDFT) is of order  $N^2$  as there are N data points to calculate, each of which requires N complex arithmatic operations.

For length n input vector x, the DFT is a length n vector X, with n elements:

$$f_j = \sum_{k=0}^{n-1} x_k e^{-(2\pi i/n)jk}$$

$j = 0, \dots, n-1.$

On the other hand, DFT has algorithm complexity and hence is not a very efficient method. It will not be very useful for the majority of practical DSP applications. However, there are number of different Fast Fourier Transform (FFT) algorithms that enable the calculation of a signal much faster than DFT.

#### 2.3 How does FFT work:

As discussed earlier, the FFT operated by decomposing an N point time domain signal into each composed of a single point. The second step is to calculate the N frequency spectra corresponding to these N time domain signals. Lastly, the N spectra are synthesized into a single frequency spectrum [11].

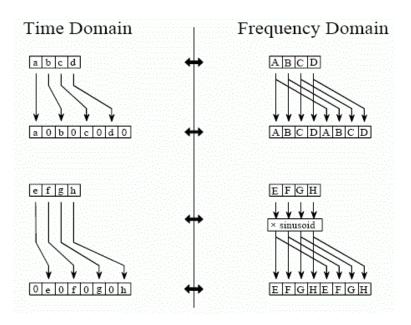

#### Figure 2.2: Time Domain Decomposition.

The above figure shows an example of the time domain decomposition used in the FFT. In this example, a 16 point signal is decomposed through four separate stages. The first stage breaks the 16 point signal into two signals each consisting of 8 points. The second stage decomposes the data into four signals of 4 points. This pattern continues until there are N signals composed of a single point. An interlaced decomposition is used each time a signal is broken in two, that is, the signal is separated into its even and odd numbered samples. After understanding the structure of decomposition we can say that using it, any N point signal can be easily simplified. It is nothing more than a reordering of the samples in the signal.

| Sample numbers<br>in normal order |        | Sample numbers<br>after bit reversal |        |

|-----------------------------------|--------|--------------------------------------|--------|

| Decimal                           | Binary | Decimal                              | Binary |

| 0                                 | 0000   | 0                                    | 0000   |

| 1                                 | 0001   | 8                                    | 1000   |

| 2                                 | 0010   | 4                                    | 0100   |

| 3                                 | 0011   | 12                                   | 1100   |

| 4                                 | 0100   | 2                                    | 0010   |

| 5                                 | 0101   | 10                                   | 1010   |

| 6                                 | 0110   | 6                                    | 0100   |

| 7                                 | 0111   | 14                                   | 1110   |

| 8                                 | 1000   | 1                                    | 0001   |

| 9                                 | 1001   | 9                                    | 1001   |

| 10                                | 1010   | 5                                    | 0101   |

| 11                                | 1011   | 13                                   | 1101   |

| 12                                | 1100   | 3                                    | 0011   |

| 13                                | 1101   | 11                                   | 1011   |

| 14                                | 1110   | 7                                    | 0111   |

| 15                                | 1111   | 15                                   | 1111   |

|                                   |        |                                      |        |

Figure 2.3: Rearrangement pattern required.

The given figure shows the rearrangement pattern required. On the left, the sample numbers of the original signal are listed along with their binary equivalents. On the right, the rearranged sample numbers are listed, also along with their binary equivalents. The important part is that the binary numbers are the reversals of each other. For example, sample 3 (0011) is exchanged with sample number 12 (1100). Likewise, sample number 14 (1110) is swapped with sample number 7 (0111), and so forth. The FFT time domain decomposition is usually carried out by a bit reversal sorting algorithm. This involves rearranging the order of the N time domain samples by counting in binary with the bits flipped left-for-right.

The next step in the FFT algorithm is to find the frequency spectra of the 1 point time domain signals. The frequency spectra of the 1 point signal is equal to itself, that means nothing is

required to do this step. Now each of the 1 point signals is a frequency spectrum, not a time domain signal.

The last step in the FFT is to combine the N frequency spectra in the exact reverse order that the time domain decomposition took place. The algorithm gets messy here. There is no shortcut for bit reversal. It is must to go back one stage at a time. In the first stage, 16 frequency spectra (1 point each) are synthesized into 8 frequency spectra (2 point each). In the second stage, the 8 frequency spectra (2 point each) are synthesized into 4 frequency spectra (4 point each) and so on. The last stage results the output of the FFT, a 16 point frequency spectrum.

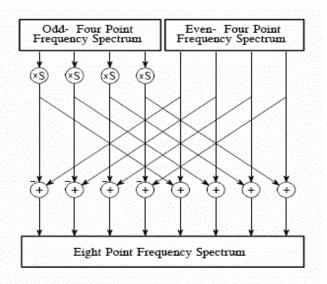

Figure 2.4: Time domain to Frequency domain.

The figure shows how two frequency spectra, each composed of 4 points, are combined into a single frequency spectrum of 8 points. This synthesis must undo the interlaced decomposition done in the time domain. In other work=ds, the frequency domain operation must correspond to the time domain procedure of combining two 4 point signals by interlacing. Considering two time domain signals, abcd and efgh. An 8 point time domain signal can be formed by two steps: dilute each 4 point signal with zeroes to make it an 8 point signal and then add the signals together. That is abcd becomes a0b0c0d0, and efgh becomes e0f0g0h0. Adding these two 8 point signal produces aebfcgdh. Diluting the time domain with zeroes corresponds to the duplication of the frequency spectrum. Therefore, the frequency spectra are combined in the FFT by duplicating them and then, adding the duplicated spectra together.

FFT synthesis flow diagram. This shows the method of combining two 4 point frequency spectra into a single 8 point frequency spectrum. The ×S operation means that the signal is multiplied by a sinusoid with an appropriately selected frequency.

Figure 2.5: FFT Synthesis flow diagram.

In order to match up added, the two time domain signals diluted with zeroes in a slightly different way. In one signal, the odd points are zero while in the other signal, the even points are zero. In other words, one of the time domain signals (0e0f0g0h) is shifted to the right by one sample. This time domain shift corresponds to multiplying the spectrum by a sinusoid. A shift in the time domain is equivalent to convolving the signal with a shifted delta function. This multiplies the signal's spectrum with the spectrum of the shifted delta function. The spectrum of a shifted delta function is a sinusoid. This was the basic of FFT. In case of image it may work differently, which has discussed later [11].

## **2.4 FFT Algorithms:**

As it has been discussed earlier DFT is a complex algorithm and not that efficient. Due to slow processing, it is not applicable in real world problems. To make DFT calculation faster and efficient there are number of FFT algorithms. Such as Radix-2, Butterfly, Cooley-tukey, Prime-factor FFT algorithm, Bruun's FFT algorithm, Radar's FFT algorithm, Bluestein's FFT algorithm etc. In our project we have used Cooley-tukey algorithm of FFT for recognition.

Cooley-tukey algorithm is the most common FFT algorithm. It is named after J.W Cooley and John Tukey. It re-expresses the Discrete Fourier Transform (DFT) of an arbitrary composite size  $N = N_1N_2$  in terms of smaller DFTs of sizes  $N_1$  and  $N_2$ , recursively, in order to reduce the computation time to O(NlogN) for highly-composite N.

The Cooley-Tukey algorithm can be combined arbitrarily with any other algorithm, as it breaks the DFT into smaller DFTs [12].

## 2.4.1 FFT implementation in NIOS 2 using Cooley-tukey Algorithom:

We have implemented FFT in NIOS2 using Cooley Tukey Algorithm. To achieve this we first created a processor using Qsys. We added various components such as CPU, SDRAM, PLL, Tri state bridge, Onchip memory etc. We made connection by connecting master to slave, source to sink, assigned base address and connected clock through PLL. After adding all the components, it automatically generates a blank code which we will use in our Verilog project.

After that we have written our Verilog code to interface in our FPGA through pin assignment. Then we included our SOPC code in Verilog code and interface with our board's pin which generates the .SOF file. Finally we have completed our hardware configuration.

Next, we have written our C code for FFT in Eclipse.

Finally, we wrote code for Cooley–Tukey Algorithm in C and implemented on NIOS 2 processor. We compiled the code and saw the result in the console pane.

```

Problems Tasks Console Properties Nios II Console Cons

```

Figure 2.6: Result of Cooley Tukey.

The inverse FFT re-transforms the image from frequency domain to spatial domain or time domain. The FFT and its inverse of a 2D image are given by the following equations:

$$F(x) = \sum_{n=0}^{N-1} f(n)e^{-j2\pi(x\frac{n}{N})}$$

$$f(n) = \frac{1}{N} \sum_{n=0}^{N-1} F(x) e^{j2\pi(x\frac{n}{N})}$$

Here f (m, n) is the pixel at f (m, n) coordinates, F(x,y) is the value of the image in the frequency domain at (x,y) coordinates. M and N are the dimensions of the image. Since image is two dimensional, we applied 2D FFT on it. The 2D transform can be done as two 1D transforms as shown below (shown only the horizontal direction) —one in the horizontal direction followed by the other in the vertical direction on the result of the horizontal transform. The end result is equivalent to perform the 2D transform in the frequency space.

$$F(x,y) = \sum_{m=0}^{M-1} \sum_{n=0}^{N-1} f(m,n) e^{-j2\pi(x\frac{m}{M} + y\frac{n}{N})}$$

$$f(m,n) = \frac{1}{MN} \sum_{m=0}^{M-1} \sum_{n=0}^{M-1} F(x,y) e^{j2\pi(x\frac{m}{M} + y\frac{n}{N})}$$

The FFT that's implemented in the application here requires that the dimensions of the image are power of two. An interesting property of FFT is that the transform of N points can be written as the sum of two N/2 transforms. This is important because some of the computations can be reused thus eliminating expensive operations [13].

The output of the Fourier Transform is a complex number and has a much greater range than the image in the spatial domain. Therefore, to accurately store these values, they are stored as floats. Furthermore, the dynamic range of the Fourier coefficient is too large to be displayed on the screen and these values are jscaled to bring them within the range of values that can be displayed [13].

A modern interpretation of FFT states that, "any well-behaved function can be represented by a superposition (combination or sum) of sinusoidal waves. It can be said that, the frequency domain representation is just another way to store and reproduce the spatial domain image [14].

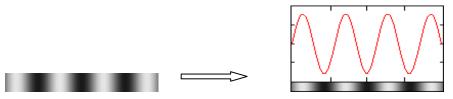

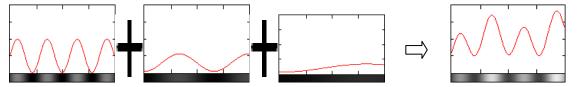

If we take a single row or column of pixel from any image and graph it, we will find that it looks more like a wave.

If the fluctuations are more regular in spacing and amplitude, we would get something more like a wave pattern. Such as,

If we were to add more waves together, we might get a pattern that is closer to the original image.

The superposition of waves or addition ojf waves in much closer, but still does not match the image pattern. However we can continue in this manner, adding more waves and adjusting them until the resulting composite wave gets closer and closer to the actual profile of the original image. Eventually by adding enough waves we can exactly reproduce the original image. Therefore, it can be said that images are nothing but the summation of sine and cosine waves.

In other words, by adding together a sufficient number of sine waves of the right frequency and amplitude, any fluctuating pattern can be reproduced. Fourier Transform generally works out to find out the waves that comprise an image [14].

The Fast Fourier Transform is an important image processing tool which is used to decompose an image into its sine and cosine components or waves. Undoubtedly, the output of FFT represents the image in the frequency domain, while the input image is the spatial domain or time domain equivalent. In the Fourier domain image, each point represents a particular frequency contained the spatial domain image.

If we want to access the geometric characteristic of a spatial domain image, then FFT can be used. Because the image in the Fourier domain is decomposed into its sinusoidal components, which is the easy way to examine or process certain frequencies of the image, that influences the geometric structure in the spatial domain [14].

In most implementations the Fourier image is shifted in such a way that the DC-value or the image mean is displayed in the center of the image. The further away from center of an image point is, the higher is its corresponding frequency [15] [16].

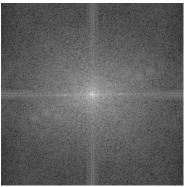

In general if we apply FFT on an image, we get the complex result. The magnitude calculated from the complex result is shown in [15] [16].

Figure 2.7: The magnitude calculated from the complex result

It is seen that the DC value is by far the largest component of the image. However, the intensity values in the Fourier image or the dynamic ranges of the Fourier coefficients is too large to be displayed on the screen, therefore all other values appear as black. If we apply logarithmic transformation to the image we obtain

Figure 2.8: Magnitude after logarithmic transform.

We can see that the image contains component of all frequencies, but their magnitude gets smaller for higher frequencies. Hence, low frequencies contain more image information than the higher ones. The transformed image tells us that there are two dominating directions in the Fourier image, one passing vertically and one horizontally through the center. These originate from the regular patterns in the background of the original image.

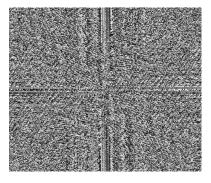

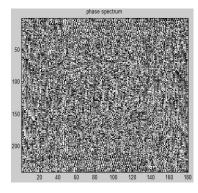

The phase of the FFT of the same image can be shown as

Figure 2.9: The phase of FFT

The value of each point determines the phase of the corresponding frequency. As in the magnitude image, we can identify the vertical and horizontal lines corresponding to patterns in the original image. The phase image does not contain much new information about the structures of the spatial domain image. Therefore, we will confine ourselves to displaying only the magnitude of the Fourier Transform unless our interest does not belong to reconstruct the image [15] [16].

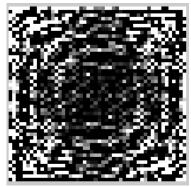

On the other hand, if we do not separate the magnitude and phase part of an image, after applying FFT on that image we will obtain

Figure 2.10: Magnitude and Phase of a Fourier image.

The above diagram contains both the magnitude and phase value of a Fourier image. In our project we have considered the both parts.

#### 2.6 Applications:

Face recognition systems have achieved a huge popularity due to wide range of applications. It has been an area of research from very beginning. Applications exist in two main categories: practical application and research application.

From practical standpoint face recognition is extensively used in security systems. The FBI is already using it to identify suspects who are caught on surveillance cameras. The places like airports, International borders the need is raising for a face recognition system that identifies individuals. Face recognition systems can be used in entertainment purpose like video games.

In research applications, face recognition has paved the way for research in areas like image and video processing. Due to the increasing demand of this system into many sectors, researchers are working on developing many algorithms of face recognition. Principle Component Analysis (PCA and KPCA), Linear Discriminant Analysis (LDA), Independent component analysis (ICA), genetic algorithms, neural networks, FFT these are the algorithms established so far by the researchers. In our project we will be focusing on implementing FFT and PCA on the FPGA board. Then we will compare the results at the end. The FFT is used in a wide range of applications, such as image analysis, image filtering, image reconstruction, image compression and we used it for image recognition as well.

## 2.7 Benefits of using FPGA-

As it has mentioned earlier that one of the important objectives of our project is to get acquainted with FPGA board, since it is a complete new area for us. While researching we have known very interesting things about FPGA and had decided to choose our project based on this board.

An FPGA is exactly what the name suggests: a Field Programmable Gate Array. We program it as a piece of hardware. The FPGA basically implements look up tables. It is good at doing complex logic very fast. Using hardware programming languages such as VHDL and Verilog someone can create complex logic structures. Speed is the biggest advantage of FPGA. It is reprogrammable. More than one project can be implemented using same FPGA board.

FPGAs exceed the computing power of digital signal processors by taking the advantage of hardware parallelism. It accomplishes more per clock cycle. It has specialized functionality to closely match application requirements. It supports long term maintenance. As a product, functional enhancement can be made, without spending time on redesigning hardware or modifying board layout. However, FPGAs are much expensive than microcontrollers. If our design needs greater integration density then FPGAs are appropriate. For smaller projects we go for microcontrollers [17].

# **Chapter 3:**

# **MATLAB Implementation**

# 3.1 Basic Approach

Before implementing the process in hardware, we verified our project in Matlab first. In our project first we have used FFT as a basic algorithm.

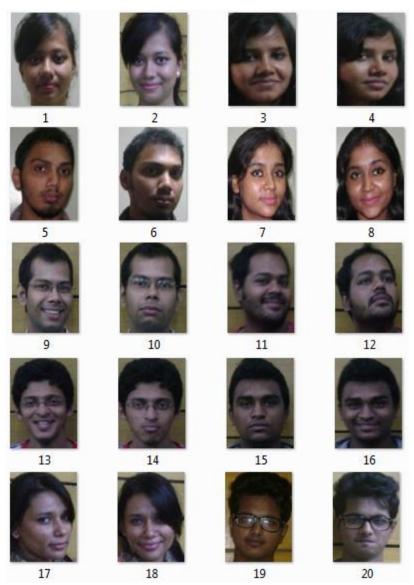

- We have made our own database consisting of Brac University students and used them to develop our recognition system. The database that contains the images of different expressions of the students is named "Train Database". It has total 20 images. Here we have considered two different expression of an image.

- We have used another database which is named the "Test Database". The database

that contains the image that will be compared with the train database's image is

named the "Test Database". It may contain image inside or outside image of Train

Database.

- Firstly we placed the Train Database containing 20 images in a directory using Matlab.

- Then we resized the image into 50:50 to ensure same dimension for every image.

- For the ease of further processing we converted the RGB data into Gray scale, which reduces the matrix dimension.

- After that we have applied FFT on the entire database using the Matlab function FFT2, as images are two dimensional.

- Next we have computed the mean value of the FFT images using mean2 function.

We repeated the above steps on test database also.

- Then we made an array containing the differences of means between test and train databases. This is to mention that Test database can contain a single image.

- We have set a threshold by trial and error method which is 21.

- If the difference of mean is less than 21, it has been declared that the image is matched. For the values that are more than 21, we considered the images are not matched. Images that are not included in the Train Database will not match in the end.

The whole procedure can be shown in a following flow chart.

Figure 3.1: Flowchart of FFT based face recognition.

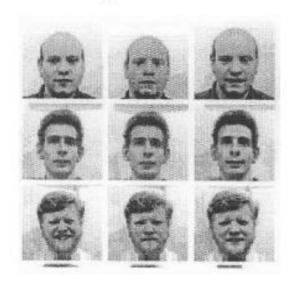

Figure 3.2: Train Database

In Figure 3.2, our Train Database is shown. It is noticeable in the database, that the images we have taken are not uniform. One image has the light effect, another may not. One is smiling, another is not. It has been done intentionally, so that we can identify the limitations of FFT spontaneously. To check, FFT's performance whether it can match considering the light effect and different expressions.

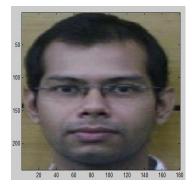

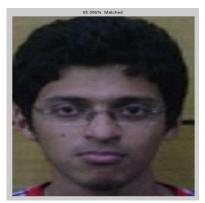

Another Database we have the Test Database it may or may not be from the Train Database. It can include only one image. For a while let's consider the Test Database has the following image.

Figure 3.3: Test Database Image

Since another two expressions of the above image is present in the Train Database, if we run the system the answer will be "Matched".

# 3.2 Two dimensional FFT on an image:

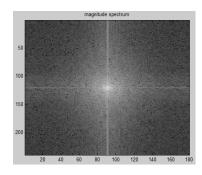

In image processing, the 2D FFT allows one to see the frequency spectrum of the data in both dimensions and lets one visualize filtering operations more easily. The 2D FFT is simply a Fourier transform of one dimension of the data, followed by a Fourier transform over the second dimension of the data. In the following example we have performed a 2D FFT on an image, switched the magnitude and phase content. Now we would get to see what actually happened in Matlab when we applied 2D FFT of an image from our own database.

Considering the code written below [19].

```

close all;

clear all;

img = imread('Farhan.jpg','jpg');

imagesc(img)

img = fftshift(img(:,:,2));

F = fft2(img);

figure;

```

```

imagesc(100*log(1+abs(fftshift(F)))); colormap(gray);

title('magnitude spectrum');

figure;

imagesc(angle(F)); colormap(gray);

title('phase spectrum');

```

Before entering into our main recognition code, using the above code we applied FFT2 on an image to observe the output and it results

**The Original Image**

**Magnitude Spectrum**

**Phase Spectrum**

The 2D FFTs are accomplished using fft2. The image files are imported as unit8, so they should be converted to double arrays before doing the FFTs. The FFT of real, non-even data is complex, so the magnitude and phase of the 2D FFTs should be displayed. The function fftshift is used to shift the quadrant of the FFT around to see the lowest frequencies in the center of the plot [18].

If we look at the FFT of above image, it can be seen that most of the energy in the Fourier domain is present in the center on the image, which corresponds to low frequency data in the image domain. This corresponds to many gradual changes in the image. The phase of the FFT is hard to interpret and generally looks like noise. However, the phase holds a great deal of the information needed to reconstruct the image. To demonstrate the role of the phase of the FFT, we switched the magnitude and phase of the image. If we want to reconstruct the image it is necessary to show the magnitude and phase part separately. However, our project is not concerned with reconstructing the image using inverse 2D FFT; therefore we have considered the magnitude and phase part together in a single frame [18].

## 3.3 Functions used in Matlab:

In this section we will discuss the functions that have been used in Matlab for recognition and the results.

```

%Import images

sdirectory = 'Train Database';

tifffiles = dir([sdirectory '/*.jpg']);

I = cell(1,numel( tifffiles));

for k = 1:length(tifffiles)

filename = [sdirectory '/' tifffiles(k).name];

I{k} = imread(filename);

%Resize images

Rb=imresize(I{k},[50 50]);

%RGB to Gray images

J=rgb2gray(Rb);

```

figure, imshow(J)

figure, imshow(uint8(fftb))

"Imread" is used to import the images into Matlab. This function can handle most of the standara image file formats, such as bmp, jpg, tiff and png [18]. In our code "Imshow" is usd to display the images. "Imshow" is one of several functions that plot images, but this function automatically eliminates the axes, displaying image nicely.

This function works well for original images. When we applied "Imshow" in our original image it shows

**Original Image**

After applying RGBtoGray function in the original image we obtained

**Gray scale Image**

After turning the original image into gray scale, we performed 2D FFT on the image considering both magnitude and the phase, it results

**FFT Image**

FFT based face recognition is able to recognize faces with slight change in expression. In Test Database we put an image of different expression of one the images of Train Database. After simulation they matched. Though it is not effective as PCA algorithm, yet to some extend it works perfectly and we get

85.096% Matched

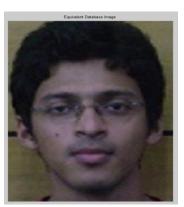

**Equivalent Database Image**

We experimented taking another image of different expression along with glasses to verify whether FFT can recognize it and it showed

78.6761% Matched

**Equivalent Database Image**

Therefore, it can be said undoubtedly that FFT can recognize faces of different expressions successfully.

On the other hand, if we place the same image to Test Database that is already stored to the Train Database, the accuracy is 100%. For example

100% Matched

**Equivalent Database Image**

This means if we test exactly the same image, this algorithm can identify the same image from the train database.

Therefore, we used the above steps to verify if our proposed algorithm is suitable, and also to what extent, as a face recognition algorithm.

# Chapter 4

# **4.1 DE0 Board and TRDB\_D5M Specifications:**

The field-programmable gate array (FPGA) is a semiconductor device that can be programmed after manufacturing. We can use a FPGA to implement any logical function that an application-specific integrated circuit (ASIC) could perform. Unlike previous generation FPGAs using I/Os with programmable logic and interconnects, today's FPGAs consist of various mixes of configurable embedded SRAM, high-speed transceivers, high-speed I/Os, logic blocks, and routing. Most importantly, an FPGA contains programmable logic components called logic elements (LEs) and a hierarchy of reconfigurable interconnects that allow the LEs to be physically connected. We can configure LEs to perform complex combinational functions, or merely simple logic gates like AND and XOR. In most FPGAs, the logic blocks also include memory elements, which may be simple flipflops or more complete blocks of memory. In addition, newer FPGA families are being developed with hard embedded processors, transforming the devices into systems on a chip (SoC) [20].

Advantages of using FPGAs over ASICs and ASSPs are including:

- Rapid prototyping

- Shorter time to market

- The ability to re-program in the field for debugging

- Lower NRE costs

- Long product life cycle to mitigate obsolescence risk

# 4.2 Cyclone III FPGA: Architecture

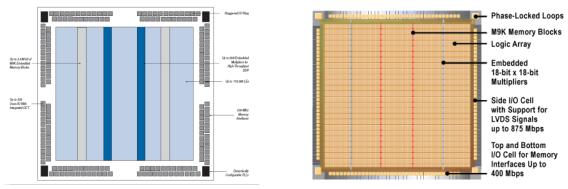

Figure 4.1 : Cyclone III Device Architecture Overview Figure 4.2 : Cyclone III FPGA Floorplan

Cyclone<sup>®</sup> III FPGAs has low power, high functionality, and low cost. The 65nm architecture consists of up to 120K vertically arranged logic elements (LEs), 4 Mbits of embedded memory arranged as 9-Kbit (M9K) blocks, and 200 18x18 embedded multipliers. Cyclone III LS FPGAs have a memory-rich and multiplier-rich floor plan consisting of up to 200K logic elements, 8.2 Mbits of embedded memory, and 396 embedded multipliers [20].

Both architectures include highly efficient interconnect and low-skew clock networks, providing connectivity between logic structures for clock and data signals. The logic and routing core fabric is surrounded by I/O elements (IOEs) and phase-locked loops (PLLs), as shown in Figure 4.2.

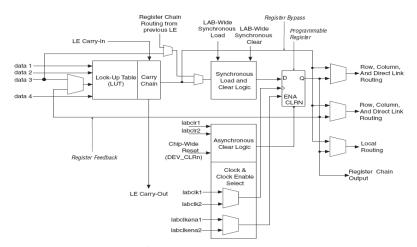

## **4.3 Logic Elements:**

The logic array consists of LABs, with 16 LEs, LAB control signals, LE carry chains, Resister chains and local interconnect in each LAB. LABs are grouped into rows and columns across the device. Cyclone III devices range from 5,136 to 119,088 LEs. A LE, is compact and provides advanced features with efficient logic utilization. Each LE has four-input look-up table (LUT), a programmable register, a carry chain connection, a register chain connection and support for resister packing and resister feedback. Moreover, it has the ability to drive all types of interconnect: local, row, column, resister chain and direct link interconnect [20].

Figure 4.3: Cyclone III Logic Elements

# 4.4 Cyclone III FPGA: Applications

The Cyclone III FPGAs are the first to implement a complete suite of security features at the silicon, software, and IP level on a low-power, high-functionality FPGA platform [20].

Cyclone III FPGAs has the following application areas:

- Automotive

- Consumer

- Displays of all sizes

- Industrial

- Military

- Video and image processing

- Wireless communications

## 4.5 Altera Cyclone III 3C16 FPGA device:

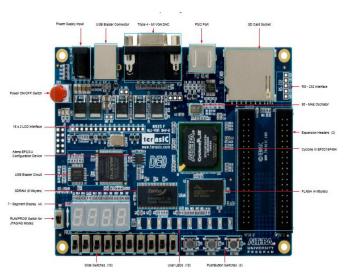

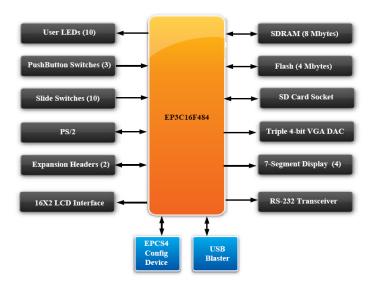

The DE0 board has many features that allow the user to implement a wide range of designed circuits, from simple circuits to various multimedia projects. DE0 has Altera Cyclone® III 3C16 FPGA device, Altera Serial Configuration device – EPCS4, USB Blaster, 8-Mbyte SDRAM, 4-Mbyte Flash memory, SD Card socket, 3 pushbutton switches, 10 toggle switches, 10 green user LEDs,50-MHz oscillator for clock sources, VGA DAC with VGA-out connector, RS-232 transceiver, PS/2 mouse/keyboard connector, Two 40-pin Expansion Headers [20].

Figure 4.4: DE0 FPGA Specifications.

To provide maximum flexibility for the user, all connections are made through the Cyclone IIII FPGA device. Thus, the user can configure the FPGA to implement any system design.

Figure 4.5: DE0 FPGA Components.

DE0 board has 50 MHz Clock input and Cyclone IIII 3C16 which has 15,408 LEs, 56 M9K Embedded Memory Blocks, 504K total RAM bits, 56 embedded multipliers, 4 PLLs, 346 user I/O pins and FineLine BGA 484-pin package. It has Built-in USB Blaster circuit, SDRAM which has one 8-Mbyte Single Data Rate Synchronous Dynamic memory chip and Supports 16-bits data bus. In addition it has 4-Mbyte NOR Flash memory which Support Byte (8-bits)/Word (16-bits) mode and General User Interfaces which includes 10 Green color LEDs (Active high), 4 seven-segment displays (Active low) and 16x2 LCD Interface (Not include LCD module). Moreover, it has SD card socket which Provides both SPI and SD 1-bit mod SD Card access. Furthermore, it has Pushbutton switches, Slide switches, VGA output, Serial ports and two 40-pin expansion headers [20].

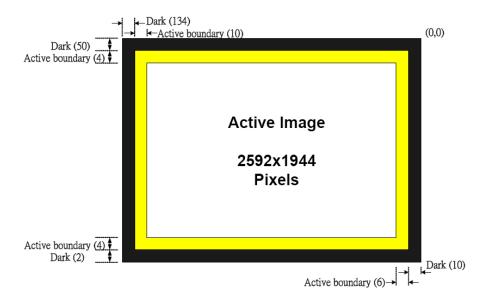

# **4.6 Camera Module Pixel Array Structure:**

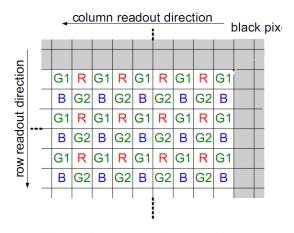

TRDB-D5M Camera Module is used to capture the image of a person. The address start from (Column 0, Row 0) and it locates at the upper-right corner of the whole region. TRDB-D5M pixel array consists of 2,752 column by 2,004 row. However, whole region is not considered as an active region. Array consists of a 2,592 column by 1,944 row is considered as an active region including boundary region. In addition, boundary region is not used to show pictures

to avoid edge effects. Moreover, the black region which is surrounded by the boundary region is not used to display any pictures.

Figure 4.6: Pixel Array Description

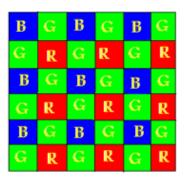

Pixels are output in a Bayer pattern format consisting of four "colors"—Green1, Green2, Red, and Blue (G1,G2, R, B)—representing three filter colors. When no mirror modes are enabled, the first row output alternates between G1 and R pixels, and the second row output alternates between B and G2 pixels. The Green1 and Green2 pixels have the same color filter, but they are treated as separate colors by the data path and analog signal chain.

## 4.7 I2C Protocol:

In early 80's Philips designed I2C bus. This name is taken from Inter IC and mostly called as IIC or I2C [21]. It permits simple communication to achieve data communication between components that resides on same circuit board. It is not as famous as USB or Ethernet but much of electronic devices depend on I2C protocol. It is unique in the use of special combination of signal conditions and changes. It entails only 2 signals or bus lines for serial communications, one is clock and other is data, clock is recognized as SCL or SCK (for serial clock) and data is known as SDA. I2C protocol uses certain registers for common resolutions, their frame rates, LVAL, FVAL, exposure time, green gain, red gain and blue gain.

# 4.8 Camera Image Acquisition System:

When FPGA gets power to start, system initializes sensor chip and determines mode of operation and certain value of registers in image sensor controls corresponding parameters

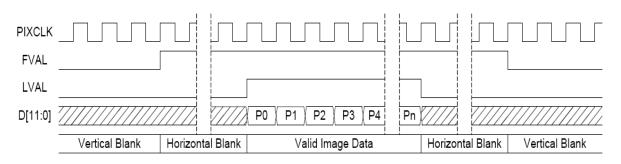

[22]. From the following figure it can be seen that LVAL is vertical synchronization signal and FVAL is horizontal reference signal, PIXCLK represents pixel output synchronization signal. When FVAL signal goes high, the system sends out 1280 (number of columns) data at the same time, and the LVAL will appear 960 (number of rows) times high during the FVAL high. One frame image with resolution 1280\*960 is collected completely when the next FVAL signal rising edge arrives.

Figure 4.7: Default Pixel Output Timing

## 4.8.1 Frame Valid

This hardware pin is asserted during the total No. of active rows in the image. This pin is also responsible for the start and end of the pixel stream in the image. This pin goes high only once during each image provided by the camera. In above figure, FVAL goes high when camera provides image.

For a complete configuration, we also need to write the valid values for the various configuration registers in the camera. For example we configure the camera when to start row and columns and what should be the rate of images provided by the camera. Digital and analog gain for the three color components are adjusted to give best performance in specific environment.

## 4.8.2 Line Valid

This is the hardware pin on the camera which goes high during the valid pixels in a row of the image. This pin asserted number of row times in the image. For our configuration, this pin is asserted 960 times for one image. Each time "line valid" pin goes high, there are 1280 pixels transferred by the camera. Each pixel is transferred by triggering the "pixel clock" pin in the camera.

## 4.9 Bayer to RGB conversion in FPGA

Image sensor exports the image in Bayer format and in FPGA a Bayer color filter array converts Bayer pattern image into RGB. The pattern of this filter shows that half of its pixels are green while quarter of the total number is assigned for red and same for blue color. Odd pixel lines in the image sensor contain green and blue components, while the even lines contain red and green color components.

Figure 4.8: Bayer Pattern Filter

Above figure shows a bayer pattern filter and each pixel shows only one component of each primary color. To convert an image from Bayer format to RGB format, each pixel needs to have values of all three primary colors.

#### 4.9.1 RGB conversion

Camera is configured in such a way that a Bayer image is getting 960 rows and 1280 columns with 5 frames per second. Camera outputs the data in Bayer pattern with 12 bit on parallel bus. In Bayer pattern format, each pixel contains one of three primary colors, which consists of four colors: green1, blue, red and green2. The layout is shown in following figure that means two of the remaining color components are missing in each pixel of Bayer pattern.

Figure 4.9: Bayer image Pixels

This bayer pattern data is then passed through a module which converts it into RGB values, and utilizes four pixels of Bayer pattern format to construct one pixel of RGB. After applying formula, other two component's value can be find out. Camera manages green pixels as two different colors depending on which line they are coming from. In Bayer format, when 1<sup>st</sup> complete row and only first 2 pixels of the second row complete scanning, then filter creates the 1<sup>st</sup> pixel of RGB.

Figure 4.10: RGB pixel from Bayer format

Above figure shows a RGB pixel format. As the second row out of camera completes scanning, first complete row of RGB image is created. Similarly with the completion of 3<sup>rd</sup> and 4<sup>th</sup> row of Bayer pattern image a 2<sup>nd</sup> RGB pixel row completed. As the pixels are being received by the camera, they are simultaneously being transformed into RGB and simultaneously being sent to the memory module in the FPGA. After that we converted this RGB pixel into grayscale using the following formula

#### **Grayscale = (Red+ Green+ Blue)/3**

This conversion is used to reduce the matrix dimension. Next this memory module stores this pixel in the external SDRAM through external bus and so on.

# **Chapter 5 Hardware Implementation:**

Altera Corporation is the pioneer of programmable logic solutions. And we have used Altera's FPGA board to use in our project. Our FPGA board is from the Cyclone III device family and its model number is DE0 [27]. In our project we have used 'Qsys' extensively. Qsys is the Altera's system integrated tool.' Qsys' system integration tool saves significant amount of time and effort in the FPGA design process by automatically generating interconnect logic to connect intellectual property (IP) functions and subsystems. Qsys is the next-generation SOPC Builder tool that is powered by a new FPGA-optimized network-on-a-chip (NoC) technology delivering higher performance, enhanced design reuse, and faster verification compared to SOPC Builder [27].

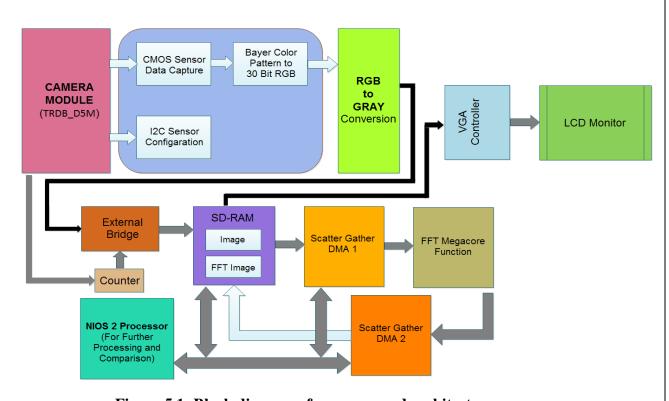

A block diagram of our problem formulation for the 'Qsys' part is given below:

Figure 5.1: Block diagram of our proposed architecture.

The hardware architecture we proposed is as follows:

An image is captured from the FPGA board compatible camera module TRDB\_D5M.

The output pixels or the raw data are in Bayer color Pattern.

Therefore the data is passed through Bayer color pattern to 30 bit RGB (RED, GREEN, BLUE) module.

Once the pixels are in RGB, they are then converted into Grayscale (to reduce down the number of planes, in this case from 3 planes to 1 plane, to reduce the complexity of data manipulation).

This Grayscale data (or the captured image) is then stored in memory (SDRAM) through the assistance of the external bridge bus and SDRAM controller.

At this stage, to verify if the data is actually stored in the SDRAM we can include the VGA controller and the Video In decoder and display the data on a LCD monitor.

Once the data (or the image) is stored in the SDRAM, the data is accessed from the SDRAM through the Scatter Gather DMA (direct memory access) controller and is passed to the FFT block (Fast Fourier Transform block).

The output, that is, the data after FFT is again stored in SDRAM, this time at a different memory location (in order to keep both the stored data). At this stage another DMA controller is used to transfer these data and access the SDRAM.

Then both sets of data are now available in the SDRAM.

The above steps are followed again, to keep the information of another image (the concept of creating database).

Then Nios II carries out further processing of comparison and recognition for both the images (FFT values are compared).

The data route can be viewed from the RTL viewer to get an idea on the logic gate implementation for different blocks we have used.

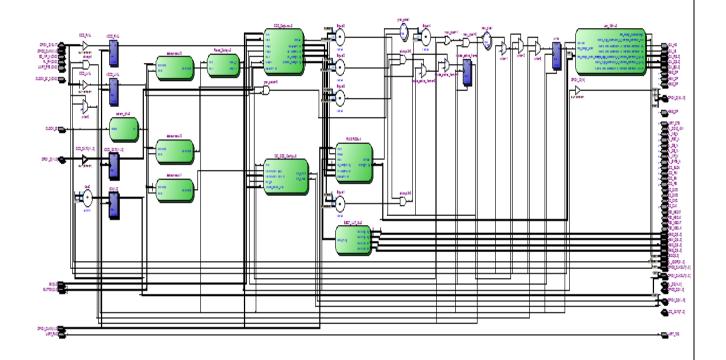

Figure 5.2: RTL Viewer

To accomplish the above processes we have used some 'Qsys' components.

The components that we have considered putting in our system are as follows--- (the order of the components might not be exactly as the following list)

- 1) External Bus to Avalon Bridge.

- 2) SDRAM controller.

- 3) Avalon ALTPLL.

- 4) SG-DMA (scatter-gather) Controllers.

- 5) VGA controller.

- 6) Video DMA Controller.

- 7) FFT block generated from Mega Wizard.

- 8) NIOSII Processor.

- 9) On-chip Memory (RAM).

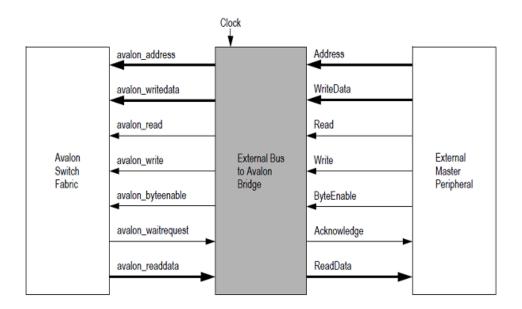

- **5.1 External Bus to Avalon Bridge:** We have used this IP core or component to make an interface with our external camera module to our system. This bridge provides a

simple interface for a peripheral device (in our case, the TRDB\_D5M) to connect with the Avalon

Switch Fabric as a master device. The Bridge creates a bus-like interface to which one or more "master" peripherals can be connected.[34]

Figure 5.3: External bus to avalon bridge.

The Bus signals provided are: 1) Address- k bits (up to 32).

- 2) Read-1 bit.

- 3) Write- 1 bit.

- 4) Byte Enable- 16,8,4,2 or 1 bit.

- 5) Write Data- 128,64,32,16 or 8 bits.

- 6) Read Data- 128,64,32,16 or 8 bits.

- 7) Acknowledge- 1 bit.

The bus is synchronous — all bus signals must be read by the master peripheral on the rising edge of the clock. A bus transfer happens when either Write or Read is high. For our project we coded in such a way that the bridge does the work of a write command as we want to write the data from the camera to the SDRAM.

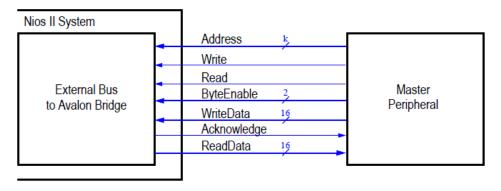

Figure: External Bus to Avalon Bridge with Nios II system

Two parameters are needed to specify in 'Qsys' External Bridge to Avalon core:

- 1) Data Width the number of data bits involved in a transfer. The Bridge supports data widths of 8,16,32,64, and128 bits.

- 2) Address Range the addressable space supported by the Bridge. It is possible to specify the address range of 1,

- 2,4,8,16,32,64,128,256,512,and 1024, in either bytes, kilobytes (kB) or megabytes (MB).

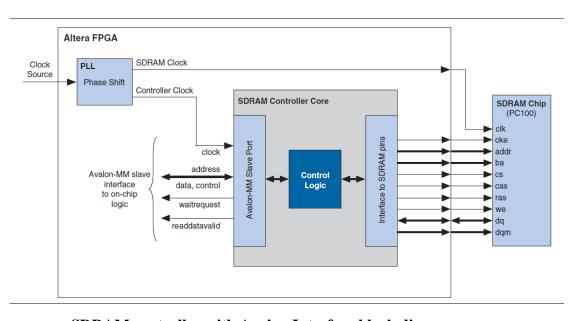

- **5.2 SDRAM controller:** it allows designers to create custom systems in an Altera device that connect easily to SDRAM chips. This SDRAM controller connects to one or more SDRAM chips, and handles all SDRAM protocol requirements [23].

SDRAM controller with Avalon Interface block diagram.

#### **Avalon MM interface**

The Avalon-MM slave port is the user-visible part of the SDRAM controller core. The slave port presents a flat, contiguous memory space as large as the SDRAM chip(s). The Avalon-MM interface behaves as a simple memory interface. There are no memory-mapped configuration registers.

## **Signal Timing and Electrical Characteristics**

The timing and sequencing of signals depends on the arrangement of the core. The hardware designer configures the core to match the SDRAM chip chosen for the system. The SDRAM controller Mega Wizard has two pages: **Memory Profile** and **Timing**. These can be configured by using the option 'Custom' or we could use any of the several predefined SDRAM configurations provided if the If the SDRAM subsystem on the target board (DE0 in our case) matches one of the preset configurations. Some of the preset configurations are for

- Micron MT8LSDT1664HG module

- Four SDR100 8 MByte × 16 chips

- Single Micron MT48LC2M32B2-7 chip

- Single Micron MT48LC4M32B2-7 chip

- Single NEC D4564163-A80 chip (64 MByte × 16)

- Single Alliance AS4LC1M16S1-10 chip

- Single Alliance AS4LC2M8S0-10 chip

But we have configured it for our convenience which was appropriate for our SDRAM subsystem.

The **Memory Profile** page allows one to indicate the structure of the SDRAM subsystem such as address and data bus widths, the number of chip select signals, and the number of banks.

| Settings                                                  |              | Allowed<br>Values                   | Default<br>Values | Description                                                                                                                                                                                                                                                       |