### **NOTICE**

The drivers and utilities for Octagon products, previously provided on a CD, are now in a self-extracting zip file located at the Octagon Systems web site on the product-specific page. Download this file to a separate directory on your hard drive, then double click on it to extract the files. All references in this manual to files and directories on the CD now refer to files in the Utilities zip file.

## OCTAGON SYSTEMS

Embedded PCs For Extreme Environments

**2040 PC/104 CPU User's Manual**5167 (1099)

DiskOnChip® is a registered trademark of M–Systems. LynxOS® is a registered trademark of Lynx Real–Time Systems, Inc. Micro  $PC^{TM}$ , PC SmartLink $^{TM}$ , Octagon Systems Corporation®, the Octagon logo and the Micro PC logo are trademarks of Octagon Systems Corporation. PICO  $FA^{TM}$  is a trademark of Phoenix Technologies Ltd. QuickBASIC® is a registered trademark of Microsoft Corporation. QNX® is a registered trademark of QNX Software Systems Ltd. ROM–DOS $^{TM}$  is a trademark of Datalight. Windows  $PC^{TM}$ , Windows  $PC^{TM}$ , and Windows  $PC^{TM}$  are trademarks of Microsoft Corporation.

Copyright 1999—Octagon Systems Corporation. All rights reserved. However, any part of this document may be reproduced, provided that Octagon Systems Corporation is cited as the source. The contents of this manual and the specifications herein may change without notice.

The information contained in this manual is believed to be correct. However, Octagon assumes no responsibility for any of the circuits described herein, conveys no license under any patent or other right, and makes no representations that the circuits are free from patent infringement. Octagon makes no representation or warranty that such applications will be suitable for the use specified without further testing or modification.

Octagon Systems Corporation general policy does not recommend the use of its products in life support applications where the failure or malfunction of a component may directly threaten life or injury. It is a Condition of Sale that the user of Octagon products in life support applications assumes all the risk of such use and indemnifies Octagon against all damage.

Technical support: 303–426–4521

Telephone: 303–430–1500 FAX: 303–426–8126

Web site: www.octagonsystems.com

#### **IMPORTANT!**

#### Please read the following section before installing your product:

Octagon's products are designed to be high in performance while consuming very little power. In order to maintain this advantage, CMOS circuitry is used.

CMOS chips have specific needs and some special requirements that the user must be aware of. Read the following to help avoid damage to your card from the use of CMOS chips.

## **■ Using CMOS circuitry in industrial control**

Industrial computers originally used LSTTL circuits. Because many PC components are used in laptop computers, IC manufacturers are exclusively using CMOS technology. Both TTL and CMOS have failure mechanisms, but they are different. Described below are some of the failures which are common to all manufacturers of CMOS equipment. However, much of the information has been put in the context of the Micro PC.

Octagon has developed a reliable database of customer-induced, field failures. The average MTBF of Micro PC cards exceeds 11 years, yet there are failures. Most failures have been identified as customer-induced, but there is a small percentage that cannot be identified. As expected, virtually all the failures occur when bringing up the first system. On subsequent systems, the failure rate drops dramatically.

- Approximately 20% of the returned cards are problem—free. These cards, typically, have the wrong jumper settings or the customer has problems with the software. This causes frustration for the customer and incurs a testing charge from Octagon.

- Of the remaining 80% of the cards, 90% of these cards fail due to customer misuse and accident. Customers often cannot pinpoint the cause of the misuse.

- Therefore, 72% of the returned cards are damaged through some type of misuse. Of the remaining 8%, Octagon is unable to determine the cause of the failure and repairs these cards at no charge if they are under warranty.

The most common failures on CPU cards are over voltage of the power supply, static discharge, and damage to the serial and parallel ports. On expansion cards, the most common failures are static discharge, over voltage of inputs, over current of outputs, and misuse of the CMOS circuitry with regards to power supply sequencing. In the case of the video cards, the most common failure is to miswire the card to the flat panel display. Miswiring can damage both the card and an expensive display.

- **Multiple component failures:** The chance of a random component failure is very rare since the average MTBF of an Octagon card is greater than 11 years. In a 7 year study, Octagon has <u>never</u> found a single case where multiple IC failures were <u>not</u> caused by misuse or accident. It is very probable that multiple component failures indicate that they were user—induced.

- **Testing "dead" cards:** For a card that is "completely nonfunctional", there is a simple test to determine accidental over voltage, reverse voltage or other "forced" current situations. Unplug the card from the bus and remove all cables. Using an ordinary digital ohmmeter on the 2,000 ohm scale, measure the resistance between power and ground. Record this number. Reverse the ohmmeter leads and measure the resistance again. If the ratio of the resistances is 2:1 or greater, fault conditions most likely have occurred. A common cause is miswiring the power supply.

- Improper power causes catastrophic failure: If a card has had reverse polarity or high voltage applied, replacing a failed component is not an adequate fix. Other components probably have been partially damaged or a failure mechanism has been induced. Therefore, a failure will probably occur in the future. For such cards, Octagon highly recommends that these cards be replaced.

- Other over-voltage symptoms: In over-voltage situations, the programmable logic devices, EPROMs and CPU chips, usually fail in this order. The failed device may be hot to the touch. It is usually the case that only one IC will be overheated at a time.

- **Power sequencing:** The major failure of I/O chips is caused by the external application of input voltage while the Micro PC power is off. If you apply 5V to the input of a TTL chip with the power off, nothing will happen. Applying a 5V input to a CMOS card will cause the current to flow through the input and out the 5V power pin. This current attempts to power up the card. Most inputs are rated at 25 mA maximum. When this is exceeded, the chip may be damaged.

- **Failure on powerup:** Even when there is not enough current to destroy an input described above, the chip may be destroyed when the power to the card is applied. This is due to the fact that the input current biases the IC so that it acts as a forward biased diode on powerup. This type of failure is typical on serial interface chips.

- **Hot insertion:** Plugging cards into the card cage with the power on will usually not cause a problem. (**Octagon urges that you do not do this!**) However, the card may be damaged if the right sequence of pins contacts as the card is pushed into the socket. This usually damages bus driver chips and they may become hot when the power is applied. This is one of the most common failures of expansion cards.

- **Terminated backplanes:** Some customers try to use Micro PC cards in backplanes that have resistor/capacitor termination networks. CMOS cards cannot be used with termination networks. Generally, the cards will function erratically or the bus drivers may fail due to excessive output currents.

- Excessive signal lead lengths: Another source of failure that was identified years ago at Octagon was excessive lead lengths on digital inputs. Long leads act as an antenna to pick up noise. They can also act as unterminated transmission lines. When 5V is switched onto a line, it creates a transient waveform. Octagon has seen submicrosecond pulses of 8V or more. The solution is to place a capacitor, for example 0.1 μF, across the switch contact. This will also eliminate radio frequency and other high frequency pickup.

## **■ Avoiding damage to the heatsink/CPU**

#### **WARNING!**

When handling any Octagon CPU card, extreme care must be taken not to strike the heatsink (if installed) against another object, such as a table edge. Also, be careful not to drop the CPU card, since this may cause damage to the heatsink/CPU as well.

*Note* Any physical damage to the CPU control card is **not** covered under warranty.

| 2040 PC/104 CPU | user's manua |

|-----------------|--------------|

|-----------------|--------------|

## **Contents**

| Abbreviation | ns and terms used in this manual                          | xii         |

|--------------|-----------------------------------------------------------|-------------|

| Conventions  | s used in this manual                                     | xiv         |

|              | nd warnings                                               |             |

|              | nd format and procedures                                  |             |

| About this n | nanual                                                    |             |

| Overview:    | Section 1 - Installation                                  |             |

| Chapter 1:   | Overview                                                  | <b>1</b> -1 |

| Descript     | ion                                                       | 1-1         |

|              | /104 CPU major hardware features                          |             |

|              | U                                                         |             |

|              | id-state disks                                            |             |

|              | SSD0                                                      | 1-1         |

|              | SSD1                                                      |             |

|              | SSD2                                                      |             |

| RA           | M                                                         |             |

|              | rial ports protected against ESD                          |             |

| Mu           | lltifunctional printer port                               | 1-2         |

|              | tchdog timer added for safety                             |             |

| Rea          | al time calendar/clock with battery-backup                | 1-3         |

| Ke           | ypad and LCD display support for low cost operator        |             |

| •            | interface                                                 | 1-3         |

| Spe          | eaker, keyboard, and mouse                                | 1-3         |

|              | /104 16–bit interface                                     |             |

|              | rdware reset                                              |             |

|              | olt operation lowers system cost                          |             |

|              | /104 CPU major software features                          |             |

|              | agnostic software verifies system integrity automatically |             |

|              | TUP information stored in EEPROM for high reliability     |             |

|              | penix BIOS                                                |             |

|              | ot sequence                                               |             |

| Fas          | st boot                                                   | 1-4         |

|              | ations                                                    |             |

|              | gged environmental operation                              |             |

|              | e                                                         |             |

|              |                                                           |             |

| Chapter 2:   | Quick start                                               |             |

| Equipmo      | ent required                                              | 2-1         |

| Configui     | ration jumpers                                            | 2-2         |

|              | ng the 2040 PC/104 CPU board                              |             |

| Mo           | unting on a flat surface                                  | 2-4         |

| Con          | nnecting to a PC/104 interface                            | 2-4         |

| Power su     | ıpply                                                     | 2-5         |

|              | disks                                                     |             |

|              | nsole                                                     |             |

| Floren       | misso                                                     | 2 (         |

| Configuring setup                                           | 2-9        |

|-------------------------------------------------------------|------------|

| Installing a floppy disk drive                              | . 2-10     |

| Creating a boot disk                                        |            |

| Copying files                                               |            |

| Chapter 3: SETUP program                                    | 3-1        |

| Running SETUP over the console port                         |            |

| SETUP example                                               |            |

| Chapter 4: Save and run programs                            | 4-1        |

| Save and run your programs on the 2040 PC/104 CPU           | 4-1        |

| Adding your application                                     | 4-1        |

| Overriding the autoexecution of your application            | 4-2        |

| Option 1                                                    |            |

| Option 2                                                    |            |

| Option 3                                                    |            |

| Overview: Section 2 - Hardware                              |            |

|                                                             |            |

| Chapter 5: Serial ports                                     | 5-1        |

| Description                                                 | 5-1        |

| Serial port configurations                                  |            |

| COM1                                                        |            |

| COM2                                                        |            |

| Function and use of serial ports                            |            |

| COM1 as the serial console device                           | 5-3<br>5-4 |

|                                                             | J-4        |

| Chapter 6: LPT1 parallel port                               |            |

| LPT1 parallel port                                          |            |

| Printer                                                     |            |

| Floppy drive                                                |            |

| Display                                                     |            |

| Keypad                                                      |            |

| Opto rack                                                   | 6-4        |

| Chapter 7: Console devices                                  | 7-1        |

| Description                                                 | 7-1        |

| Selecting console devices                                   | 7-1        |

| COM1 as serial console device                               | 7-2        |

| Keyboard, speaker, and mouse                                |            |

| Transferring files between the 2040 PC/104 CPU and your PC  |            |

| ROM-DOS operating system                                    |            |

| MS-DOS operating system                                     | 7-5        |

| Transferring files to the 2040 PC/104 CPU                   | 7-6        |

| Transferring files from the 2040 PC/104 CPU                 | 7-7        |

| Downloading files to the 2040 PC/104 CPU using PC SmartLINK | 7-8        |

| Chapter 8:  | SSDs, DRAM, and battery backup                                                  | 8-1                  |

|-------------|---------------------------------------------------------------------------------|----------------------|

| Descript    | ion                                                                             | 8-1                  |

| Booting     |                                                                                 | 8-1                  |

|             |                                                                                 |                      |

| SSD1 so     | cket/M–Systems DiskOnChip                                                       | 8-1                  |

| SSD2        |                                                                                 | <b> 8</b> -3         |

| SS          | D2 socket                                                                       | 8-4                  |

| Aco         | cessing SRAM on the 2040                                                        | 8-4                  |

| DRAM        |                                                                                 | 8-6                  |

| Battery     | backup for SSD2 SRAM and real time calendar clock                               | 8-6                  |

|             | External drives                                                                 |                      |

| Descript    | ion                                                                             | 9-1                  |

| Floppy d    | lisk controller                                                                 | 9-1                  |

|             | wer requirements                                                                |                      |

| Ins         | talling a floppy disk drive                                                     | 9-2                  |

| Hard dis    | sk controller                                                                   | 9-3                  |

| Chapter 10: | Interpreting "beep" codes                                                       | 10-1                 |

| Descript    | ion                                                                             | 10-1                 |

| Chapter 11: | PC/104 expansion                                                                | 11-1                 |

|             | ion                                                                             |                      |

| 1           |                                                                                 |                      |

| Overview: S | Section 3 – System management                                                   |                      |

| Chapter 12: | Watchdog timer and hardware reset                                               | 12-1                 |

| Descript    | ion                                                                             | 12-1                 |

|             | g function definitions using Borland C code                                     |                      |

|             | able watchdog                                                                   |                      |

|             | obe watchdog                                                                    |                      |

| Dis         | sable watchdog                                                                  | 12-1                 |

| Watchdo     | g function definitions using enhanced INT 17h handler                           | 12-2                 |

|             | able watchdog                                                                   |                      |

|             | obe watchdog                                                                    |                      |

|             | sable watchdog                                                                  |                      |

|             | WDTimer                                                                         |                      |

|             | rementWDTimer                                                                   |                      |

| Hardwa      | re reset                                                                        | 12-6                 |

| Chapter 13: | Serial EEPROM                                                                   |                      |

|             | ion                                                                             |                      |

|             | EPROM                                                                           |                      |

| Rea         | ad a single word from the serial EEPROM                                         | 13-1                 |

| Wr          | ite a single word to the serial EEPROM                                          | 13-2                 |

| Rea         |                                                                                 | 400                  |

|             | ad multiple words from the serial EEPROM                                        | 13-3                 |

|             | ad multiple words from the serial EEPROMite multiple words to the serial EEPROM | 13-3<br>13-3         |

| Ret         | ad multiple words from the serial EEPROM                                        | 13-3<br>13-3<br>13-4 |

| Chapter 14:                                                                | Troubleshooting14                                                                                                                                    | -1                               |

|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| No s                                                                       | creen activity – checking console serial communications 14-                                                                                          | -1                               |

|                                                                            | oled serial console screen activity                                                                                                                  |                                  |

| Cyct                                                                       | em generates a BIOS message but locks up when booting from                                                                                           | - 1                              |

|                                                                            |                                                                                                                                                      | 9                                |

| C                                                                          | SSD1                                                                                                                                                 | -2                               |

| Syst                                                                       | em will not recognize hard drive                                                                                                                     | -2                               |

| Syst                                                                       | em locks up after powerdown/powerup 14                                                                                                               | -2                               |

| Technical                                                                  | assistance                                                                                                                                           | -2                               |

| Overview: Se                                                               | ection 4 – Appendices                                                                                                                                |                                  |

| Appendix A:                                                                | Technical data A                                                                                                                                     | -1                               |

| Technical                                                                  | specifications A-                                                                                                                                    | -1                               |

| Connector                                                                  | pinouts                                                                                                                                              | -5                               |

| Appendix B:                                                                | Software utilitiesB                                                                                                                                  | -1                               |

|                                                                            | ionB-                                                                                                                                                |                                  |

| III daact                                                                  | 1011 D                                                                                                                                               | - T                              |

|                                                                            |                                                                                                                                                      |                                  |

| COM1CO                                                                     | N.EXE B-                                                                                                                                             | -2                               |

| COM1CO<br>I17HNDL                                                          | N.EXE B-<br>R.EXE B-                                                                                                                                 | -2<br>-2                         |

| COM1CO<br>I17HNDL<br>LPT1CON                                               | N.EXE B-<br>.R.EXE B-<br>N.COM B-                                                                                                                    | -2<br>-2<br>-3                   |

| COM1CO<br>I17HNDL<br>LPT1CON<br>PGMBIOS                                    | N.EXE       B-         .R.EXE       B-         N.COM       B-         S.EXE       B-                                                                 | -2<br>-2<br>-3<br>-4             |

| COM1CO<br>I17HNDL<br>LPT1CON<br>PGMBIOS<br>RESET.CO                        | N.EXE       B-         .R.EXE       B-         V.COM       B-         S.EXE       B-         OM       B-                                             | -2<br>-2<br>-3<br>-4<br>-5       |

| COM1CO<br>I17HNDL<br>LPT1CON<br>PGMBIOS<br>RESET.CO<br>SETUP.CO            | N.EXE       B-         .R.EXE       B-         N.COM       B-         S.EXE       B-         OM       B-         OM       B-                         | -2<br>-2<br>-3<br>-4<br>-5       |

| COM1CO<br>I17HNDL<br>LPT1CON<br>PGMBIOS<br>RESET.CO<br>SETUP.CO            | N.EXE       B-         .R.EXE       B-         V.COM       B-         S.EXE       B-         OM       B-                                             | -2<br>-2<br>-3<br>-4<br>-5       |

| COM1CO<br>I17HNDL<br>LPT1CON<br>PGMBIOS<br>RESET.CO<br>SETUP.CO<br>SCONSOS | N.EXE       B-         .R.EXE       B-         N.COM       B-         S.EXE       B-         OM       B-         OM       B-                         | -2<br>-2<br>-3<br>-4<br>-5<br>-5 |

| COM1CO<br>I17HNDL<br>LPT1CON<br>PGMBIOS<br>RESET.CO<br>SETUP.CO<br>SCONSOS | N.EXE       B-         .R.EXE       B-         N.COM       B-         S.EXE       B-         OM       B-         OM       B-         LE.EXE       B- | -2<br>-2<br>-3<br>-4<br>-5<br>-5 |

## **List of Figures**

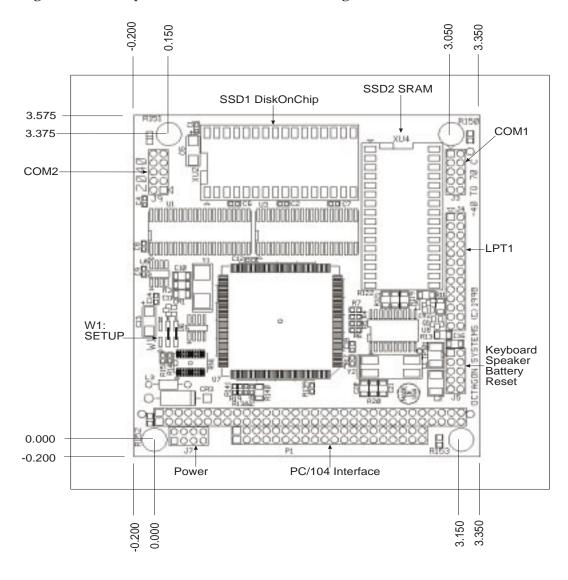

| Figure 2–1  | Component locations and mounting dimensions 2-3         |

|-------------|---------------------------------------------------------|

| Figure 2–2  | Power connector                                         |

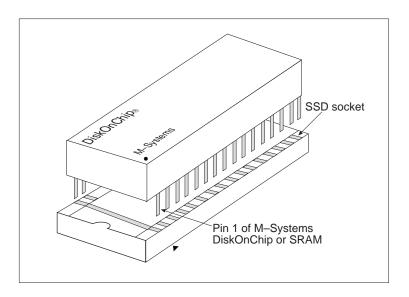

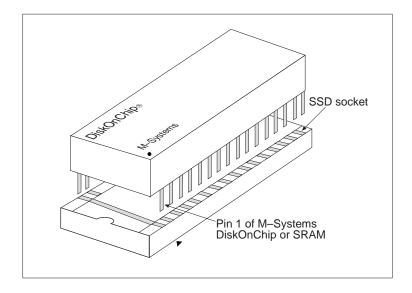

| Figure 2–3  | M-Systems pin alignment with the 2040 SSD1 socket 2-7   |

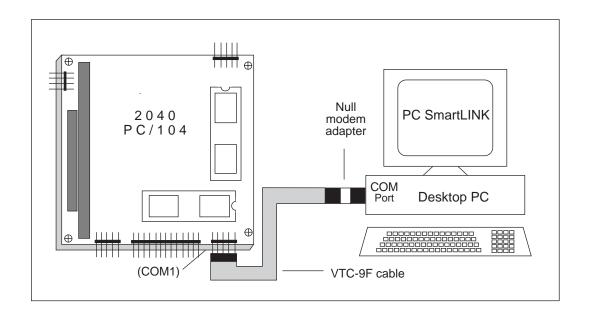

| Figure 2–4  | Serial console connections                              |

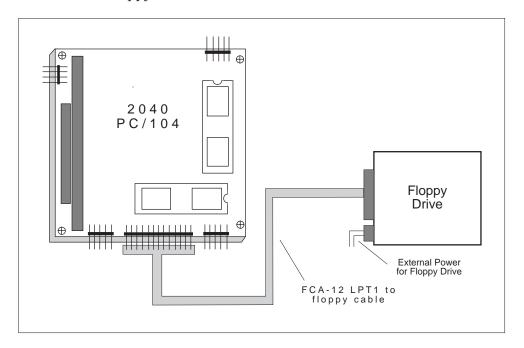

| Figure 2–5  | LPT1 and a Floppy Drive 2-10                            |

| Figure 5–1  | Custom null modem adapter with RTS and RI connected 5-3 |

| Figure 5-2  | 2040 PC/104 CPU serial devices 5-4                      |

| Figure 6–1  | LPT1 as a printer port 6-1                              |

| Figure 6–2  | LPT1 as a display or keypad port 6-3                    |

| Figure 6–3  | LPT1 and an opto rack                                   |

| Figure 7–1  | Custom null modem adapter with RTS and RI connected 7-2 |

| Figure 7–2  | The 2040 PC/104 CPU and a serial console                |

| Figure 7–3  | Downloading files using PC SmartLINK and                |

| O           | TRANSFER.EXE                                            |

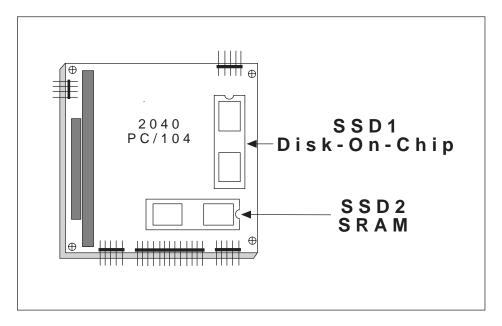

| Figure 8–1  | SSD socket locations 8-2                                |

| Figure 8–2  | M-Systems pin alignment with the 2040 SSD1 socket 8-2   |

| Figure 9–1  | LPT1 and a Floppy Drive 9-2                             |

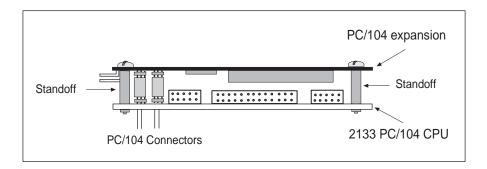

| Figure 11–1 | Typical PC/104 module stack 11-1                        |

## **List of Tables**

| Table 2–1  | SETUP: W1                                    | 2-2  |

|------------|----------------------------------------------|------|

| Table 2-2  | Power pinout: J7                             | 2-6  |

| Table 3-1  | SETUP Jumpers: W1                            | 3-1  |

| Table 5–1  | COM1 and COM2 pinouts (J3 and J9 connectors) |      |

| Table 7–1  | Speaker, battery, keyboard, and reset: J5    | 7-4  |

| Table 8–1  | Connector J5 pinout                          | 8-3  |

| Table 8–2  | System control register                      | 8-5  |

| Table 8–3  | Speaker, battery, keyboard, and reset: J5    |      |

| Table 10–1 | Phoenix BIOS beep codes                      | 10-2 |

| Table 10–1 | Phoenix BIOS beep codes (cont'd)             |      |

| Table 10–2 | Additional error codes for Phoenix BIOS      | 10-4 |

| Table A-1  | 2040 PC/104 CPU memory map                   |      |

| Table A–2  | 2040 PC/104 CPU I/O map                      | A-3  |

| Table A–3  | DMA map                                      | A-4  |

| Table A-4  | Interrupt map                                | A-4  |

| Table A-5  | Available LPT1 port addresses                |      |

| Table A-6  | PC/104 signal assignments                    | A-5  |

| Table A-7  | Speaker, battery, keyboard, and reset: J5    | A-6  |

| Table A-8  | Power: J7                                    | A-6  |

| Table A-9  | LPT1 printer connector: J4                   | A-7  |

| Table C-1  | Cables and terminal board                    | C-1  |

| Table C-2  | LCD displays and keypads                     | C-1  |

| Table C-3  | Opto rack and modules                        | C-2  |

| Table C-4  | Miscellaneous part numbers                   | C-2  |

|            |                                              |      |

# Abbreviations and terms used in this manual

Throughout this manual, the following symbols and terms are used:

Autoexecution Automatic execution of a program on powerup or

reset.

BIOS Basic Input Output System.

Console port Video card or COM1 where BIOS and DOS messages

appear and keyboard input is available.

DRAM Dynamic Random Access Memory devices.

Expansion card The expansion cards add I/O functions to the

PC/104 system, such as analog input/output, digital

input/output, motion control, and display.

Flash Electrically erasable PROM which allows at least

100,000 write cycles.

h The suffix "h" denotes a hexadecimal number. A

decimal number has no prefix or suffix. For example,

1000h and 4096 are equivalent.

KB Kilobyte (1,024 8-bit bytes).

MB Megabyte (1,048,576 8-bit bytes).

Memory device The type of static RAM, DRAM, flash memory, or

EPROM specified for either volatile or nonvolatile

memory.

PC/104 An expansion bus used for holding 8- and 16-bit

expansion expansion cards.

PC SmartLINK A serial communications software package designed

by Octagon for use with the 2040 PC/104 CPU.

Solid-state disk

(SSD)

A simulated disk which uses a high speed solid-state

memory device. For example, flash memory,

EEPROM, or static RAM.

SRAM Static Random Access Memory.

TTL compatible Transistor transistor logic compatible; 0-5V logic

levels.

W[ – ] Denotes a jumper block and the pins to connect.

XMODEM A communications protocol which allows transfer of

files between two computers.

## Conventions used in this manual

## **■ Notes and warnings**

*Note* A note is supplementary or background information. At other times, it is a hint or reminder that makes a task easier or quicker.

#### **WARNING!**

A warning gives vital information. Failure to heed a warning may cause system failure, equipment damage, or bodily harm to the system operator.

## **≡** Command format and procedures

Commands must be entered in a specific format. To indicate the format, this manual uses the conventions below. The conventions cover the rules for issuing all commands, including the most complex ones. The command format looks like this:

```

command [type_this | or_ this] input {optional_input}

```

Follow these rules and conventions:

■ Information which appears on your screen is shown in a different type face, for example:

```

PhoenixBIOS(TM) A486 Version 1.03

Copyright (C) 1985-1994 Phoenix Technologies, Ltd.

All Rights Reserved

Octagon Systems Corp.

```

■ Commands that you must key in are shown in Courier Bold, for example:

C:> RESET

■ Italicized refers to information that is specific to your particular system or program, e.g.,

Enter filename means enter the name of your file.

- Paired angle brackets are used to indicate a specific key on your keyboard, e.g., <ESC> means the escape key; <CTRL> means the control key; <F1> means the F1 function key.

- All addresses are given in hexadecimal, for example, 328h.

## About this manual

The *2040 PC/104 CPU user's manual* provides information about installing and configuring the 2040 PC/104 CPU. This manual is divided into four sections:

- Section 1 Installation

- Chapter 1: Overview Chapter 2: Quick start

- Chapter 3: SETUP programs

- Chapter 4: Save and run programs

- Section 2 Hardware

- Chapter 5: Serial ports

- Chapter 6: LPT1 parallel port Chapter 7: Console devices

- Chapter 8: SSDs, DRAM, and battery backup

- Chapter 9: External drives

- Chapter 10: Interpreting "beep" codes

- Chapter 11: PC/104 expansion

- Section 3 System management

- Chapter 12: Watchdog timer and hardware reset

- Chapter 13: Serial EEPROM Chapter 14: Troubleshooting

- Section 4 Appendices

- Appendix A: Technical data

- Appendix B: Software utilities

- Appendix C: Accessories

| 2040 P | C/104 | CPU | user's | manua |

|--------|-------|-----|--------|-------|

|        |       |     |        |       |

## Overview: Section 1 - Installation

Section 1 provides installation and programming instructions, startup options, and system configuration program examples. The following chapters are included:

Chapter 1: Overview

Chapter 2: Quick start

Chapter 3: SETUP programs

Chapter 4: Save and run programs

## Chapter 1: Overview

## **■ Description**

The 2040 is a rugged and reliable PC/104 CPU with a low–power 386SX 40 MHz CPU. The 2040 PC/104 CPU integrates serial communications, a multifunctional parallel port, a solid–state disk, keyboard and speaker ports, and a PC/104 interface.

## **≡ 2040 PC/104 CPU major hardware features**

#### **CPU**

The CPU is a low-power 386SX with a clock speed of 40 MHz.

#### Solid-state disks

#### SSD<sub>0</sub>

The 2040 PC/104 CPU has an on-board 512 KB flash which contains the BIOS and software extensions.

#### SSD1

A 32-pin DIP socket accepts an M-Systems DiskOnChip®. The socket exhibits high retention force and affords a gas tight contact.

#### SSD<sub>2</sub>

A 32-pin DIP socket accepts either a 128 KB or a 512 KB SRAM. SRAM is automatically backed up when an AT battery is connected. The socket exhibits high retention force and affords a gas tight contact.

#### **RAM**

The 2040 PC/104 CPU has 4 MB DRAM on board.

#### Serial ports protected against ESD

The 2040 PC/104 CPU has two serial ports for 8-wire RS-232C interfaces. COM1 can also be used as a console interface. These serial ports have the following common specifications:

- IEC1000, level 3, ESD protection specification

- Contact discharge ±6 kV

- Air-gap discharge ±8 kV

- Backdrive protection

- 16C550 compatible

- Up to 115.2K baud

- 16-byte FIFO buffers

- Enabled and disabled in SETUP

### Multifunctional printer port

The 2040 PC/104 CPU incorporates the latest enhanced parallel port. It includes the following features:

- Unidirectional

- Bidirectional

- IEEE 1284, ECP and EPP modes

- 14 mA of drive current

- Backdrive protection

- Floppy drive mode

The following represent applications in the multifunctional parallel port:

- LPT1 for PC compatible printers

- 17 general purpose digital I/O lines

- Up to a 4 x 4 matrix keypad

- 4-line alphanumeric display

- MPB-16PC, 16-position opto-module rack

### Watchdog timer added for safety

The watchdog timer resets the system or generates an NMI (nonmaskable interrupt) if the program stops unexpectedly. The watchdog is enabled, disabled and strobed under software control. The time–out period is 1.6 seconds typical, 1.00 seconds minimum to 2.25 seconds maximum. The watchdog timer can be strobed by the I17HNDLR.EXE utility (a TSR program) to extend the timeout up to a maximum of 60 hours.

#### Real time calendar/clock with battery-backup

The real time clock is fully AT compatible and uses the standard DOS calls. An optional off-card battery powers the real time clock when the 5 volt supply is removed.

## Keypad and LCD display support for low cost operator interface

For embedded applications, the parallel printer port can interface with a 16-key matrix keypad and a 2- or 4-line LCD display. The 2040 PC/104 CPU is supplied with software that provides keypad scanning and display operation. Supplied display and keypad drivers in C and Basic support these devices.

### Speaker, keyboard, and mouse

A speaker and keyboard can be connected to the utility port. If a mouse is needed, it can be connected to a COM port. The keyboard controller accepts an AT style keyboard. Alternately, COM1 can be used as a console port, and all keyboard and video information is redirected through COM1. Neither the keyboard nor the mouse are required for operation.

#### PC/104 16-bit interface

The PC/104 interface accepts an 8– or 16–bit PC/104 expansion board. PC/104 expansion boards are available from several manufacturers. As many as three PC/104 expansion boards may be stacked on the 2040 PC/104 CPU.

#### Hardware reset

A hardware reset ensures complete reset of the system and all attached peripherals. A hardware reset can be done by any of the following methods:

- An expired watchdog timer cycle

- Cycling power

- Momentarily pulling the master reset line to ground (pin 3, connector J5)

### 5 Volt operation lowers system cost

The 2040 PC/104 CPU operates from a single 5V ±5% supply.

- $\blacksquare$  5V ±5%, 800 mA maximum

- +12V, -12V, and -5V supplied to PC/104 connector; not required for 2040 PC/104 CPU operation

## **≡ 2040 PC/104 CPU major software features**

#### Diagnostic software verifies system integrity automatically

The 2040 PC/104 CPU has built–in diagnostic software that can be used to verify on–card I/O and memory functions. On powerup, a series of tests is performed. If a problem occurs, the failed test can be identified by a series of beeps. The test is performed automatically every time the system is reset or powered up. Memory verification does not require software, test equipment, monitor, keyboard, disks, or test fixtures. See the *Interpreting "beep" codes* chapter for a complete listing of tests and failures and their descriptions.

### SETUP information stored in EEPROM for high reliability

Loss of SETUP data is serious in industrial applications. Most PCs store SETUP information in battery–backed CMOS RAM. If the battery fails or is replaced during routine maintenance, this information is lost. Without a keyboard and monitor in embedded applications, time consuming re–initialization is required.

The 2040 PC/104 CPU stores the SETUP information in EEPROM. If a backup battery should fail, only the system date and time are lost.

#### **Phoenix BIOS**

The 2040 PC/104 CPU has a Phoenix AT BIOS with Octagon BIOS extensions.

### **Boot sequence**

A 2040 PC/104 CPU can be configured to boot from an on-card, solid-state disk, an external floppy, or a hard disk.

#### Fast boot

You can speed up the BIOS portion of the boot process to approximately five seconds by disabling the "Power on memory test" in Setup. This deletes the memory test and rearranges some of the other test sequences, decreasing the boot time by about 65%.

## **■ Specifications**

### Rugged environmental operation

■ Operating temperature −40° to 70°C

■ Nonoperating temperature −55° to 90°C, nonoperating

■ Relative humidity 5% to 95% noncondensing

■ Altitude -100m to 10,000m

■ Shock 40g, 3 axis

■ Vibration 6g, 3 axis

#### **Size**

3.8" x 3.6"

## Chapter 2: Quick start

This chapter covers the basics of setting up a 2040 PC/104 CPU system and tells you:

- How to set the configuration jumpers on the 2040 PC/104 CPU

- How to install the 2040 PC/104 CPU

- How to connect a power supply

- How to install a bootable disk

- How to use a serial console

#### **WARNING!**

The 2040 PC/104 CPU contains static sensitive CMOS components. Do the following to avoid damaging your card and its components:

- Ground yourself before handling the 2040 PC/104 CPU card

- Disconnect power before removing or inserting a PC/104 expansion board

- When programming a memory device, place the device in the socket before applying power.

## **Equipment required**

There are several options for installing a bootable disk and loading your applications. This chapter provides procedures for installing an M–Systems DiskOnChip and using a floppy disk drive to transfer files to the DOC. The following equipment is required:

- +5V power supply

- VTC-9F, FCA-12, and null modem cables

- floppy disk drive

- M-Systems DiskOnChip, preformatted and loaded with an operating system

## **■ Configuration jumpers**

Before you continue with the installation of your 2040 PC/104 CPU, review the following table for a list of jumper configurations to ensure you have the correct configuration.

The 2040 PC/104 CPU component diagram is on the following page.

Table 2-1 SETUP: W1

| Pins | Description                                                                  |

|------|------------------------------------------------------------------------------|

| 1–2  | (N)MI: Watchdog time-out connected to NMI                                    |

| 3–4* | (R)eset: Watchdog time-out connected to reset                                |

| 5-6* | (S)etup: Use SETUP information:<br>On* = on-board EEPROM; Off = BIOS default |

<sup>\* =</sup> default

Note When the "N" jumper W1[1-2] is on instead of the default "R" jumper W1[3-4], the system will not reset after SETUP is run. A power cycle reset is required.

Figure 2-1 Component locations and mounting dimensions

## **≡ Installing the 2040 PC/104 CPU board**

The 2040 PC/104 CPU can be installed two ways – mounted on a flat surface, or connected to a PC/104 interface. The following equipment is included with the 2040:

- 4 threaded hex stainless steel standoffs (4–40 x 3/8")

- 4 screws (4–40 x 1/4")

- 4 KEP nuts (4–40)

- 4 internal star lock washers (4–40)

### Mounting on a flat surface

To mount the 2040 PC/104 CPU on a flat surface, use the #4 standoffs, washers, and screws and place them in the four holes on the 2040 PC/104 CPU board. Refer to Figure 2–1 for the center–to–center mounting hole dimensions and for the location of the designated holes used for mounting the hardware. Fasten the board securely to the mounting surface.

#### **WARNING!**

Before the 2040 PC/104 CPU is powered on for bench testing, all four standoffs, screws and washers should be secured to the board. The standoff pieces will ensure full support of the 2040 PC/104 CPU board. These hardware pieces will reduce the circuit board flex when a PC/104 expansion board and/or the SSD are inserted. Flexing of the 2040 PC/104 CPU board should be avoided, since it can cause problems with the copper circuit traces, keyboard, monitor, and surface mounted components.

### Connecting to a PC/104 interface

The 2040 PC/104 CPU can be connected to an existing PC/104 system. Use the #4 standoffs, washers, and screws and place them in the four holes on the 2040 PC/104 CPU board, with the male end of the standoff facing down. Align the PC/104 pins with the connectors below, and the standoffs with the mounting holes below, then firmly press the boards together. Secure the boards together with the KEP nuts.

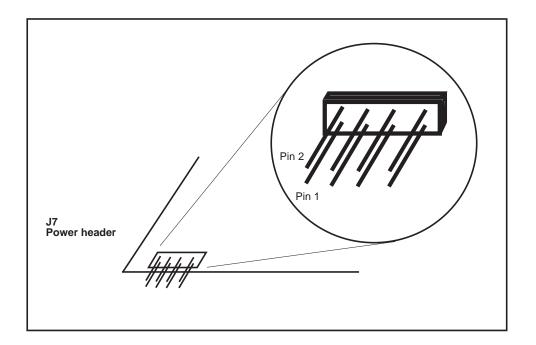

## **■ Power supply**

The 2040 PC/104 CPU requires 5V  $\pm 5\%$ , 800 mA maximum. It is designed to operate from a single +5 VDC supply, typically supplied at connector J7. In some configurations where the 2040 is connected to another PC/104 system, the power required by the 2040 can be drawn from the system through the PC/104 connector. If you are using the PC/104 interface, you may also require  $\pm 12$  VDC. Make sure that you utilize both +5 VDC conductors and both ground conductors. Refer to Figure 2–2 and Table 2–2.

#### **WARNING!**

Accidently crossing the wires, i.e., plugging +5V wires into the ground connector or the ground wires into the +5V connector will damage the 2040 PC/104 CPU.

It is important that a quality power supply be used with the 2040 PC/104 CPU. For example, when a particular application calls for a custom power supply, there are several internal issues to consider such as current capacity, line and load regulation, maximum ripple, hold up time, efficiency, and current limiting. You should also consider the power devices and equipment such as the power cable conductor gauge, number and length of conductors, mating connectors, and the power supply to external PC/104 devices.

Octagon supplies are designed to ramp up fast (less than 50 ms), discharge fast on power down and to regulate properly under a no load condition.

Most desktop PC switching supplies are rated at 5V at 20A or more. Switching supplies usually requires a 20% load to operate properly, that is, 4A or more. Since a typical Micro PC system takes less than 2A, the desktop PC supply does not regulate properly. Output drift up to 6-7V and/or 7-8 voltage spikes have been reported. If the power supply comes up slowly (that is, longer than 50 ms), the sequencing of ICs on the board may be out of sync, thus, causing the system to lock up.

If large output capacitors are used, powering the system down and then up may lock up the Micro PC. If the power supply does not drain below 0.7V, the CMOS components on the Micro PC will act like diodes and forward bias.

If using a non-Octagon supply, select a supply that has a low or no minimum load requirement, comes up in less than 50 ms and discharges quickly on power down.

#### **WARNING!**

Make sure the power supply is OFF when connecting the power cable to the 2040 PC/104 CPU board. Damage to the 2040 PC/104 CPU may occur if the power is ON when connecting the power cable.

Figure 2–2 Power connector

Table 2–2 Power pinout: J7

| Pin | Function          |

|-----|-------------------|

| 1   | Gnd               |

| 2   | +5 VDC            |

| 3   | NC                |

| 4   | +12 VDC to PC/104 |

| 5   | -5 VDC to PC/104  |

| 6   | -12 VDC to PC/104 |

| 7   | Gnd               |

| 8   | +5 VDC            |

### **≡** Bootable disks

The 2040 PC/104 CPU has an on-board 512 KB flash which contains the BIOS and software extensions. It does not contain an operating system or a bootable disk.

The 2040 PC/104 CPU is fully compatible with several operating systems, including MS-DOS and ROM-DOS. You can download a trial version of ROM-DOS from www.datalight.com/rom-dos.htm.

There are three choices for supplying a bootable disk: a floppy drive (through LPT1 or a PC/104 card), a PC/104 hard drive, or an M–Systems DiskOnChip (DOC). The example in this chapter shows how to use a DOC to boot your system and a floppy drive connected to LPT1 to install your applications.

The memory address for an M-Systems DiskOnChip is at E8000–EBFFFh. This memory address is not bank switchable and cannot be disabled.

When ordering an M-Systems DiskOnChip, you can specify that you want it preformatted and with an operating system already installed. This simplifies your startup procedures. Refer to your M-Systems utility disk for more information on using DiskOnChip.

Before installing the DOC, remove power from the 2040. Align pin 1 of the DiskOnChip with pin 1 of the SSD1 socket, then firmly press the chip into the socket. Refer to Figure 2–3 for correct SSD alignment.

Figure 2-3 M-Systems pin alignment with the 2040 SSD1 socket

### **≡ Serial console**

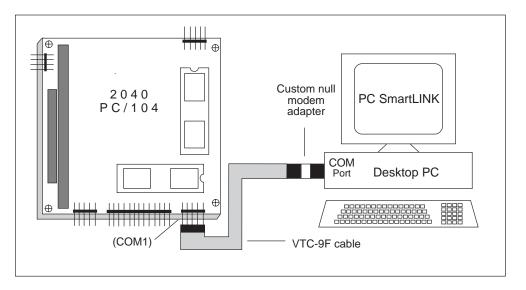

COM1 can serve as a console device, allowing you to use your desktop PC to communicate with the 2040. The default configuration stored in the BIOS SETUP is for COM1 to be a console device. Use the figure below to connect a desktop computer to the 2040 as a console device. This connection requires a VTC-9F cable and a null modem adapter. It also requires PC SmartLINK, available from Octagon, or an equivalent terminal emulator.

*Note* When interfacing the 2040 PC/104 CPU to your desktop PC, you must use a null modem adapter.

Figure 2-4 Serial console connections

Power up the 2040. You should see the BIOS sign—on messages for the 2040 on your monitor. If the boot process completes and the C:\> prompt appears, you have a bootable disk. Go to the *Floppy disk* section for information on transferring files.

If the message "press C to try again or S for setup" appears, the boot did not complete. The most likely reason is that the DOC does not have an operating system installed. Press S to enter Setup, then configure LPT1 as a floppy drive, number of floppy drives to 1, and floppy drive size to the size of the floppy you will be installing. Save the Setup changes, then power off the 2040. Ensure that the S jumper is on so that the next time the 2040 is powered, it will use the parameters from the Setup stored in EEPROM. Proceed to the next section, *Floppy drive*.

## **≡ Floppy drive**

This section describes how to install a floppy drive. The floppy drive can be used as a boot device, or to transfer programs to a DOC.

Note If you have a DOC installed on the 2040 and have booted, you may have the utilities TRANSFER.EXE or REMDISK/REMSERVE (ROM DOS) or INTERLINK/INTERSVR (MS DOS) on the DOC. You can use these utilities to transfer files from your host computer to the 2040 over the serial console. Refer to the documentation included with your operating system for information on how to use these utilities.

#### Configuring setup

The default in the BIOS SETUP is for LPT1 in bidirectional mode. If you have previously run SETUP and changed the settings for LPT1 to floppy drive, and saved those settings, ensure that the SETUP jumper is on so that the BIOS uses the settings from the EEPROM.

You can enter SETUP by pressing the "backspace" key followed by the "S" key during BIOS POST sequence (this occurs between the memory test and boot). Configure LPT1 as a floppy drive, number of floppy drives to 1, and floppy drive size to the size of the floppy you will be installing. Save the Setup changes, then power off the 2040. Ensure that the SETUP jumper is on so that the BIOS uses the settings from the EEPROM during the next boot.

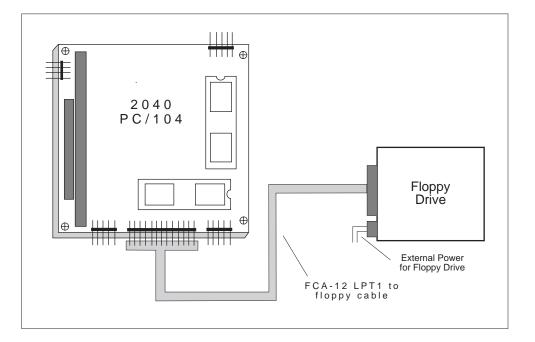

### Installing a floppy disk drive

- 1. Disconnect power to the 2040 PC/104 CPU.

- 2. Insert one end of an Octagon FCA-12 cable into the rear of the floppy drive. Make sure pin 1 on the cable is connected to pin 1 on the drive.

- 3. Insert the other end of the cable into J4 on the 2040 PC/104 CPU.

- 4. Connect power to the floppy drive.

- 5. Power up the system. If you have a bootable disk in SSD1, the system should boot up. If you do not have a bootable disk in SSD1, you will need to insert a boot disk into the floppy disk drive. Refer to the next section for information on creating a boot disk.

Figure 2-5 LPT1 and a Floppy Drive

### Creating a boot disk

You can create a floppy boot disk on any PC that has DOS installed. This floppy can then be inserted in the floppy disk drive connected to the 2040 and used to boot the system.

To create a boot disk, insert a blank, formatted floppy into the floppy drive of your PC. If you are running Windows on your PC, exit Windows and open up the DOS shell. Type the command sys A:, then press Enter.

The SYS command copies three files to the floppy disk. Two of the files are hidden (not shown by the DIR command), and the third file is COMMAND.COM. These three files are sufficient to boot the system.

Insert the boot disk in the 2040 floppy drive, then power on the system. The console monitor should return the A:\ prompt. Type C: to change to the C drive (if you have installed a DiskOnChip). Type DIR then press Enter.

If the C: or DIR commands return the message "No drive found" or "Abort Retry Fail", the DiskOnChip is probably not formatted. Refer to your M-Systems documentation for information on how to format the DOC.

If the DIR command returns a list of files from the DOC, and the list does not contain the file COMMAND.COM, then the DOC most likely does not contain an operating system. Return to the A: drive, type the command SYS C:, then press Enter. This should copy the boot files to the DOC. Remove the floppy disk from the floppy disk drive and cycle power to the 2040. The 2040 should boot from the DOC.

## **≡** Copying files

Once you have a bootable disk in SSD1, or a bootable PC/104 hard drive, you can use the floppy disk drive to transfer files to the bootable disk. Use the COPY command to copy files (such as, COPY MYPRGRM.COM C:\). Once the files are copied, you can remove the floppy disk drive.

When DOS starts up, it processes the files CONFIG.SYS and AUTOEXEC.BAT. If you add the command line for your application to the AUTOEXEC.BAT file, your application will automatically start when the system boots. Refer to your operating system documentation for information on modifying these two files.

# Chapter 3: SETUP program

The SETUP program defines the 2040 PC/104 CPU system parameters. This program is shipped with default configuration parameters stored in the serial EEPROM. Changes are made by running the SETUP program. The SETUP program is stored on the 2040 utility disk.

SETUP can be entered in one of two ways:

- Run SETUP.COM. To run SETUP.COM, this program must be resident on either the floppy disk drive and/or hard drive, or on a flash device such as the M-Systems DiskOnChip. SETUP.COM is on the 2040 utility disk.

- Press the "backspace" key followed by the "S" key during BIOS POST sequence (this occurs between the memory test and boot).

The system will display the 2040 setup parameters and available options. Select the option by pressing the space bar until the correct information appears, then press <ENTER>. Press <ESC> twice if you want to exit setup without saving your responses.

By removing the SETUP jumper from the "S" position at W1[5–6], you force the setup to revert to the defaults stored in BIOS. The default settings allow you to restart the system in a known configuration.

Table 3-1 SETUP Jumpers: W1

| Pins | Description                                                                  |  |  |

|------|------------------------------------------------------------------------------|--|--|

| 1–2  | (N)MI: Watchdog time–out connected to NMI                                    |  |  |

| 3–4* | (R)eset: Watchdog time-out connected to reset                                |  |  |

| 5-6* | (S)etup: Use SETUP information:<br>On* = on-board EEPROM; Off = BIOS default |  |  |

|      |                                                                              |  |  |

<sup>\* =</sup> default

*Note* Options having an \* are default settings.

Serial Console on COM1:

Enabled\*

Disabled

*Note* When this option is disabled, it may be overridden by connecting the COM1 RTS line to the COM1 RI line.

```

COM1 Console Baud Rate:

1200

2400

4800

9600*

14400

19200

28800

38400

57600

115200

```

Power on memory test:

Enabled\*

Disabled

Disabling this option speeds up the BIOS boot process to about five seconds (Octagon's "fast boot" feature). It disables the memory test and rearranges the sequence of other power-on tests. Note that this feature only speeds up the Octagon BIOS portion of the boot process. It does not affect the time required to load various operating systems. You may also press the space bar to cancel the memory test while in progress.

```

■ Boot Sequence:

C: Only*

A: Then C:

```

*Note* The M-Systems DiskOnChip software typically overrides the "C: Only" option.

```

■ Serial Port A:

Enabled*

Disabled

```

- Serial Port B:

Enabled\*

Disabled

- Parallel (LPT) Port:

Enabled\*

Disabled

- Parallel Port Mode:

Bidirectional mode\*

EPP mode

ECP mode

Floppy disk mode

Standard (Unidirectional) mode

Note Standard mode is provided for compatibility only. We recommend the use of bidirectional mode. EPP and ECP modes are provided for equipment that has the capability to operate in these modes for enhanced performance.

```

Parallel Port Address: 378h* 278h 3BCh

```

- Parallel Port Interrupt:

IRQ5

IRQ7\*

- Number of floppy drives: 0\*, 1, 2

- Floppy drive 1 size: 5.25", 360KB 5.25", 1.2 MB 3.5", 720KB 3.5", 1.44 MB\*

- Floppy drive 2 size: 5.25", 360KB 5.25", 1.2 MB 3.5", 720KB 3.5", 1.44 MB\*

- Swap drives A and B: Yes, No\*

- Number of hard drives: 0\*, 1, 2

- Auto drive configuration: Enabled\* Disabled

- Drive 0 parameters:

Cylinders (xxx):

Heads (x):

Sectors (xx):

- Drive 1 parameters:

Cylinders (xxx):

Heads (x):

Sectors (xx):

- Setup entry via hotkey:

Enabled\*

Disabled

- Shadow video BIOS:

Enabled

Disabled\*

- Shadow C8000H CFFFFH Disabled\* Enabled

- Shadow D0000H D7FFFH Disabled\* Enabled

- Shadow D8000H DFFFFH Disabled\*

Enabled

Press ENTER to SAVE the changes or Press ESC to EXIT without saving the changes. Saving options. Options saved.

Depending on the options you have selected, the system may display the following message:

You must reset for these options to take effect.

If you entered SETUP with the hotkeys (i.e., "backspace" and "S" keys), the system will reboot automatically. However, if the watchdog jumper is set to NMI, then the I/O parity check error appears and the board will halt. A power cycle reset is then required.

#### Running SETUP over the console port

- 1. To run SETUP make sure you have established a communications link between a keyboard and monitor (via a PC/104 video card) with the 2040 PC/104 CPU *or* a serial communications link between the 2040 PC/104 CPU and your PC. See the *Console devices* chapter for more information on these two communication links. Ensure the SETUP.EXE file has been copied from the 2040 utility disk to the boot drive, or that a floppy drive is connected to the system.

- 2. Enter:

C:\> SETUP

Note If you are not booting from the SSD1 drive, the drive designator may differ.

Note You may also enter **SETUP** after the memory test and before the system has booted by pressing the "backspace" key followed by the "S" key.

3. The system will display the 2040 PC/104 CPU setup parameters and available options. Select the option by pressing the space bar until the correct information appears, then press <ENTER>. Press <ESC> twice if you want to exit SETUP without saving your responses.

#### SETUP example

The following example configures a system with no memory test, 9600 baud, printer at 378h, and booting from C:

OCTAGON SYSTEMS CORPORATION 2040 PC/104 CPU SETUP UTILITY Vx.x

```

(c) Phoenix Technologies, Ltd. 1985, 1995

(Press SPACE to CHANGE, ENTER to ACCEPT, ESC to EXIT)

Serial Console on COM1:

Enabled

COM1 Console Baud Rate: 9600

Power on memory test: DISABLED

Boot Sequence: C: ONLY

ENABLED

Serial Port A:

Serial Port B:

ENABLED

Parallel (LPT) Port:

Parallel Port Mode:

ENABLED

Bidirectional Printer

Port

Parallel Port Address:

378h

Parallel Port Address: 378h

Parallel Port Interrupt: IRQ7

Number of floppy drives: 1

Floppy drive 1 size: 3.5", 1.4

Swap drives A and B: No

Number of hard drives: 0

SETUP Entry via Hotkey: ENABLED

Shadow Video BIOS area: DISABLED

Shadow D0000h-DFFFFh: DISABLED

Shadow D8000h-DFFFFh: DISABLED

Shadow D8000h-DFFFFFh: DISABLED

3.5", 1.44 MB

Shadow D8000h-DFFFFh:

DISABLED

Press ENTER to SAVE the changes

Press R to RESTART with original values or

Press ESC to EXIT without saving the changes:

Options Saved.

You must reset for these options to take effect.

2040 C:\>

```

*Note* Executing SETUP /D will change all setup parameters to default values.

# Chapter 4: Save and run programs

# **■ Save and run your programs on the** 2040 PC/104 CPU

Once you have written, tested and debugged your application, you can then save it in SSD1 if you have a DOC, or to a PC/104 hard disk. When you reboot the 2040 PC/104 CPU, your program can automatically load into DOS memory and execute. This assumes SSD1 contains a bootable DOS.

This chapter describes the following:

- Saving an application program

- Autoexecuting the program from the 2040 PC/104 CPU

- Overriding autoexecution of your program

The information in this chapter assumes you are using ROM–DOS or MS–DOS in your application. Some Microsoft programs make undocumented DOS calls. With ROM–DOS, an error returns when an undocumented DOS call is made, causing your program to operate erratically.

### Adding your application

To add your application to your SSD or hard disk, do the following:

1. Depending on the operating system you have installed, you may have the utilities TRANSFER.EXE or REMDISK/REMSERVE (ROM-DOS) or INTERLINK/INTERSVR (MS-DOS) on the DOC. You can use these utilities to transfer files from your host computer to the 2040 over a serial console. Refer to the documentation included with your operating system for information on how to use these utilities.

From a floppy drive on the 2040 PC/104 CPU, issue the COPY command.

- 2. Add or remove any device drivers for your application. You may want to do the same for the CONFIG.SYS file on your bootable drive.

- 3. To autoexecute your application, add your application name to the AUTOEXEC.BAT file.

#### Overriding the autoexecution of your application

You may stop the autoexecution of your application by doing one of the following options:

#### **Option 1**

1. Press F5 or F8 on a local keyboard (connected to the 2040). For more information, see your ROM–DOS or MS–DOS manual.

#### Option 2

- 1. Press Ctrl-C when the system is first starting. This halts all batch files.

- 2. Change AUTOEXEC.BAT and/or CONFIG.SYS to **not** call out your program.

#### **Option 3**

- 1. Install a floppy.

- 2. Change SETUP option "Boot Sequence" to "A: THEN C:"

- 3. Change SETUP to enable the floppy.

- 4. Boot from floppy.

- 5. Change AUTOEXEC.BAT on C:.

## Overview: Section 2 - Hardware

Section 2 discusses usage, functions, and system configurations of the 2040's major hardware features. The following chapters are included:

Chapter 5: Serial ports

Chapter 6: LPT1 parallel port Chapter 7: Console devices

Chapter 8: SSDs, DRAM, and battery backup

Chapter 9: External drives

Chapter 10: Interpreting "beep" codes

Chapter 11: PC/104 expansion

# Chapter 5: Serial ports

## **■ Description**

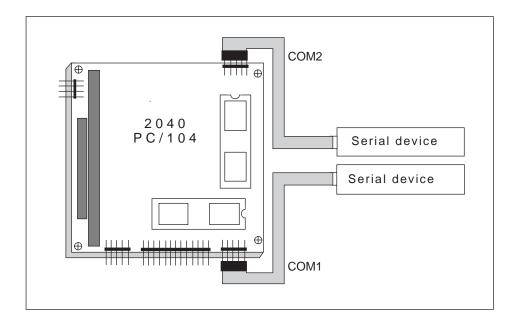

The 2040 PC/104 CPU has two serial ports, COM1 and COM2. These serial ports interface to a printer, terminal, or other serial device. Both ports support 5–, 6–, 7–, or 8–bit word lengths, 1, 1.5, or 2 stop bits, and baud rates up to 115.2K. COM1 can be used as a serial console or an 8–wire RS–232; COM2 is a dedicated 8–wire RS–232.

The serial ports have the following specifications:

- 16C550 compatible

- 16-byte FIFO buffers

- IEC 1000, level 3, ESD protection

- Contact discharge ±6 kV

- Air-gap discharge ±8 kV

- Backdrive protection

- Up to 115.2K baud operation

The following sections describe these ports in more detail.

## **≡** Serial port configurations

#### COM<sub>1</sub>

COM1 is a full 8-wire RS-232. The I/O address for COM1 is 3F8h. IRQ4 is dedicated to COM1. If COM1 is not used under interrupt control, IRQ4 may be used by other resources. If COM1 is the console, COM1 uses IRQ4. COM1 can be used for console I/O or RS-232 I/O. COM1 uses the J3, 10-pin header.

When a video card is **not** connected to the PC/104, COM1 can be used as the console port. All video and keyboard information is redirected through the console port.

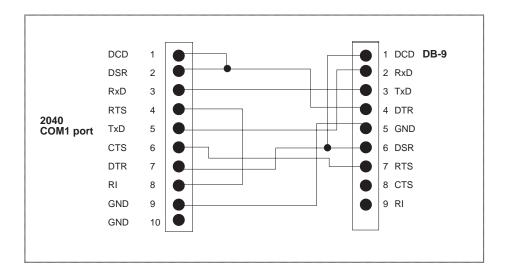

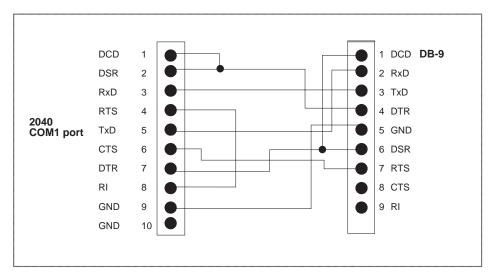

COM1 can be enabled as a serial console by two methods. SETUP allows you to select COM1 as a serial console. This is the default configuration stored in the BIOS. Also, when COM1 RTS is connected to COM1 RI the serial console on COM1 is enabled. This hardware configuration overrides the COM1 setting in SETUP. Figure 5–1 shows a custom null modem cable that performs this configuration.

Table 5–1 shows the pinout for COM1 and COM2.

#### COM<sub>2</sub>

COM2 is a dedicated full 8-wire RS-232 configuration. The I/O address for COM2 is 2F8h. IRQ3 is dedicated to COM2. If COM2 is not used under interrupt control, IRQ3 may be used by other resources. COM2 uses the J9, 10-pin header.

Table 5–1 shows the pinout for COM1 and COM2.

*Note* See the *Accessories* appendix for mating information on COM1 and COM2.

Table 5–1 COM1 and COM2 pinouts (J3 and J9 connectors)

| Pin | Signal | Pin | Signal |

|-----|--------|-----|--------|

| 1   | DCD    | 2   | DSR    |

| 3   | RxD    | 4   | RTS    |

| 5   | TxD    | 6   | CTS    |

| 7   | DTR    | 8   | RI     |

| 9   | Gnd    | 10  | Gnd    |

## **= Function and use of serial ports**

#### COM1 as the serial console device

Instead of using a PC/104 video card to connect a monitor, you can use COM1 as a console device. COM1 can be enabled as a serial console by two methods. SETUP allows you to select COM1 as a serial console. This is the default configuration stored in BIOS. Also, when COM1 RTS is connected to COM1 RI the serial console on COM1 is enabled. This hardware configuration overrides the COM1 setting in SETUP. Figure 5–1 shows a custom null modem cable that performs this configuration.

Note When interfacing the 2040 PC/104 CPU to your desktop PC, you must use a null modem cable. Commercial null modem adapters do not connect RI to RTS; they can be used if COM1 is enabled as a serial console in SETUP. The custom null modem below configures COM1 as a serial console regardless of the settings in SETUP. You also need PC SmartLINK, available from Octagon, or an equivalent terminal emulator.

Figure 5-1 Custom null modem adapter with RTS and RI connected

#### COM1 and COM2 as RS-232 I/O

COM1 and COM2 can be used as RS-232 serial ports. COM1 and COM2 support 8-wire RS-232 configurations. Use a VTC-9F or VTC-9M cable to interface from the 2040 PC/104 CPU to the serial device.

Figure 5-2 2040 PC/104 CPU serial devices

## Chapter 6: LPT1 parallel port

## **≡ LPT1** parallel port

The LPT1 port has a 26-pin connector. It supports the unidirectional standard mode, bidirectional mode, enhanced parallel port (EPP) mode, and extended capabilities port (ECP) mode. The default I/O address is 378h (IRQ7). You can also select I/O address 278h or 3BCh, or IRQ5, in the SETUP menu.

The LPT1 port supports a number of devices including a PC compatible printer, a floppy drive, a multiline display, a matrix keypad or an opto rack with opto-isolated digital I/O modules.

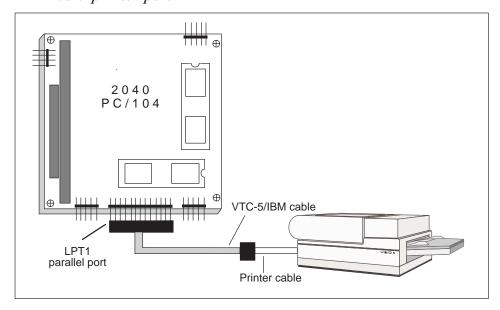

#### **≡** Printer

*Note* See the *Accessories* appendix for mating information on the LPT1 printer port connector.

To install a printer:

- 1. Make sure that the LPT1 port is in standard or bidirectional mode.

- 2. Connect an Octagon VTC-5/IBM cable from the LPT1 port to the 25-pin connector on your printer cable. You can also connect a PCA-36 cable directly from LPT1 to a Centronics interface on a printer.

- 3. Connect the cable to your printer.

Figure 6-1 LPT1 as a printer port

## **≡** Floppy drive

The LPT1 parallel port can be used as a floppy disk drive port. Refer to the *External Drives* chapter for connection information.

## **■ Display**

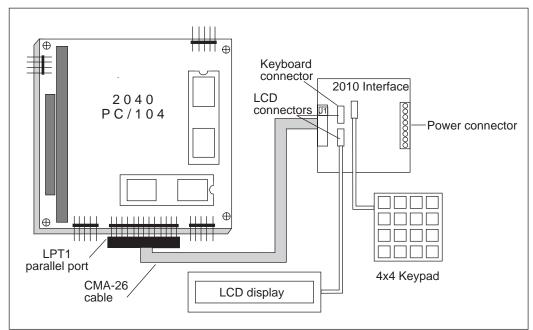

The LPT1 port supports either a 4 x 20 or a 4 x 40 liquid crystal display (LCD). To interface the displays to the 2040 PC/104 CPU, use the Octagon 2010 interface board. A CMA–26 cable is required to connect the interface board to the 2040 PC/104 CPU. The program DISPLAY.EXE (found on the 2040 PC/104 CPU utility disk) provides an easy method to use the display. Refer to the file DISPLAY.DOC on the 2040 PC/104 CPU utility disk for information on initializing and using the display. Also, refer to the *2010 product sheet* for more information on the interface board.

To install a display:

- 1. Connect a CMA-26 cable from the LPT1 port on the 2040 PC/104 CPU (J4) to J1 on the 2010. See Figure 6-2 (next page).

- 2. Connect the display cable to either the 14-pin or 16-pin header on the 2010. The size of the display will determine which header to use.

- 3. Refer to the file DISPLAY.DOC for more information on initializing and using the display.

## **≡ Keypad**

LPT1 also supports 4 x 4 matrix keypads. To interface the keypad to the 2040 PC/104 CPU, use the Octagon 2010 interface board. A CMA–26 cable is required to connect the interface board to the 2040 PC/104 CPU. The program DISPLAY.EXE (found on the 2040 PC/104 CPU utility disk) provides an easy method to use the keypad. Refer to the file DISPLAY.DOC on the 2040 PC/104 CPU utility disk for information on initializing and using the keypad. Also, refer to the *2010 product sheet* for information on the interface board.

To install a keypad:

- 1. Connect a CMA-26 cable from the LPT1 port on the 2040 PC/104 CPU (J4) to J1 on the 2010. See Figure 6-2.

- 2. Connect the keypad cable to the 10-pin header on the 2010.

- 3. Refer to the DISPLAY.DOC file for more information on reading the keypad.

Figure 6-2 LPT1 as a display or keypad port

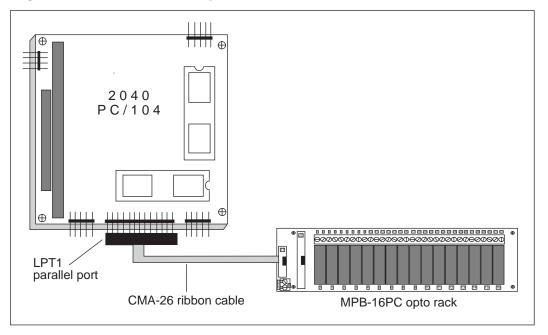

## **≡ Opto rack**

The Octagon MPB–16PC opto rack interfaces directly to the parallel printer port and can control high voltage/high current G4 opto—isolated modules. Of the sixteen positions available, eight can be either input or output, four are dedicated as inputs and the other four are dedicated as outputs. Refer to the MPB–16PC opto module rack product sheet for more information.

Figure 6-3 LPT1 and an opto rack

## Chapter 7: Console devices

## **■ Description**

The 2040 PC/104 CPU has three console options. You can use a PC/104 video card with a monitor and a keyboard as your console. You can also use COM1 as the console, or you can run the system without a console device.

## **≡ Selecting console devices**

The following represent the 2040 PC/104 CPU's three options for console devices:

- A standard PC/104 video card, such as an Octagon 2430 SVGA card, and a keyboard.

- Serial console from COM1. A serial cable/null modem adapter plugged into a host PC running SmartLINK provides both input and output. The local keyboard also allows input.

- No console device means no video output, either from a PC/104 card or the serial console. The local keyboard allows input.

#### COM1 as serial console device

Instead of using a PC/104 video card to connect a monitor, you can use COM1 as a console device. COM1 can be enabled as a serial console by two methods. SETUP allows you to select COM1 as a serial console. This is the default configuration stored in BIOS. Also, when COM1 RTS is connected to COM1 RI the serial console on COM1 is enabled. This hardware configuration overrides the COM1 setting in SETUP. Figure 7–1 shows a custom null modem cable that performs this configuration.

Note When interfacing the 2040 PC/104 CPU to your desktop PC, you must use a null modem cable. Commercial null modem adapters do not connect RI to RTS; they can be used if COM1 is enabled as a serial console in SETUP. The custom null modem below configures COM1 as a serial console regardless of the settings in SETUP. You also need PC SmartLINK, available from Octagon, or an equivalent terminal emulator.

Figure 7-1 Custom null modem adapter with RTS and RI connected

You can use a commercial null modem adapter instead of the custom null modem adapter shown above if the SETUP option "Serial Console on COM1" is enabled (default configuration). If this option is disabled in SETUP, you can get the serial console back by any of the following:

- 1. Using the custom null modem adapter shown above.

- 2. Removing the "S" jumper W1[5-6] and rebooting. This causes the 2040 to use the default SETUP settings from the BIOS.

- 3. Installing a PC/104 video card/keyboard to run SETUP and enable the serial console.

Custom null modem adapter

COM Port Desktop PC

COM Desktop PC

COM Desktop PC

COM Desktop PC

COM Desktop PC

Figure 7–2 The 2040 PC/104 CPU and a serial console

#### Keyboard, speaker, and mouse

You can add a keyboard and a local speaker with any of the console options listed above in the *Selecting console devices* section. Interface the keyboard and speaker via the 10–pin connector at J5. You may use any external speaker from 8–50 ohms. Table 7–1 shows the pinout for connector J5.

If your application requires a mouse, you can connect a serial mouse to COM1 or COM2, and load a mouse driver. The 2040 PC/104 CPU does not require a keyboard, speaker, or mouse for operation.

Table 7-1 Speaker, battery, keyboard, and reset: J5

| Pin | Signal   | Function                           |  |  |

|-----|----------|------------------------------------|--|--|

| 1   | +Speaker | +5V in series with 33 $\Omega$     |  |  |

| 2   | GND      | 3.6V external battery, negative    |  |  |

| 3   | Reset SW | External reset                     |  |  |

| 4   | KBD SW   | Inhibit switch to disable keyboard |  |  |

| 5   | KBD Data | Keyboard data                      |  |  |

| 6   | KBD CLK  | Keyboard clock                     |  |  |