## Application Note AN98071

#### Abstract

This report describes the CMOS integrated circuit PCD3316 and offers the required application information for designing the device in microprocessor controlled telephone sets and Adjunct Boxes with Caller-ID, Caller-ID on Call Waiting and Caller-Name identification.

Purchase of Philips  $I^2C$  components conveys a license under the Philips  $I^2C$  patent to use the components in the  $I^2C$  system, provided the system conforms to the  $I^2C$  specifications defined by Philips.

#### © Philips Electronics N.V. 1998

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.

The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights.

**Philips Semiconductors**

Application of the PCD3316 Caller Identification IC

Application Note AN98071

## **APPLICATION NOTE**

## Application of the PCD3316 Caller Identification IC

## AN98071

### Author(s):

Hans van Loon & Fred van Dongen Philips Semiconductors Systems Laboratory Eindhoven, The Netherlands

#### Keywords

CID / CIDCW FSK CAS Bellcore approved Add-on for telephone set

Number of pages: 69 Date: 98-08-26

#### Summary

This report is intended to provide application support on system level (HW as well as SW), for designing electronic telephone sets with the PCD3316 CIDCW receiver. The PCD3316 can be applied in ADSI phones, feature phones and adjunct boxes with (Bellcore) CID, CIDCW and CNAM systems and in CTI systems with VMWI.

The report explains the block diagram of the PCD3316 briefly and describes in more detail the functions of the device. Considerations are given for handling of the input signals as CAS, FSK, ringing and polarity inversion. Supply possibilities are discussed.

Ideas are offered for use of the device in different applications. A Bellcore approved telephone set with CID/ CIDCW and an application with VMWI, both built and tested, are described.

A chapter with 'frequently asked questions and their answers' is added.

The appendix gives an overview of the principles of signalling and requirements and standards.

## Application Note AN98071

### CONTENTS

| 1.                                                           | <b>INT</b><br>1.1<br>1.2                             | RODUCTION                                                                                                                                                                                                                                                                                                                                                                                          |                                       | . 7                                          |

|--------------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------------------------------|

| 2.                                                           | PIN                                                  | NING AND BLOCK DIAGRAM.                                                                                                                                                                                                                                                                                                                                                                            |                                       | 10                                           |

| 3.                                                           | DES                                                  | CRIPTION OF THE PCD3316                                                                                                                                                                                                                                                                                                                                                                            |                                       | 12                                           |

| 4.                                                           | <b>APF</b><br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6 | CAS receiving                                                                                                                                                                                                                                                                                                                                                                                      | · ·<br>· ·<br>· ·                     | 17<br>20<br>25<br>31<br>31                   |

| 5.                                                           | <b>APF</b><br>5.1<br>5.2<br>5.3<br>5.4               | PLICATION PROPOSALS                                                                                                                                                                                                                                                                                                                                                                                | <br><br>                              | 33<br>36<br>38                               |

| 6.                                                           | <b>RE</b><br>6.1<br>6.2                              | LIZED APPLICATIONS WITH THE PCD3316         Bellcore approved telephone set         6.1.1       Hardware description         6.1.2       Software description         6.1.3       µC considerations.         6.1.4       Timing consideration         6.1.5       Supply structure.         6.1.6       POTS mode.         6.1.7       What is done to get Bellcore approval         VMWI detector | · · · · · · · · · · · · · · · · · · · | 42<br>45<br>47<br>47<br>51<br>53<br>58<br>59 |

| 7.                                                           | FRE                                                  |                                                                                                                                                                                                                                                                                                                                                                                                    |                                       | 61                                           |

| APF                                                          | PENI                                                 | DIX 1 CID / SIGNALLING AND STANDARDS                                                                                                                                                                                                                                                                                                                                                               |                                       | 63                                           |

| Fig.<br>Fig.<br>Fig.<br>Fig.<br>Fig.<br>Fig.<br>Fig.<br>Fig. | 2<br>3<br>5<br>6<br>7<br>8<br>9<br>10                | Pin configuration                                                                                                                                                                                                                                                                                                                                                                                  | · · · · · · · · · · · · · · · · · · · | 11<br>16<br>18<br>19<br>20<br>21<br>21<br>22 |

## Application Note AN98071

|         | FSK receive control procedure                                        |     |     |     |     |     |     |     |       |      |

|---------|----------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-------|------|

| -       | POL0 and POL1 handling with a sinewave as input signal               |     |     |     |     |     |     |     |       |      |

| Fig.14  | Signal path of ringer signal from line to POL-inputs                 |     |     |     |     |     |     |     |       | 26   |

| Fig.15  | Transfer from line to POL inputs                                     |     |     |     |     |     |     |     |       | . 27 |

| Fig.16  | POL0/POL1 detection procedure                                        |     |     |     |     |     |     |     |       | . 28 |

| Fig.17  | Polarity change and ringer frequency detection procedure             |     |     |     |     |     |     |     |       | . 29 |

|         | Ringer frequency detection procedure                                 |     |     |     |     |     |     |     |       |      |

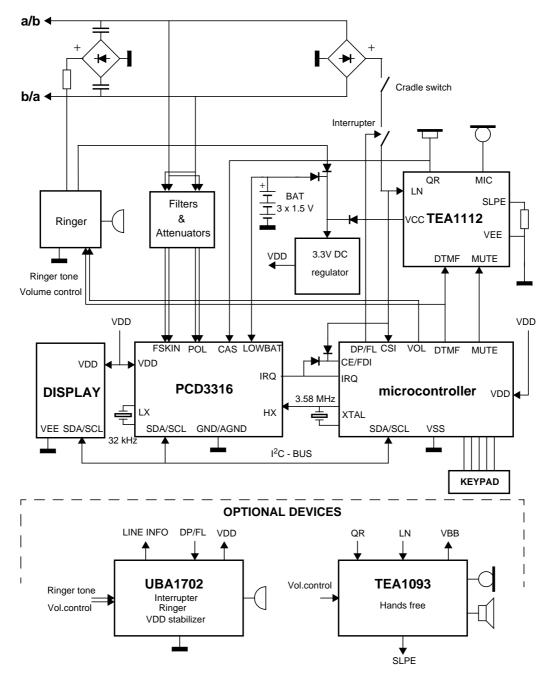

|         | Block diagram of basic telephone set with CID/CIDCW functions        |     |     |     |     |     |     |     |       |      |

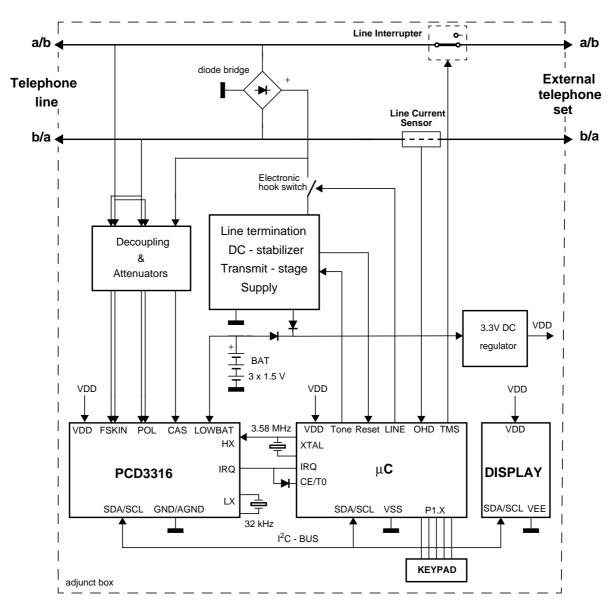

| Fig.20  | Block diagram of an Adjunct box                                      |     |     |     |     |     |     |     |       | . 36 |

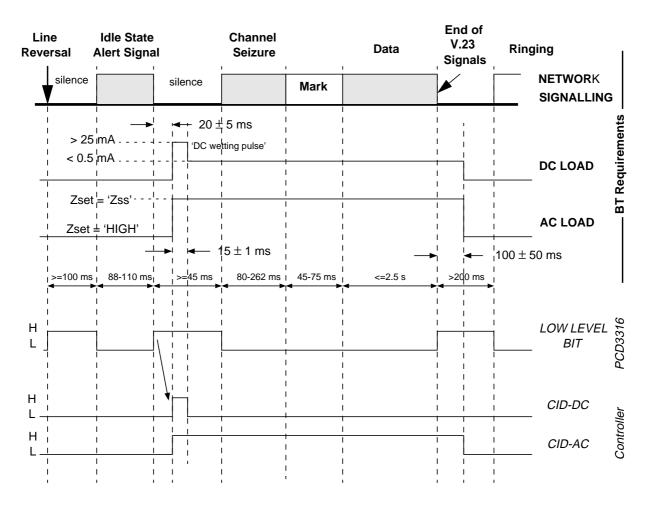

| Fig.21  | BT application; Down stream signalling and timing of control signals |     |     |     |     |     |     |     |       | . 38 |

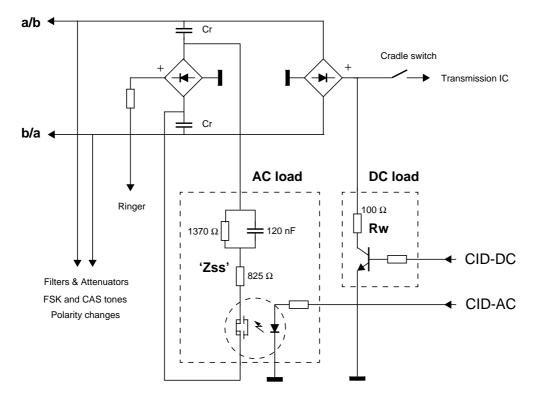

| Fig.22  | BT application; circuit adaption to basic set of Fig.19              |     |     |     |     |     |     |     |       | . 39 |

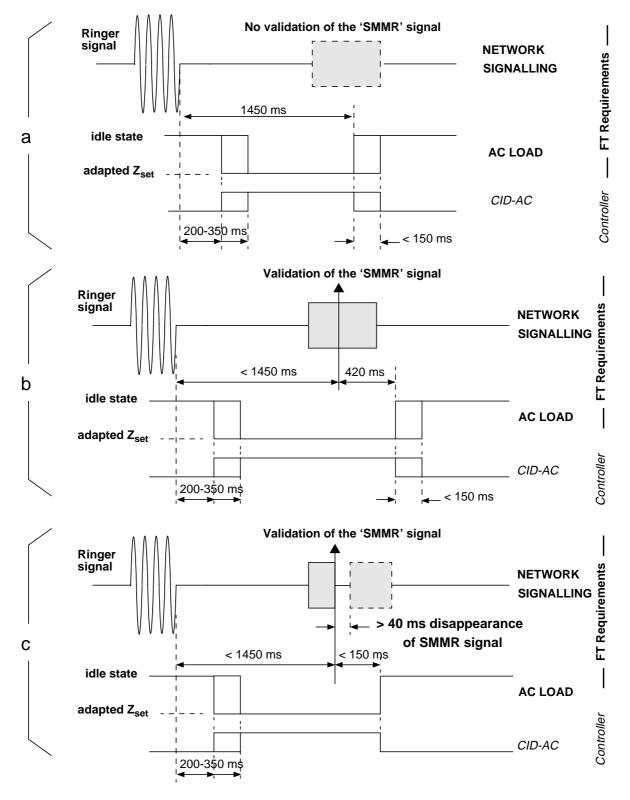

| Fig.23  | FT application; CID signalling and timing of control signals         |     |     |     |     |     |     |     |       | . 41 |

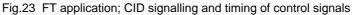

| Fig.24  | Normal CIDCW signal handling.                                        |     |     |     |     |     |     |     |       | . 48 |

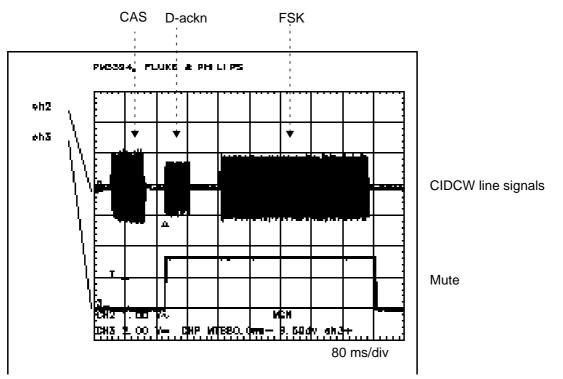

| Fig.25  | The CAS signal is not followed by FSK message                        |     |     |     |     |     |     |     |       | . 49 |

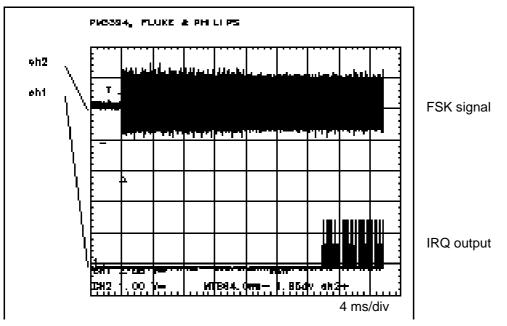

| Fig.26  | FSK and IRQ timing (complete signals).                               |     |     |     |     |     |     |     |       | . 49 |

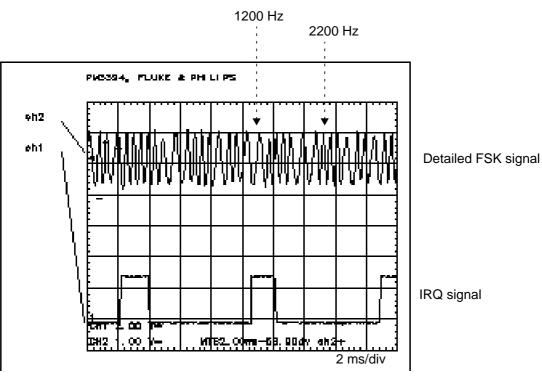

| Fig.27  | Detailed FSK and IRQ timing.                                         |     |     |     |     |     |     |     |       | 50   |

| Fig.28  | Line interrupter and ringer circuit                                  |     |     |     |     |     |     |     |       | . 54 |

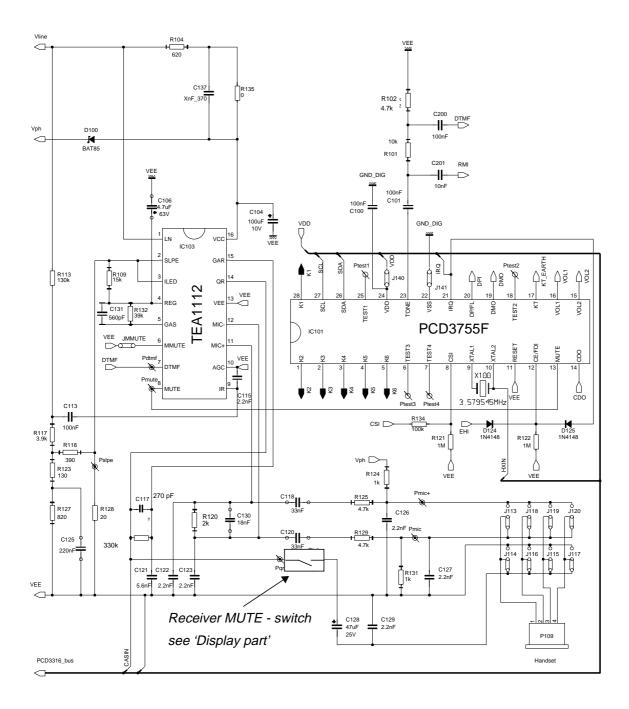

| -       | Transmission and dialler circuit.                                    |     |     |     |     |     |     |     |       |      |

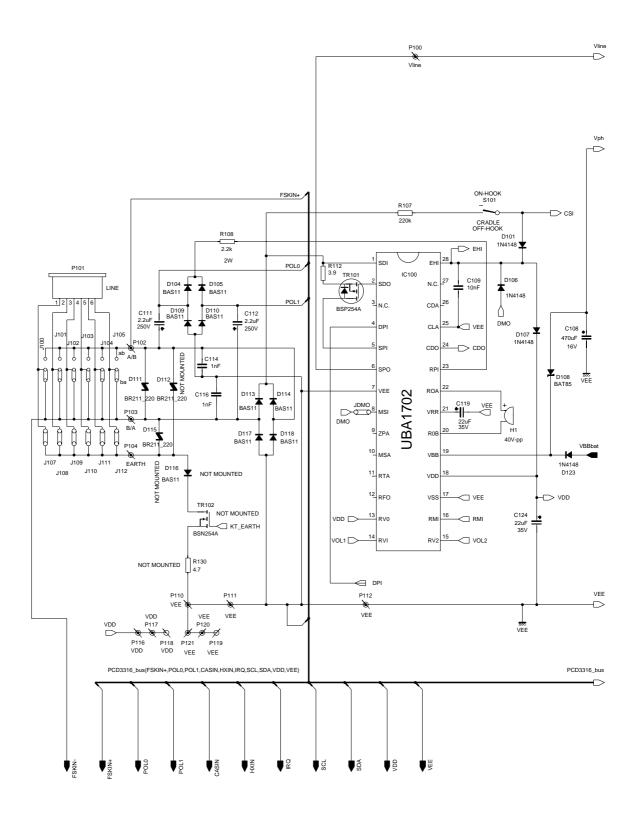

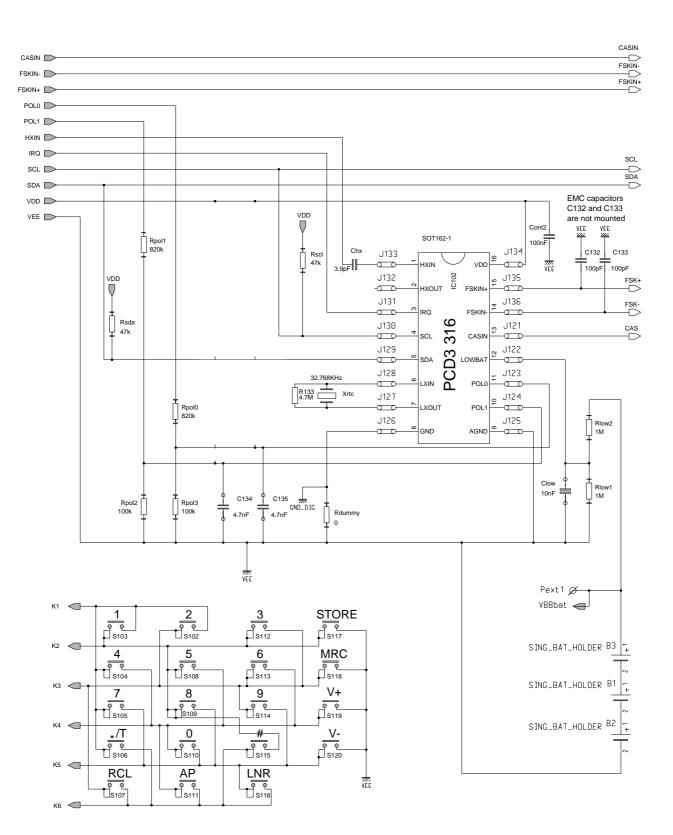

| •       | PCD3316 configuration                                                |     |     |     |     |     |     |     |       | 56   |

| •       | Display part                                                         |     |     |     |     |     |     |     |       |      |

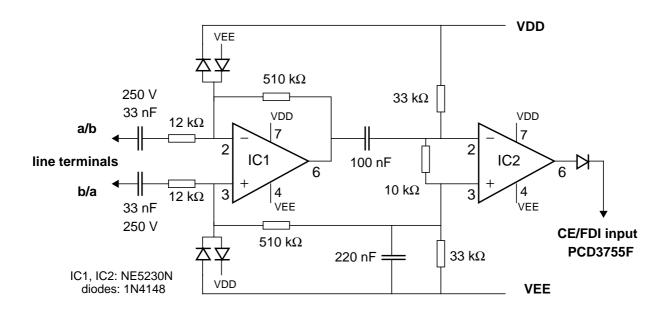

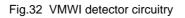

| -       | VMWI detector circuitry                                              |     |     |     |     |     |     |     |       |      |

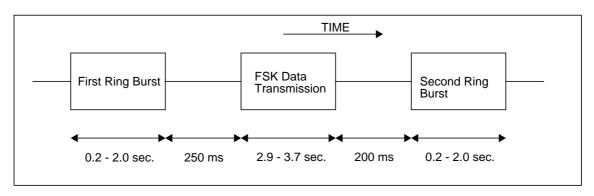

| •       | CID Timing                                                           |     |     |     |     |     |     |     |       |      |

| -       |                                                                      |     |     |     |     |     |     |     |       |      |

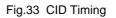

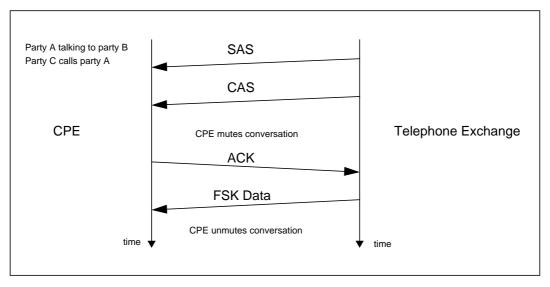

| -       | CIDCW order                                                          |     |     |     |     |     |     |     |       |      |

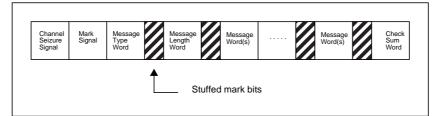

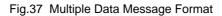

| •       | Single Data Message Format.                                          |     |     |     |     |     |     |     |       |      |

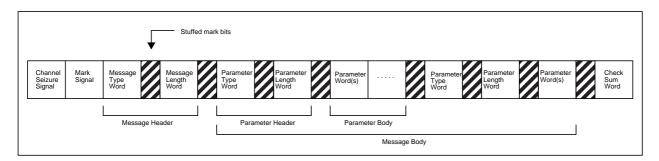

| -       | Multiple Data Message Format                                         |     |     |     |     |     |     |     |       |      |

| 0       |                                                                      |     |     |     |     |     |     |     |       |      |

| TABLE 1 | Pin functions                                                        |     |     |     |     |     |     |     |       | . 10 |

| TABLE 2 |                                                                      |     |     |     |     |     |     |     |       |      |

| TABLE 3 |                                                                      |     |     |     |     |     |     |     |       |      |

| TABLE 4 | -                                                                    |     |     |     |     |     |     |     |       |      |

| TABLE 5 | -                                                                    |     |     |     |     |     |     |     |       |      |

| TABLE 6 | 0                                                                    |     |     |     |     |     |     |     |       |      |

| TABLE 7 |                                                                      |     |     |     |     |     |     |     |       |      |

| TABLE 8 |                                                                      |     |     |     |     |     |     |     |       |      |

| TABLE 9 |                                                                      |     |     |     |     |     |     |     |       |      |

| TABLE 1 |                                                                      |     |     |     |     |     |     |     |       |      |

| TABLE 1 | -                                                                    |     |     |     |     |     |     |     |       |      |

| TABLE 1 | 8 8                                                                  |     |     |     |     |     |     |     |       |      |

| TABLE 1 | 5 <i>,</i>                                                           |     |     |     |     |     |     |     |       |      |

| TABLE   |                                                                      |     |     |     |     |     |     |     |       |      |

| TABLE 1 | 5                                                                    |     |     |     |     |     |     |     |       |      |

| TABLE 1 |                                                                      |     |     |     |     |     |     |     |       |      |

| TABLE 1 |                                                                      |     |     |     |     |     |     |     |       |      |

| TABLE 1 |                                                                      |     |     |     |     |     |     |     |       |      |

| TABLE 1 |                                                                      |     |     |     |     |     |     |     |       |      |

| TABLE 2 |                                                                      |     |     |     |     |     |     |     |       |      |

| TABLE 2 |                                                                      |     |     |     |     |     |     |     |       |      |

|         |                                                                      | • • | • • | • • | • • | • • | • • | • • | • • • | 03   |

#### 1. INTRODUCTION

The PCD3316 is a CMOS integrated circuit for receiving physical layer signals like Bellcore's CPE Alerting Signal (CAS) and BT's Idle State Tone Alert Signal. The device is capable of a very high precision detection of the dual tone (2130 and 2750 Hz) by using a patented digital algorithm.

For timing purposes the PCD3316 can be programmed to generate an interrupt signal to the micro-controller every second or every minute. This can be used for Real-Time-Clock and timing purposes, these timings are derived from an on chip 32.768 kHz crystal oscillator.

Also incorporated in the device are an FSK receiver/demodulator and a Ring or Polarity Change detector.

The status of the PCD3316, the received FSK data bytes and the ringer period can be read, from internal register, and many options can be selected via the I<sup>2</sup>C-bus serial interface.

Detection of a polarity change on the inputs POL0 or POL1, the reception of an FSK data byte, the detection of a CAS tone or a time base interrupt is signalled to the micro-controller by an interrupt request signal (IRQ). In power-down mode only the polarity comparators and the 32.768 kHz oscillator are active. The micro-controller can communicate with the PCD3316 device via the serial interface.

The PCD3316 can be used in Analog Display Services Interface (ADSI), feature phones and adjunct boxes with Bellcore CID (Caller-ID), CIDCW (Caller-ID on Call Waiting) and CNAM (Caller-NAMe) systems and Computer Telephony Integrated (CTI) systems.

Caller ID was first developed in the Bell labs, after which Nortel made the first practical implementation. Nowadays there are two FSK (Frequency Shift Keying) standards Bell 202 and CCITT V23, which mainly differ in the actual bits frequency (Bell is 1200 Hz and 2200 Hz, while CCITT is 1100 Hz and 2100 Hz). The basic Caller ID types 'Caller ID type 1 and type 2', supported by the PCD3316, are specified in APPENDIX 1.

The PCD3316 is designed with differential FSK inputs and a separated single ended CAS input to guarantee reception of low level signals respectively to separate CAS tones from near end speech by means of the side tone circuitry of the applied transmission IC.

#### 1.1 Definition and Abbreviations

| a/b; b/a<br>ADSI | Line terminals of application<br>Analog Display Service Interface |

|------------------|-------------------------------------------------------------------|

| AGC              | Automatic Gain Control; line loss compensation facility           |

| AP               | Access Pause                                                      |

| BRL              | Balance Return Loss                                               |

| BT               | British Telecom                                                   |

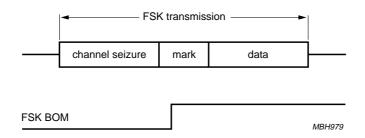

| BOM              | Begin Of Mark (FSK transmission)                                  |

| BOM              | Bill Of Materials (Components List)                               |

| CAS              | CPE Alerting System                                               |

| CID              | Caller Identification Delivery                                    |

| CIDCW            | Caller Identification Delivery on Call Waiting                    |

| CNAM             | Caller NAMe delivery                                              |

| CND              | Caller Number Delivery                                            |

| CPE              | Customer Premises Equipment                                       |

| Cradle           | Hook key                                                          |

| CTI              | Computer Telephony Integrated systems                             |

| DEMO             | Demonstration model                                               |

| DMO              | Dial Mode Operation                                               |

| DTMF             | Dual Tone Multi Frequency                                         |

| EMC              | Electro Magnetic Compatibility                                    |

**Philips Semiconductors**

# Application of the PCD3316 Caller Identification IC

## Application Note AN98071

| FSK                         | Frequency Shift Keying                                                   |

|-----------------------------|--------------------------------------------------------------------------|

| FT                          | France Telecom                                                           |

| HW                          | Hardware                                                                 |

| l <sub>line</sub>           | Line current into the a/b-terminals                                      |

| I <sup>2</sup> C            | Inter-Integrated Circuit bus                                             |

| ISAS                        | Idle State Alert Signal                                                  |

| LCD                         | Light Crystal Display                                                    |

| LED                         | Liquid Emitting Diode                                                    |

| LPH7319-3                   | Display module with driver PCF2116K                                      |

| LNR                         | Last Number Redial                                                       |

| MDMF                        | Multiple Data Message Format                                             |

| MIC                         | Microphone input                                                         |

| NDA                         | Non-Disclosure Agreement                                                 |

| Off-hook                    | Handset is lifted (Switch "cradle" in position OFF)                      |

| On-hook                     | Handset is on the base (Switch "cradle" in position ON)                  |

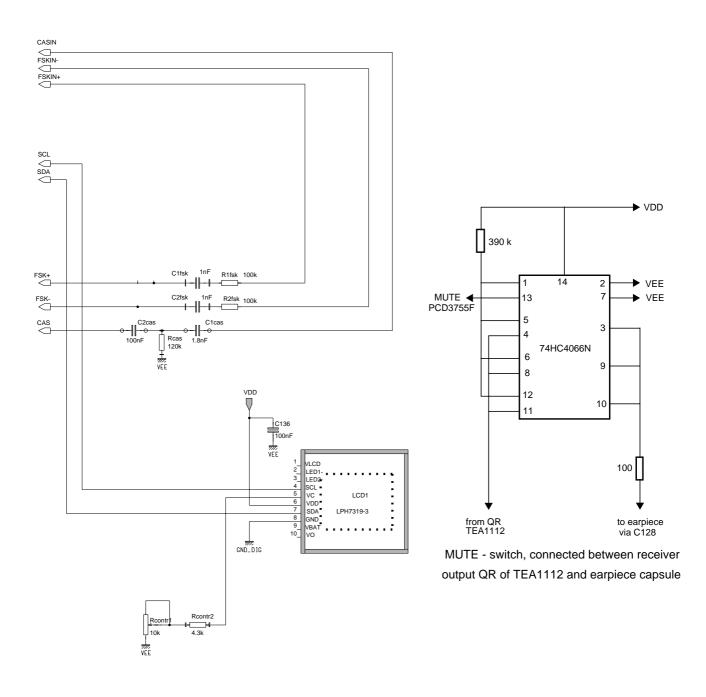

| OM5843                      | Demo Board with the UBA1702, TEA1112, PCD3755F, PCD3316 and LPH7319-3    |

| OTP                         | One Time Programmable Read Only Memory                                   |

| Pa                          | Sound pressure in Pascal; 1 Pa = $1 \text{ N/m}^2 = 94 \text{ dBSPL}$    |

| PCB                         | Printed Circuit Board                                                    |

| PCD3316                     | Caller-ID and caller ID on Call Waiting receiver                         |

| PCD3755F                    | OTP microcontroller                                                      |

| POR                         | Power On Reset                                                           |

| POTS                        | Plain Old Telephone Services                                             |

| RCL                         | Recall                                                                   |

| SAS                         | Subscriber Alerting Signal                                               |

| SINAD                       | Signal Noise and Distortion ratio                                        |

| SMDF                        | Single Message Data Format                                               |

| SW                          | Software                                                                 |

| TAS                         | Tone Alert Signal                                                        |

| TEA1112                     | Transmission IC                                                          |

| TEL+                        | Positive Earpiece input                                                  |

| TEL-                        | Negative Earpiece input                                                  |

| UBA1702                     | Line interrupter driver and ringer for PMOST                             |

| UBA1702A                    | Line interrupter driver and ringer for PNP                               |

| V <sub>ref</sub>            | Reference voltage of PCD3316, 1.25 V typical                             |

| V <sub>hys(POR)</sub>       | Power-on reset hysteresis voltage, 100 mV typical                        |

| V <sub>POR(H)</sub><br>VMWI | Power-on reset high voltage, 2.05 V typical                              |

| Zi                          | Visual Message Waiting Indicator<br>Input impedance with respect to AGND |

|                             | Line impedance                                                           |

| Z <sub>line</sub><br>z      | Set impedance between the a/b-terminals                                  |

| Z <sub>set</sub>            | Set impedative between the abrientinals                                  |

#### 1.2 References

- Philips Semiconductors DATA sheet 'PCD3316 CIDCW receiver' product specification May 1998. Order number: 9397 750 03525.

- Philips Semiconductors User Manual OM5843 Report No.: ETT/UM97002.4, 'PCD3316 CID/CW demo board', from 97-11-24.

- [3] Philips Semiconductors Data Handbook IC03a, 'Semiconductors for Wired Telecom Systems', 1997. Order no. 9397 750 00839

- Philips Semiconductors Application Handbook IC03b, 'Semiconductors for Wired Telecom Systems', 1997.

Order no. 9397 750 00811

- [5] Philips Semiconductors I<sup>2</sup>C Peripherals Data Handbook IC12, order number: 9398 750 01647, or the Brochure 'The I<sup>2</sup>C-bus and how to use it', order no. 9398 393 40011.

- TIA/EIA PN-3647 (to become ANSI TIA/EIA-xxx-1997) 'Telecommunications Telephone Terminal Equipment Type 1 Caller Identity Equipment Performance Requirements', from july 1997.

Publication from: Telecommunication Industry Association, Engineering Department, Suite 300, 2500 Wilson Boulevard, Arlington, VA22201.

- [7] prETS 300 778-1 (draft) 'PSTN; Protocol over the local loop for display and related services; Terminal Equipment requirements; Part 1: Off-line (on-hook) data transmission', from june 1997.

Publication from ETSI: European Telecommunications Standard Institute

- [8] ETS 300 659-1 'PSTN; Subscriber line protocol over the local loop for display and (related services); Part 1: On-hook data transmission', from february 1997.

Publication from ETSI: European Telecommunications Standard Institute

- [9] Philips Semiconductors Application Note AN96045. "Reference specification of a dialler implementing the reference design", Authors: C.D.Holzscherer, R.J.Cornelissen, J.G.K.Fajta. Date 16 October 96

- [10] LSSGR: Voiceband Data Transmission Interface Section 6.6, Generic Requirements GR-30-CORE issue 1, December 1994, Bell Communications Research (Bellcore).

- [11] CPE Compatibility Considerations for the Voiceband Data Transmission Interface, Special Report SR-TSV-002476 issue 1, December 1992, Bell Communications Research (Bellcore).

- [12] BT, SIN 242 Issue 02, Nov 1996. 'Calling line identification service. Terminal Equipment Requirements Part1 Idle state, Down stream signalling, Part 2 Loop state signalling

- [13] France Telecom Recommandation B 14-10W 1995, 'Interface de reception de l'identite du demandeur et de la notification pour terminaux analogiques', Edition 1 de septembre 1995.

## Application Note AN98071

### 2. PINNING AND BLOCK DIAGRAM

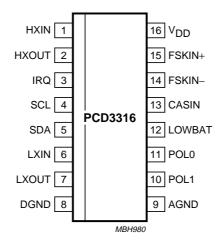

Fig.1 Pin configuration

| SYMBOL          | PIN | I/O | DESCRIPTION                                              |  |  |  |  |  |  |

|-----------------|-----|-----|----------------------------------------------------------|--|--|--|--|--|--|

| HXIN            | 1   | I   | 3.58 MHz crystal oscillator input                        |  |  |  |  |  |  |

| HXOUT           | 2   | 0   | 3.58 MHz crystal oscillator output                       |  |  |  |  |  |  |

| IRQ             | 3   | 0   | interrupt output; programmable active HIGH or active LOW |  |  |  |  |  |  |

| SCL             | 4   | I   | serial clock line of I <sup>2</sup> C-bus                |  |  |  |  |  |  |

| SDA             | 5   | I/O | serial data line of I <sup>2</sup> C-bus                 |  |  |  |  |  |  |

| LXIN            | 6   | I   | 32.768 kHz crystal oscillator input                      |  |  |  |  |  |  |

| LXOUT           | 7   | 0   | 32.768 kHz crystal oscillator output                     |  |  |  |  |  |  |

| DGND            | 8   | -   | digital ground                                           |  |  |  |  |  |  |

| AGND            | 9   | -   | analog ground                                            |  |  |  |  |  |  |

| POL1            | 10  | I   | polarity detector input 1                                |  |  |  |  |  |  |

| POL0            | 11  | I   | polarity detector input 0                                |  |  |  |  |  |  |

| LOWBAT          | 12  | I   | low battery detector input                               |  |  |  |  |  |  |

| CASIN           | 13  | I   | input pin for CAS signal                                 |  |  |  |  |  |  |

| FSKIN-          | 14  | Ι   | negative input for FSK signal                            |  |  |  |  |  |  |

| FSKIN+          | 15  | I   | positive input for FSK signal                            |  |  |  |  |  |  |

| V <sub>DD</sub> | 16  | -   | positive supply                                          |  |  |  |  |  |  |

| TABLE 1 | Pin functions |

|---------|---------------|

|---------|---------------|

## Application Note AN98071

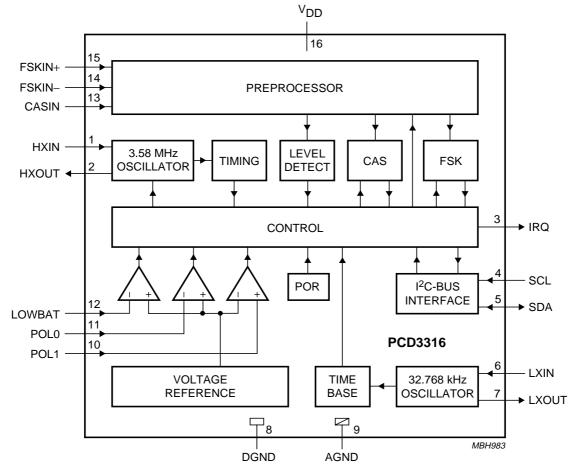

Fig.2 Block diagram of the PCD3316

### 3. DESCRIPTION OF THE PCD3316

A brief description of the PCD3316 is given in this chapter with reference to block diagram Fig.2. Evaluation results are presented of some of the PCD3316 blocks which are derived from a typical sample measured at room temperature.

VDD = 3.0 V; values of input impedances are given as typical values; unless otherwise written. The dBm values are referred to 0 dBm = 775 mV<sub>rms</sub>. The pinning and the pin functions of the PCD3316 are shown in Fig.1 respectively in TABLE 1.

An overview of the registers is given in the 'CONTROL' block by means of TABLE 2. Consult the PCD3316 data sheet [1] for circuit details, detailed description of the registers and characteristics.

### PRE-PROCESSOR (FSKIN+, FSKIN-, CASIN)

The FSK or CAS signals from the telephone line are processed by the pre-processor block by means of an A/D converter and a digital bandpass filter. The bandpass filter is applied for FSK or CAS signals depending on the mode selection in Mode register 1.

The inputs FSKIN+ and FSKIN– have a differential Zi of 1.4 M $\Omega$ . The single ended CASIN input measures 1.4 M $\Omega$  to AGND. The pre-processed signals are delivered to the Level detector, CAS detector and FSK receiver.

The CAS detector will be enabled (FSK receiver disabled):

- In Off-hook (speech) mode

The FSK receiver will be enabled (CAS detector disabled):

- In CID / on-hook mode after detection of a ringing signal

- After detection of a correct CAS tone in BT mode (on-hook) or CIDCW in off-hook mode

#### Harmonics of pre-processed FSK / CAS signals:

- FSK: The harmonics of the output signal of the pre-processor are below the –69 dBm at an input signal of 0 dBm signal, 1951 Hz and up to a frequency range of 8 kHz.

- CAS: The harmonics of the output signal of the pre-processor are below the –62 dBm at an input signal of 0 dBm signal, 1078 Hz and up to a frequency range of 8 kHz.

The CASIN input is a single ended input. More noise and distortion is expected from the reference voltage in comparison with the differential FSK input.

To prevent a so called 'Talk-Off', the first harmonic has to be low with respect to the input sensitivity from 0 dBm till around –38 dBm. Lower input levels will not be treated as valid signals. The first harmonic in worst case is around –55 dBm which is far below the requirements.

The noise level is about -80 dBm and constant over the over the frequency band from 300 Hz to 8 kHz.

### 3.58 MHz OSCILLATOR (HXIN, HXOUT)

The 3.58 MHz oscillator has to be activated by means of an external quartz crystal or ceramic resonator connected between the HXIN and HXOUT pins. This oscillator is needed for the FSK receiver and CAS detection and must be switched-off in power down mode by register setting; see [1].

#### TIMING

The block delivers the timing signals, generated by the 3.58 MHz oscillator, to the control block.

### LEVEL DETECT

The level detector has a threshold of -40 dBm typical. When the average signal level on FSKIN+/- 'or' CASIN is below this threshold, within a time period of about 8 ms, the LOW Level bit is set (Interrupt status register). The level detector is used to observe a carrier loss during FSK transmission and to detect the TAS signal for BT.

### CAS

After a Power-on reset or enabling the CAS detector the internal CAS registers are initialized. When a correct dual tone of 2130 Hz and 2750 Hz is detected with a duration of more than 60 ms, while the CAS detector is enabled, the PCD3316 will generate an interrupt and the CAS Interrupt is set (Interrupt register). Generation of interrupts will be blocked when the signal level on the CASIN input is below the threshold of the level detector.

### FSK

The FSK receiver can be enabled by setting the FSK on/off bit (Mode register 1). FSK transmission protocol starts with a channel seizure (alternation of 0's and 1's) followed by a block of marks (only 1's) and finally by the FSK data word (ref: BT / Bellcore specs) which consists of a start bit, eight data bits and a stop bit. After detection of the mark bits, the FSK-BOM indication bit is set (Status register). The FSK receiver generates an interrupt after receiving the complete data word at the IRQ pin. When a valid data word has been received, the FSK data is available in the FSK data register for further processing by the microcontroller.

### CONTROL (IRQ)

This block takes care of the IRQ (Interrupt ReQuest) handling and the interface control of internal registers, I<sup>2</sup>C interface and low battery, polarity, FSK and CAS detection.

The IRQ push-pull output is evaluated at VDD = 3.0 V with respect to maximum PORT current in low as well as in high state. Also, the output levels are measured at 2 mA source and sink currents.

Input current (low state) = 5.4 mA when 0.4 V is applied on IRQ Output current (high state) = 7.5 mA when 2.6 V is applied on IRQ

Low level = 0.14 V when 2 mA is forced into IRQ

High level = 2.90 V when 2 mA is drawn out of IRQ

### Low battery detection (LOWBAT)

A tap of the battery voltage can be compared with  $V_{ref}$  by means of the LOWBAT input. If the level on LOWBAT is less than  $V_{ref}$ , indicating end of battery life-time, the LOW-BAT indication (Status register) is set. The LOW-BAT indication is cleared when the level on LOWBAT is more than  $V_{ref}$ .

#### **Ring or Polarity change detector** (POL0, POL1)

Two comparators are available for ring and polarity detection. The ringing signal and polarity change of the DC line voltage are received by the inputs POL0 and POL1, via input attenuators, and compared with  $V_{ref}$  from the Voltage reference block. A POL0 or POL1 interrupt is generated when the level on input POL0 or POL1 crosses the  $V_{ref}$  reference level.

A polarity reversal is detected when a POL1 or POL0 interrupt is generated without setting the ringer period register. A ringer signal is detected when a sequence of interrupts are generated from POL1-POL0-POL1... which sets the ringer period register with the period time of the ringer signal by means of a binary value.

#### Registers

The PCD3316 has in total six internal registers, four registers are read only and contain the internal status/ interrupt and counter values, the two last registers are read/write and control the functionality of the device. In TABLE 2 these registers with there contents are given, for a detailed description see reference [1].

| TABLE 2 Register contents |                        |                       |                       |                          |                   |                  |           |  |  |

|---------------------------|------------------------|-----------------------|-----------------------|--------------------------|-------------------|------------------|-----------|--|--|

| BIT 7                     | BIT 6                  | BIT 5                 | BIT 4                 | BIT 3                    | BIT 2             | BIT 1            | BIT 0     |  |  |

| Interrupt sta             | tus register CIDIN     | T; address 00         | )H; read only         |                          |                   |                  |           |  |  |

| MIN<br>Interrupt          | SEC interrupt          | FSK<br>interrupt      | Low Level<br>Status   | POL1<br>Interrupt        | POL0<br>Interrupt | CAS<br>Interrupt | RES       |  |  |

| FSK data reg              | gister CIDFSK; add     | dress 01H; re         | ad only               |                          |                   |                  |           |  |  |

| D7                        | D6                     | D5                    | D4                    | D3                       | D2                | D1               | D0        |  |  |

| Status regis              | ter CIDSTA; addre      | ss 02H; read          | only                  | •                        |                   | •                | •         |  |  |

| POL1                      | POL0                   | LOW-BAT<br>Indication | FSK-BOM<br>Indication | FSK-OVR<br>Error         | FSK-FRM<br>Error  | RES              | RES       |  |  |

| Ringer perio              | d register CIDRNO      | G; address 03         | H; read only          |                          |                   |                  |           |  |  |

| D7                        | D6                     | D5                    | D4                    | D3                       | D2                | D1               | D0        |  |  |

| Mode regist               | er 1 CIDMD1; addr      | ess 04H; read         | d/write               | •                        |                   | •                | •         |  |  |

| FSK<br>on/off             | FSK BOM-mask<br>on/off | CAS on/off            | POL on/off            | INT Polarity<br>HIGH/LOW | RES               | RES              | RES       |  |  |

| Mode regist               | er 2 CIDMD2; addr      | ess 05H; read         | d/write               |                          |                   |                  |           |  |  |

| XTAL<br>on/off            | TB on/off              | SEC/MIN               | INT-SUP<br>on/off     | RES                      | RES               | VERSION 1        | VERSION 0 |  |  |

### POR

An on-chip Power-On Reset circuit activates a reset as long as VDD is below  $V_{POR(H)}$ . If VDD exceeds this level, the 3.58 MHz oscillator starts to initiate the PCD3316 and to set the registers to their default value. The initialization takes a maximum of 100 clock-cycles. The performance of the IC will be reached at the specified minimum supply voltage of 2.5 V. The IC will be switched-off when a falling VDD crosses the threshold  $V_{POR(H)} - V_{hys(POR)}$ .

Measured levels are:  $V_{POR(H)} = 1.99 \text{ V}$ ,  $V_{POR(L)} = 1.88 \text{ V}$ ,  $V_{hys(POR)} = 110 \text{ mV}$ .

## I<sup>2</sup>C - BUS INTERFACE (SCL, SDA)

The I<sup>2</sup>C-bus interface takes care of the communication with the microcontroller which is required in a system with the PCD3316. The IC operates in the slave transmitter/receiver mode only. The I<sup>2</sup>C-bus is for bidirectional, two-line communication between different ICs or modules via the serial data line (SDA) and the serial clock line (SCL).

The status of the PCD3316, the received FSK data and the ringer period can be read while many options can be selected via the  $I^2C$ -bus.

Both lines have to be connected to VDD via pull-up resistors. A detailed description of the I<sup>2</sup>C-bus specification can be found in [5].

#### Input levels

SDA and SCL are the only two digital inputs of the device. Both pins are identical I/O's with the difference that the output path of pin SCL is disabled. The input levels of these  $I^2C$  pins are specified between 0V and 30% of VDD for low levels and between 70% of VDD and VDD for high levels. Test results show low levels between 0V and > 33% of VDD and high levels between < 63% of VDD and VDD.

#### Output currents

The SDA output (open drain) can drive only a logical '0'. For values of the output current in low state refer to 'Control (IRQ)' in this chapter, because the circuitry for driving the low levels are in both ports the same.

### VOLTAGE REFERENCE

This block generates the reference voltage  $V_{ref} = 1.25 \text{ V} (\pm 100 \text{ mV})$  applied for low battery detection and ring or polarity detection.

### TIME BASE

The time base block is driven by the 32 kHz oscillator. In case the TB-on/off bit (Mode register 2) is set, the time base block generates a 1 second or a 1 minute interrupt signal and every second or minute the MIN and/or SEC interrupt bits are set. The SEC/MIN bit (Mode register 2) selects whether every second or every minute an interrupt is generated. All possible selections can be found in [1].

Resetting bit TB on/off will only disable the time base interrupts; the 32 kHz oscillator continues to operate.

### 32 kHz OSCILLATOR (LXIN, LXOUT)

This oscillator is permanently operating. It uses a 32.768 kHz quartz crystal (or resonator) connected between the LXIN and LXOUT pins. The 32 kHz oscillator is used for the Ring or Polarity change detector, the Low battery detector, the Low level detector, detection of a correct twist level and for generation of either 1 second or 1 minute interrupt.

#### SUPPLY / Ground references / Power down (VDD, DGND, AGND)

This part which is not indicated in the block diagram requires some explanation.

The PCD3316 is supplied via the VDD pin; the VDD voltage has to be between 2.5 V and 3.6 V. The device has two ground references, DGND is the ground reference of the digital circuitry of the PCD3316 while AGND is the reference ground of the analog inputs POL0, POL1, LOWBAT, FSKIN+, FSKIN- and CASIN. The ground references have to be star-connected to the supply ground on the PCB to prevents disturbances of the analog ground.

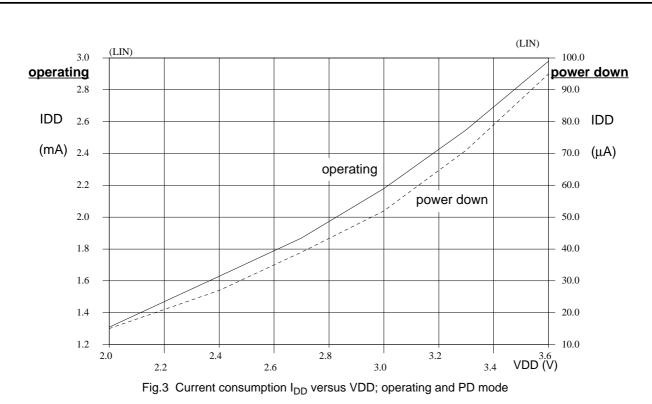

The specified current consumption is 2.3 mA maximum in operating mode and 70  $\mu$ A maximum in power down mode at VDD = 2.5 V in both cases.

The current consumption  $I_{DD}$  as a function of VDD of the PCD3316 is shown in Fig.3 for operating as well as PD mode. In operating mode both clocks are running, 3.58 MHz and 32 kHz, while FSK as well as CAS are disabled. The 3.58 MHz clock is disabled in PD mode. In this mode only the POL/LOWBAT-comparators and the 32 kHz oscillator are active. The internal 'power down' is SW-controlled.

## Application Note AN98071

### 4. APPLICATION CONSIDERATIONS

For receiving CAS, FSK and POLs signals special hardware and control (software) are necessary while recognizing the difference between polarity inversion and ringing needs special control. In all these cases also the connection with a micro-computer and the supply considerations e.g mains, batteries and/or telephone line supply are important. This chapter gives considerations on these hardware and control (software).

### 4.1 CAS receiving

The Bellcore's CAS (CPE Alerting System) signals are only received in off-hook mode, if the CAS detection is enabled. The PCD3316 will generate an interrupt when a correct dual tone (2130 and 2750 Hz) is detected. After receiving a proper CAS signal the PCD3316 will be switched to FSK mode and waits for CIDCW messages.

#### Hardware considerations:

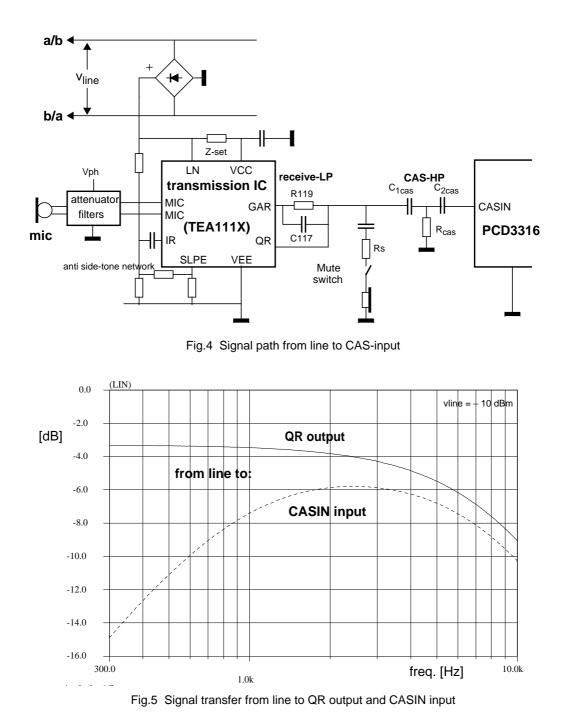

CAS tones with frequencies of 2130 Hz and 2750 Hz have to be detected in off-hook mode by the PCD3316 at signal levels down to –32 dBm on the line (Bellcore spec). To reduce the influence from near end speech, the CASIN input of the PCD3316 is coupled to the receive output (QR) of the transmission IC, taking advance of the side tone suppression of the transmission circuitry. Furthermore, a high pass filter in the CAS signal transfer (CAS-HP) reduces also the influence of speech.

The input sensitivity of the PCD3316 is –37.8 dBm minimum. So, the CAS tones (at 2130 Hz and 2750 Hz) can be attenuated from line to CASIN input, taking into account the:

- required gain of the receiver stage of the transmission IC which depends on the sensitivity of the earpiece and the loudness requirements of the set

- influence of the CAS-HP filter at the CAS tone frequencies

- influence of the low pass filter of the receiver stage (receive-LP) of the transmission IC depending on the loudness requirements of the set

The signal path of the CAS tones from line to CASIN input of the PCD3316 is shown in Fig.4. The components from receiver output of the transmission IC corresponds with the components of the application of chapter 6.1. The CAS signal from the line is attenuated by the anti side-tone network, amplified by the receiver stage of the transmission IC, filtered by the 'receive-LP' filter and the 'CAS-HP' filter before it is offered to the CASIN input. The resistor in series with the earpiece can be necessary to attenuate the signal to the earpiece while a larger gain is required for the CAS tones.

The cut-off frequency  $f_{-LP}$  of the 'receive-LP' filter is determined by C117 and R119//R<sub>int</sub>; R<sub>int</sub> is an internal resistance of the transmission IC. The cut-off frequency  $f_{-HP}$  of the 'CAS-HP' filter is determined by  $C_{1cas}$  and  $R_{cas}$ //Zi<sub>CAS</sub> with Zi<sub>CAS</sub> is the input impedance of the CASIN input. Capacitor  $C_{2cas}$  is a couple device determined by:  $C_{2cas} \cdot Zi_{CAS} >> C_{1cas} \cdot R_{cas}$ .

The application of chapter 6.1 (Bellcore approved) is taken as an example.

- **Receive gain**: The overall gain from line to earpiece is -10 dB due to the application of a sensitive earpiece. This -10 dB attenuation is too much for the CAS tones. The lowest signal levels at the line of -32 dBm can not be detected by the PCD3316 because they are below the -40 dBm threshold. In this case the receive gain is enlarged for the CAS tones and reduced for the earpiece by the series resistor Rs. The gain from line to CASIN input is adjusted to -4 dB (by means of R119 =  $330 \text{ k}\Omega$ ) while the gain from line to earpiece is -10 dB due to Rs =  $100 \Omega$  and the internal resistance of the Mute-switch. The applied earpiece has an impedance of  $150 \Omega$ .

- **CAS tone transfer**: Due to the effect of the 'receive-LP' and the 'CAS-HP' filters at the CAS tone frequencies on the adjusted gain, the resulting attenuation of the CAS tones is about –6 dB (instead of the adjusted –4 dB) as shown in Fig.5. The cut-off frequency is chosen at  $f_{-HP} = 800$  Hz with  $C_{1cas} = 1.8$  nF and  $R_{cas} = 120$  k $\Omega$  while  $Zi_{CAS} = 1.4$  M $\Omega$  typical.

## Application Note AN98071

Cut-off frequency  $f_{-LP}$  is set at 7.5 kHz with C117 = 270 pF, R119 = 330 k $\Omega$  and Rint = 100 k $\Omega$  as a result of acoustical tests.

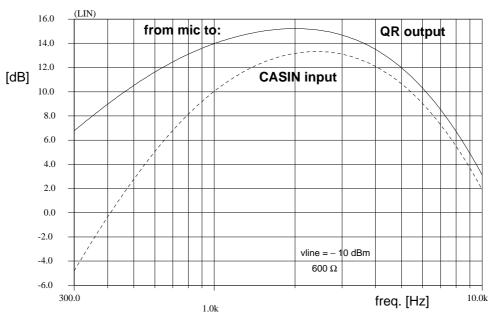

**Near end speech**: Own speech can influence the detection of CAS tones because the levels of speech at the line can be more than the lowest CAS tone levels. The anti side-tone network of the transmission IC reduces the transfer of own speech from microphone to earpiece, and CASIN input in this case. The reduction depends on the line termination and the definition of the anti side-tone network; consult the 'side tone stories' in [3].

## **Application Note** AN98071

The transfer from the microphone to the CASIN input is shown in Fig.6 measured at a line termination of 600  $\Omega$ and an anti side-tone network defined for cables with mean length of 5 km and 0.5 mm diameter. The side tone reduction, in this worst case condition, is about 8 dB.

Fig.6 Signal transfer from microphone to QR output and CASIN input

#### SW / Control considerations:

Direct after off-hook the micro-computer has to put the PCD3316 in CAS receive mode. Therefore, in the mode registers of the PCD3316 the CAS bit has to be set to logic "1", the FSK bit has to be set to logic "0" and the XTAL bit has to be set to logic "1" via the I<sup>2</sup>C-bus. TABLE 3 shows the final contents of the PCD3316 mode registers at CAS receive mode.

|                                                 | TABLE 3 PCD3316 Mode register contents at CAS receive mode |                |                |                     |            |                  |                  |  |  |  |

|-------------------------------------------------|------------------------------------------------------------|----------------|----------------|---------------------|------------|------------------|------------------|--|--|--|

| BIT 7                                           | BIT 6                                                      | BIT 5          | BIT 4          | BIT 3               | BIT 2      | BIT 1            | BIT 0            |  |  |  |

| D7                                              | D6                                                         | D5             | D4             | D3                  | D2         | D1               | D0               |  |  |  |

| Mode register 1 CIDMD1; address 04H; read/write |                                                            |                |                |                     |            |                  |                  |  |  |  |

| FSK<br>"0"                                      | FSK BOM-mask<br>"0"                                        | CAS<br>"1"     | POL<br>"0"     | INT Polarity<br>"1" | RES<br>"0" | RES<br>"0"       | RES<br>"0"       |  |  |  |

| Mode regist                                     | Mode register 2 CIDMD2; address 05H; read/write            |                |                |                     |            |                  |                  |  |  |  |

| XTAL<br>"1"                                     | TB<br>"0"                                                  | SEC/MIN<br>"0" | INT-SUP<br>"0" | RES<br>"0"          | RES<br>"0" | VERSION 1<br>"0" | VERSION 0<br>"0" |  |  |  |

| TABLE 3 | PCD3316 | Mode register | contents at | CAS receive mode |

|---------|---------|---------------|-------------|------------------|

| -       |         |               |             |                  |

The interrupt polarity needed depends on the hardware/ software used, we use the active high posibility.

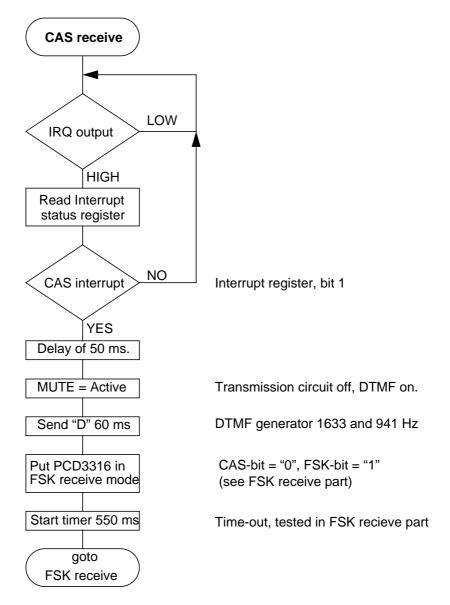

If a CAS tone is received by the PCD3316, it generates an interrupt request on the IRQ ouput pin, the microcomputer reads the internal registers of the PCD3316 and takes the necessary actions to make FSK receiving after this possible. The complete CAS receive control flow is given in Fig.7.

## Application Note AN98071

After receiving a CAS tone a 550 ms timeout is necessary because it is not allowed to mute the transmission part for more than 600 ms. If the first FSK-byte is not received before this time-out expires, the power down mode of the PCD3316 is entered.

### 4.2 FSK receiving

An FSK transmission (as specified by BT and Bellcore) consist of a channel seizure (on-hook) which is transmitted first (sequences of 1010....), followed by a block of marks (all 1's) finalised by the data. These mark bits are detected by the PCD3316 which sets the FSK-BOM indication bit (Status register, bit 4). This bit is reset when the FSK receiver is disabled (see Fig.8). A logic '0' is presented by a signal of 2200 Hz and a logic '1' by 1200 Hz.

## Application Note AN98071

Fig.8 FSK transmission specification (on-hook)

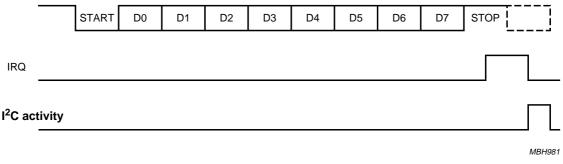

If the FSK BOM-mask bit is set (mode register 1, bit 6), the FSK receiver will wait till this FSK-BOM indication bit is set (reset after a "0" and less then eleven "1"), and will then generate an interrupt after it has received a complete data word. An FSK data word consists of one start bit (space), followed by eight data bits and several stop bits (mark). Interrupt will not be generated during the channel seizure and during the blocks of marks (see Fig.9) when the FSK BOM-mask is set.

Fig.9 IRQ generation after reading a valid data byte

When this FSK BOM-mask bit is not set (mode register 1, bit 6), the FSK receiver will not wait with the generation of interrupts until a Begin of Mark (BOM) has been detected but will handle the channel seizure as normal data. The mark bits will still not generate interrupts, because there are no start bits.

This FSK data is available in the FSK data register and can be read by the  $\mu$ C via the I<sup>2</sup>C-bus.

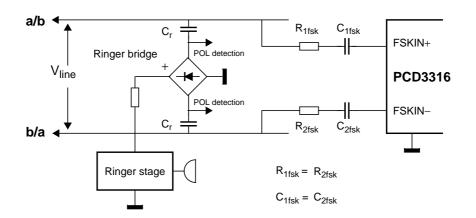

#### Hardware considerations:

The FSK inputs of the PCD3316 have to be connected symmetrically with the line terminals without attenuation to detect FSK signals down to –40 dBm. Series components are required for DC blocking and high voltage protection by means of the components  $C_{xfsk}$  ( $C_{1fsk}$  and  $C_{2fsk}$ ) and  $R_{xfsk}$  ( $R_{1fsk}$  and  $R_{2fsk}$ ) as shown in Fig.10 as well as in the application of Fig.31.

$R_{xfsk}$  calculation: 2 x  $R_{xfsk}$  <<  $Zi_{FSK}$  (1.4 M $\Omega$  typical) to prevent signal loss from the line to the inputs.  $R_{xfsk}$  have to reduce also the currents into the FSK pins below the specified 10 mA-max. at maximum line signals. A value of 2 x 100 k $\Omega$  is chosen as shown in Fig.31.

The maximum input current into the internal protection diodes, is limited to 1.0 mA-peak at 200 V-peak between the line terminals.

## Application Note AN98071

$C_{xfsk}$  calculation:  $C_{xfsk}/2 > 1/(2 \cdot \pi \cdot f \cdot R_t)$  (F) to prevent signal loss;

with f > 1100 Hz and  $R_t = 2$ .  $R_{xfsk} + Zi_{FSK} = 1.6 M\Omega$  the value of  $C_{xfsk}$  has to be more than 180 pF. Chosen is  $C_{xfsk} = 1$  nF. The minimum voltage for  $C_{xfsk} = 200$  V-peak.

Fig.10 Signal path of FSK signals from line to FSK-inputs

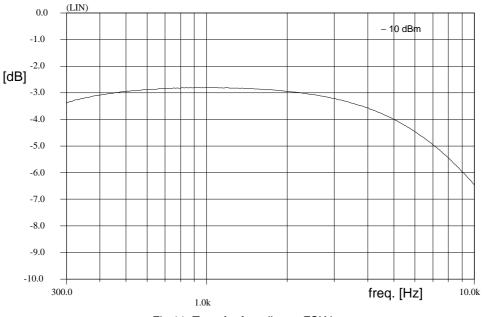

The signal loss from line to FSK inputs at the FSK frequencies measures about 2.8 dB according Fig.11.

#### SW / Control considerations:

After CAS, ringer burst, or polarity change the PCD3316 has to be put in FSK receiving mode. Therefore in the mode registers of the PCD3316 the FSK bit has to be set to logic "1", the CAS bit has to be set to logic "0", because we only want interrupts at real FSK-data receiving the FSK BOM-mask bit has to be set to logic "1" and the XTAL bit has to be set to logic "1". TABLE 4 shows the final contents of the PCD3316 mode registers at FSK receive mode.

|                                                 | TABLE 4 TODOSTO MODE register contents at TOK receive mode |                |                |                     |            |                  |                  |  |  |  |

|-------------------------------------------------|------------------------------------------------------------|----------------|----------------|---------------------|------------|------------------|------------------|--|--|--|

| BIT 7                                           | BIT 6                                                      | BIT 5          | BIT 4          | BIT 3               | BIT 2      | BIT 1            | BIT 0            |  |  |  |

| D7                                              | D6                                                         | D5             | D4             | D3                  | D2         | D1               | D0               |  |  |  |

| Mode register 1 CIDMD1; address 04H; read/write |                                                            |                |                |                     |            |                  |                  |  |  |  |

| FSK<br>"1"                                      | FSK BOM-mask<br>"1"                                        | CAS<br>"0"     | POL<br>"0"     | INT Polarity<br>"1" | RES<br>"0" | RES<br>"0"       | RES<br>"0"       |  |  |  |

| Mode register 2 CIDMD2; address 05H; read/write |                                                            |                |                |                     |            |                  |                  |  |  |  |

| XTAL<br>"1"                                     | TB<br>"0"                                                  | SEC/MIN<br>"0" | INT-SUP<br>"0" | RES<br>"0"          | RES<br>"0" | VERSION 1<br>"0" | VERSION 0<br>"0" |  |  |  |

#### TABLE 4 PCD3316 Mode register contents at FSK receive mode

Because here only the FSK part is switched-on it is not necessary to activate the interrupt suppression bit (Mode register 2, bit 4 = "0"), however if the minute/seconde interrupt is on (for clock or timer purposes) it is necessary to activate (Mode register 2, bit 4 = "1"), so that during FSK reception these interrups are suppressed automatically.

In CID application it is necessary to make/keep the POL interrupt active during FSK receive. It must be possible to receive outside the FSK-bytes also the next ringer signal.

The FSK receive part needs a lot of process power and may not to long be activated, therefore it is protected by a time-out. During receiving FSK-byte this timer is loaded by the FSK receive part itself, at first activation after CAS, ringer burst, or polarity change these program part will load the timer.

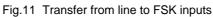

If a FSK byte is received by the PCD3316, it generates an interrupt request on the IRQ ouput pin, the microcomputer reads the internal registers of the PCD3316 and takes the necessary actions to make FSK receiving after this possible. The complete FSK receive control flow is given in Fig.12.

## Application Note AN98071

#### Fig.12 FSK receive control procedure

In off-hook mode it is possible that mark bits are sent after the last received FSK-byte. Therefore it is necessary that the low level bit of the PCD3316 is polled before this procedure is ended. Then also the mute can be deactivated. If all FSK-bytes are received the caller id information can be put on a display.

To be sure that no problem occurs during FSK receive the status register of the PCD3316 has to be read too. Two error bits are available to indicate synchronization problems. FSK-OVR error bit (status register, bit 3) indicates that a previous byte is lost due to an overrun, FSK-FRM error bit (status register, bit 2) indicates an incorrect start- or stop-bit.

## Application Note AN98071

The on-chip level detector can be used to detect a carrier loss during FSK transmission (interrupt register, bit 4). The data can be rejected when the signal level is below the reference level, this to avoid that noise is interpreted as data.

### 4.3 Ring or Polarity Change Detection by POL0 and POL1

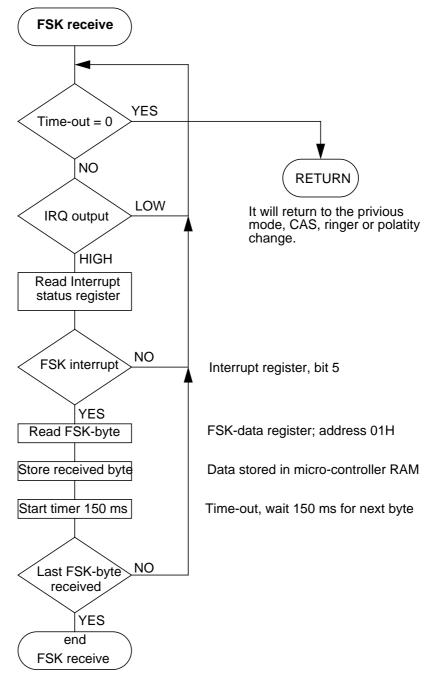

For ring and polarity change detection two comparators are available in the PCD3316. The reference level of the comparators is set internally by the reference voltage generator. The voltage levels on the two polarity comparators inputs, POL0 and POL1, are compared with the reference voltage  $V_{ref}$ . If input POL0 is lower than  $V_{ref}$  or input POL1 is higher than  $V_{ref}$ , bits POL0 and POL1 of the status register (status register, bit 7 and 6) are high respectively and these bits become low if POL0 is higher than  $V_{ref}$  and POL1 is lower than  $V_{ref}$ . Every time the POL0 status bit changes from logic 1 to logic 0, a POL0 interrupt is generated. Every time the POL1 status bit changes from logic 1, a POL1 interrupt is generated.

Fig.13 shows the above explained POL0 and POL1 handling when a sine-wave is applied on the telephone lines.

Fig.13 POL0 and POL1 handling with a sinewave as input signal.

## Application Note AN98071

The period time of a POL1-POL0-POL1 sequence is available in the ringer period register in multiples of 1/2048 s. At power-up and in all other cases that a POL1 is available, the contents of the ringer period register is 255.

Polarity Change is that only POL1 or POL0 is generated while the contents of the ringer period register is 255.

**Ringer** is that there is a sequence of POL1-POL0-POL1-etc, while at the second POL1 after a POL0 the contents of the ringer period register is the time of the previous POL1-POL0-POL1 sequence.

Only the 32 kHz clock is needed for the ringer or polarity change detection.

#### Hardware considerations:

The ringer frequency is converted into a binary number when a sequence of POL0-POL1-POL0 interrupts is generated; see before in this chapter or in [1]. To generate the POL0-POL1-POL0 interrupt sequence the input signals of POL0 and POL1 have to exceed Vref = 1.25V and must have a phase shift of a half-period between each other, as shown in Fig.13.

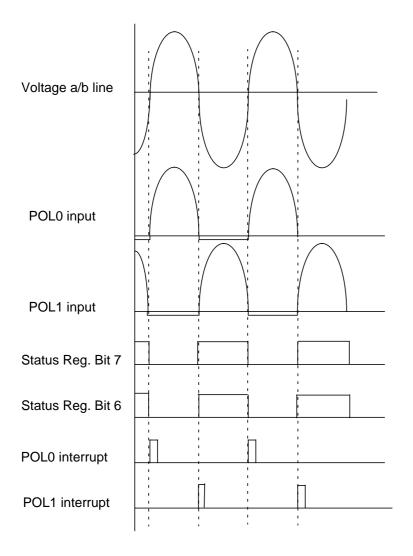

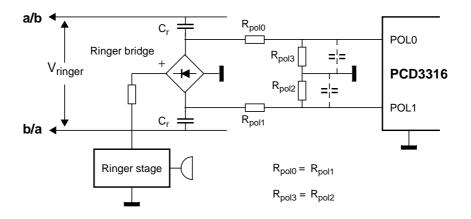

The POL inputs of the PCD3316 have to be connected with the line via attenuators by using the ringer capacitors as shown in Fig.14.

To detect the ringer signals or polarity changes the input voltage at POL0 and POL1 has to exceed  $V_{ref} = 1.25 \text{ V}$  (± 125 mV). The minimum ringer voltage at the line, to be detected, can be calculated as follows by using the attenuator components Rpol1 and Rpol2 of POL1 input as shown in Fig.30:

$\begin{aligned} v_{\text{ringer-min}} &= V_{\text{ref}} \cdot (R_{\text{pol2}} / / Zi_{\text{pol}} + R_{\text{pol1}}) / \left[ \sqrt{2} \cdot (R_{\text{pol2}} / / Zi_{\text{pol}}) \right] \quad (\text{Vrms}) \\ & \text{with } V_{\text{ref}} = 1.25 \text{ V}, \text{ } R_{\text{pol1}} = 820 \text{ } \text{k}\Omega, \text{ } R_{\text{pol2}} = 100 \text{ } \text{k}\Omega, \text{ } Zi_{\text{pol}} > 1.25 \text{ } \text{M}\Omega \text{ the calculated value of } \\ v_{\text{ringer-min}} = 8.7 \text{ Vrms}. \end{aligned}$

This is a theoretical value in case the line is not loaded with the ringer stage of the set. The real minimum ringer voltage which is detected by the PCD3316, as applied in the application of chapter 6.1, is about 13 Vrms due to the voltage drops across the 2.2  $\mu$ F ringer capacitors C<sub>r</sub>.

Note that the application of chapter 6.1 is provided with the UBA1702 which has an internal ringer threshold. This ringer threshold, which can be adjusted, determines the minimum ringer voltage at which the ringer capsule is activated. Without UBA1702 the minimum ringer voltage has to be adjusted by the ratio of the R<sub>polx</sub> resistors.

Fig.14 Signal path of ringer signal from line to POL-inputs

## Application Note AN98071

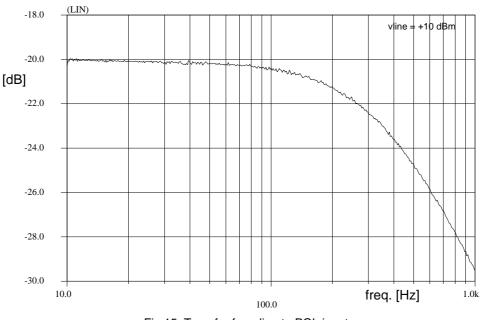

The signal transfer from line to POL-inputs is shown in Fig.15 with the POL attenuation components as shown in Fig.30. The low pass effect in the transfer is caused by the two 4.7 nF capacitors across the POL inputs.

Fig.15 Transfer from line to POL inputs

#### SW / Control considerations:

Immediately after reset, the micro-computer has to put the PCD3316 in POL detection mode. Therefore the POL bit has to be set to logic "1". The CAS and FSK functions are normal off to save power, but it is allowed to have these functions active too (CAS or FSK bit also "1"). TABLE 5 shows the final contents of the PCD3316 mode registers at POL detection mode.

|                                                 | TABLE 5 FCD3316 Mode register contents at FOL detection mode |                |                |                     |            |                  |                  |  |  |  |

|-------------------------------------------------|--------------------------------------------------------------|----------------|----------------|---------------------|------------|------------------|------------------|--|--|--|

| BIT 7                                           | BIT 6                                                        | BIT 5          | BIT 4          | BIT 3               | BIT 2      | BIT 1            | BIT 0            |  |  |  |

| D7                                              | D6                                                           | D5             | D4             | D3                  | D2         | D1               | D0               |  |  |  |

| Mode register 1 CIDMD1; address 04H; read/write |                                                              |                |                |                     |            |                  |                  |  |  |  |

| FSK<br>"0"                                      | FSK BOM-mask<br>"0"                                          | CAS<br>"0"     | POL<br>"1"     | INT Polarity<br>"1" | RES<br>"0" | RES<br>"0"       | RES<br>"0"       |  |  |  |

| Mode regist                                     | Mode register 2 CIDMD2; address 05H; read/write              |                |                |                     |            |                  |                  |  |  |  |

| XTAL<br>"0"                                     | TB<br>"1"                                                    | SEC/MIN<br>"0" | INT-SUP<br>"0" | RES<br>"0"          | RES<br>"0" | VERSION 1<br>"0" | VERSION 0<br>"0" |  |  |  |

| TABLE 5 | PCD3316 | Mode register | contents at PO | detection mode |

|---------|---------|---------------|----------------|----------------|

|         |         |               |                |                |

Distinction between the detection of a polarity change or ringer detect has to be made by software. The PCD3316 only generates POL0 and POL1 interrupts and measures the time between two POL1 interrupts.

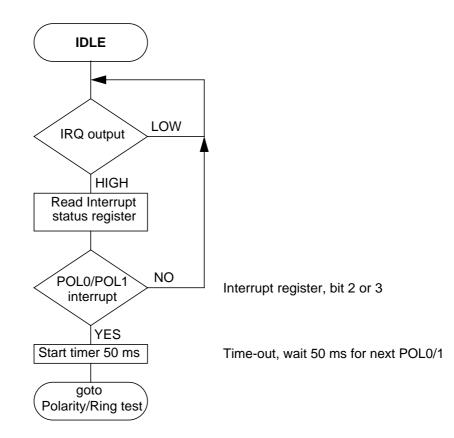

The explanation of this control has been split-up into three parts, first there is tested if there was a POL0/POL1 activity on the line, second selection is made between polarity change and ringer and final the ringer frequency and activation is controlled. The first control flow, detect the first POL0/POL1 activity is given in Fig.16.

## Application Note AN98071

Fig.16 POL0/POL1 detection procedure

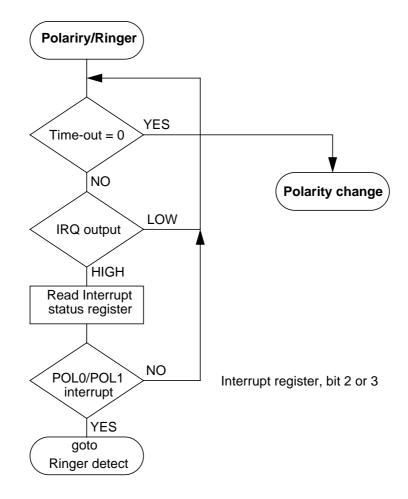

After preforming the above described test we know that there is activity on the telephone lines. However if it is polarity change or ringer we need the second control procedure. To decide between the two posibilities the timer is loaded with the lowest possible time between two POL0/POL1 interrupts if its is a ringer signal (50 ms means a ringer frequency of 10Hz or higher). The second control flow, selection between polarity change and possible ringer frequency, is given in Fig.17.

## Application Note AN98071

Fig.17 Polarity change and ringer frequency detection procedure.

When the time-out expires (no POL0 or POL1 interrupt detected) there was only a polarity change on the telephone line. In the BT application this will be used as start of the Caller ID procedure. In other applications this will be seen as a disturbance and will be switched back to the IDLE part.

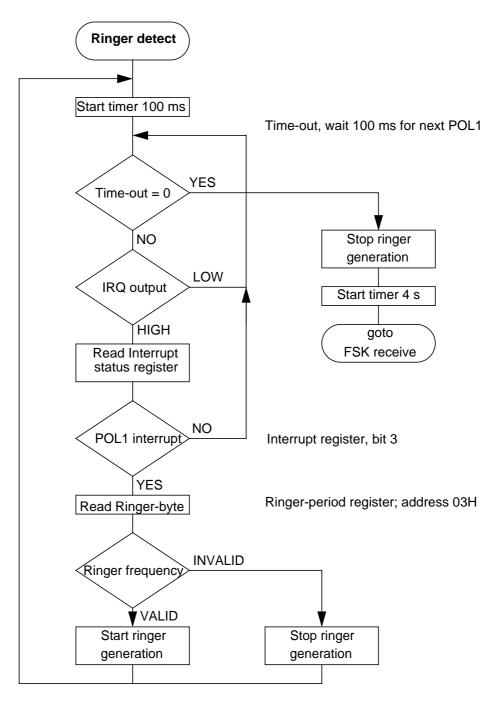

Still we are not sure that there is a valid ringer signal on the telephone line. Herefore the ringer frequency has to be measured and validated. The final POL0/POL1 control flow, the detection if there is a valid ringer frequency, is given in Fig.18.

## Application Note AN98071

Fig.18 Ringer frequency detection procedure.

In the ringer detection part only the POL1 interrupt has to be tested, because only after a POL1 interrupt the ringer period register is reloaded with a new value.

If no new POL1 interrupts are generated, because the ringer has stopped, the implemented timer will automatically stop the ringer generation and prepare it for FSK receiving. The 4s time-out will be tested in the FSK receive part.

#### 4.4 Power Down state

The PCD3316 can be forced in a Power-down state by switching off the 3.58 MHz system clock and the A/D converter. This is done by setting mode register 2, bit 7 to logic 0. To guarantee correct operation, otherwise the PCD3316 stays in the selected function, the following order of actions must be performed:

- 1. Switch-off CAS and FSK detection (if turned on).

- 2. Read the interrupt register, thus cleaning pending interrupts generated by the CAS and FSK detector.

- 3. Switch-off the 3.58 MHz oscillator by reset bit 7 of mode register 2.

### 4.5 Low Battery Detect

The PCD3316 has an extra comparator to guard the battery voltage. If the voltage on the LOWBAT input is less than the reference voltage  $V_{ref}$ , the LOW\_BAT indication (status register, bit 5) is high, otherwise it is low.

#### Hardware considerations:

A tap of the battery voltage has to be connected with the LOWBAT input to monitor the minimum working voltage of the PCD3316 and PCD3755F or other type of  $\mu$ C. Detection level of the PCD3316 is V<sub>ref</sub> = 1.25 V ± 125 mV. For a VDD-minimum = 2.5 V, detection has to be done at VBBbat = 2.5 + 0.125 + V<sub>D123</sub> + (VBB – VDD) following the supply structure of the application of chapter 6.1.

With  $V_{D123} = 0.6 \text{ V}$  and (VBB - VDD) = 100 mV (2.5 V < VBB < 3.0) the minimum level of VBBbat = 3.32 V.

In this case with 3 x 1.5 V batteries, an attenuation of a factor 0.414, from VBBbat to LOWBAT, has to be made. At  $R_{low1} = 1 M\Omega$  the value of  $R_{low2}$  has to be 1.5 M $\Omega$ . The input current into LOWBAT, which is < 1 nA, can be neglected.

#### **Control considerations:**

Because the setting of the LOW-BAT bit (status register, bit 5) generates no interrupt on the IRQ pin, this bit should be polled. A practical solution is to read the status register value when a minute or second interrupt is generated, and put the low battery indication on the display.

### 4.6 Real-Time-Clock or Call-Timer signal

The PCD3316 doesn't have a real-time-clock or call-timer hardware on-board, but with the 32 kHz oscillator the time base is able to generate either a 1 second or a 1 minute interrupt signal which can be used by the micro-computer to make a real-time-clock or a call timer. After reading the interrupt the interrupt is reset.

#### Control considerations real-time-clock:

- 1. For real-time-clock you need the minute interrupt generation, therefore the TB bit has to be set to logic "1" (mode registers 2, bit 6) and the SEC/MIN bit has to be set to logic "0" (mode register 2, bit 5).

- 2. Every minute the PCD3316 generates an interrupt request via pin IRQ of the PCD3316 to the microcomputer.

- 3. The micro-computer will read the "interrupt status register" of the PCD3316 and tests if the MIN interrupt (interrupt register, bit 7) is set, if yes the micro-computer will continue with point 4, else it waits for next interrupt (point 2).

- 4. The micro-computer will update the real-time-clock, put it on the display and wait for next interrupt.

Because normal Caller ID messages include the present time, this can be used to synchronise this real-timeclock.

#### Control considerations call-timer:

- 1. For call-timer you need the second interrupt generation, therefore the TB bit has to be set to logic "1" (mode registers 2, bit 6) and the SEC/MIN bit has to be set to logic "1" (mode register 2, bit 5).

- 2. Every second the PCD3316 generates an interrupt request via pin IRQ of the PCD3316 to the microcomputer.

- 3. The micro-computer will read the "interrupt status register" of the PCD3316 and tests if the SEC interrupt (interrupt register, bit 6) is set, if yes the micro-computer will continue with point 4, else it waits for next interrupt (point 2).

- 4. The micro-computer will update the call-timer, put it on the display and wait for next interrupt.

Of course every time you start a new telephone call this timer has to be set to zero.

### 5. APPLICATION PROPOSALS

This chapter describes application proposals of the PCD3316 CID / CIDCW receiver IC elucidated with block diagrams and timing diagrams as far as useful. Proposed are a 'Basic set', an 'Adjunct box' and application adaptions to meet the British Telecom (BT) and France Telecom (FT) requirements. Only the most important parts of the applications are shown in the block diagrams while the descriptions are kept briefly. The PCD3316 is described in this report and specified in [1]. Details of the other ICs: transmission IC TEA1112, microcontroller PCD3755F, ringer/interrupter UBA1702, handsfree IC TEA1093 can be found in [3] while applications are shown in [4].

The applications in this chapter have to be seen as proposals only, which are not built and not tested.

### 5.1 Basic telephone set with CID / CIDCW

This basic application with CID / CIDCW functions is meant for 'Bellcore' oriented countries. The blockdiagram is shown in Fig.19 using the TEA1112, PCD3316, microcontroller, display and discrete ringer. Realized and tested applications with the PCD3316 are described in chapter 6. The microcontroller must be a type with DTMF generator on chip (for instance the PCD3755F).

#### Transmission / dialling

The TEA1112 takes care of the interface between the microphone and ear capsule of the handset and the line while during DTMF dialling the tones from the  $\mu$ C are transmitted to the line. The transmission functions are line powered. The discrete 'hook-switch', shown in Fig.19 as a simple switch, is controlled by the  $\mu$ C via DP/FL to perform line interruptions for pulse dialling and flash. After lifting the 'cradle switch' the hook-switch is activated while the  $\mu$ C is set in the transmission mode via CSI and CE. The dialling function are available while the display is informed via the I<sup>2</sup>C - bus.

#### Ringing

The ringer circuitry, built up with discrete components, contains ringer supply and volume control. The PCD3316 generates an IRQ signal when a ringer voltage is detected on the POL inputs and activates the microcontroller by means of CE. The microcontroller generates a ringer tone when the 'binary representation' of the ringer frequency from the PCD3316 is detected as a valid frequency. The ringer stage drives the PXE ringer capsule. Volume control (if available in the ringer stage) is controlled by the microcontroller via the keypad.

#### PCD3316 - CID / CIDCW

The PCD3316 communicates with the microcontroller by means of the  $I^2C$  - bus. Timing of the CAS and FSK functions is derived from the 3.58 MHz oscillator of the microcontroller. The 32 kHz oscillator activates the LOWBAT, Ring and Polarity detectors.

The CID / CIDCW signals from the line as ringing, polarity change and FSK signals are attenuated and band filtered before entering the device inputs of the PCD3316. The CAS signal is derived from the receiver output of the TEA1112 to separate the CAS signal from own speech by means of the anti side-tone network of the circuitry around the TEA1112.

The LOWBAT input of the PCD3316 detects too low battery voltages. During on-hook, the PCD3316 is in PD with the 32 kHz oscillator running while the microcontroller is in stop mode. Polarity changes or ringing signals from the line are detected by the PCD3316. The PCD3316 wakes-up the microcontroller (IRQ + CE) while the microcontroller activates, on his turn, the PCD3316 via the  $I^2C$  - bus to receive CAS and FSK signals.

#### VDD supply

The PCD3316, microcontroller and display are supplied by VDD. Battery support is necessary during off-hook because the VCC supply point is too weak to deliver enough current, at low line voltages, for the microcontroller and PCD3316 and display. At higher line voltages VCC could contribute.

## Application Note AN98071

During on-hook, current consumption is rather low due to the PD or stop mode of the PCD3316 respectively microcontroller which saves battery energy. The devices becomes operational when polarity changes or ringing signals from the line are detected resulting in an increase of the current consumption from VDD. If required the supply of the devices during ringing could be delivered by the ringer stage. Consult chapter 6.1.5 concerning supply structure.

Fig.19 Block diagram of basic telephone set with CID/CIDCW functions

## Application Note AN98071

#### **Optional functions**

Fig.19 shows also the TEA1093 and the UBA1702 to create a number of extra or optional functions.

Furthermore, the discrete ringer part and hook-switch of the basic set can be replaced by the UBA1702 while the UBA1702 offers also a stabilized VDD voltage of 3.3 V using the battery voltage or ringing voltage as input. See chapter 6.1.

The TEA1093 can be applied to design a handsfree telephone set. This device contains a loudspeaker amplifier supplied from the line. Application examples of the TEA1093 can be found in [4].

### 5.2 Caller ID / Call Waiting Adjunct box

A standalone Adjunct Box with the PCD3316 is proposed in this chapter. It has to be connected between the telephone line and telephone set by means of two plugs as indicated in Fig.20. The box contains circuitry to receive and to handle the CID / CIDCW data. A 'Line Current Sensor' and a 'Line Interrupter' are placed in series with the external telephone set to detect the line current flowing to the telephone set respectively to switch-off the telephone set from the line. The Line Interrupter has to be 'normally closed' when it is not activated; see the Note at the end of this chapter about the details.

Fig.20 Block diagram of an Adjunct box

The adjunct box has its own line voltage stabilizer and line termination to adapt the box to the line when the external telephone set is switched-off from the line in off-hook mode. The transmit stage of the adjunct box is used to send a DTMF acknowledge signal to the line. FSK, POL and CAS signals from the line are offered to the

## Application Note AN98071

PCD3316 via decoupling capacitors, attenuators and filters if required. The PCD3316 has its 32 kHz oscillator to detect polarity and ringing signals from the line in power down mode while the 3.58 MHz timing signal is delivered by the microcontroller. Information between PCD3316, microcontroller and display is provided by the  $I^2C$  circuitry of the devices and the  $I^2C$  - bus. The keypad could be applied to set the pre-conditions of the display, to handle the stored numbers and names and for Call Back facilities. The adjunct box is battery supplied as indicated in Fig.20. Mains supply via a transformer can be an option.

The following states are described as follows: