Universidade do Minho Escola de Engenharia

Fernando Filipe Antunes Gomes Silva Reis

IP Camera on FPGA with a Web Server

Universidade do Minho Escola de Engenharia

Fernando Filipe Antunes Gomes Silva Reis

IP Camera on FPGA with a Web Server

Dissertação de Mestrado Ciclo de Estudos Integrados Conducentes ao Grau de Mestre em Engenharia Electrónica Industrial e Computadores

Trabalho efectuado sob a orientação do Professor Doutor João Monteiro

# **Abstract**

As advances on fields such as embedded systems and networks emerge, new products with increasing features can be created. An example is an IP camera. An IP camera provides a good solution for remote real-time monitoring, allowing users to view and manage video and images with this new kind of networked devices.

This thesis proposes a network IP camera solution based on the Altera Nios II embedded soft-core processor. The implementation consists on custom hardware and software – so that the specific software runs on the developed hardware.

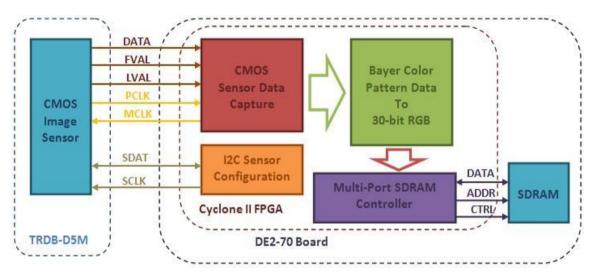

The hardware design specifies all the modules implemented on a FPGA. Images captured by CMOS sensor are converted into RGB format and stored in the SDRAM. The NIOS II soft-core processor reads each frame, does the compression, and handles network connections.

The software includes an operating system, µClinux, and a Web server running on top of it. Live images are compressed in Motion JPEG format by software, and the IP camera provides event management functionalities using additional implemented features.

From the user point of view, the web user interface page allows live view from the camera and also system configuration, being compatible with the most popular browsers. It is available in Portuguese, English and German, with the possibility to add more languages.

# Resumo

Com os avanços nas áreas de projecto e implementação de sistemas embebidos, bem como em tecnologias de rede, novos produtos com muitas funcionalidades podem ser criados. Um exemplo são as câmaras IP. Uma câmara IP torna-se uma boa solução para a monitorização em tempo real, permitindo aos utilizadores visualizarem e gerirem o vídeo e as imagens remotamente com um dispositivo ligado a uma rede.

Este projecto propõe uma solução de uma câmara IP ligada à rede baseada no microprocessador embebido para FPGAs da Altera, Nios II. A implementação consiste em hardware e software personalizado – em que o software corre sobre o hardware desenvolvido.

O projecto de hardware especifica todos os módulos implementados no FPGA. As imagens capturadas pelo sensor CMOS são convertidas para o formato RGB e guardadas na SDRAM. O processador NIOS II lê cada frame, faz a compressão e lida com as comunicações de rede.

O projecto de software inclui um sistema operativo, µClinux, e a implementação de um servidor Web a correr sobre o sistema operativo. Imagens em tempo real são comprimidas no formato de compressão Motion JPEG por software e a câmara IP fornece funcionalidades de gestão de eventos utilizando recursos adicionais implementados.

Do ponto de vista do utilizador, a página Web de interface com o utilizador permite a visualização de imagens em tempo real e também a configuração do sistema, sendo compatível com os principais navegadores de internet. Estão disponíveis os idiomas Português, Inglês e Alemão, mas com a possibilidade de adicionar mais idiomas.

# **Contents**

| 1. | INTR     | ODUCTION                                  | . 1 |

|----|----------|-------------------------------------------|-----|

|    | 1.1. M   | OTIVATION                                 | . 1 |

|    | 1.2. Su  | RVEILLANCE SYSTEM                         | . 2 |

|    | 1.3. Ev  | ENT MANAGEMENT AND INTELLIGENT VIDEO      | . 2 |

|    | 1.4. G   | DALS                                      | . 3 |

|    | 1.4.1.   | Image Capture                             | . 3 |

|    | 1.4.2.   | Microprocessor Implementation             | . 3 |

|    | 1.4.3.   | Complete IP Camera System                 | . 4 |

|    | 1.5. TH  | ESIS OUTLINE                              | . 4 |

| 2. | SUR      | /EILLANCE SYSTEMS                         | . 7 |

|    | 2.1. ST. | ATE OF THE ART                            | . 7 |

|    | 2.1.1.   | Commercial Solutions                      | . 7 |

|    | 2.1.2.   | Research Projects                         | 11  |

|    | 2.2. IP  | Camera Design                             | 12  |

|    | 2.2.1.   | Image Sensor Technology                   | 12  |

|    | 2.2.2.   | Soft-core Processors                      | 13  |

|    | 2.2.3.   | Video Compression                         | 15  |

|    | 2.2.4.   | IP Network                                | 17  |

|    | 2.3. So  | FTWARE DESIGN                             | 20  |

|    | 2.3.1.   | Programming Languages                     | 20  |

|    | 2.3.2.   | Hardware Description Language (HDL)       | 20  |

|    | 2.3.3.   | High Level Software Programming Languages | 22  |

|    | 2.3.4.   | Embedded OS                               | 23  |

|    | 2.4. IP  | SURVEILLANCE OVERVIEW                     | 27  |

|    | 2.4.1.   | Video Management                          | 27  |

|    | 242      | Δnnlications                              | 28  |

| 3. | SYSTE              | M ANALYSES AND DESIGN                                 | 31 |

|----|--------------------|-------------------------------------------------------|----|

| 3  | 3.1. <b>S</b> YST  | TEM CONSTRAINS ANALYSIS                               | 31 |

|    | 3.1.1.             | FPGA constraints                                      | 31 |

|    | 3.1.2.             | Time constraint                                       | 32 |

|    | 3.1.3.             | Data constraint                                       | 32 |

| 3  | 3.2. FPG           | A DEVELOPMENT BOARD                                   | 33 |

|    | 3.2.1.             | Characteristics of the DE2-70 board                   | 33 |

|    | 3.2.2.             | Quartus II Design Software                            | 37 |

|    | 3.2.3.             | ModelSim-Altera                                       | 38 |

| 3  | 3.3. A SH          | ORT OVERVIEW OF THE IMPLEMENTED SYSTEM                | 38 |

| 4. | IMPLE              | MENTATION                                             | 41 |

| 4  | 4.1. CAN           | IERA HARDWARE MODULE                                  | 41 |

|    | 4.1.1.             | Technical specifications                              | 41 |

|    | 4.1.2.             | Image Capture                                         | 42 |

| 4  | 4.2. Nios          | S II IMPLEMENTATION                                   | 49 |

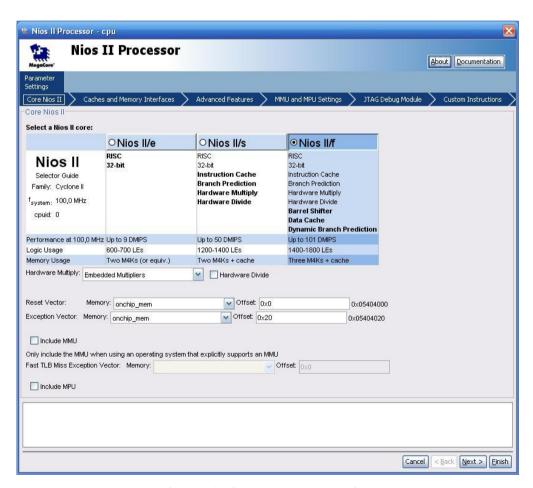

|    | 4.2.1.             | Nios II Processor Core                                | 51 |

|    | 4.2.2.             | UART Peripheral                                       | 52 |

|    | 4.2.3.             | Interval Timer Peripheral                             | 52 |

|    | 4.2.4.             | I/O Components                                        | 52 |

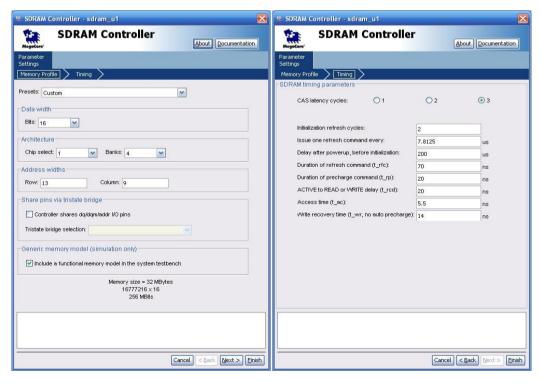

|    | 4.2.5.             | SDRAM Memory Controller                               | 53 |

|    | 4.2.6.             | LCD Module                                            | 54 |

|    | 4.2.7.             | Ethernet Interface                                    | 54 |

|    | 4.2.8.             | Serial Peripheral Interface (SD/MMC Module)           | 54 |

|    | 4.2.9.             | CMOS Slave Controller                                 | 55 |

| 4  | 4.3. μ <b>C</b> LI | NUX CONFIGURATION FOR NIOS II AND FPGA TARGET         | 59 |

|    | 4.3.1.             | μClinux Requirements                                  | 59 |

|    | 4.3.2.             | Compiling the μClinux Kernel                          | 59 |

|    | 4.3.3.             | μClinux Root Filesystem                               | 61 |

|    | 4.3.4.             | Cross-Compiling Programs for μClinux                  | 61 |

|    | 4.3.5.             | Customizing the Kernel and Applications               | 61 |

|    | 4.4. THE           | OVERALL ARCHITECTURE OF WEB-BASED SURVEILLANCE SYSTEM | 63 |

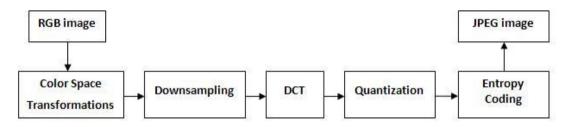

| 4   | 1.5. | IMAGE CAPTURE AND MOTION JPEG COMPRESSION | 67 |

|-----|------|-------------------------------------------|----|

| 5.  | T    | ESTING & EXPERIMENTS                      | 75 |

| 6.  | FI   | EATURES AND USER MANUAL                   | 83 |

| 6   | 5.1. | PRODUCT OVERVIEW                          | 83 |

| 6   | 5.2. | Install the Camera on a Network           | 83 |

| 6   | 5.3. | LANGUAGE SETTINGS                         | 83 |

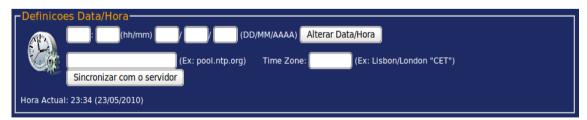

| 6   | 5.4. | DATE AND TIME SETTINGS                    | 84 |

| 6   | 5.5. | Network Settings                          | 85 |

| 6   | 5.6. | SECURITY PROPERTIES                       | 85 |

| 6   | 5.7. | IMAGE PROPERTIES                          | 86 |

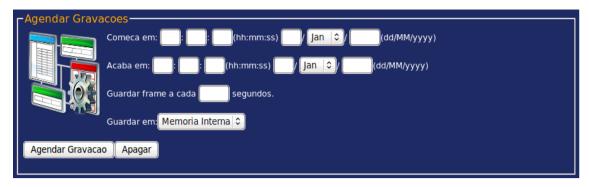

| 6   | 5.8. | SCHEDULE A RECORDING                      | 86 |

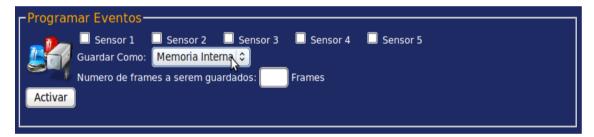

| 6   | 5.9. | SCHEDULE AN EVENT                         | 87 |

| 6   | 5.10 | . Specifications                          | 87 |

| 7.  | C    | ONCLUSION AND FUTURE WORK                 | 89 |

| 7   | 7.1. | Future Work                               | 90 |

| REI | FERE | NCES                                      | 91 |

# **List of Figures**

| FIGURE 1.1: PROJECT OVERVIEW                                                        | 1    |

|-------------------------------------------------------------------------------------|------|

| FIGURE 1.2: IMAGE CAPTURE BLOCK DIAGRAM                                             | 3    |

| FIGURE 1.3: MICROPROCESSOR IMPLEMENTATION.                                          | 4    |

| FIGURE 1.4: FINAL SYSTEM IMPLEMENTATION: THE CMOS CONTROLLER BLOCK MANAGES THE DATA | Д    |

| COMMUNICATION AND FRAME REQUESTS BETWEEN SDRAM 1 AND THE MICROPROCESSOR             | 4    |

| FIGURE 2.1: AXIS 2100 NETWORK CAMERA [AXNE10].                                      | 8    |

| FIGURE 2.2: UNC-9211 IP CAMERA [HITE10].                                            | 9    |

| FIGURE 2.3: VIVOTEK IP8161 IP CAMERA [5].                                           | 10   |

| FIGURE 2.4: NETCAM XL IP CAMERA [STNE10].                                           | 10   |

| FIGURE 2.5: IMAGE SENSORS: CCD (LEFT); CMOS (RIGHT) [Ax06]                          | 12   |

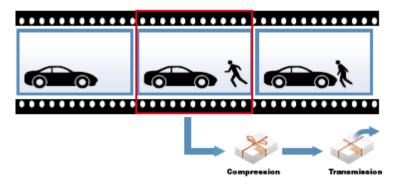

| FIGURE 2.6: MJPEG ENCODES EACH FRAME INDEPENDENTLY [VIHA10]                         | 15   |

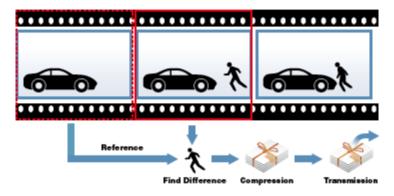

| FIGURE 2.7: MPEG-4 FINDS DIFFERENCES BETWEEN KEY FRAMES AND FOLLOWING FRAMES [VIHA1 | .0]. |

|                                                                                     | 16   |

| FIGURE 2.8: PROGRAMMING LANGUAGES USED TO DEVELOP EMBEDDED DEVICES [HAFU08]         | 24   |

| FIGURE 2.9: DIGITAL INPUT SURVEILLANCE DEVICES [VIHA10].                            | 28   |

| FIGURE 2.10: DIGITAL OUTPUT SURVEILLANCE DEVICES [VIHA10]                           | 28   |

| FIGURE 3.1: THE DE2-70 BOARD [ALDE09]                                               | 33   |

| Figure 3.2: Quartus II design flow [AlQu07].                                        | 37   |

| FIGURE 4.1: BLOCK DIAGRAM OF THE IMAGE CAPTURE BLOCK                                | 42   |

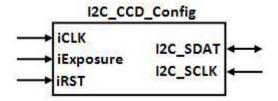

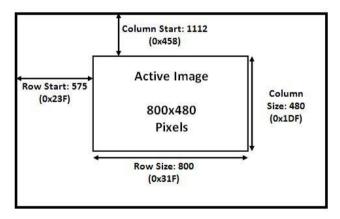

| FIGURE 4.2: I2C SENSOR CONFIGURATION BLOCK.                                         | 43   |

| FIGURE 4.3: ACTIVE IMAGE CAPTURED BY THE CMOS SENSOR.                               | 43   |

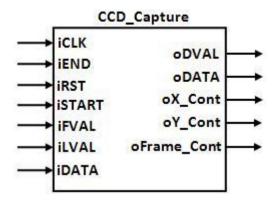

| FIGURE 4.4: CMOS SENSOR DATA CAPTURE BLOCK.                                         | 45   |

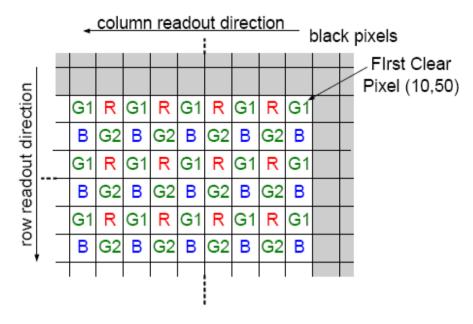

| FIGURE 4.5: PIXEL COLOR PATTERN DETAIL [TECM09]                                     | 46   |

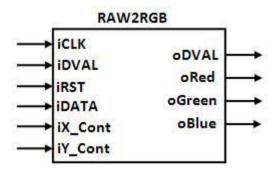

| FIGURE 4.6: RAW DATA TO RGB FORMAT BLOCK.                                           | 46   |

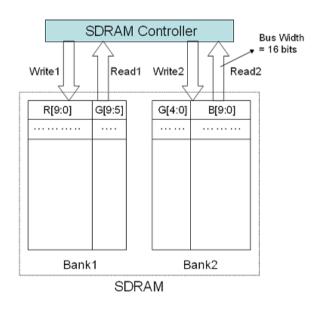

| FIGURE 4.7: SDRAM MEMORY BANKS [CNHO09].                                            | 47   |

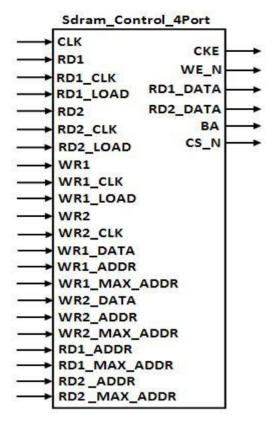

| FIGURE 4.8: SDRAM CONTROL BLOCK.                                                    | 48   |

| FIGURE 4.9: NIOS II PROCESSOR WITH PERIPHERALS.                                     | 50   |

| FIGURE 4.10: NIOS II PROCESSOR CORE SETTINGS.                                       | 51   |

| FIGURE 4.11: INTERVAL TIMER SETTINGS                                                | 52   |

| FIGURE 4.12: THE SDRAM CONTROLLER CONFIGURATIONS.                           | 53 |

|-----------------------------------------------------------------------------|----|

| FIGURE 4.13: SPI (3 WIRE SERIAL) SETTINGS.                                  | 55 |

| FIGURE 4.14: MENUCONFIG BASIC SETUP AND KERNEL SETTINGS FOR THE FIRST BUILD | 60 |

| FIGURE 4.15: NETWORKING SUPPORT OPTION.                                     | 62 |

| FIGURE 4.16: DM9000 SUPPORT OPTION                                          | 62 |

| FIGURE 4.17: FILESYSTEM SUPPORT CONFIGURATION                               | 62 |

| FIGURE 4.18: ALTERA SPI CONTROLLER                                          | 63 |

| FIGURE 4.19: MMC/SD/SDIO OVER SPI                                           | 63 |

| FIGURE 4.20: BOA SERVER OPTION.                                             | 64 |

| FIGURE 4.21: ENABLE GENERIC CGI                                             | 64 |

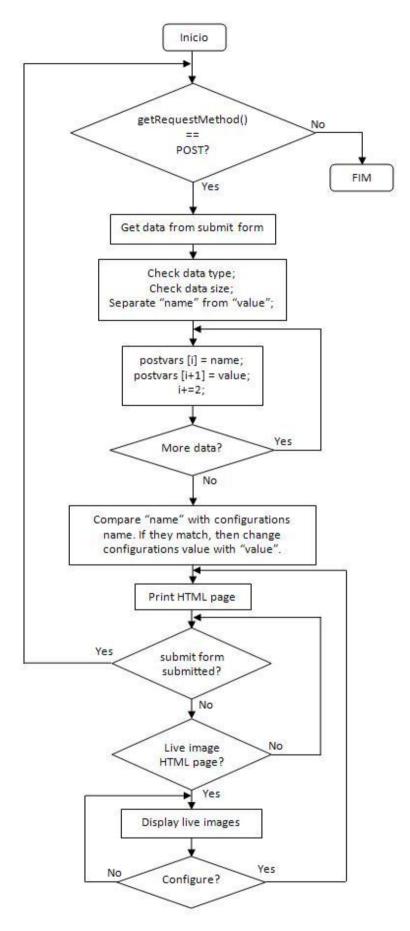

| FIGURE 4.22: FLOWCHART OF WEB SERVER.                                       | 66 |

| FIGURE 4.23: BASELINE SEQUENTIAL JPEG ENCODING.                             | 70 |

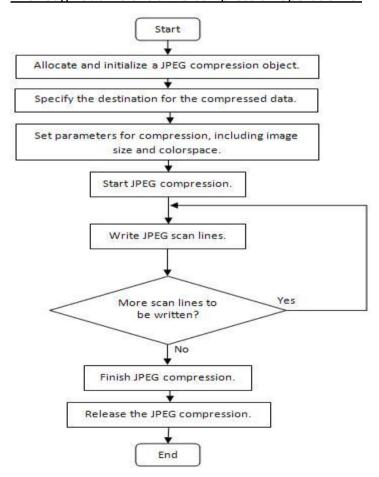

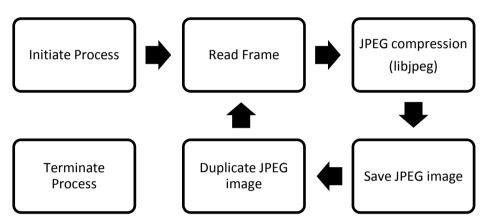

| FIGURE 4.24: FLOWCHART OF JPEG COMPRESSION.                                 | 70 |

| FIGURE 4.25: IMAGE CAPTURE AND JPEG ENCODING DAEMON                         | 73 |

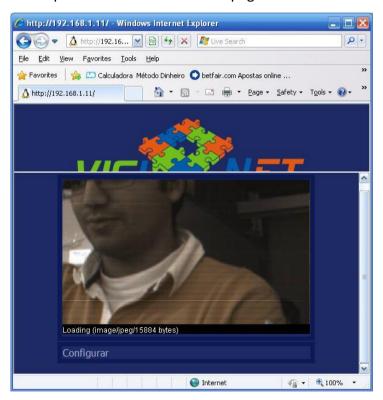

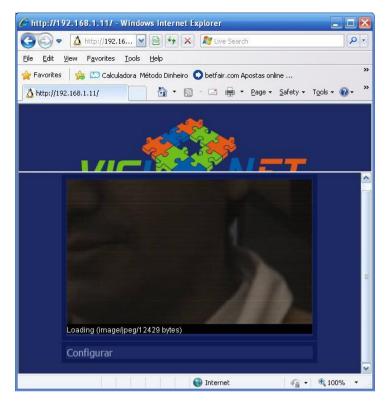

| FIGURE 5.1: LIVE VIEW WEB PAGE.                                             | 76 |

| FIGURE 5.2: IMAGE CAPTURED WITH 4X DIGITAL ZOOM.                            | 77 |

| FIGURE 5.3: LIVE IMAGES WITH DIFFERENT EXPOSURE TIME.                       | 78 |

| FIGURE 5.4: ALTERA DE2-70 + CMOS SENSOR DEVELOPMENT KIT.                    | 79 |

| Figure 6.1: Language Settings.                                              | 83 |

| Figure 6.2: Date and Hour Settings.                                         | 84 |

| FIGURE 6.3: NETWORK SETTINGS.                                               | 85 |

| FIGURE 6.4: SECURITY PROPERTIES.                                            | 85 |

| FIGURE 6.5: IMAGE PROPERTIES                                                | 86 |

| Figure 6.6: Schedule a Recording.                                           | 87 |

| FIGURE 6.7: SCHEDULE AN EVENT WEB PAGE.                                     | 87 |

# **List of Tables**

| Table 2.1: Features usage comparison for CMOS and CCD                  | 13 |

|------------------------------------------------------------------------|----|

| TABLE 2.2: COMPARISON OF MJPEG, MPEG-4, H.264 [VIHA10]                 | 17 |

| Table 2.3: Comparison of IPv4 and IPv6 [ViHa10].                       | 18 |

| TABLE 2.4: MAIN TRANSMISSION PROTOCOLS USED IN NETWORK CAMERAS [Ax06]. | 20 |

| TABLE 2.5: OS SUPPORT FOR THE NIOS II PROCESSOR [HAFU08].              | 24 |

| TABLE 3.1: COMPARISON BETWEEN FPGA AND ASIC [XIFP10]                   | 32 |

| TABLE 4.1: PARAMETERS AND SPECIFICATIONS OF THE CAMERA MODULE [TECM09] | 41 |

| Table 4.2: I2C Sensor configuration settings.                          | 44 |

| Table 4.3: SDRAM settings.                                             | 47 |

| Table 4.4: Summary of parallel I/O module settings.                    | 53 |

| Table 4.5: DM9000A module settings                                     | 54 |

| Table 4.6: Final SOPC system.                                          | 58 |

| Table 4.7: hwselect options.                                           | 60 |

| Table 5.1: Memory utilization.                                         | 75 |

| TARLE 5.2: RUN-TIME ANALYSES TO CALCULATE FRAME RATE                   | 79 |

# **Acronyms**

ADC Analog-to-Digital Converter

**CCTV** Closed-Circuit Television

**CGI** Common Gateway Interface

**DAC** Digital-to-Analog Converter

**DCT** Discrete Cosine Transform

**DMA** Direct Memory Access

**DMIPS** Dhrystone Million Instructions Per Second

**DVR** Digital Video Recorder

**FPGA** Field-Programmable Gate Array

**GPL** General Public License

**I2C** Inter-integrated Circuit

IC Integrated Circuit

IDE Integrated Development Environment

IP Internet Protocol

JPEG Joint Photographic Experts Group

**LCD** Liquid Crystal Display

MAC Media Access Control

MCU Minimum Coded Blocks

MMU Memory Management Unit

MP3 MPEG-1/2 Audio Layer 3

MPU Memory Protection Unit

NTSC National Television System Committee

PAL Phase Alternating Line

PDA Personal Digital Assistant

PTZ Pan Tilt Zoom

RTL Register Transfer Level

SD Secure Digital

SDRAM Synchronous Dynamic Random Access Memory

**SECAM** Sequential Colour with Memory

**SPI** Serial Peripheral Interface

SSRAM Synchronous Static Random Access Memory

TCP Transport Control Protocol

**UDP** User Datagram Protocol

**URL** Uniform Resource Locator

**USD** United States Dollars

VHDL VHSIC Hardware Description Language

VHSIC Very-High-Speed Integrated Circuit

**USB** Universal Serial Bus

# 1.Introduction

This chapter presents the overall context of this project. Firstly, a succinct motivation for the project is presented, enhancing the importance of this kind of systems in present days. After, a short background description of surveillance systems, event management and Intelligent Video is given. Next, the project goals and tasks are presented in a step-by-step approach, and finally, the organization of this thesis is detailed.

# 1.1. Motivation

This project is the result of the work done in Embedded System Research Group during the last year of the MSc in Industrial Electronics Engineering (Computer Technology).

The main goal of this project is to design and implement a System-On-Chip (SoC), in this case: an IP camera system. Although other commercial IP cameras do exist and are feature rich, this project aims to architect a system where all the important features for surveillance systems are implemented and be able to customize it and include new features as requested by customers.

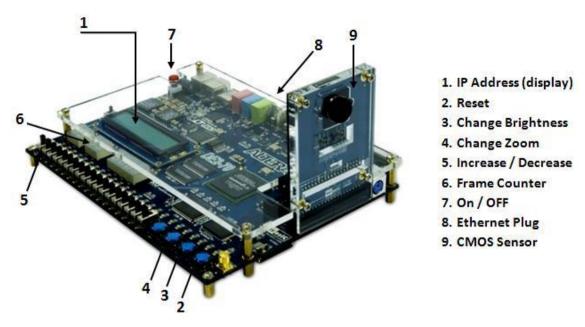

Figure 1.1 shows the project overview. The SoC prototype is based on an Altera DE2-70 development board, using the TRDB-D5M 5 megapixel CMOS sensor, to capture images. A host PC does the FPGA programming and is used for debugging, through USB Blaster programming. The development board connects to the network, through an Ethernet connection.

Figure 1.1: Project overview.

# 1.2. Surveillance System

"A surveillance system is a system design to process and monitor the behavior of people, objects or processes within a given system for conformity to expected/desired norms in trusted systems for security/social control. It can be either secrete or evident" [CoDeGo08].

A video surveillance system connected through a data network offers several advantages and advanced features that no analog surveillance system can support. Among the advantages are: remote access from anywhere with a network connection; high quality images (analog cameras have significant problems with interlacing scan being difficult to capture fast-moving objects); event management and intelligent video capabilities, with the possibility to schedule an event or implement software of image analyses; ease of integration and the highest scalability, flexibility and economy. [EzAr10]

# 1.3. Event Management and Intelligent Video

Now that cameras are increasingly affordable, surveillance systems are being generalized all over the places. They are used in security systems as an answer to theft, fraud and several kinds of attacks, in industry, in production lines and even to monitor employees.

A frequent problem in surveillance systems is the large amount of recorded video and little time to analyze it properly. Advanced network cameras with built-in intelligence and analysis capabilities take care of this problem, reducing the amount of recordings without interest and allowing programmed reactions.

Network cameras, duo to its worldwide connection and other built-in features like motion detection, alarm, audio detection, active tampering, alarm connections, I/O (input/output), and events management functions, allow a real-time operation. These features allow network cameras to continuously analyze inputs to detect an event and automatically react with the proper actions, such as video recording and sending alarm notifications with a much better cost efficiency.

### **1.4. Goals**

The main goal of this project is to fully implement an IP camera system on a FPGA. This means, in terms of hardware, to implement a system with a soft-core processor, memories, image acquisition, image processing blocks, and network capabilities. The trade-off between the use of FPGA versus an ASIC is included in section 3.1.1.

For software, the system requires an operating system that supports an application that deals with each frame acquired; furthermore a Web server and a TCP/IP implementation, allowing live images to be viewed on Internet.

To achieve this, the project was split in several steps described below.

# 1.4.1. Image Capture

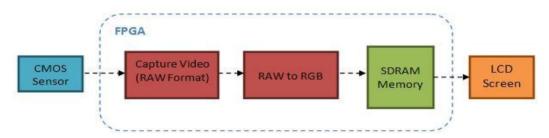

The aim of this first part was to implement video frames capture with the camera sensor and save them on SDRAM memory. To test this block, an LCD (4.3" TRDB-LTM from TERASIC [Te09]) is also connected to SDRAM memory. This way frames are displayed on the LCD (Figure 1.2). This project is part of a broader project that includes on the fly reconfiguration of some hardware and software characteristics.

Figure 1.2: Image Capture block diagram.

# 1.4.2. Microprocessor Implementation

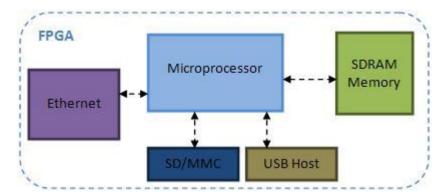

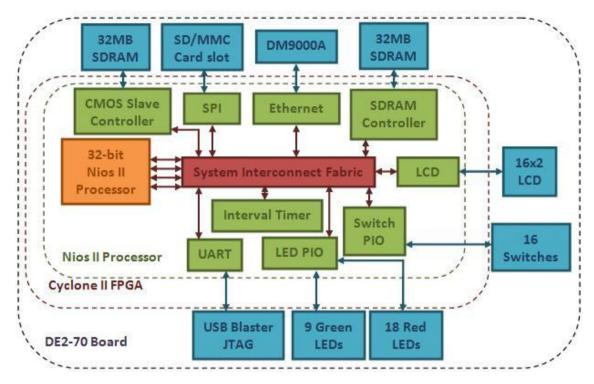

Next step was to implement a microprocessor on FPGA, to run an operating system and application software that includes a Web server and data processing programs. Other specialized hardware blocks were implemented: Ethernet capabilities to provide network access; a SDRAM module to control data exchange between processor and SDRAM chip; a SD/MMC card interface and USB host, to save or read data and add extra storage space if needed. More details in Figure 1.3.

Figure 1.3: Microprocessor implementation.

# 1.4.3. Complete IP Camera System

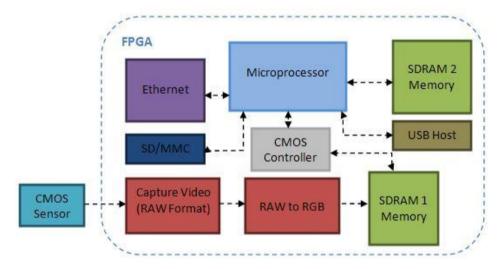

The final step was the assembling of all parts making the proposed system. The image capture block and the microprocessor block, work in parallel. While each frame is being stored in SDRAM 1, the microprocessor does its processing using SDRAM 2. In Figure 1.4, a final implementation is presented.

Figure 1.4: Final system implementation: the CMOS Controller block manages the data communication and frame requests between SDRAM 1 and the microprocessor.

# 1.5. Thesis outline

Besides this chapter, this document has 6 more chapters.

Chapter 2, **Surveillance Systems**, presents several concepts on surveillance cameras systems and a survey on commercial solutions and research projects for IP cameras.

Chapter 3, **System Description**, describes the FPGA as a prototyping system. The FPGA development board and the IDE for FPGA development are presented; the final system implementation on FPGA is also briefly described.

Chapter 4, **Implementation**, details the hardware and software design, explaining all the tasks to build the final system. It makes reference to the image sensor and its technical specifications; the implementation of the processor and its peripherals; the implementation of the operating system; and finally, software blocks of the Web server implementation and image compression.

Chapter 5, **Testing & Experiments**, describes the system validation, analyses processor, memory utilization and system performance.

Chapter 6, **Features and User Manual**, presents all the features of the IP camera system, as a manual. Here all configurations and settings are explained in the user perspective.

The last chapter, **Conclusion and Future Work**, discusses the project and all the work done. Further improvements and other ideas are suggested.

# 2. Surveillance Systems

The initial phase of this work consisted on a survey over IP cameras available in the market and related research projects. The search was focused towards low-cost products, mainly for surveillance purposes. The most relevant aspects are system performance and price.

It was also done an overview of the basic building blocks available in a regular IP camera, in terms of image sensor technology, processor, video compression, network properties, and operating system.

# 2.1. State of the Art

The increasing widespread of Internet and the emergence of innovative technologies led to a significant growth on IP based surveillance industry, over the past few years. This section intent to provide an overview of existing solutions on the market and also research projects.

# 2.1.1. Commercial Solutions

Nowadays a wide range of IP camera solutions exists, from tens to hundreds of Euros. These prices differences have to do with the fact that there are different application markets: stores, transports, schools, industrial, public surveillance, medical care.

IP cameras can be divided in two types: fixed, and PTZ (Pan, Tilt and Zoom). While fixed cameras have no motion or very limited motion, PTZ cameras can move horizontally, vertically, and zoom in/out.

Some IP cameras can work during day and night. When the brightness decreases to a certain level, the camera changes to night vision mode and uses infra-red (IR) vision.

In terms of image resolution, cameras are available from 300k pixel to 5 megapixels. Latest IP cameras use a HDTV resolution with 1280x720 pixels. This higher resolution means more data payload per frame, and to deal with this, it is needed the

use of image/video compression mechanisms. The most common used are Motion JPEG, MPEG-4, and H.264.

All surveyed devices support TCP/IP to allow communication. Currently IPv4 (32-bit address) is the most used, but there are also products with IPv6 (128-bit address). Regarding level 4 protocols, IP cameras implements at least one of the transport protocols: Transport Control Protocol (TCP), and User Datagram Protocol (UDP), but is common to see cameras supporting both of them.

Next sections do an overview of IP camera devices available on the market from the main companies. The cameras selected were those that roughly match those characteristics required in this project.

#### **AXIS 2100 Network Camera**

The AXIS 2100 [AxNe10] is a low-cost IP camera that supports: TCP/IP, SMTP e-mail, HTTP and other protocols. Configuration and management can be done via the product's own Web-based administration tools. It has external device connection with IR-sensors, switches, and alarm relays. It has a BOA Web server working in a Linux operating system. It delivers up to 10 images per second with a Motion JPEG compression format. The selling price in October 2010 is \$300.00 USD. [WeCa10]

Figure 2.1: Axis 2100 Network Camera [AxNe10].

# **Technical Specifications:**

- **Networking:** 10/100 Ethernet, with: TCP/IP, HTTP, FTP, SMTP, NTP, ARP, and BOOTP.

- I/O Connector: 1 optical-isolated alarm input. 1 digital output (max 24V, 100mA) with programmable digital input/output for remote image storage via FTP or SMTP, pre/post alarm image storage.

- Image Updating: Up to 10 frames/second over 10Mbps or 100Mbps networks.

- Alarm Buffer: Up to 500kB memory available for pre/post alarm image storage.

Hardware: ARTPEC-1 compression chip; ETRAX-100, including, 32 bit RISC, 100

MIPS CPU, 8 MB RAM, 2 MB FLASH PROM.

# **Gateway UNC-9211**

The UNC-9211 [HiTe10] is a PTZ camera for domestic use. It is very versatile in terms of resolution, and compression format; includes audio capability.

Figure 2.2: UNC-9211 IP Camera [HiTe10].

# **Technical Specifications:**

- **Sensor type:** Color 1/3" CCD Sensor (Sony).

- Video compression: MPEG-4, Motion JPEG, H.263, and 3GPP.

- Video frame rate: up to 30fps.

- **Communication protocol:** HTTP, RTSP, FTP, SMTP, TCP/IP, UDP, ARP, ICMP, DHCP, PPPoE, DDNS, UPnP, SAMBA, 3GPP.

- System: 32-bit RISC CPU, 32MB RAM, and 4MB Flash.

- Operating System: μClinux.

- I/O connectors: 6 alarm input.

### Vivotek IP8161

Vivotek IP8161 [Vi10] is a professional fixed network-camera. It is especially suitable for wide open spaces such as building entrance and airports, or applications requiring accurate identification, such as human faces in banks or vehicle license plates in parking lots. Featuring a 2 megapixel sensor, this camera also has PTZ functions. It works during day and night, and has a built-in SD/SDHC card slot for portable storage. The selling price in October 2010 is \$529.00 USD. [SeBe10]

Figure 2.3: Vivotek IP8161 IP Camera [Vi10].

# **Technical specifications:**

- **System:** TI DM365 SoC CPU, 256MB RAM, 128MB Flash.

- Operating System: Linux 2.6

- Image Sensor: 1/3.2" CMOS sensor.

- Video Compression: H.264, MPEG-4, Motion JPEG.

Network Protocols: IPv4, IPv6, TCP/IP, HTTP, HTTPS, UPnP, RTSP/RTP/RTCP,

IGMP, SMTP, FTP, DHCP, NTP, DNS, DDNS, PPPoE, CoS, QoS, SNMP and 802.1x.

### NetCam XL

The NetCam XL IP camera [StNe10] is specially designed to be used in street environments. It has the ability to attach a weather station and display the current weather data on the live images. According to [StNe10], the basic price starts at \$399.00 USD and can go to \$699.00 USD for megapixel model.

Figure 2.4: NetCam XL IP Camera [StNe10].

# **Technical specifications:**

- Imaging: Sharp 1/3" CCD Sensor.

- **System:** Motorola Coldfire CPU, 32MB DRAM, and 4MB Flash.

- **Operating System:** μClinux.

Network Protocols: TCP/IP, HTTP, FTP, ARP, Telnet.

- I/O Ports: 4 input alarms.

# 2.1.2. Research Projects

There are several projects regarding design IP cameras on FPGA technology. In terms of FPGA, the most used are Spartan and Virtex from Xilinx [Xi10], and Cyclone series from Altera [Al09]. Projects with Xilinx family FPGAs use mainly the embedded PowerPC processor [XiPeRe10], although Microblaze [XiTo10] is an option too. With the Altera FPGA development board, designers use the Nios II soft-core processor [AlEmPr09], well-documented and fully supported by Altera.

The Elphel project [El10] implemented the 353/363 series camera. It uses the ETRAX FS [AxEt10] processor running Linux that has support for multiple hardware interfaces: 10/100 Ethernet; USB 1.1; RS-232. For video processing/compression it is used the Xilinx Spartan 3E with 1200 logic elements. The system memory is a 64 MB SDRAM, and 128 MB flash memory. Images are captured using a high-resolution 5 megapixels CMOS sensor. Elphel provides high performance cameras based on free software and hardware designs. Users are free to buy Elphel cameras and change their software/hardware design to create other products for new applications.

Another IP camera project [Gu07] developed in *Instituto Superior Técnico* uses the Xilinx Virtex-4 FX FPGA with an embedded PowerPC 405 processor. The image sensor is retrieved from a low-cost 1.3 megapixels sensor; memory has 64 MB SDRAM. The software is implemented with the Xilinx Microkernel support. The Web server implements a webpage that refreshes one frame per second; it is also possible to change the brightness.

An intelligent IP Camera with motion detection implemented in FPGA was created in Denmark [CoDeGo08]. The project was based on an Altera FPGA DE2-35 development board. The main purpose of this work is to record a video each time a movement is detected, and save it on a SD-Card or make it accessible through an Ethernet network. The motion detection algorithm is implemented using the Nios II soft-core processor.

# 2.2. IP Camera Design

# 2.2.1. Image Sensor Technology

Based on the manufacturing process, there are two types of sensors: CMOS (Complementary Metal Oxide Semiconductor) and CCD (Charge-coupled Device). Each technology has its strengths and weaknesses that make it suitable for different applications. The CCD sensors are produced with a technology created specifically for the camera industry. The initial CMOS sensors used a technology standard that was widely used in memory chips for PCs. Today's CMOS sensors use a more specialized technology, and sensor's quality is increasing rapidly.

Figure 2.5: Image sensors: CCD (left); CMOS (right) [Ax06].

### **CCD Technology**

A CCD is an analog shift register that conveys analog signals through successive stages. The analog signals in each row of capacitors are transmitted and converted to digital via an ADC IC. CCD sensors are used in cameras for more than 30 years, and offer several advantages. In general, they still offer a slightly better sensitivity to light and generate a bit less noise than CMOS sensors. A greater sensitivity to light generates better images in low light conditions. However, CCD sensors are more expensive and more complex to integrate in a camera. A CCD can also consume up to 100 times more energy than an equivalent CMOS sensor.

# **CMOS Technology**

CMOS is a well-known and constantly developing manufacturing process used in the semiconductors industry. Each pixel on a CMOS sensor is accompanied by an amplifier based on a p-n junction structure. The p-n junction structure receives photons from the sensor and transmits them to an image signal processor. Recent advances in CMOS image sensors are bringing them close, in terms of image quality to the CCD sensors. CMOS sensors reduce the total cost of the cameras, as they contain all the required logic to manufacture the cameras. Compared to CCDs, CMOS sensors offer more integration possibilities and more features. CMOS sensors also feature a faster output (which is an advantage for higher resolution images), lower power consumption and reduced size of the system. CMOS sensors with megapixel resolution are more widely available and are less expensive than megapixel CCD sensors.

Table 2.1: Features usage comparison for CMOS and CCD.

|             | CMOS                    | CCD                      |

|-------------|-------------------------|--------------------------|

| Features    | - Low power consumption | - High light sensitivity |

|             | - Low cost              | - High color saturation  |

| Environment | Widely used indoor      | Widely used outdoor      |

#### 2.2.2. Soft-core Processors

There are two kinds of CPU cores for FPGA: hard and soft. Hardware based processor is a specialized area of the FPGA integrated circuit. On the other hand, soft-core processors are implemented using general-purpose FPGA logic cells. Main embedded CPU soft-cores are: Nios II, MicroBlaze, PicoBlaze, and Leon.

## **Nios II**

Nios II [AlEmPr09] is a proprietary 32-bit RISC architecture and a processor core owned by Altera for use on their FPGAs. The soft-core nature of the Nios II processor let the system designer implement and generates a custom Nios II core, taking in account application's specific requirements. Nios II functionality can be extended by adding a MMU (Memory Management Unit), or creating custom instructions.

Nios II is available in 3 different configurations: Nios II/f (fast), Nios II/s (standard), and Nios II/e (economy):

- Nios II/f core is designed for maximum performance at the expense of core size. Main features are: 6-stages pipeline, 1 instruction per cycle, optional MMU and MPU, and hardware multiply.

- Nios II/s core is designed to maintain a balance between performance and cost. Main features are: 5-stages pipeline, 1 instruction per cycle, and hardware multiply.

- Nios II/e core is designed for smallest possible logic utilization of the FPGA.

Main features are: no pipeline, 1 instruction per 6 cycles, no supplementary arithmetic blocks.

Nios II uses the Avalon switch fabric as interface to its embedded peripherals. Multiple masters can operate simultaneously, using a slave-side arbitration scheme.

To configure and generate a Nios system, designers use the SOPC (System-On-a-Programmable Chip) builder, available in Quartus II package.

### **MicroBlaze**

The MicroBlaze [XiTo10] is a 32-bit RISC soft-core processor designed for Xilinx FPGAs. Many aspects of the MicroBlaze can be user configured: cache size, pipeline depth (3-stages or 5-stages), embedded peripherals, memory management unit, and bus-interfaces can be customized. On Virtex-5 FPGA family, processor speed can be up to 210MHz.

Xilinx EDK (Embedded Development Kit) is the development package for building Micro Blaze (and PowerPC) embedded processor systems in Xilinx FPGAs. It contains the Micro Blaze core, peripheral cores, and the software development tools: GNU C compiler, GNU debugger, Eclipse IDE.

### Leon

LEON3 [AeGa10] is an open-source 32-bit architecture RISC processor. Main features are: 7-stages pipeline; separated data cache and data instructions; configurable cache; MMU; clock up to 125MHz in FPGA.

### **PicoBlaze**

PicoBlaze [XiInPr10] is an 8-bit RISC architecture and a CPU core owned by Xilinx. PicoBlaze was designed to operate in low-density FPGAs and occupy about 100 Spartan/Virtex slices. Some key features: 16 general purpose registers, up to 256 inputs/outputs ports.

# 2.2.3. Video Compression

Video compression technologies reduce file size with little or no negative effect on visual quality. However, a high compression ratio may cause a trade-off between bandwidth and image quality. Today, most network video compression vendors use standard techniques to ensure compatibility and interoperability. Motion JPEG, MPEG-4, and H.264 are the three major video compression technologies used by the IP surveillance industry. Each technology has a different compression ratio and is intended for different applications and purposes.

# **Motion JPEG**

Motion JPEG or M-JPEG, announced by JPEG (Joint Photographic Experts Group), is a digital video sequence consisting of a series of individual JPEG images [JpCo09]. One advantage of Motion JPEG is that each image in a video sequence has the same quality guaranteed, determinate by the compression level chosen for the network camera or video encoder. Each frame is encoded and decoded independently without referring to the previous or sequential frames (Figure 2.6). The main disadvantage of Motion JPEG is that it does not use any video compression techniques to reduce data, because it is a series of static images.

Figure 2.6: MJPEG encodes each frame independently [ViHa10].

### MPEG-4

MPEG-4 was formed by the MPEG working group under ISO and IEC in 1998 [ViHa10]. It was developed for limited bandwidth applications that streams high quality video. MPEG-4 implements a technique that compares key frames with next sequential frames, leaving out redundant information and compressing only frame-to-frame differences. This result in a large decrease of the original file size reducing the bandwidth requirements. Figure 2.7 shows MPEG-4 comparing frames and compressing only differences between frames.

Figure 2.7: MPEG-4 finds differences between key frames and following frames [ViHa10].

### H.264

H.264 was initially developed by ITU (International Telecommunication Union) and then published by JVT, a group combined by ITU and ISO/IEC, in 2003. H.264 is also known as MPEG-4 part 10. It has a higher compression ratio comparing to MPEG-4 or Motion JPEG [ViHa10]. H.264 technology is similar to MPEG-4, where sequential and previous key frames are required during compression and decompression. H.264 provides a more efficient method for compression with more precise motion search and prediction. It requires, however, more powerful CPU capabilities.

Table 3.1 shows a comparison between MJPEG, MPEG-4 and H.264, where H.264 features higher compression ratio, but at expense of a 10 times higher CPU usage.

|                               | MJPEG                                                            | MPEG-4                                                                                              | H.264                                                                                               |

|-------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Compressed file size          | 20%                                                              | 2%                                                                                                  | 1%                                                                                                  |

| Bandwidth comparison ratio    | 20                                                               | 2                                                                                                   | 1                                                                                                   |

| Encoding CPU<br>loading ratio | 1                                                                | 4                                                                                                   | 10                                                                                                  |

| Application                   | <ul><li>Local storage</li><li>Snapshot</li><li>viewing</li></ul> | <ul> <li>Moving         picture         viewing         - Real-time         transmission</li> </ul> | <ul> <li>Moving         picture         viewing         - Real-time         transmission</li> </ul> |

Table 2.2: Comparison of MJPEG, MPEG-4, H.264 [ViHa10].

# 2.2.4. IP Network

Different network technologies are used to provide various advantages of a networked video system. This section discusses communication over the Internet using TCP/IP protocol; and presents an overview of the data transmission protocols used in network video.

### **IP Address**

Each network device has its identification, an IP address, from the level 3 protocol employed – IP, Internet Protocol. Nowadays, there are two versions of IP: IP version 4 (IPv4) and IP version 6 (IPv6). The main difference between the two is that an IPv6 has a much larger address space, using 128 bits against 32 bits of an IPv4 address. The problem with IPv4 is that since the number of network devices is increasing at a very fast pace, the IPv4 address space is rapidly nearing exhaustion, opening space to IPv6. IPv4 addresses are grouped into four blocks, each separated by one point. Each block represents a number between 0 and 255.

The following blocks of the IP address space are reserved for local networks:

- 10.0.0.0 ~ 10.255.255.255

- 172.16.0.0 ~ 172.31.255.255

- 192.168.0.0 ~ 192.168.255.255

All devices that must communicate over the Internet should have their own public IP address. A public IP address is an address assigned by an Internet service provider (ISP). An ISP may assign a dynamic IP address, which can change during a session, or a

static address. As so, an IPv4 address for a network camera can be assigned in two main ways: 1) automatically, using DHCP where a dynamic address is assigned, and 2) by manually entering a static IP address.

DHCP (Dynamic Host Configuration Protocol) automatically assigns a valid IP address to a network device on the Internet. Assigning a fixed IP address to each device will result in waste of IP addresses when the devices are not in operation. DHCP tries to make more efficient use of the IP addresses.

The IPv6 standard consists of 128 bits, which are divided into eight parts, each group containing four 16-bit digits. As said before, the main advantage of IPv6 is the availability of a huge number of IP addresses, and the possibility of allowing a device to automatically configure its IP address using its MAC address. Table 2.3 shows a comparison between IPv4 and IPv6.

FeatureIPv4IPv6Address space32 bits128 bitsConfiguration settingsManualAutoPriority controlNoYesAuthenticationNoYes

Table 2.3: Comparison of IPv4 and IPv6 [ViHa10].

#### **Transmission Protocols**

This section introduces the two transmission protocols, in the TCP/IP stack: TCP (Transmission Control Protocol) and UDP (User Datagram Protocol). These transport protocols act as carriers for many other protocols. The HTTP (Hypertext Transfer Protocol) is a layer 7, or application, protocol employed to browse Web pages on servers around the world via the Internet, and it is carried by TCP. Other application layer examples are FTP (File Transfer Protocols), SMTP (Send Mail transfer Protocols), and RTP (Real-time Transport Protocol).

### Transmission Control Protocol (TCP)

TCP creates a reliable transmission channel, based on connections. TCP handles the task of dividing large blocks of data into smaller packets, and ensures that data sent by one side is received at the other end. The reliability of TCP is achieved by retransmission, but can cause considerable delays. In general, TCP is used when

reliable communication is more important than latency, thus providing better video quality, but affecting real-time effect.

# **User Datagram Protocol (UDP)**

UDP uses a simple transmission model without implicit hand-shaking dialogue to provide reliability, ordering, or data integrity, leaving the whole control mechanism and error checking over the higher protocols that needs it. Since UDP does not perform any transmission of data losses, therefore does not introduce further delays, being mainly used for time-sensitive responses and when the video quality is less important.

# **Hypertext Transfer Protocol (HTTP)**

HTTP works as a request-response protocol in the client-server computing model. It is designed to allow users to view information on a web page through a browser. Taking advantage of this feature, it is also a common way to display video images from a network camera, where the video device works as a Web server, providing the video stream to the user or application.

### File Transfer Protocol (FTP)

FTP is used to upload and download files to and from a server. Several models support an FTP client allowing to upload information from a network camera (snapshots or video clips) to a FTP server, whenever an event occurs.

# Send Mail Transfer Protocol (SMTP)

The SMTP is an internet standard for e-mail transmissions across Internet Protocol networks. Some network cameras can send snapshots or notifications from the email client implemented.

### Real-time Transport Protocol (RTP)

The RTP is an Internet Protocol standard that specifies a way to manage real-time transmissions. It runs on top of UDP, although it can use other transport protocols. RTP components include a sequence number, to detect lost packets; a payload identification, which describes the specific media encoding; frame identification, which

marks the beginning and end of each frame; and a source identification, which identifies the frame's originator. RTP is a common way to transmit videos and audio with H.264/MPEG-4 compression format. On Table 2.4 there is a description of the main protocols implemented on cameras.

**Application Layer Transport Layer** Description **FTP** TCP Data transfer over internet / intranet. ТСР SMTP is specified for outgoing mail **SMTP** transport. TCP Designed for users to view information on a **HTTP** web page through a browser. UDP/TCP Real-time multimedia streaming applications **RTP** that require time constraints.

Table 2.4: Main transmission protocols used in network cameras [Ax06].

# 2.3. Software Design

# 2.3.1. Programming Languages

This section describes the different programming languages, use in this project, for different purposes. The FPGA configuration is specified using a hardware description language (HDL) (2.3.2). High level languages are used in embedded OS (2.3.4).

# 2.3.2. Hardware Description Language (HDL)

The FPGA is generally configured using a HDL (Hardware Description Language). A HDL can describe the operation of a circuit, its design and organization, the same way it can be simulated to test and verify its operation. HDLs have the ability to model multiple parallel blocks (flip-flops, adders, etc...) that can execute independent from each other.

Taking as example a software programming language that is processed by a compiler, HDLs use a synthesizer to transform HDL code into a physically realizable gate netlist. HDLs have several advantages compared to traditional schematic-based design [Pa03]:

- The design can be described at a very abstract level using HDLs;

- If a new technology emerges, designers do not need to redesign their circuit;

- Functional verification can be done early by using HDLs designs.

Verilog HDL and VHDL are the two most widely-used and well-supported HDL implementations used in industry, but others HDL languages do exist, namely: AHDL, MyHDL, Ruby, RHDL, SystemVerilog and SystemC.

## Verilog

"The Verilog language is a hardware description language that specifies a digital system at a wide range of levels of abstraction. The language supports the early conceptual stages of design with its behavioral level of abstraction, and the later implementation stages with its structural abstractions." [ThMo02]

A Verilog design consists of a hierarchy of modules. Modules communicate with each other through a set of declared input, output, and bidirectional ports. Inside a module it is possible to have: net/variable declarations (wire, reg, integer ...), concurrent and sequential statement blocks, and instances of other modules. Sequential statements are placed inside a begin/end block and executed in sequential order within the block.

#### **VHDL**

VHDL (VHSIC Hardware Description Language) [Co89] is a hardware description language used in electronic design automation to describe digital and mixed-signal system such as FPGA and integrated circuits. VHDL was created at the US Department of Defense as a language for documenting designs. Nowadays a wide range of designs are modeled in VHDL.

Every VHDL statement can be executed concurrently (VHDL is a parallel language). Sequential steps can be also possible if explicit. Also, explicit time delays can be achieved to execute a statement after a certain time. The key advantage of VHDL when used for system design is that it allows the behavior of the required system to be described (modeled) and verified (simulated) before synthesis tools translate that design into real hardware (gates and wires).

Other companies promote other HDL languages for different reasons: some try to reduce the complexity of designing in HDLs, raising the abstraction level of the design. There are over a dozen of HDL languages, some still supported, and others are outdated. Only main and current HDL languages are referenced.

#### **AHDL**

"The Altera Hardware Description Layer (AHDL) is a high level, modular language especially suited for complex combinatorial logic, group operations, state machines, and truth tables." [SaSm00]

A disadvantage of AHDL is that it is proprietary. An advantage is that all language constructs are synthesizable.

#### Handel-C

The Handel language is a subset of Occam used for hardware synthesis research at Oxford University during the early nineties [Sh04]. It is a high level programming language which targets low-level hardware. It contains all the necessary features to describe complex algorithms.

## 2.3.3. High Level Software Programming Languages

A high level language is a programming language more abstract, easier to use, and more portable across platforms. This abstraction is intended to make the language user-friendly, simplifying the task for the creation of complex programs.

The terms high-level and low-level are relative. Some programmers may refer C as low-level language, but in this thesis context C/C++ are considered high-level languages.

## **C** language

"C is a versatile, flexible, and powerful programming language that was designed and developed in 1972." [ReZi10]

A program written in C has functions and variables. Inside functions are statements and the variables hold the results of computations. All variables must be declared, either within a function or outside of any function.

#### C++ language

C++ [Sa95] is essentially C with extensions for object-oriented programming. Some features are: strongly typed, multi-paradigm, not platform specific, and exception handling functionality. Its application domain includes system software, application software, device drivers, embedded software, and high-performance server and client applications.

#### C Sharp

C Sharp [WiSh10] is a multi-paradigm programming language encompassing imperative, declarative, functional, object-oriented, and component-oriented. It is intended to be a simple, modern, general-purpose, object-oriented programming language. "C sharp has borrowed many good features from Java." [Ba08]

## Java

"The language derives much of its syntax from C and C++ but has a simpler object model and fewer low-level facilities. Java applications are typically compiled to bytecode (.class files) that can run on any Java Virtual Machine (JVM) regardless of computer architecture. Java is a general-purpose, concurrent, class-based, object-oriented language that is specifically designed to have as few implementation dependencies as possible." [WiJa10]

Java is currently one of the most popular programming languages in use, and is widely used from application software to web applications.

## 2.3.4. Embedded OS

Embedded processors now require complex software that needs support for multitasking, synchronization of tasks, scheduling and buffering I/O operations, memory management, graphic displays, file systems, and networking. Supporting all this services became harder when developing custom code. Nowadays, the time spent developing needs to be shorter.

An OS (Operating System) can provide a wide list of features and services. Software developers can work at a higher level of abstraction by using the API (Application Programming Interface) of the operating system. An embedded OS

typically requires less processing power and has a smaller memory footprint than a desktop OS. It also is likely to support booting from flash memory, produce ROMable code, and to have I/O device drivers for the I/O devices that are more commonly found in small devices. A C/C++ compiler is typically provided with the OS. Software developing is almost done in C/C++ and usually come with a C/C++ compiler, assembler, and debugging tools.

Nowadays, there are many open source operating systems. One of the most known is  $\mu Clinux$ .

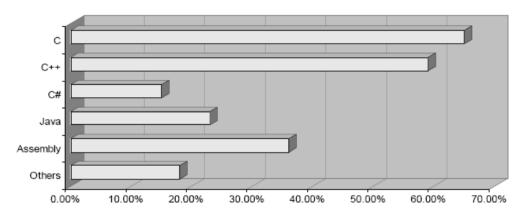

A survey demonstrated that C language and derivates are the choice for the majority of the embedded family development [HaFu08]. A detailed result of this survey is shown in (Figure 2.8).

Figure 2.8: Programming languages used to develop embedded devices [HaFu08].

Several embedded operating systems are supported on the Nios II soft-core processor as seen in (Table 2.5). Some are open source, others are commercial.

| os               | RTOS | OS Type     | Company Name        | Nios II IDE<br>Plug-in |

|------------------|------|-------------|---------------------|------------------------|

| eCos             | YES  | Open Source | eCosCentric         |                        |

| Euros RTOS       | YES  | Commercial  | Euros               |                        |

| Erika Enterprise | YES  | Commercial  | Evidence            | YES                    |

| Thread X         | YES  | Commercial  | Express Logic       | YES                    |

| MicroC/OS-II     | YES  | Commercial  | Micrium             | YES                    |

| embOS            | YES  | Commercial  | Segger              |                        |

| uClinux          |      | Open Source | Community Supported | YES                    |

Table 2.5: OS support for the Nios II Processor [HaFu08].

eCos, MicroC/OS-II, and  $\mu$ Clinux are the most popular OS available for the Nios II processor. Next sections take a detailed look at those embedded OS.

#### μClinux

The uClinux [EmLi10] stands for "Microcontroller Linux", and it is a fork of the Linux kernel for microcontrollers without a memory management unit (MMU). Initially,  $\mu$ Clinux was targeted to the Motorola DragonBall family of embedded 68k processors. Currently,  $\mu$ Clinux includes Linux kernel releases for 2.0, 2.4, and 2.6 as well as a collection of user applications, libraries and tool chains.

μClinux has support for several architectures, and forms the basis of several embedded products: network routers, network cameras, security cameras, DVD, mp3 players, VoIP phones, scanners, and card readers.

An open source version [NiWi09] of uClinux has been ported to the Nios II processor.

#### eCos

Embedded Configurable Operating System (eCos) [Ec10] is an open source, royalty-fee, real-time operating system intended for embedded systems and applications which need only one process with multiple threads. It is designed to be customizable for application requirements to deliver the best possible run-time performance and minimize hardware needs. It is implemented in C/C++ and has compatibility layers and API for POSIX and uTRON.

eCos was designed for devices with memory size in the tens of hundreds of kilobytes, or with real-time requirements. A minimum of 2 MB of RAM is needed, not including application and service needs. eCos runs on a wide variety of hardware platforms, including: ARM, IA-32, Motorola 68k, MIPS, Nios II, PowerPC, and SPARC.

At the beginning managed by Cygnus, eCos is now free software developed by a community ensuring on-going technical innovation and platform software.

# MicroC/OS-II

MicroC/OS-II [Mi10] is a highly portable, scalable, preemptive, real-time, multitasking kernel for microprocessors and microcontrollers. It is written in C for

maximum portability. It is currently maintained by Micrium Incorporation and can be licensed on product line basis. Micrium also created other middleware software products such as uC/OS-View, uC/CAN, uC/TCP-IP, uC/FS, uC/GUI, uC/MOD-BUS, uC/LCD, uC/USB (Mass Storage Device and Bulk) and a large assortment of uC/TCP-IP applications such as client software for DHCP, POP3, SNTP, FTP, TFTP, DNS, SMTP, and TTCP.

MicroC/OS-II can manage up to 255 tasks and provides services such as semaphores, mutual exclusion semaphores, event flags, message mailboxes, message queues, task management, fixed-size memory block management, and time/timer management [Mi10].

Altera has ported MicroC/OS-II to the Nios II processor. Altera distributes MicroC/OS-II in the Nios EDS, and supports the Nios II implementation of the MicroC/OS-II kernel.

MicroC/OS-II is suitable to use on a wide-range of applications: Avionics, Medical Equipment/Devices, Data Communications Equipment, White Goods (Appliances), Mobile Handsets, Industrial Controls, Consumer Electronics, Automotive, and other embedded applications.

Nios II microC/OS-II has a free license for universities and students provided by Micrium.

#### **RTEMS**

The Real-Time Executive for Multiprocessor Systems (RTEMS) [Rt10] is a full featured real-time operating system that supports a variety of open API and interface standards. RTEMS does not provide any form of memory management or process. Its design has been ported to various target processors architectures: ARM, ATMEL AVR, Blackfin, x86, 68k, MIPS, Nios II, PowerPC, and SPARC.

#### **FreeRTOS**

FreeRTOS [Fr10] is a portable, open source, royalty fee, mini real time kernel. It is distributed under the GPL. Some supported architectures are: ARM, Atmel AVR, Micro Blaze, x86, 8052, Coldfire, and Nios II.

## 2.4. IP Surveillance Overview

The development of innovative technologies and rapid expansion of Internet usage, led to a growth of IP surveillance industry, driving changes in the video surveillance market. IP surveillance is increasing its importance in the video surveillance market, mainly with IP cameras.

An IP surveillance system consists of an IP camera that transmits a sequence of images, allowing users to view and manage the video and image remotely with a networked device, such as a personal computer. Other components can also be part of an IP surveillance system depending on the needs: a video server, a network video recorder, and central management software.

# 2.4.1. Video Management

An IP surveillance system must include video management to achieve reliability, flexibility, scalability and high efficiency. Video management provides basic monitoring, recording and management functions, and advanced functions as intelligent surveillance. Usually video management software is included in IP camera's Web server and these functions are performed by the IP camera itself.

Users can view live video images with a Web browser, and it is possible to allow more than one user to access the images.

Recording can be performed in different modes. Each time the user desires to record, the IP camera does a continuously recording. It is possible to schedule a period of recording, where the IP camera records the video and then store all data, giving the possibility to the user to watch the video whenever needed. Other option is to record only when a specific event is triggered.

It is possible to connect digital input devices. In surveillance systems these devices are alarms and sensors: anti-glass break sensors, active infrared sensors, smoke sensors, and passive infrared sensor, and other type of sensors. Figure 2.9 shows various input devices available to connect to an IP camera.

Figure 2.9: Digital input surveillance devices [ViHa10].

It is also possible to connect digital output devices: a soundalarm, a flashlight alert, warning signals etc. Figure 2.10 shows some output devices used in surveillance environment.

Figure 2.10: Digital output surveillance devices [ViHa10].

# 2.4.2. Applications

IP surveillance systems can be used in a wide-range of applications. It can be used to monitor people behavior, public places, specific facilities, etc. There are some typical application possibilities in key business areas [Ax06]:

- Stores: IP surveillance system applied in stores can decrease the number of thefts and robberies, increasing staff's security and optimizing the store management. A great advantage of IP surveillance is the possibility to implement EAS (Electronic Article Surveillance) in the store, where each stolen product is reported immediately and recorded. IP cameras are not only used for surveillance, they can monitor costumer's habits and register most visited areas.

- **Transportation:** IP surveillance can increase security in airports, highways, train stations, and other transport systems. IP cameras can also be used to monitor city traffic.

- **Education:** From elementary schools to university, IP surveillance helps to avoid vandalism and increasing security for students, teachers and staff. IP cameras can be used for remote learning for students who cannot attend school.

- Industrial environment: IP cameras can monitor production lines, verifying the correctness of the assembly process. In the office, IP cameras can provide videoconferencing.

- Streets surveillance: IP surveillance is a basic tool to fight against crime and protect citizens. Police can have access to these cameras and every time an irregular situation is detected, a quick response can be guaranteed.

- Government: Public buildings, museums, offices, libraries, prisons can be protected by IP cameras 24 hours a day. With an intelligent system is also possible to do people counting, and elaborate statistics.

- **Medical care:** IP surveillance increases the security of staff, patients, and visitors.

Doctors can monitor patients from any place that has an Internet connection.

# 3. System Analysis and Design

This chapter presents the system constraints analysis, in terms of FPGA, processing time and data consistency. It also presents the FPGA development board used for IP camera design and the Quartus II design software.

All choices for the implemented system are described, in terms of programming language, FPGA development board, CMOS sensor used, embedded operating system and the soft-core processor.

# 3.1. System constrains analysis

This section gives an overview of the different constraints of the system.

#### 3.1.1. FPGA constraints

One of the first constraints in camera system development is to evaluate the implementation of the IP camera system with all necessary features on a FPGA platform.

#### FPGA definition

A field-programmable gate array is a logic device that contains a two-dimensional array of generic logic cells and programmable switches. A logic cell can be configured to perform a simple function, and a programmable switch can be customized to provide interconnections among logic cells. A custom design can be implemented by specifying the function of each programmable switch [Ch08].

#### **FPGA versus ASIC**

Compared to ASICs the flexibility of a FPGA is at the same time its weakness in terms of area, delay and power consumption: 20 to 35 times more area is required, 3 to 4 times slower in speed performance, and consumes roughly 10 times more energy. Despite these disadvantages, FPGAs present an alternative for digital system implementation mainly for small enterprises or small entities [Ch08] as it has a shorter

time-to-market and cheaper costs for a reasonable amount of systems. Table 3.1 summarizes FPGA advantages and ASIC advantages.

Table 3.1: Comparison between FPGA and ASIC [XiFp10].

| FPGA Design Advantages         | ASIC Design Advantages           |

|--------------------------------|----------------------------------|

| Faster time-to-market          | Full custom capability           |

| Development cost cheaper       | Lower unit costs                 |

| More predictable project cycle | Smaller form factor              |

| Field reprogramability         | Higher raw internal clock speeds |

# Requirements for the FPGA Development Board

- Support / documentation / examples available and up to date;

- Input / output for camera sensor;

- SD/MMC Card Slot for adding extra storage space and firmware update option;

- USB host connector;

- Possibility to add a soft-core processor;

- Enough memory for video frame.

#### 3.1.2. Time constraint

Time constraints are an important subject in an IP camera system. The image capture, processing and buffering needs to be fast enough, avoiding bottlenecks. On the other hand, software needs to take into account execution speed. It is important to have efficiency in image compression algorithm. Time constraints are related to data constraints (3.1.3).

# 3.1.3. Data constraint

To buffer captured frames, temporary data memory needs to have enough space to allocate several frames. The other constraint regards to the image type format. Main encoding algorithms work with RGB and YUV format.

The soft-core processor needs a minimum amount of RAM to accomplish its task. This amount of memory depends on which embedded OS is running, video frame payload, and executing programs needs.

Storage expansion using external SD/MMC Card or USB pen drive is also a requirement in order to store video streams.

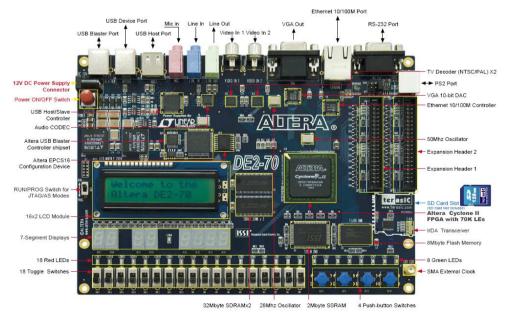

# 3.2. FPGA Development Board

The DE2-70 development board features a Cyclone II FPGA chip [AlDe09]. All main board components are connected to the chip pins, allowing the user to configure the connections between them as desired. The DE2-70 board includes switches, LEDs, 7-segment displays, and a 16 x 2 character display. If memory is needed, it is also available SSRAM, SDRAM, and Flash memory chips. For experiments that require a processor, it is possible to instantiate Altera's Nios II processor, and for simple input/output interfaces, RS-232 and PS/2 connectors are available. For more complex design projects, it is possible to use USB and Ethernet connectors, a SD/MMC Card slot, and two expansion headers.

The software provided with DE2-70 board is the Quartus II Web Edition design tools.

#### 3.2.1. Characteristics of the DE2-70 board

An image of the DE2-70 board is shown in Figure 3.1. It depicts the layout of the board and indicates the location of connectors and key components.

Figure 3.1: The DE2-70 Board [AlDe09].

Detailed information about DE2-70 Development Board [AIDe09]:

## Cyclone II 2C70 FPGA

- 68,416 Logic Elements

- 250 M4K RAM blocks

- 1,152,000 total RAM bits

- 150 embedded multipliers

- 4 PLLs (Phase-Locked Loop)

- 622 user I/O pins

- Fine Line BGA 896-pin package

# Serial Configuration device and USB Blaster circuit

- Altera's EPCS16 Serial Configuration device

- On-board USB Blaster for programming and user API control

- JTAG and AS programming modes are supported

## SSRAM (Synchronous Static Random Access Memory)

- 2-Mbyte standard synchronous SSRAM

- Organized as 512K x 36 bits

- Accessible as memory for the Nios II processor and by the DE2-70 Control

Panel

#### **SDRAM**

- Two 32-Mbyte Single Data Rate Synchronous Dynamic RAM memory chips

- Organized as 4M x 16 bits x 4 banks

- Accessible as memory for the Nios II processor and by the DE2-70 Control

Panel

# Flash memory

- 8-Mbyte NOR Flash memory

- Support both byte and word mode access

- Accessible as memory for the Nios II processor and by the DE2-70 Control

Panel

# SD card socket

Provides SPI (Serial Peripheral Interface) and 1-bit SD mode for SD Card access Accessible as memory for the Nios II processor with the DE2-70 SD Card

Driver

#### **Pushbutton switches**

- 4 pushbutton switches

- Debounced by a Schmitt trigger circuit

- Normally high; generates one active-low pulse when the switch is pressed

- Toggle switches

# 18 toggle switches for user inputs

- A switch causes logic 0 when in the DOWN (closest to the edge of the DE2-70 board) position and logic 1 when in the UP position

## **Clock inputs**

- 50-MHz oscillator

- 28.63-MHz oscillator

- SMA external clock input

#### **Audio CODEC**

- Wolfson WM8731 24-bit sigma-delta audio CODEC

- Line-level input, line-level output, and microphone input jacks

- Sampling frequency: 8 to 96 KHz

- Applications for MP3 players and recorders, PDAs, smart phones, voice recorders, etc.

## **VGA** output

- Uses the ADV7123 140-MHz triple 10-bit high-speed video DAC

- With 15-pin high-density D-sub connector

- Supports up to 1600 x 1200 at 100-Hz refresh rate

- Can be used with the Cyclone II FPGA to implement a high-performance TV Encoder

## NTSC/PAL/ SECAM TV decoder circuit

- Uses two ADV7180 Multi-format SDTV Video Decoders

- Supports worldwide NTSC/PAL/SECAM color demodulation

- One 10-bit ADC, 4X over-sampling for CVBS

- Supports Composite Video (CVBS) RCA jack input

Supports digital output formats: 8-bit ITU-R BT.656 YCrCb 4:2:2 output + HS,

VS, and FIELD Applications: DVD recorders, LCD TV, Set-top boxes, Digital

TV, Portable video devices, and TV PIP (picture in picture) display.

#### 10/100 Ethernet controller

- Integrated MAC and PHY with a general processor interface

- Supports 100Base-T and 10Base-T applications

- Supports full-duplex operation at 10 Mb/s and 100 Mb/s, with auto-MDIX

- Fully compliant with the IEEE 802.3u Specification

- Supports IP/TCP/UDP checksum generation and checking

- Supports back-pressure mode for half-duplex mode flow control

# **USB Host/Slave controller**

- Complies fully with Universal Serial Bus Specification Rev. 2.0

- Supports data transfer at full-speed and low-speed

- Supports both USB host and device

- Two USB ports (one type A for a host and one type B for a device)

- Provides a high-speed parallel interface to most available processors;

supports Nios II with a Terasic driver

- Supports Programmed I/O (PIO) and Direct Memory Access (DMA);

#### **Serial ports**

- One RS-232 port

- One PS/2 port

- DB-9 serial connector for the RS-232 port

- PS/2 connector for connecting a PS2 mouse or keyboard to the DE2-70 board

#### IrDA transceiver

- Contains a 115.2-kb/s infrared transceiver

- 32 mA LED drive current

- Integrated EMI shield

- IEC825-1 Class 1 eye safe

- Edge detection input

#### Two 40-pin expansion headers

- 72 Cyclone II I/O pins, as well as 8 power and ground lines, are brought out to two 40-pin expansion connectors

- 40-pin header is designed to accept a standard 40-pin ribbon cable used for IDE hard drives

- Diode and resistor protection is provided

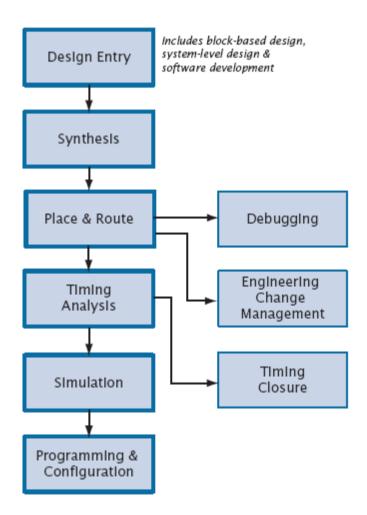

# 3.2.2. Quartus II Design Software

The Altera Quartus II design software [AlQu07] provides a complete, multiplatform design environment. Figure 5 shows an illustration of the Quartus II design flow.

Figure 3.2: Quartus II design flow [AlQu07].

The design flow involves the following steps [ShPa10]:

- Design Entry the desired circuit is specified either by means of a schematic diagram, or by using a hardware description language, such as Verilog or VHDL.

- **Synthesis** the entered design is synthesized into a design implementation in terms of logic gates.

- Place & Route establishes the placement of the logic elements defined in the netlist into the logic elements (LE) in an actual FPGA chip.

- Timing Analysis analyzes propagation delays along the various paths in the fitted circuit, to provide an indication of the expected performance of the circuit.

- **Simulation** functional or timing simulation is performed.

- Programming & Configuration the designed circuit is implemented in a physical FPGA chip by programming the configuration switches that configure the LEs and establish the required wiring connections.

#### 3.2.3. ModelSim-Altera

Mentor Graphics Corporation's ModelSim-Altera version 6.5b software is included in the Quartus II version 9.1 design software. It performs a functional and a timing simulation of a Quartus II-generated design containing Verilog HDL, VHDL, or both.

The ModelSim-Altera software gives designers advanced test bench capabilities for faster simulation and faster time-to-market. Test benches can be written in the same language as the design source code, i.e, Verilog HDL, as the original design. Test benches can apply stimulus to a module and monitor its outputs. Test benches can monitor outputs and appropriate messages or warnings can be displayed as required by the user [Hd10].

# 3.3. A short Overview of the Implemented System

The hardware system design implied the implementation of image acquisition and image processing blocks, a soft-core processor, and other necessary blocks. On the

other hand, in embedded software system design, the software is developed and downloaded to the embedded system.

#### **Programming Language**

The hardware design was implemented using Verilog HDL. Reference design of TRD-D5M camera sensor provided by Altera is in Verilog HDL. Also, original image acquisition block and other IP core blocks provided by Altera are in Verilog HDL.

Software programs were developed under C language and later cross-compiled to Nios II processor.

#### **FPGA Development Board**

The project was implemented using an Altera DE2-70 FPGA Board. The Cyclone II FPGA with 70.000 logic elements allows the full implementation of the IP Camera System. The Altera DE2-70 board features used are:

- USB Blaster for FPGA programming and Debug;

- 32-MB SDRAM-1 to be used as frame images buffer;

- **32-MB SDRAM-2** to be used as Nios II processor SDRAM;

- SD-Card Socket to allow the use of SD/MMC Cards. This memory card can be used as storage card or to update firmware;

- Pushbuttons/switch to control CMOS sensor exposure time, restart system,

and other configurations;

- 10/100 Ethernet controller to provides networking connections;

- USB Host controller to allow the use of USB storage devices;

- **40-pin expansion header** to connect a CMOS camera;

## **Camera CMOS sensor**

The camera sensor used in this project is the TRDB-D5M [TeCm09]. It is a Micron 5 Mega Pixel CMOS sensor with controlled exposure time and output data is in RGB Bayer Pattern format. This camera sensor is fully compatible with Altera DE2-70 Board.

## **Embedded Operating System**

The  $\mu$ Clinux is the operating system chosen for this project. An open-source  $\mu$ Clinux-distribution for NIOS II is available and supported by [NiWi09]. It is also

provide support for peripherals. Once  $\mu Clinux$  is downloaded into the hardware, the communication is done through USB Blaster JTAG cable.

# **Soft-core Processor**

The soft-core processor for the camera system is the Nios II processor.

# 4. Implementation

## 4.1. Camera Hardware Module

# 4.1.1. Technical specifications