# PQ7-M105IT Series

# User's Manual

Version 1.2

$Copyright @ Portwell, Inc., 2011. \ All \ rights \ reserved.$  All other brand names are registered trademarks of their respective owners.

## **Table of Contents**

How to Use This Manual

| Chapter 1 System Overview                              | 1-1               |

|--------------------------------------------------------|-------------------|

| 1.1 Introduction                                       | 1-1               |

| 1.2 Check List                                         |                   |

| 1.3 Product Specification                              | 1-2               |

| 1.4 Mechanical Drawing                                 | 1-3               |

| 1.5 System Architecture                                | 1-5               |

| Chapter 2 Hardware Configuration                       | 2-1               |

| 2.1 Jumper Setting                                     | 2-1               |

| 2.2 Jumper Setting of Portwell EVB Carrier             | 2-3               |

| 2.3 Connector Allocation of Portwell EVB Carrier       | 2-5               |

| Chapter 3                                              | 17                |

| 3.1 Atom™ Ultra low power CPU (E620/E640T/E660T/E680T) | 17                |

| 3.2 Intel® Platform Controller Hub EG20T               |                   |

| 3.3 Main Memory                                        | 17                |

| 3.4 Installing Q7 modules                              |                   |

| 3.4.1 Chipset Component Driver                         |                   |

| 3.4.2 Intel® Integrated Graphics                       |                   |

| 3.4.3 Intel® PROSet Gigabit Ethernet Controller        |                   |

| 3.4.4 Audio Controller                                 |                   |

| Chapter 4                                              | 20                |

| 4.1 Entering Setup Launch System Setup                 | 20                |

| 4.2 Main                                               |                   |

| 4.3 Advanced                                           | 22                |

| 4.4 Chipset                                            | 37                |

| 4.5 Boot                                               |                   |

| 4.6 Security                                           | 46                |

| 4.7 Save & Exit                                        | 47                |

| Chapter 5                                              | 49                |

| 5.1 Hardware Quick Installation                        | 50                |

| 5.1 Hardware Quick Installation                        | """"""" <u></u> % |

| 5.3 FAQ                                                | 52                |

Appendix A

Appendix B

### How to Use This Manual

The manual describes how to configure your PQ7-M105IT series to meet various operating requirements. It is divided into five chapters, with each chapter addressing a basic concept and operation of this Q<sub>SEVEN</sub> Module.

**Chapter 1 : System Overview.** Presents what you have in the box and give you an overview of the product specifications and basic system architecture for this model of single board computer.

**Chapter 2 : Hardware Configuration.** Describes the definition and location for Jumpers that you can easily configure your system.

**Chapter 3 : System Installation.** Describes the CPU, main memory SKU to get a clear information.

**Chapter 4 : BIOS Setup Information.** Specifies the meaning of each setup parameters, how to get advanced BIOS performance and update new BIOS. In addition, POST checkpoint list will give users some guidelines of trouble-shooting.

**Chapter 5 : Troubleshooting.** A quickly guide to start up your system development.

The content of this manual and EC declaration document is subject to change without prior notice. These changes will be incorporated in new editions of the document. **Portwell** may make supplement or change in the products described in this document at any time.

Updates to this manual, technical clarification, and answers to frequently asked questions will be shown on the following web site: <a href="http://www.portwell.com.tw">http://www.portwell.com.tw</a>

# Chapter 1 System Overview

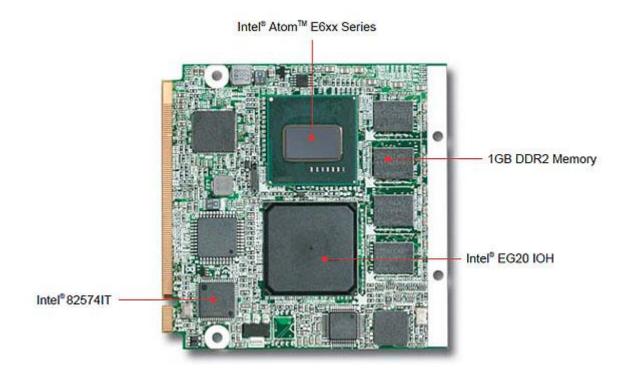

#### 1.1 Introduction

Q<sub>SEVEN</sub>, a new industrial computer platform in "Module board" and "Carrier board" architecture, equipped processor or its socket, chipset, memory or memory socket and single Ethernet controller on it. The On-The-Shelf Module board allows users to create their own Carrier board easily and quickly since most critical parts are ready on Module board. Q<sub>SEVEN</sub> Module board offers expansion interfaces such as PCI Express, SATA, LPC, LVDS, USB, SDVO and Audio etc. that could support variety functions depending on Carrier board design.

The Carrier board was customized design to fit in different mechanical requirements. In the meanwhile, its variety functions were also customized to meet the application. Compares to the platform that designed from nothing, Q<sub>SEVEN</sub> architecture platform only needs to develop Carrier board. Users could keep their know-how which related to their core competence in the Carrier board.

PQ7-M105IT series equipped Intel Tunnel Creek chipset with Atom E680T /E660T /E640T /E620 processor on-board), 512 MB DDR2 memories (up to 2GB) on-board, one Gigabit Ethernet controller on it to provide expansion interfaces – PCI Express x1.

#### 1.2 Check List

The PQ7-M105IT series package should cover the following basic items

One PQ7-M105IT series module board

If any of these items is damaged or missing, please contact your vendor and keep all packing materials for future replacement and maintenance.

### 1.3 Product Specification

- Main processor

- Intel® Atom Processor E680T/E660T/E640T/E620

- Main Memory

- Onboard DDR2 800 up to 2GB

- L2 Cache Memory

- 512K L2 Cache, Build-in processor

- Chipset

- Intel EG20T chipset

- Expansion Interfaces

- PCI Express

- Four PCI Express x1 links

- LVDS

- Supports maximum 80MHz single channel LVDS interface

- Single channel LVDS interface support: 24 bpp

- Maximum Panel resolution supported up to 1280 x 768

- SDVO (Serial Digital Video Output)

- A maximum pixel clock of 160 MHz is supported on the SDVO interface.

- Ethernet

- Intel 82574IT Gigabit Ethernet controller is equipped

- USB Interface

- Support eight USB 2.0 ports

- SATA Interface

- Support Two SATA ports with 3-Gbps Generation 2 and AHCI.

- Option NANDrive storage onboard, up to 32GB capacity.

- Outline Dimension (L X W):

- 70mm x 70mm

- Operating Temperature:

- 40°C ~ 85°C

- Storage Temperature:

- 40°C ~ 85°C

- Relative Humidity:

- $-5\% \sim 90\%$ , non-condensing

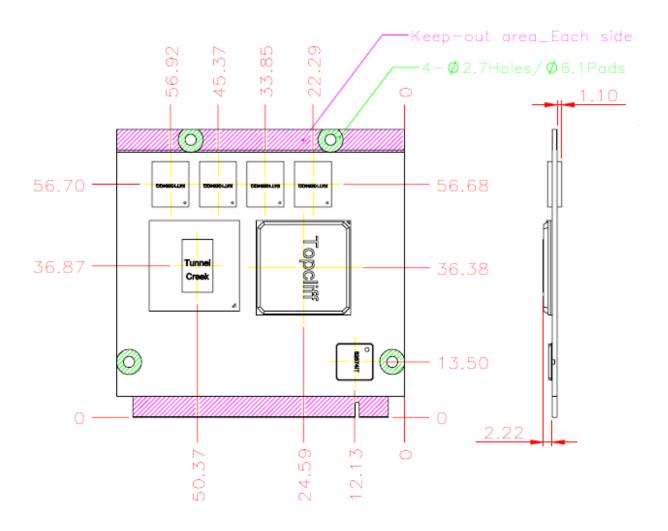

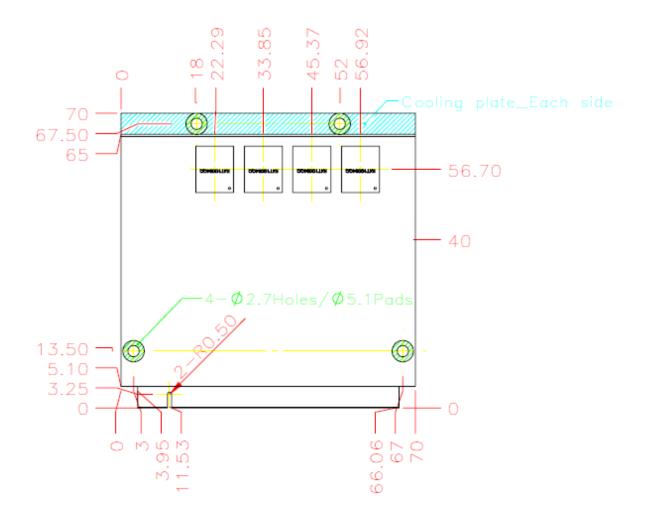

### 1.4 Mechanical Drawing

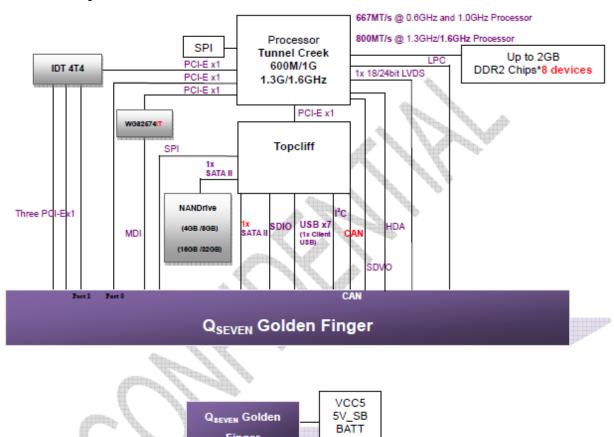

#### 1.5 **System Architecture**

PQ7-M105IT Series System Block Diagram

GND

Q<sub>SEVEN</sub> Golden Finger

### **Chapter 2**

### **Hardware Configuration**

This chapter gives the definitions and shows the positions of jumpers, headers and connector. The default settings shipped from factory are marked (\*).

2.1 Jumper Setting

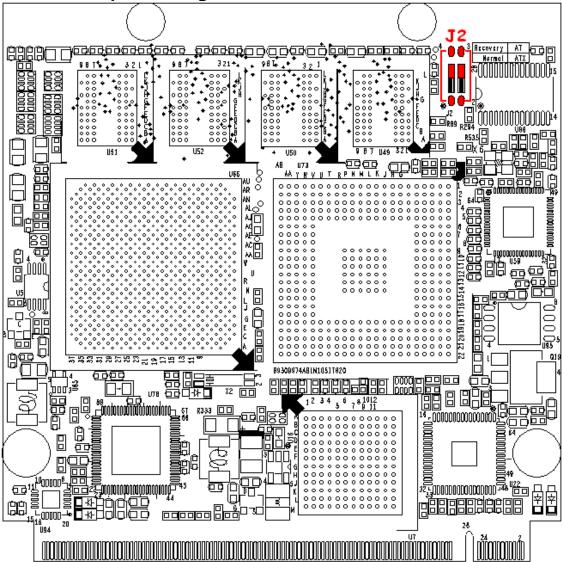

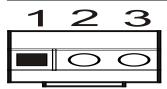

### **J2: BIOS Recovery select and AT ATX select**

**J2**: **BIOS** Recovery select and AT ATX select

| JP7    | Process Selection             |

|--------|-------------------------------|

| 1:ON   | BIOS recovery                 |

| 1: OFF | Normal Operation ★            |

| 2 : ON | Auto power up                 |

| 2:OFF  | Need Power Button to boot up★ |

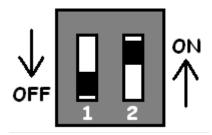

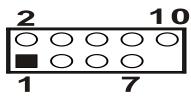

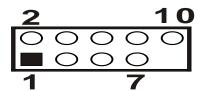

### 2.2 Jumper Setting of Portwell EVB Carrier

This section is the configuration jumpers on Portwell EVB Carrier. PQ7-M105IT is in the proper position.

Figure 2-1 PQ7-M105IT Jumper & Connector Location

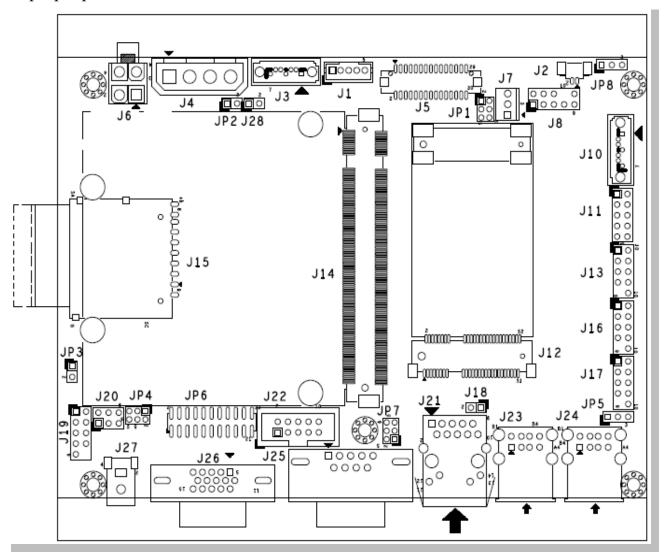

### JP1: LVDS Power Level

| JP1 | Process Selection |

|-----|-------------------|

| 1-3 | 3.3V ★            |

| 3-4 | 12V               |

| 3-5 | 5V                |

### JP2: CPU Board BIOS Disable

| JP2 | Function     |

|-----|--------------|

| 1-2 | BIOS Disable |

### JP3: Auto Power Button selection

| JP3 | Function               |

|-----|------------------------|

| 1-2 | Auto power button mode |

### JP4: RTC CMOS Clear Jumper Setting

| JP4       | Function       |

|-----------|----------------|

| 1-3 \ 2-4 | For com port ★ |

| 3-5 \ 4-6 | For IrDA       |

### JP5: USB Host/Client Select

| JP5 | Function |

|-----|----------|

| 1-2 | Host ★   |

| 2-3 | Client   |

#### JP6 : COM2 RS232/485/422 Selection

| JP6   | Function                            |

|-------|-------------------------------------|

| RS232 | 5-6,9-11,10-12,15-17,16-18 <b>★</b> |

| RS485 | 1-2,7-9,8-10,19-20                  |

| RS422 | 3-4,7-9,8-10,13-15,14-16,21-22      |

### JP7: LVDS Back-light Power Level

| JP7     | Process Selection |

|---------|-------------------|

| 1-3,2-4 | 5V, Active High ★ |

| 1-3,4-6 | 12V, Active High  |

| 3-5,2-4 | 5V, Active Low    |

| 3-5,4-6 | 12V, Active Low   |

### JP8: CMOS Reset

| JP8 | Function            |

|-----|---------------------|

| 1-2 | Normal Operation ★  |

| 2-3 | Clear CMOS Contents |

### 2.3 Connector Allocation of Portwell EVB Carrier

$\ensuremath{\mathrm{I/O}}$  peripheral devices are connected to the interface connectors.

### **Connector Function List**

| Connector | Function                                  | Remark |

|-----------|-------------------------------------------|--------|

| J1        | LVDS Panel Back-light Power Connector     |        |

| J2        | RTC Battery Connector                     |        |

| J3/10     | SATA Interface Connector                  |        |

| J4        | Power Header                              |        |

| J5        | LVDS Connector                            |        |

| J6        | 4P Power Connector for 12V                |        |

| J7        | 3P FAN Power Connector (System)           |        |

| J8        | Audio Header                              |        |

| J11       | 8-Bit GPIO Header                         |        |

| J12       | Mini-PCI E Connector                      |        |

| J13       | LPC Debug Port                            |        |

| J14       | MXM Connector                             |        |

| J15       | SD Card Slot                              |        |

| J16       | Dual Port USB Header (Only USB2.0 Device) |        |

| J17       | Client USB Header                         |        |

| J19       | Front Panel Control Header                |        |

| J20       | IrDA Connector                            |        |

| J21       | RJ45 Lan Port                             |        |

| J22       | COM2 Serial Port BOX Header               |        |

| J23/J24   | Dual Port USB                             |        |

| J25       | COM 1 Serial Port Connector               |        |

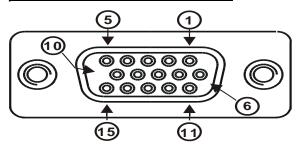

| J26       | D-Sub15 VGA Connector                     |        |

| J27       | DC Jack 12V                               |        |

| J28       | Reserve Header                            |        |

### **Pin Assignments of Connectors**

### J1: LVDS Panel Back-light Power Connector

| PIN No. | Signal Description |

|---------|--------------------|

| 1       | Backlight Power    |

| 2       | Ground             |

| 3       | +12V               |

| 4       | L_BKLTCTL          |

| 5       | +5V                |

### <u>J2 : RTC Battery Connector</u>

| PIN No. | Signal Description |  |

|---------|--------------------|--|

| 1       | Positive           |  |

| 2       | Negative           |  |

### J3/10: SATA Interface Connector

| PIN No. | Signal Description |           |  |

|---------|--------------------|-----------|--|

| 1       | GND                | GND       |  |

| 2       | SATA_TXP0          | SATA_TXP1 |  |

| 3       | SATA_TXN0          | SATA_TXN1 |  |

| 4       | GND                | GND       |  |

| 5       | SATA_RXN0          | SATA_RXN1 |  |

| 6       | SATA_RXP0          | SATA_RXP1 |  |

| 7       | GND                | GND       |  |

### J4: Power Header

| PIN No. |     | Signal Description |

|---------|-----|--------------------|

| 1       | V12 |                    |

| 2       | GND |                    |

| 3       | GND |                    |

| 4       | VCC |                    |

### **J5: LVDS Panel Connector**

| PIN No. | Signal Description | PIN No. | Signal Description |

|---------|--------------------|---------|--------------------|

| 1       | VDD_LVDS           | 2       | VDD_LVDS           |

| 3       | DF_LA_DATA+0       | 4       | DF_LA_DATA-0       |

| 5       | DF_LA_DATA+1       | 6       | DF_LA_DATA-1       |

| 7       | DF_LA_DATA+2       | 8       | DF_LA_DATA-2       |

| 9       | DF_LA_DATA+3       | 10      | DF_LA_DATA-3       |

| 11      | DF_LA_CLK+         | 12      | DF_LA_CLK-         |

| 13      | L_CTLA_CLK         | 14      | L_CTLB_DATA        |

| 15      | GND                | 16      | GND                |

| 17      | DF_LB_DATA+0       | 18      | DF_LB_DATA-0       |

| 19      | DF_LB_DATA+1       | 20      | DF_LB_DATA-1       |

| 21      | DF_LB_DATA+2       | 22      | DF_LB_DATA-2       |

| 23      | DF_LB_DATA+3       | 24      | DF_LB_DATA-3       |

| 25      | DF_LB_CLK+         | 26      | DF_LB_CLK-         |

| 27      | N/A                | 28      | N/A                |

| 29      | GND                | 30      | GND                |

### <u>J6: 4P Power Connector for 12V</u>

| PIN No. | Signal Description |

|---------|--------------------|

| 1       | Ground             |

| 2       | Ground             |

| 3       | +12V               |

| 4       | +12V               |

### J7: 3P FAN Power Connector

| PIN No. | Signal Description         |  |

|---------|----------------------------|--|

| 1       | Ground                     |  |

| 2       | +12V                       |  |

| 3       | Fan Speed Detecting signal |  |

### <u>J8 : Audio Header</u>

| PIN No. | Signal Description |

|---------|--------------------|

| 1       | CN_MIC-R           |

| 2       | AGND               |

| 3       | CN_MIC-L           |

| 4       | AGND               |

| 5       | CN_LINOUT-R        |

| 6       | NC                 |

| 7       | VCC                |

| 8       |                    |

| 9       | CN_LINOUT-L        |

| 10      | NC                 |

### J11:8-Bit GPIO Header

| PIN No. | Signal Description | PIN No. | Signal Description |

|---------|--------------------|---------|--------------------|

| 1       | SIO_GPIO0          | 2       | SIO_GPIO4          |

| 3       | SIO_GPIO1          | 4       | SIO_GPIO5          |

| 5       | SIO_GPIO2          | 6       | SIO_GPIO6          |

| 7       | SIO_GPIO3          | 8       | SIO_GPIO7          |

| 9       | Ground             | 10      | VCC                |

### J12: Mini-PCIE Slot

| PIN No. | Signal Description | PIN No. | Signal Description |

|---------|--------------------|---------|--------------------|

| 1       | PCIE_WAKE#         | 2       | VCC3               |

| 3       | N/C                | 4       | GND                |

| 5       | N/C                | 6       | VCC1_5             |

| 7       | CLKREQ#            | 8       | N/C                |

| 9       | GND                | 10      | N/C                |

| 11      | DF_CLK_PCIE#       | 12      | N/C                |

| 13      | DF_CLK_PCIE        | 14      | N/C                |

| 15      | GND                | 16      | N/C                |

| 17      | N/C                | 18      | GND                |

| 19      | N/C                | 20      | N/C                |

| 21      | GND                | 22      | RST#               |

| 23      | DF_PCIE_RXN1       | 24      | 3.3VAUX            |

| 25      | DF_PCIE_RXP1       | 26      | GND                |

| 27      | GND                | 28      | VCC1_5             |

| 29      | GND                | 30      | SMB_CLK            |

| 31      | DF_PCIE_TXN1       | 32      | SMB_DAT            |

| 33      | DF_PCIE_TXP1       | 34      | GND                |

| 35      | GND                | 36      | DF_USB_PN0         |

| 37      | N/C                | 38      | DF_USB_PP0         |

| 39 | N/C | 40 | GND    |

|----|-----|----|--------|

| 41 | N/C | 42 | N/C    |

| 43 | N/C | 44 | N/C    |

| 45 | N/C | 46 | N/C    |

| 47 | N/C | 48 | VCC1_5 |

| 49 | N/C | 50 | GND    |

| 51 | N/C | 52 | VCC3   |

### J13: LPC Debug Port

| PIN No. | Signal Description | PIN No. | Signal Description |

|---------|--------------------|---------|--------------------|

| 1       | LPC_AD0            | 2       | VCC3               |

| 3       | LPC_AD1            | 4       | RST#               |

| 5       | LPC_AD2            | 6       | LPC_FRAME#         |

| 7       | LPC_AD3            | 8       | CLK_LPC_FWH        |

| 9       |                    | 10      | GND                |

### <u>J14</u>: MXM Connector

| PIN No. | Signal Description       | PIN No. | Signal Description       |

|---------|--------------------------|---------|--------------------------|

| 1       | GND                      | 2       | GND                      |

| 3       | DF_LAN1_MDIN3            | 4       | DF_LAN1_MDIN2            |

| 5       | DF LAN1 MDIP3            | 6       | DF LAN1 MDIP2            |

| 7       | LAN1 LINK100-            | 8       | LAN1 LINK1000-           |

| 9       | DF_LAN1_MDIN1            | 10      | DF_LAN1_MDIN0            |

| 11      | DF_LAN1_MDIP1            | 12      | DF_LAN1_MDIP0            |

| 13      | LAN1_LINK#               | 14      | LAN1_ACT-                |

| 15      | VCTREF_GBE0_CT           | 16      | SLP_S5#                  |

| 17      | LPC_PME#                 | 18      | SLP_S3#                  |

| 19      | VSB3                     | 20      | PWRBTN#_PM               |

| 21      | SLP_BTN# (not implement) | 22      | LID_BTN# (not implement) |

| 23      | GND                      | 24      | GND                      |

| 25      | GND                      | 26      | PWROK_Q7                 |

| 27      | BATLOW# (not implement)  | 28      | RST_SYS#                 |

| 29      | DF_SATA0_TX+             | 30      | DF_SATA1_TX+             |

| 31      | DF_SATA0_TX-             | 32      | DF_SATA1_TX-             |

| 33      | SATA_ACT#                | 34      | GND                      |

| 35      | DF_SATA0_RX+             | 36      | DF_SATA1_RX+             |

| 37      | DF_SATA0_RX-             | 38      | DF_SATA1_RX-             |

| 39      | GND                      | 40      | GND                      |

| 41      | BIOS_DISABLE#            | 42      | SLOT2_CLK                |

| 43      | SLOT2_CD#                | 44      | SD2_LED                  |

| 45      | SLOT2_CMD                | 46      | SLOT2_WP                 |

| 47      | SD2PWR#                  | 48      | SLOT2_DATA1              |

| 49      | SLOT2_DATA0              | 50      | SLOT2_DATA3              |

| 51      | SLOT2_DATA2              | 52      | SLOT2_DATA5              |

| 53      | SLOT2_DATA4              | 54      | SLOT2_DATA7              |

| 55      | SLOT2_DATA6              | 56      | RSVD                     |

| 57      | GND                      | 58      | GND                      |

| 59      | HAD_SYNC                 | 60      | SMB_CLK                  |

| 61      | HAD_RST#                 | 62      | SMB_DATA                 |

| 63      | HAD_BITCLK               | 64      | SMB_ALERT#               |

| 65      | HAD_SDATAIN0             | 66      | I2C_CLK                  |

| 67      | HAD_SDATAOUT             | 68      | I2C_DAT                  |

| 69      | PM_THRM#                 | 70      | WDTRIG#                  |

| 71      | THERMTRIP#               | 72      | WDOUT (not implement)    |

| 73      | GND                      | 74      | GND                      |

| 75      | DF_USB_PN7               | 76      | DF_USB_PN6               |

| 77      | DF_USB_PP7               | 78      | DF_USB_PP6               |

| 79      | USB_6_7_OC#              | 80      | USB_4_5_OC#              |

| 81      | DF_USB_PN5               | 82      | DF_USB_PN4               |

| 83      | DF_USB_PP5               | 84      | DF_USB_PP4               |

| 85  | USB_2_3_OC                | 86  | USB_0_1_OC#                |  |

|-----|---------------------------|-----|----------------------------|--|

| 87  | DF_USB_PN3                | 88  | DF_USB_PN2                 |  |

| 89  | DF_USB_PP3                | 90  | DF_USB_PP2                 |  |

| 91  | USB_HOST_PRES#            | 92  | USB HC SEL                 |  |

| 93  | DF USB PN1                | 94  | DF USB PN0                 |  |

| 95  | DF_USB_PP1                | 96  | DF_USB_PP0                 |  |

| 97  | GND                       | 98  | GND                        |  |

| 99  | LA_DATAP0                 | 100 | LB_DATAPO (not implement)  |  |

| 101 | LA DATANO                 | 102 | LB_DATAN0 (not implement)  |  |

| 103 | LA_DATAP1                 | 104 | LB_DATAP1 (not implement)  |  |

| 105 | LA_DATAN1                 | 106 | LB_DATAN1 (not implement)  |  |

| 107 | LA_DATAP2                 | 108 | LB_DATAP2 (not implement)  |  |

| 109 | LA_DATAN2                 | 110 | LB_DATAN2 (not implement)  |  |

| 111 | L_VDDEN                   | 112 | L_BKLTEN                   |  |

| 113 | LA_DATAP3                 | 114 | LB_DATAP3 (not implement)  |  |

| 115 | LA_DATAN3                 | 116 | LB_DATAN3 (not implement)  |  |

| 117 | GND                       | 118 | GND                        |  |

| 119 | DF_LA_CLKP                | 120 | DF_LB_CLKP (not implement) |  |

| 121 | DF_LA_CLKN                | 122 | DF_LB_CLKN (not implement  |  |

| 123 | L_BKLTCTL                 | 124 | RSVD                       |  |

| 125 | LVDS_DID_DAT              | 126 | LVDS_BLC_DAT               |  |

| 127 | LVDS_DID_ CLK             | 128 | LVDS_BLC_CLK               |  |

| 129 | RSVD                      | 130 | RSVD                       |  |

| 131 | SDVO_CLK+                 | 132 | SDVO_INT+                  |  |

| 133 | SDVO_CLK-                 | 134 | SDVO_INT-                  |  |

| 135 | GND                       | 136 | GND                        |  |

| 137 | SDVO_GREEN+               | 138 | SDVO_FLDSTALL+             |  |

| 139 | SDVO_GREEN-               | 140 | SDVO_FLDSTALL-             |  |

| 141 | GND                       | 142 | GND                        |  |

| 143 | SDVO_BLUE+                | 144 | SDVO_TVCLKIN+              |  |

| 145 | SDVO_BLUE-                | 146 | SDVO_TVCLKIN-              |  |

| 147 | GND                       | 148 | GND                        |  |

| 149 | SDVO_RED+                 | 150 | SDVO_CTRLDATA              |  |

| 151 | SDVO_RED-                 | 152 | SDVO_CTRLCLK               |  |

| 153 | N/C                       | 154 | N/C                        |  |

| 155 | DF_CLK_PCIE+              | 156 | PCIE_WAKE#                 |  |

| 157 | DF_CLK_PCIE-              | 158 | RST#                       |  |

| 159 | GND                       | 160 | GND                        |  |

| 161 | PCIE_TX3+ (not implement) | 162 | PCIE_RX3+(not implement)   |  |

| 163 | PCIE_TX3- (not implement) | 164 | PCIE_RX3- (not implement)  |  |

| 165 | GND                       | 166 | GND                        |  |

| 167 | PCIE_TX2+ (not implement) | 168 | PCIE_RX2+(not implement)   |  |

| 169 | PCIE_TX2- (not implement) | 170 | PCIE_RX2- (not implement   |  |

| 171 | EXCD0_PERST#              | 172 | EXCD1_PERST#               |  |

| 173 | PCIE_TX1+                 | 174 | PCIE_RX1+                  |  |

| 175 | PCIE_TX1-                   | 176 | PCIE_RX1-                   |  |

|-----|-----------------------------|-----|-----------------------------|--|

| 177 | EXCD0_CPPE# (not implement) | 178 | EXCD1_CPPE# (not implement) |  |

| 179 | PCIE_TX0+                   | 180 | PCIE_RX0+                   |  |

| 181 | PCIE_TX0-                   | 182 | PCIE_RX0-                   |  |

| 183 | GND                         | 184 | GND                         |  |

| 185 | LPC_AD0                     | 186 | LPC_AD1                     |  |

| 187 | LPC_AD2                     | 188 | LPC_AD3                     |  |

| 189 | CLK_LPC_FWH                 | 190 | LPC_FRAME#                  |  |

| 191 | LPC_SERIRQ                  | 192 | LPC_LDRQ#(not implement)    |  |

| 193 | V3.3A_RTC                   | 194 | SPKR                        |  |

| 195 | FAN_TACHOIN (not implement) | 196 | FAN_PWMOUT (no implement    |  |

| 197 | GND                         | 198 | GND                         |  |

| 199 | RSVD                        | 200 | RSVD                        |  |

| 201 | RSVD (use for A20M#)        | 202 | RSVD                        |  |

| 203 | RSVD                        | 204 | MFG_N/C                     |  |

| 205 | VSB5                        | 206 | VSB5                        |  |

| 207 | MFG_N/C                     | 208 | MFG_N/C                     |  |

| 209 | MFG_N/C                     | 210 | MFG_N/C                     |  |

| 211 | VCC                         | 212 | VCC                         |  |

| 213 | VCC                         | 214 | VCC                         |  |

| 215 | VCC                         | 216 | VCC                         |  |

| 217 | VCC                         | 218 | VCC                         |  |

| 219 | VCC                         | 220 | VCC                         |  |

| 221 | VCC                         | 222 | VCC                         |  |

| 223 | VCC                         | 224 | VCC                         |  |

| 225 | VCC                         | 226 | VCC                         |  |

| 227 | VCC                         | 228 | VCC                         |  |

| 229 | VCC                         | 230 | VCC                         |  |

J15: SD Card Slot

| PIN No. | Signal Description |

|---------|--------------------|

| 1       | DAT3               |

| 2       | CMD_RSP            |

| 3       | GND                |

| 4       | VCC                |

| 5       | CLK                |

| 6       | GND                |

| 7       | DAT0               |

| 8       | DAT1               |

| 9       | DAT2               |

| Sa      | WP#                |

| Sb      | CD#                |

| Sc      | CD#_COM            |

### J16: Dual Port USB Header(Only USB2.0 Device)

| PIN No. | Signal Description | PIN No. | Signal Description |  |

|---------|--------------------|---------|--------------------|--|

| 1       | +5V                | 2       | +5V                |  |

| 3       | USBD6N             | 4       | USBD7N             |  |

| 5       | USBD6P             | 6       | USBD7P             |  |

| 7       | Ground             | 8       | Ground             |  |

|         |                    | 10      | NC                 |  |

### J17: Client USB Header

| PIN No. | Signal Description | PIN No. | Signal Description |

|---------|--------------------|---------|--------------------|

| 1       | +5V                | 2       | NC                 |

| 3       | USBD1N             | 4       | NC                 |

| 5       | USBD1P             | 6       | NC                 |

| 7       | Ground             | 8       | NC                 |

|         |                    | 10      | NC                 |

### J19: Front panel Connector

| PIN No. | Signal Description | PIN No. | Signal Description |  |

|---------|--------------------|---------|--------------------|--|

| 1       | HD_LED_P           | 2       | FP PWR/SL_P        |  |

| 3       | HD_LED_N           | 4       | FP PWR/SL_N        |  |

| 5       | RST_SW_N           | 6       | PWR_SW_P           |  |

| 7       | RST_SW_P           | 8       | PWR_SW_N           |  |

| 9       | RSVD_DNU           | 10      |                    |  |

### J20: IrDA Connector

| PIN No. | Signal Description |  |  |

|---------|--------------------|--|--|

| 1       | IRRX               |  |  |

| 2       | Ground             |  |  |

| 3       | Ground             |  |  |

| 4       | NC                 |  |  |

| 5       | IRTX               |  |  |

| 6       | VCC                |  |  |

### J21: RJ45 LAN Port

| PIN No. | Signal Description |

|---------|--------------------|

| 1       | L1_MDIP0           |

| 2       | L1_MDIN0           |

| 3       | L1_MDIP1           |

| 4       | L1_MDIN1           |

| 5       | VCTREF_GBE0_CT     |

| 6       | GND                |

| 7       | L1_MDIP2           |

| 8       | L1_MDIN2           |

| 9       | L1_MDIP3           |

| 10      | L1_MDIN3           |

| 11      | LAN1_ACT-          |

| 12      | LAN1_LINK#         |

| 13      | LAN1_LINK1000-     |

| 14      | LAN1_LINK100-      |

### J22: COM2 Serial Port BOX Header

| PIN No. | Signal Description | PIN No. | Signal Description |

|---------|--------------------|---------|--------------------|

| 1       | DCD#2              | 2       | DSR#2              |

| 3       | RXD#2              | 4       | RTS#2              |

| 5       | TXD#2              | 6       | CTS#2              |

| 7       | DTR#2              | 8       | RI#2               |

| 9       | GND                | 10      |                    |

### J23: Dual Port USB

| PIN No. | Signal Description | PIN No. | Signal Description |

|---------|--------------------|---------|--------------------|

| A1      | +5V                | B1      | +5V                |

| A2      | USBD3N             | B2      | USBD2N             |

| A3      | USBD3P             | В3      | USBD2P             |

| A4      | Ground             | B4      | Ground             |

### J24: Dual Port USB

| PIN No. | Signal Description | PIN No. | Signal Description |  |

|---------|--------------------|---------|--------------------|--|

| A1      | +5V                | B1      | +5V                |  |

| A2      | USBD5N             | В2      | USBD4N             |  |

| A3      | USBD5P             | В3      | USBD4P             |  |

| A4      | Ground             | B4      | Ground             |  |

### <u>J25 : COM 1 Serial Port Connector</u>

| PIN No. | Signal Description        |        |        |  |

|---------|---------------------------|--------|--------|--|

|         | RS-232                    | RS-422 | RS-485 |  |

| 1       | DCD (Data Carrier Detect) | TX-    | DATA-  |  |

| 2       | RXD (Receive Data)        | TX+    | DATA+  |  |

| 3       | TXD (Transmit Data)       | RX+    | N/C    |  |

| 4       | DTR (Data Terminal Ready) | RX-    | N/C    |  |

| 5       | GND (Ground)              | GND    | GND    |  |

| 6       | DSR (Data Set Ready)      | N/C    | N/C    |  |

| 7       | RTS (Request to Send)     | N/C    | N/C    |  |

| 8       | CTS (Clear to Send)       | N/C    | N/C    |  |

| 9       | RI/5V/12V                 | N/C    | N/C    |  |

### J26: D-SUB15 VGA Connector

| PIN No. | Signal Description | PIN No. | Signal Description |

|---------|--------------------|---------|--------------------|

| 1       | RED                | 2       | GREEN              |

| 3       | BLUE               | 4       | ID0                |

| 5       | Ground             | 6       | Ground             |

| 7       | Ground             | 8       | Ground             |

| 9       | NC                 | 10      | Ground             |

| 11      | ID1                | 12      | DDCDATA            |

| 13      | HSYNC              | 14      | VSYNC              |

| 15      | DDCCLK             |         |                    |

### **J27 : DC Jack 12V**

| PIN No. | Signal Description |  |  |

|---------|--------------------|--|--|

| 2       | V12CON_IN          |  |  |

| 3       | GND                |  |  |

| 4       | GND                |  |  |

### **Chapter 3**

#### **System Installation**

This chapter provides the instructions to set up the system. The additional information is enclosed to help you set up onboard devices

### 3.1 Atom™ Ultra low power CPU (E620/E640T/E660T/E680T)

Depending on ordering models, PQ7-M105 equips Intel® ATOM E620/ E640T/ E660T/E680T CPU, it's an ultra low power consumption CPU. Alone with module type board and wide-temperature capability, it is suitable for various kind of applications.

It's an All-In-One CPU solution which also includes the function of Intel® Integrated Graphic and PCI-Express signals.

#### 3.2 Intel® Platform Controller Hub EG20T

PQ7-M105 uses EG20T as IOH. It supports SATA II, USB, I2C BUS and CAN BUS, which is default supported by EG20T without adding any add-on card.

### 3.3 Main Memory

PQ7-M105 has on-board soldered memory chip. It's DDR2 800 Mhz with 512MB, 1GB and 2GB. Memory clock and related settings can be detected by BIOS.

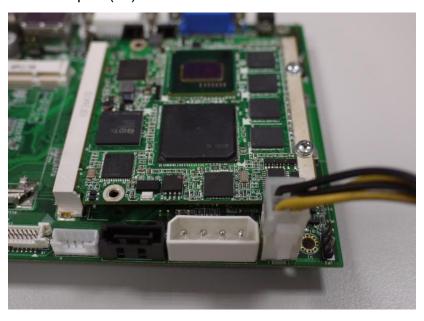

### 3.4 Installing Q7 modules.

To install your PQ7-M105 standard chassis or proprietary environment, please perform the following:

- Step 1: Check all jumpers setting on proper position of the carrier board.

- Step 2: Install PQ7-M105 onto carrier board and screwed Q7 slots.

- Step 3: Place PQ7-M105 into the dedicated position in the system

- Step 4: Attach cables to existing peripheral devices and secure it

#### WARNING

Please ensure that SBC is properly inserted and fixed by mechanism.

#### Note:

Please refer to section 3.3.1 to 3.3.7 to install INF/VGA/LAN/Audio drivers.

#### 3.4.1 Chipset Component Driver

PQ7-M105 uses state-of-art Intel® EG20T PCH chipset. It's a new chipset that some old operating systems might not be able to recognize. To overcome this compatibility issue, for previous Windows Operating Systems such as Windows XP, please install its INF before any of other Drivers are installed. You can find very easily this chipset component driver in PQ7-M105 CD-title.

Moreover, if using some old OS, the driver may not be supported anymore. We recommend changing the different OS to comply with this new chipset.

#### 3.4.2 Intel® Integrated Graphics.

With latest ATOM series structure, PQ7-M105 has integrated graphic built-in CPU. Therefore Intel® Integrated Graphic supports sharing on board physical memories. PQ7-M105 has internal LVDS & SDVO signal depending on the design of carrier board. This combination makes PQ7-M105 an excellent piece of multimedia hardware.

With no additional video adaptor, this onboard video will usually be the system display output. By adjusting the BIOS setting to disable on-board VGA, an add-on PCI-Express Graphic card can take over the system display.

#### **Drivers Support**

Please find all the drivers in the PQ7-M105 CD-title. Drivers support, Windows XP/VISTA/Win7.

#### 3.4.3 Intel® PROSet Gigabit Ethernet Controller

#### **Drivers Support**

Please find Intel® WG82574IT driver in /Ethernet directory of PQ7-M105 CD-title. The drivers support Windows XP/Vista/Win7.

#### 3.4.4 Audio Controller

Please find Intel® High Definition Audio driver form PCOM-B216VG-VI CD-title. The drivers support Windows 2000 /XP/Vista/Win7.

### **Chapter 4**

#### **BIOS Setup Information**

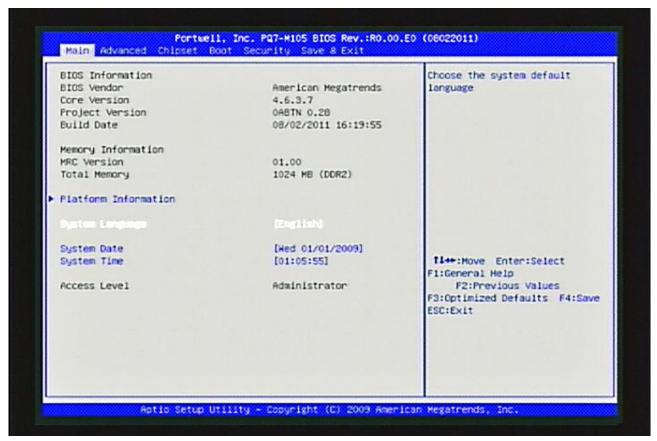

PQ7-M105 is equipped with the UEFI AMI BIOS stored in SPI Flash ROM. These BIOS has a built-in Setup program that allows users to modify the basic system configuration easily. This type of information is stored in NVRAM so that it is retained during power-off periods. When system is turned on, PQ7-M105 communicates with peripheral devices and checks its hardware resources against the configuration information stored in the CMOS memory. If any error is detected, or the CMOS parameters need to be initially defined, the diagnostic program will prompt the user to enter the SETUP program. Some errors are significant enough to abort the start up.

### 4.1 Entering Setup -- Launch System Setup

Power on the computer and the system will start POST (Power On Self Test) process. When the message below appears on the screen, press <Del> key will enter BIOS setup screen.

#### Press <Del> to enter SETUP

If the message disappears before responding and still wish to enter Setup, please restart the system by turning it OFF and On or pressing the RESET button. It can be also reset by pressing <Ctrl>, <Alt>, and <Delete> keys on keyboard simultaneously.

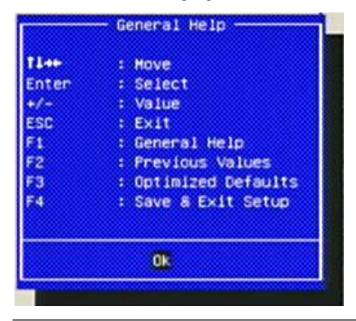

#### Press <F1> to Run SETUP or Resume

The BIOS setup program provides a General Help screen. The menu can be easily called up from any menu by pressing <F1>. The Help screen lists all the possible keys to use and the selections for the highlighted item. Press <Esc> to exit the Help screen.

#### 4.2 Main

Use this menu for basic system configurations, such as time, date etc.

#### **BIOS**

#### **BIOS Information, Memory Information**

These items show the firmware and memory specifications of your system. Read only.

#### **System Time**

The time format is <Hour> <Minute> <Second>. Use [+] or [-] to configure system Time.

#### **System Date**

The date format is <Day>, <Month> <Date> <Year>. Use [+] or [-] to configure system Date.

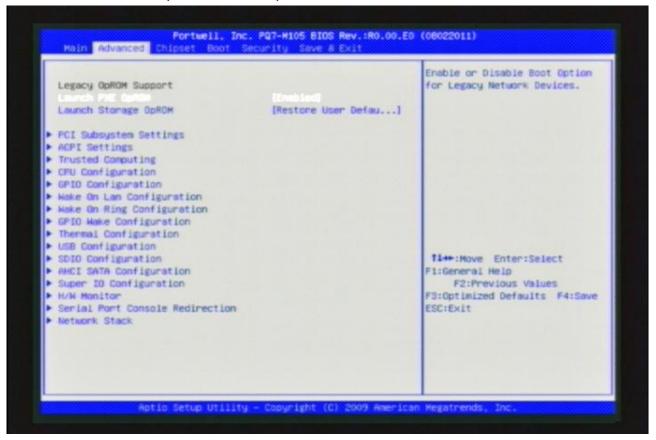

#### 4.3 Advanced

Use this menu to set up the items of special enhanced features.

#### Launch PXE OpROM

Enable of Disable Boot Option for Legacy Network Devices to have the ability booting up via Ethernet.

Choices: Disabled, Enabled.

#### **Launch Storage OpROM**

Enable of Disable Boot Option for Legacy Mass Storage devices.

If there is an add-on card with storage ROM, this option must set to enable.

Choices: Disabled, Enabled.

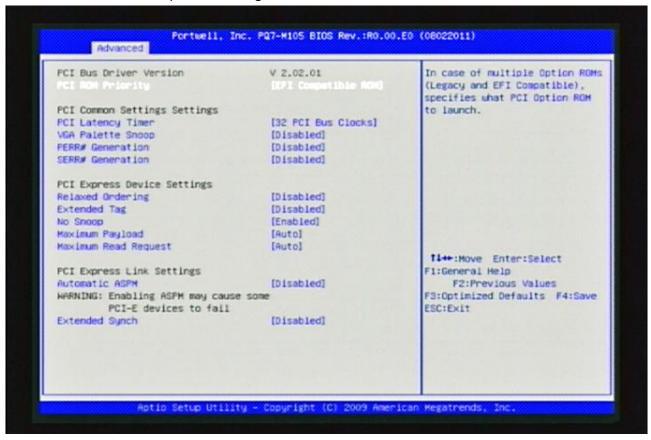

#### **PCI Subsystem Settings**

PCI, PCI-X and PCI Express Settings

#### **PCI ROM Priority**

In case of multiple Options (Legacy and EFI Compatible), specifies what PCI Option ROM to launch.

Choices: EFI Compatible ROM, Legacy ROM

#### **PCI Latency Timer**

Value to be programmed into PCI Latency Timer Register.

Choices: 32 PCI, 64 PCI, 96 PCI, 128 PCI, 160 PCI, 192 PCI, 224 PCI, 248 PCI Bus Clocks.

#### **VGA Palette Snoop**

Enable or Disable VGA Palette Register Snooping

Choices: Disabled, Enabled.

#### **PERR# Generation**

Enable or Disable PCI Device to generate PERR#

Choices: Disabled, Enabled.

#### **SERR# Generation**

Enable or Disable PCI Device to generate SERR#

Choices: Disabled, Enabled.

#### **Relaxed Ordering**

Enables or Disables PCI Express Device Relaxed ordering.

Choices: Disabled, Enabled.

#### **Extended Tag**

If Enable allows Device to use 8-bit Tag field as a requester

Choices: Disabled, Enabled.

#### No Snoop

Enables or Disables PCI Express No Snoop option.

Choices: Disabled, Enabled.

#### **Maximum Payload**

Set Maximum Payload of PCI Express or allow system BIOS to select the value.

Choices: Auto, 128 Bytes, 256 Bytes, 512 Bytes, 1024 Bytes, 2048 Bytes, 4096 Bytes.

#### **Maximum Read Request**

Set Maximum Read request size of PCI Express or allow system BIOS to select the value.

Choices: Auto, 128 Bytes, 256 Bytes, 512 Bytes, 1024 Bytes, 2048 Bytes, 4096 Bytes.

#### **ASPM Support**

Automatically Enable ASPM based on reported capabilities and known issues.

Choices: Disabled. Auto, Force L0.

#### **Extended Synch**

If Enabled allows generation of Extended Synchronization patterns.

Choices: Disabled, Enabled.

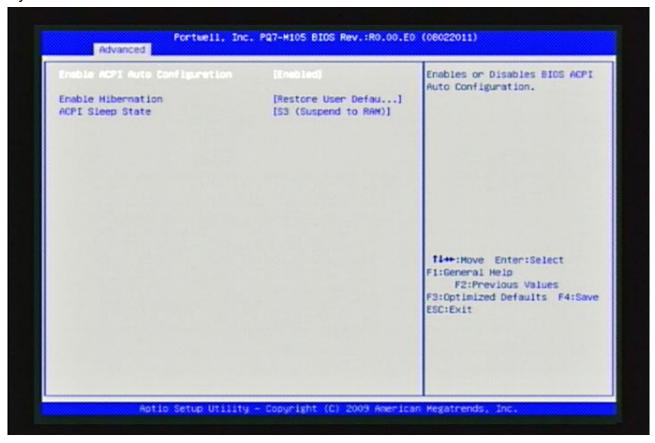

#### **ACPI Settings**

System ACPI Parameters.

#### **Enable ACPI Auto Configuration**

Enables or Disables BIOS ACPI Auto configuration.

Choices: Enabled, Disabled.

#### **Enable Hibernation**

Enables or Disables system ability to Hibernation (OS/S4 Sleep state).

This option may not be effective with some OS.

Choices: Enabled, Disabled.

#### **ACPI Sleep State**

Select the highest ACPI sleep state that the system will enter when SUSPEND button is pressed.

Choices: Suspend Disabled, S1 (CPU Stop Clock), S3 (Suspend to RAM).

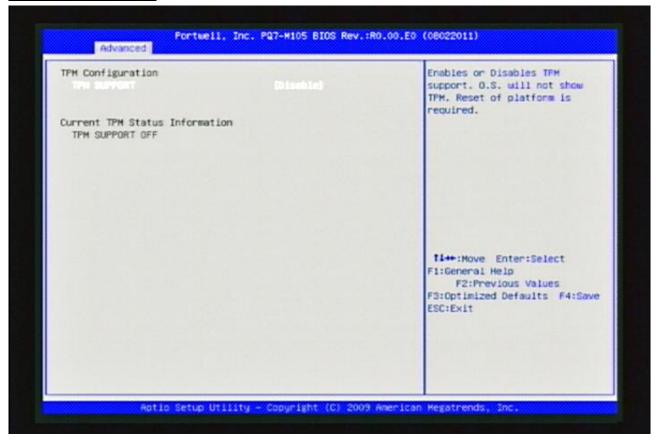

### **Trusted Computing**

### **TPM SUPPORT**

Enable or disable TPM Support

Choices: Enabled, Disabled.

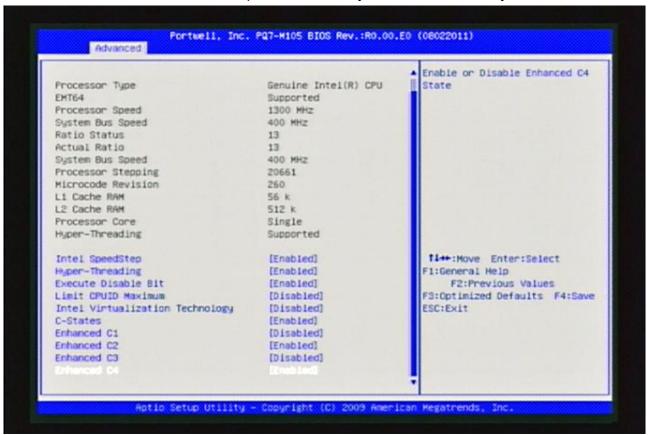

#### **CPU Configuration**

These items show the advanced specifications of your CPU. Read only.

#### Intel SpeedStep

Enables or Disables Intel® SpeedStep™

Choices: Disabled, Enabled

#### **Hyper-Threading**

Enables for Windows XP and Linux (OS optimized for Hyper-Threading Technology) and Disabled for other OS (OS that's not optimized for Hyper-Threading Technology)

Choices: Disabled, Enabled

#### **Execute Disable Bit**

XD can prevent certain classes of malicious buffer overflow attacks when combined with a supporting OS (Windows Server 2003 SP1, Windows XP SP2, SuSE Linux 9.2, RedHat Enterprise 3 update3.)

Choices: Disabled, Enabled

#### **Limit CPUID Maximum**

Disabled for Windows XP.

Choices: Disabled, Enabled

#### **Intel Virtualization Technology**

When enabled, a VMM can utilized the additional hardware capabilities provided by Vandorpool Technology.

Choices: Disabled, Enabled

#### **C-States**

Enables or Disables C2 and above.

Choices: Disabled, Enabled

#### **Enhanced C1**

Enables or Disables Enhanced C1 state.

Choices: Disabled, Enabled

#### **Enhanced C2**

Enables or Disables Enhanced C2 state

Choices: Disabled, Enabled

#### **Enhanced C3**

Enables or Disables Enhanced C3 state

Choices: Disabled, Enabled

#### **Enhanced C4**

Enables or Disables Enhanced C4 state

Choices: Disabled, Enabled

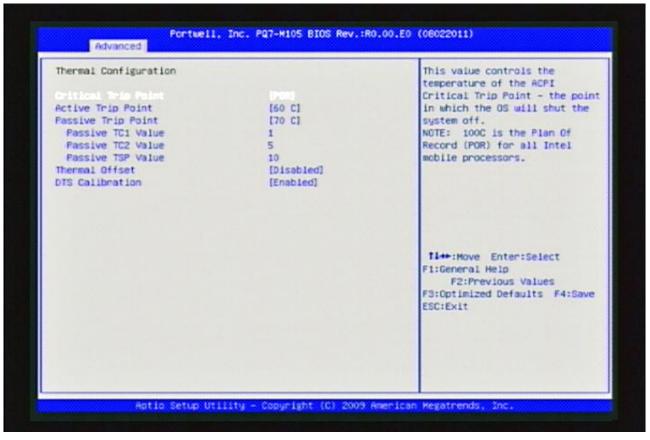

# **Thermal Confighration**

**Thermal Configuration Parameters**

# **Critical Trip Point**

This value controls the temperature of the ACPI Critical Trip Point – the point in which the OS will shut the system off.

Choices: POR, 30, 40, 50, 60, 70, 80, 90, 95 C

# **Active Trip Point**

This value controls the temperature of the ACPI active Trip Point – the point in which the OS will turn the processer fan on.

Choices: Disabled, 30, 40, 50, 60, 70, 80, 90, 95, 100 C

### **Passive Trip Point**

This value controls the temperature of the ACPI Passive Trip Point – the point in which the OS will begin throttling the processer.

Choices: Disabled, 30, 40, 50, 60, 70, 80, 90, 95, 100 C

### **Passive TC1 Value**

This value sets the TC1 value for the ACPI Passive Cooling Formula. Range 1-16

Choices: 1-16

### Passive TC2 Value

This value sets the TC2 value for the ACPI Passive Cooling Formula. Range 1-16

Choices: 1-16

### **Passive TSP Value**

This item sets the TSP value for the ACPI Passove cooling formula. It represesents in thenths of a second how often the OS will read the temperature when passive colling is enabled. Range 2-32

Choices: 2-32

### **Thermal Offset**

Whether Thermal offset (Read from CPU MSK 03Fh) is used by the KSC to adjust thermal management.

Choices: Disabled, Enabled

### **DTS Calibration**

Enable or disable DTS Calibration.

Choices: Disabled, Enabled

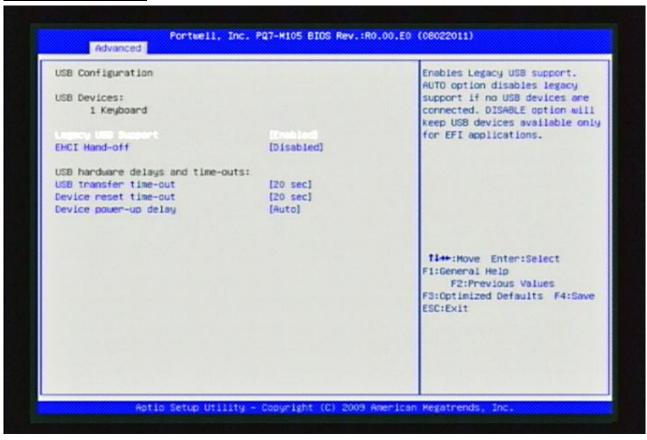

### **USB Configuration**

# **Legacy USB Support**

Enable Legacy USB support. AUTO option disables legacy support if no USB devices are connected Disabled option will keep USB devices available only for EFI applications.

Choices: Disabled, Enabled

### **EHCI Hand-off**

This is workaround for OS without EHCI hand-off support. The EHCI ownership changing should be claimed by EHCI driver.

Choices: Disabled, Enabled

### **USB Transfer time-out**

The time-out value for Control, Bulk and Interrupt transfers.

Choices: 1, 5, 10, 20 sec

### **Device reset time-out**

USB mass storage device start unit command time-out

Choices: 10, 20, 30, 40 sec

# **Device power-up delay**

Maximum time the device will take before it properly reports itself to the Host controller. 'AUTO' uses default value: for a Root port is 100 ms, for a Hub port, the delay is taken from Hub descriptor.

Choices: Auto, Manual

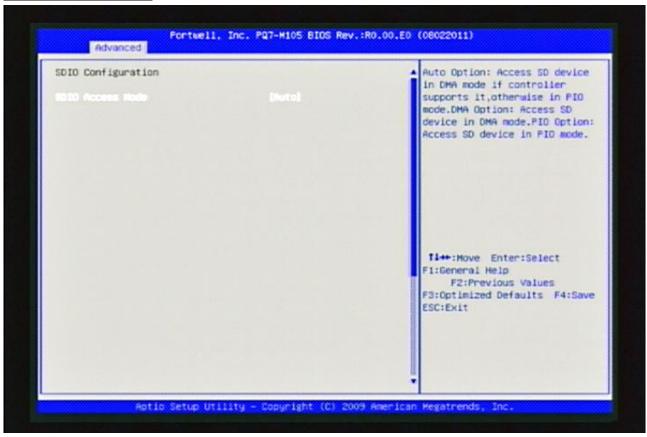

# **SDIO Configuration**

### **SDIO Access Mode**

Auto option: Access SD device in DMA mode if controller supports it, otherwise in PIO mode. DMA option: Access SD device in DMA mode. PIO option: Access SD device in PIO mode.

Choices: Auto, DMA, PIO

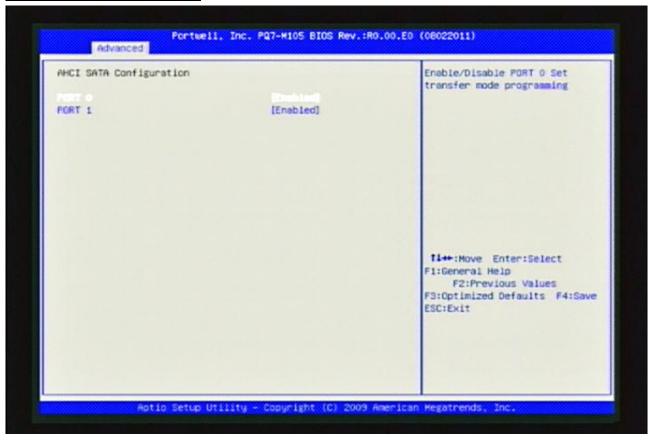

# **AHCI SATA Configuration**

# Port 0

Enables or disables PORT 0 set transfer mode programming.

Choices: Disabled, Enabled

# Port 1

Enables or disables PORT 0 set transfer mode programming.

Choices: Disabled, Enabled

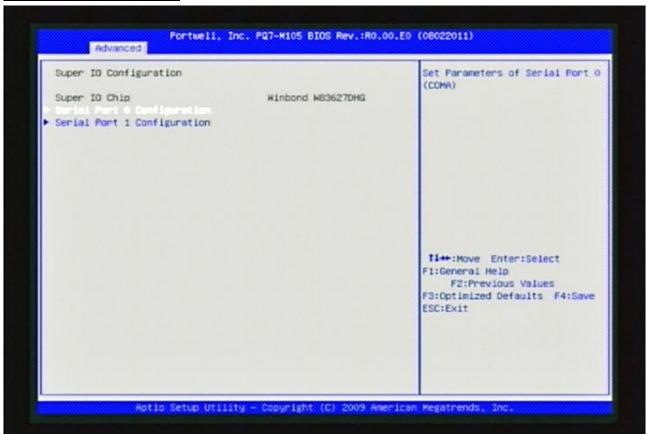

# **Super IO Configuration**

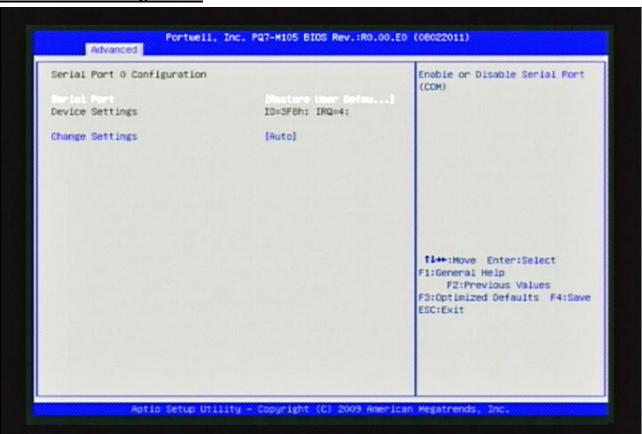

# **Serial Port 0 Configuration**

### **Serial Port**

Choices: Disabled, Enabled

# **Change Settings**

Choices: Auto, IO=3F8h; IRQ=4;

IO=3F8h; IRQ=3, 4, 5, 6, 7, 9, 10, 11, 12; IO=2F8h; IRQ=3, 4, 5, 6, 7, 9, 10, 11, 12; IO=3E8h; IRQ=3, 4, 5, 6, 7, 9, 10, 11, 12; IO=2E8h; IRQ=3, 4, 5, 6, 7, 9, 10, 11, 12;

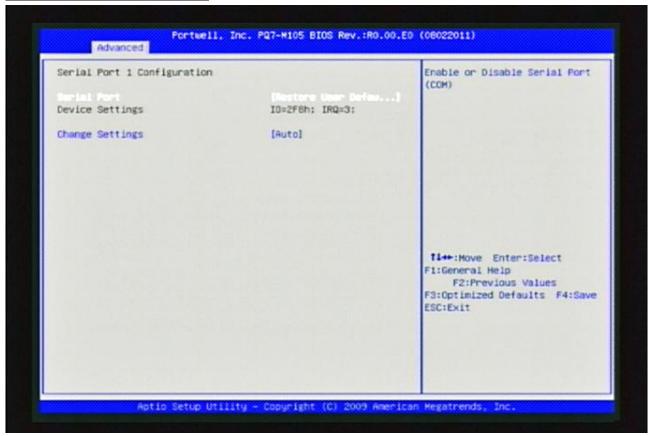

### **Serial Port 1 Configuration**

### **Serial Port**

Choices: Disabled, Enabled

### **Change Settings**

Choices: Auto, IO=2F8h; IRQ=3;

IO=3F8h; IRQ=3, 4, 5, 6, 7, 9, 10, 11, 12; IO=2F8h; IRQ=3, 4, 5, 6, 7, 9, 10, 11, 12; IO=3E8h; IRQ=3, 4, 5, 6, 7, 9, 10, 11, 12; IO=2E8h; IRQ=3, 4, 5, 6, 7, 9, 10, 11, 12;

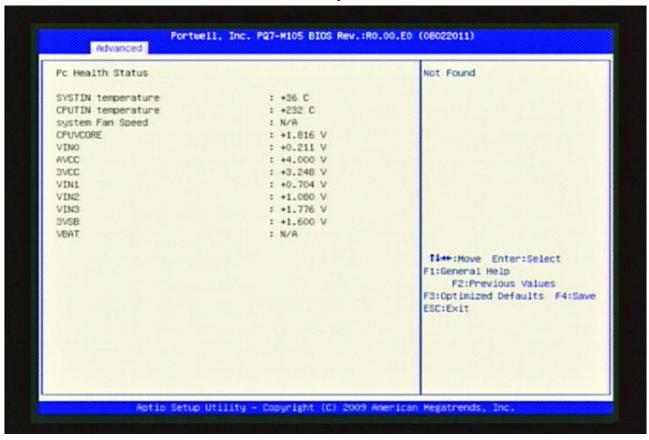

# **H/W Monitor**

This section shows the status of SBC, read only

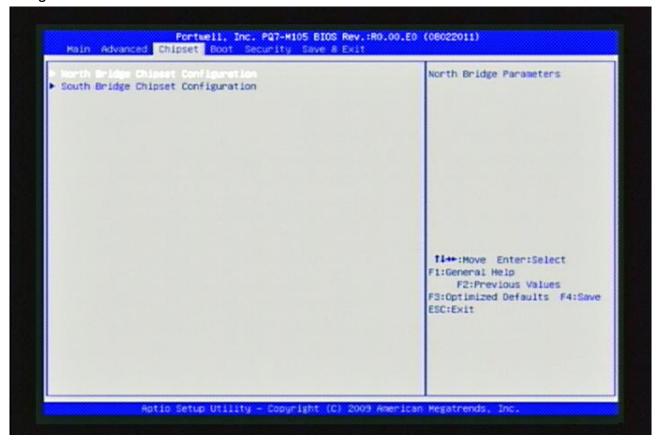

# 4.4 Chipset

This menu controls the advanced features of the onboard Host Bridge and South Bridge.

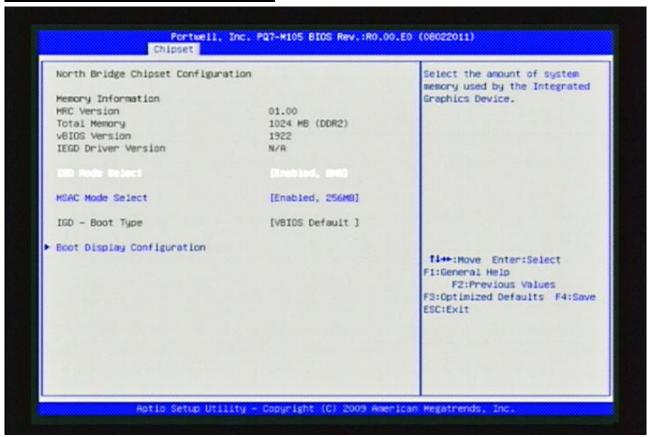

# **North Bridge Chipset Configuration**

### **IGD Mode Select**

Select the amount of system memory used by the ntegrated Graphics Device.

Choices: Disabled, Enabled 1MB, 4MB, 8MB, 16MB, 32MB, 48MB, 64MB

### **MSAC Mode Select**

Select the size of the graphic memory aperture and untrused space. Used by the Integrated Graphics Device.

Choices: Enabled 128MB, 256MB, 512MB

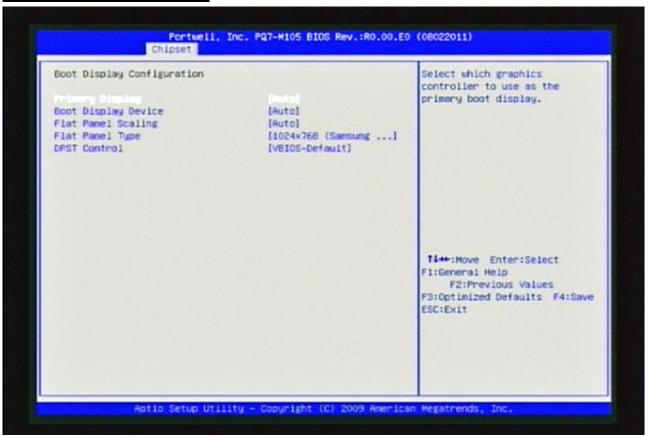

### **Boot Display Configuration**

# **Primary Display**

Select which graphics controller to use as the primary boot display.

Choices: Auto, IGD, PEG

# **Boot Display Device**

Choices: Auto, Integrated LVDS, External DVI/HDMI, External TV, External CRT, External LVDS

### Flat Panel Scaling

ChoicesL Auto, Focred, Disabled

### **Flat Panel Type**

Choices: 640x480 (generic), 800x600 (generic), 1024x768 (generic), 640x480 (NEC 8.4"), 800x600 (NEC 9"), 1026x600 (TMD 5.61"), 1026x600 (Samsung 4.8"), 1024x768 (Samsung 15"), 1280x768 (Sharp 7.2"), 1280x800 (Samsung 15.4")

### **DPST Control**

Choices: VBIOS-Default, DPST Disabled, DPST Enabled L1, L2, L3, L4, L5

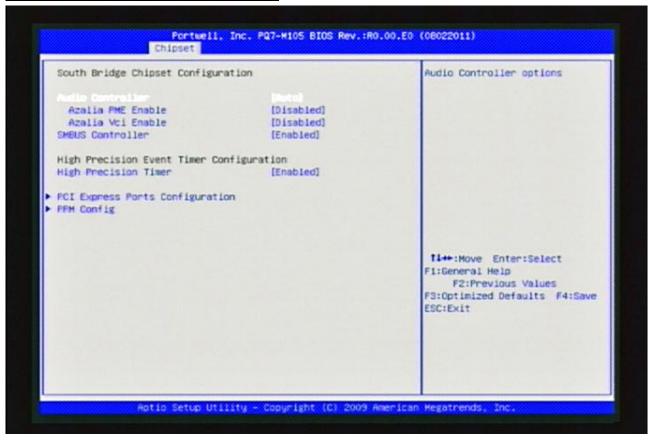

# **South Bridge Chipset Configuration**

# **Audio Controller**

Audio Controller options

Choices: Auto, Disabled, Enabled,

# **SMbus Controller**

SMbus controller options

Choices: Disabled, Enabled

# **High Precision Timer**

Enables or Disables the High Precision event timer.

Choices: Disabled, Enabled

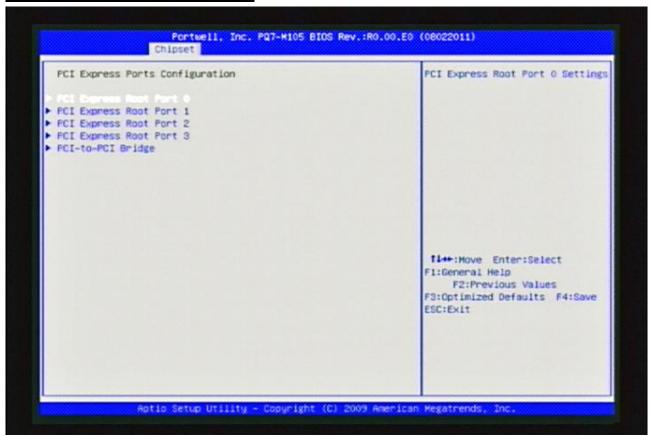

### **PCI Express Ports Configuration**

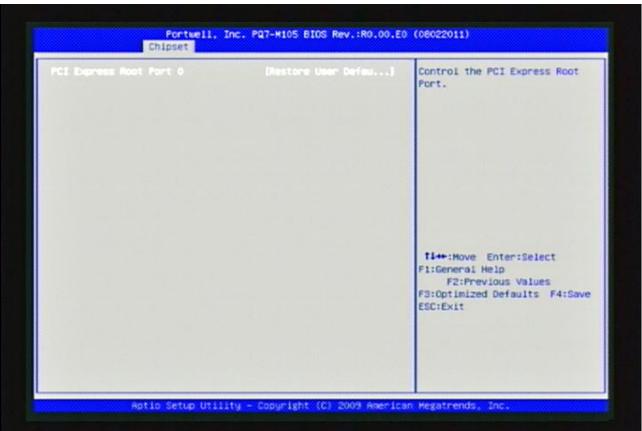

# PCI Express Root Port 0~3 (Settings are all the same)

# **PCI Express Root Port**

Choices: Enabled, Disabled

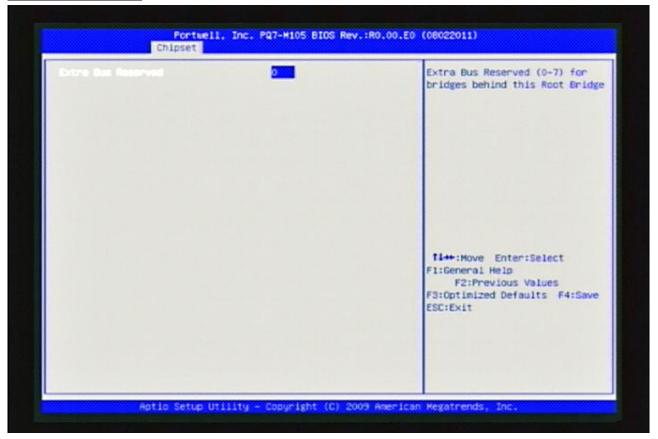

# PCI-to-PCI Bridge

# **Extra Bus Reserved**

Extra Bus reserved (0-7) for bridges behind this Root bridge.

Choices: 0-7

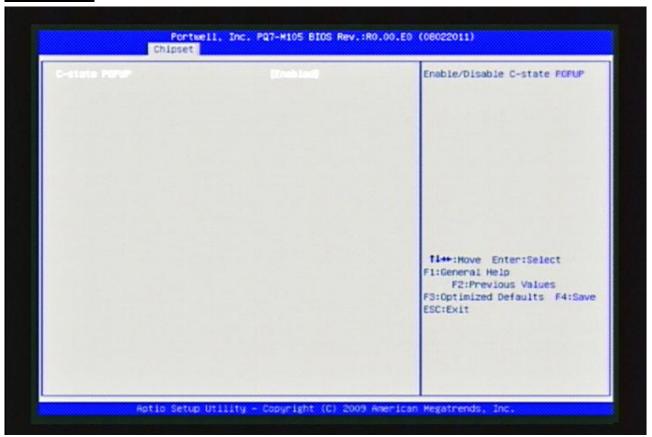

# **PPM Config**

# **C-State POPUP**

Enables or disables C-state POPUP.

Choices: Enabled, Disabled

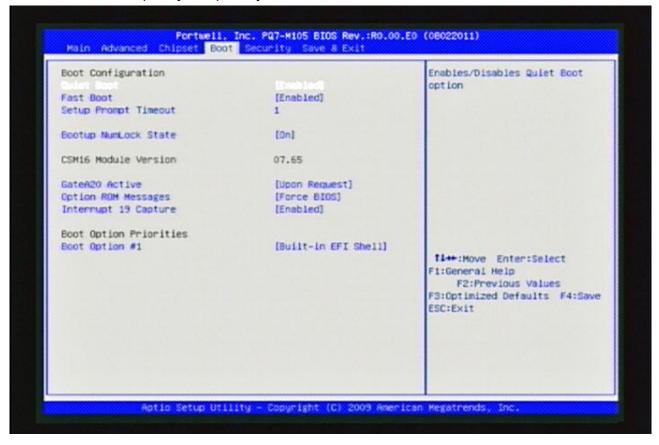

#### 4.5 Boot

Use this menu to specify the priority of boot devices.

### **Quiet Boot**

This BIOS feature determines if the BIOS should hide the normal POST messages with the motherboard or system manufacturer's full-screen logo. When it is enabled, the BIOS will display the full-screen logo during the boot-up sequence, hiding normal POST messages.

Please note that enabling this BIOS feature often adds 2-3 seconds of delay to the booting sequence. This delay ensures that the logo is displayed for a sufficient amount of time. Therefore, it is recommended that you disable this BIOS feature for a faster boot-up time.

Choices: Disabled, Enabled.

#### **Fast Boot**

Enabling this setting will cause the BIOS POST routine to skip some of its tests during boot up for faster system boot.

Choices: Disabled, Enabled.

### **Setup Prompt Timeout**

Choices: 1-65535

### **Boot Up Num-Lock State**

This setting is to set the Num Lock status when the system is powered on. Setting to [On] will turn on the Num Lock key when the system is powered on. Setting to [Off] will allow users to use the arrow keys on the numeric keypad.

Choices: On, Off.

### **GateA20 Active**

Choices: Upon Request, Always

# **Option ROM Messages**

This item is used to determine the display mode when an optional ROM is initialized during POST. When set to [Force BIOS], the display mode used by AMI BIOS is used. Select [Keep Current] if you want to use the display mode of optional ROM.

Choices: Force BIOS, Keep Current.

#### **Interrupt 19 Capture**

Interrupt 19 is the software interrupt that handles the boot disk function. When enabled, this BIOS feature allows the ROM BIOS of these host adaptors to "capture" Interrupt 19 during the boot process so that drives attached to these adaptors can function as bootable disks. In addition, it allows you to gain access to the host adaptor's ROM setup utility, if one is available.

When it is disabled, the ROM BIOS of these host adaptors will not be able to "capture" the Interrupt 19. Therefore, you will not be able to boot operating systems from any bootable disks attached to these host adaptors. Nor will you be able to gain access to their ROM setup utilities.

Choices: Disabled, Enabled.

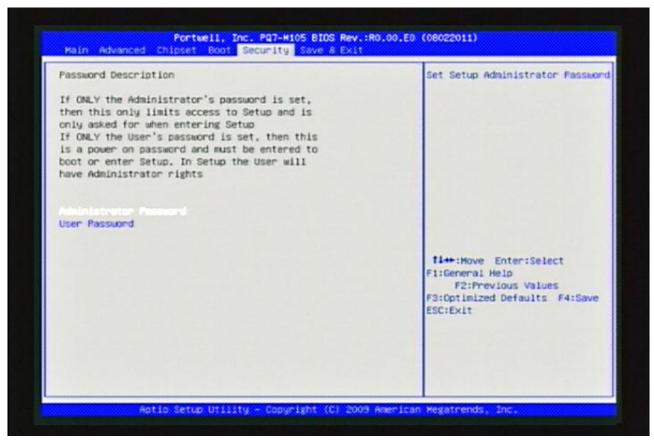

# 4.6 Security

Use this menu to set supervisor and user passwords.

### **Administrator Password**

Administrator Password controls access to the BIOS Setup utility. These settings allow you to set or change the supervisor password.

### **User Password**

User Password controls access to the system at boot. These settings allow you to set or change the user password.

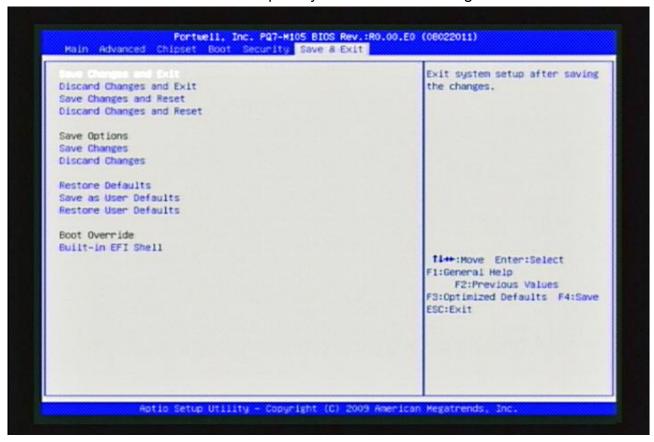

### 4.7 Save & Exit

This menu allows you to load the BIOS default values or factory default settings into the BIOS and exit the BIOS setup utility with or without changes.

### **Save Changes and Exit**

Save Changes and exit the BIOS setup menu.

# **Discard Changes and Exit**

Abandon all changes and exit the Setup Utility.

### **Save Changes and Reset**

Exit System Setup and save your changes to CMOS then reboot.

### **Save Changes**

Save changes but not exit or reset

### **Discard Changes**

Cancel all changes that's been made.

### **Discard Changes and Reset**

Abandon all changes and exit the Setup Utility then reboot

### **Restore Defaults**

Use this menu to load the default values set by the SBC manufacturer specifically for optimal performance of the SBC.

# Save as User Defaults

Save all changes and considers as User's default.

# **Restore User Default**

Restore the setting according to User's default

# **Launch EFI Shell from filesystem device**

To enter the Built-in EFI shell for further modification such as upgrade BIOS.

# **Chapter 5**

### **Troubleshooting**

This chapter provides a few useful tips to quickly get PQ7-M105 running with success. As basic hardware installation has been addressed in Chapter 2, this chapter will focus on system integration issues, in terms of BIOS setting, and OS diagnostics.

### 5.1 Hardware Quick Installation

There are two methods to power on PQ7-M105 + PQ7-C100XL-CAN which are **4 Pins DC** +12V connector or DC +12V IN Jack.

DC +12V Jack connect to PQ7-C100XL-CAN. (J30)

# 4 Pins directly +12V DC input. (J8)

Do NOT connect 4pins DC +12V and DC +12V Jack at the same time.

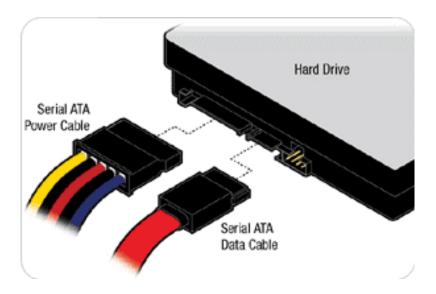

### Serial ATA Hard Disk Setting for IDE

Serial ATA channel can only connect to one SATA hard disk at a time; there are total 2 connectors, J3, J12 (PQ7-C100XL-CAN). The installation of Serial ATA is simpler and easier than IDE because of SATA hard disk doesn't require HDD priority setting jumper, which can reduce mistake of hardware installation. All you need to do is plugging in two cables and choose SATA mode needed in BIOS.

# 5.2 BIOS Setting

To make sure that you have a successful start with PQ7-M105, it is recommended while going with the boot-up sequence. Hit the "DEL" key and enter the BIOS setup menu to load default setting then tune up a stable BIOS configuration according to your needs.

# Loading the default optimal setting

When prompted with the main setup menu, please scroll down to "Load Optimal Defaults", press "Enter" and "Y" to load in default optimal BIOS setup. This will force your BIOS setting back to the initial factory configuration. It is recommended to do this so you can be sure the system is running with the BIOS setting that Portwell has highly endorsed. As a matter of fact, users can load the default BIOS setting any time when system appears to be unstable in boot up sequence.

### Improper disable operation

There are too many occasions where users disable a certain device/feature in one application through BIOS setting. These variables may not be set back to the original values when needed. These devices/features will certainly fail to be detected.

When the above conditions happen, it is strongly recommended to check the BIOS settings. Make sure certain items are set as they should be. These include the COM1/COM2 ports, USB ports, external cache, on-board VGA and Ethernet.

It is also very common that users would like to disable a certain device/port to release IRQ resource. A few good examples are

Disable COM1 serial port to release IRQ #4

Disable COM2 serial port to release IRQ #3

Etc...

A quick review of the basic IRQ mapping is given below for your reference.

| Interrupt Request Lines IRQ |              |                   |

|-----------------------------|--------------|-------------------|

| IRQ#                        | Current Use  | Default Use       |

| IRQ 0                       | System ROM   | System Timer      |

| IRQ 1                       | System ROM   | Keyboard Event    |

| IRQ 2                       | [Unassigned] | Usable IRQ        |

| IRQ 3                       | [Unassigned] | Usable IRQ        |

| IRQ 4                       | [Unassigned] | Usable IRQ        |

| IRQ 5                       | [Unassigned] | Usable IRQ        |

| IRQ 6                       | System ROM   | Diskette Event    |

| IRQ 7                       | [Unassigned] | Usable IRQ        |

| IRQ 8                       | System ROM   | Real-Time Clock   |

| IRQ 9                       | [Unassigned] | Usable IRQ        |

| IRQ 10                      | [Unassigned] | Usable IRQ        |

| IRQ 11                      | [Unassigned] | Usable IRQ        |

| IRQ 12                      | System ROM   | IBM Mouse Event   |

| IRQ 13                      | System ROM   | Coprocessor Error |

| IRQ 14                      | System ROM   | Hard Disk Event   |

| IRQ 15                      | [Unassigned] | Usable IRQ        |

It is then very easy to find out which IRQ resource is ready for additional peripherals. If IRQ resource is not enough, please disable some devices listed above to release further IRQ numbers.

#### 5.3 FAQ

#### Installation Problem

### Question: I forget my password of system BIOS, what am I supposed to do?

Answer: You can use CMOS clear jumper on carrier board depending on carrier board design. Or you can remove the Q7 module from socket for a while then plug it back, the setting will restore to default again.

# Question: How to update the BIOS file of the PQ7-M105?

#### Answer:

Please visit web site of the Portwell download center as below hyperlink and register an account. http://www.portwell.com.tw/support/

Input your User name and password to log in the download center.

Select the "Search download" to input the keyword "PQ7-M105".

Find the "BIOS" page to download the ROM file and flash utility.

Execute the zip file to root of the bootable USB Pen drive.

Insert your bootable USB Pen drive in PQ7-M105 board and power-on.

Input the "AFUDOS XXXXX.ROM /P /B /N " to start to update BIOS. ("XXXXX" is the file name of the ROM file.)

Switch "Off" the Power Supply when you finished the update process.

Perform a Clear CMOS action.

Switch "ON" the Power Supply then press the "del" key to BIOS to load "Restore Defaults" then save them to exit.

#### Note:

Please visit our technical web site at http://www.portwell.com.tw

For additional technical information, which is not covered in this manual, you can mail to tsd@mail.portwell.com.tw or to our sales for further assistance. Thank you.