# M.Sc. Thesis

# 90 nm VLSI Design of an 8-bits Microcontroller

## Jose A. Moar Gomez

#### Abstract

Integrated Circuit (IC) design complexity has increased radically since the first "hand-made" designs in the late 50s, with a few transistors. Nowadays, Very Large Scale Integration (VLSI) designs contains hundreds thousand, million or even billion transistors and not only the experience of the designer, but also Electronic Design Automation (EDA) tools and some methodology is needed.

The purpose of this thesis is the design in 90nm UMC technology of an 8-bit microcontroller for its final manufacture using Modelsim, Design Compiler and SoC Encounter and following a standard cell design methodology. During the different steps of the VLSI flow (behavioural specification and verification, synthesis and layout generation), it will be shown how to deal with the design issues that arise: (DFT insertion, clock gating, clock&reset tree generation, etc.)

Starting from a tested FPGA implementation in VHDL based on the AVR ATmega103 microcontroller from ATMEL, the final result is an 8-bit microcontroller with the following features: 16k x 16 bits of Program Memory (PM), 8K bytes Data Memory (DM), 256 bytes parameter memory, 3 8bits I/O ports, UART, SPI, JTAG interface, additional PM programming capability (apart from the JTAG) and Wishbone interface including an USB 1.1 slave and another slave to implement and test a simple scan chain prototype. In addition the clock frequency can be increased up to 200 MHz.

### THESIS

submitted in partial fulfillment of the Requirements for the degree of

MASTER OF SCIENCE

$\mathrm{in}$

#### **Microelectronics**

by

Jose A. Moar Gomez born in A Coruña, Spain

Committee members

| Advisor: | Dr.ir. T.G.R.M. van Leuken    |  |  |

|----------|-------------------------------|--|--|

| Member:  | Prof.dr.ir. A.J. van der Veen |  |  |

| Member:  | Dr.ir. W.A. Serdijn           |  |  |

This work was performed in:

Circuits and Systems Group Department of Microelectronics & Computer Engineering Faculty of Electrical Engineering, Mathematics and Computer Science Delft University of Technology

**Delft University of Technology** Copyright © 2009 Circuits and Systems Group All rights reserved.

# Abstract

Integrated Circuit (IC) design complexity has increased radically since the first "hand-made" designs in the late 50s, with a few transistors. Nowadays, Very Large Scale Integration (VLSI) designs contains hundreds thousand, million or even billion transistors and not only the experience of the designer, but also Electronic Design Automation (EDA) tools and some methodology is needed.

The purpose of this thesis is the design in 90nm UMC technology of an 8-bit microcontroller for its final manufacture using Modelsim, Design Compiler and SoC Encounter and following a standard cell design methodology. During the different steps of the VLSI flow (behavioural specification and verification, synthesis and layout generation), it will be shown how to deal with the design issues that arise: (DFT insertion, clock gating, clock&reset tree generation, etc.)

Starting from a tested FPGA implementation in VHDL based on the AVR ATmega103 microcontroller from ATMEL, the final result is an 8-bit microcontroller with the following features: 16k x 16 bits of Program Memory (PM), 8K bytes Data Memory (DM), 256 bytes parameter memory, 3 8bits I/O ports, UART, SPI, JTAG interface, additional PM programming capability (apart from the JTAG) and Wishbone interface including an USB 1.1 slave and another slave to implement and test a simple scan chain prototype. In addition the clock frequency can be increased up to 200 MHz.

# Acknowledgments

First of all, I would like to specially thank my parents, my godfather and all my family in general for all the support throughout my academic life; without them, this would not have been possible. I also would like to acknowledge Estela, my girlfriend, for all the help, patience and support during the consecution of this thesis.

I am extremely grateful to my advisor Rene van Leuken, for offering me the possibility to make the present thesis and all the given assistance, and to Alexander de Graaf and Laura Bruns for all the help in the technical and administrative part respectively.

And last but not least, I would like to express my gratitude to all my friends from:

Vigo: Lu, for being always wishing to help me in the difficult moments. Diego, Gonzalo and Mario, who were the best flat mates possible. Carlos, for all the good moments in Vigo and Delft. Carliños, Eviña, Raquel, Maruchi, Elena, Chus, Camilo, McEiras, Natalia, Patiño, Alberto, Fernando... for all the nice time we spent together. And of course Cris, who made really special my years in Vigo, which I will never forget.

Delft: Dani, David, Marta and Yago, who helped me a lot during my first weeks in The Netherlands. Ruben, Guille and Javi for all the unforgettable moments. And in general, to all my present friends in Delft and the ones that already left: Chema, Lola, Manu, Antieh, Anna, Victor, Xesc, Scarlett, Blanca, Ali, Iria, Yvan, Anxo, Andrs, Martn, Diego, Javi, Andres, Estefi, Esther, Raposo, Rebe, Iñigo, Hector, Luis, Alvaro,... and specially to all my house mates for making me feel as in my hometown: Calvin, Lynn, Robin, Robbert, Dennis, Bas, Arthur, Charlotte, Halie, Hans, Gaby, Annelote, Eva, Rik and Joris.

A Coruña: Bruño, Noelia, Souto, Rebro, Rubn, Uri, Chechu, Robert, Ana and Alba for having been always there.

Jose Moar Delft February 24th, 2009

# Contents

Abstract

| A        | cknov | wledgments                                        | $\mathbf{v}$ |

|----------|-------|---------------------------------------------------|--------------|

| 1        | Intr  | roduction                                         | 1            |

| _        | 1.1   | Motivation                                        | 1            |

|          | 1.2   | Thesis Goals                                      | 2            |

|          | 1.3   | Results                                           | 2            |

|          | 1.4   | Thesis Organisation                               | 2            |

| <b>2</b> | Bac   | kground                                           | 3            |

|          | 2.1   | Brief ICs history                                 | 3            |

|          | 2.2   | VLSI design flow                                  | 4            |

|          |       | 2.2.1 Specification                               | 4            |

|          |       | 2.2.2 RTL Behavioral Description and Verification | 4            |

|          |       | 2.2.3 Synthesis                                   | 5            |

|          |       | 2.2.4 Layout Generation                           | 5            |

|          | 2.3   | Standard cell design                              | 6            |

|          |       | 2.3.1 Faraday 90nm Standard Cell library          | 7            |

|          |       | 2.3.2 Memory Compiler from Faraday                | 7            |

|          | 2.4   | EDA tools                                         | 8            |

|          |       | 2.4.1 Getting help                                | 9            |

|          | 2.5   | Design for Testability                            | 10           |

|          |       | 2.5.1 Scan Design                                 | 10           |

|          | 2.6   | Wishbone Bus Interface                            | 12           |

|          | 2.7   | AVR Microcontroller                               | 13           |

|          | 2.8   | JTAG interface                                    | 14           |

|          | 2.9   | Summary                                           | 16           |

| 3        | RTI   | L behavioural description                         | 17           |

|          | 3.1   | Modifications                                     | 17           |

|          | 3.2   | New components                                    | 18           |

|          |       | 3.2.1 Reset synchronizer                          | 18           |

|          |       | 3.2.2 Reset Chain                                 | 18           |

|          |       | 3.2.3 MyJtag                                      | 19           |

|          |       | 3.2.4 USB 1.1 IP Core                             | 20           |

|          |       | 3.2.5 Scan Chain prototype in a Wishbone slave    | 21           |

|          |       | 3.2.6 I/O pads                                    | 21           |

|          | 3.3   | Summary                                           | 22           |

iii

| 4        | Ver        | ification with Modelsim 23                               |

|----------|------------|----------------------------------------------------------|

|          | 4.1        | Test Benches                                             |

|          |            | 4.1.1 Test cases                                         |

|          |            | 4.1.2 Generating the program code                        |

|          | 4.2        | RTL Behavioural verification                             |

|          | 4.3        | Synthesised netlist and post-layout netlist verification |

|          | 4.4        | Testing the component MyJtag                             |

|          | 4.5        | Summary                                                  |

| <b>5</b> | Syn        | thesis with Design Compiler 31                           |

|          | 5.1        | Constraining the design                                  |

|          |            | 5.1.1 Compile strategy                                   |

|          |            | 5.1.2 Input delay                                        |

|          |            | 5.1.3 Special buffers and inverters for the clock        |

|          |            | 5.1.4 Generated clocks                                   |

|          | 5.2        | Synchronous and asynchronous reset                       |

|          | 0.2        | 5.2.1 Asynchronous reset                                 |

|          |            | 5.2.2 Synchronous reset                                  |

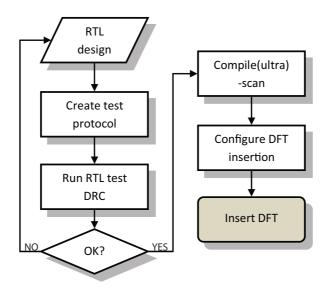

|          | 5.3        | Scan Chain insertion                                     |

|          | 0.0        | 5.3.1 Create test protocol                               |

|          |            | 5.3.2 RTL Design Rule Checking                           |

|          |            | 5.3.3 Compile, configure and insert the DFT              |

|          | 5.4        | Increasing the clock frequency                           |

|          | 0.4        | 5.4.1 Higher frequency consequences                      |

|          | 5.5        | Clock gating                                             |

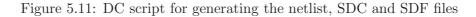

|          | 5.6        | Preparing data for simulation and P&R                    |

|          | 5.0<br>5.7 | Summary                                                  |

|          | 5.7        | Summary                                                  |

| 6        | •          | out generation 45                                        |

|          | 6.1        | Initialization steps                                     |

|          |            | 6.1.1 Footprints                                         |

|          |            | 6.1.2 I/O file                                           |

|          |            | 6.1.3 Excluded net                                       |

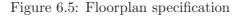

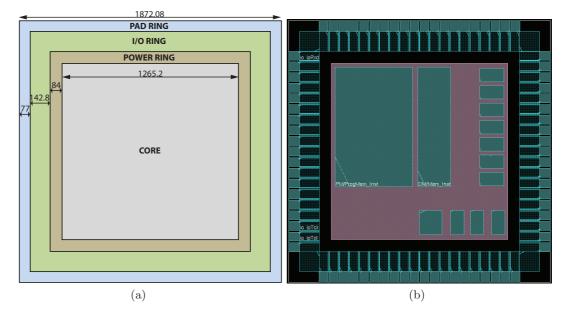

|          | 6.2        | Floorplan                                                |

|          | 6.3        | Power plan                                               |

|          | 6.4        | Placement                                                |

|          |            | 6.4.1 Setup timing violations                            |

|          | 6.5        | Clock and reset tree generation                          |

|          |            | 6.5.1 Hold timing violations                             |

|          | 6.6        | Route                                                    |

|          | 6.7        | Verification and results                                 |

|          | 6.8        | Summary                                                  |

| 7        | Bac        | k-annotated synthesis 59                                 |

|          | 7.1        | Summary                                                  |

| 8             | Results              | 63 |

|---------------|----------------------|----|

|               | 8.1 Future work      | 63 |

| $\mathbf{Li}$ | ist of Abbreviations | 65 |

| Bi            | Bibliography         | 67 |

# List of Figures

| 1.1               | Electronic systems                                       | 1               |

|-------------------|----------------------------------------------------------|-----------------|

| 2.1<br>2.2        | Moore's Law and CPU transistors                          | 4<br>5          |

| 2.3               | Standard cell with three metal layers                    | $\frac{7}{8}$   |

| $2.4 \\ 2.5$      | Read and write cycle timing for the SRAM used as PM      | 8<br>11         |

| $\frac{2.5}{2.6}$ |                                                          | $11 \\ 12$      |

| 2.0<br>2.7        |                                                          | 12 $12$         |

| 2.1               |                                                          | $12 \\ 13$      |

| 2.8<br>2.9        |                                                          | $15 \\ 15$      |

| 2.9<br>2.10       | 8                                                        | $15 \\ 15$      |

| 2.10              |                                                          | 10              |

| 3.1               | 1                                                        | 17              |

| 3.2               |                                                          | 18              |

| 3.3               |                                                          | 19              |

| 3.4               | USB architecture modification                            | 21              |

| 4.1               | Modelsim script                                          | 24              |

| 4.2               |                                                          | $\frac{21}{25}$ |

| 4.3               | 0                                                        | $\frac{20}{26}$ |

| 4.4               |                                                          | $\frac{-0}{26}$ |

| 4.5               |                                                          | $27^{-5}$       |

| 4.6               |                                                          | $\frac{-}{28}$  |

| 4.7               |                                                          | 29              |

|                   |                                                          | ~~~             |

| 5.1               |                                                          | 33              |

| 5.2               | 0                                                        | 34              |

| 5.3               |                                                          | 34              |

| 5.4               | 0 2                                                      | 35              |

| 5.5               |                                                          | 35              |

| 5.6               | 0                                                        | 37              |

| 5.7               | 1                                                        | 38              |

| 5.8               | *                                                        | 39              |

| 5.9               | 1                                                        | 40              |

| 5.10              | 1                                                        | 41              |

| 5.11              | DC script for generating the netlist, SDC and SDF files  | 44              |

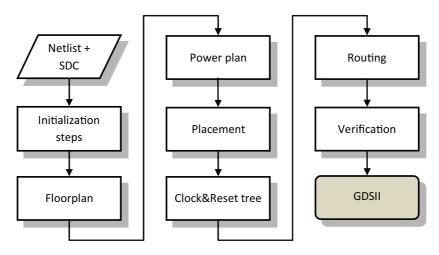

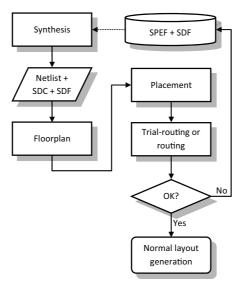

| 6.1               | Layout generation flow                                   | 45              |

| 6.2               | Original footprint file (a) and the modified version (b) | 46              |

| 6.3               | Fixing the footprint nomenclature                        | 47              |

| 6.4               | I/O File                                                 | 48              |

| 6.5               | Floorplan specification                                  | 50              |

| 6.6               | Layout dimensions (a) and floorplan (b)                  | 50              |

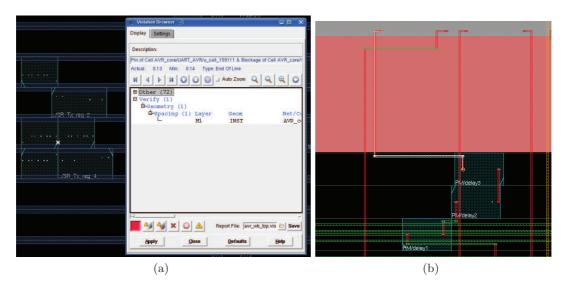

| 6.7  | "Spacing violation" (a) and delay cells placement (b)                     |

|------|---------------------------------------------------------------------------|

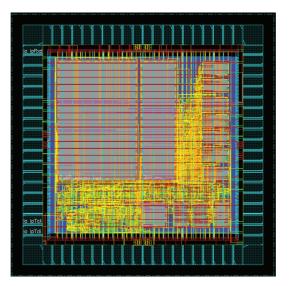

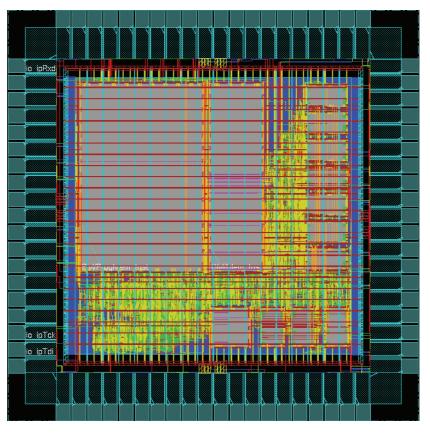

| 6.8  | Layout after placement                                                    |

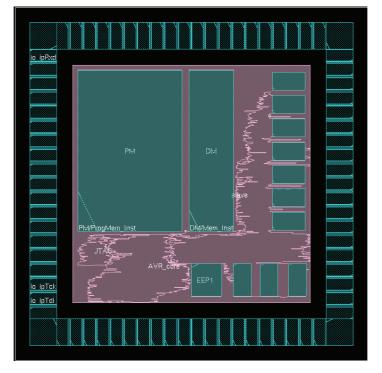

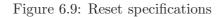

| 6.9  | Reset specifications                                                      |

| 6.10 | Clock tree                                                                |

| 6.11 | Potential hold timing violation (a) and the corresponding solution (b) 55 |

| 6.12 | Routing script                                                            |

| 6.13 | Final layout                                                              |

| 6.14 | GDSII extraction                                                          |

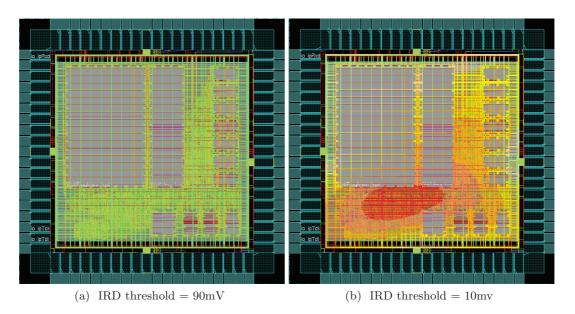

| 6.15 | IR Drop for two different thresholds                                      |

| 7.1  | Back-annotated synthesis flow                                             |

| 7.2  | Back annotated synthesis script for Design Compiler                       |

| 7.3  | Back annotated synthesis script for SOC Encounter                         |

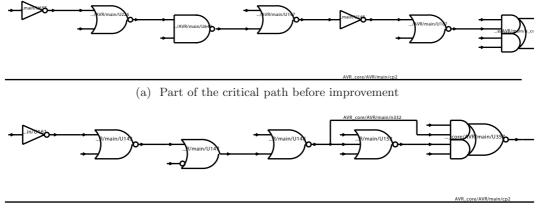

| 7.4  | Optimization in the critical path                                         |

| 7.5  | Critical path improvement                                                 |

# List of Tables

| 2.1 | Timing values for the SRAM used as PM (ns)      | 9  |

|-----|-------------------------------------------------|----|

| 5.2 | Normal and clock buffer delays (ps)             | 42 |

|     | Power consumption (mW) at different frequencies |    |

| 6.1 | I/O pads                                        | 48 |

| 8.1 | Microcontroller features                        | 64 |

# 1

Current society would be unimaginable without electronic gadgets. Nowadays, nobody can imagine having no Internet, computers, TV, mobile phones, etc. and the trend of dependence on technology is still growing (Figure 1.1). In this scheme of development, electronic devices are becoming more and more complex and initial integrated circuits (IC) developed in the 50s with a few transistors has grown to current IC with billions of transistors. This last evolution of ICs, the VLSI (Very Large Scale Integration) generation, demands a much more sophisticated way of designing than the handmade approach of the earliest ICs. There is also a big challenge involving the more and more "narrow" technology as far as CMOS manufacturing process is concerned. Coping with these huge designs and all the problems related with shrinking technology (synthesis, clock & reset tree generation, DFT techniques, power distribution ...) are the fields of this thesis.

Electronic systems are everywhere

Figure 1.1: Electronic systems

# 1.1 Motivation

Technology advances incredibly fast allowing more complex designs which make essential a continuous activity of research and development in order to ride the technology wave in the field of VLSI design.

In the other hand, microcontrollers have a wide range of applications; it is estimated that there is around 40 microcontrollers in a typical home. Furthermore, according to Semico<sup>1</sup>, over 4 billion 8-bit microcontrollers were sold in 2006.

<sup>&</sup>lt;sup>1</sup> Semico Research Corp is an american semiconductor marketing and consulting research company

# 1.2 Thesis Goals

Therefore, there are two goals to be achieved in this thesis:

- The main purpose is to complete a VLSI design flow in 90 nm technology with up-todate EDA tools (Design Compiler from Synopsys and SoC Encounter from Cadence) in order to set up a design environment for more complex and specific designs.

- Fabricate a low power microcontroller that includes the Wishbone and JTAG interfaces, USB 1.1 standard and scan chain capability.

# 1.3 Results

Throughout this thesis will be detailed the procedure that has been employed to achieve the following results:

- Generation of the GDSII file for an 8-bit microcontroller with the Wishbone interface, i.e., consecution of a ready-to-manufacture complex design in 90nm technology.

- Increased clock frequency from 20MHz up to 200MHz through architectural modifications and advanced design techniques such as back-annotated synthesis.

- Integration of a complex transmission interface such as the USB 1.1 into an 8-bit microcontroller using the Wishbone bus.

- Successfully application of DFT techniques using a multiplexed flip-flop scan chain.

- Clock gating implementation to reduce power consumption.

- Development of an additional programming interface for the PM.

# 1.4 Thesis Organisation

This thesis is organized in the following manner:

- Chapter 2 gives a basic background about the methodology and tools used in the design, and also includes a brief explanation about the microcontroller, the JTAG and Wishbone interfaces and the concept of Design for Testability using a Scan Chain approach.

- Chapter 3 presents the starting point of the design, the changes that has been made and the new functionalities.

- Chapters 4 to 7 collect all the issues that arise during the design flow with the solution(s) that has been taken.

- Chapter 8 shows the results and possible future work.

www.semico.com.

It has already been said before that a line of attack should be clearly defined when dealing with actual IC designs and maybe not so indispensable with the "old" ones. Throughout this chapter will be briefly introduced the evolution of ICs, applied methodology, tools that has been used and specific technology employed for the manufacturing. Furthermore, the microcontroller, Wishbone and JTAG interfaces and Design for Testability technique will be explained.

# 2.1 Brief ICs history

There are some discrepancies about who conceived the first IC: Jack Kilby of Texas Instruments or Robert Noyce of Fairchild Semiconductor. Whoever was the "father", the birth of the first IC in 1958 initiated a revolution in the circuit design field.

Starting with circuits containing only a few transistors, Small-Scale Integration (SSI), the IC was already used in important applications such as the aerospace Apollo program or FM inter-carrier sound processing in television receivers. During the late 60s and mid 70s, the IC evolved to circuits with hundreds of transistors, Medium-Scale Integration (MSI), and subsequently to circuits with tens of thousands of transistors, Large-Scale Integration (LSI).

These first designs were "handmade" and based only on the experience of the designer, but the more the circuits increase the number of transistors the more impracticable was the design without any "external help". This "external help" is known as EDA tools (Electronic Design Automation) and was an essential part of the next evolution step in IC, the VLSI age (Very Large Scale Integration), which was initiated at the early 80s with circuits including hundreds of thousands of transistors. Nowadays, this number increased beyond several billion transistors, what makes clear the need of EDA tools and some method or design flow that allows managing huge designs like that.

This growing trend was already predicted by Gordon E. Moore in his publication "Cramming more components onto integrated circuits" [6]:

The complexity for minimum component costs has increased at a rate of roughly a factor of two per year... Certainly over the short term this rate can be expected to continue, if not to increase. Over the longer term, the rate of increase is a bit more uncertain, although there is no reason to believe it will not remain nearly constant for at least 10 years. That means by 1975, the number of components per integrated circuit for minimum cost will be 65,000. I believe that such a large circuit can be built on a single wafer.

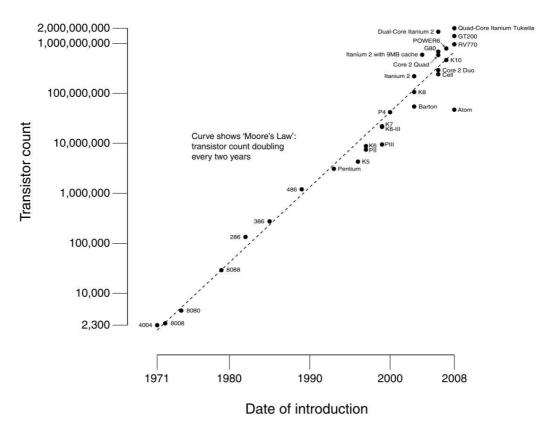

Later, in 1975, Moore changed his prediction to a doubling every two years and this statement remains still valid nowadays and it is known as the "Moore's law" (Figure 2.1)

## CPU Transistor Counts 1971-2008 & Moore's Law

Figure 2.1: Moore's Law and CPU transistors

# 2.2 VLSI design flow

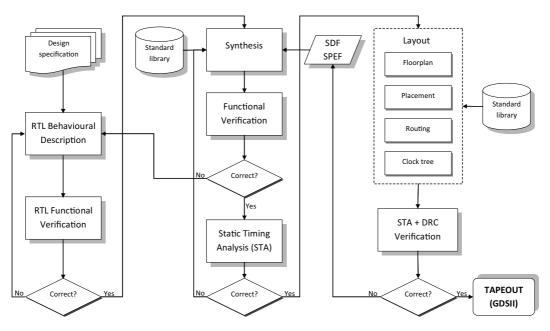

In the previous section, the need of some kind of methodology was stated. In this section, we will present this methodology as a design flow that allows IC designers to get an error-free circuit. The diverse steps of a typical design flow are shown in Figure 2.2 and are subsequently explained in subsections 2.2.1 to 2.2.4.

#### 2.2.1 Specification

The design starts setting the requirements that our circuit has to fulfill. These specifications can be described with any system specification language (C, C++, Matlab, etc.)

#### 2.2.2 RTL Behavioral Description and Verification

The specifications are now converted into an RTL behavioral description using an HDL (Hardware Description Language) such as Verilog or VHDL. The correct behaviour is then checked by a simulation program (for instance, Modelsim from Mentor Graphics or VCS from Synopsys) using test benches.

Figure 2.2: VLSI Design Flow example

### 2.2.3 Synthesis

Synthesis is the process by which the circuit behavior is transformed into a design implementation in terms of logic gates. It includes the following steps:

- *RTL Synthesis and Library Mapping*: The VHDL code is translated into a netlist of interconnected general gates and registers and then it is mapped to the particular gates defined in the target library. Design Compiler from Synopsys or Synplify Pro from Synplicity are typical programs used for this task

- Functional Verification: At this point, it is necessary to check if the structural netlist performs the same function as the original behavioral HDL. The easiest way is to run again the test benches that have been used in the behavioral step.

- *Static Timing Analysis*: The circuit is behavioral and structural equivalent but timing requirements has to be tested. A static timing analysis can be run quickly to check if the circuit is fast enough or if we should come back to a previous design step and redesign our project.

#### 2.2.4 Layout Generation

Layout generation is the last step before sending the chip to fabrication. It takes the structural netlist from the previous step and generates the physical layout. The next steps are comprised in the layout generation:

• *Floorplanning*: It is being more and more common to perform and initial manual floorplanning before the automatic placement. In this way, some hierarchy is given to the design in order to avoid placing a "flat" design. The benefit of this approach is to get closer modules that has to communicate with each other with the purpose of minimize the wire length.

- *Placement*: Where to place the standard cells is the first task that needs to be solved in the Layout Generation. The simple idea is to minimize the length of wires, but, for example, in a *timing-driven placement* the intention is to decrease as much as possible the delay on the critical paths.

- *Routing*: At this point, the cells are placed and they need to be interconnected. The routing step can be divided in two stages: global routing and detailed routing. In the first stage (global routing) the problem is abstracted to establish through which channels the connections will flow. Then, in the second stage (detailed routing) the exact position of a connection wire within a channel is determined.

- *Timing Analysis*: This is the critical step of the design flow and it can be seen as a bottleneck in the process. The static timing analysis is rerun after the place and route in order to check if the timing requirements are accomplished. It can be necessary some iterations of synthesis and P&R (place and routing) before our goal is reached. This iteration process is called *back-annotated synthesis*.

- Clock tree generation: How the clock is distributed in a design is one of the most limiting factors in order to achieve high frequency circuits. The clock signal has to get all the clocked components at the same time in order to achieve a correct operation, and the more the frequency is increased, the more clock inaccuracy we have. The clock inaccuracy consists of two elements: the clock skew and the clock jitter. In addition to this, it is also important to take care about power consumption reduction using clock gating. This factor is extremely important because, for example in Intel chips, the clock network can be even 50% of the total power consumption.

# 2.3 Standard cell design

There is one more aspect that should be pointed out in addition to the design flow explained in Section 2.2: how is actually the physical layout generated? Typically there are two main options:

- *Full custom design*: The designer has to generate the layout of each transistor and the interconnection between all of them. This approach allows maximizing the performance of the circuit, but it is not possible to apply when dealing with big designs such a microcontroller.

- Standard cell design: In the other hand, standard cell design takes advantage of the repetition of smaller sub-circuits to create a level of abstraction that allows the designer focusing on the high-level (logical function) aspect of the digital design. These smaller sub-circuits can be seen as "low-level layouts", created using a full custom technique, that are encapsulated into abstract logic representations (logic gates, flip-flops, buffers, etc.).

When opting for the latter design method, as is the case in this thesis, a library containing the standard cells should be provided. The library that has been used in this design is explained next.

#### 2.3.1 Faraday 90nm Standard Cell library

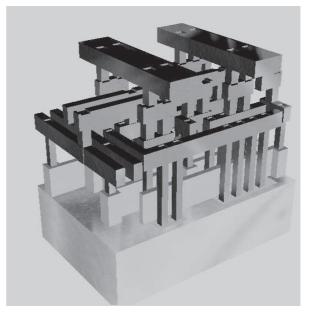

Faraday The FSD0A\_A library from used  $_{

m in}$ this thesis is a 90nm standard cell UMC's 90 library for nm logic SP-RVT (Low-K) process, where  $SP^1$ stands for "Standard Performance" RVT for "Regular Voltage and а 3D representation standard cell. of  $\mathbf{a}$

Threshold". Figure 2.3shows The Low-K term refers to the small dielectric constant  $(\kappa)$  of the material that has been used to replace the silicon dioxide in the manufacturing This substitution is aimed process. to reduce parasitic capacitance, enable faster switching and get lower heat dissipation. All these manufacturing process related issues are beyond the scope of this thesis and we refer to [2], [3] and the UMC documentation for more details.

This library supplies a set of common core cells (logic cells, flip-flops, latches, RAM cells...) with up to 12 different drive strengths in order to improve performance and also includes 2.5V I/O cells with the following programmable capabilities:

- Input pull-up/pull-down/keeper control

- Schmitt trigger control

- Input gated control

- Output slew rate control

- Different output driving possibilities (from 2 to 16 mA)

All the I/O cells are available in Pad-Limited or Core-Limited<sup>2</sup> versions.

#### 2.3.2 Memory Compiler from Faraday

The embedded memories used in this thesis are also intended for UMC's 90 nm logic SP-RVT (Low-K) process. Faraday Technology supplies a memory compiler where different

Figure 2.3: Standard cell with three metal layers

<sup>&</sup>lt;sup>1</sup>UMC offers different options in 90nm technology depending on the application: LL (Low Leakage) devices are intended for portable and wireless applications, HS (High Speed) option is available for graphics applications while SP is a trade-off solution between performance and power consumption.

$<sup>^{2}</sup>$ Pad- and core-limited refer to the most restrictive factor in terms of size: the amount of core logic or the number of IO pads. Pad-limited pads are narrower and longer, while core-limited are wider and shorter. This makes sense as overall area is smaller.

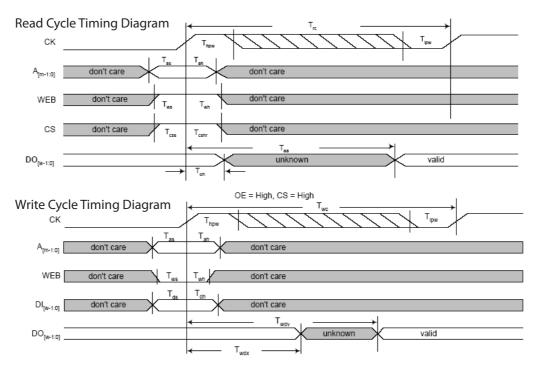

Figure 2.4: Read and write cycle timing for the SRAM used as PM

combinations of words, bits, and aspect ratios can be selected to generate the memory. In addition, the memory compiler also provides the data sheet, Verilog and VHDL behavioural simulation models, LEF files for the place & routing, etc. For instance, Figure 2.4 and Table 2.1 show the read and write cycle timing diagram for the SRAM used as PM with the corresponding values.

# 2.4 EDA tools

We will present concisely the three EDA tools that have been used during the VLSI design flow in this thesis:

- *Modelsim SE 6.3a* from Mentor Graphics is a hardware simulation and debug environment quite popular between IC designers. It provides the designer with the possibility of verifying the functionality of the circuit and also including timing information through an "SDF" file (Standard Delay Format). It supports multi-language simulation (VHDL, Verilog, SystemVerilog) and TCL/tk scripting, among other features.

- Design Compiler (version Z-2007.03-SP4 and B-2008.09-SP1-1) from Synopsys is the EDA tool use to perform the logic synthesis, i.e., transform the abstract description of the circuit into a design implementation in terms of logic gates. It offers the facilities for facing successfully with the challenges of a design: timing, area, low power and high test coverage.

- SOC Encounter 6.2 from Cadence completes the last step of the VLSI design flow, i.e., it performs the floorplanning, power distribution, place and routing, clock tree

| Symbol                 | Description                                 | BC   | TC   | WC   |

|------------------------|---------------------------------------------|------|------|------|

| taa                    | Address access time from CK rising          | 0.93 | 1.46 | 2.70 |

| toh                    | Output data hold time after CK rising       | 0.45 | 0.71 | 1.31 |

| trc                    | Read cycle time                             | 1.17 | 1.79 | 3.21 |

| tcss                   | CS setup time before CK rising              | 0.10 | 0.17 | 0.31 |

| $\operatorname{tcshr}$ | CS hold time after CK rising in read cycle  | 0.00 | 0.00 | 0.00 |

| tcshw                  | CS hold time after CK rising in write cycle | 0.00 | 0.00 | 0.00 |

| twh                    | WEB hold time after CK rising               | 0.06 | 0.08 | 0.14 |

| tah                    | Address hold time after CK rising           | 0.00 | 0.00 | 0.00 |

| tas                    | Address setup time before CK rising         | 0.04 | 0.08 | 0.19 |

| twc                    | Write cycle time                            | 1.18 | 1.80 | 3.17 |

| tws                    | WEB setup time before CK rising             | 0.05 | 0.08 | 0.15 |

| tdh                    | Input data hold time after CK rising        | 0.03 | 0.04 | 0.07 |

| tds                    | Input data setup time before CK rising      | 0.08 | 0.13 | 0.25 |

| twdv                   | Output data valid after CK rising           | 0.93 | 1.46 | 2.70 |

| twdx                   | Output data invalid after CK rising         | 0.45 | 0.71 | 1.31 |

| thpw                   | Clock high pulse width                      | 0.09 | 0.12 | 0.16 |

| tlpw                   | Clock low pulse width                       | 0.10 | 0.15 | 0.27 |

| toe                    | Output data valid after OE rising           | 0.07 | 0.11 | 0.19 |

| toz                    | Output data go to Hi-Z ater OE falling      | 0.04 | 0.06 | 0.11 |

Table 2.1: Timing values for the SRAM used as PM (ns)

synthesis..., in order to produce the GDSII file (Graphic Data System) for the final tape-out of the circuit.

#### 2.4.1 Getting help

All the tools described before are delivered with extensive documentation and huge manuals, but it does not take too long in turning out insufficient. This problem mainly applies for Design Compiler and SOC Encounter which are quite expensive programs, mostly used in companies, and therefore, it is difficult to get information about how to solve specific problems. On the contrary, Modelsim is a much more common software being used in professional but also educational environments. According to this, the following "sources of help" are suggested:

- When dealing with Modelsim, the fastest way to solve any kind of problem is Google (even faster than consulting the own Modelsim manual)

- For problems with Design Compiler, after checking the user guide, SolvNet can be used. *Solvnet.synopsys.com* is the on line resource for Synopsys tool support and downloads, that offers access to the Synopsys knowledge data base containing up-to-date product manual, technical articles and day-a-day issues posted by Synopsys users.

- Sourcelink.cadence.com is the equivalent of Solvnet for Cadence.

Both Synopsys and Cadence allows designers to post question on theirs sites, but unfortunately, this facility is not supported for university accounts. In addition, there are some web sites that can be also really helpful with these tools and also for clarifying some concepts. A small selection is presented:

- www.edaboard.com

- www.deepchip.com

- www.edacafe.com

# 2.5 Design for Testability

Testing and validation is an important issue in IC design that is often overlooked. A correct design is not synonymous with an error-free manufactured component because manufacturing defects has to be taken into account: impurities in the silicon crystal, short circuits between wires or layers, broken interconnections, etc. Clearly, it is necessary to validate the circuit after the manufacturing process, nevertheless, testing a component that has been designed without having that purpose in mind can be extremely expensive in terms of money and time. Therefore, when considering test capabilities in a design, there are two important properties:

- *Controllability* determines the ease of setting an internal node to a certain value. The best example of high controllability is a node that can be settable through an input pad. A circuit having nodes with poor controllability takes extremely long to get it into a specific state, and, sometimes, it is not even possible.

- *Observability* can be seen as a measure of the ease of observing a specific circuit node at the output of the integrated circuit. Ideally, it should be possible to observe every single gate output either directly or indirectly (within some clock cycles).

*Design For Testability* is a design technique, of which the objective is to improve controllability and observability in the circuit. The two main approaches are:

- BIST (Built In Self Test)

- Scan Design

Scan design is the approach used in this thesis and will be discussed in the next section. An explanation about BIST and another aspects of the DFT technique can be found in [7].

#### 2.5.1 Scan Design

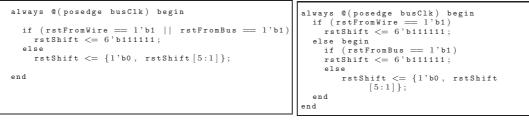

Scan design is a DFT strategy that consists in replacing the normal registers by scannable registers. The scan registers can operate in two modes: in *normal mode* the register operates as normal registers while in *scan mode* they are connected in order to create a *scan chain*. A scan chain can be seen as a shift register where the designer can shift data in and out. As will be shown in Sections 2.5.1.1 to 2.5.1.3 three extra IO ports are needed in the design. In this thesis we will use the "DFT Compiler" capability from Design Compiler to implement a simple scan chain in the design. DFT Compiler supports the following scan models:

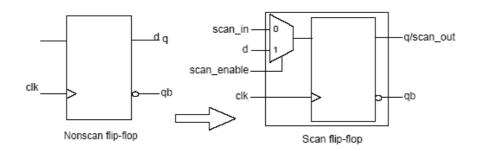

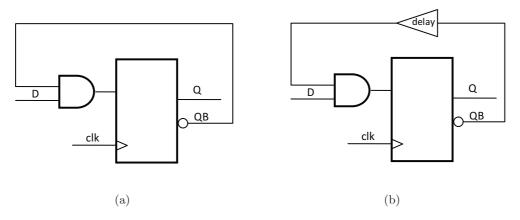

Figure 2.5: Multiplexed scan style

#### 2.5.1.1 Multiplexed Flip-Flop Style

The most basic scannable flip-flop can be achieved combining a normal D flip-flop with a multiplexer as shown in Figure 2.5. The main advantage of this style is its low area overhead while the main disadvantage is the additional delay introduced by the multiplexer, which can become really critical when the register is part of the critical path. The multiplexed scan style is the most commonly supported in technology libraries (Faraday library used in this thesis also provides specific scannable D flip-flops) and requires the following test pins:

- Scan input

- Scan output

- Scan enable

In Section 5.3 is explained how to implement a simple multiplexed style scan chain. A more complete explanation about all the details involving scan insertion can be found in [8] and [9].

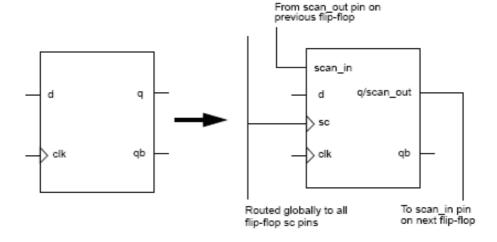

#### 2.5.1.2 Clocked Scan Style

The difference with the previous style is that, now, instead of a selection signal an additional clock is presented. When this clock is active, the test data is shifted into the register. Figure 2.6 shows an example of clocked scan style, which also needs three test pins (the scan enable pin is now substituted for the test clock pin). The difference with the previous style is that, preserving the low area overhead, a better performance is obtained with the cost of an additional clock.

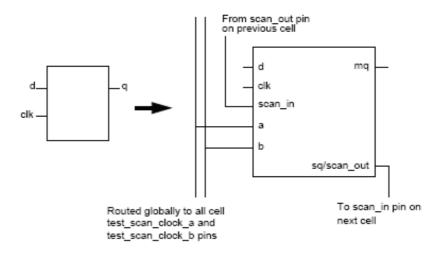

#### 2.5.1.3 LSSD Style

The Level Sensitive Scan Design (LSSD) style consists in two latches working as master-slave pair. It has the best performance in comparison with the previous styles at the expense of a high area overhead and an extra test pin. There are three variations of the LSSD scan style: single-latch, double-latch and clocked that are explained in [8]. Figure 2.7 shows the substitution of a normal latch for a single-latch LSSD style.

Figure 2.6: Clocked Scan Style

Figure 2.7: Single-latch LSSD Style

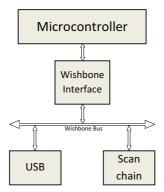

## 2.6 Wishbone Bus Interface

Wishbone Bus Interface is a System on Chip (SoC) interconnection method that allows integrating digital circuits together in a chip and it is used by a lot of designs in the OpenCores<sup>3</sup> project. The Wishbone Bus is a flexible, simple and portable way of interconnecting "IP Cores" (Intellectual Property Cores) to our circuit, which means that a new functionality can be added quickly and easily in the design. It can be seen as a standard for the IP Cores interfaces, which is very useful for independent development of the cores but assuring a final successful integration. The Wishbone Bus has been specified as a "logical bus", that is to say, in terms of "signals", clock cycles and high and low levels. The ambiguity in electrical information or bus topology lets designers more freedom to combine different designs. It presents a Master/Slave architecture with four different types of interconnection:

Figure 2.8: Wishbone shared bus interconnection

- *Point to Point*: It is the simplest interconnection. Allows only one master to communicate with only one slave.

- Data Flow Interconnection: It is used when data can be processed in a sequential way. Every IP core has both a master and a slave interface and the data "flows" through the line of interconnected cores. It is a kind of pipelining because exploits parallelism and, therefore, decreasing execution time.

- Shared Bus Interconnection: It is a multi-master/multi-slave interconnection, that is to say, more than one master and more than one slave can be connected to the bus at the same time. In this situation, when more than one master is connected, it is necessary arbitration. Both the arbiter and the shared-bus implementation are entirely specified by the system integrator. A possible example could be a PCI bus with round-robin.

- Crossbar Switch Interconnection: It is the last and most complex way of interconnection in the Whisbone bus. Crossbar switch interconnection allows two or more master to communicate at the same time with two or more slaves (each slave can only be addressed by one master, that is to say, two masters cannot addressed the same slave, but it is possible different slaves at the same time). In this case, the arbiter indicates when a master can gain access to a specific slave. The average data transfer rate is higher than in the shared bus scheme but the requirements in interconnection logic and routing resources are also higher.

In this thesis will be used a "shared bus interconnection" to communicate one master, a microcontroller implementing the Wishbone interface, and two slaves, an USB (see Section 3.2.4) and a scan chain prototype (see Section 3.2.5). This architecture can be seen in Figure 2.8

# 2.7 AVR Microcontroller

The microcontroller implemented in this thesis is based on the "AVR ATmega103" from Atmel. The ATmega103 is an 8-bit microcontroller with the following main features:

- RISC architecture with 121 instructions and 32 8-bit general purpose registers

- 128KB PM, 4KB DM and 4KB EEPROM

- SPI, UART, Watchdog, two 8-bit timers, PWM, ADC and 32 programmable I/O lines

Some of this features has been changed in the design implemented in this thesis, (for instance, the new sizes of the memories are 32K for the PM, 8KB for the DM and 256bytes EEPROM), another ones have been removed (Watchdog, PWM, ADC) and some new features have been included. All these changes can be seen in Chapter 3.

## 2.8 JTAG interface

JTAG (Join Test Action Group) was an industry group founded in 1985 to create a method to test circuit boards that were becoming smaller and smaller and, in this way, much more complex to be tested. The industry standard developed became in 1990 an IEEE standard, 1149.1 IEEE Standard Test Access Port and Boundary-Scan Architecture. The method devised by this group was how to perform a boundary-scan testing at the IC level, which means that a large debugging can be performed through a small numbers of test pins, and it is the most popular and used "design-for-test" technique nowadays. The JTAG interface consists at least of three inputs ports and one output (there is an optional extra input for asynchronous initialization of the test logic). These set of pins are known in JTAG terminology as the Test Access Port (TAP) and they are the following:

- *TDI* (Test Data In) is sampled at the rising edge of TCK and shifted into the device's test or programming logic.

- *TDO* (Test Data Out) represents the data shifted out of the device's test or programming logic and is valid on the falling edge of TCK.

- TCK (Test Clock) synchronizes the internal state machine operations

- *TMS* (Test Mode Select) is sampled at the rising edge of TCK to determine the next state

- TRST (Test Reset, optional) resets the internal state machine when it is driven low

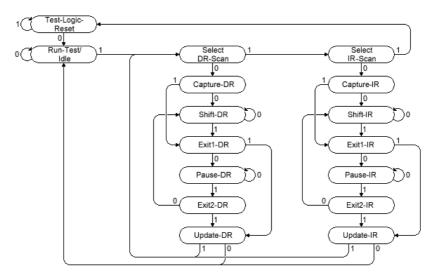

The operation of the JTAG interface is controlled by a 16 state-machine called the *TAP* controller. The different states are selected with the TMS signal (it is interested to point out that five consecutive ones always get the "Test Logic Reset" state). The state transition diagram can be seen in Figure 2.9. A typical test process using the JTAG interface is as follows:

- 1. The diagnostic data is set on the input pins.

- 2. The input data is saved in the boundary scan registers monitoring the input pins.

- 3. The output data is scanned from the TDO pin.

- 4. The output data is compared with the expected values according to the input data to check the correctness of the circuit.

Apart from the described functionality, the JTAG has been extended by Atmel to include the following additional functionalities in the latest AVR microcontrollers:

Figure 2.9: TAP controller state transition diagram

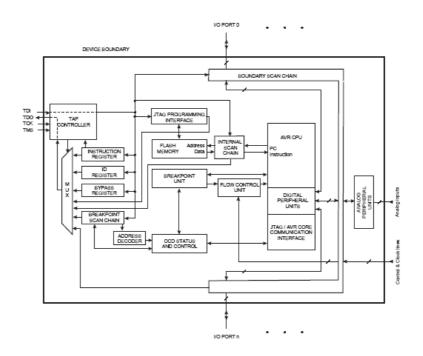

Figure 2.10: AVR JTAG block diagram

- Programming the non-volatile memories, fuses and lock bits.

- On-chip debugging with the AVR Studio.

In this thesis, only the programming capabilities for the PM using the JTAG interface have been implemented. Figure 2.10 shows the block diagram of the extended JTAG.

# 2.9 Summary

In this chapter a briefly introduction to the background concerning the scope of this thesis was given; including topics such as methodology employed throughout this VLSI design, tools that have been used, necessity of DFT techniques, Wishbone and JTAG interfaces, etc.

Next chapter will describe the modifications applied to the design and the new components included.

As it was mentioned before, the starting point is a tested FPGA implementation of the AVR Atmega 103 including the Wishbone interface. In that case, the slave attached was an LCD controller and the design was tested successfully in a Xilinx Avnet xc3s2000 FPGA. From this, it can be assumed that the RTL behavioral description of both, the core and the Wishbone interface, is synthesisable and acceptably verified.

# 3.1 Modifications

From the initial design, the following components are not necessary anymore:

- Debouncer: Filters mechanical switch bounces from the FPGA reset push button.

- CPUWaitGenerator: It is used when the core is connected with low speed memories.

- *Xilinx memories*: the program, data an EEPROM memories were implemented using the specific memory blocks from Xilinx.

The Xilinx memories have been replaced by the following embedded Faraday memories:

- 3 single port SRAM of 32K, 8K and 256 bytes for the PM, DM and EEPROM.

- 10 synchronous two-port register files for implementing the 10 FIFOs in the USB Wishbone slave.

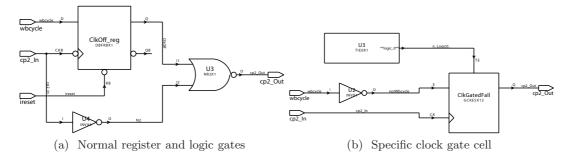

Furthermore, the component  $ClockSwitch^{1}$  has been implemented using a specific clock gate cell from Faraday in order to avoid "risky" implementations as depicted in Figure 3.1.

Figure 3.1: ClockSwitch implementation

<sup>&</sup>lt;sup>1</sup>This component is used to stop the clock of the AVR core when communicating with slower Wishbone slaves.

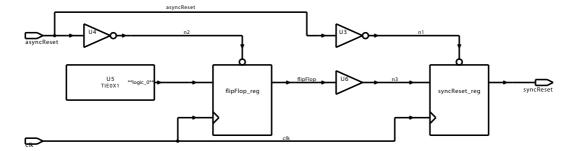

Figure 3.2: Reset Synchronizer

## 3.2 New components

The next list presents the new modules in the design, which are briefly explained in the following subsections:

- Reset synchronizer

- Reset chain

- MyJtag

- USB 1.1 IP Core

- Scan chain prototype wishbone slave

- I/O pads

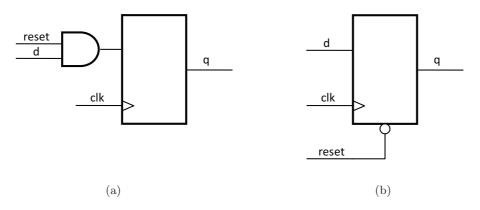

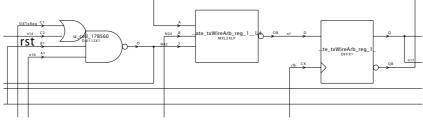

#### 3.2.1 Reset synchronizer

With the exception of the SPI and the USB, the rest of the components have an asynchronous reset, which means that some mechanism is needed to avoid metastability in the circuit. Metastability occurs when the reset removal violates the "reset recovery time", that is, the reset signal is (de)asserted too close to the falling/rising edge of the clock.

A possible solution is to insert a "reset synchronizer" as depicted in Figure 3.2, where only the first flip-flop has potential metastability problems since the second one has the same input and output when the reset is removed. In this way, the circuit is brought into the reset state asynchronously but the reset removal is performed synchronously in two clock cycles.

#### 3.2.2 Reset Chain

In Section 3.2.1 was presented how to avoid metastability because of the reset removal. Another critical issue concerning this aspect is to generate a valid sequence of reset removal, that is, most of the times, not all the components in the design can be taken out the reset state at the same time. This is due to the fact that not all the components need the same number of clock cycles to recover from the reset state. For example, component A is using data generated from component B and in both of them the reset is removed at the same time. In this case, if B needs more time than A in order to present valid data after the reset has been removed, A could use wrong data from B and leads the whole circuit to malfunction.

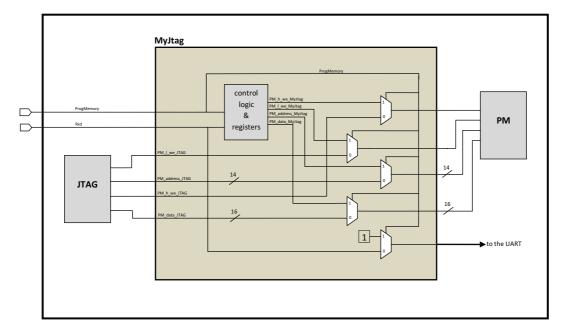

Figure 3.3: MyJtag simplified diagram block

In this thesis, the only component that presents this potential problem is the AVR core, so the reset sequence is really simple: the reset signal for all the components is removed at the same time apart from the one going to the AVR core, which is delayed 16 clock cycles.

In addition, this component also keeps the AVR core in reset state while using the JTAG or MyJtag (see Section 3.2.3) capabilities.

## 3.2.3 MyJtag

The function of this component is to give an alternative way of programming the Program Memory (PM) in the case the JTAG interface is not working properly due to some manufacturing defect. It is using three IO ports:

- *clkExt* (external clock pin): The purpose is to avoid synchronisation problems when reading the data into the shift register.

- *progMemory* (control pin): when set to 1 it means that this component is going to be used to program the PM.

- *rxd* (data input pin): this pin is being shared with the UART to reduce the total number of IO ports needed.

MyJtag block diagram is shown in figure Figure 3.3. Essentially, it works as follows:

- 1. The rxd signal has to be set high because a low starting bit is used.

- 2. The progMemory signal is set high so as to take the AVR core into the reset state and to select the internal data and address registers for the PM.

- 3. After the starting bit, data is read into the shift register with each rising edge of the external clock.

4. Every 16 bits, the address register is incremented by one and the data is written in the PM.

It is assumed that the external data is being generated by the external clock, so no synchronisation mechanism is needed. About the maximum speed of this external clock, the I/O buffer delay limits the frequency to approximately 1 GHz, and, taking into account that an instruction is written in the memory every 16 bits, it yields a PM writing rate of 62.5 MHz, which is feasible.

Anyway, there is no need in squeezing the design up to this point: with a 32K bytes PM and an external clock frequency in the range of the AVR core, for example 150 MHz, the PM will be "filled" completely in:

$$\frac{32K*8}{15\cdot 10^7 bps} \approx 2ms$$

which is a more than acceptable value.

## 3.2.4 USB 1.1 IP Core

As its name suggests, this IP Core, successfully proven in an FPGA, implements the USB 1.1 standard with the following features:

- 8-bits Wishbone slave interface

- Include low (1.5 Mbps) and high (12 Mbps) speed capability.

- Control, bulk, interrupt and isochronous transfers are supported.

- Four endpoints with independent 64 bytes FIFOs for each one.

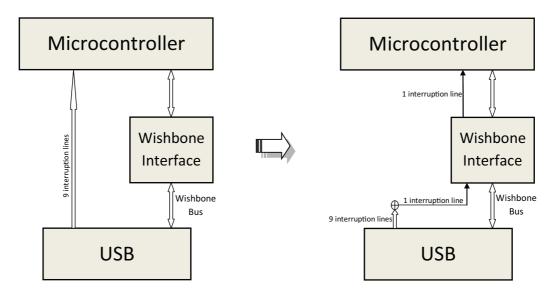

The USB also presents 9 interruptions lines that have to be attached to the microcontroller. Unfortunately, there is only one external interruption available that is already been used for the wishbone interface. In order to solve this problem, the 9 interruptions can be "xored" in one line and, to find out what interruption has been activated, the interruption status register has to be read. Figure 3.4 shows this change in the architecture.

In addition to the previous modification, special memories from Faraday have been used to implement the 10 FIFOs used in the USB (one transmission and one reception FIFO for each endpoint and also another pair for the host mode).

Furthermore, it has to be taken into account that the USB require the following clocks:

- USB logic clock: It is the internal clock of the USB. It has to run at 48MHz with a tolerance of +/-0.25%.

- Wishbone clock: This is the clock use for the Wishbone interface implemented in the USB. It can be asynchronous to the internal clock but it is limited to the following frequency range: 24MHz <= Wishbone clock <= 240MHz.

Further information about this IP core can be found in [5].

Figure 3.4: USB architecture modification

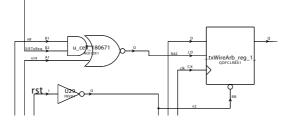

### 3.2.5 Scan Chain prototype in a Wishbone slave

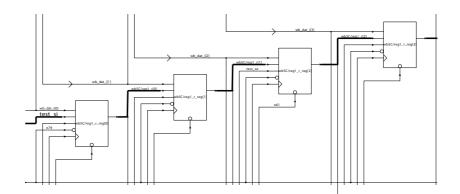

This component has a double objective: implements a basic Scan Chain that consists of four registers and shows how the microprocessor can handle different Wishbone slaves

Concerning the Wishbone interface, the intention is to create a component that can be used to verify if the microprocessor can handle correctly more than one Wishbone slave. With that goal, a simple slave that adds two 8-bits number was implemented. It consists of four 8-bits registers: two for the addends, one for the result and one control register. The addition is carried out when the LSB of the control register is written to one. The four register can be written and read from the microcontroller.

Regarding the Scan Chain objective, the importance of Design for Testability was explained in section Section 2.5. For that reason, a first approach to this technique is put into practice as can be seen in figure Figure 5.7, where the four register used in the Wishbone slave were included in the scan chain. The idea is to set up a basic scene where this technique can be tested without affecting the performance of the other components.

### 3.2.6 I/O pads

Some way must be provided to communicate data between the chip and the external circuitry. In order to accomplish this function, in [3] can be seen that I/O pads must have the following properties:

- *Protects against over voltage damage*: Extremely high voltages can be put on an input pin just by touching it with a finger.

- Drives large capacitance: Typical values for off-chip signals are between 2 and 50 pF.

- Protects the circuit against electrostatic discharge (ESD<sup>2</sup>)

$<sup>^{2}</sup>$ The term "electrostatic discharge" is used to denote the unexpected and temporary electric current that flows between two objects at different electrical potentials. This current can damage the semiconductor and insulating materials of the circuit.

- Provides level conversion: Voltage level must be compatible with external devices.

- Has a small number of pins (low cost)

- Limits slew rates to control high-frequency noise

A brief explanation about the I/O cells from Faraday used in this thesis was given in Section 2.3.1, where the different programmable capabilities were detailed. For our design, a pad-limited version with 8mA output driving strength has been selected due to  $SSO^3$  (simultaneous Switching Output) limitations. With this strength, the maximum output load that can be driven is limited to 41.48pF at 200MHz and to 82.96pF at 100MHz due to electromigration effects (see Section 6.1.2 for more details).

# 3.3 Summary

The different modifications in order to convert an initial FPGA into an ASIC have been explained in this chapter. Also the new components and functionalities were discussed in Section 3.2, were, among other features, an additional method to program the PM was described, and the new component implementing the USB 1.1 standard was introduced.

Next, the test cases used to verify the design and how to apply them using Modelsim will be explained.

$<sup>^{3}</sup>$ In Section 6.1.2 can be seen that 16 I/O power/ground cells have been employed for 54 I/O signal cells, which yields in ratio of almost 7 I/O cells per power/ground pair. According to Faraday documentation, a higher value for the drive strength will result in important SSO noise effects.

As it was mentioned in Section 2.2, Modelsim is used to verify the correct behaviour of the design in three different phases:

- *RTL Behavioural Description*: At this stage, Modelsim is used to check that the design accomplishes with the specifications and product requirements. It has to be pointed out that only the operation is verified, i.e., no timing information is taken into account.

- *Netlist after synthesis*: Once the design is synthesized, all the test benches used in the previous phase has to be rerun in order to check that they produce the same output. The difference is that now, besides checking the correct behavioural of the circuit, the delay of the logic gates is annotated into the simulation to verify the timing requirements.

- *Netlist after place & routing*: When the layout of the circuit has been generated, interconnection delays and more accurate timing information of the gates can be used to rerun again the test benches.

The test benches that have been employed are the same in every phase and are briefly explained in Section 4.1. Afterwards, in Sections 4.2 and 4.3 is explained how to apply a test bench in the three phases. The last section, Section 4.4, discuss the difference when testing the component MyJtag.

# 4.1 Test Benches

A test bench is a piece of HDL (mainly VHDL or Verilog) code that is used to verify the functional correctness of a HDL model. It can be seen as wrapper where the top entity of the design under test (DUT) is instantiated in order to apply stimulus to the DUT and verify the corresponding outputs. In this thesis, the DUT is a microcontroller, so, apart from generating stimulus for the inputs, a program should be load in the PM. How to generate this code is explained in Section 4.1.2 Regarding the use of Modelsim, we refer to [10] for all the details about how to use this tool for simulating a design, but there are two features that deserve to be stressed:

• Loading the PM: Loading instructions into the PM can be performed with the following instruction:

mem load -infile "file.hex" -format hex "MemoryInstanceName"

Where *file.hex* is the file containing the instructions in hexadecimal. This command is very useful, for instance, when the simulation has to be restarted.

• *Tcl/Tk scripting*: Modelsim supports Tcl/Tk scripting which allows us to save a significant amount of time when using the tool more than once. In general, several "simulation

Figure 4.1: Modelsim script

+ correction" cycles have to be executed before obtaining the desired result, where most of the time some steps are repeated without any change.

The combination of these two features can be seen in Figure 4.1. In this example a simulation is executed just typing:

### source simular UART

in the command window. Throughout this chapter the different steps to generate and apply a test bench to the design will be illustrated using one of the test cases explained in Section 4.1.1; we will use, for instance, the UART test case.

### 4.1.1 Test cases

Verifying that a circuit is 100% correct is almost impossible; consequently, some assumption must be taken in order to limit the number of cases to test. In this thesis, the microcontroller core and the USB wishbone slave are functionally correct and synthesisable for an FPGA environment. For that reason, it has been assumed to be sufficient the following test cases:

- UART: This test receives a value through the UART and retransmits again the same value multiplied by 3.

- SPI: The same test case as before is repeated, but now with the SPI.

- MyJtag: The PM is programmed with this component.

- USB: The USB wishbone slave is set and some data is sent.

- Scan Chain: Data has been written to and read from the Scan Chain Wishbone slave using the already mentioned scan chain.

- I/O ports: Some data is write to and read from the three 8-bits I/O ports.

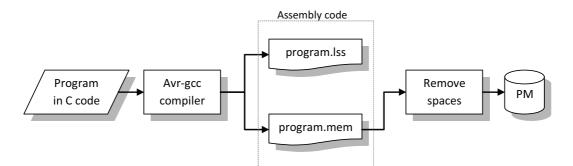

### 4.1.2 Generating the program code

As have been said, for testing a microcontroller, it is necessary to generate the instructions that have to be load into the PM. Fortunately, there exists a complete tool chain for AVR microcontrollers that can be used, among other purposes, to generate the assembly code of the

Figure 4.2: From C to Assembly code

program. One of these tools is the *avr-gcc*, a free-ware C compiler and assembler that allows us to use a high-level programming language like C to generate the assembly instructions as shown in Figure 4.2. The *avr-gcc* generates several files, the most relevant of which for us are the ".lss" and ".mem" files. The ".mem" file contains the operation codes and is used to load the program into the PM, while the ".lss" shows the assembly instructions mnemonics, which is really useful for debugging purposes. An example can be seen in Figure 4.3 for the UART test case. It is important to remember to delete the blank spaces in the ".mem" file because Modelsim does not complain about it, but inserts "00" in every place where it finds a blank space, creating two wrong instructions in place of only one correct instruction:

> $"\_90\_0c" \xrightarrow{To PM} "0094" \& "000c"$ instead of: "940c"  $\xrightarrow{To PM}$  "940c"

# 4.2 RTL Behavioural verification

According to Figure 2.2, at this point of the VLSI design flow, the correct behaviour of the circuit should be checked. In a normal procedure, every component should be tested separately before integrate them all together, but, as was stated in Section 4.1.1, it will be assumed that the microcontroller core (described in VHDL) and the USB wishbone slave (described in Verilog) are functionally correct. Regarding the other components, MyJtag, reset syncrhonizer, reset chain and the *Scan Chain Wishbone slave*, they have been included and tested one by one in the overall design. The first task to perform in order to simulate the DUT is to generate a "test bench file" in VHDL or Verilog<sup>1</sup>, which provides the stimulus. The test bench file used for the UART test case can be seen in Figure 4.4<sup>2</sup>. In order to understand the simulation results in Figure 4.5a, the following has to be taken into account:

- The UART has been configured with a baud rate equal to 62500bps which yields in a symbol period of 16us.

<sup>&</sup>lt;sup>1</sup>Modelsim supports multi-language simulation, consequently it is not a problem that the AVR core is described in VHDL and the USB in Verilog

$<sup>^{2}</sup>$ Only the last part of the file is shown (the stimulus).

```

#include <inttypes.h>

000000a4 <UART_receive >:

#include <avr/io.h>

#include <avr/interrupt.h>

#include <stdlib.h>

//Wait for a character

unsigned char UART_receive (void) {

\#include <avr/pgmspace.h>

#include <avi/pgmspace

#include <stdio.h>

#include "uartCcode.h"

#include "uart.h"

while ( !(\,\texttt{USR}\,\,\&\,\,(1{<}{<}\texttt{RXC}\,)\,)\,)

0x0b, 7

; 11

a4 :

5f 9b

sbis 0x0

<UART_receive>

. -4

; 0 x a 4

a6:

fe cf

rjmp

void

main () {

return UDR:

init_uart ();

sei();

char x,y;

// Initialize UART

// Enable interruptions

Initialize UART

in r24, 0 \times 0 c; 12

8c b1

a8:

}

99 27

eor r25, r25

ac:

08 95

ret

x = UART_receive();

000000 \, \text{ae} \, < \text{main} >:

x = x * 3;

<init_uart>

printf("%c",x);

0e 94 71 01 call

0x2e2

: 0x2e2

ae:

94

b2:

78

sei

for (;;);

0x0b. 7

: 11

b4:

5f 9b

sbis

}

<main+0x6>

rjmp .-4 ; 0xb

in r24, 0x0c ; 12

subi r24, 0xFF ; 255

eor r25, r25

fe cf

b6:

8c b1

8f 5f

//Wait for a character

unsigned char UART_receive (void) {

b8:

ba:

99 27

bc:

while ( !(USR & (1<<RXC))) ;

\substack{ < \texttt{putchar} > \\ 0\texttt{e} \ 94 \ \texttt{d1} \ 01 \ \texttt{call} }

; 0x3a2

be:

0 x 3 a 2

return UDR;

< main + 0x14 >

. -2

c2:

ff cf

rjmp

; 0 x c 2

```

(a)

(b)

Figure 4.3: UART C code (a) and part of the .lss file (b)

```

reset <= '1' after 0 ns,'0' after 200 ns;

sys_clk <= not sys_clk after 5 ns; -- 100 MHz

--Sending a character to the uart at 62500 bps (16 us bit period)

rxdChar:process

begin

rxd <= '1'; wait for 400 us;

rxd <= '0'; wait for 16 us;

rxd <= '0'; wait for 32 us;

rxd <= '0'; wait for 32 us;

rxd <= '1'; wait for 32 us;</pre>

```

Figure 4.4: Stimilus example in a test bench

- The microcontroller is waiting for a character (33 in hexadecimal in the example) that is going to be retransmitted multiplied by 3.

- The frame format is configured with a starting bit (always low) and one stop bit (always high). Furthermore, the transmission starts with the LSB (less significant bit); for that reason, when transmitting a 33 to the *UART* the "rxd" line shows the following binary sequence:

$$33 \rightarrow \underbrace{0}_{\text{data}} \underbrace{11001100}_{\text{data}} \underbrace{1}_{\text{stop}}$$

and in the same way, the expected 99 will be:

$$99 \rightarrow \underbrace{0}_{\text{data}} \underbrace{11001100}_{\text{data}} \underbrace{1}_{\text{stop}}$$

| <ul> <li>/avr_wb_top_tbuart/txd</li> <li>/avr_wb_top_tbuart/rxd</li> </ul> | 1                      |                       |           |               |

|----------------------------------------------------------------------------|------------------------|-----------------------|-----------|---------------|

| A 🖬 💿 Nov                                                                  | 400                    | 000 ns                | 600000 ns |               |

| 💼 🖌 🤤 🧰 Cursor 1                                                           | 1 389 ns               |                       | 704048    | 6.889 ns      |

|                                                                            | (a)                    | RTL simulation        |           |               |

| /avr_wb_top_tbuart/txd<br>/avr_wb_top_tbuart/rxd                           | 1                      |                       |           |               |

| 🛎 📰 👁 🛛 Now                                                                | 800200 ns              | 400000 ns             | 600000 ns | 800000 n      |

| 🗟 🖌 😑 Cursor 1                                                             | 70 4047.835 ns         |                       | 704047    |               |

|                                                                            | (b) Post               | -synthesis simulation |           |               |

|                                                                            |                        |                       |           |               |

| 🛎 🛒 🖲 📃 👘 Now 1200 ns                                                      | <sup>3</sup> 200000 ns | 400000 ns             | 600000 ns |               |

| 💼 🎤 🔍 Cursor 1 .033 ns                                                     | 3                      |                       |           | 704048.033 ns |

(c) Post-layout simulation

Figure 4.5: Simulation of the UART

# 4.3 Synthesised netlist and post-layout netlist verification

The simulation procedure for the synthesised and post-layout netlist is similar to the RTL simulation, but now we have the possibility of including the cell delays and, in the post-layout simulation, the interconnection delays. In order to perform an annotated simulation the SDF files generated by Design Compiler and SOC Encounter (see Section 5.6 and Section 6.7) have to be read into Modelsim. This can be done by adding the following options to the first line of the script presented in Figure 4.1:

vsim - sdftyp "topInstanceNam" = "pathToSDFfile" - sdfnoerror ...

Furthermore, the following replacements in the SDF file generated by SOC Encounter have to be done:

| RBQ() | $\rightarrow$ | (negedge RB) Q ()   |

|-------|---------------|---------------------|

| SBQ() | $\rightarrow$ | (negedge SB) $Q$ () |

| RB QB | $\rightarrow$ | (negedge RB) QB     |

| SB QB | $\rightarrow$ | (negedge SB) QB     |

| SB Q  | $\rightarrow$ | (negedge SB) $Q$    |

otherwise, the timing information related with the "set" and "reset" signal will not be annotated. This is due to some differences in the syntax of the SDF generated by SOC Encounter. For further information about SDF syntax check [10].

Figure 4.6: Opearation code from hexadecimal to VHDL signals

Figure 4.5 shows the repetition of the test bench performed in the previous section. It can be seen the extra delay due to the cell delays in Figure 4.5b and some additional delay in Figure 4.5c due to the interconnections.

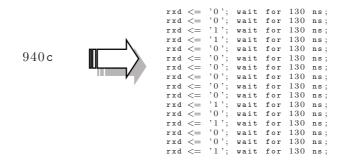

# 4.4 Testing the component MyJtag

Unlike the other test cases, in this one the PM cannot be loaded as before, because that is the purpose of this component. Therefore, in order to test MyJtag, a small application has been developed in C. It receives a file containing the instruction codes in hexadecimal and returns the corresponding VHDL file to test this component. An example of the input and output files can be seen in Figure 4.6. According to this, to prove that this additional programming capability works properly, the other test cases will be loaded into the PM using this method. For instance, the transmission of a character with the SPI. Figure 4.7b shows how the data is being loaded into the PM and in Figure 4.7a it can be seen that everything is working as expected.

# 4.5 Summary

Throughout this chapter the test cases applied to design have been described. It has been discussed also how to generate this test cases and the differences in the different phases of the design flow (RTL behavioural description, post-synthesis and post-layout). Finally, the method employed to test the component MyJtag was explained.

In the following chapter will be discussed how to synthesize the design using Design Compiler and some solutions to increase the clock frequency and reduce the power.

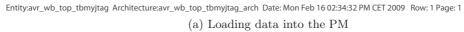

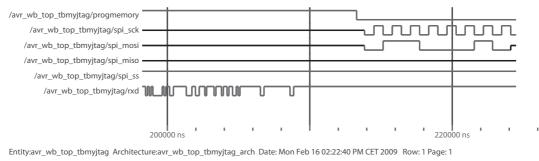

| /avr_wb_top_tbmyjtag/dut/myjtag_inst/progmemory  |      |              |   |      |        |

|--------------------------------------------------|------|--------------|---|------|--------|

| /avr_wb_top_tbmyjtag/dut/myjtag_inst/rxd_in      |      | f            |   | Ļ    |        |

| /avr_wb_top_tbmyjtag/dut/myjtag_inst/shift_reg   |      | 11111111111  |   |      |        |

| /avr_wb_top_tbmyjtag/dut/myjtag_inst/pm_data_reg | 940C | 0050         | 9 | 40C  | 0050   |

| /avr_wb_top_tbmyjtag/dut/myjtag_inst/pm_addr_reg | 001E | 001F         | C | 020  | 0021   |

| /avr_wb_top_tbmyjtag/dut/pm/address              | 001E | 001F         | C | 020  | 0021   |

| /avr_wb_top_tbmyjtag/dut/pm/din                  | 940C | 0050         | 9 | 40C  | 0050   |

| /avr_wb_top_tbmyjtag/dut/pm/dout                 | 940C | <b>0</b> 050 |   | 940C | 0050   |

|                                                  |      | 68000 ns     |   | 720  | 100 ns |

(b) Transmitting a character

Figure 4.7: MyJtag test

In this chapter will be discussed some issues related with performing the design synthesis step using Design Compiler. A nice definition of synthesis can be found on [11]:

"Synthesis is the process of taking a design written in a hardware description language, such as VHDL, and compiling it into a netlist of interconnected gates which are selected from a user-provided library of various gates."

# 5.1 Constraining the design

Among the numerous issues that arises during the synthesis of a design using Design Compiler, the most important ones for the scope of this thesis have been selected and will be detailed in the following subsections.

# 5.1.1 Compile strategy

In order to obtain the best results from Design Compiler, a two-pass compilation strategy should be apply. First, the design has to be compiled with the appropriate options depending on the requirements. In this thesis the timing requirements are more restrictive than the area requirements, therefore an example of a first compilation could be:

# $compile\_ultra \ -timing^1$

Then, the design can be optimized using:

$compile\_ultra$  -incremental

# 5.1.2 Input delay

The synchronizers used in the general digital I/O ports are triggered by a falling edge. If Design Compiler is not aware of this fact, it will assign an input delay of half of the clock period to that pins. To avoid this situation, it has to be specified the maximum input delay and that the delay is relative to the falling edge of the clock:

set\_input\_delay -clock "clkName" -max "delay" -clock\_fall ["listOfports"]

# 5.1.3 Special buffers and inverters for the clock

Normal buffers and inverters have smaller area than the specific ones for the clock, but the second ones are better for balancing and optimizing the clock tree as can be seen in the delay comparison shown in Table 5.1. According to this, clock buffers and inverters should not be used during optimization of the design. This can be achieve using the following command before the incremental compilation:

<sup>&</sup>lt;sup>1</sup> "Compile\_ultra" is only available with DC Ultra license

|         | Load | 1.20  | 00 ff         | 3.01  | 2 ff  | 7.56  | 60 ff | 18.9  | 97 ff         | 47.6  | 52 ff         | 119.  | .5 ff |

|---------|------|-------|---------------|-------|-------|-------|-------|-------|---------------|-------|---------------|-------|-------|

|         | Path | tplh  | $_{\rm tphl}$ | tplh  | tphl  | tplh  | tphl  | tplh  | $_{\rm tphl}$ | tplh  | $_{\rm tphl}$ | tplh  | tphl  |

| BUFX1   | I-O  | 29.80 | 42.98         | 36.69 | 47.73 | 53.27 | 56.32 | 94.54 | 74.18         | 197.5 | 114.6         | 455.5 | 214.0 |

| BUFCKX1 | I-O  | 31.92 | 35.61         | 37.26 | 41.17 | 49.22 | 53.41 | 77.82 | 82.09         | 148.8 | 153.1         | 327.2 | 330.9 |

Table 5.1: Normal and clock buffer delays (ps)

set\_dont\_use "libname"/"cell\_list"

### 5.1.4 Generated clocks

In Section 5.4 will be explained that in some situations, a clock divider can be used in this design. This fact has to be specified in Design Compiler; otherwise, the generated clock will be treated as a normal data signal. For instance, a divided by two clock can be specified by:

create\_generated\_clock -divide\_by 2 -source "source\_clock" [get\_pins "root\_pin"]

# 5.2 Synchronous and asynchronous reset