MOTOROLA Semiconductor Inc.

COMMUNICATIONS & ADVANCED CONSUMER TECHNOLOGY GROUP

# NDUCTOR, INC. **MPC821 APPLICATION DEVELOPMENT SYSTEM** (ADS) **USER'S MANUAL** ARCHIVE

**Board Revision - A**

Issue 0.1 - Draft 8/24/95 - ENG Issue 1.1a - 2/9/96 - ENG Revision Issue 1.2a - 5/6/96 - PILOT Revision Issue 1.3a - 6/26/96 - 'A' Revision

For More Information On This Product, Go to: www.freescale.com . . · - --- - -

## TABLE OF CONTENTS

| 1 | -                | General Information                                                                                                                                                                                       | 1        |

|---|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|   | 1•1<br>1•2       | Introduction                                                                                                                                                                                              | 1        |

|   | 1•2              | Abbreviations' List                                                                                                                                                                                       | 1        |

|   | 1•3              | Related Documentation                                                                                                                                                                                     | 1        |

|   | 1•4              | SPECIFICATIONS<br>MD00014 DD Factures                                                                                                                                                                     | 1        |

|   | 1•5              | MPC821ADS Features                                                                                                                                                                                        | 3        |

|   | 1•6              | Revision Pilot to Revision A Changes                                                                                                                                                                      | 5        |

| • | 1•7              | Revision ENG to Revision PILOT Changes                                                                                                                                                                    | 5        |

| 2 |                  | Hardware Preparation and Installation                                                                                                                                                                     | 7        |

|   | 2•1              | INTRODUCTION                                                                                                                                                                                              | 7        |

|   | 2•2              |                                                                                                                                                                                                           | 7        |

|   | 2•3              | HARDWARE PREPARATION                                                                                                                                                                                      | 7        |

|   | 2•3•1            | Revision ENG to Revision PILOT Changes<br>Hardware Preparation and Installation<br>INTRODUCTION<br>UNPACKING INSTRUCTIONS<br>HARDWARE PREPARATION<br>ADI Port Address Selection<br>Clock Source Selection | 9        |

|   | 2•3•2            | Clock Source Selection                                                                                                                                                                                    | 9        |

|   | 2•3•2•1          | Clock Generator Replacement - 017                                                                                                                                                                         | 9        |

|   | 2•3•3            | Power-On Reset Source Selection                                                                                                                                                                           | 10       |

|   | 2•3•4            | VDDL Source Selection                                                                                                                                                                                     | 11       |

|   | 2•3•5            | Keep Alive Power Source Selection                                                                                                                                                                         | 11       |

|   | 2•4              | INSTALLATION INSTRUCTIONS                                                                                                                                                                                 | 12       |

|   | 2•4•1            | Host Controlled Operation                                                                                                                                                                                 | 12       |

|   | 2•4•2            | Debug Port Controller For Target System                                                                                                                                                                   | 12       |

|   | 2•4•3            | Stand Alone Operation                                                                                                                                                                                     | 13       |

|   | 2•4•4            | +5V Power Supply Connection                                                                                                                                                                               | 14       |

|   | 2•4•5            | P8: +12V Power Supply Connection                                                                                                                                                                          | 14       |

|   | 2•4•6            | ADI Installation                                                                                                                                                                                          | 15       |

|   | 2•4•7            | Host computer to MPC821ADS Connection                                                                                                                                                                     | 15       |

|   | 2•4•8            | Terminal to MPC821ADS RS-232 Connection                                                                                                                                                                   | 15       |

| 2 | 2•4•9            |                                                                                                                                                                                                           | 16       |

| 3 |                  | OPERATING INSTRUCTIONS                                                                                                                                                                                    | 17       |

|   | 3•1<br>2•2       |                                                                                                                                                                                                           | 17       |

|   | 3•2              |                                                                                                                                                                                                           | 17       |

|   | 3•2•1            | SOFT RESET Switch SW1                                                                                                                                                                                     | 17       |

|   | 3•2•2<br>2•2•2   | ABORT Switch SW2                                                                                                                                                                                          | 17       |

|   | 3•2•3<br>2•2•4   | HARD RESET - Switches SW1 & SW2                                                                                                                                                                           | 17       |

|   | 3•2•4<br>3•2•5   | DS2 - Software Options Switch                                                                                                                                                                             | 17<br>18 |

|   | 3•2•5<br>3•2•6   | J4 Power Bridge                                                                                                                                                                                           | 18       |

|   | 3•2•0<br>3•2•7   | GND Bridges<br>RUN Indicator - LD1                                                                                                                                                                        | 18       |

|   | 3•2•8            | FLASH ON - LD2                                                                                                                                                                                            | 18       |

|   | 3•2•8            | DRAM ON - LD3                                                                                                                                                                                             | 18       |

|   | 3•2•9<br>3•2•10  | ETH ON - LD4                                                                                                                                                                                              | 18       |

|   | 3•2•10<br>3•2•11 | Ethernet RX Indicator - LD5                                                                                                                                                                               | 18       |

|   | 3•2•11           | Ethernet TX Indicator - LD6                                                                                                                                                                               | 18       |

|   | 3•2•12           | Ethernet JABB Indicator - LD7                                                                                                                                                                             | 18       |

|   | 3•2•13<br>3•2•14 | IRD ON - LD8                                                                                                                                                                                              | 18       |

|   | 3•2•14<br>3•2•15 | Ethernet CLSN Indicator LD9                                                                                                                                                                               | 18       |

|   | 3•2•15<br>3•2•16 | Ethernet PLR Indicator - LD10                                                                                                                                                                             | 19       |

|   | 3•2•10           | Ethernet LIL Indicator - LD10                                                                                                                                                                             | 19       |

|   | 5-2-17           |                                                                                                                                                                                                           | 19       |

**Freescale Semiconductor, Inc.**

Release 1.3a

#### TABLE OF CONTENTS

|   |             | 3•2•18            | RS232 ON - LD12                                                                                                                                                                                                            | 19       |

|---|-------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|   |             | 3•2•19            | PCMCIA ON - LD13                                                                                                                                                                                                           | 19       |

|   |             | 3•2•20            | 5V Indicator - LD14                                                                                                                                                                                                        | 19       |

|   |             | 3•2•21            | 3.3V Indicator - LD15                                                                                                                                                                                                      | 19       |

|   | 3•3         |                   | MEMORY MAP                                                                                                                                                                                                                 | 20       |

|   | 3•4         |                   | Programming The MPC Registers                                                                                                                                                                                              | 20       |

|   |             | 3•4•1             | Memory Controller Registers Programming                                                                                                                                                                                    | 21       |

| 4 |             |                   | Functional Description                                                                                                                                                                                                     | 34       |

|   | 4•1         |                   | MPC821 Or MPC860                                                                                                                                                                                                           | 34       |

|   | 4•2         |                   | Reset & Reset - Configuration                                                                                                                                                                                              | 34       |

|   |             | 4•2•1             | Keep Alive Power-On Reset                                                                                                                                                                                                  | 34       |

|   |             | 4•2•2             | Main Power - On Reset                                                                                                                                                                                                      | 34       |

|   |             | 4•2•3             | Manual Soft Reset                                                                                                                                                                                                          | 34       |

|   |             | 4•2•4             | Manual Hard Reset                                                                                                                                                                                                          | 35       |

|   |             | 4•2•5             | MPC Internal Sources                                                                                                                                                                                                       | 35       |

|   |             | 4•2•6             | Functional Description<br>MPC821 Or MPC860<br>Reset & Reset - Configuration<br>Keep Alive Power-On Reset<br>Main Power - On Reset<br>Manual Soft Reset<br>Manual Hard Reset<br>MPC Internal Sources<br>Reset Configuration | 35       |

|   |             | 4•2•6•1           | Power - On Reset Configuration                                                                                                                                                                                             | 35       |

|   |             | 4•2•6•2           | Hard Reset Configuration                                                                                                                                                                                                   | 35       |

|   |             | 4•2•6•3           | Soft Reset Configuration                                                                                                                                                                                                   | 36       |

|   | <b>4•</b> 3 |                   | Local Interrupter                                                                                                                                                                                                          | 36       |

|   | <b>4</b> ∙4 |                   | Clock Generator                                                                                                                                                                                                            | 37       |

|   |             | 4•4•1             | SPLL Support                                                                                                                                                                                                               | 37       |

|   | 4•5         |                   | Buffering                                                                                                                                                                                                                  | 37       |

|   | 4•6         | RC                | Chip - Select Generator                                                                                                                                                                                                    | 37       |

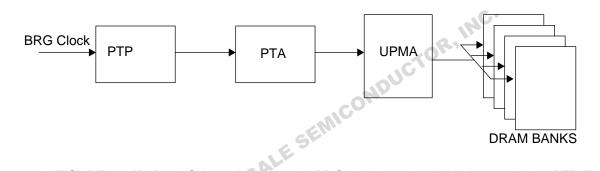

|   | 4•7         | P                 | DRAM                                                                                                                                                                                                                       | 38       |

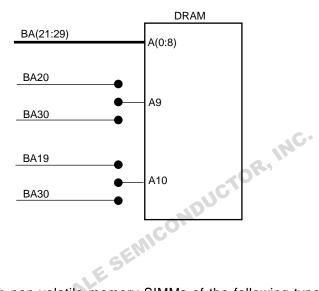

|   |             | 4•7•1             | DRAM 16 Bit Operation                                                                                                                                                                                                      | 38       |

|   |             | 4•7•2             | DRAM Performance Figures                                                                                                                                                                                                   | 39       |

|   |             | 4•7•3             | Refresh Control                                                                                                                                                                                                            | 40       |

|   |             | 4•7•4             | Variable Bus-Width Control                                                                                                                                                                                                 | 41       |

|   | 4•8         |                   | Flash Memory                                                                                                                                                                                                               | 42       |

|   | 4•9         |                   | Ethernet Port                                                                                                                                                                                                              | 44       |

|   | 4•10        |                   | Infra - Red Port                                                                                                                                                                                                           | 44       |

|   | 4•11        |                   | RS232 Port                                                                                                                                                                                                                 | 45       |

|   |             | 4•11•1            | RS-232 Port Signal Description                                                                                                                                                                                             | 45       |

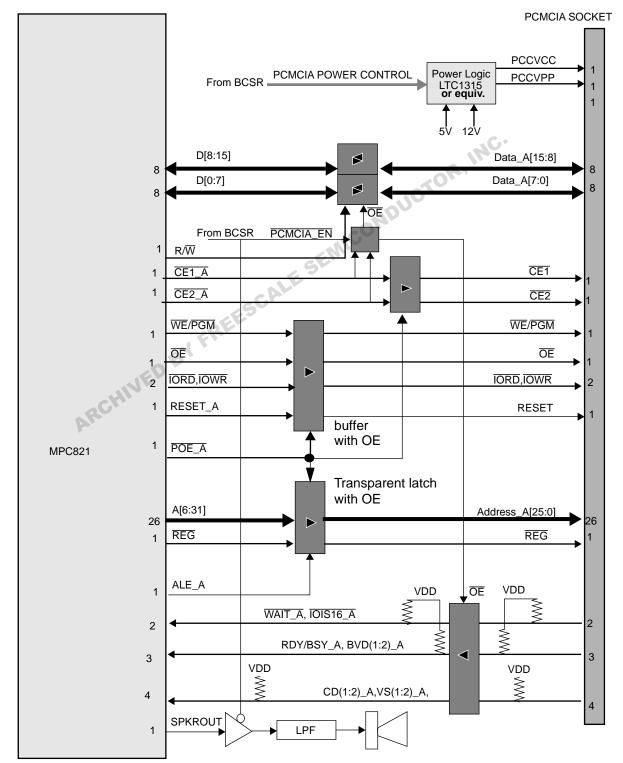

|   | 4•12        |                   | PCMCIA Port                                                                                                                                                                                                                | 45       |

|   |             | 4•12•1            | PCMCIA Power Control                                                                                                                                                                                                       | 46       |

|   | 4•13        |                   | LCD Port                                                                                                                                                                                                                   | 46       |

|   | 4•14        |                   | Board Control & Status Register - BCSR                                                                                                                                                                                     | 48       |

|   |             | 4•14•1<br>4•1.4•0 | BCSR Disable Protection Logic                                                                                                                                                                                              | 48       |

|   |             | 4•14•2            | BCSR0 - Hard Reset Configuration Register                                                                                                                                                                                  | 48       |

|   |             | 4•14•3<br>4•1.4•4 | BCSR1 - Board Control Register                                                                                                                                                                                             | 49       |

|   |             | 4•14•4<br>4•14•5  | BCSR2 - Board Status Register - 1                                                                                                                                                                                          | 51       |

|   |             | 4•14•5            | BCSR3 - Auxiliary Control / Status Register                                                                                                                                                                                | 53<br>56 |

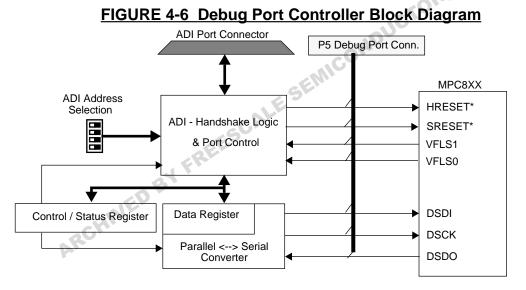

|   | 4•15        |                   | Debug Port Controller<br>MDC 214 DS As Debug Port Controller For Torget System                                                                                                                                             | 56<br>56 |

|   |             | 4•15•1            | MPC821ADS As Debug Port Controller For Target System                                                                                                                                                                       | 56<br>57 |

|   |             |                   | Debug Port Connection - Target System Requirements                                                                                                                                                                         | 57<br>57 |

|   |             | 4•15•2<br>4•15•2  | Debug Port Control / Status Register<br>Standard MPCXXX Debug Port Connector Pin Description                                                                                                                               | 57<br>58 |

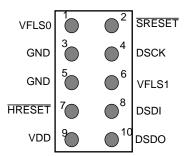

|   |             | 4•15•3            | Standard MPCXXX Debug Port Connector Pin Description                                                                                                                                                                       | 00       |

#### TABLE OF CONTENTS

| 4.15.3.1     | VFLS(0:1)                                                                                                                                                             | 58  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|              | HRESET*                                                                                                                                                               | 58  |

|              | SRESET*                                                                                                                                                               | 59  |

|              | DSDI - Debug-port Serial Data In                                                                                                                                      | 59  |

|              | DSCK - Debug-port Serial Clock                                                                                                                                        | 59  |

|              | DSDO - Debug-port Serial Data Out                                                                                                                                     | 59  |

| 4•16         | Power                                                                                                                                                                 | 59  |

| 4•16•1       | 5V Bus                                                                                                                                                                | 61  |

| 4•16•2       | 3.3V Bus                                                                                                                                                              | 61  |

| 4•16•3       | 2V Bus                                                                                                                                                                | 61  |

| 4•16•4       | 12V Bus                                                                                                                                                               | 61  |

| 4•16•5       | Keep Alive Power                                                                                                                                                      | 61  |

| 5 -          | 5V Bus<br>3.3V Bus<br>2V Bus<br>12V Bus<br>Keep Alive Power<br>Support Information<br>Interconnect Signals<br>P1 ADI - Port Connector<br>P2 - Ethernet Port Connector | 62  |

| 5•1          | Interconnect Signals                                                                                                                                                  | 62  |

| 5•1•1        | P1 ADI - Port Connector                                                                                                                                               | 62  |

| 5•1•2        | P2 - Ethernet Port Connector                                                                                                                                          | 63  |

| 5•1•3        | P3 - RS232 Port Connector                                                                                                                                             | 63  |

| 5•1•4        | PCMCIA Port Connector                                                                                                                                                 | 64  |

| 5•1•5        | P5 - External Debug Port Controller Input Interconnect.                                                                                                               | 66  |

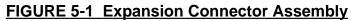

| 5•1•6        | P6, P9, P10 & P12 Expansion and Logic Analyzer Connectors.                                                                                                            | 67  |

| 5•1•6•1      | Connecting Application Boards to the Expansion Connectors                                                                                                             | 67  |

| 5•1•7        | P7 - 5V Power Connector                                                                                                                                               | 88  |

| 5•1•8        | P8 - 12V Power Connector                                                                                                                                              | 88  |

| 5•1•9        | P11 - LCD Connector                                                                                                                                                   | 88  |

| 5•1•10       | P13 - QUADS Compatible Communication Connector                                                                                                                        | 90  |

| 5•2          | MPC821ADS Part List                                                                                                                                                   | 95  |

| APPENDIX A - | Programmable Logic Equations                                                                                                                                          | 101 |

| A•1          | U7 - Debug Port Controller                                                                                                                                            | 102 |

| A•2          | U10 - Auxiliary Board Control                                                                                                                                         | 126 |

| A•3          | U11 - Board Control & Status Register                                                                                                                                 | 142 |

| APPENDIX B - | ADI I/F                                                                                                                                                               | 174 |

| B•1          | ADI Port Signal Description                                                                                                                                           | 174 |

| APPENDIX C - | ADI Installation                                                                                                                                                      | 176 |

| C•1          | INTRODUCTION                                                                                                                                                          | 176 |

| C•2          | IBM-PC/XT/AT to MPC821ADS Interface                                                                                                                                   | 176 |

| C•2•1        | ADI Installation in IBM-PC/XT/AT                                                                                                                                      | 176 |

| C•3          | SUN-4 to MPC821ADS Interface                                                                                                                                          | 177 |

| C•3•1        | ADI Installation in the SUN-4                                                                                                                                         | 178 |

### LIST OF FIGURES

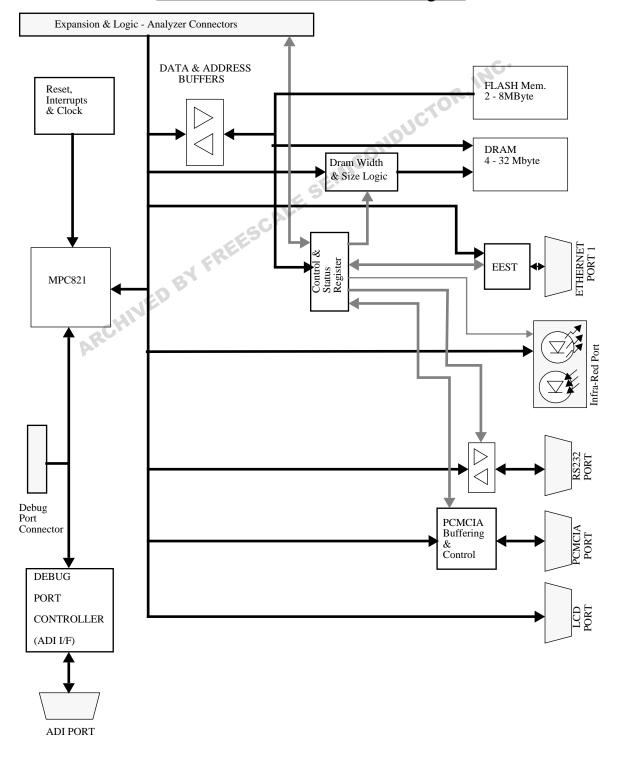

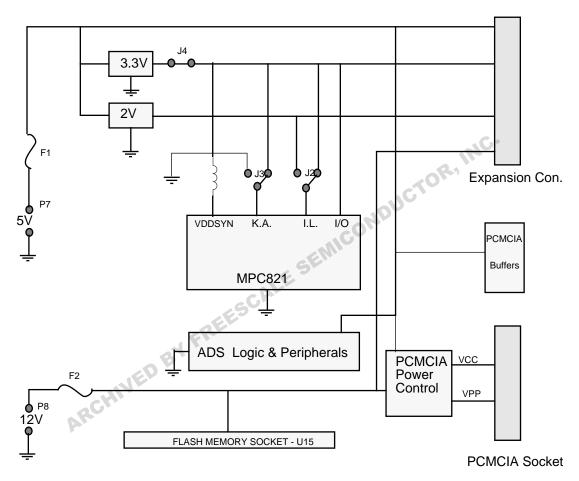

| FIGURE 1-1  | MPC821ADS Block Diagram                                                                                     | 4   |

|-------------|-------------------------------------------------------------------------------------------------------------|-----|

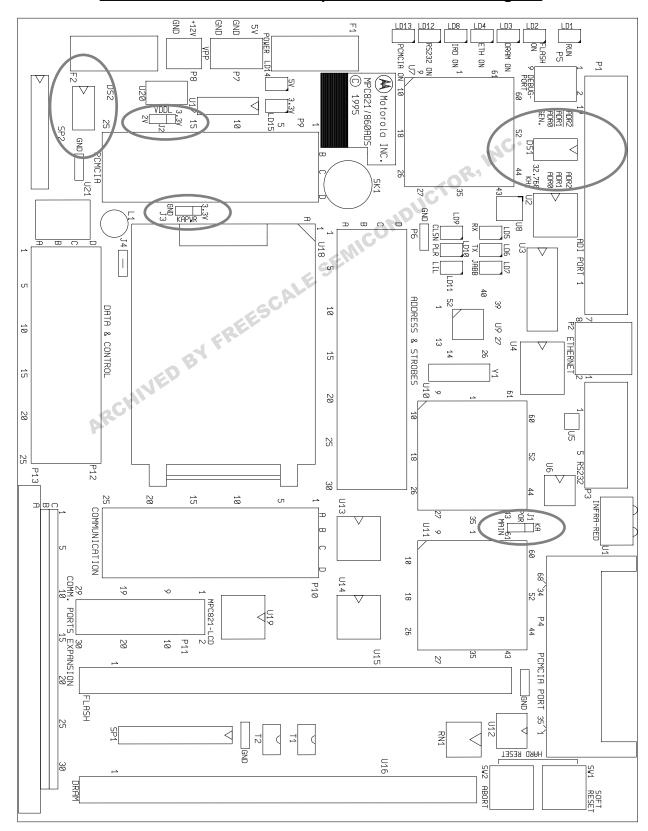

| FIGURE 2-1  | MPC821ADS Top Side Part Location diagram                                                                    | 8   |

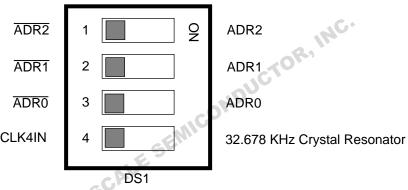

| FIGURE 2-2  | Configuration Dip-Switch - DS1                                                                              | 9   |

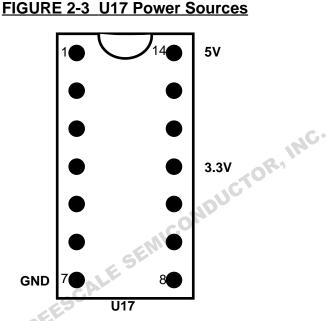

| FIGURE 2-3  | U17 Power Sources                                                                                           | 10  |

| FIGURE 2-4  | Power-On Reset Source Selection                                                                             | 11  |

| FIGURE 2-5  | VDDL Source Selection                                                                                       | 11  |

| FIGURE 2-6  | Keep Alive Power Source Selection                                                                           | 12  |

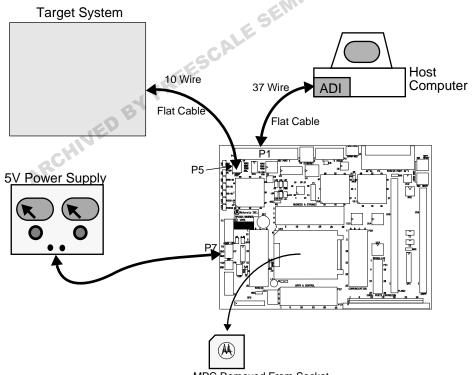

| FIGURE 2-7  | Host Controlled Operation Scheme                                                                            | 12  |

| FIGURE 2-8  | Debug Port Controller For Target System Operation Scheme                                                    | 13  |

| FIGURE 2-9  | Stand Alone Configuration                                                                                   | 14  |

| FIGURE 2-10 | Stand Alone Configuration<br>P7: +5V Power Connector<br>P8: +12V Power Connector<br>P1 - ADI Port Connector | 14  |

| FIGURE 2-11 | P8: +12V Power Connector                                                                                    | 15  |

| FIGURE 2-12 | P1 - ADI Port Connector                                                                                     | 15  |

| FIGURE 2-13 | P3 - RS-232 Serial Port Connector                                                                           | 16  |

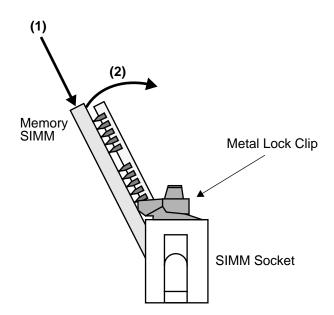

| FIGURE 2-14 | Memory SIMM Installation                                                                                    | 16  |

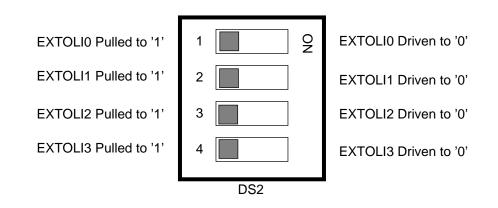

| FIGURE 3-1  | DS2 - Description                                                                                           | 17  |

| FIGURE 4-1  | Refresh Scheme                                                                                              | 40  |

| FIGURE 4-2  | DRAM Address Lines' Switching                                                                               | 42  |

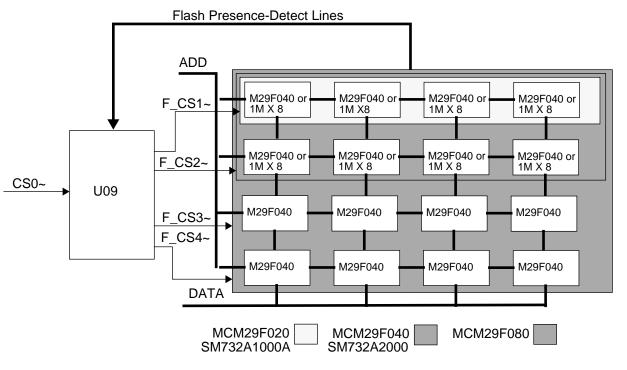

| FIGURE 4-3  | Flash Memory SIMM Architecture                                                                              | 43  |

| FIGURE 4-4  | RS232 Serial Port Connector                                                                                 | 45  |

| FIGURE 4-5  | PCMCIA Port Configuration                                                                                   | 47  |

| FIGURE 4-6  | Debug Port Controller Block Diagram                                                                         | 56  |

| FIGURE 4-7  | Standard Debug Port Connector                                                                               | 58  |

| FIGURE 4-8  | MPC821ADS Power Scheme                                                                                      | 60  |

| FIGURE A-1  | ADI Port Connector                                                                                          | 174 |

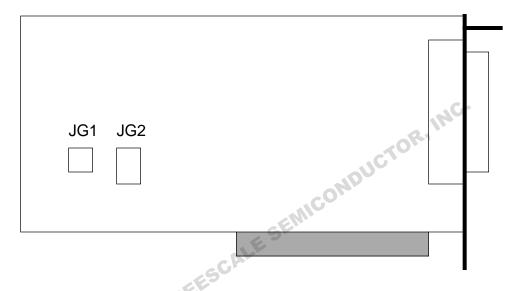

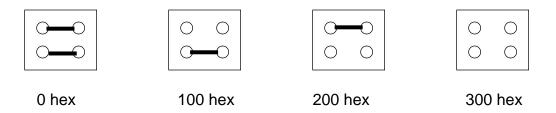

| FIGURE A-1  | Physical Location of jumper JG1 and JG2                                                                     | 177 |

| FIGURE A-2  | JG1 Configuration Options                                                                                   | 177 |

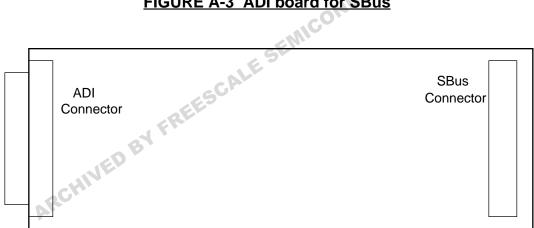

| FIGURE A-3  | ADI board for SBus                                                                                          | 178 |

· · · <del>·</del> · · · · · · ·

---- -

#### LIST OF TABLES

| TABLE 1-1.  | MPC821ADS Specifications                          | 1  |

|-------------|---------------------------------------------------|----|

| TABLE 3-1.  | MPC821ADS Main Memory Map                         | 20 |

| TABLE 3-2.  | SIU REGISTERS' PROGRAMMING                        | 21 |

| TABLE 3-3.  | Memory Controller Initializations For 50Mhz       | 22 |

| TABLE 3-4.  | UPMA Initializations for 60nsec DRAMs @ 50MHz     | 24 |

| TABLE 3-5.  | UPMA Initializations for 70nsec DRAMs @ 50MHz     | 25 |

| TABLE 3-6.  | UPMA Initializations for 60nsec EDO DRAMs @ 50MHz | 26 |

| TABLE 3-7.  | UPMA Initializations for 70nsec EDO DRAMs @ 50MHz | 27 |

| TABLE 3-8.  | Memory Controller Initializations For 25Mhz       | 27 |

| TABLE 3-9.  | UPMA Initializations for 60nsec DRAMs @ 25MHz     | 30 |

| TABLE 3-10. | UPMA Initializations for 70nsec DRAMs @ 25MHz     | 31 |

| TABLE 3-11. | UPMA Initializations for 60nsec EDO DRAMs @ 25MHz | 32 |

| TABLE 3-12. | UPMA Initializations for 70nsec EDO DRAMs @ 25MHz | 33 |

| TABLE 4-1.  | Regular DRAM Performance Figures                  | 39 |

| TABLE 4-2.  | EDO DRAM Performance Figures                      | 39 |

| TABLE 4-3.  | DRAM ADDRESS CONNECTIONS                          | 42 |

| TABLE 4-4.  | Flash Memory Performance Figures                  | 44 |

| TABLE 4-5.  | BCSR0 Description                                 | 49 |

| TABLE 4-6.  | BCSR1 Description                                 | 50 |

| TABLE 4-7.  | PCCVPP(0:1) Assignment                            | 51 |

| TABLE 4-8.  | BCSR2 Description                                 | 52 |

| TABLE 4-9.  | Flash Presence Detect (4:1) Encoding              | 52 |

| TABLE 4-10. | DRAM Presence Detect (2:1) Encoding               | 53 |

| TABLE 4-11. | DRAM Presence Detect (4:3) Encoding               | 53 |

| TABLE 4-12. | EXTOOLI(0:3) Assignment                           | 53 |

| TABLE 4-13. | BCSR3 Description                                 | 54 |

| TABLE 4-14. | MPC821ADS Revision Number Conversion Table        | 54 |

| TABLE 4-15. | FLASH Presence Detect (7:5) Encoding              | 55 |

| TABLE 4-16. | Debug Port Control / Status Register              | 57 |

| TABLE 4-17. | Off-board Application Maximum Current Consumption | 60 |

| TABLE 5-1   | P1 - ADI Port Interconnect Signals                | 62 |

| TABLE 5-2   | P2 - Ethernet Port Interconnect Signals           | 63 |

| TABLE 5-3   | P3 - Interconnect Signals                         | 63 |

| TABLE 5-4.  | P4 - PCMCIA Connector Interconnect Signals        | 64 |

| TABLE 5-5.  | P5 - Interconnect Signals                         | 67 |

| TABLE 5-6.  | P6 - Interconnect Signals                         | 69 |

| TABLE 5-7.  | P9 - Interconnect Signals                         | 74 |

| TABLE 5-8.  | P10 - Interconnect Signals                        | 79 |

| TABLE 5-9.  | P12 - Interconnect Signals                        | 84 |

| TABLE 5-10. | P7 - Interconnect Signals                         | 88 |

| TABLE 5-11. | P8 - Interconnect Signals                         | 88 |

| TABLE 5-12. | P11 - Interconnect Signals                        | 89 |

| TABLE 5-13. | P13 - Interconnect Signals                        | 91 |

| TABLE 5-14. | MPC821ADS Part List                               | 95 |

|             |                                                   |    |

Release 1.3a

#### **General Information**

## 1 - General Information

#### 1•1 Introduction

This document is an operation guide for the MPC821ADS board. It contains operational, functional and general information about the ADS. The MPC821ADS is meant to serve as a platform for s/w and h/w development around the MPC821. Using its on-board resources and its associated debugger, a developer is able to load his code, run it, set breakpoints, display memory and registers and connect his own proprietary h/w via the expansion connectors, to be incorporated to a desired system with the pda.

This board could also be used as a demonstration tool, i.e., application s/w may be burned<sup>A</sup> into its flash ,IICONIDUCTOR memory and ran in exhibitions etc'.

#### 1•2 Abbreviations' List

- PDA Personal Digital Assistant, the MPC821 •

- **UPM User Programmable Machine**

- GPCM General Purpose Chip-select Machine

- GPL General Purpose Line (associated with the UPM)

- I/R Infra-Red

- MPCADS the MPC821ADS, the subject of this document.

- BSCR Board Control & Status Register.

- ZIF Zero Input Force

- BGA Ball Grid Array

#### 1•3 **Related Documentation**

- MPC821 User's Manual.

- MC68160 Data Sheet.

- ADI Board Specification.

#### 1•4 SPECIFICATIONS

The MPC821ADS specifications are given in TABLE 1-1.

#### **TABLE 1-1. MPC821ADS Specifications**

| CHARACTERISTICS                               | SPECIFICATIONS                                          |

|-----------------------------------------------|---------------------------------------------------------|

| Power requirements (no other boards attached) | +5Vdc @ 1.7 A (typical), 3 A (maximum)<br>+12Vdc - @1A. |

| Microprocessor                                | MPC821 @ 50 MHz                                         |

#### **General Information**

#### TABLE 1-1. MPC821ADS Specifications

| CHARACTERISTICS                                    | SPECIFICATIONS                                                                                              |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| Addressing<br>Total address range:<br>Flash Memory | 4 GigaBytes<br>2 MByte, 32 bits wide expandable to 8 MBytes                                                 |

| Dynamic RAM                                        | 4 MByte, 36 bits wide SIMM (32 bit data, 4 bit parity)<br>option to use higher density SIMM, up to 32 MByte |

| Operating temperature                              | 0°C - 30°C                                                                                                  |

| Storage temperature                                | -25°C to 85°C                                                                                               |

| Relative humidity                                  | 5% to 90% (non-condensing)                                                                                  |

| Dimensions:<br>Height<br>Depth<br>Thickness        | 9.173 inches (233 mm)<br>7.08 inches (180 mm)<br>0.063 inches (1.6 mm)                                      |

ARCHIVED BY FREESCA

#### **General Information**

#### 1•5 MPC821ADS Features

- MPC821, running up to 50 MHz, mounted on ZIF BGA socket.

- 4 MBytes of 60-nsec DRAM, support is given to various types of memory varying from 4MByte configured as 1M X 32, upto 32MByte configured as 8M X 32.

- Support for EDO page mode DRAM SIMMs made by Micron - the MT8D432X and the MT16D832X. puctor, INC.

- Automatic Dram SIMM identification.

- □ 2 MByte Flash SIMM. Support for upto 8 MByte.

- Automatic Flash SIMM identification.

- Memory Disable Option for all local memory map slaves.

- Board Control & Status Register BCSR, Controlling Board's Operation.

- Programmable Hard-Reset Configuration via BCSR.

- **T.P.** Ethernet port via MC68160 EEST on SCC1 with Standby Mode.

- Infra-Red Transceiver on SCC2 with Shutdown Option.

- 5V-only PCMCIA Socket With Full Buffering, Power Control and Port Disable Option. Complies with PCMCIA 2.1+ Standard.

- Module Enable Indications.

- RS232 port on SMC1 with Low-Power Option.

- On Board Debug Port Controller with ADI I/F.

- MPC821ADS Serving as Debug Station for Target System option.

- LCD Display Connector.

- Optional Hard-Reset Configuration Burned in Flash<sup>A</sup>.

- All MPC Pins Available At Expansion & Logic Analyzer Connectors.

- External Tools' Identification Capability, via BCSR.

- Soft / Hard Reset Push Button

- ABORT Push Button

- Single<sup>B</sup> 5V Supply.

- Reverse / Over Voltage Protection for Power Inputs.

- 3.3V / 2V MPC Internal Logic Operation, 3.3V MPC I/O Operation.

A. Available only if supported also on-chip.

B. Unless a 12V supply is required for a PCMCIA card.

#### **General Information**

- □ External Keep Alive Power Source Option.

- Dever Indications for Each Power Bus.

- Software Option Switch provides 16 S/W options via BCSR.

FIGURE 1-1 MPC821ADS Block Diagram

#### **General Information**

#### **1•6** Revision Pilot to Revision A Changes

- 1) DS2 which on PILOT revision was connected on SP2 with blue wires, is now integrated into the PCB, located nearby SP2.

- UA38 which on revision PILOT was glued and connected with blue-wires, is now integrated into the PCB. Gate allocation within UA38, is different from revision PILOT, to provide better PCB routing.

- 3) Revision code in BCSR is changed to 2.

- 4) Added optional RA21 (0 ohm) and CA7 (0.01µF) for 10-Base-T interface network.

- 5) Some SMD pads were enlarged to assist manufacturing.

#### 1•7 Revision ENG to Revision PILOT Changes

- 1) Added support for ads to function as debug station:

- Added independent 20MHz clock generator for debug port controller

- Added MUX (U38) so that internal logic is clocked by the above generator

- Removed pervious debug clock logic, derived from CLKOUT of the MPC.

- Added signal named CHINS~ (CHip-In-Socket, active-low) which is connected to one of the MPC's GND pins (isolated from GND layer). This signal controls the above mux and the indication LEDs illumination.

- Added pull-up resistors on the Chip-Select lines, to avoid possible data-bus contention when MPC is off-socket.

- DRAMEN~ becomes active-low to allow buffer manipulation supporting LEDs darkness when MPC off-socket. Signal RUN becomes active-high from the same reason.

(Sh. 1, 7, 8, 9, 11, 14)

- Signals EXTM(1:4) changed to BADDR(28:30),AS~ correspondingly, to support future external master support. (Sh. 1, 11, 13)

- 3) MODCK0 renamed to MODCK2, to comply with MPC's spec convention. (Sh 1, 3, 13)

- 4) Signal BCLOS~, which was optional for data buffers' enable logic, is found redundant and removed from ADS logic. Renamed to GPL4A~. (Sh 1, 2, 3, 12)

- 5) Added 3 Flash memory Presence Detect lines F\_PD(5:7) to BCSR (U11/65:67) (ENG U10) to support varying flash memory delays. (Sh 3, 4, 11)

- 6) Added support for SMART flash simms:

- 12V VPP connected to SIMM

- BA10 connected also to the SIMM, to support 1M X 8 devices

(Sh. 4)

- 7) BCSR power on reset logic was changed to support board's power-up recovery when keep-alive power remained active. (Sh. 3, 9)

- 8) Power-on reset logic changes:

- KA power-on reset is not driven by U10 (ENG U9) but directly to the MPC.

- Added AC14 (U23) powered by KAPWR to support this. (AC14's s-t is required for mach connection due to slow rise time of PORST~)

- D3 and R12 powered from KAPWR from the same reason.

- Added option for PON reset by main 3.3V bus. (J1)

Release 1.3a

#### For More Information On This Product, Go to: www.freescale.com

#### **General Information**

(Sh. 3, 9)

- 9) BA9 and BA10 are connected to U10 (ENG U9) instead of BA11 and BA12, for flash bank selection. Bug correction. (Sh. 3)

- 10) Renewed support for 32Khz crystal:

- CLK4IN is gated (UA38), so when working with 32768 Hz crystal, CLK4IN is driven constantly to '0'. This, to avoid clock jitter with this mode of operation.

- Parallel resistor increased to 20MΩ.

(Sh. 7)

11) PLL's XFC capacitors were changed to react for formula change. Lower MF range capacitor is changed to 5nF to cover 1:5 to 1:10 MF range, while higher MF range capacitor was changed to 0.68uF to cover 1:458<sup>A</sup> to 1:1220<sup>B</sup> MF range

(Sh. 7)

- 12) PCMCIA power controller is changed to LTC1315 (by Linear Technologies):

- PCCVPPG~ signal and indication are removed, not supported by this device

- VPP selection code is changed.

- DRAMEN no longer controls power to the dram.

- Old 12V voltage pump remains as contingency for possible unavailability of the device, although the device switching outputs drive 12V. R55, R56 & R59 are therefore not assembled.

(Sh. 3, 9)

- 13) Added ADS board revision tag in BCSR.

- 14) Added signals RS\_EN~ and ETHEN~ to P13 Quads Compatible connector, for tool designer benefit. (Sh. 16)

- 15) Added 4-switches dip-switch DS2, connected over EXTOLI(0:3) lines, to provide s/w option selection capability.

A. Lowest MF allowed with 32768 Hz crystal, due to 15MHz minimal PLL frequency.

B. Highest MF allowed with 32768 Hz crystal, considering 40MHz rated MPC.

Hardware Preparation and Installation

## 2 - Hardware Preparation and Installation

## 2•1 INTRODUCTION

This chapter provides unpacking instructions, hardware preparation, and installation instructions for the MPC821ADS.

## 2•2 UNPACKING INSTRUCTIONS

#### <u>NOTE</u>

If the shipping carton is damaged upon receipt, request carrier's agent to be present during unpacking and inspection of equipment.

Unpack equipment from shipping carton. Refer to packing list and verify that all items are present. Save packing material for storing and reshipping of equipment.

#### **CAUTION**

AVOID TOUCHING AREAS OF INTEGRATED CIRCUITRY; STATIC DISCHARGE CAN DAMAGE CIRCUITS.

#### 2•3 HARDWARE PREPARATION

To select the desired configuration and ensure proper operation of the MPC821ADS board, changes of the Dip-Switch settings may be required before installation. The location of the switches, LEDs, Dip-Switches, and connectors is illustrated in FIGURE 2-1. The board has been factory tested and is shipped with Dip-Switch settings as described in the following paragraphs. Parameters can be changed for the following conditions:

- ADI port address

- MPC Clock Source

- Power-On Reset Source.

- MPC Keep Alive Power Source

- MPC Internal Logic Supply Source

Hardware Preparation and Installation FIGURE 2-1 **MPC821ADS Top Side Part Location diagram**

Freescale Semiconductor, Inc.

Release 1.3a

#### Hardware Preparation and Installation

#### 2•3•1 ADI Port Address Selection

The MPC821ADS can have eight possible slave addresses set for its ADI port, enabling up to eight MPC821ADS boards to be connected to the same ADI board in the host computer. The selection of the slave address is done by setting switches 1, 2 & 3 in the Dip-Switch - DS1. Switch 1 stands for the most-significant bit of the address and switch 3 stands for the least-significant bit. If the switch is in the 'ON' state, it stands for logical '1'. In FIGURE 2-2 DS1 is shown to be configured to address '0'.

#### FIGURE 2-2 Configuration Dip-Switch - DS1

3 - 5 MHz Generator via CLK4IN

Table 2-1 describes the switch settings for each slave address:

#### Table 2-1 ADI Address Selection

| ADDRESS | Switch 1 | Switch 2 | Switch 3 |

|---------|----------|----------|----------|

| 0 PC    | OFF      | OFF      | OFF      |

| 1       | OFF      | OFF      | ON       |

| 2       | OFF      | ON       | OFF      |

| 3       | OFF      | ON       | ON       |

| 4       | ON       | OFF      | OFF      |

| 5       | ON       | OFF      | ON       |

| 6       | ON       | ON       | OFF      |

| 7       | ON       | ON       | ON       |

#### 2•3•2 Clock Source Selection

Switch #4 on DS1 selects the clock source for the MPC. When it is in the 'ON' position while the ADS is powered-up, the on-board 32.768 KHz crystal resonator becomes the clock source and the PLL multiplication factor becomes 1:513. When switch #4 is in the 'OFF' position while the ADS is powered-up, the on-board 4<sup>A</sup>MHz clock generator (U17) becomes the clock source while the PLL multiplication factor becomes 1:5.

#### 2•3•2•1 Clock Generator Replacement - U17

When replacing U17 with another clock generator it should be noticed that there are 2 supply level available at U17:

1) 5V supply at pin 14.

A. A 5MHz clock generator is provided as well.

#### Hardware Preparation and Installation

2) 3.3V supply available at pin 11.

From looking at FIGURE 2-3 "U17 Power Sources" above, we see that 5V oscillator may be used with 14 pins only form-factor while 3.3V oscillators may be used with 8 pins only form-factor.

#### **WARNING**

IF A 14 Pin Form-Factor, 3.3V Clock Generator is inserted to U17, PERMANENT DAMAGE Might Be Inflicted To The Device.

#### WARNING

Since the MPC clock input is NOT 5V FRIENDLY, any clock generator inserted to U17, MUST BE 3.3V compatible. If a 5V output clock generator is inserted to U17, PERMANENT DAMAGE might be inflicted to the MPC.

#### 2•3•3 Power-On Reset Source Selection

As there are differences between MPC revisions regarding the functionality of the Power-On Reset logic, it is therefore necessary to select different sources for Power-ON reset generation.

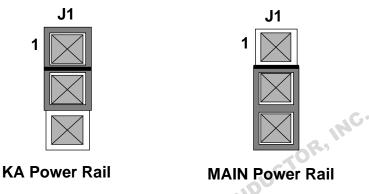

J1 on the ADS is used to select Power-On Reset source: when a jumper is placed between positions 1 - 2 of J1, Power-On reset to the MPC is generated by the Keep-Alive power rail. I.e., When KAPWR goes below 2.005V - Power-On reset is generated. When a jumper is place between position 2 - 3 of J1, Power-On reset to the MPC is generated from the MAIN 3.3V power rail. I.e., when the MAIN 3.3V power rail goes below 2.805V Power-On reset is generated.

Hardware Preparation and Installation FIGURE 2-4 Power-On Reset Source Selection

#### 2•3•4 VDDL Source Selection

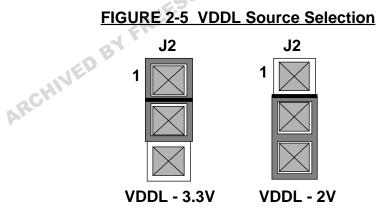

J2 serves as a selector for VDDL - MPC internal logic supply. When a jumper is placed between positions 1 - 2 of J2, VDDL is supplied with 3.3V. When a jumper is placed between positions 2 - 3 of J2, VDDL is supplied by 2V power source. The jumper on J2 is factory set between positions 1 - 2 to supply 3.3 to VDDL.

#### 2•3•5 Keep Alive Power Source Selection

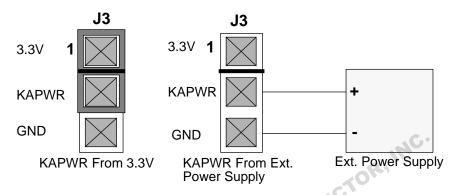

J3 selects the Keep Alive power source of the MPC. When a jumper is placed between positions 1 - 2 of J3, the Keep Alive power is fed from the main 3.3V bus. When an external power source<sup>A</sup> is to be connected to the Keep Alive power rail, it should be connected between positions 2 (the positive pole) and position 3 (GND) of J3.

A. E.g., a battery.

Hardware Preparation and Installation

FIGURE 2-6 Keep Alive Power Source Selection

## **2•4** INSTALLATION INSTRUCTIONS

When the MPC821ADS has been configured as desired by the user, it can be installed according to the required working environment as follows:

- Host Controlled Operation

- Debug Port Controller for Target System

- Stand-Alone

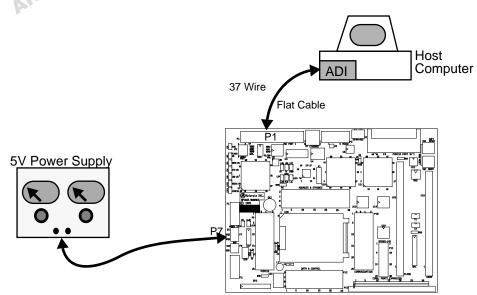

#### 2•4•1 Host Controlled Operation

In this configuration the MPC821ADS is controlled by a host computer via the ADI through the debug port. This configuration allows for extensive debugging using on-host debugger.

#### 2•4•2 Debug Port Controller For Target System

This configuration resembles the previous, but here the local MPC is removed from its socket while the ADS is connected via a 10 lead Flat-Cable between P5 and a matching connector on a target system.

#### Hardware Preparation and Installation

#### **WARNING**

When connecting the ADS to a target system via P5 and a 10 lead flat-cable, the MPC MUST be REMOVED from its SOCKET (U18). Otherwise, PERMANENT DAMAGE might be inflicted to either the Local MPC or to the Target MPC.

With this mode of operation, all on-board modules are disabled and can not be accessed in anyway, except for the debug port controller. Also, all indications except for 5V power, 3.3V power and RUN are darkened.

All debugger commands and debugging features are available in this mode, including s/w download, breakpoints, etc'... The target system may be reset or interrupted by the debug port or reset by the ADS's RESET switches. It is the responsibility of the target system designer, to provide Power-On-Reset and HARD-Reset configurations, while SOFT-Reset configuration is provided by the debug-port controller. See also 4•15•1 "MPC821/860ADS As Debug Port Controller For Target System" on page 56.

#### FIGURE 2-8 Debug Port Controller For Target System Operation Scheme

MPC Removed From Socket

#### 2•4•3 Stand Alone Operation

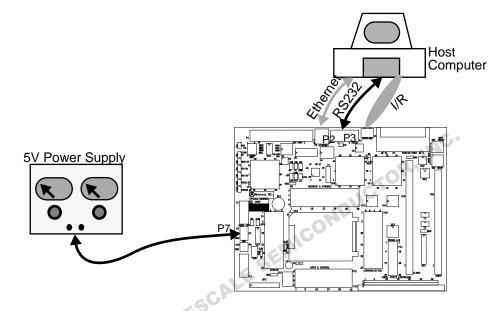

In this mode, the board is not controlled by the host via the ADI/Debug port. It may connect to host via one of its other ports, e.g., RS232 port, I/R port, Ethernet port, etc'. Operating in this mode requires an application program to be programmed into the board's Flash memory (while with the host controlled operation, no memory is required at all).

Hardware Preparation and Installation FIGURE 2-9 Stand Alone Configuration

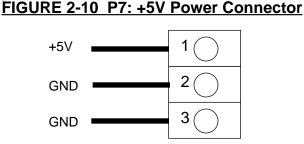

#### 2•4•4 +5V Power Supply Connection

The MPC821ADS requires +5 Vdc @ 5 A max, power supply for operation. Connect the +5V power supply to connector P7 as shown below:

P7 is a 3 terminal block power connector with power plug. The plug is designed to accept 14 to 22 AWG wires. It is recommended to use 14 to 18 AWG wires. To provide solid ground, two Gnd terminals are supplied. It is recommended to connect both Gnd wires to the common of the power supply, while VCC is connected with a single wire.

#### <u>NOTE</u>

Since hardware applications may be connected to the MPC821ADS using the expansion connectors P6, P9, P10, P12 or P13, the additional power consumption should be taken into consideration when a power supply is connected to the MPC821ADS.

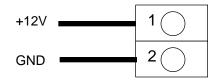

#### 2•4•5 P8: +12V Power Supply Connection

The MPC821ADS requires +12 Vdc @ 1 A max, power supply for the PCMCIA channel Flash programming capability. The MPC821ADS can work properly without the +12V power supply, if there is no need to program a 12V programmable PCMCIA flash card.

Connect the +12V power supply to connector P6 as shown below:

Release 1.3a

# Freescale Semiconductor, Inc.

#### For More Information On This Product, Go to: www.freescale.com

Hardware Preparation and Installation

#### FIGURE 2-11 P8: +12V Power Connector

P8 is a 2 terminal block power connector with power plug. The plug is designed to accept 14 to 22 AWG wires. It is recommended to use 14 to 18 AWG wires.

#### 2•4•6 ADI Installation

For ADI installation on various host computers, refer to APPENDIX C - "ADI Installation" on page 176.

#### 2•4•7 Host computer to MPC821ADS Connection

The MPC821ADS ADI interface connector, P1, is a 37 pin, male, D type connector. The connection between the MPC821ADS and the host computer is by a 37 line flat cable, supplied with the ADI board. FIGURE 2-12 below shows the pin configuration of the connector.

#### FIGURE 2-12 P1 - ADI Port Connector

| C.                                                                                                                                                    |                                                                                                          |                                                                                                      |                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Gnd<br>Gnd<br>Gnd<br>Gnd<br>Gnd<br>(+ 12 v) N.C.<br>HOST_VCC<br>HOST_VCC<br>HOST_VCC<br>HOST_ENABLE~<br>Gnd<br>Gnd<br>Gnd<br>PD0<br>PD2<br>PD4<br>PD6 | 20<br>21<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>37 | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>9 | N.C<br>D_C~<br>HST_ACK<br>ADS_SRESET<br>ADS_HRESET<br>ADS_SEL2<br>ADS_SEL1<br>ADS_SEL0<br>HOST_REQ<br>ADS_REQ<br>ADS_ACK<br>N.C.<br>N.C.<br>N.C.<br>N.C.<br>PD1<br>PD3<br>PD5<br>PD7 |

NOTE: Pin 26 on the ADI is connected to +12 v power supply, but it is not used in the MPC821ADS.

#### 2•4•8 Terminal to MPC821ADS RS-232 Connection

A serial (RS232) terminal or any other RS232 equipment, may be connected to the RS-232 connector P3. The RS-232 connector is a 9 pin, female, D-type connector as shown in FIGURE 2-13.

The connector is arranged in a manner that allows for 1:1 connection with the serial port of an IBM-AT<sup>A</sup> or compatibles, i.e. via a flat cable.

A. IBM-AT is a trademark of International Business Machines Inc.

Hardware Preparation and Installation

#### FIGURE 2-13 P3 - RS-232 Serial Port Connector

| CD  | 1 | 0 |      |

|-----|---|---|------|

| ΤХ  | 2 | 6 | DSR  |

|     |   | 7 | RTS  |

| RX  | 3 | 8 | CTS  |

| DTR | 4 | - |      |

|     |   | 9 | N.C. |

| GND | 5 |   |      |

|     |   |   |      |

CONDUCTOR, INC. NOTE: The RTS line (pin 7) is not connected on the MPC821ADS.

#### 2•4•9 Memory Installation

The MPC821ADS is supplied with two types of memory SIMM:

- **Dynamic Memory SIMM** •

- Flash Memory SIMM. •

To avoid shipment damage, these memories are packed aside rather than being installed in their sockets. Therefore, they should be installed on site. To install a memory SIMM, it should be taken out of its package, put diagonally in its socket (no error can be made here, since the Flash socket has 80 contacts, while the DRAM socket has 72) and then twisted to a vertical position until the metal lock clips are locked. See FIGURE 2-14 "Memory SIMM Installation" below.

#### CAUTION

The memory SIMMs have alignment nibble near their #1 pin. It is important to align the memory correctly before it is twisted, otherwise damage might be inflicted to both the memory SIMM and its socket.

#### FIGURE 2-14 Memory SIMM Installation

#### **OPERATING INSTRUCTIONS**

#### **3 - OPERATING INSTRUCTIONS**

#### 3•1 INTRODUCTION

This chapter provides necessary information to use the MPC821ADS in host-controlled and stand-alone configurations. This includes controls and indicators, memory map details, and software initialization of the board.

#### 3•2 CONTROLS AND INDICATORS

The MPC821ADS has the following switches and indicators.

#### 3•2•1 SOFT RESET Switch SW1

JCTOR, INC. The SOFT RESET switch SW1 performs Soft reset to the MPC internal modules, maintaining MPC's configuration (clocks & chip-selects) and dram contents. The switch signal is debounced, and it is not possible to disable it by software. At the end of the Soft Reset Sequence, the Soft Reset Configuration is sampled and becomes valid.

#### 3•2•2 ABORT Switch SW2

The ABORT switch is normally used to abort program execution, this by issuing a level 0 interrupt to the MPC. If the ADS is in stand alone mode<sup>A</sup>, it is the responsibility of the user to provide means of handling the interrupt, since there is no resident debugger with the MPC821ADS. The ABORT switch signal is debounced, and can not be disabled by software.

#### 3-2-3 HARD RESET - Switches SW1 & SW2

When BOTH switches - SW1 and SW2 are depressed simultaneously, HARD reset is generated to the MPC. When the MPC is HARD reset, all its configuration is lost, including data stored in the DRAM and the MPC has to be re-initialized. At the end of the Hard Reset sequence, the Hard Reset Configuration stored in BCSR0 becomes valid.

#### 3•2•4 DS2 - Software Options Switch

DS2 is a 4-switches Dip-Switch, mounted over SP2. This switch is connected over EXTOLI(0:3) lines, and since EXTOLI(0:3) lines are available at BCSR, S/W options may be manually selected, according to DS2 state.

#### FIGURE 3-1 DS2 - Description

A. I.e., detached from a debug station.

#### **OPERATING INSTRUCTIONS**

#### 3•2•5 J4 Power Bridge

J4 is a soldered jumper, which is in series with the 3.3V power bus. This jumper may be removed<sup>A</sup> if current measurements on the 3.3V bus are to be held.

#### <u>Warning</u>

There are also GND bridges on board, which physically resemble J4. Do not mistake J4 to be a GND jumper, otherwise, permanent damage might be inflicted to the MPC821ADS.

#### **3•2•6** GND Bridges

There are 4 GND bridges on the MPC821ADS. They are meant to assist general measurements and logicanalyzer connection.

#### <u>Warning</u>

When connecting to a GND bridge, use only INSULATED GND clips. Failure in doing so, might result in permanent damage to the MPC821ADS.

#### 3•2•7 RUN Indicator - LD1

When the green RUN led - LD1 is lit, it indicates that the MPC is not in debug mode, i.e., VFLS0 & VFLS1 == 0. It is important to remember, that if the VFLS(0:1) pins are programmed for alternative use rather than function as VFLS lines, this indication is meaningless.

#### 3•2•8 FLASH ON - LD2

When the yellow FLASH ON led is lit, it indicates that the FLASH module is enabled in the BCSR1 register. I.e., any access done to the CS0~ address space will hit the flash memory. When it is dark, the flash is disabled and CS0~ may be used off-board via the expansion connectors.

#### 3•2•9 DRAM ON - LD3

When the yellow DRAM ON led is lit, it indicates the DRAM is enabled in BCSR1. Therefore, any access made to CS1~ (or CS2~) will hit on the DRAM. When it is dark, it indicates that either the DRAM is disabled in BCSR1, enabling the use of CS1~ and CS2~ off-board via the expansion connectors.

#### 3•2•10 ETH ON - LD4

When the yellow ETH ON led is lit, it indicates that the ethernet port transceiver - the MC68160 EEST, connected to SCC1 is active. When it is dark, it indicates that the EEST is in power down mode, enabling the use of SCC1 pins off-board via the expansion connectors.

#### 3•2•11 Ethernet RX Indicator - LD5

The green Ethernet Receive LED indicator blinks whenever the EEST is receiving data from one of the Ethernet port.

#### 3•2•12 Ethernet TX Indicator - LD6

The green Ethernet Receive LED indicator blinks whenever the EEST is transmitting data via the Ethernet port.

#### 3•2•13 Ethernet JABB Indicator - LD7

The red Ethernet TP Jabber LED indicator - JABB, lights whenever a jabber condition is detected on the TP ethernet port.

#### 3•2•14 IRD ON - LD8

A. By a skilled technician only.

#### **OPERATING INSTRUCTIONS**

When the yellow IRD ON led is lit, it indicates that the Infra-Red transceiver - the TFDS3000, connected to SCC2, is active and enables communication via that medium. When it is dark, the I/R transceiver is in shutdown mode, enabling the use of SCC2 pins off-board via the expansion connectors.

#### 3•2•15 Ethernet CLSN Indicator LD9

The red Ethernet Collision LED indicator CLSN, blinks whenever a collision condition is detected on the ethernet port, i.e., simultaneous receive and transmit.

#### 3•2•16 Ethernet PLR Indicator - LD10

The red Ethernet TP Polarity LED indicator - PLR, lights whenever the wires connected to the receiver input of the ethernet port are reversed. The LED is lit by the EEST, and remains on while the EEST has automatically corrected for the reversed wires.

#### 3•2•17 Ethernet LIL Indicator - LD11

The yellow Ethernet Twisted Pair Link Integrity LED indicator - LIL, lights to indicate good link integrity on the TP port. The LED is off when the link integrity fails.

#### 3•2•18 RS232 ON - LD12

When the yellow RS232 ON led is lit, it designates that the RS232 transceiver connected to SMC1, is active and communication via that medium is allowed. When dark, it designates that the transceiver is in shutdown mode, so SMC1 pins may be used off-board via the expansion connectors.

#### 3•2•19 PCMCIA ON - LD13

When the yellow PCMCIA ON led is lit, it indicates the following:

- 1) Address & strobe buffers are driven towards the PCMCIA card

- Data buffers may be driven to / from the PCMCIA card depending on the CE1A~ and CE2A~ signals and transfer direction.

- 3) Card status lines are driven towards the MPC from the PCMCIA card.

When it is dark, it indicates that all the above buffers are tri-stated and the pins associated with PCMCIA channel A, may be used off-board via the expansion connectors.

#### 3•2•20 5V Indicator - LD14

The yellow 5V led, indicates the presence of the +5V supply at P7.

#### 3•2•21 3.3V Indicator - LD15

The yellow 3.3V led indicates that the 3.3V power bus is powered

#### **OPERATING INSTRUCTIONS**

#### <u>3•3</u> <u>MEMORY MAP</u>

All accesses to MPC821ADS's memory slaves are controlled by the MPC's memory controller. Therefore, the memory map is reprogrammable to the desire of the user. After Hard Reset is performed by the debug station, the debugger checks to see the size, delay and type of the DRAM and FLASH memory mounted on board and initializes the chip-selects accordingly. The DRAM and the FLASH memory respond to all types of memory access i.e., user / supervisory, program / data and DMA.

| ADDESS RANGE        | Memory Type                      | Device Type |                                     |                         |          | Port<br>Size |

|---------------------|----------------------------------|-------------|-------------------------------------|-------------------------|----------|--------------|

| 00000000 - 003FFFFF | DRAM SIMM                        | MCM36100    | MCM36100 MCM36200 MCM36400 MCM36800 |                         | MCM36800 | 32           |

| 00400000 - 007FFFFF | DRAM SIMM                        |             | MCM36200                            | MCM36400                | MCM36800 | 32           |

| 00800000 - 00FFFFFF | DRAM SIMM                        |             | MICO                                | MCM36400                | MCM36800 | 32           |

| 01000000 - 01FFFFFF | DRAM SIMM                        | SCALE       | SEL                                 |                         | MCM36800 | 32           |

| 02000000 - 020FFFFF | Empty Space                      | GALL        |                                     |                         |          |              |

| 02100000 - 02103FFF | BCSR(0:3) <sup>a</sup>           | EES         | EES                                 |                         |          |              |

| 02104000 - 021FFFFF | Empty Space                      |             |                                     |                         |          |              |

| 02200000 - 02207FFF | MPC Internal<br>MAP <sup>c</sup> |             |                                     |                         |          | 32           |

| 02208000 - 027FFFFF | Empty Space                      |             |                                     |                         |          |              |

| 02800000 - 029FFFFF | Flash SIMM                       | MCM29F020   | MCM29F040<br>SM732A1000A            | MCM29F080<br>SM732A2000 |          | 32           |

| 02A00000 - 02BFFFFF |                                  |             | MCM29F040<br>SM732A1000A            | MCM29F080<br>SM732A2000 |          | 32           |

| 02C00000 - 02FFFFF  |                                  |             |                                     | MCM29F080<br>SM732A2000 |          | 32           |

| <b>TABLE 3-1.</b> | MPC821ADS | Main | <b>Memory Map</b> |

|-------------------|-----------|------|-------------------|

|-------------------|-----------|------|-------------------|

a. The device appears repeatedly in multiples of its size. E.g., BCSR0 appears at memory locations 2100000, 2100010, 2100020..., while BCSR1 appears at 2100004, 2100014, 2100024... and so on.

b. Only upper 16 bit are in fact used.

c. Refer to the MPC821 User's Manual for complete description of the MPC internal memory map.

#### <u>3•4</u> Programming The MPC Registers

The MPC provides the following functions on the MPC821ADS:

- 1) DRAM Controller

- 2) Chip Select generator.

- 3) UART for terminal or host computer connection.

- 4) Ethernet controller.

- 5) Infra-Red Port Controller

- 6) General Purpose I/O signals.

#### **OPERATING INSTRUCTIONS**

The internal registers of the MPC must be programmed after Hard reset as described in the following paragraphs. The addresses and programming values are in hexadecimal base.

For better understanding the of the following initializations refer to the MPC821 User's Manual for more information.

| Register | Init Value[hex] | Description                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SIUMCR   | 01632440        | Internal arbitration, External master arbitration priority - 0, External arbitration priority - 0, PCMCIA channel II pins - debug pins, Debug Port on JTAG port pins, FRZ/IRQ6~ - IRQ6~, debug register - locked, No parity for non-CS regions, DP(0:3)/IRQ(3:6)~ pins - DP(0:3), reservation disabled, SPKROUT - Tri-stated, BS_A(0:3)~ and WE(0:3)~ are driven just on their dedicated pins, GPL_B5~ enabled, GPL_A/B(2:3)~ function as GPLs. |

| SYPCR    | FFFFF88         | Software watchdog timer count - FFFF, Bus-monitor timing FF, Bus-monitor - Enabled, S/W watch-dog - Freeze, S/W watch-dog - disabled, S/W watch-dog (if enabled) causes NMI, S/W (if enabled) not prescaled.                                                                                                                                                                                                                                    |

| TBSCR    | 00C2            | No interrupt level, reference match indications cleared, interrupts disabled, no freeze, time-base disabled.                                                                                                                                                                                                                                                                                                                                    |

| RTCSC    | 01C2            | Interrupt request level - 1, 32768 Hz source, second interrupt disabled, Alarm interrupt disabled, Real-time clock - FREEZE, Real-time clock disabled.                                                                                                                                                                                                                                                                                          |

| PISCR    | 0082            | No level for interrupt request, Periodic interrupt disabled, clear status, interrupt disabled, FREEZE, periodic timer disabled.                                                                                                                                                                                                                                                                                                                 |