#### Programming Raggedstone1 User Guide, (Rev1.0)

This user guide will take the user through some simple easy steps on how to program Raggedstone1 through the platform flash using Xilinx's non-volatile programming proms fitted onboard, the format of this guide is visual using screenshots for much of the flow and explanation.

## STEPS TO UNDERTAKE:

- 1. Opening Xilinx ISE and creating a project,

- 2. Inputting code and synthesizing,

- 3. Assigning package pins to the design,

- 4. Place and routing the Design,

- 5. Generating the .bit file,

- 6. Generating the .mcs prom file in impact,

- 7. Programming the proms onboard Raggedstone1,

- 8. Testing the functionality of the design.

#### User Guide AIMS:

The aims of this user guide are to give the user a basic understanding of how to go about generating a working functional design in ISE and implementing the design onto a real hardware platform.

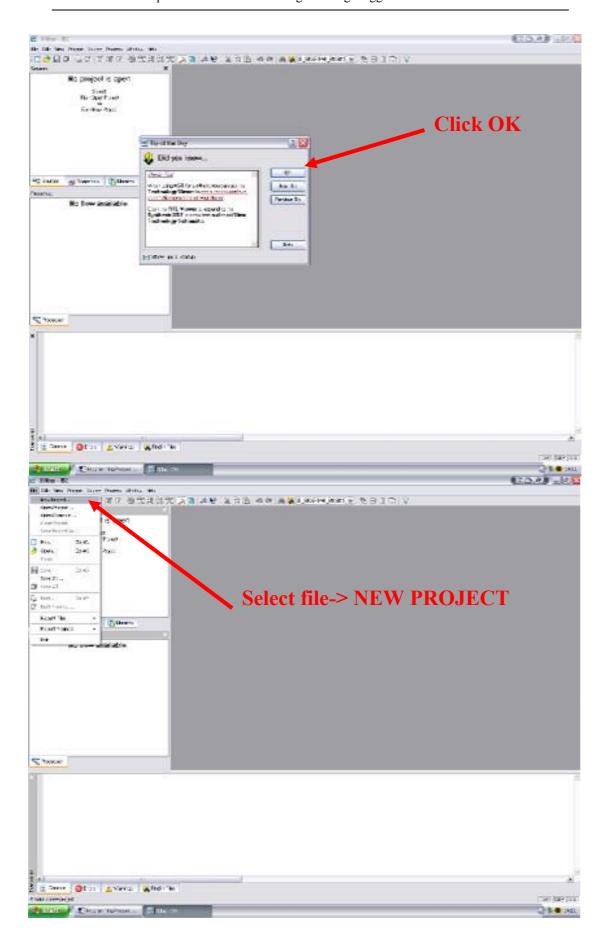

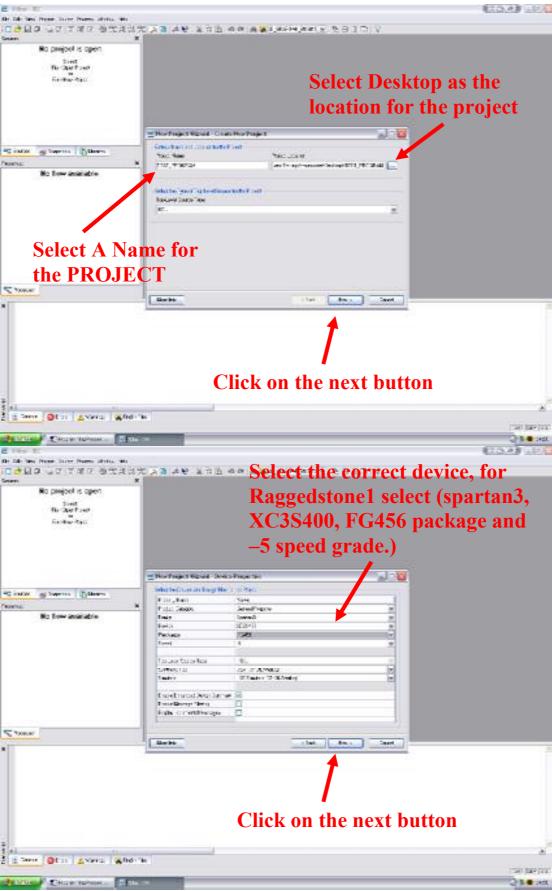

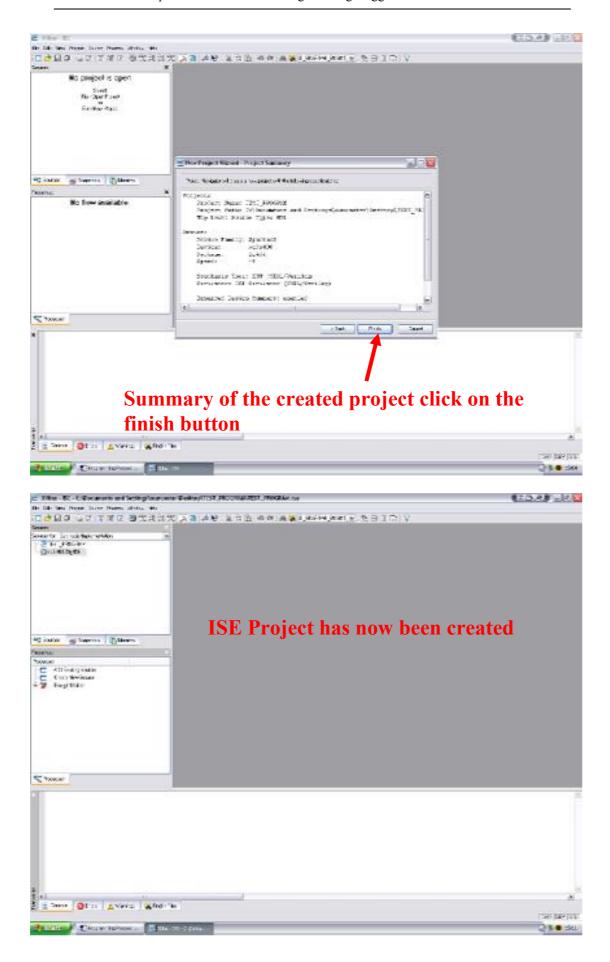

## Chapter 1, Opening Xilinx ISE and creating a project.

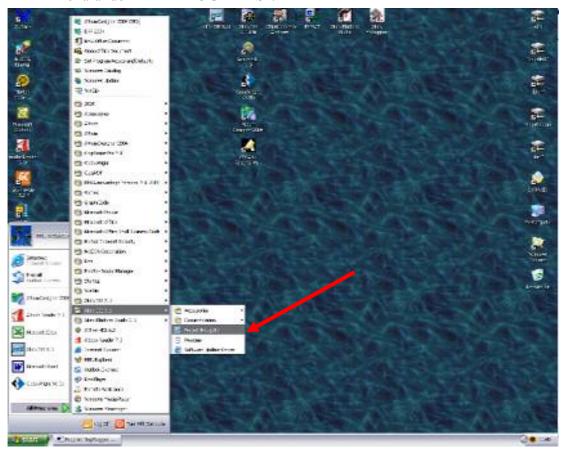

There are two ways to open Xilinx ISE, these are through the windows navigation structure or of the users desktop.

• Desktop, double click on the Xilinx ISE shortcut icon on the desktop (default install feature)

• Navigation, Click on the Project Navigator icon under the Xilinx ISE 8.?.? menu under "ALL PROGRAMS".

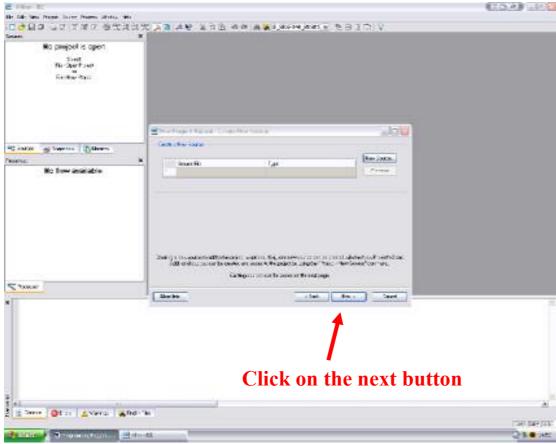

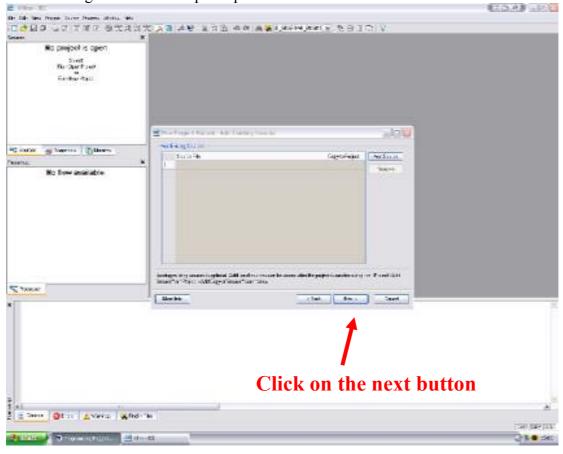

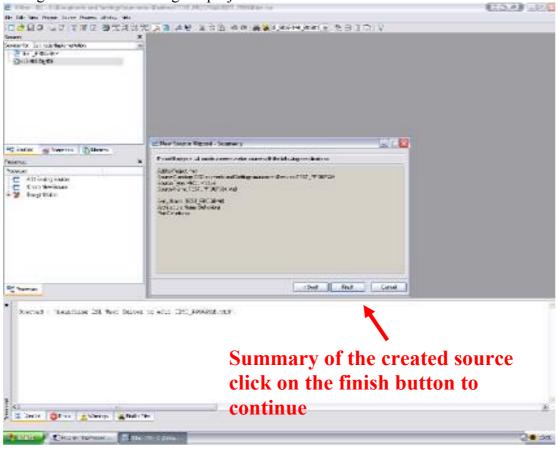

• The next window allows the creation of a new source file by defining the IO ports of the design, for this user guide we will skip this process.

• The next window allows the addition of a source file already written, for this user guide we will skip this process.

#### Chapter 2, Inputting code and Synthesizing.

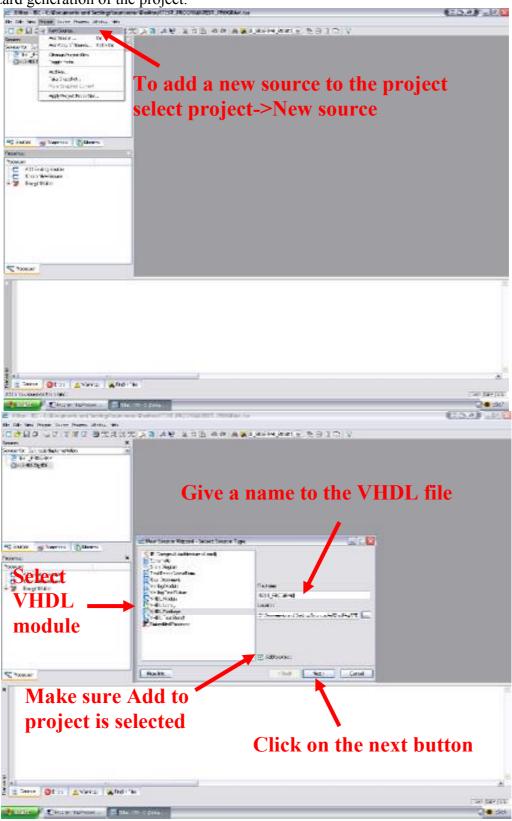

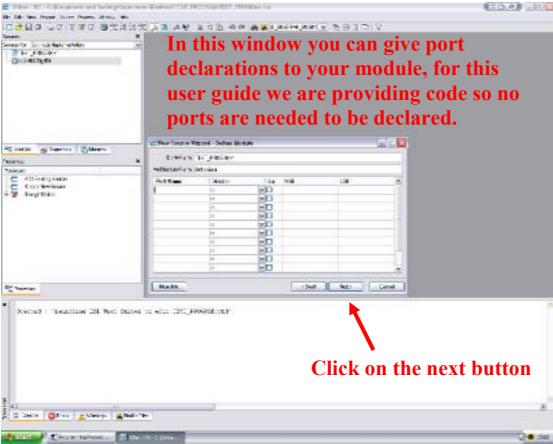

As mentioned before you have seen two possible ways of adding code to the created project we will use a third method which can add code to existing projects after the wizard generation of the project.

This Window is the same one you would see if you selected to add a new source through the wizard creating the project.

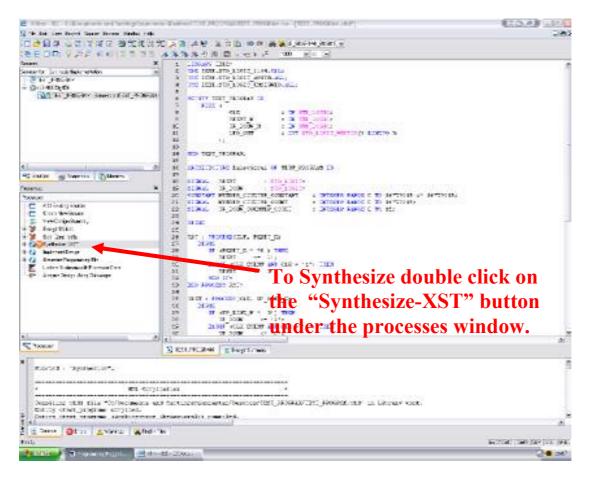

• Cut and paste following code into the created VHDL file and save the file.

```

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY TEST PROGRAM IS

PORT (

CLK : IN STD_LOGIC;

RESET_N : IN STD_LOGIC;

UP_DOWN_N : IN STD_LOGIC;

OUT STD_LOGIC_VECTOR(3 DOWNTO 0)

LED_OUT

END TEST PROGRAM;

ARCHITECTURE Behavioral OF TEST_PROGRAM IS

SIGNAL RESET : STD_LOGIC;

SIGNAL UP_DOWN : STD_LOGIC;

CONSTANT NUMBER_COUNTER_CONSTANT : INTEGER RANGE 0 TO 16777215 := 16777215;

SIGNAL NUMBER COUNTER COUNT

: INTEGER RANGE 0 TO 16777215;

SIGNAL UP_DOWN_COUNTER_COUNT

: INTEGER RANGE 0 TO 15;

BEGIN

RST: PROCESS(CLK, RESET_N)

BEGIN

IF (RESET_N = '0') THEN

RESET <= '1';

ELSIF (CLK'EVENT AND CLK = '1') THEN

RESET

END IF;

END PROCESS RST;

UDST: PROCESS(CLK, UP_DOWN_N)

BEGIN

IF (UP\_DOWN\_N = '0') THEN

UP DOWN <= '1';

ELSIF (CLK'EVENT AND CLK = '1') THEN

UP DOWN <= '0';

END IF:

END PROCESS UDST;

SM: PROCESS(CLK, UP_DOWN, RESET)

BEGIN

IF (RESET = '1') THEN

NUMBER_COUNTER_COUNT <= NUMBER_COUNTER_CONSTANT;

UP_DOWN_COUNTER_COUNT <= 0;

LED OUT <= "0000"

ELSIF (CLK'EVENT AND CLK = '1') THEN

LED OUT <= CONV_STD_LOGIC_VECTOR(UP_DOWN_COUNTER_COUNT,4);

IF ( NUMBER_COUNTER_COUNT = 0 ) THEN

NUMBER_COUNTER_COUNT <= NUMBER_COUNTER_CONSTANT;

IF (UP \overline{DOWN} = '0') THEN

UP_DOWN_COUNTER_COUNT <= UP_DOWN_COUNTER_COUNT + 1;</pre>

UP DOWN COUNTER COUNT <= UP DOWN COUNTER COUNT - 1;

END IF;

ELSE

NUMBER_COUNTER_COUNT <= NUMBER_COUNTER_COUNT - 1;</pre>

UP_DOWN_COUNTER_COUNT <= UP_DOWN_COUNTER_COUNT;</pre>

END IF:

END IF;

END PROCESS SM;

END Behavioral;

```

Now that we have a design we want to implement in hardware we need to assign the package pins to function correctly please see chapter3.

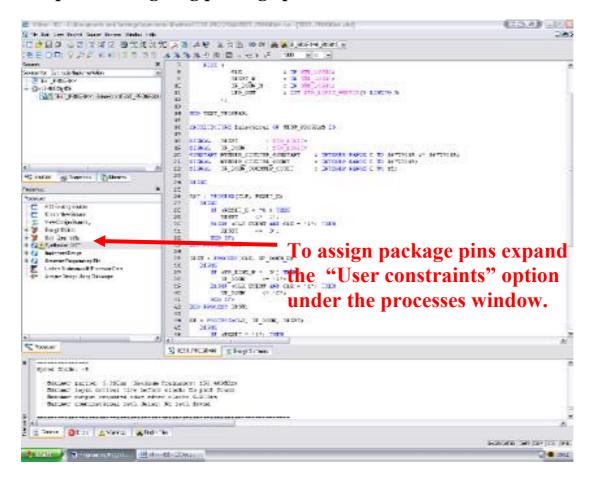

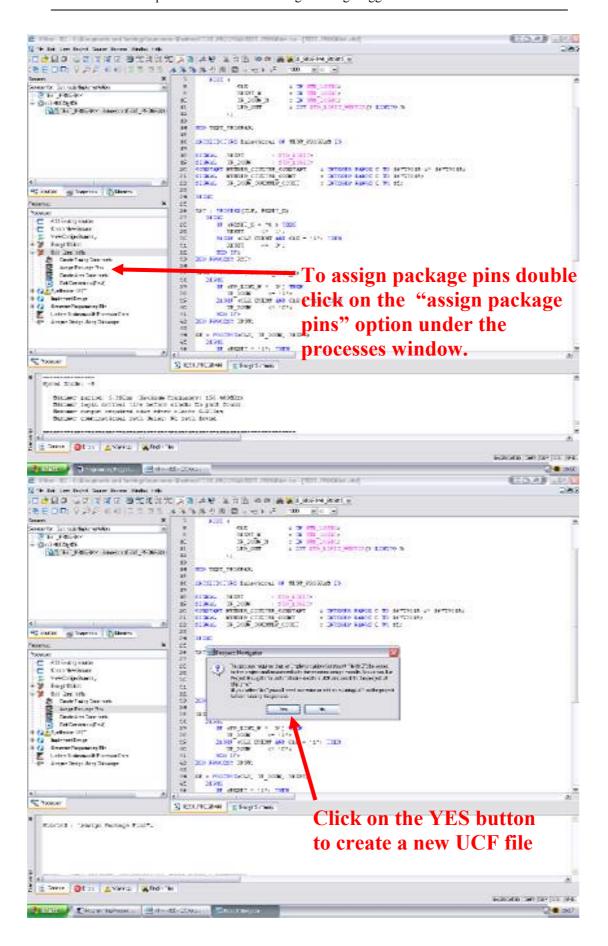

## Chapter3, Assigning package pins.

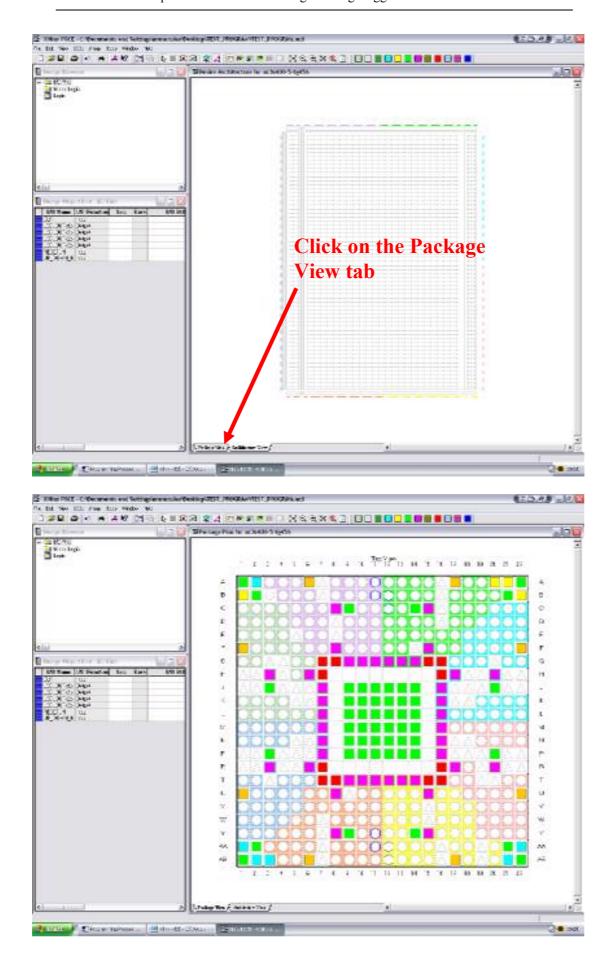

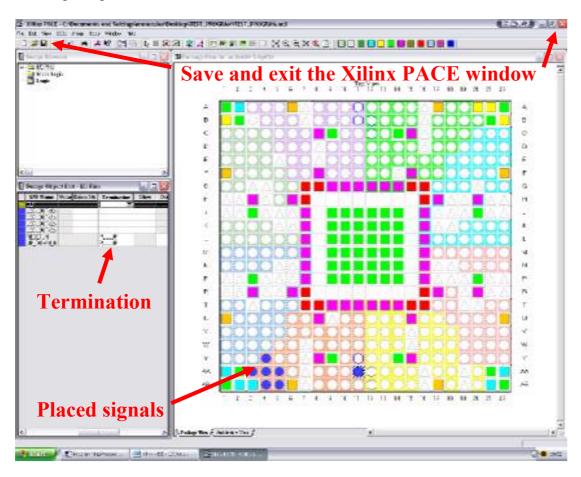

• To assign the package pins click and hold on the relevant signal and drag it to the pin require for the design.

| Signal     | PIN                                                       |

|------------|-----------------------------------------------------------|

| CLK        | AA11 for onboard clock socket or A11 for PCI clock signal |

| LED_OUT<0> | AB4                                                       |

| LED_OUT<1> | AA4                                                       |

| LED_OUT<2> | AA5                                                       |

| LED_OUT<3> | AB5                                                       |

| RESET_N    | Y4                                                        |

| UP_DOWN_N  | AA3                                                       |

• For the push buttons we need to enable the pull up resistor for these inputs to function correctly, to do this, in the Design object list window scroll across until the termination heading is in view. Click on the relevant box and select pull up.

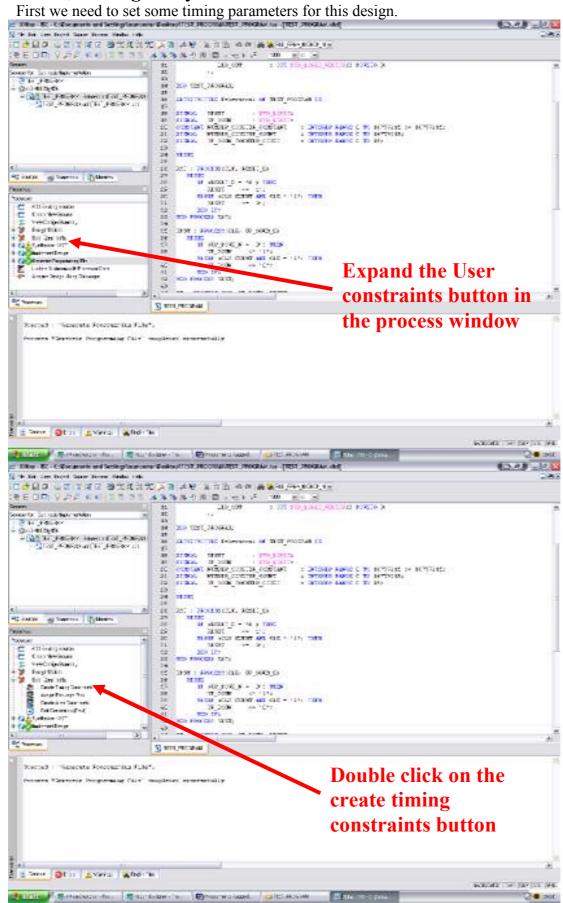

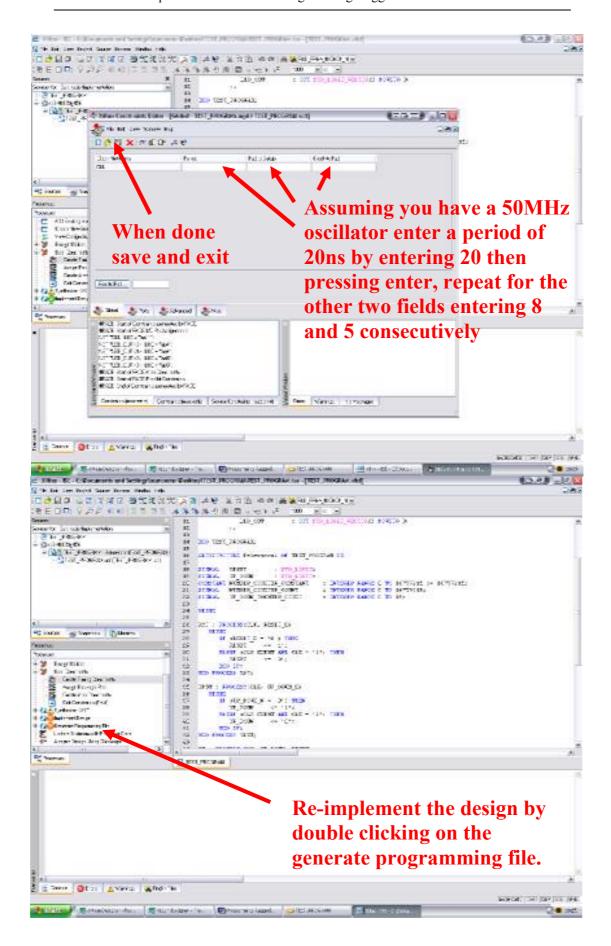

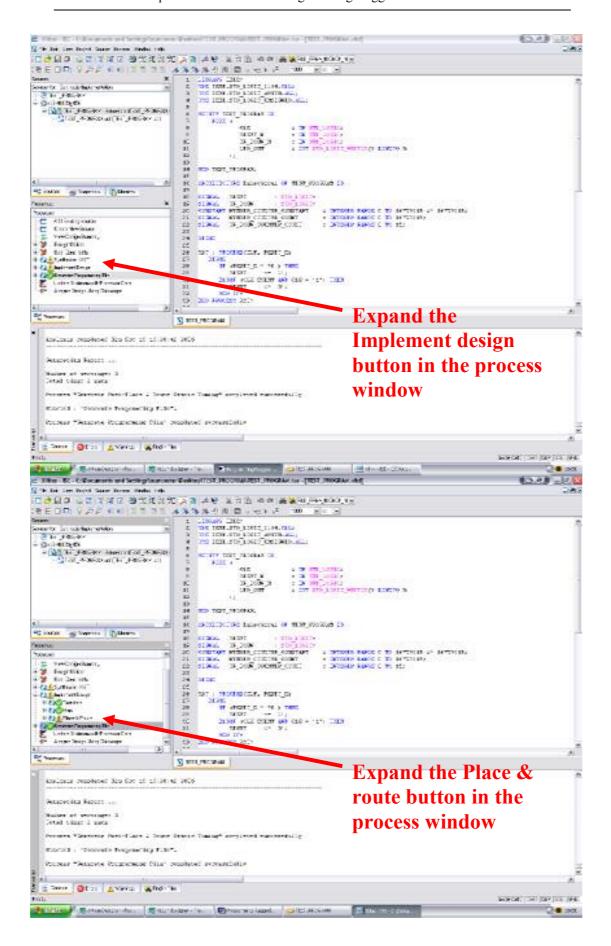

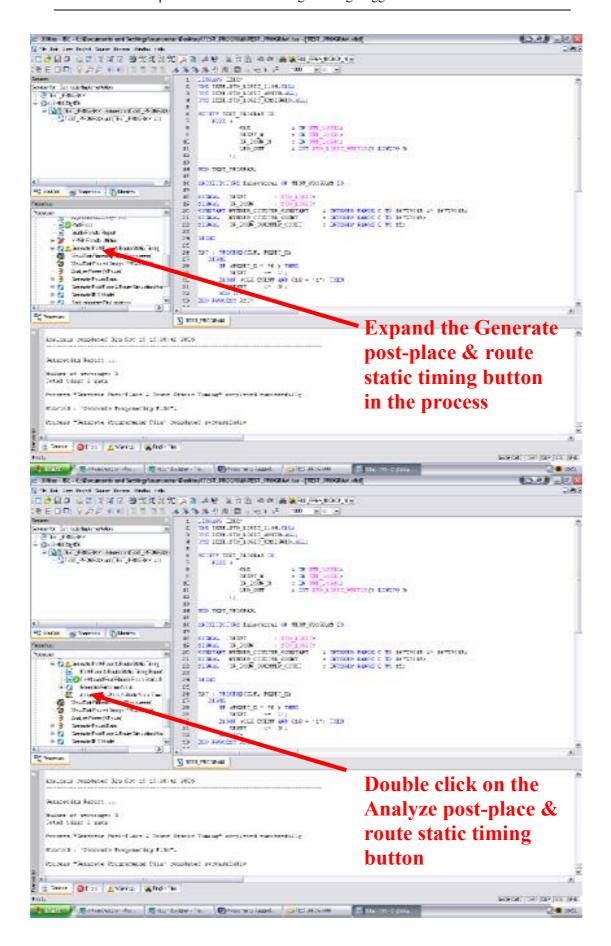

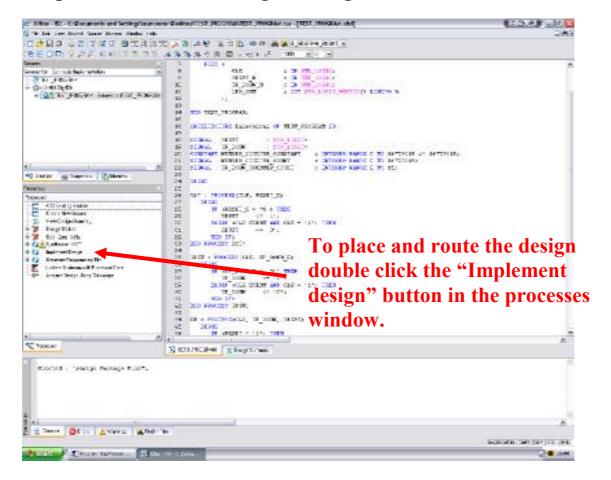

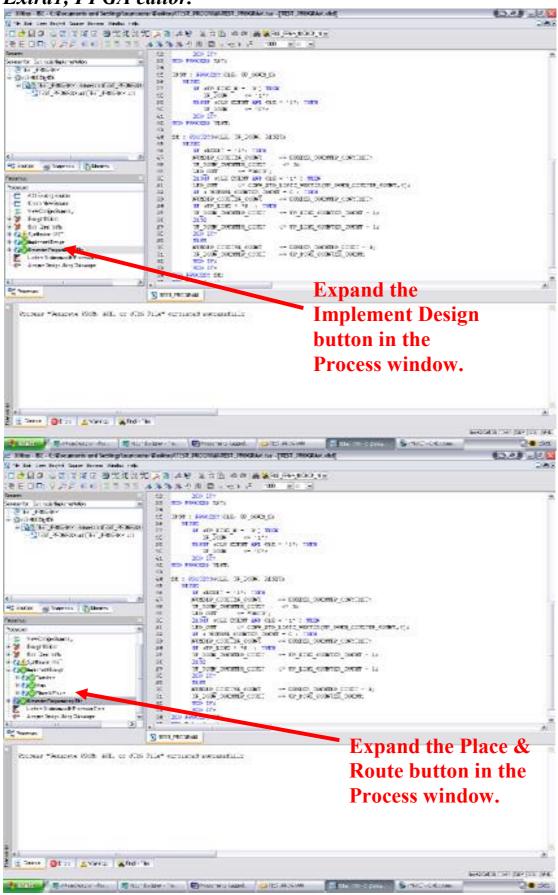

#### Chapter 4, Place and routing the design.

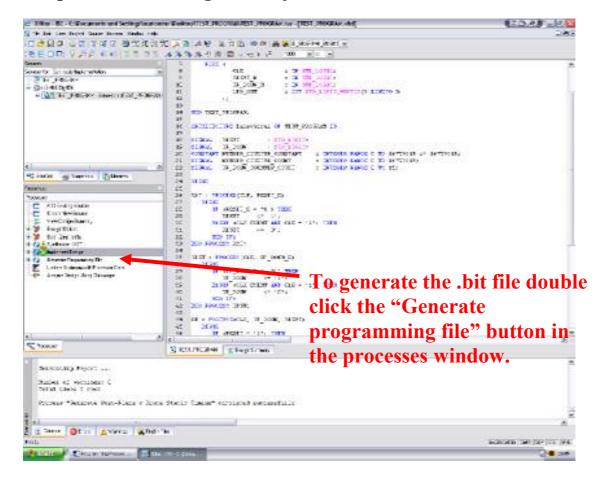

#### Chapter 5, Generating the .bit file.

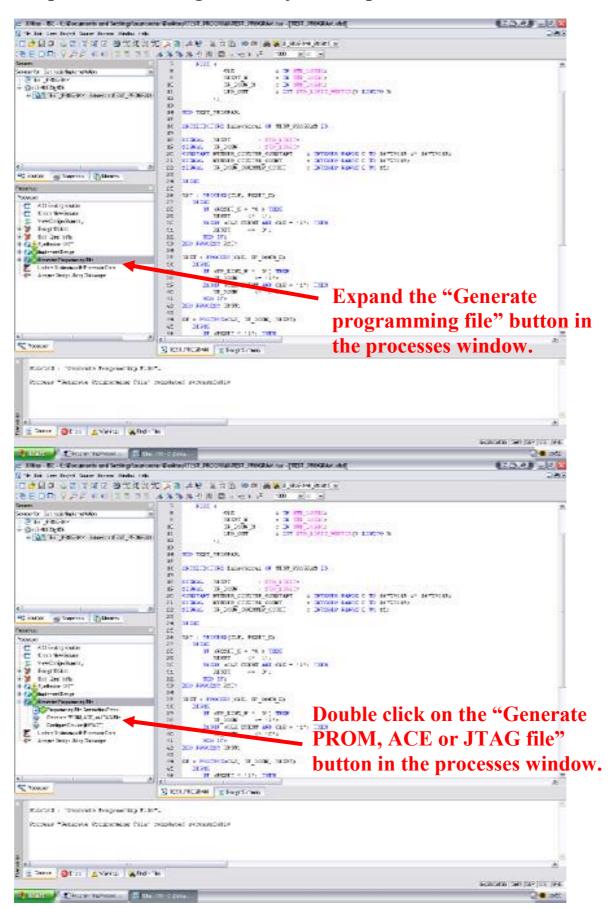

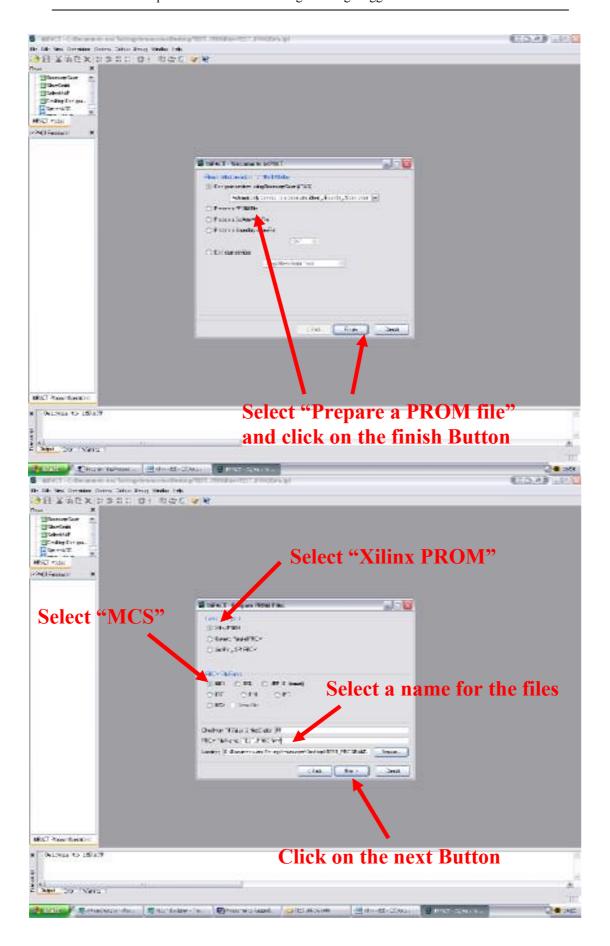

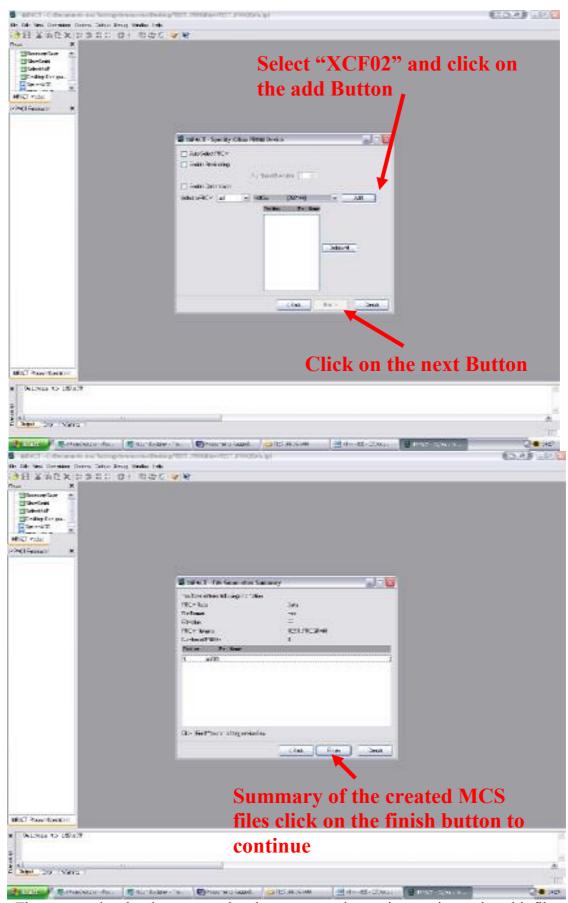

#### Chapter 6, Generating the .mcs file in impact.

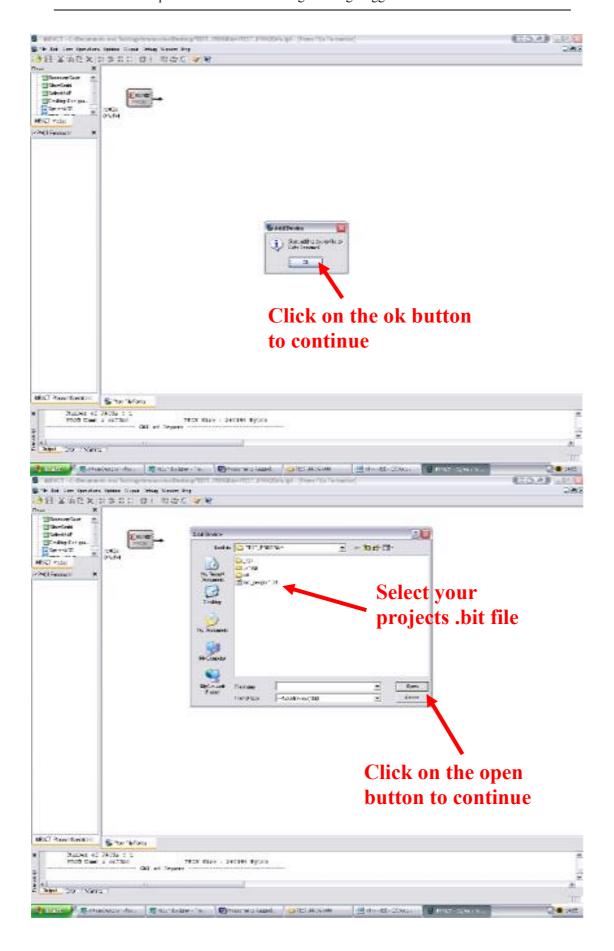

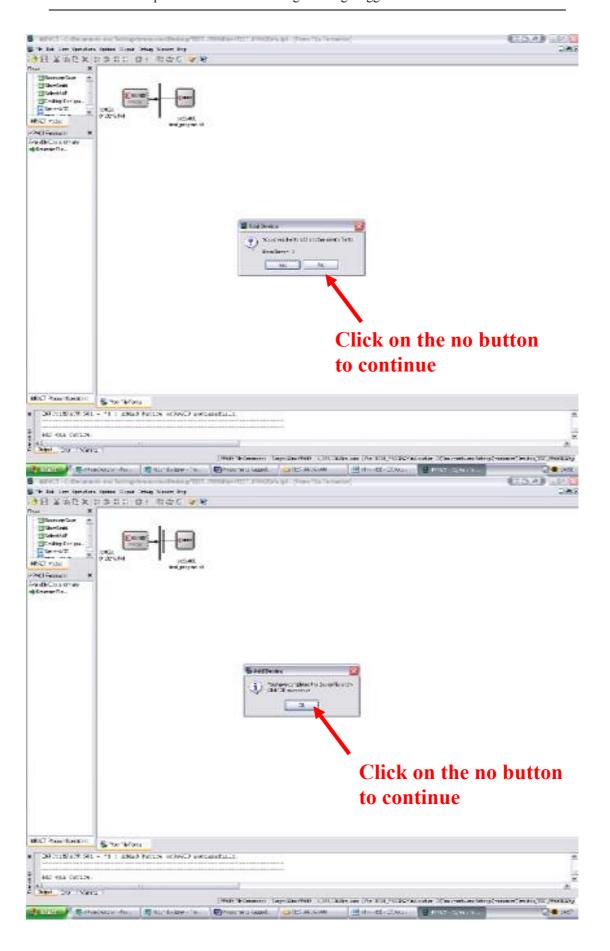

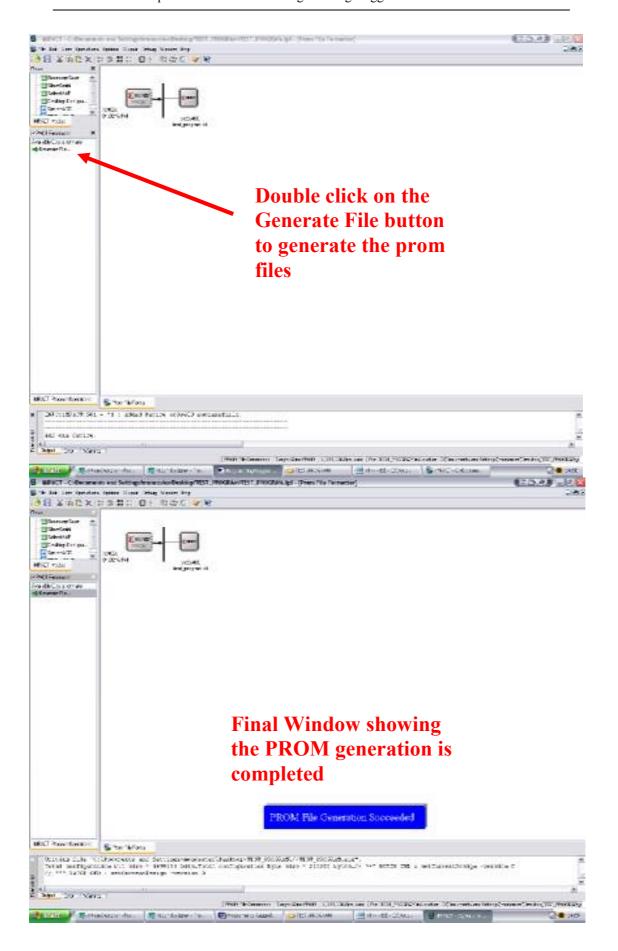

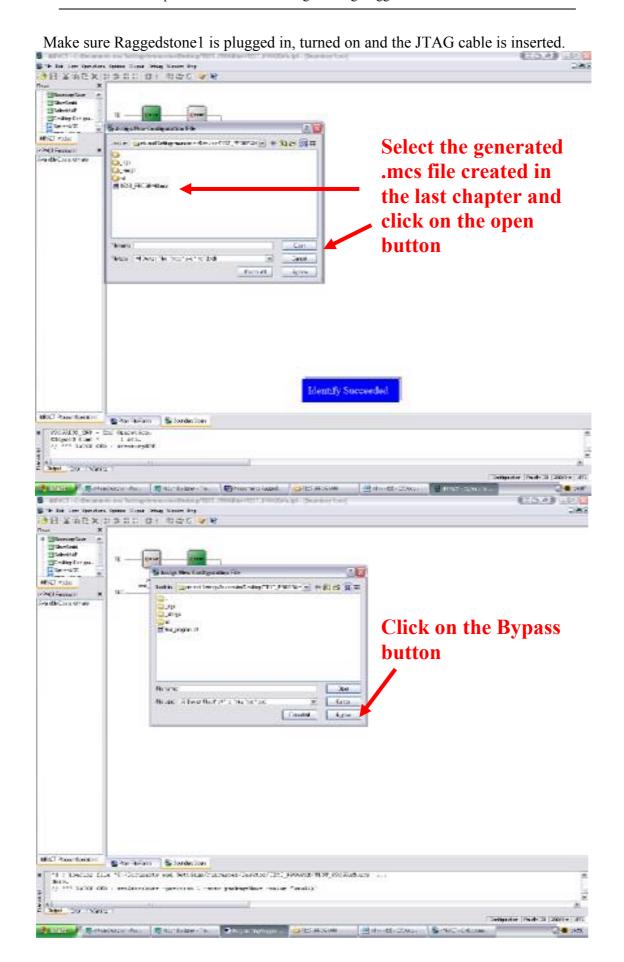

The .mcs project has been created and now we need to assign our ise project .bit file.

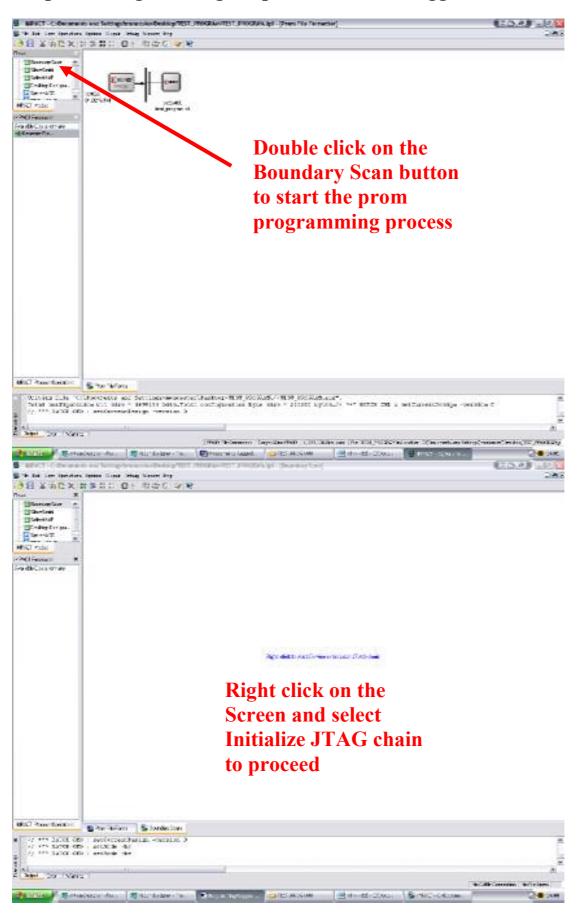

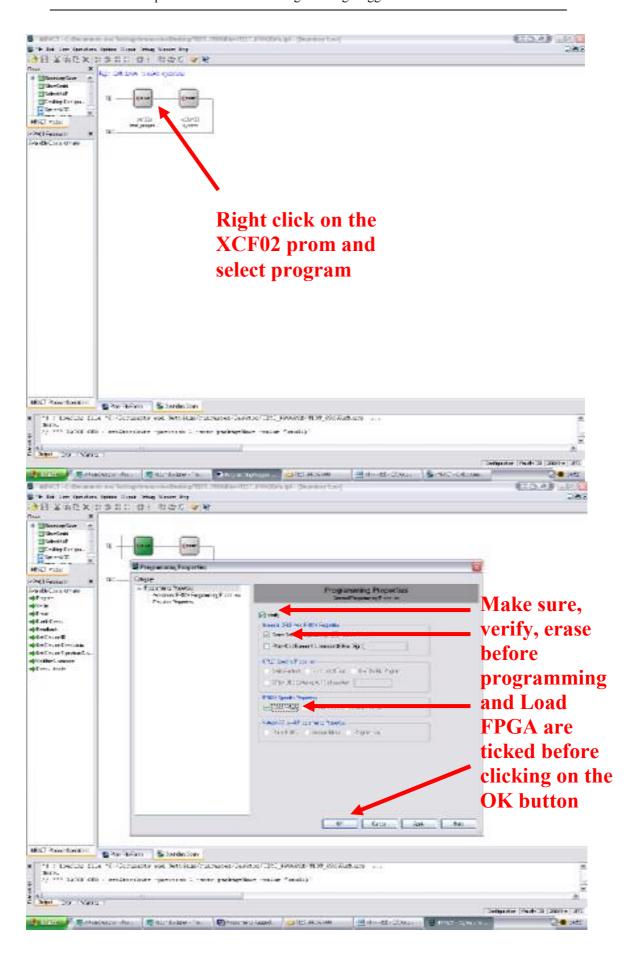

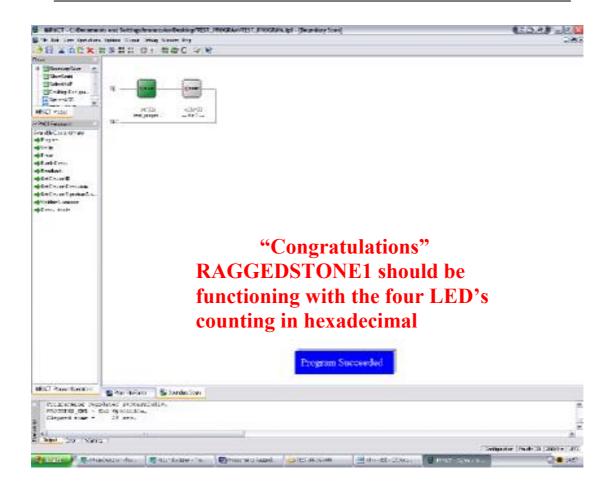

#### Chapter 7, Programming the proms onboard Raggedstone 1.

#### Chapter8, Testing the functionality of the design.

On Raggedstone1 the LED's should be counting upwards, if you press Switch 2 the FPGA is in reset and the LED's are all turned off.

Pressing and holding Switch 1 turns the count around and the count starts to decrease when either "all on" or "all off" and depending on the count you hit an overflow situation and the count wraps around.

# EXTRA, Other programs of interest within ISE.

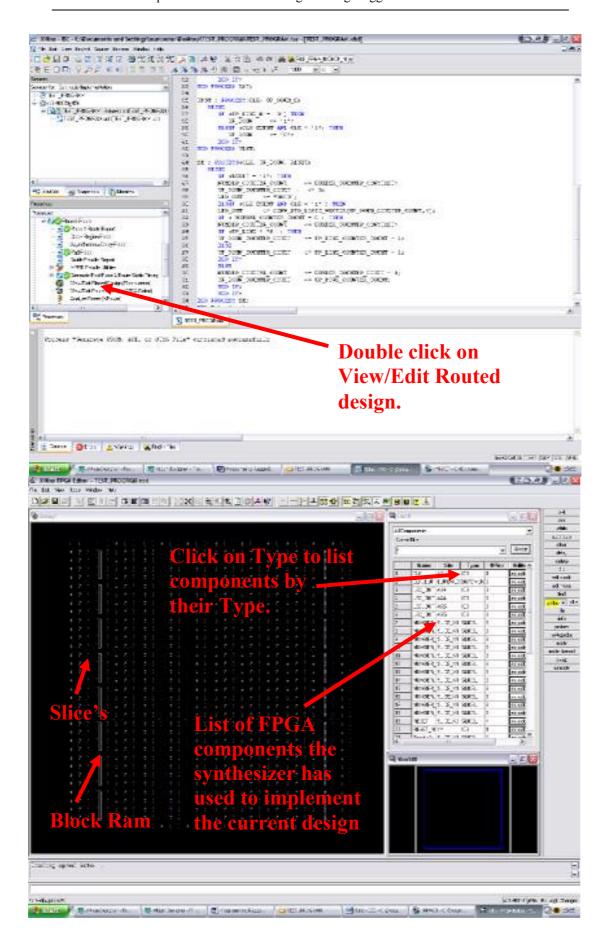

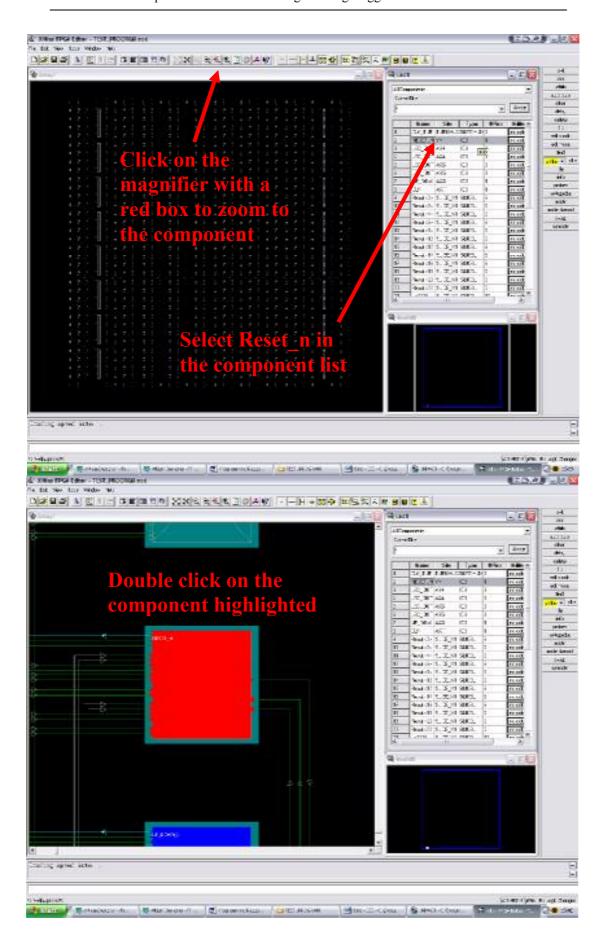

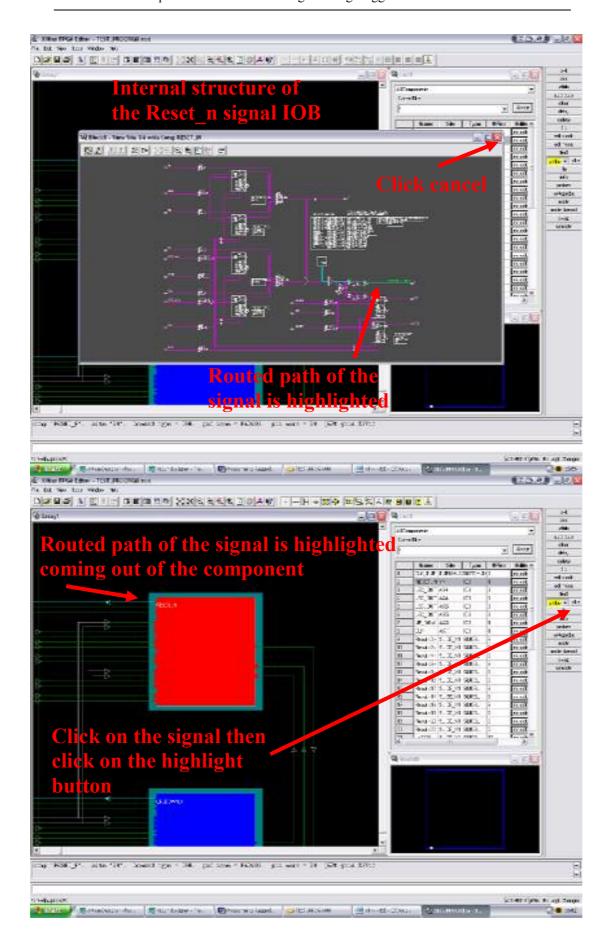

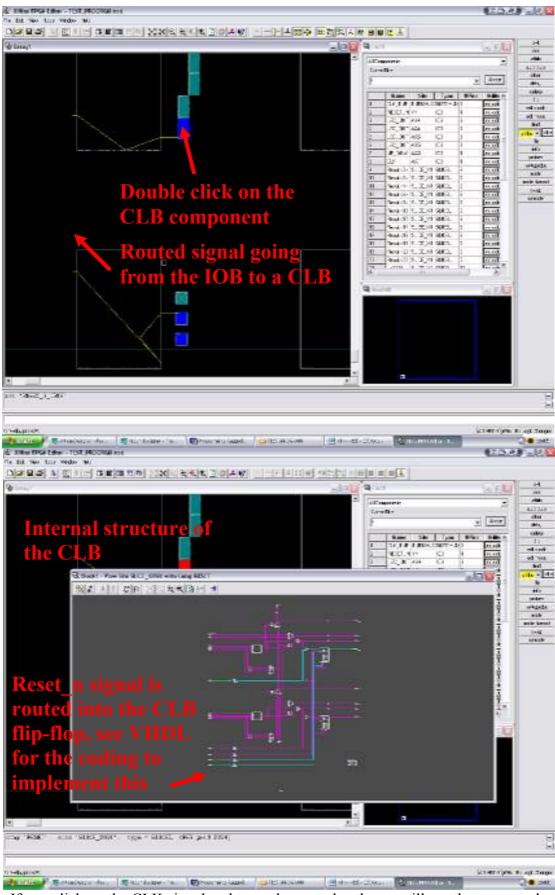

- FPGA editor, visually inspect the routing and placed design implemented in the FPGA,

- Timing analyzer, view timing reports and see functioning times to current placement.

Extra1, FPGA editor.

If you click on the CLK signal and trace the routed path you will see that you reach a clock buffer clicking on the signal after shows the clock tree for this design.

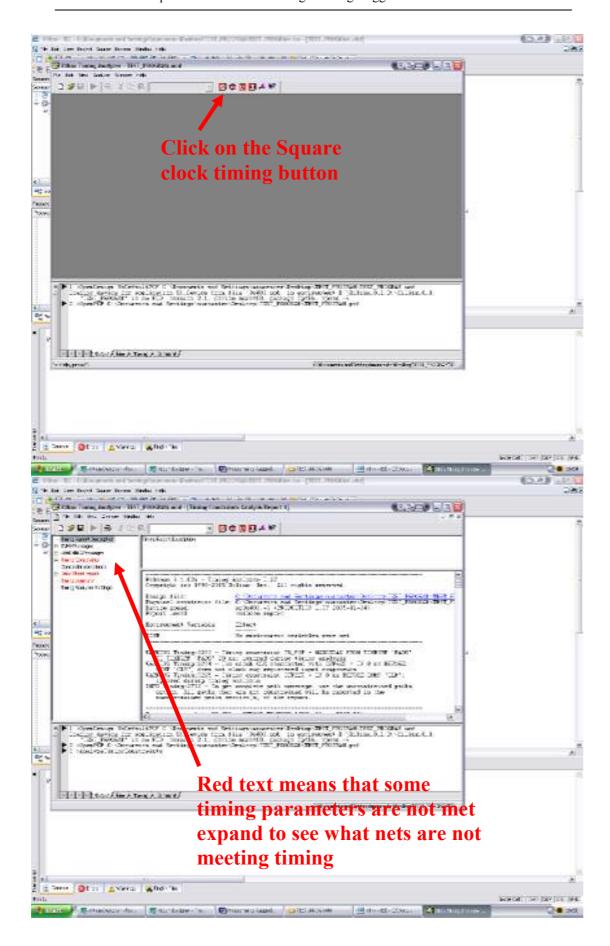

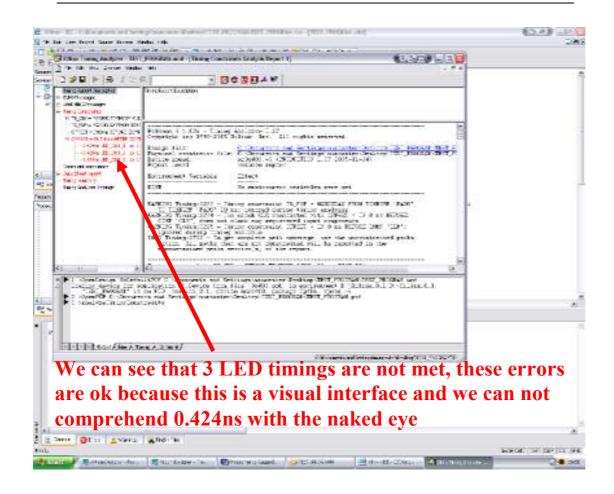

#### Extra2, Timing analyzer.