# SECTION 7 COMMUNICATION PROCESSOR MODULE (CPM)

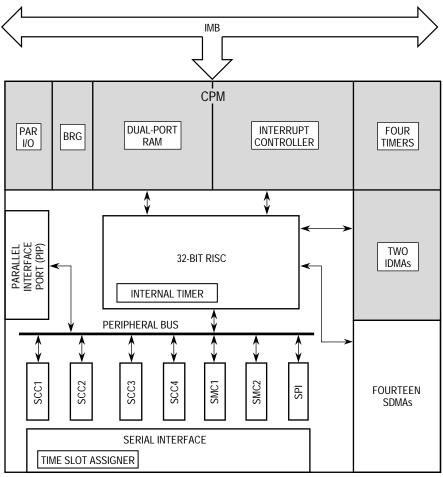

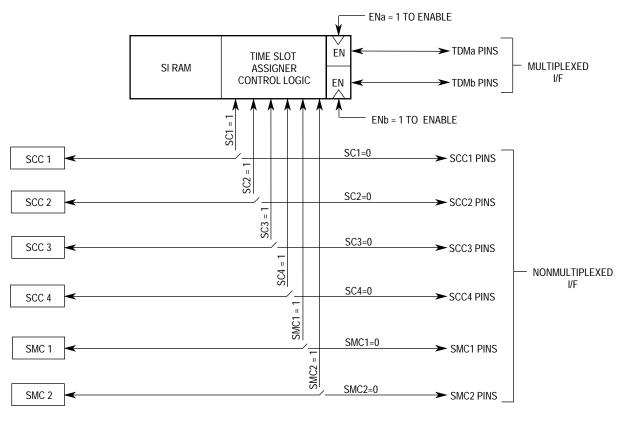

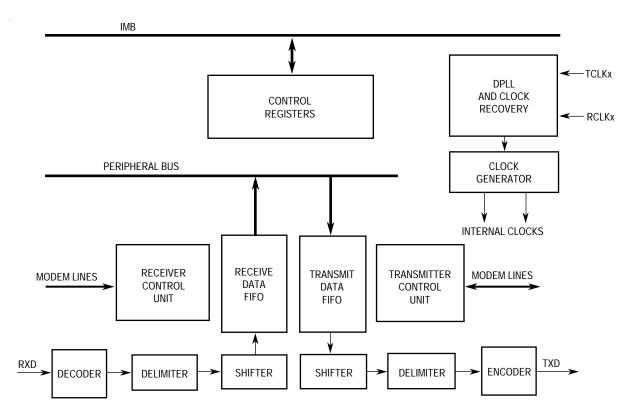

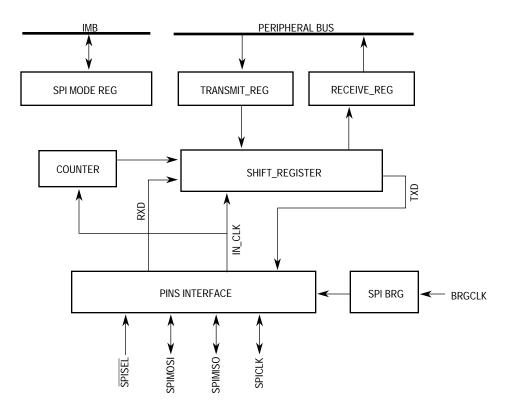

The CPM includes many blocks that work together to allow an extremely flexible and integrated approach to solving many communications problems. The CPM (see Figure 7-1) includes the following modules:

- RISC Controller

- Four Full-Duplex Serial Communication Controllers (SCCs) Support the Following Protocols:

- -IEEE 802.3/Ethernet (Optional Feature on SCC)

- -High-Level/Synchronous Data Link Control (HDLC/SDLC)

- —HDLC Bus (Multidrop Bus Configuration of HDLC)

- —AppleTalk (HDLC-Based Local Area Network (LAN) Protocol)

- -Universal Asynchronous Receiver Transmitter (UART)

- —Synchronous UART (Isochronous, 1x Clock Mode)

- -Binary Synchronous Communication (BISYNC)

- -Totally Transparent Operation

- -Signaling System #7 (HDLC-Based Protocol. RAM Microcode Option Only)

- Profibus (RAM Microcode Option Only)

- -Asynchronous HDLC (RAM Microcode Option Only)

- -Multiple Chanel GCI (RAM Microcode Option Only)

- -ATM Framing (RAM Microcode Option Only)

- -Enhanced Ethernet Filtering (RAM Microcode Option Only)

- Four Independent Baud Rate Generators

- Two Serial Management Controllers (SMCs) Provide Additional UART and Totally Transparent Functionality or Support the GCI Channel 0 and 1 Monitor and C/I Channels in Integrated Services Digital Network (ISDN)

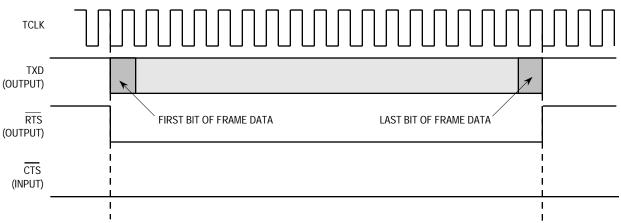

- Serial Interface Provides Nonmultiplexed Serial Interface (NMSI) for the Four SCCs (includes TXD, RXD, TCLK, RCLK, RTS, CTS, and CD pins)

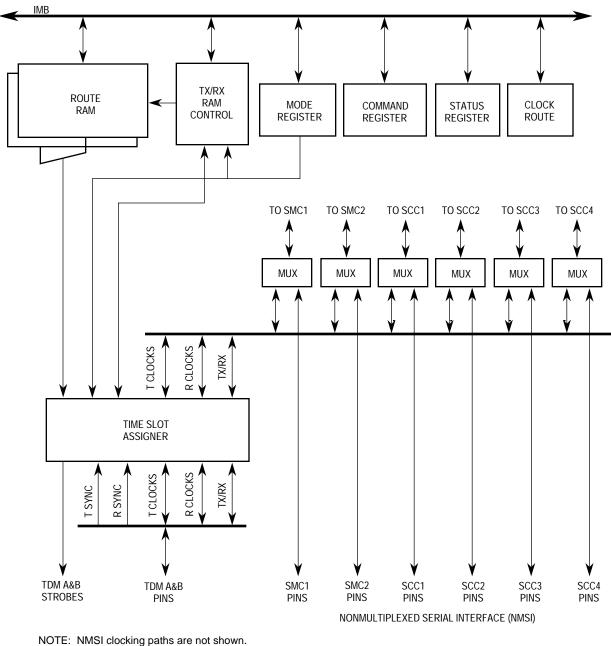

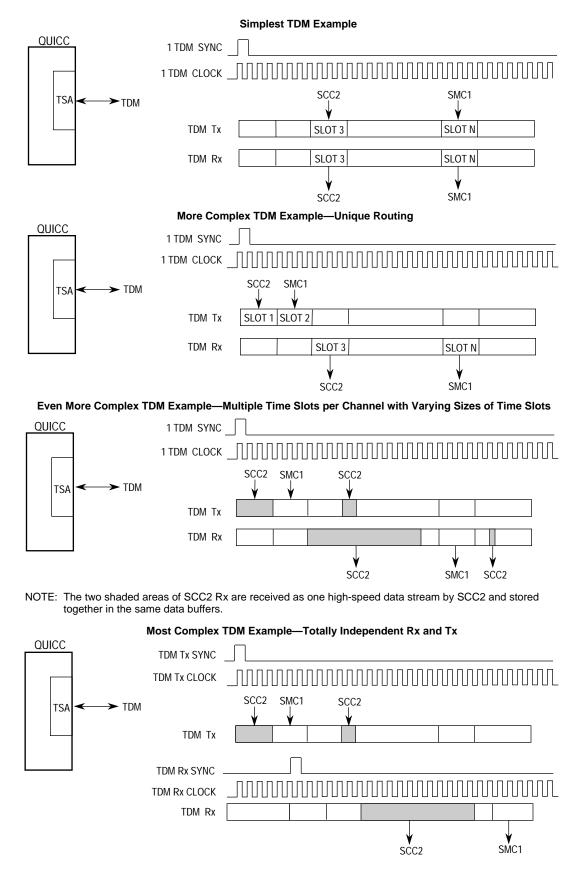

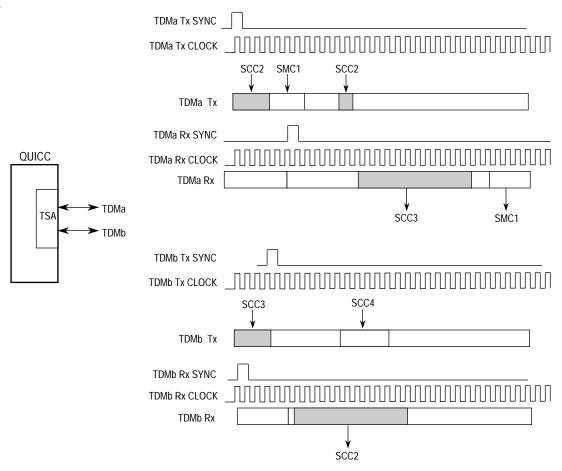

- Time Slot Assigner (TSA) Supports Multiplexing of Data from any of the Four SCCs and Two SMCs onto Two Time-Division Multiplexed (TDM) Interfaces. The TSA Supports the Following TDM Formats:

—T1/CEPT Lines

- -Pulse Code Modulation (PCM) Highway Interface

- -ISDN Primary Rate

- -Motorola Interchip Digital Link (IDL)

- -General Circuit Interface (GCI), also known as IOM-2

- -User-Defined Interfaces

- Serial Peripheral Interface (SPI) for Synchronous Interchip Communication

- Fourteen Serial Direct Memory Access (SDMA) Channels Support the SCC, SMCs, and SPI

- Two Independent Direct Memory Access (IDMA) Channels Support External Memory and Peripherals

- A Command Set Register Supports the RISC, IDMA, SCCs, SMCs, and SPI

- Four General-Purpose 16-Bit Timers or Two 32-Bit Timers

- Internal Timers to Implement Up to 16 Additional Timers

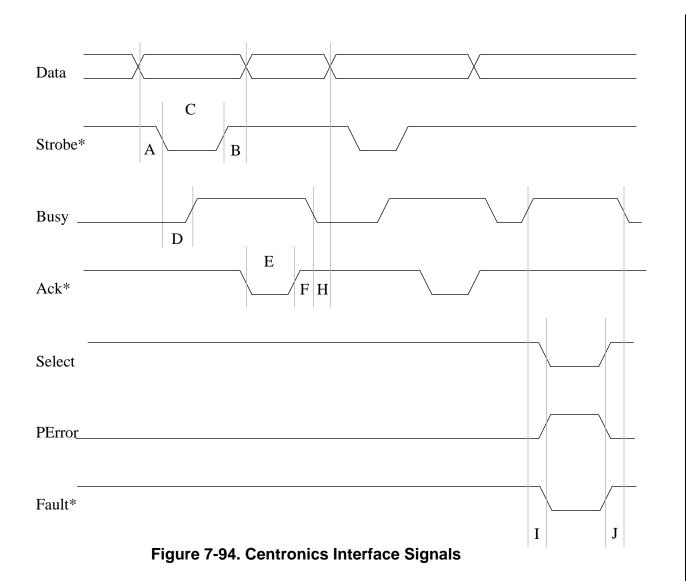

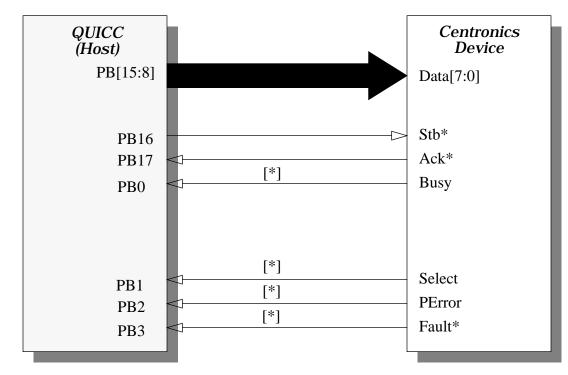

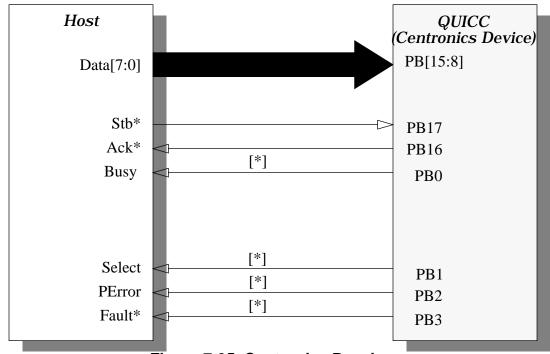

- General-Purpose Parallel Port for Parallel Protocols such as Centronics (Can Also Be Used as Standard Parallel I/O)

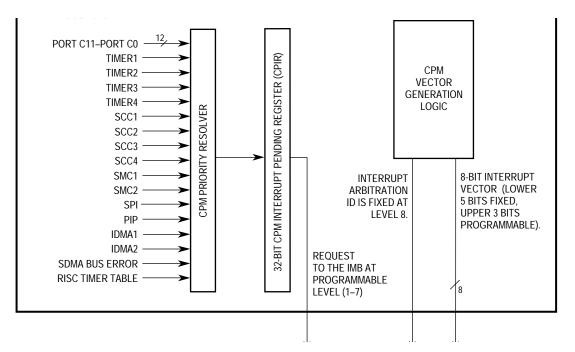

- CPM Interrupt Controller

- 2.5-kbyte Dual-Port RAM

- Twelve Parallel I/O Lines with Interrupt Capability

NOTE: The term "CP" refers to the nonshaded portion of the CPM.

Figure 7-1. CPM Block Diagram

### 7.1 RISC CONTROLLER

The RISC controller is the 32-bit central controller of the communication processor module (CPM). Since its execution occurs on a separate bus that is hidden from the user, it does not impact CPU32+ core performance. The RISC controller works with the serial channels and parallel interface port (PIP) to implement the user-chosen protocols and to manage the SDMA channels that transfer data between the SCCs and memory. The RISC controller contains an internal timer that can be used to implement up to 16 additional timers for the user application software. These features are collectively known as the communication processor (CP), which is a subset of the overall CPM. Additionally, the RISC controller can manage the operation of the IDMA channels, if desired. The 32-bit RISC handles the lower layer tasks and DMA control activities, leaving the 32-bit CPU32+ core (or other external processor) free to handle higher layer activities. Thus, the QUICC can be thought of as a dual 32-bit processor system.

The RISC controller communicates with the host (CPU32+ core or other external processor) in several ways. First, many parameters are exchanged through the dual-port RAM. In the case of simultaneous accesses (at least one of which is a write operation), the RISC controller may be delayed by one clock in its access to the dual-port RAM. The host is never delayed. Second, the RISC controller can execute special commands issued by the host. These commands are only required to be issued in special situations. Third, the RISC controller can generate interrupts through the CPM interrupt controller. Fourth, status/event registers, which show events that have occurred within the RISC, may be read at any time by the CPU32+ or an external processor.

The RISC controller has the ability to control a set of up to 16 timers. These timers are separate and distinct from the four general-purpose timers and baud rate generators in the CPM. The 16 timers are ideally used in protocols that do not require extreme precision, but in which it is desirable to off-load the host CPU from having to scan the timer tables that are created in software. These timers are clocked from an internal timer used only by the RISC controller.

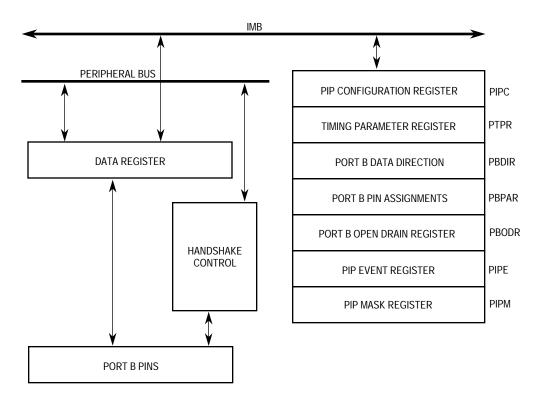

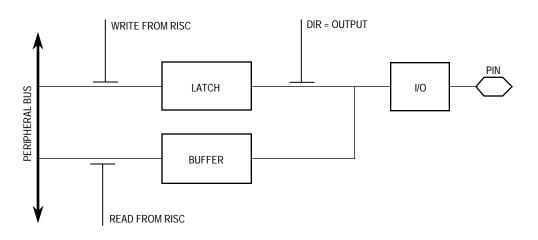

The RISC controller uses the peripheral bus to communicate with all of its peripherals. Each SCC has a separate receive and transmit FIFO. The SCC1 FIFOs are 32-bytes each; the other SCC FIFOs are 16-bytes each. The SMC and SPI FIFO sizes are double-buffered. The PIP is a single register interface.

The following priority scheme determines the processing priority of the RISC controller. It is as follows:

- 1. Reset in CP Command Register or System Reset

- 2. DMA Bus Error

- 3. Commands Issued to the CP Command Register

- 4. CC1 Rx

- 5. SCC1 Tx

- 6. SCC2 Rx

- 7. SCC2 Tx

- 8. CC3 Rx

- 9. SCC3 Tx

- 10. SCC4 Rx

- 11.SCC4 Tx

- 12. SMC1 Rx

- 13. SMC1 Tx

- 14. SMC2 Rx

- 15. SMC2 Tx

- 16. SPI Rx

- 17. SPI Tx

- 18. PIP

- 19. RISC Timer Tables

The RISC controller has an option to execute microcode from a portion of user RAM, located in the on-chip dual-port RAM. In this mode, either 512 bytes or 1024 bytes of the user RAM cannot be accessed by the host or another bus master and are used exclusively by the RISC. In this mode, the RISC controller can fetch instructions from both the dual-port RAM and its private ROM. This mode allows Motorola to add new protocols or enhancements to the QUICC in the form of Motorola-supplied RAM microcodes. The binary microcode is obtained from Motorola and then loaded by the user into the dual-port RAM.

The RISC controller contains one configuration register described in the following paragraph.

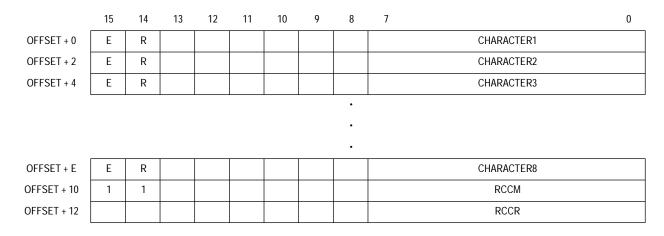

# 7.1.1 RISC Controller Configuration Register (RCCR)

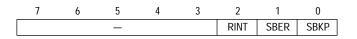

The 16-bit, memory-mapped, read-write RCCR is used to configure the RISC processor and controls the RISC internal timer. This register is initialized to zero at reset. Bits 0-7 should not be modified unless the user is downloading a Motorola-supplied RAM microcode package..

| 15   | 14 | 13 | 12 | 11  | 10  | 9 | 8 | 7 | 6 | 5 | 4    | 3    | 2 | 1 | 0 |

|------|----|----|----|-----|-----|---|---|---|---|---|------|------|---|---|---|

| TIME | -  |    |    | TIN | 1EP |   |   |   |   |   | RESE | RVED |   |   |   |

TIME—Timer Enable

This bit enables the RISC controller internal timer. The timer will generate a tick to the RISC based on the value programmed into the TIMEP bit. TIME may be modified at any time to start or stop the scanning of the RISC timer tables.

### Bit 14—Reserved

### TIMEP—Timer Period

This field controls the RISC controller timer tick. The RISC timer tables are scanned on each timer tick. The input to this timer tick generator is the general system clock divided by 1024. The formula is  $(TIMEP + 1) \times 1024 = (general system clock period)$ . Thus, a val-

ue of 0 stored in these bits gives a timer tick of  $1 \times (1024) = 1024$  general system clocks. A value of 63 (decimal) stored in these bits gives a timer tick of  $64 \times (1024) = 65536$  general system clocks.

Bits 7-0—Reserved - set to zero.

### 7.1.2 RISC Microcode Revision Number

The RISC controller writes a revision number stored in its ROM to a dual-port RAM location called REV\_num. REV\_num is located in the miscellaneous parameter RAM. The other locations are reserved for future use. The microcode rivision number only reflect the revision of the micro code. It dose not always refrect the MASK number.

| Address        | Name    | Width | Description               |

|----------------|---------|-------|---------------------------|

| Misc Base + 00 | REV_num | Word  | Microcode Revision Number |

| Misc Base + 02 | RES     | Word  | Reserved                  |

| Misc Base + 04 | RES     | Long  | Reserved                  |

| Misc Base + 08 | RES     | Long  | Reserved                  |

### 7.2 COMMAND SET

The host processor (CPU32+ or other external processor) issues commands to the RISC by writing to the command register (CR). The CR only needs to be accessed on rare occasions. For instance, to terminate the transmission of a frame by an SCC without waiting until the end of the frame, a STOP TX command can be issued to an SCC through the command register. The commands are described in general terms in the following paragraphs; they are described in specific terms when the protocol or feature is described in detail.

The host should set the FLG bit in the CR when it issues commands. The CP clears FLG after completing the command to indicate to the host that it is ready for the next command. Subsequent commands to the CR may be given only after FLG is cleared. The software reset command (issued by setting the RST bit) may be given regardless of the state of FLG, but the host should still set FLG when setting RST.

The CR, a 16-bit, memory-mapped, read-write register, is cleared by reset.

| 15  | 14 | 13 | 12 | 11 | 10  | 9   | 8 | 7 | 6   | 5   | 4 | 3 | 2 | 1 | 0   |

|-----|----|----|----|----|-----|-----|---|---|-----|-----|---|---|---|---|-----|

| RST |    | _  |    |    | OPC | ODE |   |   | CHI | NUM |   |   | _ |   | FLG |

#### RST—Software Reset Command

This bit is set by the host and cleared by the CP. On execution of this command, the RST bit and the FLG bit are cleared within two general system clocks. The RISC reset routine is approximately 60 clocks long, but the user can begin initialization of the CP immediately after this command is given. This command is useful when the host wants to reset the registers and parameters for all the channels (SCCs, SMCs, SPI, and PIP) as well as the RISC processor and RISC timer tables. This command does not affect the serial interface (SI) or the parallel I/O registers.

Bits 14–12, 3–1—Reserved

**OPCODE**—Operation Code

The opcodes are listed in Table 7-1.

| Opcode | SCC                     | SMC (UART/Trans)    | SMC (GCI)              | SPI                    | IDMA      | Timer     |

|--------|-------------------------|---------------------|------------------------|------------------------|-----------|-----------|

| 0000   | INIT RX & TX<br>PARAMS  | INIT RX & TX PARAMS | INIT RX & TX<br>PARAMS | INIT RX & TX<br>PARAMS |           |           |

| 0001   | INIT RX<br>PARAMS       | INIT RX PARAMS      |                        | INIT RX<br>PARAMS      |           |           |

| 0010   | INIT TX PARAMS          | INIT TX PARAMS      |                        | INIT TX PARAMS         |           |           |

| 0011   | ENTER HUNT<br>MODE      | ENTER HUNT MODE     |                        |                        |           |           |

| 0100   | STOP TX <sup>1</sup>    | STOP TX             |                        |                        |           |           |

| 0101   | GR STOP TX <sup>2</sup> |                     |                        |                        | INIT IDMA |           |

| 0110   | RESTART TX              | RESTART TX          |                        |                        |           |           |

| 0111   | CLOSE RX BD             | CLOSE RX BD         |                        | CLOSE RX BD            |           |           |

| 1000   | SET GROUP<br>ADDR       |                     |                        |                        |           | SET TIMER |

| 1001   |                         |                     | GCI TIMEOUT            |                        |           |           |

| 1010   | RESET BCS               |                     | GCI ABORT REQ          |                        |           |           |

| 1011   |                         |                     |                        |                        |           |           |

| 1100   | U                       | U                   | U                      | U                      | U         | U         |

| 1101   | U                       | U                   | U                      | U                      | U         | U         |

| 1110   | U                       | U                   | U                      | U                      | U         | U         |

| 1111   | U                       | U                   | U                      | U                      | U         | U         |

#### Table 7-1. Opcodes

NOTES:

1.STOP TX = MC68302 original STOP TRANSMIT command.

2.GR STOP TX = GRACEFUL STOP TRANSMIT command.

INIT TX and RX PARAMETERS. This command initializes the transmit and receive parameters in the parameter RAM to the values that they had after the last reset of the CP. This command is especially useful when switching protocols on a given serial channel.

INIT RX PARAMETERS. This command initializes the receive parameters of the serial channel.

INIT TX PARAMETERS. This command initializes the transmit parameters of the serial channel.

ENTER HUNT MODE. This command causes the receiver to stop receiving and begin looking for a new frame. The exact operation of this command may vary depending on the protocol used.

STOP TX. This command aborts the transmission from this channel as soon as the transmit FIFO has been emptied. It should be used in cases where transmission needs to be stopped as quickly as possible. Transmission will proceed when the RESTART command is issued. GRACEFUL STOP TX. This command stops the transmission from this channel as soon as the current frame has been fully transmitted from the transmit FIFO. Transmission will proceed once the RESTART command is issued and the R-bit is set in the next transmit buffer descriptor.

RESTART TX. When the STOP TX command has been issued, this command can be used to restart the transmission at the current buffer descriptor.

CLOSE RX BD. This command causes the receiver to simply close the current receive buffer descriptor, making the receive buffer immediately available for manipulation by the user. Reception continues normally using the next available buffer descriptor. This command may be used to access the data buffer without waiting until the data buffer is completely filled by the SCC $\mu$ SET TIMER. This command activates, deactivates, or reconfigures one of the 16 timers in the RISC timer table.

SET GROUP ADDRESS. This command sets a bit in the hash table for the Ethernet logical group address recognition function.

GCI ABORT REQUEST. The GCI receiver sends an abort request on the E-bit.

GCI TIMEOUT. The GCI performs the timeout function.

RESET BCS. This command is used in BISYNC mode to reset the block check sequence calculation.

Undefined (U). Reserved for use by Motorola-supplied RAM microcodes.

### CH NUM—Channel Number

These bits are set by the host to define the specific sub-block on which the command is to operate. Some sub-blocks share channel number encodings if their commands are mutually exclusive.

| 0000 | SCC1            |

|------|-----------------|

| 0001 |                 |

| 0010 |                 |

| 0011 |                 |

| 0100 | SCC2            |

| 0101 | SPI/RISC Timers |

| 0110 |                 |

| 0111 |                 |

| 1000 | SCC3            |

| 1001 | SMC1/IDMA1      |

| 1010 |                 |

| 1011 |                 |

| 1100 | SCC4            |

| 1101 | SMC2/IDMA2      |

| 1110 |                 |

| 1111 |                 |

FLG—Command Semaphore Flag

The bit is set by the host and cleared by the CP.

- 0 = The CP is ready to receive a new command.

- 1 = The CR contains a command that the CP is currently processing. The CP clears this bit at the end of the command execution or after reset.

### 7.2.1 Command Register Examples

To perform a complete reset of the CP, the value \$8001 should be written to the CR. Following this command, the CR will return the value \$0000 in two clocks.

To execute an ENTER HUNT MODE command to SCC3, the value \$0381 should be written to the CR. While the command is executing, the CR will return the value \$0381. When the command has been completely executed, the CR will return the value \$0380.

### 7.2.2 Command Execution Latency

The worst-case command execution latency is 120 clocks. The typical command execution latency is about 40 clocks.

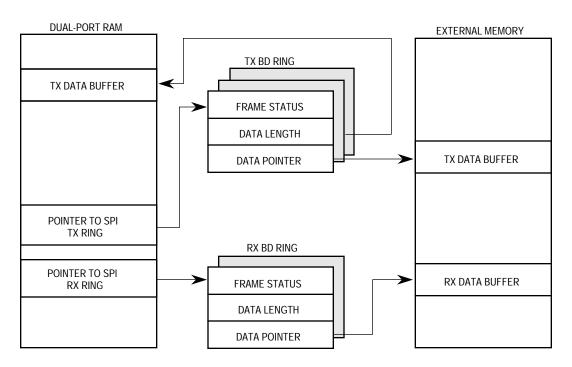

### 7.3 DUAL-PORT RAM

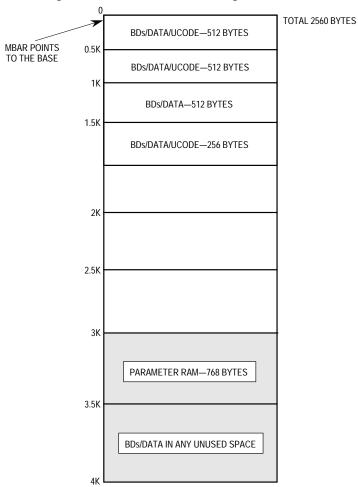

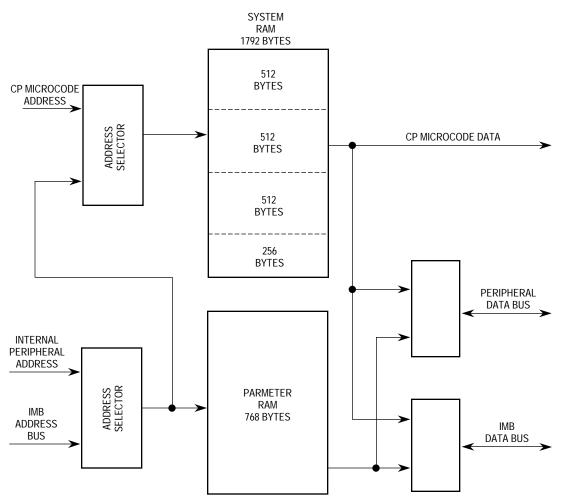

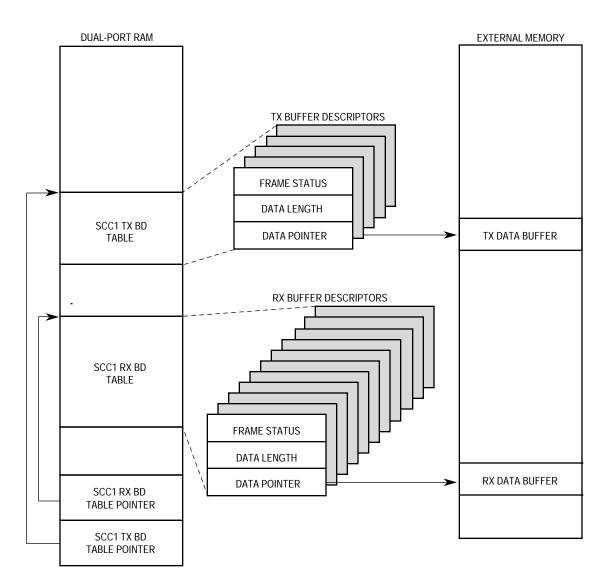

The CPM has 2560 bytes of static RAM configured as dual-port memory. The dual-port RAM memory map is shown in Figure 7-2, and a block diagram is shown in Figure 7-3.

Figure 7-2. Dual-Port RAM Memory Map

Figure 7-3. Dual-Port RAM Block Diagram

The dual-port RAM can be accessed by the RISC or one of four bus masters: CPU32+ core, IDMAs, SDMAs, or external bus master. When the dual-port RAM is accessed by an external bus master, CPU32+ core, IDMA, or SDMA channel, it is accessed in three clocks. When the dual-port RAM is accessed by the RISC, it is accessed in one clock. In the case of simultaneous access (with at least one write operation), the RISC is delayed by one clock.

When the dual-port RAM is accessed by the CPU32+ core, IDMAs, SDMAs, or external bus master, the data and address are taken from the IMB. The data is then presented on the IMB data bus. The RISC has access to the entire dual-port RAM for data fetches and portions of the system RAM for microcode instruction fetches.

The dual-port RAM is used for five possible tasks; any two tasks can occur simultaneously. The first use is to store parameters associated with the SCCs, SMCs, SPI, and IDMAs in the 768-byte parameter RAM. The second use is to store the buffer descriptors that describe where data is to be received and transmitted from. The third use is to store data from the serial channels. This usage is optional since data may also be stored externally in the system memory. The fourth use is to store RAM microcode for the RISC processor. This feature allows additional protocols to be added by Motorola in the future. The fifth use is for additional scratchpad RAM space for the user program.

Only the parameters in the parameter RAM and the microcode RAM option require fixed addresses to be used. The buffer descriptors, buffer data, and scratchpad RAM may be located in the internal system RAM or in any unused parameter RAM (for instance, in the available area when a serial channel or sub-block is not being used).

When a microcode from RAM is executed, certain portions of the system RAM are no longer available. This includes either the first 512-byte block and the last 256-byte block for a small RAM microcode, and the first two 512-byte blocks and the last 256-byte block for a large RAM microcode. The third 512-byte block is always available as system RAM.

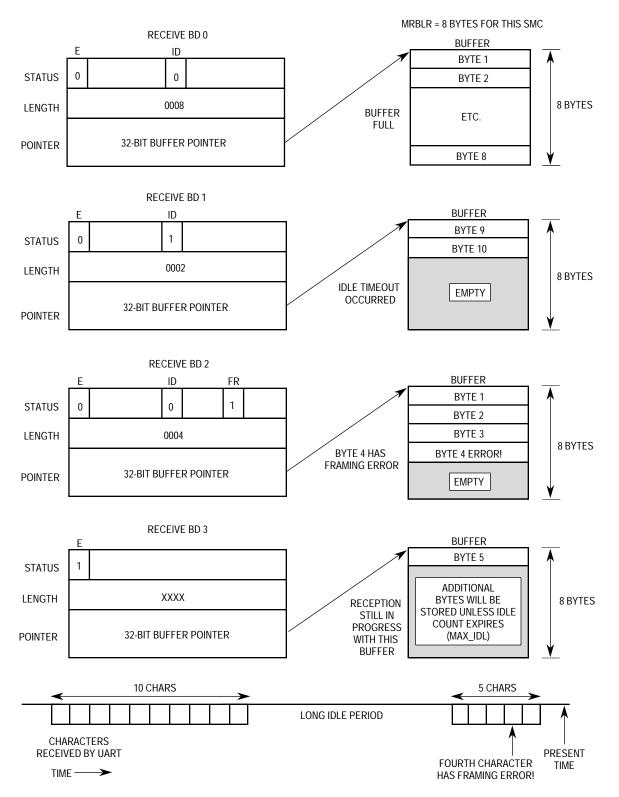

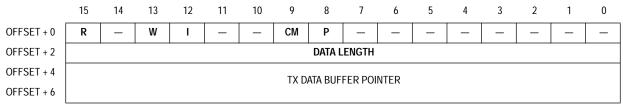

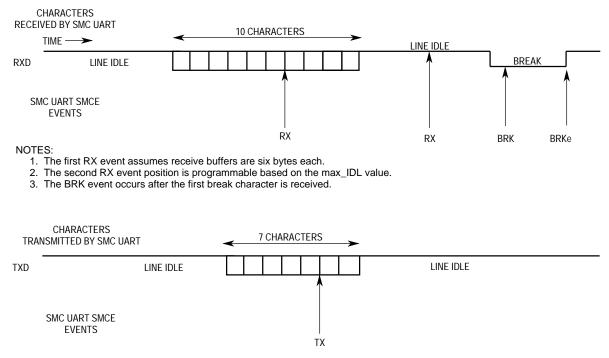

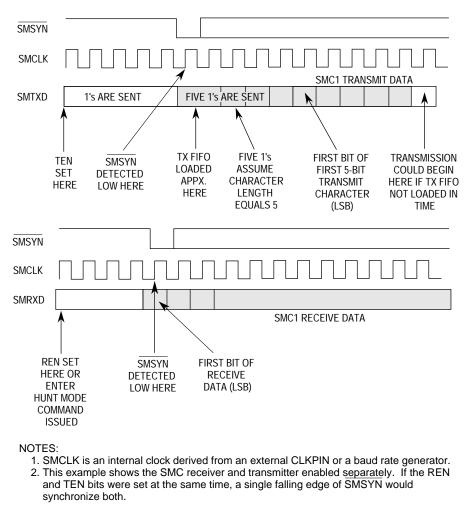

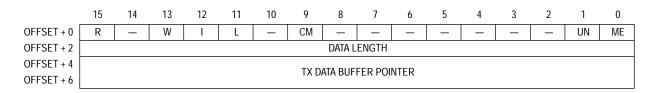

### 7.3.1 Buffer Descriptors

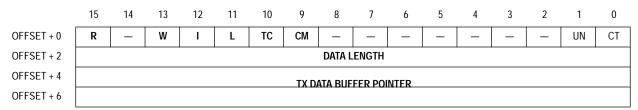

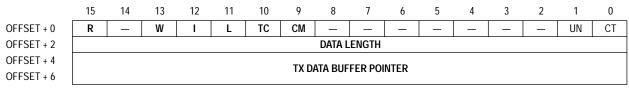

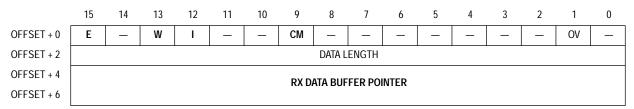

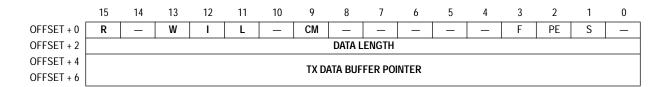

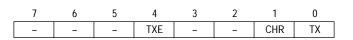

The SCCs, SMCs, SPI always use buffer descriptors for controlling data buffers. The buffer descriptor format of the SCCs, SMCs, and SPI is identical. The buffer descriptor format for these channels is shown in the following illustration.

|            | 150                            |

|------------|--------------------------------|

| OFFSET + 0 | STATUS AND CONTROL             |

| OFFSET + 2 | DATA LENGTH                    |

| OFFSET + 4 | HIGH-ORDER DATA BUFFER POINTER |

| OFFSET + 6 | LOW-ORDER DATA BUFFER POINTER  |

If the IDMA is used in the buffer chaining or auto buffer mode, the IDMA channel also uses buffer descriptors. The buffer descriptors for the IDMA are described in 7.6.1 IDMA Key Features;.

### 7.3.2 Parameter RAM

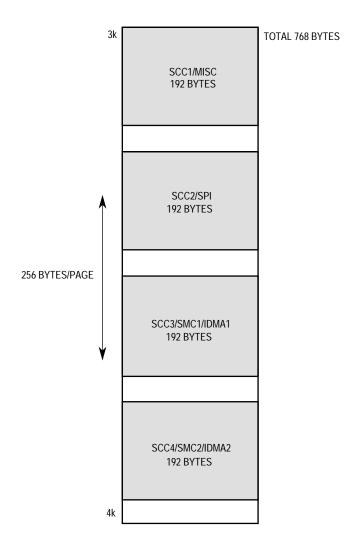

The CP maintains a section of dual-port RAM called the parameter RAM. This RAM contains many parameters for the operation of the SCCs, SMCs, SPI, and the IDMA channels. An overview of the parameter RAM structure is shown in Figure 7-4. The exact definition of the parameter RAM is contained in each subsection describing a device that uses a parameter RAM.

Figure 7-4. Parameter RAM Overview

### 7.4 RISC TIMER TABLES

The RISC controller has the ability to control up to 16 timers. These timers are separate from the four general-purpose timers and baud rate generators in the CPM. The 16 timers are ideally used in protocols that do not require extreme precision, but in which it is desirable to off-load the host CPU from having to scan the timer tables that are created in software. These timers are clocked from an internal timer used only by the RISC.

The features of the RISC timer tables are as follows:

- Up to 16 Timers Supported

- Two Timer Modes: One-Shot and Restart

- Maskable Interrupt on Timer Expiration

- Programmable Timer Resolution As Low As 41 μs at 25 MHz

- Maximum Timeout Period of 172 Sec at 25 MHz

Continuously Updated Reference Counter

All operations on the RISC timer tables are based on a fundamental "tick" of the RISC internal timer, which is programmed in the RISC RCCR. The tick is a multiple of 1024 general system clocks. (See 7.1 RISC Controller for more details.)

The RISC timer tables have the lowest priority of all RISC operations. Therefore, if the RISC is so busy with other tasks that it does not have time to service the timer during a tick interval, one or more of the timers may not be updated during a tick.

This behavior can actually be used to estimate the worst-case loading of the RISC processor. (See Table 7-2 for more details.)

The RISC timer tables are configured in the RCCR, the RISC timer table parameter RAM, and by the SET TIMER command issued to the CP command register, the RISC timer event register, and the RISC timer mask register.

### 7.4.1 RISC Timer Table Parameter RAM

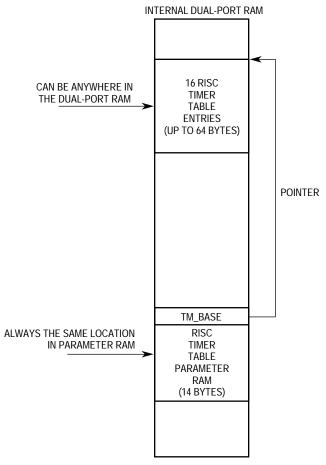

Two areas of internal RAM are used for the RISC timer tables: the RISC timer table parameter RAM and RISC timer table entries (see Figure 7-5). The RISC timer table parameter RAM area begins at the RISC timer base address (see Table 7-2). This area is used for the general timer parameters.

Figure 7-5. RISC Timer Table RAM Usage

| Address         | Name    | Width | Description                   |

|-----------------|---------|-------|-------------------------------|

| Timer Base + 00 | TM_BASE | Word  | RISC Timer Table Base Address |

| Timer Base + 02 | TM_ptr  | Word  | RISC Timer Table Pointer      |

| Timer Base + 04 | R_TMR   | Word  | RISC Timer Mode Register      |

| Timer Base + 06 | R_TMV   | Word  | RISC Timer Valid Register     |

| Timer Base + 08 | TM_cmd  | Long  | RISC Timer Command Register   |

| Timer Base + 0C | TM_cnt  | Long  | RISC Timer Internal Count     |

Table 7-2. RISC Timer Table Parameter RAM

NOTE: Boldfaced items are initialized by the user.

TM\_BASE. The actual RISC timers are located by the user as a small block of memory in the dual-port RAM. TM\_BASE is the offset from the beginning of dual-port RAM where that block resides. The user should allocate 4 bytes at TM\_BASE for each timer used (64 bytes at TM\_BASE if all 16 timers are used). If less than 16 timers are used, the timers should always be allocated in ascending order (RISC timer 0, RISC timer 1, etc.) to save space. For example, if the user only needs two timers, then 8 bytes are required at location TM\_BASE as long as the user only enables RISC timer 0 and RISC timer 1.

#### NOTE

TM\_BASE should always be aligned to a long-word boundary (i.e., evenly divisible by 4).

TM\_ptr. This value is used exclusively by the RISC to point to the next timer to be accessed in the timer table. It should not be modified by the user.

R\_TMR. This value is used exclusively by the RISC to store the mode of the timer: one-shot (bit is zero) or restart (bit is one). R\_TMR should not be modified by the user. The SET TIMER command should be used instead.

R\_TMV. This value is used exclusively by the RISC to store whether a timer is currently enabled. A bit is a one if the corresponding timer is enabled. R\_TMV should not be modified by the user. The SET TIMER command should be used instead.

TM\_cmd. This value is used as a parameter location when the SET TIMER command is issued. The user should write this location prior to issuing the SET TIMER command. This parameter is defined as follows:

| 31 | 30 | 29 |   |   | 20 | 19    | 16     | 15 |    |          |           |     | 0 |

|----|----|----|---|---|----|-------|--------|----|----|----------|-----------|-----|---|

| V  | R  |    | - | _ |    | TIMER | IUMBER |    | TI | MER PERI | OD (16 BI | TS) |   |

#### V—Valid

This bit should be set to enable the timer and cleared to disable the timer.

#### R—Restart

This bit should be set for an automatic restart or cleared for a one-shot operation of the timer.

Bits 29–20—Reserved

These bits should be written with zeros.

Bits 19–16—Timer Number

The timer number is a value from 0 to 15 that signifies the timer is configured.

Bits 15–0—Timer Period

The timer period is the 16-bit timeout value of the timer. The maximum value is 65536, which is programmed by writing \$0000 to the timer period.

TM\_cnt. This value is simply a tick counter that is updated by the RISC after each tick. It is updated if the RISC internal timer is enabled, regardless of whether any of the 16 timers are enabled. It can be used to track the number of ticks that the RISC has received and responded to. This value is updated only after the RISC scans the timer table.

# 7.4.2 RISC Timer Table Entries

The actual 16 timers themselves are located in the block of memory following the TM\_BASE location. Each timer occupies 4 bytes. The first word forms the initial value of the timer written during the execution of the SET TIMER command, and the next word is the current value of the timer, which is decremented until it reaches zero. These locations should not be modified by the user; they are documented only as a debugging aid for user code.

# 7.4.3 RISC Timer Event Register (RTER)

This 16-bit register is used to report events recognized by the 16 timers and to generate interrupts. Bit 0 corresponds to timer 0, and bit 15 corresponds to timer 15. Note that an interrupt will only be generated if the RISC timer table bit is set in the CPM interrupt mask register. RTER may be read at any time. A bit is cleared by writing a one (writing a zero does not affect a bit's value), and more than one bit may be cleared at a time. This register is cleared at reset.

# 7.4.4 RISC Timer Mask Register (RTMR)

This 16-bit register is used to enable interrupts that may be generated in the RISC timer event register. If a bit is set, it enables the corresponding interrupt in the RTER. If a bit is cleared, it masks the corresponding interrupt in the RTER. Note that an interrupt will only be generated if the RISC timer table bit is set in the CPM interrupt mask register. This read-write register is cleared at reset.

# 7.4.5 SET TIMER Command

This command is used to enable, disable, and configure the 16 timers in the RISC timer table. The SET TIMER command is issued to the CR. This means the value \$0851 should be written to CR. However, before writing this value, the TM\_cmd value should be set up by the user. See 7.4.1 RISC Timer Table Parameter RAM for details.

# 7.4.6 RISC Timer Initialization Sequence

The following sequence initializes the RISC timers:

1. Configure the RCCR to determine the desired tick interval that will be used for the en-

tire timer table. The TIME bit would normally be turned on at this time; however, it can be turned on later if it is required that all RISC timers be synchronized.

- Determine the maximum number of timers to be located in the timer table and configure TM\_BASE in the RISC timer table parameter RAM to point to a location in the dual port RAM with 4 × N bytes available, where N is the number of timers. If N is less than 16, use timer 0 through timer N–1 (for space efficiency).

- 3. Clear the TM\_cnt in the RISC timer table parameter RAM to show how many ticks have elapsed since the RISC internal timer was enabled. This step is optional.

- 4. Clear the RISC timer event register if it is not already cleared. (Ones are written to clear this register.)

- 5. Configure the RTMR to enable those timers that should generate interrupts. (Ones enable interrupts.)

- 6. Set the RISC timer table bit in the CPM interrupt mask register to generate interrupts to the system. (The CPM interrupt controller may require other initialization not mentioned here.)

- 7. Configure the TM\_cmd field of the RISC timer table parameter RAM. At this point, determine whether a timer is to be enabled or disabled, one-shot or restart, and what its timeout period should be. If the timer is being disabled, the parameters (other than the timer number) are ignored.

- 8. Issue the SET TIMER command by writing \$0861 to the CR.

- 9. Repeat the preceding two steps for each timer to be enabled or disabled.

### 7.4.7 RISC Timer Initialization Example

The following sequence initializes RISC timer 0 to generate an interrupt approximately every second using a 25-MHz general system clock:

- 1. Write the TIMEP bits of the RCCR with 111111 to generate the slowest clock. This value will generate a tick every 65536 clocks, which is every 2.6 ms at 25 MHz.

- 2. Configure TM\_BASE in the RISC timer table parameter RAM to point to a location in the dual-port RAM with 4 bytes available. Assuming the beginning of dual-port RAM is available, write \$0000 to TM\_BASE.

- 3. Write \$0000 to TM\_cnt in the RISC timer table parameter RAM to see how many ticks have elapsed since the RISC internal timer was enabled. This step is optional.

- 4. Write \$FFFF to the RTER to clear any previous events.

- 5. Write \$0001 to the RTMR to enable RISC timer 0 to generate an interrupt.

- 6. Write \$00020000 to the CPM interrupt mask register to allow the RISC timers to generate a system interrupt. Initialize the CPM interrupt configuration register.

- 7. Write \$C0000EE6 to the TM\_cmd field of the RISC timer table parameter RAM. This enables RISC timer 0 to time out after 3814 (decimal) ticks of the timer. The timer will automatically restart after it times out.

- 8. Write \$0851 to the CR to issue the SET TIMER command.

- 9. Set the TIME bit in the RCCR to enable the RISC timer to begin operation.

### 7.4.8 RISC Timer Interrupt Handling

The following sequence describes what would normally occur within an interrupt handler for the RISC timer tables:

- 1. Once an interrupt occurs, read the RISC timer event register to see which timer or timers have caused interrupts. The RISC timer event bits would normally be cleared at this time.

- 2. Issue additional SET TIMER commands at this time or later, as desired. Nothing need be done if the timer is being restarted automatically for a repetitive interrupt.

- 3. Clear the R-TT bit in the CPM interrupt status register.

- 4. Execute the RTE instruction.

### 7.4.9 RISC Timer Table Algorithm

The RISC scans the timer table once every tick. For each valid timer in the timer table, the RISC decrements the count and checks for a timeout. If no timeout occurs, it moves to the next timer. If a timeout occurs, the RISC sets the corresponding event bit in the RISC timer event register. It checks to see if the timer is to be restarted. If so, it leaves the timer valid bit set in the R\_TMV location and resets the current count to the initial count; otherwise, it clears the R\_TMV bit. Once the timer table is scanned, the RISC updates the TM\_cnt value in the RISC timer table parameter RAM and ceases working on the timer tables until the next tick.

If a SET TIMER command is issued, the RISC controller makes the appropriate modifications to the timer table and parameter RAM, but does not scan the timer table until the next tick of the internal timer. It is important to use the SET TIMER command to properly synchronize the timer table alterations to the execution of the RISC.

### 7.4.10 RISC Timer Table Application: Track the RISC Loading

The RISC timers can be used to track the loading of the RISC controller. The following sequence gives a method for using the 16 RISC timers to determine if the RISC controller ever exceeds the 96% utilization level during any tick interval. Removing the timers then adds a 4% margin to the RISC utilization level. The aggressive user can use this technique to push the RISC performance to its limit in an application.

The user should use the standard initialization sequence, with the following differences:

- 1. Program the tick of the RISC timers to be  $1024 \times 16 = 16384$ .

- 2. Disable RISC timer interrupts, if desired.

- 3. Using the SET TIMER command, initialize all 16 RISC timers to have a timer period of \$0000, which equates to 65536.

- 4. Program one of the four general-purpose timers to increment once every tick. The general-purpose timer should be free-running and should have a timeout of 65536.

- 5. After hours of operation, compare the general-purpose timer to the current count of RISC timer 15. If RISC timer 15 is more than two ticks different from the general-purpose timer, the RISC controller has, during some tick interval, exceeded the 96% uti-

lization level.

### NOTE

The general-purpose timers are up-counters, but the RISC timers are down-counters. The user should consider this fact when comparing timer counts.

### 7.5 TIMERS

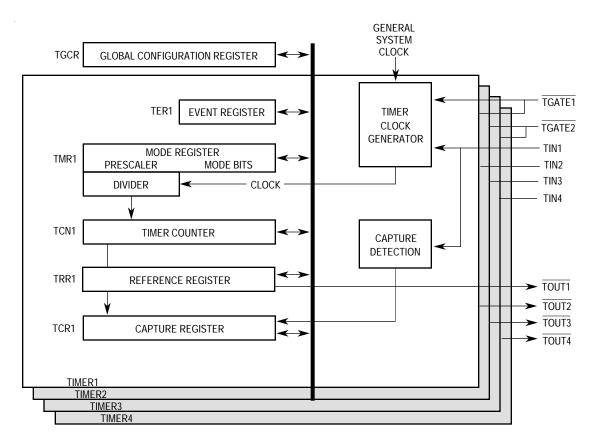

The CPM includes four identical, 16-bit, general-purpose timers or two 32-bit timers. Each general-purpose timer consists of a timer mode register (TMR), a timer capture register (TCR), a timer counter (TCN), a timer reference register (TRR), and a timer event register (TER). The TMR contains the prescaler value programmed by the user. In addition, there is one timer global configuration register (TGCR). The timer block diagram is shown in Figure 7-6.

Figure 7-6. Timer Block Diagram

# 7.5.1 Timer Key Features

The four identical general-purpose timers have the following features:

- Maximum Period of 10.7 Sec (at 25 MHz)

- 40-ns Resolution (at 25 MHz)

- Programmable Sources for the Clock Input

- Input Capture Capability

- Output Compare with Programmable Mode for the Output Pin

- Two Timers Internally or Externally Cascadable To Form a 32-Bit Timer

- Free Run and Restart Modes

- Functionally Compatible with Timer 1 and Timer 2 on the MC68302

### 7.5.2 General-Purpose Timer Units

The clock input to the prescaler may be selected from three sources: the general system clock, the general system clock divided by 16, or the corresponding TINx pin. Each option is discussed in the following paragraphs.

The general system clock is generated in the clock synthesizer and defaults to the system frequency (for instance, 25 MHz). However, the general system clock has the option to be divided before it leaves the clock synthesizer. This mode, called slow go, is used to save power. Whatever the resulting frequency of the general system clock, the user may choose either that frequency or that frequency divided by 16 as the input to the prescaler of each timer.

Alternatively, the user may choose the TINx pin to be the clock source. TINx is internally synchronized to the internal clock. If the user has chosen to internally cascade two 16-bit timers to a 32-bit timer, then a timer may internally use the clock generated by the output of another timer.

The clock input source is selected by the ICLK bits of the corresponding TMR. The prescaler is programmed to divide the clock input by values from 1 to 256. The output of the prescaler is used as an input to the 16-bit counter.

The best resolution of the timer is one clock cycle (40 ns at 25 MHz). The maximum period (when the reference value is all ones) is 268,435,456 cycles (10.7 sec at 25 MHz). Both values assume that the general system clock is the full 25 MHz.

Each timer may be configured to count until a reference is reached and then either begin a new time count immediately or continue to run. The FRR bit of the corresponding TMR selects each mode. Upon reaching the reference value, the corresponding TER bit is set, and an interrupt is issued if the ORI bit in the TMR is set.

Each timer may output a signal on the timer output pin (TOUT1, TOUT2, TOUT3, or TOUT4) when the reference value is reached (selected by the OM bit of the corresponding TMR). This signal can be an active-low pulse or a toggle of the current output. The output can also be internally connected to the input of another timer, resulting in a 32-bit timer.

Each timer has a 16-bit TCR, which is used to latch the value of the counter when a defined transition of TIN1, TIN2, TIN3, or TIN4 is sensed by the corresponding input capture edge detector. The type of transition triggering the capture is selected by the CE bits in the corresponding TMR. Upon a capture or reference event, the corresponding TER bit is set, and a maskable interrupt request is issued to the CPM interrupt controller.

The timers may be gated/restarted by an external gate signal. There are two gate pins: TGATE1 controls timer 1 and/or timer 2; TGATE2 controls timer 3 and/or timer 4.

Normal gate mode enables the count on a falling edge of the TGATEx pin and disables the count on the rising edge of the TGATEx pin. Normal gate mode allows the timer to count conditionally based on the state of the TGATEx pin.

Restart gate mode performs the same function as normal mode, except that it also resets the counter on the falling edge of the TGATEx pin. The restart gate mode has applications in pulse interval measurement and bus monitoring:

- Pulse Measurement—The restart gate mode can measure a low pulse on the TGATEx pin. The rising edge of the TGATEx pin completes the measurement, and if TGATEx is externally connected to TINx, causes the timer to capture the count value and generate a rising-edge interrupt.

- Bus Monitoring—The restart gate mode can detect a signal that is abnormally stuck low. The bus signal should be connected to the TGATEx pin. The timer count is reset on the falling edge of the bus signal, and if the bus signal does not go high again within the number of user-defined clocks, an interrupt can be generated.

The gate function is enabled in the TMR, and the gate operating mode is selected in the TGCR.

### NOTE:

TGATE is internally synchronized to the system clock. If TGATE meets the asynchronous input setup time (spec #47A) then, when working with the internal clock, the counter will begin counting after 1 system clock.

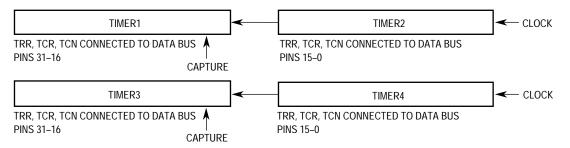

**7.5.2.1 CASCADED MODE.** In this mode (see Figure 7-7) two 16-bit timers can be internally cascaded to form a 32-bit counter. Timer 1 may be internally cascaded to timer 2, and timer 3 may be internally cascaded to timer 4. Since, the decision to cascade timers is made independently, the user may select such options as two 16-bit timers and one 32-bit timer. The TGCR is used to put the timers into cascaded mode.

Figure 7-7. Timer Cascaded Mode Block Diagram

If the CAS bit is set in the TGCR, the two timers function as a one 32-bit timer with one 32-bit TRR, one 32-bit TCR, and one 32-bit TCN. In this case, TMR1 and/or TMR3 are ignored, and the modes are defined using TMR2 and/or TMR4. The capture will be controlled from TIN2 or TIN4. Interrupts will be generated from TER2 or TER4.

When working in the cascaded mode, the cascaded TRR, TCR, and TCN should always be referenced with 32-bit bus cycles.

**7.5.2.2 TIMER GLOBAL CONFIGURATION REGISTER (TGCR).** The TGCR is a 16-bit, memory-mapped, read/write register that contains configuration parameters used by all four timers. It allows starting and stopping any number of timers simultaneously if one bus cycle is used to access TGCR. The TGCR is cleared by reset.

| [ | 15   | 14   | 13   | 12   | 11  | 10   | 9    | 8    | 7    | 6    | 5    | 4    | 3   | 2    | 1    | 0    |

|---|------|------|------|------|-----|------|------|------|------|------|------|------|-----|------|------|------|

|   | CAS4 | FRZ4 | STP4 | RST4 | GM2 | FRZ3 | STP3 | RST3 | CAS2 | FRZ2 | STP2 | RST2 | GM1 | FRZ1 | STP1 | RST1 |

CAS4—Cascade Timers

- 0 = Normal Operation.

- 1 = Timers 3 and 4 are cascaded to form a 32-bit timer.

- CAS2—Cascade Timers

- 0 = Normal Operation.

- 1 = Timers 1 and 2 are cascaded to form a 32-bit timer.

### FRZ—Freeze

- 0 = The corresponding timer ignores the FREEZE pin.

- 1 = Halt the corresponding timer if the FREEZE pin is asserted. (The FREEZE pin is asserted in background debug mode when the CPU32+ is enabled.)

### STP —Stop Timer

- 0 = Normal operation.

- 1 = Reduce power consumption of the timer. This bit stops all clocks to the timer, except the clock from the IMB interface, which allows the user to read and write timer registers. The clocks to the timer remain stopped until the user clears this bit or a hardware reset occurs.

### RST—Reset Timer

- 0 = Reset the corresponding timer (a software reset is identical to an external reset).

- 1 = Enable the corresponding timer if the STP bit is cleared.

### GM2—Gate Mode for Pin 2

This bit is only valid if the gate function is enabled in TMR3 or TMR4.

- 0 = Restart gate mode. The TGATE2 pin is used to enable/disable the count. The falling edge of TGATE2 enables and restarts the count, and the rising edge of TGATE2 disables the count.

- 1 = Normal gate mode. This mode is the same as 0, except the falling edge of TGATE2 does not restart the count value in TCN.

GM1—Gate Mode for Pin 1

This bit is only valid if the gate function is enabled in TMR1 or TMR2.

- 0 = Restart gate mode. The TGATE1 pin is used to enable/disable count. A falling TGATE1 pin enables and restarts the count, and a rising edge of TGATE1 disables the count.

- 1 = Normal gate mode. This mode is the same as 0, except the falling edge of TGATE1 does not restart the count value in TCN.

**7.5.2.3 TIMER MODE REGISTER (TMR1, TMR2, TMR3, TMR4).** TMR1–TMR4 are identical 16-bit, memory-mapped, read/write registers. These registers are cleared by reset.

### NOTE

The TGCR should be initialized prior to the TMRs, or erratic behavior may occur. The only exception is the RST bit in the TGCR, which may be modified at any time.

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5  | 4   | 3   | 2  | 1  | 0  |

|----|----|----|----|----|----|---|---|---|---|----|-----|-----|----|----|----|

|    |    |    | Р  | S  |    |   |   | ( | E | OM | ORI | FRR | IC | LK | GE |

PS—Prescaler Value

The prescaler is programmed to divide the clock input by values from 1 to 256. The value 00000000 divides the clock by 1; the value 11111111 divides the clock by 256.

CE—Capture Edge and Enable Interrupt

- 00 = Disable interrupt on capture event; capture function is disabled.

- 01 = Capture on rising TINx edge only and enable interrupt on capture event.

- 10 = Capture on falling TINx edge only and enable interrupt on capture event.

- 11 = Capture on any TINx edge and enable interrupt on capture event.

### OM—Output Mode

- 0 = Active-low pulse on TOUTx for one timer input clock cycle as defined by the ICLK bits. Thus, TOUTx may be low for one general system clock period, one general system clock/16 period, or one TINx pin clock cycle period. TOUTx changes occur on the rising edge of the system clock.

- 1 = Toggle the TOUTx pin. TOUTx changes occur on the rising edge of the system clock.

ORI—Output Reference Interrupt Enable

- 0 = Disable interrupt for reference reached (does not affect interrupt on capture function).

- 1 = Enable interrupt upon reaching the reference value.

#### FRR—Free Run/Restart

- 0 = Free run. The timer count continues to increment after the reference value is reached.

- 1 = Restart. The timer count is reset immediately after the reference value is reached.

ICLK—Input Clock Source for the Timer

00 = Internally cascaded input.

For TMR1, the timer 1 input is the output of timer 2.

For TMR3, the timer 3 input is the output of timer 4.

- For TMR2 and TMR4, this selection means no input clock is provided to the timer.

- 01 = Internal general system clock.

- 10 = Internal general system clock divided by 16.

- 11 = Corresponding TIN pin: TIN1, TIN2, TIN3, or TIN4 (falling edge).

GE—Gate Enable

- 0 = The TGATE signal is ignored.

- 1 = The TGATE signal is used to control the timer.

**7.5.2.4 TIMER REFERENCE REGISTERS (TRR1, TRR2, TRR3, TRR4).** Each TRR is a 16-bit, memory-mapped, read-write register containing the reference value for the timeout. TRR1–TRR4 are set to all ones by reset. The reference value is not reached until TCN increments to equal TRR.

**7.5.2.5 TIMER CAPTURE REGISTERS (TCR1, TCR2, TCR3, TCR4).** Each TCR is a 16bit register used to latch the value of the counter. TCR1–TCR4 appear as memory- mapped, read-only registers to the user. TCR1–TCR4 are cleared by reset.

**7.5.2.6 TIMER COUNTER (TCN1, TCN2, TCN3, TCN4).** Each TCN is a 16-bit, memorymapped, read-write up-counter. A read cycle to TCN1–TCN4 yields the current value of the timer, but does not affect the counting operation. A write cycle to TCN1–TCN4 sets the register to the written value, causing its corresponding prescaler to be reset.

### NOTE

Write operation to this register while the timer is not running may not update the register correctry. User should always use timer refrence register to define desired count value.

**7.5.2.7 TIMER EVENT REGISTERS (TER1, TER2, TER3, TER4).** Each TER is a 16-bit register used to report events recognized by any of the timers. On recognition of an output reference event, the timer sets the REF bit in the TER, regardless of the corresponding ORI in the TMR. The capture event will be set only if enabled by the CE bits in the TMR. TER1–TER4, which appear to the user as memory-mapped registers, may be read at any time.

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1   | 0   |

|----|----|----|----|----|----|---|---|---|---|---|---|---|---|-----|-----|

|    |    |    |    |    |    | - |   |   |   |   |   |   |   | REF | CAP |

A bit is reset by writing a one to that bit (writing a zero does not affect a bit's value). More than one bit may be reset at a time. Both bits must be reset before the timer will negate the interrupt to the CPM interrupt controller. This register is cleared by reset.

Bits 15–2—Reserved

### REF—Output Reference Event

The counter has reached the TRR value. The ORI bit in the TMR is used to enable the interrupt request caused by this event.

CAP—Capture Event

The counter value has been latched into the TCR. The CE bits in the TMR are used to enable generation of this event.

### 7.5.3 Timer Examples

The following example lists the required initialization sequence of timer 2 to generate an interrupt every 10  $\mu$ s, assuming a general system clock of 25 MHz. This means that an interrupt should be generated every 250 system clocks.

- 1. TGCR = \$0000. Put timer 2 into the reset state. Do not use cascaded mode.

- TMR2 = \$001A. Enable the prescaler of the timer to divide-by-1 and the clock source to general system clock. Enable an interrupt when the reference value is reached, and restart the timer to repeatedly generate 10-μs interrupts.

- 3. TCN2 = \$0000. Initialize the timer 2 count to zero. This is the default state of this register.

- 4. TRR2 = \$00FA. Initialize the timer 2 reference value to 250 (decimal).

- 5. TER2 = \$FFFF. Clear TER2 of any bits that might have been set.

- 6. CIMR = \$00040000. Enable the timer 2 interrupt in the CPM interrupt controller. Initialize the CPM interrupt configuration register.

- 7. TGCR = \$0010. Enable timer 2 to begin counting.

To implement the same function with a 32-bit timer using timer 1 and timer 2, the following sequence may be used:

- 1. TGCR = \$0080. Cascade timer 1 and timer 2. Put timer 1 and timer 2 in the reset state.

- TMR2 = \$001A. Enable the prescaler of timer 2 to divide-by-1 and the clock source to general system clock. Enable an interrupt when the reference value is reached, and restart the timer to repeatedly generate 10 µs interrupts.

- 3. TMR1 = \$0000. Enable timer 1 to use the output of timer 2 as its input, which is the default state of this register.

- 4. TCN1 = \$0000, TCN2 = \$0000. Initialize the combined timer 1 and timer 2 count to zero which is the default state of this register. (This can be accomplished with one 32-bit data move to TCN1.)

- 5. TRR1 = \$0000, TRR2 = \$00FA. Initialize the combined timer 1 and timer 2 reference value to 250 (decimal). (This can be accomplished with one 32-bit data move to TRR1.)

- 6. TER2 = \$FFFF. Clear TER2 of any bits that might have been set.

- 7. CIMR = \$00040000. Enable the timer 2 interrupt in the CPM interrupt controller. Initialize the CPM interrupt configuration register.

- 8. TGCR = \$0091. Enable timer 1 and timer 2 to begin counting. Leave the timers in cas-

caded mode.

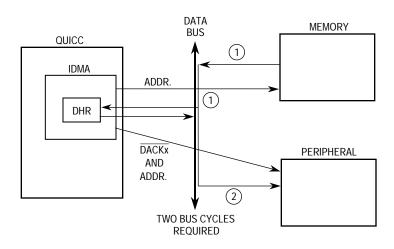

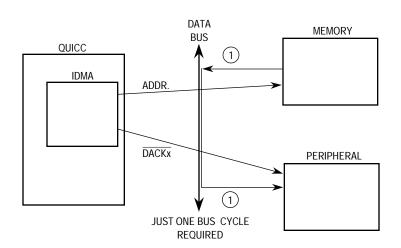

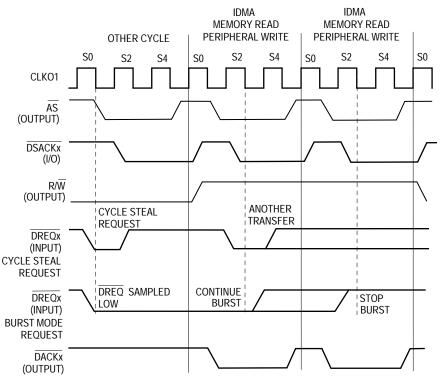

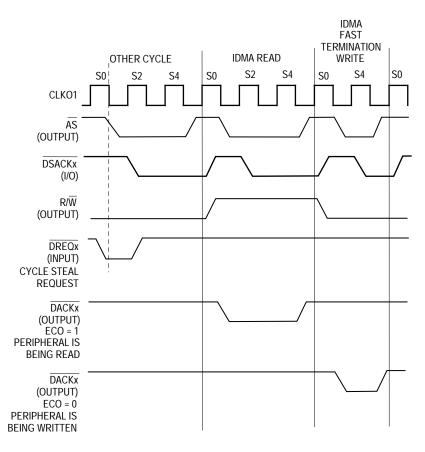

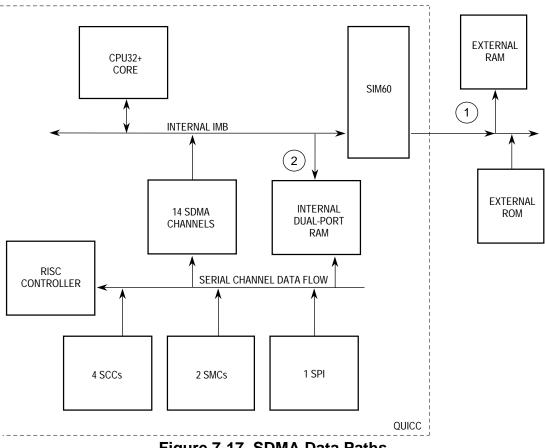

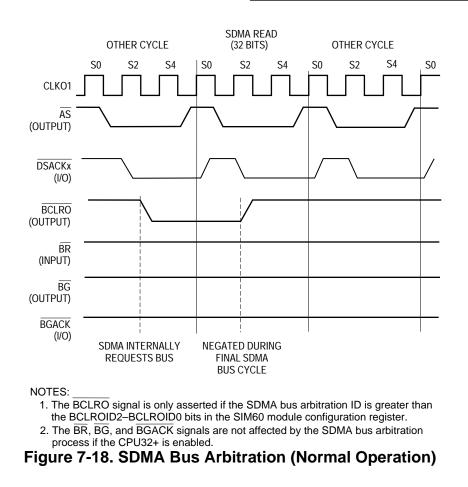

### 7.6 IDMA CHANNELS

The QUICC includes a number of DMA channels, including 14 SDMA channels for the four SCCs, two SMCs, and SPI and two general-purpose IDMA controllers. The SDMA channels are discussed in 7.7 SDMA Channels. The IDMA channels are discussed in the following paragraphs.

The two general-purpose IDMA controllers can operate in different modes of data transfer as programmed by the user. The IDMA can transfer data between any combination of memory and I/O. In addition, data may be transferred in either byte, word, or long-word quantities, and the source and destination addresses may be either odd or even. The most efficient packing algorithms are used in the IDMA transfers. The single address mode gives the highest performance, allowing data to be transferred between memory and a peripheral in a single bus cycle. The chip-select and wait-state generation logic on the QUICC may be used with the IDMA.

The IDMA supports three buffer handling modes: single buffer, auto buffer, and buffer chaining. Single buffer mode is that of the traditional DMA controller. The auto buffer mode allows blocks of data to be repeatedly moved from one location to another without user intervention. The buffer chaining mode allows a chain of blocks to be moved. The user specifies the data movement using buffer descriptors that are similar to those used by an SCC. These buffer descriptions reside in the dual-port RAM.

If the single buffer mode of the IDMA is used, programming the IDMA is very similar (although not exactly software compatible) to that of the IDMA on the MC68302 or the DMA controller on the MC68340. The auto buffer and buffer chaining modes, however, are not available on those devices, and the single address mode is not available on the MC68302.

The maximum transfer rate of the IDMA is 50 Mbyte/sec. This assumes a 32-bit data transfer from memory to peripheral using fast termination (2 clocks per bus cycle) timing and single address mode: (4 Bytes  $\times$  25 MHz Clocks/sec)/(2 Clocks per Transfer) = 50 Mbyte/sec.

The maximum transfer rate of the IDMA in dual address mode is 25 Mbyte/sec. This assumes a 32-bit source and destination, fast termination (2 clocks per bus cycle) timing, and two bus cycles for each transfer: (4 Bytes  $\times$  25 MHz Clocks/sec)/(4 Clocks per Transfer) = 25 Mbyte/sec.

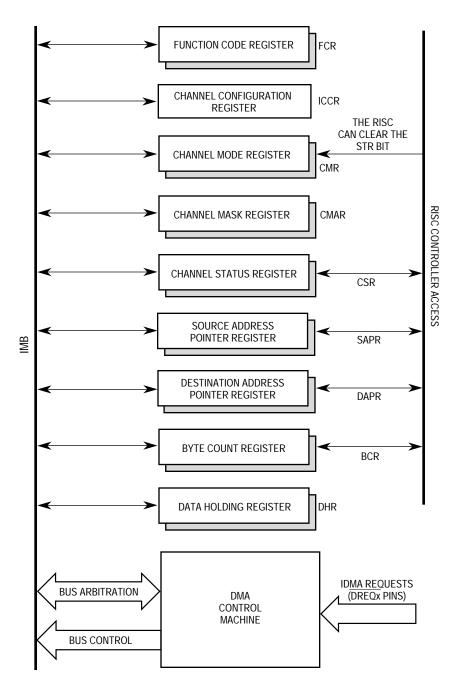

The IDMA controller block diagram is shown in Figure 7-8.

Figure 7-8. IDMA Controller Block Diagram

# 7.6.1 IDMA Key Features;

The IDMA contains the following features:

- Two Independent, Fully Programmable DMA Channels

- Dual Address or Single Address Transfers with 32-Bit Address and 32-Bit Data Capability

- Up to 50 Mbyte/sec Transfer Rates in Single Address Mode and 25 Mbyte/sec in Dual Address Mode (assuming a 25-MHz system clock)

- 32-Bit Byte Transfer Counters

- 32-Bit Address Pointers That Can Increment or Remain Constant

- Operand Packing and Unpacking for Dual Address Transfers using the Most Efficient Techniques

- Supports All Bus-Termination Modes

- Provides Full DMA Handshake for Cycle Steal and Burst Transfers

- Supports Fixed and Rotating Priority Between IDMA Channels

- Buffer Handling Modes: Single Buffer, Auto Buffer, and Buffer Chaining

### 7.6.2 IDMA Registers

Each IDMA channel has eight registers that define its specific operation. These registers include a 32-bit source address pointer register (SAPR), a 32-bit destination address pointer register (DAPR), an 8-bit function code register (FCR), a 32-bit byte count register (BCR), a 16-bit channel mode register (CMR), an 16-bit channel configuration register (ICCR), an 8-bit channel status register (CSR), and an 8-bit channel mask register (CMAR). These registers provide the addresses, transfer count, and configuration information necessary to set up a transfer. They also provide a means of controlling the IDMA channel and monitoring its status. All registers can be modified by the CPU32+ core.

For the auto buffer and buffer chaining modes, the RISC controller uses a buffer descriptor ring to automatically initialize the DAPR, SAPR, and BCR. The buffer descriptor ring resides in dual-port RAM so that it may be accessed by the RISC controller without bus overhead.

The IDMA channel also includes a 32-bit data holding register (DHR), which is not accessible to the CPU32+ core and is used by the IDMA for temporary data storage.

**7.6.2.1 IDMA CHANNEL CONFIGURATION REGISTER (ICCR).** The 16-bit ICCR configures both IDMA channels. It is always readable and writable in the supervisor mode, although writing is not recommended unless the module is disabled. It is initialized to \$0000 at reset.

| 15  | 14 | 13 | 12 | 11 | 10 | 9   | 8 | 7 | 6 | 5    | 4 | 3 | 2 | 1 | 0 |

|-----|----|----|----|----|----|-----|---|---|---|------|---|---|---|---|---|

| STP | FI | RZ | AR | BP |    | ISM |   | — |   | IAID |   |   | - | _ |   |

STP—Stop Bit

- 0 = The system clock operates normally within the IDMA.

- 1 = Stop the system clock to the IDMA channels. This setting is used to conserve power when both IDMAs are unused.

### FRZ1-FRZ0-Freeze

These bits determine the action to be taken when the FREEZE signal is asserted. The IDMA negates its internal bus request and keeps it negated until FREEZE is negated or the IDMA is reset.

00 = The IDMA channels ignore the FREEZE signal.

01 = Reserved.

10 = The IDMA channels freeze on the next bus cycle.

11 = Reserved.

#### ARBP—Arbitration Priority

These two bits select the arbitration priority between the two IDMA channels.

00 = IDMA channel 1 has priority over channel 2.

01 = IDMA channel 2 has priority over channel 1.

10 = Rotating priority.

11 = Reserved.

ISM—Interrupt Service Mask

These bits contain the interrupt service mask. When the interrupt service level on the IMB is greater than the interrupt service mask, the IDMA vacates the bus and negates its bus request to the IMB until the interrupt level service is less than or equal to the interrupt service mask.

#### NOTE

The user should program ISM to 7 for typical user applications. This gives the IDMA priority over all interrupt handlers. These bits MUST be set to 7 if the QUICC is in slave mode.

#### Bits 7, 3–0—Reserved

IAID—IDMA Arbitration ID

These bits establish bus arbitration priority level among sub-blocks that have the capability of becoming bus master. In the QUICC, the IDMAs, the SDMAs, and the SIM60 DRAM refresh controller can become bus masters. An arbitration ID uses a number (0-7) to decide the priority of multiple bus masters that are requesting the IMB. A 0 is the lowest priority and a 7 is the highest priority.

The value programmed into the IAID bits is the arbitration ID of the highest priority IDMA channel. The arbitration ID of the lowest priority IDMA channel is IAID minus 2. The ARBP bits determine which IDMA channel has the higher priority. If round-robin priority is selected, then the IDMA channels alternate between the two IAID values.

Example: If ARBP = 00, selecting IDMA channel 1 to always have the highest priority, the IAID values are:

IDMA channel 1 arbitration ID = IAID

IDMA channel 2 arbitration ID = IAID - 2

### NOTES

The user should program IAID to 2 in typical user applications. IAID should not be programmed to a value less than 2. This val-

ue should be less than the SDMA arbitration ID so that the SDMA channels have priority over the IDMA channels. User must program this field to 7 when the QUICC is configured in slave mode.

**7.6.2.2 CHANNEL MODE REGISTER (CMR).** Each IDMA channel contains a 16-bit CMR that is reset to \$0000. It is used to configure most of the IDMA options.

| 1! | 5 | 14  | 13  | 12  | 11   | 10 | 9    | 8    | 7     | 6 | 5     | 4 | 3  | 2 | 1   | 0   |

|----|---|-----|-----|-----|------|----|------|------|-------|---|-------|---|----|---|-----|-----|

| EC |   | SRM | S/D | RCI | REQG |    | SAPI | DAPI | SSIZE |   | DSIZE |   | BT |   | RST | STR |

### ECO — External Control Option

Dual Address Mode: this bit defines which device is connected to the control signals.

- 0 = The control signals (DREQx, DACKx, and DONEx) are associated with the destination (write) portion of the transfer.

- 1 = The control signals (DREQx, DACKx, and DONEx) are associated with the source (read) portion of the transfer.

Single Address Mode: this bit defines the direction of the transfer.

- 0 = The device writes to memory, and the control signals (DREQx, DACKx, and DON-Ex) are used by the device to provide data during the destination (write) portion of the transfer.

- 1 = The device reads from memory, and the control signals (DREQx, DACKx, and DONEx) are used by the device to write data during the source (read) portion of the transfer.

#### NOTE

If REQG is programmed to be internal (REQG = 0X),  $\overline{\text{DREQx}}$  is ignored.

#### SRM — Synchronous Request Mode

This bit controls how external devices may use the DREQx pin for IDMA service. This bit is only relevant for applications that use external request mode or use the external DONEx pin to terminate the IDMA operation.

- 0 = Asynchronous request mode is selected. The DREQx and DONEx input signals are internally synchronized to the IDMA clock before they are used by the IDMA.

- 1 = Synchronous request mode is selected. The DREQx and DONEx input signals are used by the IDMA without first being internally synchronized. This results in faster operation, but should only be used if setup and hold times can be met.

- S/D Single/Dual Address Transfer

- 0 = The IDMA channel runs standard dual address transfers. Each transfer requires at least two bus cycles. Data packing is performed using the DHR.

- 1 = The IDMA channel runs single address transfers from a peripheral to memory or from memory to a peripheral. The transfer requires one bus cycle. The DHR is not used for these transfers because the data is transferred directly into the destination location.

RCI — RISC Controls IDMA

- 0 = Single Buffer Mode. The user programs all IDMA registers for each buffer transfer.

- 1 = Auto buffer or buffer chaining mode. The RISC reconfigures the IDMA channel at the end of each buffer transfer according to the buffer descriptor ring. The choice between auto buffer and buffer chaining is made in the buffer descriptor itself.

### REQG — Request Generation

The REQG bits define what generates the requests for IDMA activity over the bus.

- 00 = Internal request at limited rate (limited burst bandwidth) set by BT bits

- 01 = Internal request at maximum rate (one burst)

- 10 = External request burst transfer mode (DREQx is level sensitive)

- 11 = External request cycle steal ( $\overline{DREQx}$  is edge sensitive)

### SAPI — SAPR Increment

- 0 = SAPR is not incremented after each transfer.

- 1 = SAPR is incremented by one, two, or four after each transfer, according to the SSIZE bits. (SAPR may be incremented by an amount less than the SSIZE value at the beginning or end of a block transfer, depending on the source starting address or byte count.)

### DAPI — DAPR Increment

- 0 = DAPR is not incremented after each transfer.

- 1 = DAPR is incremented by one, two, or four after each transfer, according to the DSIZE bits. (DAPR may be incremented by an amount less than the DSIZE value at the beginning or end of a block transfer, depending on the destination starting address or byte count.)

#### SSIZE — Source Size

The following decoding shows the definitions for the SSIZE bits. The user should set these bits to the port size of the source (e.g., choose byte for an 8-bit peripheral).

- 00 = Long word

- 01 = Byte

- 10 = Word

- 11 = Reserved

### DSIZE — Destination Size

The following decoding shows the definitions for the DSIZE bits. The user should set these bits to the port size of the destination (e.g., choose byte for an 8-bit peripheral).

- 00 = Long word

- 01 = Byte

- 10 = Word

- 11 = Reserved

#### BT — Burst Transfer

The BT bits control the maximum percentage of the IMB that the IDMA can use during each 1024 clock cycle period after enabling the IDMA.

- 00 = IDMA gets up to 75% of the bus bandwidth.

- 01 = IDMA gets up to 50% of the bus bandwidth.

- 10 = IDMA gets up to 25% of the bus bandwidth.

- 11 = IDMA gets up to 12.5% of the bus bandwidth.

#### NOTE

These percentages are valid only when using internal request generation (REQG = 00).

### **RST—Software Reset**

This bit resets the IDMA to the same state as an external reset. The IDMA clears RST when the reset is complete.

- 0 = Normal operation.

- 1 = The channel aborts any external pending or running bus cycles and terminates channel operation. Setting RST clears all bits in the CSR and CMR.

### NOTE

The user should reset the IDMA channel prior to issuing the LP-STOP instruction.

### STR—Start Operation

This bit starts the IDMA transfer if the REQG bits are programmed for an internal request. If the REQG bits are programmed for an external request, this bit must be set before the IDMA will recognize the first request on the DREQx input.

- 0 = Stop channel. Clearing this bit causes the IDMA to stop transferring data at the end of the current bus cycle. The IDMA internal state is not altered.

- 1 = Start channel. Setting this bit allows the IDMA to start transferring data (or continue if previously stopped).

### NOTES

STR is cleared automatically when the transfer is complete.

If the STR bit is cleared by software during the middle of an IDMA operand transfer, the IDMA will continue to hold the bit in a one state until the operand transfer has completed. Thus, if the user waits for the STR bit to be cleared after clearing it in software, he is assured that the values of SAPR, DAPR, and BCR accurately show the current state of the IDMA transfer.

**7.6.2.3 SOURCE ADDRESS POINTER REGISTER (SAPR).** The SAPR contains 32 address bits of the source operand used by the IDMA to access memory or memory-mapped peripheral controller registers. During the IDMA read cycle, the address on the master address bus is driven from this register. The SAPR may be programmed by the SAPI bits to be incremented or remain constant after each operand transfer.

The register is incremented using unsigned arithmetic and will roll over if an overflow occurs. For example, if a register contains \$FFFFFFF and is incremented by one, it will roll over to \$00000000. This register can be incremented by one, two, or four, depending on the SSIZE bits and the starting address in this register.

The SAPR may be initialized by the host processor or by the RISC controller via a buffer descriptor's ring structure when the RCI bit is set for special buffer handling modes.

**7.6.2.4 DESTINATION ADDRESS POINTER REGISTER (DAPR).** The DAPR contains 32 address bits of the destination operand used by the IDMA to access memory or memory-mapped peripheral controller registers. During the IDMA write cycle, the address on the master address bus is driven from this register. The DAPR may be programmed by the DAPI bits to be incremented or remain constant after each operand transfer.

The register is incremented using unsigned arithmetic and will roll over if overflow occurs. For example, if a register contains \$FFFFFFF and is incremented by one, it will roll over to \$00000000. This register can be incremented by one, two, or four, depending on the DSIZE bit and the starting address.

The DAPR may be initialized by the host processor or by the RISC controller via a buffer descriptor's ring structure when the RCI bit is set for special buffer handling modes.

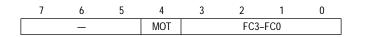

**7.6.2.5 FUNCTION CODE REGISTER (FCR).** Each IDMA channel has an 8-bit FCR that is initialized to \$00 at reset.

7

6

5

4

3

2

1

0

DFC3-DFC0

SFC3-SFC0

SFC3-SFC0

During an IDMA bus cycle, the SFC and DFC bits define the source and destination function code values that are output by the IDMA and the appropriate address registers. The address space on the function code lines may be used by an external memory management unit (MMU) or other memory-protection device to translate the IDMA logical addresses to proper physical addresses. The function code value programmed into the FCR is placed on pins FC3–FC0 during a bus cycle to further qualify the address bus value.

#### NOTES

This register is typically set to 1xxx1xxxb to cause the IDMA to operate in the DMA function code space, as opposed to a CPU program or data space.

To keep interrupt acknowledge cycles unique in the system, do not set this register to \$77.

**7.6.2.6 BYTE COUNT REGISTER (BCR).** This 32-bit register specifies the number of bytes of data to be transferred by the IDMA. The largest value that can be specified is 4 Gbytes (BCR = \$0000000). This register is decremented once for each byte transferred successfully, for a total of 1, 2, or 4 per operand transfer. BCR may be even or odd as desired. The

IDMA channel will terminate the transfer of a block of memory if this register reaches zero during operation.

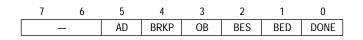

**7.6.2.7 CHANNEL STATUS REGISTER (CSR).** The CSR is an 8-bit register used to report events recognized by the IDMA controller. On recognition of an event, the IDMA sets its corresponding bit in the CSR, regardless of the corresponding bits in the CMAR. The CSR is a memory-mapped register that may be read at any time. A bit is reset by writing a one and is left unchanged by writing a zero. More than one bit may be reset at a time, and the register is cleared by reset.

### Bits 7–6—Reserved

### AD—Auxiliary Done

This bit is valid in auto buffer and buffer chaining modes. It is set when the IDMA channel has completed a buffer transfer for a buffer descriptor (BD) that has its I-bit set. For AD to be set, the BCR must have been decremented to zero with no errors occurring during any IDMA transfer bus cycle. The IDMA will then move to the next BD and continue to transfer data.

#### BRKP—Breakpoint

This bit indicates that the breakpoint signal was asserted during an IDMA transfer. This bit is cleared by writing a one or by reset. Writing a zero has no effect on BRKP.

#### **OB**—Out of Buffers

This bit is valid only when the RISC controls the IDMA (RCI bit in the CMR is set). It is set when working with the RISC controller and there are no more valid buffers out of which to transfer data.

#### **BES**—Bus Error Source

This bit indicates that the IDMA channel terminated with an error during the read cycle. The channel terminates the IDMA operation without setting DONE. BES is cleared by writing a one or by setting RST in the CMR. Writing a zero has no effect on BES.

### **BED**—Bus Error Destination

This bit indicates that the IDMA channel terminated with an error during the write cycle. The channel terminates the IDMA operation without setting DONE. BED is cleared by writing a one or by setting RST in the CMR. Writing a zero has no effect on BED.

#### DONE—Normal Channel Transfer Done

This bit indicates that the IDMA channel has terminated normally. Normal channel termination is defined as follows:

1. In single buffer mode, the BCR has decremented to zero, and no errors have occurred during any IDMA transfer bus cycle.

- 2. In buffer chaining or auto buffer modes, the BCR has decremented to zero, the L-bit in the BD has been set, and no errors have occurred during any IDMA transfer bus cycle.

- 3. An external peripheral has asserted DONEx during an access by the IDMA to that peripheral and no errors have occurred during any IDMA transfer bus cycle.

DONE will not be set if the channel terminates due to an error. DONE is cleared by writing a one or by setting RST in the CMR. Writing a zero has no effect on DONE.

**7.6.2.8 CHANNEL MASK REGISTER (CMAR).** The CMAR is an 8-bit, memory-mapped, read-write register that has the same bit format as the CSR. If a bit in the CMAR is a one, the corresponding interrupt in the CSR will be enabled. If the bit is a zero, the corresponding interrupt in the CSR will be masked. CMAR is cleared at reset.

**7.6.2.9 DATA HOLDING REGISTER (DHR).** This 7-byte register serves as a buffer register for the data being transferred during dual address IDMA cycles. No address for DHR is given since this register cannot be addressed by the programmer. The DHR allows the data to be packed and unpacked by the IDMA during the transfer. For example, if the source operand size is byte and the destination operand size is word, then two-byte read cycles occur, followed by a one-word write cycle. The two bytes of data are buffered in the DHR until the word write cycle occurs. The DHR allows for packing and unpacking of operands for all possible combinations: bytes to words, bytes to long words, words to long words, words to bytes, long words to bytes, and long words to words.

### 7.6.3 Interface Signals

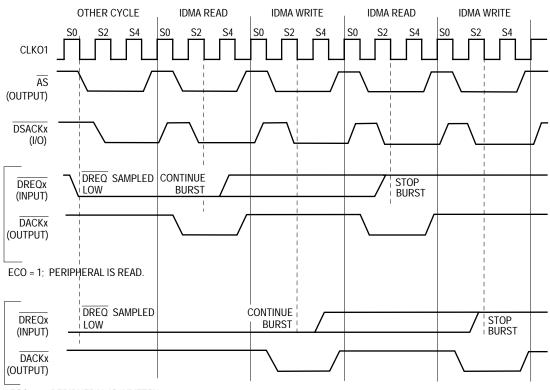

The IDMA has three dedicated control signals per channel: DMA request ( $\overline{DREQx}$ ), DMA acknowledge ( $\overline{DACKx}$ ), and end of IDMA transfer ( $\overline{DONEx}$ ). The peripheral used with these signals may be either a source or a destination of the IDMA transfers.

#### NOTE

DREQ must be level sensitive if IDMA uses buffer chaining mode.

**7.6.3.1 DREQ AND DACK.** These are the handshake signals between the peripheral requiring service and the QUICC. When the peripheral requires IDMA service, it asserts DREQx, and the QUICC begins the IDMA process. When the IDMA service is in progress, DACKx is asserted during accesses to the device. DREQx is ignored when the IDMA is programmed to one of the internal request modes.

**7.6.3.2 DONEX.** This bidirectional open-drain signal is used to indicate the last IDMA transfer. DONEx is always an output of the IDMA if the transfer count is exhausted.

DONEx may also operate as an input. If DONEx is externally asserted during internal request modes, the IDMA transfer is terminated. With external request modes, DONEx may be used as an input to the IDMA controller to indicate that the device being serviced requires no more transfers and the transmission is to be terminated.

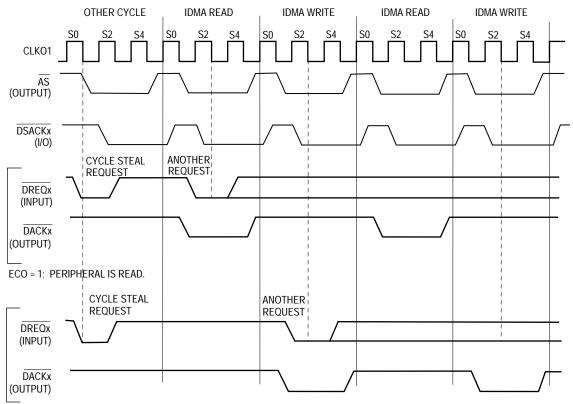

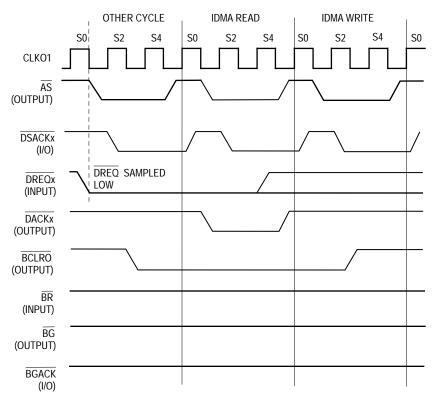

### 7.6.4 IDMA Operation

Every IDMA operation involves the following steps: IDMA channel initialization, data transfer, and block termination. In the initialization phase, the core (or external processor) loads the registers with control information, initializes the IDMA BDs (if auto buffer or buffer chaining is used), and then starts the channel. In the transfer phase, the IDMA accepts requests for operand transfers and provides addressing and bus control for the transfers. The termination phase occurs when the operation is complete and the IDMA interrupts the core if interrupts are enabled.

To initialize a block transfer operation, the user must initialize the IDMA registers. For the auto buffer and buffer chaining modes, the IDMA BDs must be initialized with information describing the data block, device type, request generation method, and other special control options. See 7.6.2 IDMA Registers and 7.6.4.2.3 IDMA Commands (INIT\_IDMA) for further details.

**7.6.4.1 SINGLE BUFFER.** The single buffer mode is used to transfer only one buffer of data. When the buffer has been completely transferred (transfer count exhausted or DONEx is asserted), the IDMA channel operation is terminated, STR is cleared, and a maskable interrupt is generated by the DONE bit in the CSR.

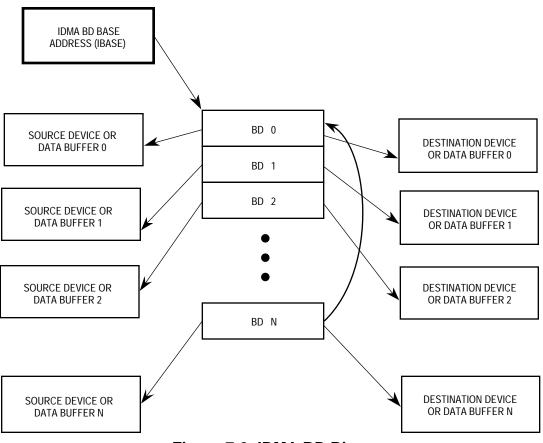

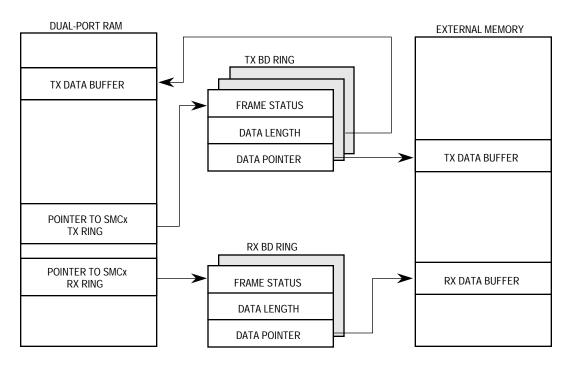

**7.6.4.2 AUTO BUFFER AND BUFFER CHAINING.** The auto buffer and the buffer chaining modes are supported with the RISC controller by setting the RCI bit in the CMR. The host processor should initialize the IDMA BD ring (see Figure 7-9) with the appropriate buffer handling mode, source address, destination address, and block length. The user then sets the STR bit in the CMR. All transfer modes described in 7.6.4.4.4 External Cycle Steal are still valid. The function codes for the source and destination addresses are programmed as described in 7.5.2.5 Timer Capture Registers (TCR1, TCR2, TCR3, TCR4).

Figure 7-9. IDMA BD Ring

The data associated with each IDMA channel for the auto buffer and buffer chaining modes is stored in buffers. Each buffer is referenced by a BD. The BDs use a ring structure located in the dual-port RAM.

**7.6.4.2.1 IDMA Parameter RAM.** When an IDMA channel is configured to the auto buffer or buffer chaining mode, the QUICC uses the IDMA parameters listed in Table 7-2.T

| Address        | Name   | Width | Description          |  |  |  |  |

|----------------|--------|-------|----------------------|--|--|--|--|

| IDMA Base + 00 | IBASE  | Word  | IDMA BD Base Address |  |  |  |  |

| IDMA Base + 02 | IBPTR  | Word  | IDMA BD Pointer      |  |  |  |  |

| IDMA Base + 04 | ISTATE | Long  | IDMA Internal State  |  |  |  |  |

| IDMA Base + 08 | ITEMP  | Long  | IDMA Temp            |  |  |  |  |

Table 7-3. IDMA Parameter RAM

NOTE: The entry in boldface must be initialized by the user.

The IBASE entry defines the starting location in the dual-port RAM for the set of IDMA BDs. It is an offset from the beginning of the dual-port RAM. The user must initialize this entry before enabling the IDMA channel. Furthermore, the user should not overlap BD tables of two enabled serial channels or IDMA channels, or erratic operation will result. IBASE should contain a value that is divisible by 16. The IBPTR entry points to the next BD that the IDMA will transfer data to when it is in IDLE state or points to the current BD during transfer processing. After a reset or when the end of an IDMA BD table is reached, the CP initializes this pointer to the value programmed in the IBASE entry.

ISTATE and ITEMP are for RISC use only.

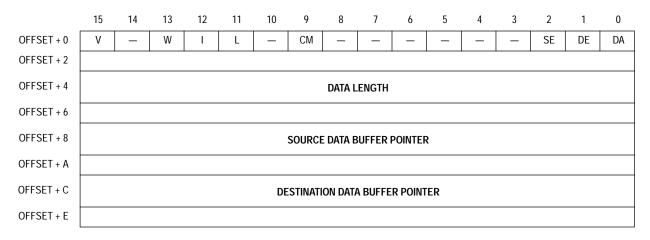

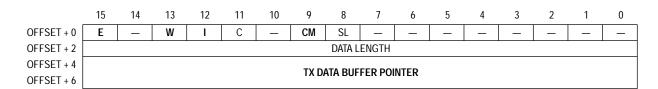

**7.6.4.2.2 IDMA Buffer Descriptors (BDs).** Source addresses, destination addresses, and byte counts are presented to the RISC controller using special IDMA BDs. The RISC controller reads the BDs, programs the IDMA channel, and notifies the CPU32+ about the completion of a buffer transfer using the IDMA BDs. This concept is like that used for the serial channels on the QUICC, except that the BD is larger to contain additional information.

NOTE: Entries in boldface must be initialized by the user.

The following bits are prepared by the user before transfer and are set by the RISC controller after the buffer has been transferred.

#### V—Valid

- 0 = The data buffers associated with this BD are not currently ready for transfer. The user is free to manipulate this BD or its associated data buffer. When it is not in auto buffer mode, the RISC controller clears this bit after the buffer has been transferred (or after an error condition is encountered).

- 1 = The data buffers have been prepared for transfer by the user. (Note that only one data buffer needs to be prepared if the source/destination is a peripheral device.) It may be only the source data buffer when the destination is a device or the destination data buffer when the source is a device. No fields of this BD may be written by the user once this bit is set.

### NOTE

The only difference between auto buffer mode and buffer chaining mode is that the V-bit is not cleared by the RISC controller in the auto buffer mode. Auto buffer mode is enabled by the CM bit. W-Wrap (Final BD in Table)

- 0 = This is not the last BD in the table.

- 1 = This is the last BD in the table. After the associated buffer has been used, the RISC controller will transfer data from the first BD in the table (pointed to by IBASE). The number of BDs in this table is programmable and is determined only by the W-bit and the overall space constraints of the dual-port RAM.

#### I—Interrupt

- 0 = No interrupt is generated after this buffer has been serviced.

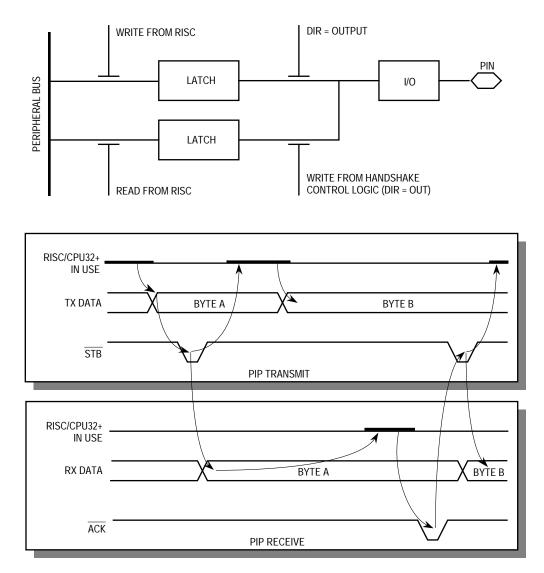

- 1 = When this buffer has been serviced by the RISC controller the AD bit in the CSR will be set, which can cause an interrupt.