# **ProceV** TM

Preliminary Data Book January 2014

GiDEL products and their generated products are not designed, intended, authorized, or warranted to be suitable for use in life-support applications, devices or systems or other critical applications.

© 1993 - 2014 by *GiDEL* Ltd. All rights reserved. *GiDEL*, *ProceV<sup>TM</sup>*, PSDB, *ProcWizard<sup>TM</sup>*, *ProcMultiPort<sup>TM</sup>* and other product names are trademarks of *GiDEL* Ltd., which may be registered in some jurisdictions. This information is believed to be accurate and reliable, but *GiDEL* LTD. assumes no responsibility for any errors that may appear in this document. *GiDEL* reserves the right to make changes in the product specifications without prior notice.

Windows, Stratix V, TMS320C6414, DDRII, CameraLink and other brand and product names are trademarks or registered trademarks of their respective holders.

#### USA

1600 Wyatt Drive Suite 1 Santa Clara CA 95054, USA

Tel: 1 - 408 - 969 - 0389 Fax: 1 - 408 - 465 - 7361

sales usa@GiDEL.com

#### Worldwide

2 Ha'ilan Street, P.O. Box 281 Or Akiva, Israel 30600

Fax: +972 - 4610 - 2501 Tel: +972 - 4610 - 2500 sales\_eu@GiDEL.com

Web: <u>www.GiDEL.com</u> info@GiDEL.com

| Content       | S                                             |                                              | iii |  |  |

|---------------|-----------------------------------------------|----------------------------------------------|-----|--|--|

| Figures.      | •••••                                         |                                              | vi  |  |  |

| Tables        | •••••                                         |                                              | vii |  |  |

| 1.0 Scop      | e                                             |                                              | 1   |  |  |

| 2.0 Intro     | oducti                                        | on                                           | 2   |  |  |

| 3.0 Key       | Featu                                         | res                                          | 4   |  |  |

| 3.1.          | Pro                                           | ceV Performance                              | 5   |  |  |

| 4.0 Stan      | dard ]                                        | Models                                       | 6   |  |  |

| 5.0 Arch      | itectu                                        | ıre                                          | 8   |  |  |

| 5.1.          |                                               | ceV Block Diagram                            |     |  |  |

| 5.2.          |                                               | ceV Signal Buses                             |     |  |  |

| 5             | .2.1.                                         | PSDB Connector (J4) Buses- Single-Ended Mode | 10  |  |  |

| 5             | .2.2.                                         | PSDB Connector (J4) Buses- LVDS mode         |     |  |  |

| 5             | .2.3.                                         | Internal Bus                                 | 12  |  |  |

| 5             | .2.4.                                         | General purpose I/O Bus                      | 12  |  |  |

| 5.3.          | Pro                                           | ceV Clocking System                          | 12  |  |  |

| 5             | .3.1.                                         | ProceV Global Clocks                         | 13  |  |  |

| 5             | .3.2.                                         | ProceV Individual Clocks                     | 13  |  |  |

| 5             | .3.3.                                         | ProceV High-Speed Reference clocks           | 14  |  |  |

| <b>6.0 DM</b> | A Con                                         | troller                                      | 15  |  |  |

| 6.1.          | DM                                            | A Performance                                | 16  |  |  |

| 7.0 Com       | nector                                        | 'S                                           | 17  |  |  |

| 7.1.          | Boa                                           | ard Connectors Overview                      | 17  |  |  |

| 7.2.          | CXI                                           | P Connector (J1)                             | 19  |  |  |

| 7.3.          | SFF                                           | SFP+ Connectors (J18)                        |     |  |  |

| 7.4.          | 7.4. High Speed Inter-Board Connectors (J6,7) |                                              |     |  |  |

| 7.5.          | .5. PSDB Connector (J4)2                      |                                              |     |  |  |

| 7.6.          | External I/O Connector (J3)27                 |                                              |     |  |  |

| 7.7.          | RJ4                                           | 15 Connector (J8)                            | 28  |  |  |

| 7.8.          | Ext                                           | External Power (12V) Connector (J2)29        |     |  |  |

| 8.0 N | <b>Memo</b> i | ies                                                         | <b>30</b> |

|-------|---------------|-------------------------------------------------------------|-----------|

| 8     | 3.1.          | Two-level structure Stratix V embedded memory               | 30        |

| 8     | 3.2.          | On-board Memory Blocks - DDRII <sup>+</sup> SRAM (optional) | 30        |

| 8     | 3.3.          | ECC DDR3 DRAM SODIMM Modules – 72 bit wide                  | 31        |

| 8     | 3.4.          | SODIMM Connectivity                                         | 32        |

| 8     | 3.5.          | SRAM Connectivity                                           | 34        |

| 9.0 1 | LEDs.         |                                                             | 36        |

| 9     | ).1.          | Power LEDs                                                  | 36        |

| 9     | ).2.          | Status LEDs                                                 | 36        |

| 9     | 9.3.          | General Purpose User LEDs                                   | 37        |

| 9     | 9.4.          | SFP+ LEDs                                                   | 37        |

| 10.0  | Techn         | ical Specifications                                         | 38        |

| 1     | 0.1.          | Electrical and Mechanical Environment                       | 38        |

|       | 10.           | 1.1. Humidity                                               | 38        |

|       | 10.           | 1.2. Temperature                                            | 38        |

| 1     | 0.2.          | MTBF                                                        | 38        |

| 1     | 0.3.          | ProceV Mechanical Description                               | 39        |

| 1     | 0.4.          | Power Consumption                                           | 40        |

| 1     | 0.5.          | ProceV Timing Model                                         | 42        |

|       | 10.5          | 5.1. Groups Skew                                            | 42        |

|       | 10.5          | 5.2. Clock Accuracy                                         | 43        |

|       | 10.5          | 5.3. System I/O Frequency                                   | 43        |

| 11.0  | Instal        | lation                                                      | 44        |

| 1     | 1.1.          | Requirements                                                | 44        |

| 1     | 1.2.          | Installing the ProceV board                                 | 44        |

| 1     | 1.3.          | Loading Designs in PCI Express Mode                         | 45        |

| 12.0  | GiDE          | EL Accessories                                              | 46        |

| 1     | 2.1.          | GiDEL Proc Developer's Kit™                                 | 46        |

| 1     | 2.2.          | GiDEL ProcWizard™                                           | 46        |

| 1     | 2.3.          | GiDEL ProcMultiPort™                                        | 47        |

| 1     | 2.4.          | GiDEL ProcMegaDelay™                                        | 48        |

| 1     | 2.5.          | GiDEL ProcMegaFIFO™                                         | 48        |

| 1     | 2.6.          | GIDEL PSDB Daughterboards                                   | 49        |

| 13.0 Appe  | endix. |                                                | 50 |

|------------|--------|------------------------------------------------|----|

| 13.1.      | Thro   | ughput Calculations                            | 50 |

| 13.        | .1.1.  | M20K Throughput Calculations                   | 50 |

| 13.        | .1.2.  | Stratix V MLAB Throughput Calculations         | 50 |

| 13         | .1.3.  | On-board SRAM Memories Throughput Calculations | 50 |

| 13.        | .1.4.  | DDR3 SDRAM SODIMM Throughput Calculations      | 51 |

| 13.        | .1.5.  | Additional Devices Needed                      | 51 |

| 14.0 Refer | rences | s                                              | 52 |

| 14.1.      | Refe   | rences                                         | 52 |

| 15.0 Gloss | sary   |                                                | 53 |

| 16.0 Revis | sion H | listory                                        | 54 |

| 16.1.      | РСВ    | History                                        | 54 |

| 16.2.      | Firm   | ware History                                   | 54 |

| 16.3.      | Proc   | eV Data Book History                           | 54 |

# **Figures**

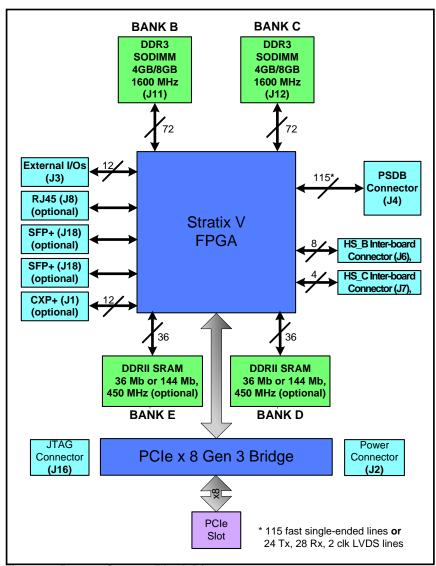

| Figure 1: ProceV System Block Diagram          | 8  |

|------------------------------------------------|----|

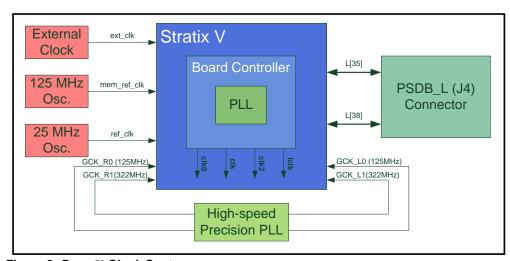

| Figure 2: ProceV Clock System                  |    |

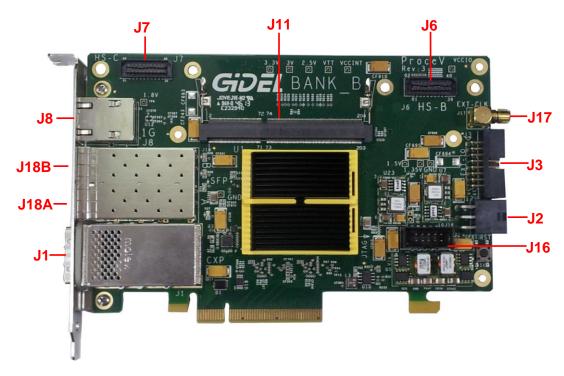

| Figure 3: Components Side (CS) Connectors      |    |

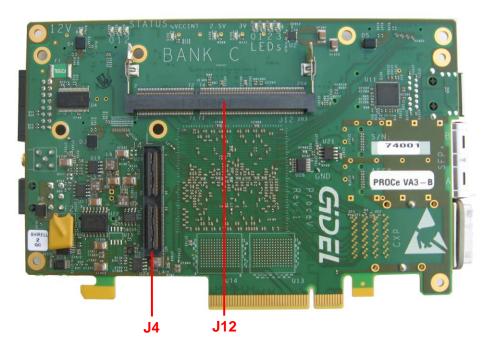

| Figure 4: Print Side (PS) Connectors           | 18 |

| Figure 5: ProceV Mechanical Dimensions (in mm) |    |

| Table 1: ProceV Memory Throughput                     | 5  |

|-------------------------------------------------------|----|

| Table 2: GiDEL ProceV Standard Models                 |    |

| Table 3: DMA Performance Benchmark System             | 16 |

| Table 4: DMA Performance                              | 16 |

| Table 5: Component Side Connector Description         | 17 |

| Table 6: Print Side Connector Description             | 18 |

| Table 7: CXP Top-Level Signals                        | 19 |

| Table 8: SFP+ Top-Level Signals                       | 20 |

| Table 9: HS-B Connector (J6) Pin-out                  |    |

| Table 10: HS-C Connector (J7) Pin-out                 | 22 |

| Table 11: HS Connectors' Top-Level Signals            | 23 |

| Table 12: PSDB_L(J4) connector pin-out                |    |

| Table 13: PSDB_L (J4) pin-out in LVDS Mode            | 26 |

| Table 14: J3-General Purpose IO Connector Assignments | 27 |

| Table 15: IO Working Frequency                        | 27 |

| Table 16: 88E1118R PHY Top-Level Signals              |    |

| Table 17: Power Connector Pin Map (cable side)        | 29 |

| Table 18: Power Connector (J2) Pin-out                | 29 |

| Table 19: SODIMM Top-Level Signals                    |    |

| Table 20: SRAM Top-Level Signals                      | 34 |

| Table 21: Power LEDs                                  | 36 |

| Table 22: Status LEDs                                 | 36 |

| Table 23: ProceV Operating Conditions                 | 38 |

| Table 24: Maximum current Limits                      |    |

| Table 25: ProceV Internal Voltage Sources             | 40 |

| Table 26: Groups Skew                                 | 42 |

| Table 27: Clock Accuracy                              | 43 |

| Table 28: System I/O Frequency                        | 43 |

| Table 29: PSDB Connector Heights.                     | 51 |

| Table 30: Table of Acronyms                           | 53 |

| Table 31: PCB History                                 | 54 |

| Table 32: Firmware History                            | 54 |

| Table 33: Data Book History                           | 54 |

The purpose of this data book is to provide architectural, hardware and installation information for the  $ProceV^{TM}$  system.

This data book is organized in the following chapters:

**Introduction** – Board description and purpose.

**Key Features** – Main features and performance.

**Standard Models** – Standard product models available.

**Architecture** – Board architecture, components, busses and clocks.

**DMA Controller** – DMA operation and performance.

**Connectors** – Board connectors' description and pin-out.

**Memories** – Memory structure.

**LEDs** – LEDs functions.

**Technical Specifications** - Electrical, mechanical and other technical specifications.

**Installation** – Requirements and installation instructions.

**GIDEL Accessories** – GiDEL management software and IPs.

**Appendix** – Additional information.

References – List of referenced documents.

**Glossary –** Term definitions and acronyms.

**Revision History –** Board and document revision history.

# 2.0 Introduction

The *ProceV*™ system provides a high-capacity, high-speed FPGA-based platform along with 16+GB of memory with ~20GB/s sustain access rate. The combination of high-speed direct communication to the FPGA via PCIe gen 3, CXP, SFP+, RJ45 and General Purpose physical layer interface makes the ProceV ideal for HPC(High Performance Computing) and high performance low-latency networking applications.

The **ProceV** architecture, based on Altera's Stratix V FPGA technology, is capable of running at typical system speeds of 150-450 MHz.

The *ProceV* is 8-lane PCI Express hosted offering both high performance and flexible architecture, based on massive memory and diverse add-on daughterboards for large application needs. In addition to two SODIMM sockets, 1.6Gb/s each, providing up to 16 GB of ECC DDR3 memory, the ProceV provides an option for 2x144 Mb or 2x36 Mb on-board DDRII<sup>+</sup> SRAM memory. This vast memory conjoined with PCIe connection permits strong co-processing between a PC with standard OS and the FPGA accelerator.

The *ProceV* system, supported by GiDEL's *ProcDeveloper's Kit*™ management software and soft IPs, offers an incredible improvement in time-to-market.

In addition, the **ProceV** is enhanced by GiDEL's line of **PSDB** daughterboards enabling interfacing with external I/O lines and video applications, including SDI, DVI and Camera Link standards.

ProceV supports new simple SerDes-based fast connections between boards and accessories of up to 169 Gb/s full duplex.

The **ProceV** system is suitable for the following applications:

- √ High-speed low latency networking and network analysis

- ✓ Trading

- ✓ Life science Applications

- ✓ ASIC and SoC Prototyping

- ✓ DSP (Digital Signal Processing) and HPRC (High Performance Reconfigurable Computing)

- ✓ Surveillance, Machine Vision and Imaging

- √ High performance acquisition systems

The **ProceV** all-inclusive system, composed of on-board controllers and automatic code generation application software, eliminates the need to:

- ✓ Write a PCI Express driver.

- ✓ Write an application driver layer.

- ✓ Define board constraints.

- ✓ Design memory controller.

- ✓ Write environment FPGA code.

With the *ProceV* system and supporting development tools designers can focus on their proprietary value-added design instead of spending valuable time recreating standard design components. GiDEL's soft IPs and automatic HDL code generation enable high speed and easy-to-use parallel access to large memories. User designs may be in HDL, C-based, Simulink (graphical design) or any combination of them. For information on other design entry tools, please contact GiDEL.

# 3.0 Key Features

- Support Altera Stratix V GX (A3, A7, AB) and GS (D5, D8) FPGAs.

- Gen-3 8-lane PCI Express host interface and stand alone option.

- Four level memory structure (16+ GB).

- ✓ Up to 2640 M20K (20K-bit) SRAM blocks (50 Mb) 8,000 GB/s typical throughput

- ✓ Up to 17,960 Enhanced MLAB (640-bit) SRAM blocks (8 Mb)

- √ 2 x DDR3 ECC SODIMMs Banks with up to a total of 16 GB at a sustain throughput of 19.2 GB/s

- ✓ Optional 2 x 144Mb or 2 x 36Mb DDRII<sup>+</sup> SRAM memories (up to 450Mhz)

- Typical system frequency of 150 450MHz.

- Up to 32 DMA channels.

- Up to 3,926 of 18x18 bit multipliers implemented in Stratix V devices.

- Optional: 1 CXP connector cage suitable for 100 Gigabit Ethernet (100GBASE-CR10, 100GBASE-SR10), 3x40 Gigabit Ethernet, or single Infiniband 12xQDR link

- Optional: 2 SFP+ cage suitable for 10 Gigabit Ethernet and Optical Transport Network

- Optional: RJ45 port suitable for 1000MBase-T and 100MBase-TX

- 2 High-Speed Inter-Board connectors (up to 12x14.1 Gb/s) for board to board and Proc High-Speed (PHS) daughterboards connectivity

- PHS daughterboards enabling additional protocol and connectivity options such as CoaXPress, QSFP and SAS/SATA.

- 12 general purpose LVTTL External IOs

- Support for a single PSDB type 1 daughter board used for a GiDEL's off-the-shelf or user add-on Interface including logic Analyzer mictors, Camera Link, SDI, DVI and other interfaces.

- Immediate and simple high bandwidth use of the on-board memories with the innovative GIDEL *ProcMultiPort*™ configurable IP (a part of GIDEL Proc Developer's Kit). Each memory can be used for parallel data streaming, and for debug data capture.

- Flexible clocking System.

- Temperature monitoring.

- Supported by GiDEL's Proc Developer's Kit management software.

- Drivers for Windows and Linux 64-bit Operating Systems.

### 3.1. ProceV Performance

The **ProceV** system provides high performance capabilities. Table 1 details the **ProceV's** throughput and memory capacity. Note that the performance is dependent on Proc board model.

Table 1: ProceV Memory Throughput

| Memory<br>Structure            | Capacity                                  | Typical Data Rate<br>Per Single Data Bit | Throughput* |

|--------------------------------|-------------------------------------------|------------------------------------------|-------------|

| Embedded in FPGA               | Up to 2640 x<br>M20K Blocks               | 300 MHz                                  | 8,000 GB/s  |

| Optional<br>On-Board<br>Memory | 2 x 144Mb or<br>2 x 36Mb SRAM<br>(36-bit) | 800 Mb/s                                 | 6.4 GB/s    |

| SODIMM<br>Modules              | 2 x 8GB DDR3                              | 1600 Mb/s                                | 19.2 GB/s   |

<sup>\*</sup> Refer to the Appendix for throughput calculations (paragraph 13.1)

For further information regarding the embedded memory blocks, refer to the *Altera Stratix V Handbook*.

# 4.0 Standard Models

This chapter details the standard models product available.

The model names have the following structure: **Proceaa-bcdeefg**, where:

aa: Type of Stratix V devices:

GX Device: A3, A7, AB

GS Device: D8

b: Speed grade:

A = -1 speed grade, B = -2 speed grade, C = -3 speed grade

c: CXP Option:

X=CXP, Blank= without CXP

d: SFP+ option:

S=with SFP+ A and B, Blank=without SFP+

ee: 1Gbit Ethernet PHY Option:

1G =with PHY, Blank without PHY

**f:** SRAM Option:

$M = 2 \times 36 \text{ Mb } 450 \text{ Mhz DDRII+ SRAMs},$

**Blank**= without SRAM, other combinations are available for a quantity if 10 or more boards

g: External Clock Option:

CK= External clock, Blank= without external clock

The following table is a list of the available *ProceV* models:

Table 2: GiDEL ProceV Standard Models

| Ordering Code**<br>(Basic Models) | Stratix V<br>Device | Speed<br>Grade | DDR III<br>SODIMM<br>Sockets | LEs*  | M20K<br>Blocks | 18×18<br>Multipliers |

|-----------------------------------|---------------------|----------------|------------------------------|-------|----------------|----------------------|

| ProceVA3-C                        | 5S <b>GX</b> A3     | -3             | 2                            | 340 K | 957            | 512                  |

| ProceVA3-CX                       | 5S <b>GX</b> A3     | -3             | 2                            | 340 K | 957            | 512                  |

| ProceVA3-CS                       | 5S <b>GX</b> A3     | -3             | 2                            | 340 K | 957            | 512                  |

| ProceVA3-CXS                      | 5S <b>GX</b> A3     | -3             | 2                            | 340 K | 957            | 512                  |

| ProceVA3-B                        | 5S <b>GX</b> A3     | -2             | 2                            | 340 K | 957            | 512                  |

| ProceVA3-BX                       | 5S <b>GX</b> A3     | -2             | 2                            | 340 K | 957            | 512                  |

| ProceVA3-BS                       | 5S <b>GX</b> A3     | -2             | 2                            | 340 K | 957            | 512                  |

| ProceVA3-BXS                      | 5S <b>GX</b> A3     | -2             | 2                            | 340 K | 957            | 512                  |

(Table 2 – continued from previous page)

| Ordering Code**<br>(Basic Models) | Stratix V<br>Device | Speed<br>Grade | DDR III<br>SODIMM<br>Sockets | LEs*  | M20K<br>Blocks | 18×18<br>Multipliers |

|-----------------------------------|---------------------|----------------|------------------------------|-------|----------------|----------------------|

| ProceVA7-BXS                      | 5S <b>GX</b> A7     | -2             | 2                            | 622 K | 2,560          | 512                  |

| ProceVAB-BXSM                     | 5S <b>GX</b> AB     | -2             | 2                            | 952K  | 2,640          | 704                  |

| ProceVD8-BXSM                     | 5S <b>GS</b> D8     | -2             | 2                            | 695 K | 2,567          | 3,926                |

<sup>\*</sup> LE=Logic Element. For further information on the Stratix V LEs, refer to **Stratix V Device Handbook** (Altera Corporation).

**NOTE**: Default transceivers are K2=12.5 Gb/s; for transceivers K1=14.1 Gb/s, please contact GiDEL.

<sup>\*\*</sup>For other ProceV models, contact GiDEL.

# 5.0 Architecture

This chapter details the *ProceV* architecture and components.

# 5.1. ProceV Block Diagram

The **ProceV** system Block Diagram is shown in Figure 1.

Figure 1: ProceV System Block Diagram

The **ProceV** system includes the following components:

- One ALTERA Stratix V GX or GS FPGA in 1517 package.

- 8 lane PCI Express Gen 3 interface.

- Optional: 2 x 144 Mb or 2x36 Mb DDRII<sup>+</sup> SRAM@450MHz on-board memories (optional).

- 2 x 8 GB DDR3 SODIMM sockets.

- Optional: 1 CXP connector cage suitable for 100 Gigabit Ethernet (100GBASE-CR10, 100GBASE-SR10), 3x40 Gigabit Ethernet, or single Infiniband 12xQDR link (up to 12x14.1 Gb/s - supports splitter cable 1 to 12).

- Optional: 2 x SFP+ cage suitable for Fiber Channel, Gigabit Ethernet and Optical Transport Network (up to 14.1 Gb/s/SFP+)

- Optional: RJ45 port suitable for 1000MBase-T and 100MBase-TX

- 2x High-Speed connectors (up to 12x14.1 Gb/s) for inter-board and proprietary daughterboards connectivity

- 12 general purpose LVTTL External IOs

- External clock input via an SMA connector

- 1 PSDB Type 1 (Proc Daughterboard) connector with 115 I/Os or 24 LVDS TX, 28 LVDS RX and 2 LVDS clock inputs channels

- JTAG connection for the STRATIX V FPGA.

- Stand-alone capability

### 5.2. ProceV Signal Buses

The **ProceV** connectivity is automatically generated by the **ProcWizard™** software (included in **Proc Developer's Kit**). The **ProcWizard** generates the top-level design and entity/module interconnectivity in Verilog, VHDL or AHDL format, including all the **ProceV** buses as is described in the following sections. The buses are assigned names accordingly. However, the generated names may change if a PSDB daughterboard is added to the **ProceV** board. In such a case, buses that are connected to that PSDB will be named according to the corresponding buses on the PSDB.

The single-ended buses on *ProceV* boards are designed to provide maximum connectivity flexibility. However, user must take care to **avoid bus contention.** Always use one source at a time for a single signal.

To improve EMC characteristics, it is recommended to drive all unused connectivity pins to 0 (from one source).

The PSDB connector (J4) can operate in two unique modes: single-ended mode and differential (LVDS) mode. The following sections detailed the connectivity buses of each of the noted modes.

### 5.2.1. PSDB Connector (J4) Buses- Single-Ended Mode

The PSDB connector (J4) in single-ended mode includes the L[84:0], L\_IN[7:0], L\_IO[19:0] and clk\_out[1:0] buses as follows:

#### PSDB IN buses (I\_in)

**I\_in**, for backward compatibility, is used as dedicated 8-bit input (from PSDB to the STRATIX *V* FPGA). If needed L\_IN signals may also operate as outputs.

**Note:** The L\_IN bus connects the FPGA to the PSDB connector **J4** as shown in Figure 1.

#### PSDB I/O buses (I io)

**I\_io** is a 20-bit bidirectional I/O bus connecting the STRATIX *V* FPGA device to its PSDB.

#### PSDB I/O buses (I)

I is an 85 bit bidirectional I/O bus connecting the STRATIX  $\it{V}$  FPGA device to its PSDB.

The **I[35]** and **I[38]** lines are connected to optional global clock input pins of the Stratix *V* device. They may be used as bus clock signals or clock inputs.

For information on **J4** pin-out, refer to section 7.2.

#### 5.2.2. PSDB Connector (J4) Buses- LVDS mode

The PSDB connector (J4) in LVDS mode includes 24 differential transmit lines (tx[23:0]), 28 differential receive lines (rx[27:0]), and 2 differential receive reference clocks (clk\_rx[1:0]) as detailed in section 7.2.

#### 5.2.3. Internal Bus

**GiDEL ProcWizard** generates an Avalon bus and a simple logic bus that delivers direct access to internal memory-mapped I/Os and a simple interface to the internal memories. The simple bus generated by the **ProcWizard** is called the **Internal bus**.

For further information, please refer to the *Proc Internal Bus Data Book.*

#### 5.2.4. General purpose I/O Bus

The *ProceV* provides 12 bidirectional buffered LVTTL general purpose IO lines via the J3 connector. The J3 connectivity is divided into two IO data groups: IO[7..0] and IO[11..8]. The j3\_ext\_io\_dir0 and j3\_ext\_io\_dir1 signals define the data transmission direction for IO[7..0] and IO[11..8], respectively; direction is relative to the STRATIX *V* FPGA. When j3\_ext\_io\_dir[1:0] is driven high, the data is outputted from the FPGA, and when the pin is driven low, the data is inputted to the FPGA. On power-up, all 12 I/O lines are automatically configured as inputs. Some of the I/Os are connected to pull-up and pull-down resistors ensuring a stable default high or low at power up.

These signals may be connected via optocoupler, differential buffer, or other type of buffers on a dedicated interface board.

# 5.3. ProceV Clocking System

**GiDEL ProceV** boards have a flexible clocking system.

The clocks in **ProceV** boards are routed as shown in the following diagram:

Figure 2: ProceV Clock System

#### 5.3.1. ProceV Global Clocks

**ref\_clk** is a 25Mhz oscillator input that is used to generate internal clocks.

The **clk0**, **clk** and **clk2** frequencies can be set via the *ProcWizard* development software.

#### clk0

The **clk0** is used for backward design compatibility. It is the main system clock that drives the Stratix *V* FPGA. Within the FPGA device, individual clocks for internal logic can be derived from this clock.

#### clk

clk is used as main logic clock and it is equal to clk0 x 2 or clk0 x 3.

#### **Iclk**

**Iclk** is the **Local bus** clock that drives the Stratix V FPGA local bus related logic. **Iclk** frequency is up to 250 MHz.

#### clk2

**clk2** is an auxiliary clock that may be used as a slow emulation clock. Clk2's frequency is derived from clk0 divided by an even number.

#### **Memory reference clocks**

mem\_ref\_clk is a 125 Mhz clock used as SODIMM Bank B and Bank C reference clocks.

The **mem\_ref\_clk** is fixed at 125 Mhz for all GiDEL boards enabling code migration and a fixed frequency source.

#### 5.3.2. ProceV Individual Clocks

#### **External clock inputs**

ext\_clk is an external clock received from the SMA connector (J17).

In single-ended mode, J4 PSDB\_L has two external dedicated clock inputs **I[35]** and **I[38]** mode and in LVDS mode two differential receive locks **clk rx [1:0]**.

**J4** PSDB\_L is a PSDB type 1 connector with 2 backward compatible output clocks clk\_out[1:0]. On the ProceV clk\_out[1:0] may also be used as regular I/Os.

### 5.3.3. ProceV High-Speed Reference clocks

The high-speed reference clocks are generated from an external high-precision PLL and are in particularly intended for driving the Stratix V transceivers. There are four high-speed reference clocks, two connected to the left side and two to the right side of the Stratix V device as follows:

| Reference Clock | Frequency   | Description                          |

|-----------------|-------------|--------------------------------------|

| Gck_R0          | 125 MHz     | Connecting to the devices right side |

| Gck_R1          | 322.265 MHz | Connecting to the devices right side |

| Gck_L0          | 125 MHz     | Connecting to the devices left side  |

| Gck_L1          | 322.265 MHz | Connecting to the devices left side  |

# 6.0 DMA Controller

**The ProceV** board has 32 DMA channels. The DMA channels enable the board to have master control over the PCIe, while keeping simple internal logic and random access as slave only. The DMA is controlled by a driver and enables easy and effective usage of memory and system resources.

User's hardware design may control the data flow on DMA channels. For this purpose the customer should use the **user\_dreq** bus. Each bit within the bus corresponds to a specific DMA channel; for example, **user\_dreq[3]** corresponds to DMA channel 3.

After the software has initialized a DMA channel, the DMA controller starts transferring data. Data continues to be transferred as long as the **user\_dreq** signal remains low for that channel. When the **user\_dreq** signal rises, the DMA controller holds the transfer. This may take up to 10 local clocks. Data transfer resumes upon asserting **user\_dreq** signal low.

- It is not mandatory to control user\_dreq signals. If user\_dreq signals are not connected, once the DMA channel has been initialized by the software, it will operate continuously until all data has been transferred.

- 2. The DMA controller may stop and resume the DMA transfer based on the PCIe bus, internal bus and system activities.

### 6.1. DMA Performance

The DMA performance depends on:

- √ Block size

- ✓ Active PCI Express payload

- ✓ Host mother board and chipset

Table 3 and Table 4 detail the Benchmark system and the DMA performance, respectively.

Table 3: DMA Performance Benchmark System

| Components                  | Specifications |

|-----------------------------|----------------|

| Processor                   | TBD            |

| Motherboard                 | TBD            |

| Chipset                     | TBD            |

| Active PCI Express lanes    | TBD            |

| PCI Express payload (Bytes) | TBD            |

| DMA block size (Mega Bytes) | TBD            |

Table 4: DMA Performance

| Test              | Results |

|-------------------|---------|

| Board to PC speed | TBD     |

| PC to board speed | TBD     |

# 7.0 Connectors

The following chapter details the *ProceV* connectors' functionality and pin-out.

# 7.1. Board Connectors Overview

Figure 3: Components Side (CS) Connectors

| Connector    | Function                                    |  |  |  |

|--------------|---------------------------------------------|--|--|--|

| J1           | CXP (optional)                              |  |  |  |

| J2           | 12V external source                         |  |  |  |

| J3           | External I/O                                |  |  |  |

| J6           | High-speed inter-board connector B          |  |  |  |

| J7           | High-speed inter-board connector C          |  |  |  |

| J8           | RJ45 1000MBase-T and 100MBase-TX (optional) |  |  |  |

| J11          | DDR3 SODIMM (Bank B)                        |  |  |  |

| J16          | JTAG                                        |  |  |  |

| J17          | SMA for external clock (optional)           |  |  |  |

| J18(A and B) | 2 x SFP+ (optional)                         |  |  |  |

Table 5: Component Side Connector Description

Figure 4: Print Side (PS) Connectors

Table 6: Print Side Connector Description

| Connector | Function                           |

|-----------|------------------------------------|

| J12       | DDR3 SODIMM (Bank C)               |

| J4        | Daughterboard (PSDB)               |

|           | To connect via the PC's panel, you |

|           | must use PSDB_6C cable kit.        |

# 7.2. CXP Connector (J1)

The ProceV board has a single CXP connector cage enabling up to 12 full duplex transceivers at 600 Mb/s -12.5/14.1 Gb/s suitable for 100 Gigabit Ethernet (100GBASE-CR10, 100GBASE-SR10), 3×40 Gigabit Ethernet, 12×10Gigabit Ethernet or a single 120Gb/s Infiniband 12×QDR link.

The CXP connector interfaces with the FPGA via the following top-level signals:

| FPGA<br>Top-Level<br>Signal | Equivalent CXP<br>Protocol Name | FPGA I/O<br>Direction    | Description                                                                                   |

|-----------------------------|---------------------------------|--------------------------|-----------------------------------------------------------------------------------------------|

| cxp_rx[11:0]                | Rx[11:0]p/n                     | Differential<br>Input    | FPGA SerDes data inputs                                                                       |

| cxp_tx[11:0]                | Tx[11:0]p/n                     | Differential<br>Output   | FPGA SerDes data outputs – this signals are coupled with their differential pair cxp_txn[011] |

| cxp_prsnt_l                 | PRSNT_L                         | Input                    | 1: CXP module is absent                                                                       |

| Схр_ргэпі_г                 | FRONI_L                         | input                    | 0: CXP module is plugged.                                                                     |

| cxp_int_reset               | INT L/RESET L                   | Open Collector           | Open collector bi-directional signal.  Reset signal when driven "0" by the host.              |

| -                           |                                 | I/O                      | Interrupt signal when driven "0" by the module.                                               |

| cxp_sda                     | SDA                             | Open Collector I/O       | I <sup>2</sup> C data                                                                         |

| cxp_scl                     | SCL                             | Open Collector<br>Output | I <sup>2</sup> C clock                                                                        |

Table 7: CXP Top-Level Signals

# 7.3. SFP+ Connectors (J18)

The ProceV has dual SFP+ cage suitable also for  $2 \times 10$  Gigabit Ethernet cupper and Optical Transport Network.

| Connector A<br>Top-Level<br>Signals | Connector B<br>Top-Level<br>Signals | Equivalent<br>SFP+<br>Protocol<br>Name | FPGA I/O<br>Direction    | Description                                 |

|-------------------------------------|-------------------------------------|----------------------------------------|--------------------------|---------------------------------------------|

| sfp_tx_fault_a                      | sfp_tx_fault_b                      | TX_FAULT                               | Input                    | Module Transmitter Fault.                   |

| sfp_tx_disable_a                    | sfp_tx_disable_b                    | TX_DISABLE                             | Output                   | Transmitter Disable                         |

| sfp_sda_a                           | sfp_sda_b                           | SDA                                    | Open<br>collector<br>I/O | I <sup>2</sup> C Data                       |

| sfp_scl_a                           | sfp_scl_b                           | SCL                                    | Open<br>collector<br>I/O | I <sup>2</sup> C Clock                      |

| sfp_mod_abs_a                       | sfp_mod_abs_b                       | MOD_ABS                                | Input                    | 1: Module Absent,<br>0: Module<br>assembled |

| sfp_rs[1]:0_a                       | sfp_rs[1]:0_b                       | RS[1]:0                                | Output                   | Rate Select                                 |

| sfp_rx_los_a                        | sfp_rx_los_b                        | RX_LOS                                 | Open Drain<br>Input      | Receiver Loss of<br>Signal Indication       |

| sfp_rd_a                            | sfp_rd_b                            | RD- /RD+                               | Differential<br>Input    | Receiver Data Input.                        |

| sfp_td_a                            | sfp_td_b                            | TD- /TD+                               | Differential<br>Output   | Transceiver Data Output.                    |

| sfp_link_ledn_a                     | sfp_link_ledn_b                     | -                                      | Output                   | LED; 0: Illuminate                          |

| sfp_trafic_ledn_a                   | sfp_trafic_ledn_b                   | -                                      | Output                   | LED; 0: Illuminate                          |

Table 8: SFP+ Top-Level Signals

### 7.4. High Speed Inter-Board Connectors (J6,7)

The ProceV has two HS (High-Speed) inter-board connectors for board to board and daughterboards connectivity. These connectors are designated HS-B and HS-C, respectively. The HS connectors have Rx and Tx differential pairs that are connected to a Stratix V 600 Mb/s - 12.5/14.1 Gb/s transceivers. The Rx pair are designated <code>hs\_rxp[X]</code> and <code>hs\_rxn[X]</code>, and the Tx pair are designated <code>hs\_txp[X]</code> and <code>hs\_rxn[X]</code>. The Rx and Tx pairs together provide a full duplex lane with a throughput of up to 14.1 Gb/s. Connector HS-B has up to 8 full duplex lanes and connector HS-C has up to 4 full duplex lanes. Each of the transmit lines is connected to a 100 nF serial capacitor.

The following tables list the HS connectors' pin-out:

Table 9: HS-B Connector (J6) Pin-out

| Pin | External Signal Description | Pin | External Signal Description |

|-----|-----------------------------|-----|-----------------------------|

| 1   | hs_rxp0                     | 2   | hs_txp0                     |

| 3   | hs_rxn0                     | 4   | hs_txn0                     |

| 5   | hs_rxp1                     | 6   | hs_txp1                     |

| 7   | hs_rxn1                     | 8   | hs_txn1                     |

| 9   | hs_rxp2                     | 10  | hs_txp2                     |

| 11  | hs_rxn2                     | 12  | hs_txn2                     |

| 13  | hs_rxp3                     | 14  | hs_txp3                     |

| 15  | hs_rxn3                     | 16  | hs_txn3                     |

| 17  | hs_rxp4                     | 18  | hs_txp4                     |

| 19  | hs_rxn4                     | 20  | hs_txn4                     |

| 21  | hs_rxp5                     | 22  | hs_txp5                     |

| 23  | hs_rxn5                     | 24  | hs_txn5                     |

| 25  | hs_rxp6                     | 26  | hs_txp6                     |

| 27  | hs_rxn6                     | 28  | hs_txn6                     |

| 29  | hs_rxp7                     | 30  | hs_txp7                     |

| 31  | hs_rxn7                     | 32  | hs_txn7                     |

| 33  | 12v                         | 34  | 12v                         |

| 35  | hs_sdi                      | 36  | hs_sdo                      |

| 37  | hs_present                  | 38  | GND                         |

| 39  | hs_sci                      | 40  | hs_sco                      |

Table 10: HS-C Connector (J7) Pin-out

| Pin | External Signal Description | Pin | External Signal Description |

|-----|-----------------------------|-----|-----------------------------|

| 1   | hs_rxp0                     | 2   | hs_txp0                     |

| 3   | hs_rxn0                     | 4   | hs_txn0                     |

| 5   | hs_rxp1                     | 6   | hs_txp1                     |

| 7   | hs_rxn1                     | 8   | hs_txn1                     |

| 9   | hs_rxp2                     | 10  | hs_txp2                     |

| 11  | hs_rxn2                     | 12  | hs_txn2                     |

| 13  | hs_rxp3                     | 14  | hs_txp3                     |

| 15  | hs_rxn3                     | 16  | hs_txn3                     |

| 17  | hs_refckp                   | 18  | GND                         |

| 19  | hs_refckn                   | 20  | GND                         |

| 21  | Reserved                    | 22  | Reserved                    |

| 23  | Reserved                    | 24  | Reserved                    |

| 25  | Reserved                    | 26  | Reserved                    |

| 27  | Reserved                    | 28  | Reserved                    |

| 29  | Reserved                    | 30  | Reserved                    |

| 31  | Reserved                    | 32  | Reserved                    |

| 33  | 12v                         | 34  | 12v                         |

| 35  | hs_sdi                      | 36  | hs_sdo                      |

| 37  | hs_present                  | 38  | GND                         |

| 39  | hs_sci                      | 40  | hs_sco                      |

To interconnect between two HS connectors you must use the following **SAMTEC** cable or an equivalent cable: HQDP-020-[**XX.XX**]-TBR-TTL-2-B, where **XX.XX** specifies the length in inches.

This cable crosses left-side pins with right-side pins (e.g., pin1 with pin2).

**Note:** The 12V supplies up to 0.5A per connector.

Table 11: HS Connectors' Top-Level Signals

| HS-B Signals<br>(J6)        | HS-C Signals<br>(J7) | HS<br>Connector<br>Name | FPGA I/O<br>Direction | Description                                                                |

|-----------------------------|----------------------|-------------------------|-----------------------|----------------------------------------------------------------------------|

| hs_rx_b [7:0]               | hs_rx_c [3:0]        | hs_rxp/n                | Input                 | 8 / 4 Differential receivers*                                              |

| hs_tx_b [7:0] hs_tx_c [3:0] |                      | hs_txp/n                | Output                | 8 / 4 Differential transmitters*                                           |

|                             | hs_refck_c           | hs_refck/n              | Input                 | Differential reference clock                                               |

| hs_prsnt_b hs_prsnt_c       |                      | hs_present              | Input                 | 1: the connector is not used  0: Other board / daughterboard is connected. |

| hs_                         | sco                  | hs_sci                  | Output                | This is a 2-wire single-ended daisy                                        |

| hs_                         | sdo                  | hs_sdi                  | Output                | chain connecting:                                                          |

| hs_                         | _sci                 | hs_sco                  | Input                 | FPGA $\rightarrow$ HS_B $\rightarrow$<br>HS C $\rightarrow$ FPGA**         |

| hs_                         | _sdi                 | hs_sdo                  | Input                 | _                                                                          |

<sup>\*</sup> All receive and transmit lines are directly connected to the Stratix V transceiver with a throughput rate of 600 Mb/s - 12.5/14.1 Gb/s.

<sup>\*\*</sup> If one of the HS\_B/C is not connected, the connection will be by-passed on the board. The daisy chain protocol may be user-defined or TBD.

### 7.5. PSDB Connector (J4)

**The ProceV** board supports a single PSDB (type 1) daughterboards. The PSDBs enable I/O connectivity to the FPGA in such standards as Camera Link, SDI, HDMI, etc. All the PSDBs are automatically identified by the **ProcWizard**.

For further information on PSDB type 1, refer to PSDB1 Reference Guide.

The PSDB connector, **J4**, is located on the Print side of the ProceV board as shown in Figure 4. **J4** is 120-pin multi-purpose connector that can also be used in LVDS mode.

Table 12 and Table 13 provide pin-out information for the **J4** PSDB connector. The PSDB connector is a multi-purpose connectors that can function in single-ended or LVDS mode as detailed in Table 12 and Table 13, respectively.

All the signals marked as **Reserved**, are reserved for GiDEL use. These pins must be left unconnected on the user's PSDB.

When a GiDEL PSDB is connected to the ProceV, the generated FPGA top-level bus names that appear in the tables below **will be changed** to match the relevant PSDB functionality.

Table 12: PSDB\_L(J4) connector pin-out

| Pin | PSDB<br>Signal | Pin | PSDB<br>Signal | Pin | PSDB<br>Signal | Pin | PSDB<br>Signal |

|-----|----------------|-----|----------------|-----|----------------|-----|----------------|

| 1   | L0             | 34  | L_IO5          | 67  | GND**          | 100 | L60            |

| 2   | CLK_OUT1       | 35  | L24            | 68  | L_IN5          | 101 | L61            |

| 3   | L1             | 36  | L74            | 69  | L38            | 102 | L_IO17         |

| 4   | DB0            | 37  | L25            | 70  | L_IN4          | 103 | L62            |

| 5   | L2             | 38  | L_IO6          | 71  | Reserved*      | 104 | L63            |

| 6   | L_IN1          | 39  | L26            | 72  | L39            | 105 | L64            |

| 7   | L4             | 40  | L75            | 73  | L40            | 106 | L_IO18         |

| 8   | L3             | 41  | L27            | 74  | L_IO10         | 107 | L65            |

| 9   | L5             | 42  | L_I07          | 75  | L41            | 108 | L66            |

| 10  | L_IN0          | 43  | L28            | 76  | L42            | 109 | L67            |

| 11  | L7             | 44  | L76            | 77  | L43            | 110 | L_IO19         |

| 12  | L6             | 45  | L29            | 78  | L_IO11         | 111 | L68            |

| 13  | L8             | 46  | L_IO8          | 79  | L44            | 112 | L69            |

| 14  | L_IO0          | 47  | L30            | 80  | L45            | 113 | L70            |

| 15  | L10            | 48  | L77            | 81  | L46            | 114 | L_IN6          |

| 16  | L9             | 49  | L31            | 82  | L_IO12         | 115 | L71            |

| 17  | L11            | 50  | L78            | 83  | L47            | 116 | L_IN7          |

| 18  | L_IO1          | 51  | L32            | 84  | L48            | 117 | L72            |

| 19  | L13            | 52  | L79            | 85  | L49            | 118 | 12V (0.3A)     |

| 20  | L12            | 53  | L33            | 86  | L_IO13         | 119 | L73            |

| 21  | L14            | 54  | L80            | 87  | L50            | 120 | CLK_OUT0       |

| 22  | L_IO2          | 55  | L34            | 88  | L51            | 121 | GND***         |

| 23  | L16            | 56  | L_IN2          | 89  | L52            | 122 | GND***         |

| 24  | L15            | 57  | L82            | 90  | L_IO14         | 123 | GND***         |

| 25  | L17            | 58  | L81            | 91  | L53            | 124 | GND***         |

| 26  | L_IO3          | 59  | L83            | 92  | L54            | 125 | VCC***         |

| 27  | L19            | 60  | L_IN3          | 93  | L55            | 126 | VCC***         |

| 28  | L18            | 61  | L35            | 94  | L_IO15         | 127 | VCC***         |

| 29  | L20            | 62  | L84            | 95  | L56            | 128 | VCC***         |

| 30  | L_IO4          | 63  | DB1            | 96  | L57            |     |                |

| 31  | L22            | 64  | L_IO9          | 97  | L58            |     |                |

| 32  | L21            | 65  | L36            | 98  | L_IO16         |     |                |

| 33  | L23            | 66  | L37            | 99  | L59            |     |                |

<sup>\*</sup> Reserved for GiDEL use; must be disconnected on the user's PSDB.

<sup>\*\*</sup> GND pins must be connected to GND.

<sup>\*\*\*</sup> These are virtual signals. The PSDB connectors have two power strips in the middle. Signals [121..124] are connected to the top middle strip and signals [125..128] are connected to the bottom one. The top strip must be connected to GND and the bottom strip to the PSDB 3.3V source.

Table 13: PSDB\_L (J4) pin-out in LVDS Mode

| Pin | PSDB   | Pin | PSDB      | Pin | PSDB      | Pin | PSDB       |

|-----|--------|-----|-----------|-----|-----------|-----|------------|

|     | Signal |     | Signal    |     | Signal    |     | Signal     |

| 1   | RXp0   | 34  | TXn7      | 67  | GND**     | 100 | TXp19      |

| 2   | TXp0   | 35  | RXn8      | 68  | NC****    | 101 | RXn23      |

| 3   | RXn0   | 36  | TXp8      | 69  | CLK_RXp1  | 102 | TXn19      |

| 4   | DB0    | 37  | RXp9      | 70  | NC****    | 103 | RXp24      |

| 5   | RXp1   | 38  | TXn8      | 71  | Reserved* | 104 | TXp20      |

| 6   | TXn0   | 39  | RXn9      | 72  | TXp11     | 105 | RXn24      |

| 7   | RXn1   | 40  | TXp9      | 73  | CLK_RXn1  | 106 | TXn20      |

| 8   | TXp1   | 41  | RXp10     | 74  | TXn11     | 107 | RXp25      |

| 9   | RXp2   | 42  | TXn9      | 75  | RXp17     | 108 | TXp21      |

| 10  | TXn1   | 43  | RXn10     | 76  | TXp13     | 109 | RXn25      |

| 11  | RXn2   | 44  | TXp10     | 77  | RXn17     | 110 | TXn21      |

| 12  | TXp2   | 45  | RXp11     | 78  | TXn13     | 111 | RXp26      |

| 13  | RXp3   | 46  | TXn10     | 79  | RXp18     | 112 | TXp22      |

| 14  | TXn2   | 47  | RXn11     | 80  | TXp14     | 113 | RXn26      |

| 15  | RXn3   | 48  | RXp13     | 81  | RXn18     | 114 | TXn22      |

| 16  | TXp3   | 49  | RXp12     | 82  | TXn14     | 115 | RXp27      |

| 17  | RXp4   | 50  | RXn13     | 83  | RXp19     | 116 | TXp23      |

| 18  | TXn3   | 51  | RXn12     | 84  | TXp15     | 117 | RXn27      |

| 19  | RXn4   | 52  | RXp14     | 85  | RXn19     | 118 | 12V (0.3A) |

| 20  | TXp4   | 53  | RXp15     | 86  | TXn15     | 119 | NC         |

| 21  | RXp5   | 54  | RXn14     | 87  | RXp20     | 120 | TXn23      |

| 22  | TXn4   | 55  | RXn15     | 88  | TXp16     | 121 | GND***     |

| 23  | RXn5   | 56  | NC****    | 89  | RXn20     | 122 | GND***     |

| 24  | TXp5   | 57  | RXp16     | 90  | TXn16     | 123 | GND***     |

| 25  | RXp6   | 58  | NC****    | 91  | RXp21     | 124 | GND***     |

| 26  | TXn5   | 59  | RXn16     | 92  | TXp17     | 125 | VCC***     |

| 27  | RXn6   | 60  | NC****    | 93  | RXn21     | 126 | VCC***     |

| 28  | TXp6   | 61  | CLK_ RXp0 | 94  | TXn17     | 127 | VCC***     |

| 29  | RXp7   | 62  | NC****    | 95  | RXp22     | 128 | VCC***     |

| 30  | TXn6   | 63  | DB1       | 96  | TXp18     |     |            |

| 31  | RXn7   | 64  | TXp12     | 97  | RXn22     |     |            |

| 32  | TXp7   | 65  | CLK_RXn0  | 98  | TXn18     |     |            |

| 33  | RXp8   | 66  | TXn12     | 99  | RXp23     |     |            |

<sup>\*</sup> Reserved for GiDEL use; must be disconnected on the user's PSDB.

<sup>\*\*</sup> GND pins must be connected to GND.

<sup>\*\*\*</sup> These are virtual signals. The PSDB connectors have two power strips in the middle. Signals [121..124] are connected to the top middle strip and signals [125..128] are connected to the bottom one. The top strip must be connected to GND and the bottom strip to the PSDB 3.3V source.

<sup>\*\*\*\*</sup>Should not be connected in LVDS mode.

# 7.6. External I/O Connector (J3)

The **ProceV** provides 12 bidirectional buffered LVTTL general purpose IO lines via the **J3** connector. The **J3** connectivity is divided into two IO data groups: **IO[7..0]** and **IO[11..8]**. The **ext\_io\_dir0** and **ext\_io\_dir1** signals define the data transmission direction, relative to the STRATIX V FPGA. When the **ext\_io\_dir** pin is driven high, the data is outputted from the FPGA, and when the pin is driven low, the data is inputted to the FPGA. On power-up, all 12 I/O lines are automatically configured as inputs.

The following table describes the **J3** I/O connector pin-out:

| Pin | Signal | Top-Level<br>Signal Name | Default I/O<br>Resistance* | Description    |

|-----|--------|--------------------------|----------------------------|----------------|

| 1   | VCC    | N/A                      | N/A                        | 3.3 volt power |

| 2   | IO0    | j3_ext_io[0]             | 10KΩ pull-up               | I/O Bus        |

| 3   | VCC    | N/A                      | N/A                        | 3.3 volt power |

| 4   | IO1    | j3_ext_io[1]             | 10KΩ pull-up               | I/O Bus        |

| 5   | GND    | N/A                      | N/A                        | GND            |

| 6   | IO2    | j3_ext_io[2]             | N/A                        | I/O Bus        |

| 7   | GND    | N/A                      | N/A                        | GND            |

| 8   | IO3    | j3_ext_io[3]             | N/A                        | I/O Bus        |

| 9   | IO4    | j3_ext_io[4]             | N/A                        | I/O Bus        |

| 10  | IO5    | j3_ext_io[5]             | N/A                        | I/O Bus        |

| 11  | IO6    | j3_ext_io[6]             | 10KΩ pull-down             | I/O Bus        |

| 12  | IO7    | j3_ext_io[7]             | 10KΩ pull-down             | I/O Bus        |

| 13  | IO8    | j3_ext_io[8]             | 10KΩ pull-up               | I/O Bus        |

| 14  | IO9    | j3_ext_io[9]             | 10KΩ pull-up               | I/O Bus        |

| 15  | IO10   | j3_ext_io[10]            | 10KΩ pull-down             | I/O Bus        |

| 16  | IO11   | j3_ext_io[11]            | 10KΩ pull-down             | I/O Bus        |

Table 14: J3-General Purpose IO Connector Assignments

The **J3** connector maximum IO working frequencies are as follows:

Table 15: IO Working Frequency

| Cable Length | Maximum Frequency |

|--------------|-------------------|

| 0.5 meter    | 40 Mb/s           |

| 6.0 meters   | 5 Mb/s            |

<sup>\*</sup>Default input resistance at power up and when the rbf is not loaded.

# 7.7. RJ45 Connector (J8)

The ProceV has a single RJ45 port suitable for 1000MBase-T and 100MBase-TX.

The RJ45 is connected to the FPGA via Marvel's 88E1118R Alaska Gigabit Ethernet Transceiver.

| Top-Level<br>Signals | FPGA I/O<br>Direction | Description**                                                                                                         |

|----------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------|

| phy_resetn           | Output                | Hardware Reset: 0=Reset, 1=Normal                                                                                     |

| phy_mdio             | Open<br>collector I/O | Management Data with an on board pull-up Resistor                                                                     |

| phy_md               | Output                | Management Clock data Reference for the serial Management Interface                                                   |

| phy_rx_clk           | Input                 | RGMII Receive Clock provides a 125Mhz,<br>25 Mhz or 2.5 Mhz reference clock<br>derived from the received data stream. |

| phy_rx_ctrl          | Input                 | RGMII Receive Control                                                                                                 |

| phy_rxd[3:0]         | Output                | RGMII Receive Data                                                                                                    |

| phy_tx_ctrl          | Output                | RGMII Transmit Control                                                                                                |

| phy_tx_clk           | Output                | RGMII Transmit Clock provides a 125Mhz,<br>25 Mhz or 2.5 Mhz reference clock.                                         |

| phy_txd[3:0]         | Output                | RGMII Transmit Data                                                                                                   |

Table 16: 88E1118R PHY Top-Level Signals

# 7.8. External Power (12V) Connector (J2)

The External Power connector (J2) is 75W in accordance to the PCI Express REV. 3.0 ver. 0.9 2 x 3 Auxiliary Power Specification.

The J2 connector is specifically used for connecting the ProceV to a 25W slot or when operating in stand-alone mode.

Table 17: Power Connector Pin Map (cable side)

Table 18: Power Connector (J2) Pin-out

| Pin | Function     |

|-----|--------------|

| 1   | 12V          |

| 2   | 12V          |

| 3   | 12V          |

| 4   | GND          |

| 5   | GND (Sense0) |

| 6   | GND          |

# 8.0 Memories

The **ProceV** system memory has a four-level structure as follows:

Two-level structure of Stratix *V* embedded memories with ultra-high bandwidth:

MLAB (Memory Logic Array Blocks) 640-bit Memories

M20K Blocks 52 Mb Memories

Additional two level structure of peripheral on-board memory blocks:

3. **SRAM** (optional) 2 ×144/36 Mb 36-bit wide

4. **DDR3 DRAM SODIMM** 2x8GB 72-bit wide

#### 8.1. Two-level structure Stratix V embedded memory

The Stratix V embedded memory includes two different sizes of embedded memory. Each embedded memory block can be configured (depth x width), via the Quartus software, to be a single-port RAM, dual-port RAM, ROM, or shift register.

For further information on the *Stratix V* embedded memories, refer to *Stratix V Device Handbook* (Altera Corporation).

#### 8.2. On-board Memory Blocks - DDRII<sup>+</sup> SRAM (optional)

The **GiDEL ProceV** board has up to two 144 Mb or 36Mb DDRII $^+$  SRAM 36-bits wide devices (**Block D and E**) connected directly to the Stratix V device. The SRAM maximum working frequency is up to 450 Mhz.

#### 8.3. ECC DDR3 DRAM SODIMM Modules - 72 bit wide

For additional memory, Stratix V device is supported by two DDR3 Modules slots (204-Pin un-buffered SODIMM with ECC). Each DDR3 slot has a maximum capacity of 8GB. The two SODIMM memory modules are designated **Block B** and **Block C**, respectively.

The *GiDEL ProcMultiPort* controller can be used with the SODIMM modules to enable new design methodologies by replacing large and complicated designs and reducing development time. For further information, refer to the *ProcMultiPort Data Book*. Altera or any other DRAM controller may also be used.

# 8.4. SODIMM Connectivity

The following table shows the SODIMM memory modules' top-level connectivity.

Table 19: SODIMM Top-Level Signals

| Bank B<br>Top-Level<br>Signals | Bank C<br>Top-Level<br>Signals | Equivalent<br>SODIMM<br>Signal<br>Name | I/O<br>Directions | Description                                                                                                                     |

|--------------------------------|--------------------------------|----------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------|

| addr_b[0-15]                   | addr_c[0-15]                   | A(0-15)                                | Output            | Address Outputs                                                                                                                 |

| dq_b[0-63]                     | dq_c[0-63]                     | DQ(0-63)                               | 1/0               | Data input/output: bidirectional data bus.                                                                                      |

| cb_b[0-7]                      | cb_c[0-7]                      | CB(0-7)                                | 1/0               | Check bits: used for system error detection and correction.                                                                     |

| dqm_b[0-8]                     | dqm_c[0-8]                     | DM(0-8)                                | Output            | Data mask (x8 devices only):<br>DM is an Output mask signal<br>for the SODIMM to write data.                                    |

| dqs_b[0-8]                     | dqs_c[0-8]                     | DQS(0-8)                               | 1/0               | Data strobe: differential data strobes (coupled with differential pairs DQSn(0-8))                                              |

| dqsn_b[0-8]                    | dqsn_c[0-8]                    | DQSn(0-8)                              | 1/0               | Data strobe: differential data strobes (coupled with differential pairs DQS(0-8))                                               |

| ba_b[0-2]                      | ba_c[0-2]                      | BA(0-2)                                | Output            | Bank address inputs: define<br>the device bank to which an<br>ACTIVE, READ, WRITE, or<br>PRECHARGE command is<br>being applied. |

| ck_b(0-1)                      | ck_c(0-1)                      | CK(0-1)                                | Output            | Clock: differential clock inputs.<br>these signals (coupled with<br>differential pairs CKn(0-1))                                |

| ckn_b(0-1)                     | ckn_c(0-1)                     | CKn(0-1)                               | Output            | Clock: differential clock inputs (coupled with differential pair CK(0-1))                                                       |

| cas_b                          | cas_c                          | CASn                                   | Output            | Command Output                                                                                                                  |

| ras_b                          | ras_c                          | RASn                                   | Output            | Command Output                                                                                                                  |

| we_b                           | we_b                           | Wen                                    | Output            | Command Output                                                                                                                  |

| cke_b[0-1] | cke_c[0-1] | CKE(0-1) | Output                   | Clock enable:Enables<br>(registered HIGH) and disables<br>(registered LOW) internal<br>circuitry and clocks on the<br>DRAM      |

|------------|------------|----------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| cs_b[0-1]  | cs_c[0-1]  | S(0-1)n  | Output                   | Chip select:Enables<br>(registered LOW) and disables<br>(registered HIGH) the<br>command decoder                                |

| resetn_b   | resetn_c   | Resetn   | Output<br>(LVCMOS)       | Reset:RESETn is an active LOW asychronous Output that is connected to each DRAM and the registering clock driver.               |

| odt_b[0-1] | odt_c[0-1] | ODT(0-1) | Output                   | On-die termination:Enables (registered HIGH) and disables (registered LOW) termination resistance internal to the DDR3 SDRAM.   |

| event_b    | event_c    | EVENTn   | Input<br>(Open<br>Drain) | Temperature event:The EVENTn pin is asserted by the temperature sensor when critical temperature thresholds have been exceeded. |

| sda        | sda        | SDA      | I/O                      | Serial data:Used to transfer addresses and data into and out of the temperature sensor/SPD EEPROM on the I2CC bus.              |

| scl        | scl        | SCL      | Output                   | Serial clock for temperature sensor/SPD EEPROM                                                                                  |

#### 8.5. SRAM Connectivity

The ProceV has an optional dual DDR II+ synchronous SRAM memory modules referred to as Bank D and Bank E. There are two SRAM device options:

- 1. SRAM 144 Mb Cypress CY7C1650KV18.

- 2. SRAM 36 Mb Cypress CY7C1250KV18-450BZXC

The following table shows the 144 Mb SRAM memory modules' top-level connectivity.

Table 20: SRAM Top-Level Signals

| Bank D (U13)<br>Top-Level<br>Signals | Bank E (U14)<br>Top-Level<br>Signals | FPGA I/O<br>Direction  | Description                                                                                                   |

|--------------------------------------|--------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------|

| addr_d[21:1]                         | addr_e[21:1]                         | Output                 | Address [1]                                                                                                   |

| dq_d[35:0]                           | dq_e[35:0]                           | I/O                    | DQ (Data input / output )                                                                                     |

| cq_d                                 | cq_e                                 | Differential<br>Input  | Synchronous echo clock outputs                                                                                |

| cqn_d                                | cqn_e                                | Differential<br>Input  | Synchronous echo clock outputs. this signal is coupled with its differential pair cq_d/e                      |

| r_wn_d                               | r_wn_e                               | Output                 | When LDn low,                                                                                                 |

|                                      |                                      |                        | 1: Read operation,                                                                                            |

|                                      |                                      |                        | 0: Write operation                                                                                            |

| k_d                                  | k_e                                  | Differential<br>Output | Positive clock Output.                                                                                        |

| kn_d                                 | kn_e                                 | Differential<br>Output | Negative clock Output. This signal is coupled with its differential pair k_                                   |

| bwsn_d[3:0]                          | bwsn_e[3:0]                          | Output                 | Byte write select (BWS) -<br>Active low. Used to select<br>which byte is written into<br>the device [2]       |

| ldn_d                                | ldn_e                                | Output                 | Synchronous load                                                                                              |

| qvld_d                               | qvld_e                               | Input                  | Valid Input indicator. The Q<br>Valid indicates valid Input<br>data. QVLD is edge aligned<br>with CQ and CQn. |

<sup>[1]</sup> The Address is in 72-bit wide data (One address per DDR data).

For lower cost SRAM the address lines are reduced.

In some SRAMs A0 may be added to have address at 36 bit resolution.

[2] BWS 0 controls D[8:0], BWS 1controls D[17:9], BWS 2 controls D[26:18] and BWS 3 controls D[35:27]

For further information regarding the 144Mb SRAM, refer to the Cypress SRAM CY7C1650KV18 datasheet (doc #: 001-44061).

For further information regarding the 36Mb SRAM, refer to the Cypress SRAM CY7C1250KV18-450BZXC datasheet (doc #: 001-57834).

**Note:** Outputs are Synchronous to K clock. Inputs are Synchronous to CQ echo clock.

All of the **ProceV** LEDs (accept SFP+ LEDs) are located on the top of the PS (Print Side) of the board.

#### 9.1. Power LEDs

The **ProceV** board has four power LEDs as follows:

Table 21: Power LEDs.

|    | LED Name | Function                                                          |

|----|----------|-------------------------------------------------------------------|

| 1. | 12V      | 12 V - when LED illuminates it indicates there is power.          |

| 2. | ~Vccint  | 0.9 or 0.85 V – when LED illuminates it indicates a power failure |

| 3. | 2.5V     | 2.5 V - when LED illuminates it indicates that there is power.    |

| 4. | 3V       | 3.0 V - when LED illuminates it indicates that there is power.    |

#### 9.2. Status LEDs

The **ProceV** board has three Status LEDs as follows:

Table 22: Status LEDs

|    | LED<br>Name | Function                                                                  |

|----|-------------|---------------------------------------------------------------------------|

| 1. | Status0     | Temperature indicator:                                                    |

|    |             | Blinking LED indicates that temperature is approaching to critical level. |

|    |             | Constant illuminated LED: indicates overheating.                          |

| 2. | Status1     | Blinking to indicate that card is operational                             |

| 3. | Status2     | Indicates that the board has established link with the PCI Express slot   |

**Note**: The status LEDs name at the FPGA top level is status\_ledn.

## 9.3. General Purpose User LEDs

**ProceV** boards contain four general purpose user LEDs connected to the Stratix V FPGA. The user LEDs name at the top level is ledn[3:0] accordingly. The LEDs are active low (Asserting a logical "0" to a LED signal will illuminate it).

#### 9.4. SFP+ LEDs

**ProceV** boards contain four SFP+ LEDs located in CS (Component Side) close to the SFP+ connector; these LEDs may be used for SFP+ trafix information or as User defined.

# 10.0 Technical Specifications

#### 10.1. Electrical and Mechanical Environment

#### 10.1.1. **Humidity**

The **ProceV** is operational under the following conditions:

Humidity: 10 - 90% (non-condensing)

#### 10.1.2. Temperature

**ProceV** board is equipped with an on-board temperature controller.

The maximal operating temperature of the on-board STRATIX V FPGA is 85°C. If an FPGA exceeds this temperature the user logic will be reset. At 70°C, an interrupt will be issued indicating that the temperature is approaching critical level.

The **ProceV** operating limits depend on the IC type, the computer ambient temperature, and the computer air flow as detailed in the following table:

Table 23: ProceV Operating Conditions

|   | IC Type | Max Power consumption per IC[W] | Max. Computer Ambient Temp(C°) | Min<br>Computer<br>Air Flow<br>[m/sec] |

|---|---------|---------------------------------|--------------------------------|----------------------------------------|

| ļ | All     | TBD                             | TBD                            | TBD                                    |

#### 10.2.MTBF

The Mean Time Between Failures (MTBF) for the ProceV board is: 700,000 Hours.

Note: For Models with a limited VCCINT of up to 16A, the MTBF is: 900,000 Hours.

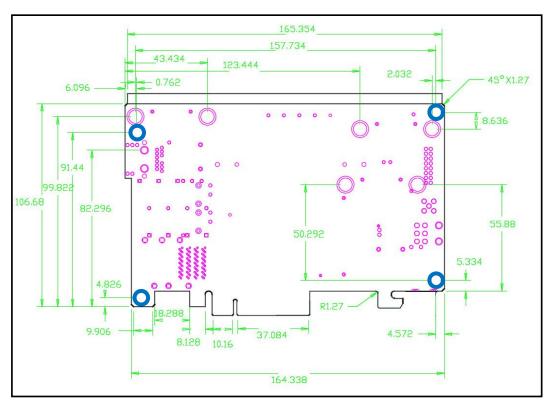

## 10.3. ProceV Mechanical Description

**ProceV** mechanical dimensions, shown in Figure 5, comply with the PCI Express standard half length form factor.

Figure 5: ProceV Mechanical Dimensions (in mm)

For **ProceV** daughterboard (PSDB) mechanical dimensions please refer to the specific PSDB's Data Book.

**Note**: The blue circles in the figure indicate mounting location for stand-alone.

#### 10.4. Power Consumption

**ProceV** is powered by 12V, supplied either by the PCI Express slot, by an external power supply or both. The maximum allowable current is summarized in the following table:

Table 24: Maximum current Limits

| 12V Source           | Max Current |

|----------------------|-------------|

| External & PCIe Slot | 5A          |

The following table summarizes the **ProceV** internal voltage sources available for user controlled resources:

Table 25: ProceV Internal Voltage Sources

| Name       | Voltage | Description                              | Max Allowable<br>Current |

|------------|---------|------------------------------------------|--------------------------|

| VCCINT     | 0.9V    | Stratix V core voltage                   | 30A <sup>(1, 2)</sup>    |

| 3.3V       | 3.3V    | Modules and cable connected peripherals. | 5.4A <sup>(3)</sup>      |

| VCCMEM1    | 1.8V    | DDRII⁺ SRAM<br>power supply              | 2.5A <sup>(4)</sup>      |

| VCCMEM2    | 1.35V   | DDRIII SODIMM power supply               | 5.3A <sup>(5)</sup>      |

| PSDB VCCIO | 2.5V ≥  | PSDB I/O power supply                    | 3A <sup>(6)</sup>        |

- (1) The VCCINT current consumption depends on the FPGA logic usage and on the system frequency. For precise power consumption information, refer to Quartus power analyzer report.

- (2) The VCCINT is limited to 16A for the ProceV models of Altera's Startix V GX A3 FPGA with Speed Rates of 3 and 4.

- (3) The 3.3V is the total current available for the following modules: SFP+ (A and B), CXP, External\_IO (J3), PSDB (J4).

- (4) The VCCMEM1 is the current that can be supplied to both SRAMs and the FPGA's 1.8V VCCIO. The current values depend on the SRAM capacity and the frequency rate. For more information on the SRAM, refer to their manufacturer's data sheet.

- (5) The VCCMEM2 current Max current supplied to both of the SODIMMs + the FPGA's 1.35V VCCIO. The current values depend on the SODIMM capacity and the sustain rate. For more information on the SODIMM, refer to their manufacturer's data sheet.

(6) The VCCIO supplies power to the PSDB IOs. The power consumption is dependent on I/O frequency and toggle rate. For precise power consumption information, refer to Quartus power analyzer report.

Total power consumption of **ProceV** can be calculated according to the following formulas:

$$P_{TOTAL} = 4.0W + P_{Modules} + 1.1* (P_{FPGA} + P_{memories})$$

$P_{FPGA}$  = FPGA power dissipation

$P_{Modules}$  = 1.1×Σ (3.3V power modules and external dependencies)

+  $\Sigma$  (12V power modules and external dependencies)

P<sub>memories</sub>= Sum of SODIMM (1.35V) and SRAM power dissipation

Note: P<sub>TOTAL</sub> must be <= 54W (or 57 for 5% power supply accuracy)

# 10.5. ProceV Timing Model

#### 10.5.1. Groups Skew

Table 26: Groups Skew