# **USER MANUAL**

# **Accessory 84E**

Universal Serial Encoder Interface

3Ax-603927-xUxx

July 21, 2015

## **Copyright Information**

© 2015 Delta Tau Data Systems, Inc. All rights reserved.

This document is furnished for the customers of Delta Tau Data Systems, Inc. Other uses are unauthorized without written permission of Delta Tau Data Systems, Inc. Information contained in this manual may be updated from time-to-time due to product improvements, etc., and may not conform in every respect to former issues.

To report errors or inconsistencies, call or email:

Delta Tau Data Systems, Inc. Technical Support

Phone: (818) 717-5656 Fax: (818) 998-7807

Email: <a href="mailto:support@deltatau.com">support@deltatau.com</a>

Website: <a href="http://www.deltatau.com">http://www.deltatau.com</a>

## **Operating Conditions**

All Delta Tau Data Systems, Inc. motion controller products, accessories, and amplifiers contain static sensitive components that can be damaged by incorrect handling. When installing or handling Delta Tau Data Systems, Inc. products, avoid contact with highly insulated materials. Only qualified personnel should be allowed to handle this equipment.

In the case of industrial applications, we expect our products to be protected from hazardous or conductive materials and/or environments that could cause harm to the controller by damaging components or causing electrical shorts. When our products are used in an industrial environment, install them into an industrial electrical cabinet or industrial PC to protect them from excessive or corrosive moisture, abnormal ambient temperatures, and conductive materials. If Delta Tau Data Systems, Inc. products are directly exposed to hazardous or conductive materials and/or environments, we cannot guarantee their operation.

## **Safety Instructions**

Qualified personnel must transport, assemble, install, and maintain this equipment. Properly qualified personnel are persons who are familiar with the transport, assembly, installation, and operation of equipment. The qualified personnel must know and observe the following standards and regulations:

IEC364resp.CENELEC HD 384 or DIN VDE 0100

IEC report 664 or DIN VDE 0110

National regulations for safety and accident prevention or VBG 4

Incorrect handling of products can result in injury and damage to persons and machinery. Strictly adhere to the installation instructions. Electrical safety is provided through a low-resistance earth connection. It is vital to ensure that all system components are connected to earth ground.

This product contains components that are sensitive to static electricity and can be damaged by incorrect handling. Avoid contact with high insulating materials (artificial fabrics, plastic film, etc.). Place the product on a conductive surface. Discharge any possible static electricity build-up by touching an unpainted, metal, grounded surface before touching the equipment.

Keep all covers and cabinet doors shut during operation. Be aware that during operation, the product has electrically charged components and hot surfaces. Control and power cables can carry a high voltage, even when the motor is not rotating. Never disconnect or connect the product while the power source is energized to avoid electric arcing.

A Warning identifies hazards that could result in personal injury or death. It precedes the discussion of interest.

A Caution identifies hazards that could result in equipment damage. It precedes the discussion of interest.

A Note identifies information critical to the understanding or use of the equipment. It follows the discussion of interest.

|     | MANUAL REVISION HISTORY                                                                                                            |          |        |          |  |  |  |  |  |

|-----|------------------------------------------------------------------------------------------------------------------------------------|----------|--------|----------|--|--|--|--|--|

| REV | DESCRIPTION                                                                                                                        | DATE     | CHANGE | APPROVED |  |  |  |  |  |

| 1   | Manual Creation.                                                                                                                   | 04/27/10 | CP     | SS       |  |  |  |  |  |

| 2   | Fixed addresses in EnDat section.                                                                                                  | 12/01/10 | RN     | RN       |  |  |  |  |  |

| 3   | Added detailed information about EnDat, Yaskawa, Tamagawa, Panasonic, Mitutoyo, BiSS B/C, Matsushita A/D and Mitsubishi protocols. | 07/17/14 | SS     | SS       |  |  |  |  |  |

| 4   | Added example for incremental EnDat2.2                                                                                             | 10/23/14 | SS     | SS       |  |  |  |  |  |

| 5   | Added XY2-100 Protocol Appendix                                                                                                    | 05/08/15 | SS     | SS       |  |  |  |  |  |

This page intentionally left blank

## **Table of Contents**

| INTRODUCTION                                            | 8   |

|---------------------------------------------------------|-----|

| Overview                                                | 8   |

| Compatibility                                           | 9   |

| CDECLEICA DIONG                                         | 10  |

| SPECIFICATIONS                                          |     |

| Environmental Specifications                            |     |

| Physical Specifications                                 |     |

| Electrical Specifications.                              | 10  |

| Configuration                                           | 10  |

| HARDWARE SETUP                                          | .11 |

| Addressing the ACC-84E                                  |     |

| Signal Format                                           |     |

| Connections                                             |     |

| Encoder Specific Connection Information                 |     |

| Encoder specific Connection Information                 | ,13 |

| SOFTWARE SETUP                                          | .15 |

| Hardware-Control Parameter Setup                        | 15  |

| Multi-Channel Setup Element                             | .17 |

| Single-Channel Setup Element                            | .29 |

| Hardware-Status Data Structure                          | 45  |

| Single-Channel Status Elements                          | .45 |

| USING THE RESULTING POSITION INFORMATION                | .66 |

| Using the ACC-84E with Power PMAC                       | 66  |

| Ongoing Commutation Phase Position                      |     |

| Power-On Commutation Phase Position                     |     |

| Ongoing Servo Position                                  | .67 |

| Power-On Servo Position                                 | .68 |

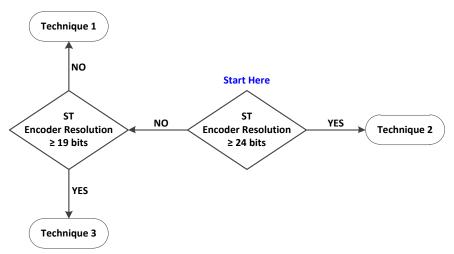

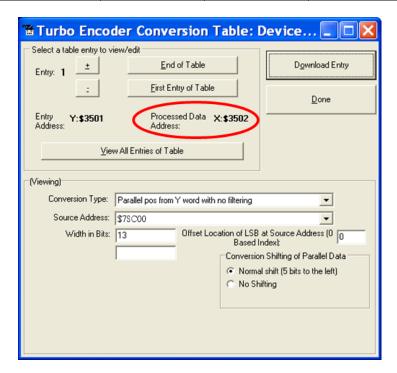

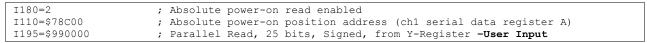

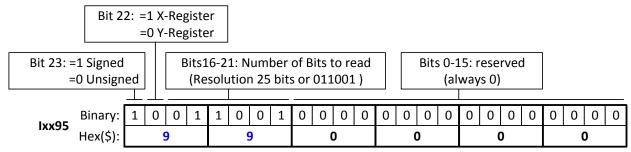

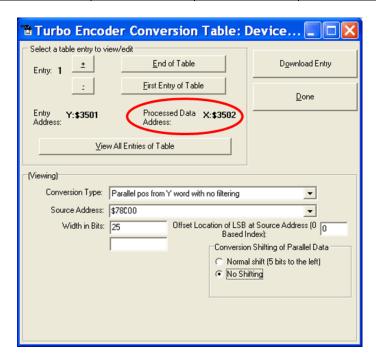

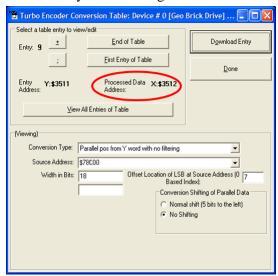

| Using the ACC-84E with Turbo PMAC                       | 69  |

| Setup Summary                                           | .70 |

| Technique 1 Example                                     |     |

| Technique 2 Example                                     | .76 |

| Technique 3 Example                                     | .81 |

| Using the ACC-84E with MACRO                            | 93  |

| Addressing and Register Addresses                       | .93 |

| Setting up the Global and Channel Registers on Power Up |     |

| Encoder Conversion Table Setup                          |     |

| Absolute Power-On Phasing and Servo Power on Position   | .95 |

| APPENDIX: SETUP EXAMPLES                                | .97 |

| SSI Feedback Setup Example                              |     |

| Multi-Channel Setup Element                                                  | 98  |

|------------------------------------------------------------------------------|-----|

| Single-Channel Setup Element                                                 |     |

| Brushless Motor with SSI Feedback - Setup Notes                              |     |

| EnDat 2.2 Feedback Setup Example:                                            | 101 |

| Absolute phase and power-up/reset position                                   |     |

| EnDat 2.2 with Incremental Encoders:                                         | 102 |

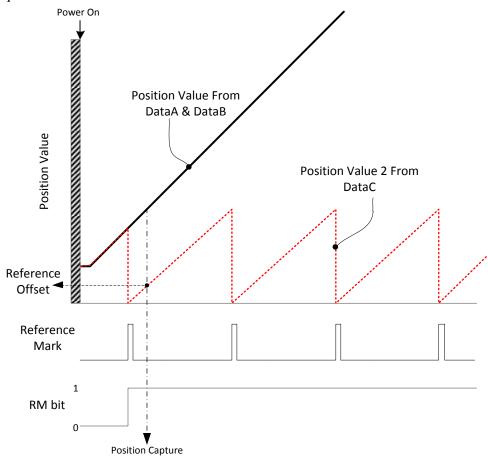

| EnDat 2.2 Reference Mark Setup Example:                                      | 104 |

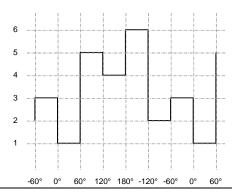

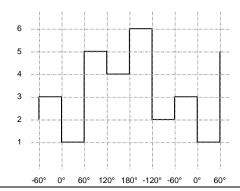

| Yaskawa Sigma II/III/V Feedback Setup Example                                | 107 |

| Channel Control Register Setup for Position Read                             | 107 |

| Encoder Specific Settings                                                    | 108 |

| BiSS-C Feedback Setup Example:                                               | 122 |

| Commutation with High Resolution Encoders (more than 23 bits per revolution) |     |

| Absolute Power-On Servo Position                                             |     |

| Absolute Power-On/Reset Phase Position                                       | 125 |

Table of Contents vii

## INTRODUCTION

#### **Overview**

The ACC-84E Universal Serial Encoder Interface Board provides up to four channels of serial encoders to be read by the UMAC and Ultralite/MACRO Station controllers. The ACC-84E is part of the UMAC or MACRO Pack family of expansion cards and these accessory cards are designed to plug into an industrial 3U rack system. The information from these accessories is passed directly to either the UMAC or MACRO Station CPU via the high speed JEXP expansion bus. ACC-84E supports different serial encoder protocols depending on the option ordered. These protocols are programmed into an on-board FPGA upon manufacturing. Multiple common protocols are supported at the moment and future developments of additional protocols are feasible. Currently, ACC-84E supports the following protocols:

| <ul><li>SSI</li></ul> | Synchronous | Serial Interface |

|-----------------------|-------------|------------------|

|-----------------------|-------------|------------------|

- EnDat 2.2 EnDat 2.2 interface from HEIDENHAIN

- Yaskawa Yaskawa Sigma II/III/V feedback support

- Tamagawa Tamagawa OAS and SA Absolute Encoders

- Panasonic A4 and A5 Encoder Series

- Mitutoyo Mitutoyo ENSIS® high-speed serial protocol (AT503/AT503A/ST70X)

- BiSS B/C BiSS B/C Unidirectional

- Matsushita

- Mitsubishi Mitsubishi Serial Encoder Protocol for HG-X Servo Motors

Each ACC-84E can only support one of the protocols mentioned above for all four channels. If the customer has two different serial protocols in the system, two separate ACC-84E cards should be used. Since ACC-84E is strictly a feedback input card, if the feedback is intended to be used as the feedback for closed loop servo control, the servo command should be sent out to the amplifier using a UMAC axis interface card depending on the signal and control type required by amplifier. Here is a list of possible axis interface cards available for UMAC systems:

- ACC-24E2 Digital amplifier breakout w/ TTL encoder inputs or MLDT

- ACC-24E2A Analog amplifier breakout w/ TTL encoder inputs or MLDT

- ACC-24E2S Stepper amplifier breakout w/ TTL encoder inputs or MLDT

- ACC-24E3 Analog/Digital Output (Power PMAC Compatible Only)

Up to 12 ACC-84E boards can be connected to one UMAC providing up to 48 channels of serial encoder feedback. Because each MACRO Station CPU can service only eight channels of servo data, only two fully populated ACC-84E boards can be connected to the MACRO-Station.

The ACC-84E board will take the data from the serial encoder and process it as up to four 24-bit binary parallel words depending on protocol specifications. This data can then processed in the UMAC or MACRO Station encoder conversion table for position and velocity feedback. With proper setup, the information can also be used to commutate brushless and AC induction motors.

Introduction 8

## Compatibility

The ACC-84E can be used with any type of CPU available for UMAC systems. These CPUs include:

- Power PMAC UMAC CPU

- > Turbo PMAC UMAC CPU

- MACRO16 UMAC CPU

Introduction 9

## **SPECIFICATIONS**

## **Environmental Specifications**

| Description           | Specification              | Notes |

|-----------------------|----------------------------|-------|

| Operating Temperature | 0°C to 45°C,               |       |

| Storage Temperature   | -25°C to 70°C              |       |

| Humidity              | 10% to 95 % non-condensing |       |

## **Physical Specifications**

| Specification                                        | Notes                                                                           |

|------------------------------------------------------|---------------------------------------------------------------------------------|

| Length: 16.256 cm (6.4 in.)                          |                                                                                 |

| Height: 10 cm (3.94 in.)<br>Width: 2.03 cm (0.8 in.) |                                                                                 |

|                                                      |                                                                                 |

| DB9 Female                                           | UL-94V0                                                                         |

|                                                      | Length: 16.256 cm (6.4 in.)  Height: 10 cm (3.94 in.)  Width: 2.03 cm (0.8 in.) |

The width is the width of the front plate. The length and height are the dimensions of the PCB.

## **Electrical Specifications**

| Description                   | Specification                                 | Notes                                                                                              |

|-------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------|

| ACC-84E Power<br>Requirements | 5V @ 360mA (±10%)<br>+15V @ 0 A<br>-15V @ 0 A | 5V current requirement mentioned is the consumption of the ACC-84E without any encoders connected. |

## Configuration

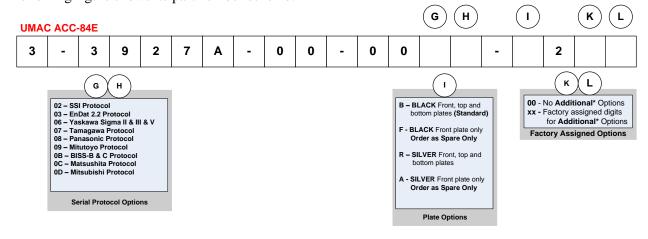

The ACC-84E can support different serial encoder protocols depending on the selected option. The following figure shows its part number scheme:

$<sup>^{\</sup>star}$  If Any **Additional Option** is required, contact factory for digits  $\boldsymbol{K}$  and  $\boldsymbol{L}$  (Factory Assigned digits).

Specifications 10

## **HARDWARE SETUP**

The ACC-84E uses expansion port memory locations defined by the type of PMAC (Power, Turbo, or MACRO) to which it is directly communicating.

## **Addressing the ACC-84E**

The Switch 1 (SW1) settings will allow you to select the starting address location for data from the first encoder. Data from encoders 2 through 4 will be placed at +4 memory locations from the base address and so on and so forth.

| Chin           |           | Base Addres | SS         |    | SW1 Positions |     |     |     |     |  |

|----------------|-----------|-------------|------------|----|---------------|-----|-----|-----|-----|--|

| Chip<br>Select | TURBO     | MACRO       | POWER      | 6  | 5             | 4   | 3   | 2   | 1   |  |

|                | Y:\$78C00 | Y:\$8800    | ACC84E[0]  | ON | ON            | ON  | ON  | ON  | ON  |  |

| CC10           | Y:\$79C00 | Y:\$9800    | ACC84E[4]  | ON | ON            | ON  | OFF | ON  | ON  |  |

| CS10           | Y:\$7AC00 | Y:\$A800    | ACC84E[8]  | ON | ON            | OFF | ON  | ON  | ON  |  |

|                | Y:\$7BC00 | Y:\$B800    | ACC84E[12] | ON | ON            | OFF | OFF | ON  | ON  |  |

|                | Y:\$78D00 | Y:\$8840    | ACC84E[1]  | ON | ON            | ON  | ON  | ON  | OFF |  |

| CS12           | Y:\$79D00 | Y:\$9840    | ACC84E[5]  | ON | ON            | ON  | OFF | ON  | OFF |  |

| CS12           | Y:\$7AD00 | Y:\$A840    | ACC84E[9]  | ON | ON            | OFF | ON  | ON  | OFF |  |

|                | Y:\$7BD00 | Y:\$B840    | ACC84E[13] | ON | ON            | OFF | OFF | ON  | OFF |  |

|                | Y:\$78E00 | Y:\$8880    | ACC84E[2]  | ON | ON            | ON  | ON  | OFF | ON  |  |

| CC14           | Y:\$79E00 | Y:\$9880    | ACC84E[6]  | ON | ON            | ON  | OFF | OFF | ON  |  |

| CS14           | Y:\$7AE00 | Y:\$A880    | ACC84E[10] | ON | ON            | OFF | ON  | OFF | ON  |  |

|                | Y:\$7BE00 | Y:\$B880    | ACC84E[14] | ON | ON            | OFF | OFF | OFF | ON  |  |

**ON** designates **Closed**. **OFF** designates **Open**. Factory default is all ON.

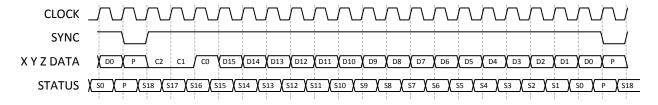

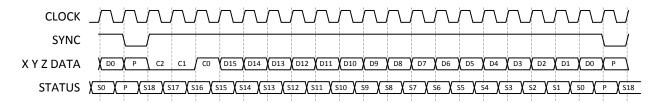

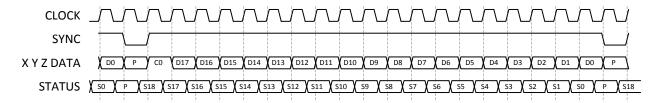

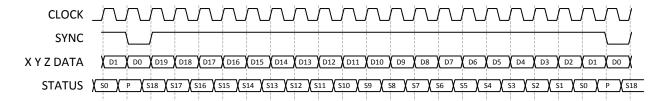

## **Signal Format**

The signal format for the encoder is dependent on the particular protocol, but in all protocols, there is a "strobe" and/or "clock" output from the controller, and a data channel into the processor from the encoder. The encoder is queried synchronously with the Power/Turbo PMAC's phase or servo clock, and the incoming serial data is latched into a memory-mapped register for the processor to read.

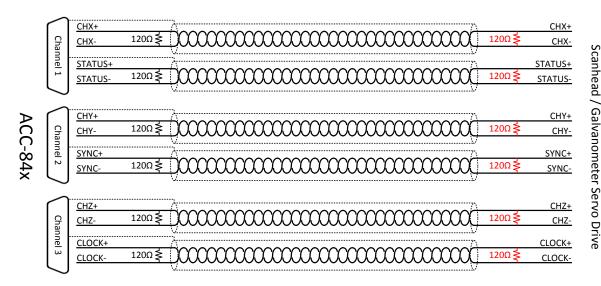

### **Connections**

Encoders are connected to the ACC-84E through four 9-pin D-sub connectors. Two connectors on the top side of the rack for encoders 1 and 2, and two connectors in the bottom side for encoders 3 and 4.

|   | D-Sub DE9 Female<br>Mating: D-Sub DE9 Male |        |                |                | © 4 © 2 O<br>© 0 O       |                          |                         |             |            |

|---|--------------------------------------------|--------|----------------|----------------|--------------------------|--------------------------|-------------------------|-------------|------------|

|   | Pin # / Fur                                | nction | SSI /<br>EnDat | Yaskawa        | Tamagawa                 | Panasonic                | Mitutoyo/<br>Mitsubishi | BiSS<br>B/C | Matsushita |

| 1 | CLOCK-                                     | OUT    | CLK-           |                | -                        | _                        |                         | MA-         | _          |

| 2 | DATA-                                      | IN/OUT | DAT-           | SDI<br>BLU/BLK | $\overline{\mathrm{SD}}$ | $\overline{\mathrm{PS}}$ | MRR<br>(*RQ/*DT)        | SLO-        | /Rx        |

| 3 | ENA-                                       | OUT    | _              |                | SENA                     |                          | _                       |             |            |

| 4 | GND                                        | COM    | GND            | GND<br>BLK     |                          |                          | GND                     |             |            |

| 5 | GND                                        | COM    | GND            | GND<br>BLK     |                          |                          | GND                     |             |            |

| 6 | CLOCK+                                     | OUT    | CLK+           |                | -                        | _                        |                         | MA+         | _          |

| 7 | DATA+                                      | IN/OUT | DAT+           | SDO<br>BLU     | SD PS MR (RQ/DT) SLO+    |                          |                         |             | Rx         |

| 8 | ENA+                                       | OUT    |                | _              | SENA -                   |                          |                         |             |            |

| 9 | + 5V                                       | OUT    |                | + 5V           |                          |                          |                         |             |            |

## **Encoder Specific Connection Information**

#### Yaskawa Sigma II/III/V Encoders

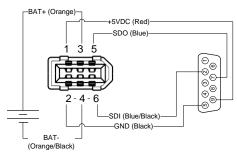

Yaskawa Sigma II/III/V absolute encoders require a 3.6V battery to maintain the multi-turn data while the controller is powered down. This battery should be placed outside of ACC-84E and the Yaskawa Sigma II/III/V encoder, possibly on the cable. The battery should be installed between orange (+3.6V) and orange/black wires (GND). Use of ready-made cables by Yaskawa is recommended. (Yaskawa part number: UWR00650)

The previous diagram shows the pin assignment from mating IEEE 1394 Yaskawa Sigma II connector to ACC-84E encoder input. The Molex connector required for IEEE 1394 can be acquired as receptacle kit from Molex, 2.00mm (.079") Pitch Serial I/O Connector, Receptacle Kit, Wire-to-Wire, Molex Part Number: 0542800609.

Note

Yaskawa Encoder expects a supply voltage of 5V with less than 5% tolerance. Make sure voltage drop is not caused by excessive wire length.

Note

Encoder wire shield must be connected to chassis ground on both encoder and connector ends.

Note

Yaskawa Sigma II/III/V require a  $120\Omega$  termination resistor between SDI and SDO twisted pair lines on ACC-84E side.

### Mitsubishi HG-□ Servo Motor Encoders

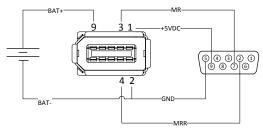

Mitsubishi HG-□ servo motor absolute encoders require a 3.6V battery to maintain the multi-turn data while the controller is powered down. This battery should be placed outside of ACC-84E and the Mitsubishi HG-□ servo motor's encoder, possibly on the cable. The battery should be installed between pin 9 of the motor encoder connector (+6V) and pin 2(GND). Use of ready-made cables by Mitsubishi is recommended. (Mitsubishi part number: UWR00650)

The diagram above shows the pin assignment from mating 3M SCR Receptacle (36110) to ACC-84E encoder input.

## **SOFTWARE SETUP**

ACC-84E supports multiple protocols and for this reason the setup for each of them will be different. For each protocol, depending on the CPU type, the setup steps differs slightly, but the general idea regardless of the protocol is the same.

Position encoders that provide numerical position information in a serial data stream, usually representing absolute position information, are becoming increasingly popular. ACC-84E is an FPGA-based interface which is programmed to support different serial protocols. Multiple serial encoder protocols are supported by ACC-84E.

## **Hardware-Control Parameter Setup**

This section describes the Power/Turbo PMAC serial encoder hardware interface in general terms. All of the supported serial encoder interfaces use differential signal pairs at 5V RS-422 levels. All have clock and/or "strobing" outputs, and all have a data signal input. In some protocols, the data line is bidirectional, supporting data output commands to the encoder.

The configuration of the hardware control registers differs slightly between serial protocols in the ACC-84E, however, the principles of setup are the same.

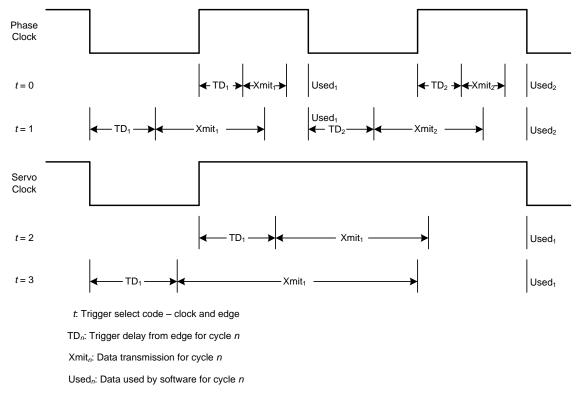

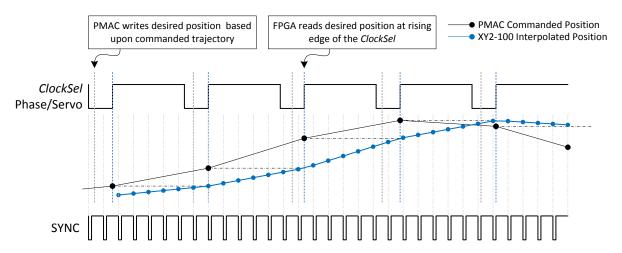

Because of the serial data protocol, the transfer of data from the encoder to the Power/Turbo PMAC interface circuitry takes a significant amount of time. The data must be ready for the processor immediately after the falling edge of the phase and/or servo clock signals, which are the interrupts to the processor telling it to start those respective tasks.

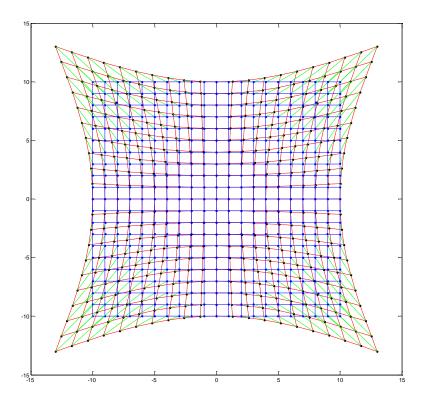

The process of querying the encoder for data must start well before these signal edges, and this timing must be carefully considered. If it starts too late, the data will not be ready in time. If it starts too early, unnecessary delay is introduced into the feedback loop, possibly compromising its performance. In both styles of interface, the multi-channel saved setup element permits the user to optimize the timing by selecting the edge (rising or falling) of the clock signal (phase or servo) that starts the triggering process, and the time delay from this edge until the actual triggering occurs. The following diagram shows the time lines for the possible configurations:

#### **Serial Encoder Interface Timing**

The "SEIGATE" FPGA on the ACC-84E UMAC board has a multi-channel setup element that affects all channels on the IC, and a single-channel setup element for each channel.

This section describes the setup elements for the serial encoder interface in general terms. Detailed information for each serial encoder protocol can be found in the following reference chapters of the manual.

This section describes the setup of the FPGA-based elements using the **Acc84E**[*i*] data structure. If you are using the FPGA-base serial encoder interface in the Power Brick, substitute "**Acc84B**[*i*]" for "**Acc84E**[*i*]".

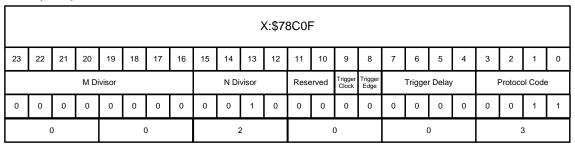

## **Multi-Channel Setup Element**

The multi-channel setup element **Acc84E**[*i*].**SerialEncCtrl** (saved element in Power PMAC only and non-saved in Turbo PMAC, must be setup in power/initialization PLC) specifies several aspects of the serial encoder configuration for all four channels of the IC: the protocol, the trigger, and the clock frequency. All three of these aspects must be common to all four channels of the IC, so it is not possible, for instance, to interface to encoders with different protocols from the same IC.

The different components of this 24-bit full-word element cannot be accessed as independent elements, so it is necessary to assemble the full-word value from the values of the individual components. It is easiest to treat the value as a hexadecimal value, so the individual components can be seen independently.

| Power PMAC               | Turbo PMAC              |       | Switch Posi | Position (SW1) |       |  |

|--------------------------|-------------------------|-------|-------------|----------------|-------|--|

| Global Control Register  | Global Control Register | 1     | 2           | 3              | 4     |  |

| ACC84E[0].SerialEncCtrl  | X:\$78C0F               | Close | Close       | Close          | Close |  |

| ACC84E[4].SerialEncCtrl  | X:\$79C0F               | Close | Close       | Open           | Close |  |

| ACC84E[8].SerialEncCtrl  | X:\$7AC0F               | Close | Close       | Close          | Open  |  |

| ACC84E[12].SerialEncCtrl | X:\$7BC0F               | Close | Close       | Open           | Open  |  |

| ACC84E[1].SerialEncCtrl  | X:\$78D0F               | Open  | Close       | Close          | Close |  |

| ACC84E[5].SerialEncCtrl  | X:\$79D0F               | Open  | Close       | Open           | Close |  |

| ACC84E[9].SerialEncCtrl  | X:\$7AD0F               | Open  | Close       | Close          | Open  |  |

| ACC84E[13].SerialEncCtrl | X:\$7BD0F               | Open  | Close       | Open           | Open  |  |

| ACC84E[2].SerialEncCtrl  | X:\$78E0F               | Close | Open        | Close          | Close |  |

| ACC84E[6].SerialEncCtrl  | X:\$79E0F               | Close | Open        | Open           | Close |  |

| ACC84E[10].SerialEncCtrl | X:\$7AE0F               | Close | Open        | Close          | Open  |  |

| ACC84E[14].SerialEncCtrl | X:\$7BE0F               | Close | Open        | Open           | Open  |  |

**Acc84E**[*i*].**SerialEncCtrl** is the full-word element that comprises the multi-channel setup for serial encoder interfaces for the ACC-84E. It is comprised of the following components (which cannot be accessed as independent elements):

| Component          | Turbo PMAC/<br>Power PMAC<br>Script Bits | Hex<br>Digit # | C<br>Bits | Functionality                              |

|--------------------|------------------------------------------|----------------|-----------|--------------------------------------------|

| SerialClockMDiv    | 23 – 16                                  | 1 - 2          | 31 - 24   | Serial clock linear division factor        |

| SerialClockNDiv    | 15 – 12                                  | 3              | 23 - 20   | Serial clock exponent division factor      |

| (Reserved)         | 11 – 10                                  | 4              | 19 – 18   | (Reserved for future use)                  |

| SerialTrigClockSel | 09                                       | 4              | 17        | Serial trigger source select               |

| SerialTrigEdgeSel  | 08                                       | 4              | 16        | Serial trigger source edge select          |

| SerialTrigDelay    | 07 – 04                                  | 5              | 15 – 12   | Serial trigger delay from source edge      |

| SerialProtocol     | 03 – 00                                  | 6              | 11 – 08   | Serial encoder protocol select (read-only) |

The component *SerialClockMDiv* controls how an intermediate clock frequency is generated from the IC's fixed 100 MHz clock frequency. The resulting serial-encoder clock frequency is then generated from this intermediate clock frequency by the component *SerialClockNDiv*, described below.

The equation for this intermediate clock frequency  $f_{int}$  is:

$$f_{\rm int}(MHz) = \frac{100}{M+1}$$

where *M* is short for *SerialClockMDiv*. This 8-bit component can take a value from 0 to 255, so the resulting intermediate clock frequencies can range from 100 MHz down to 392 kHz.

The component SerialClockNDiv controls how the final serial-encoder clock frequency is generated from the intermediate clock frequency set by SerialClockMDiv. The equation for this final frequency  $f_{ser}$  is:

$$f_{ser}(MHz) = \frac{f_{int}(MHz)}{2^N} = \frac{100}{(M+1)^* 2^N}$$

where N is short for SerialClockNDiv. This 4-bit component can take a value from 0 to 15, so the resulting  $2^N$  divisor can take a value from 1 to 32,768.

For serial-encoder protocols with an explicit clock signal, the resulting frequency is the frequency of the clock signal that is output from the ACC-84E's IC to the encoder. For "self-clocking" protocols without an explicit clock signal, this frequency is the input sampling frequency, and will be 20 to 25 times higher than the input bit rate  $f_{bit}$ . Refer to the instructions for the particular protocol for details.

The component *SerialTrigClockSel* controls which Power PMAC clock signal causes the encoder to be triggered. This single-bit component is set to 0, the encoder will be triggered on the phase clock; if it is set to 1, the encoder will be triggered on the servo clock. If the encoder feedback is required for commutation rotor angle feedback, it should be triggered on the phase clock; otherwise it can be triggered on the servo clock.

The component *SerialTrigEdgeSel* controls which edge of the clock signal (phase or servo) selected by *SerialTrigClockSel* initiates the triggering process. If this single-bit component is set to 0, the triggering process starts on the rising edge; if it is set to 1, the triggering process starts on the falling edge. Power PMAC software expects to have the resulting encoder data available to it immediately after the falling edge of the relevant phase or servo clock signal, which interrupts the processor to initiate the activity that reads this data. Since minimum delay from trigger to use is desirable, it is better to start the triggering on rising clock edge if the data can be fully transferred before the falling edge. If this is not possible, the falling edge should be used to start the triggering process.

It is best to choose the edge that minimizes the delay between the triggering of the encoder and its use by the Power/Turbo PMAC software. The software will use the received encoder value immediately after the falling edge of the phase clock for commutation feedback, and immediately after the falling edge of the servo clock for servo feedback.

If you are using the serial encoder data for commutation feedback, you must trigger using the phase clock in order to get new data every phase cycle. If there is sufficient time to receive the data in one half of a phase clock cycle, you should use the rising edge of the phase clock to trigger. For example, at the default phase clock frequency of 9 kHz, a clock cycle is  $110~\mu sec$ . If the serial encoder data can be received within  $55~\mu sec$ , the rising edge should be used. If not, the falling edge must be used.

If you are only using the serial encoder data for servo, and not commutation, feedback, the servo clock can be used for the trigger. However, it is still advisable to use the phase clock if possible to minimize the delay. When using the servo clock, as with the phase clock, use the rising edge if possible for the trigger, and the falling edge only if required.

Remember that the servo clock signal is low only for one half phase clock cycle. For example, with the default 9 kHz phase clock and 2.25 kHz servo clock, the servo clock is low for only a half of 110  $\mu$ sec phase clock cycle, and the delay from the rising edge to the next falling edge is 385  $\mu$ sec.

The component *SerialTrigDelay* specifies the delay from the specified clock edge to the actual start of the output signal that will trigger the encoder response, in units of the serial encoder clock. A non-zero value

can be used to minimize the delay between triggering the encoder and its resulting use by the Power PMAC.

The triggering does not need to start exactly on the specified clock edge. The trigger delay component *SerialTrigDelay* specifies the number of 20-microsecond intervals after the specified clock edge before the triggering of the encoder actually begins. It can take a value of \$0 to \$F (0 to 15, or 0 to 300 microseconds). Non-zero values can be used to minimize the delay between triggering of the encoder and the use of its data in the next software cycle.

The component *SerialProtocol* controls which serial-encoder protocol is selected for all channels of the IC. This 4-bit component can take a value from 0 to 15. This component is read-only, as it reflects the protocol interface that was installed in the board at the factory.

The FPGA used here comes with the interface for only a single serial protocol, which was pre-installed at the factory as specified in the order. This component of the element is read-only, simply notifying the user which protocol has been installed.

The following table shows the protocol selected for each value of this component (more protocols may be added):

| Value | Protocol   | Value | Protocol     | Value | Protocol   | Value | Protocol   |

|-------|------------|-------|--------------|-------|------------|-------|------------|

| 0     | (Reserved) | 4     | (Reserved)   | 8     | Panasonic  | 12    | Matsushita |

| 1     | (Reserved) | 5     | (Reserved)   | 9     | Mitutoyo   | 13    | Mitsubishi |

| 2     | SSI        | 6     | Sigma II/III | 10    | (Reserved) | 14    | (Reserved) |

| 3     | EnDat      | 7     | Tamagawa     | 11    | BiSS-B/C   | 15    | (Reserved) |

When used in the Script environment (Both Turbo and Power PMAC), **Acc84E**[*i*].**SerialEncCtrl** is a 24-bit element. When used in the C environment (Power PMAC Only), it is a 32-bit element, with real data in the high 24 bits, so its value in the C environment is 256 times greater than its value in the Script environment.

#### **SSI Protocol**

The following list shows typical settings of Acc84E[i].SerialEncCtrl for an SSI encoder.

**Serial Clock MDiv**: =  $(100 / f_{bit}) - 1$  // Serial clock frequency = bit transmission frequency

**SerialClockNDiv**: = 0 // No further division unless f < 400 kHz

SerialTrigClockSel: = 0 // Use phase clock if possible

**SerialTrigEdgeSel**: = 0 // Use rising clock edge if possible

SerialTrigDelay: = 0 // Can increase from 0 if possible to reduce latency SerialProtocol: = \$02 // Shows SSI protocol is programmed into IC

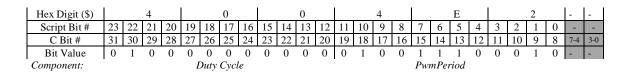

For example, for a 2.5 MHz bit transmission rate, SerialClockMDiv = (100 / 2.5) - 1 = 39 (\$23) and Acc84E[i].SerialEncCtrl is set to \$230002 for triggering on the rising edge of phase clock without delay.

| Hex Digit (\$)             |    |    | 2  |    |    |    | 3  |    |       |       | 0    |     |    |    | 0  |     |       |           | 0    |    | Ĺ    |      | 2     |    | <u> </u> | -   |

|----------------------------|----|----|----|----|----|----|----|----|-------|-------|------|-----|----|----|----|-----|-------|-----------|------|----|------|------|-------|----|----------|-----|

| Script Bit #               | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15    | 14    | 13   | 12  | 11 | 10 | 9  | 8   | 7     | 6         | 5    | 4  | 3    | 2    | 1     | 0  | -        | -   |

| C Bit #                    | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23    | 22    | 21   | 20  | 19 | 18 | 17 | 16  | 15    | 14        | 13   | 12 | 11   | 10   | 9     | 8  | 7-4      | 3-0 |

| Bit Value                  | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 1  | 0     | 0     | 0    | 0   | -  | -  | 0  | 0   | 0     | 0         | 0    | 0  | 0    | 0    | 1     | 0  | -        | -   |

| Component: SerialClockMDiv |    |    |    |    |    |    |    |    | Serie | alCle | nckN | Div |    |    | TC | TE. | Serie | $_{l}Tri$ | oDel | av | Seri | alPr | otoco | ol |          |     |

The following table lists a few common Serial clock frequency settings used with SSI protocol:

| SerialClockMDiv | Serial Clock NDiv | Serial Clock Frequency |

|-----------------|-------------------|------------------------|

| 49 (\$31)       | 0 (\$0)           | 2.0 MHz                |

| 99 (\$63)       | 0 (\$0)           | 1.0 MHz                |

| 99 (\$63)       | 1 (\$1)           | 500.0 kHz              |

| 99 (\$63)       | 2 (\$2)           | 250.0 kHz              |

#### EnDat 2.1/2.2 Protocol

The following list shows typical settings of **Acc84E**[i].**SerialEncCtrl** for an EnDat encoder. The serial clock frequency is set 25 times higher than the external clock frequency, which is the bit transmission frequency  $f_{bit(MHz)}$ , to permit oversampling of the input signal.

**SerialClockMDiv**:  $= (4/f_{bit}) - 1$  // Serial clock freq. = 25x bit transmission freq. **SerialClockNDiv**: = 0 // No further division **SerialTrigClockSel**: = 0 // Use phase clock if possible

SerialTrigClockSet: = 0 // Use phase clock if possible

SerialTrigEdgeSet: = 0 // Use rising clock edge if possible

SerialTrigDelay: = 0 // Can increase from 0 if possible to reduce latency SerialProtocol: = \$03 // Shows EnDat protocol is programmed into IC

For example, for a 2.0 MHz bit transmission rate, **SerialClockMDiv** = (4/2) - 1 = 1 (\$01) and

Acc84E[i].SerialEncCtrl is set to \$010003 for triggering on the rising edge of phase clock without delay.

Hex Digit (\$) | 0 | 1 | 0 | 0 | 3 | - - |

| Hex Digit (\$) |    |    | 0    |      |      |     | 1  |    |    |    | 0     |      |      |     | 0    |      |      |     | 0  |    |    |    | 3 |   | -   | -   |

|----------------|----|----|------|------|------|-----|----|----|----|----|-------|------|------|-----|------|------|------|-----|----|----|----|----|---|---|-----|-----|

| Script Bit #   | 23 | 22 | 21   | 20   | 19   | 18  | 17 | 16 | 15 | 14 | 13    | 12   | 11   | 10  | 9    | 8    | 7    | 6   | 5  | 4  | 3  | 2  | 1 | 0 | -   | -   |

| C Bit #        | 31 | 30 | 29   | 28   | 27   | 26  | 25 | 24 | 23 | 22 | 21    | 20   | 19   | 18  | 17   | 16   | 15   | 14  | 13 | 12 | 11 | 10 | 9 | 8 | 7-4 | 3-0 |

| Bit Value      | 0  | 0  | 0    | 0    | 0    | 0   | 0  | 1  | 0  | 0  | 0     | 0    | -    | -   | 0    | 0    | 0    | 0   | 0  | 0  | 0  | 0  | 1 | 1 | -   | -   |

| Component:     |    |    | Sori | alCl | ackN | Div |    |    | TC | TF | Sorie | 1Tri | αDel | lav | Sori | alPr | otoc | ol. |    |    |    |    |   |   |     |     |

The following table lists a few common Serial clock frequency settings used with EnDat2.1/2.2 protocol:

| $\mathcal{C}$   |                   | 1 2                | <b>1</b>               |

|-----------------|-------------------|--------------------|------------------------|

| SerialClockMDiv | Serial Clock NDiv | Serial Clock Freq. | Bit Transmission Freq. |

| 0 (\$00)        | 2 (\$2)           | 25.0 MHz           | 1.0 MHz                |

| 0 (\$00)        | 3 (\$3)           | 12.5 MHz           | 500 kHz                |

| 0 (\$00)        | 4 (\$4)           | 6.25 MHz           | 250 kHz                |

In newer version of the EnDat 2.1/2.2 firmware for ACC-84E (Released Feb. 4, 2014) bit 11 is used as backward compatible switch, which if set allows higher bit transmission frequencies.

Higher serial clock/but transmission frequency is only supported for short encoder cables, since in FPGA implementation of EnDat 2.1/2.2 in ACC-84E does not have the delay compensation feature.

The following list shows typical settings of **Acc84E**[i].**SerialEncCtrl** based upon the additional clock switch for an EnDat encoder. The the bit transmission frequency  $f_{bit\,(MHz)}$  is fixed at 1/4 of the external clock frequency.

**SerialClockMDiv**: =  $(25 / f_{bit}) - 1$  // Serial clock freq. = 4x bit transmission freq. **SerialClockNDiv**: = 0 // No further division

SerialDivSelect: = 0 // Selects higher clock frequency selection

SerialTrigClockSel: = 0 // Use phase clock if possible

SerialTrigEdgeSel: = 0 // Use rising clock edge if possible

SerialTrigDelay: = 0 // Can increase from 0 if possible to reduce latency

SerialProtocol: = \$03 // Shows EnDat protocol is programmed into IC

For example, for a 5.0 MHz bit transmission rate, SerialClockMDiv = (25 / 5) - 1 = 4 (\$04) and Acc84E[i].SerialEncCtrl is set to \$040803 for triggering on the rising edge of phase clock without delay.

| Hex Digit (\$) |    |    | 0  |    |    |    | 4  |    |    |    | 0  |    |    |    | 8  |    |    |    | 0  |    |    |    | 3 |   | -   | -   |

|----------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|-----|-----|

| Script Bit #   | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1 | 0 | ı   | -   |

| C Bit #        | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7-4 | 3-0 |

| Bit Value      | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 1  | -  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1 | 1 | -   | -   |

Component: SerialClockMDiv SerialClockNDiv DS -- TC TE SerialTrigDelay SerialProtocol

| The following table lists a few common S | Serial clock frequency | v settings used wit | h EnDat2.1/2.2 protocol: |

|------------------------------------------|------------------------|---------------------|--------------------------|

|                                          |                        |                     |                          |

| SerialClockMDiv | SerialClockNDiv | Serial Clock Freq. | Bit Transmission Freq. |

|-----------------|-----------------|--------------------|------------------------|

| 1 (\$01)        | 0 (\$0)         | 50.0 MHz           | 12.5 MHz               |

| 2 (\$02)        | 0 (\$0)         | 33.33 MHz          | 8.33 MHz               |

| 3 (\$03)        | 0 (\$0)         | 25.0 MHz           | 6.25 MHz               |

| 4 (\$04)        | 0 (\$0)         | 20.0 MHz           | 5.0 MHz                |

| 5 (\$05)        | 0 (\$0)         | 16.66 MHz          | 4.16 MHz               |

## Yaskawa Sigma II/III/V Protocol

The following list shows typical settings of Acc84E[i].SerialEncCtrl for a Yaskawa II/III/V encoder.

```

SerialClockMDiv:

= 0

// 100 MHz serial clock freq. = 25x bit transmission freq.

SerialClockNDiv:

= 0

// No further division

SerialTrigClockSel:

= 0

// Use phase clock if possible

SerialTrigEdgeSel:

= 0

// Use rising clock edge if possible

SerialTrigDelay:

= 0

// Can increase from 0 if possible to reduce latency

SerialProtocol:

= $06

// Shows Yaskawa II/III/V protocol is programmed

```

For example, for the standard 4.0 MHz bit transmission rate, a 100 MHz serial clock frequency is used, and **Acc84E**[*i*].**SerialEncCtrl** is set to \$000006 for triggering on the rising edge of phase clock without delay.

| Hex Digit (\$) | 1  |    | 0     |      | Ì   |    | 0  |       | ĺ     |      | 0   |    | ĺ  |    | 0    |       |       |      | 0  |      |      |       | 6  |   | _   | _   |

|----------------|----|----|-------|------|-----|----|----|-------|-------|------|-----|----|----|----|------|-------|-------|------|----|------|------|-------|----|---|-----|-----|

| Script Bit #   | 23 | 22 | 21    | 20   | 19  | 18 | 17 | 16    | 15    | 14   | 13  | 12 | 11 | 10 | 9    | 8     | 7     | 6    | 5  | 4    | 3    | 2     | 1  | 0 | -   | -   |

| C Bit #        | 31 | 30 | 29    | 28   | 27  | 26 | 25 | 24    | 23    | 22   | 21  | 20 | 19 | 18 | 17   | 16    | 15    | 14   | 13 | 12   | 11   | 10    | 9  | 8 | 7-4 | 3-0 |

| Bit Value      | 0  | 0  | 0     | 0    | 0   | 0  | 0  | 0     | 0     | 0    | 0   | 0  | -  | -  | 0    | 0     | 0     | 0    | 0  | 0    | 0    | 1     | 1  | 0 | -   | -   |

| Component:     | •  | S  | erial | Cloc | kML |    |    | Serie | alCle | ockN | Div |    |    | TC | TE . | Serio | ılTri | gDel | av | Seri | alPr | otoci | ol |   |     |     |

The following table lists the only Serial clock frequency setting used with Yaskawa Sigma II/III/V protocol:

| SerialClockMDiv | Serial Clock NDiv | Serial Clock Frequency |

|-----------------|-------------------|------------------------|

| 0 (\$00)        | 0 (\$0)           | 100.0 MHz              |

Yaskawa Sigma II/III/V transmission of position data requires a minimum transfer time of  $62.5~\mu sec$ . It is important to choose trigger clock and trigger edge to ensure complete transmission of data each cycle before its use by the controller.

#### Tamagawa Protocol

The following list shows typical settings of **Acc84E**[i].**SerialEncCtrl** for a Tamagawa FA-Coder serial encoder. The serial clock frequency is set 20 times higher than the external clock frequency, which is the bit transmission frequency  $f_{bit}$ , to permit oversampling of the input signal.

**Serial Clock MDiv**: =  $(5/f_{bit}) - 1$  // Serial clock freq. = 20x bit transmission freq.

*SerialClockNDiv*: = 0 // No further division

SerialTrigClockSel: = 0 // Use phase clock if possible SerialTrigEdgeSel: = 0 // Use rising clock edge if possible

SerialTrigDelay: = 0 // Can increase from 0 if possible to reduce latency SerialProtocol: = \$07 // Shows Tamagawa protocol is programmed into IC

For example, for a 2.5 MHz bit transmission rate, SerialClockMDiv = (5 / 2.5) - 1 = 1 (\$01) and Acc84E[i].SerialEncCtrl is set to \$010007 for triggering on the rising edge of phase clock without delay.

| Hex Digit (\$) |    |    |       |       |      |     |    |    |    |      | 0     |       |      | _  | 0    |      |      | _  | 0  |    | _  |    | 7 |   | -   | -   |

|----------------|----|----|-------|-------|------|-----|----|----|----|------|-------|-------|------|----|------|------|------|----|----|----|----|----|---|---|-----|-----|

| Script Bit #   | 23 | 22 | 21    | 20    | 19   | 18  | 17 | 16 | 15 | 14   | 13    | 12    | 11   | 10 | 9    | 8    | 7    | 6  | 5  | 4  | 3  | 2  | 1 | 0 | -   | -   |

| C Bit #        | 31 | 30 | 29    | 28    | 27   | 26  | 25 | 24 | 23 | 22   | 21    | 20    | 19   | 18 | 17   | 16   | 15   | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7-4 | 3-0 |

| Bit Value      | 0  | 0  | 0     | 0     | 0    | 0   | 0  | 1  | 0  | 0    | 0     | 0     | -    | -  | 0    | 0    | 0    | 0  | 0  | 0  | 0  | 1  | 1 | 1 | -   | -   |

| Component:     |    |    | Serio | alCle | ockN | Div |    |    | TC | TE : | Serio | ılTri | gDel | ay | Seri | alPr | otoc | ol |    |    |    |    |   |   |     |     |

The following table lists the only Serial clock frequency setting used with Tamagawa protocol:

| SerialClockMDiv | SerialClockNDiv | Serial Clock Frequency |

|-----------------|-----------------|------------------------|

| 1 (\$01)        | 0 (\$0)         | 50.0 MHz               |

#### Panasonic Protocol

The following list shows typical settings of **Acc84E**[i].**SerialEncCtrl** for a Panasonic encoder. The serial clock frequency is set 20 times higher than the external clock frequency, which is the bit transmission frequency  $f_{bit}$ , to permit oversampling of the input signal.

SerialClockMDiv: $= (5/f_{bit}) - 1$ // Serial clock freq. = 20x bit transmission freq.SerialClockNDiv:= 0// No further divisionSerialTrigClockSel:= 0// Use phase clock if possibleSerialTrigEdgeSel:= 0// Use rising clock edge if possible

SerialTrigEdgeSel:= 0// Use rising clock edge if possibleSerialTrigDelay:= 0// Can increase from 0 if possible to reduce latencySerialProtocol:= \$09// Shows Panasonic protocol is programmed into IC

For example, for a 2.5 MHz bit transmission rate, SerialClockMDiv = (5 / 2.5) - 1 = 1 (\$01) and Acc84E[i].SerialEncCtrl is set to \$010008 for triggering on the rising edge of phase clock without delay.

| Hex Digit (\$) |    |    | 0     |       |      |     | 1  |    |    |      | 0     |       |      |     | 0    |      |       |    | 0  |    |    |    | 8 |   | -   | -   |

|----------------|----|----|-------|-------|------|-----|----|----|----|------|-------|-------|------|-----|------|------|-------|----|----|----|----|----|---|---|-----|-----|

| Script Bit #   | 23 | 22 | 21    | 20    | 19   | 18  | 17 | 16 | 15 | 14   | 13    | 12    | 11   | 10  | 9    | 8    | 7     | 6  | 5  | 4  | 3  | 2  | 1 | 0 | -   | -   |

| C Bit #        | 31 | 30 | 29    | 28    | 27   | 26  | 25 | 24 | 23 | 22   | 21    | 20    | 19   | 18  | 17   | 16   | 15    | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7-4 | 3-0 |

| Bit Value      | 0  | 0  | 0     | 0     | 0    | 0   | 0  | 1  | 0  | 0    | 0     | 0     | -    | -   | 0    | 0    | 0     | 0  | 0  | 0  | 1  | 0  | 0 | 0 | -   | -   |

| Component:     |    |    | Serio | alCle | ockN | Div |    |    | TC | TE : | Serio | ılTri | gDel | lay | Seri | alPr | otoce | ol |    |    |    |    |   |   |     |     |

The following table lists the only Serial clock frequency setting used with Panasonic protocol:

| SerialClockMDiv | SerialClockNDiv | Serial Clock Frequency |

|-----------------|-----------------|------------------------|

| 1 (\$01)        | 0 (\$0)         | 50.0 MHz               |

#### Mitutoyo Protocol

The following list shows typical settings of Acc84E[i].SerialEncCtrl for a Mitutoyo serial encoder. The serial clock frequency is set 20 times higher than the external clock frequency, which is the bit transmission frequency  $f_{bit}$ , to permit oversampling of the input signal.

// Serial clock freq. = 20x bit transmission freq. SerialClockMDiv:  $= (5 / f_{bit}) - 1$

SerialClockNDiv: = 0// No further division

SerialTrigClockSel: = 0// Use phase clock if possible SerialTrigEdgeSel: = 0// Use rising clock edge if possible

SerialTrigDelay: = 0// Can increase from 0 if possible to reduce latency SerialProtocol: = \$09 // Shows Mitutoyo protocol is programmed into IC

For example, for a 2.5 MHz bit transmission rate, *SerialClockMDiv* = (5 / 2.5) - 1 = 1 (\$01) and **Acc84E**[i].**SerialEncCtrl** is set to \$010009 for triggering on the rising edge of phase clock without delay.

| ١ | Hex Digit (\$) |    |    | 0     |      |     |     | 1  |    |       |       | 0    |     |    |    | 0  |      |       |       | 0    |    |      |      | 9     |    | -   | -   |

|---|----------------|----|----|-------|------|-----|-----|----|----|-------|-------|------|-----|----|----|----|------|-------|-------|------|----|------|------|-------|----|-----|-----|

| ſ | Script Bit #   | 23 | 22 | 21    | 20   | 19  | 18  | 17 | 16 | 15    | 14    | 13   | 12  | 11 | 10 | 9  | 8    | 7     | 6     | 5    | 4  | 3    | 2    | 1     | 0  | -   | -   |

| ſ | C Bit #        | 31 | 30 | 29    | 28   | 27  | 26  | 25 | 24 | 23    | 22    | 21   | 20  | 19 | 18 | 17 | 16   | 15    | 14    | 13   | 12 | 11   | 10   | 9     | 8  | 7-4 | 3-0 |

| ſ | Bit Value      | 0  | 0  | 0     | 0    | 0   | 0   | 0  | 1  | 0     | 0     | 0    | 0   | -  | -  | 0  | 0    | 0     | 0     | 0    | 0  | 1    | 0    | 0     | 1  | -   | -   |

|   | Component:     |    | S  | erial | Cloc | kML | )iv |    |    | Serio | alCle | ockN | Div |    |    | TC | TE I | Serio | ılTri | gDel | ay | Seri | alPr | otoce | ol |     |     |

The following table lists the only Serial clock frequency setting used with Mitutoyo protocol:

| SerialClockMDiv | SerialClockNDiv | Serial Clock Frequency |

|-----------------|-----------------|------------------------|

| 1 (\$01)        | 0 (\$0)         | 50.0 MHz               |

#### BiSS B/C (Unidirectional) Protocol

The following list shows typical settings of **Acc84E**[*i*].**SerialEncCtrl** for a BiSS B or BiSS C (unidirectional) encoder.

```

SerialClockMDiv:

= (100 / f_{bit}) - 1 // Serial clock frequency = bit transmission frequency

SerialClockNDiv:

// No further division unless f < 400 \text{ kHz}

= 0

SerialTrigClockSel:

// Use phase clock if possible

= 0

SerialTrigEdgeSel:

// Use rising clock edge if possible

=0

SerialTrigDelay:

=0

// Can increase from 0 if possible to reduce latency

SerialProtocol:

= $0B

// Shows BiSS protocol is programmed into IC

```

For example, for a 1.0 MHz bit transmission rate, SerialClockMDiv = (100 / 1.0) - 1 = 99 (\$63) and Acc84E[i].SerialEncCtrl is set to \$63000B for triggering on the rising edge of phase clock without delay.

| Hex Digit (\$) | l  |    | 6     |      | l   |     | 3  |    | l     |               | 0    |     | l  |    | 0  |      |       |            | 0    |    |      |       | В     |     | -   | l- I |

|----------------|----|----|-------|------|-----|-----|----|----|-------|---------------|------|-----|----|----|----|------|-------|------------|------|----|------|-------|-------|-----|-----|------|

| Script Bit #   | 23 | 22 | 21    | 20   | 19  | 18  | 17 | 16 | 15    | 14            | 13   | 12  | 11 | 10 | 9  | 8    | 7     | 6          | 5    | 4  | 3    | 2     | 1     | 0   | _   | -    |

| C Bit #        | 31 | 30 | 29    | 28   | 27  | 26  | 25 | 24 | 23    | 22            | 21   | 20  | 19 | 18 | 17 | 16   | 15    | 14         | 13   | 12 | 11   | 10    | 9     | 8   | 7-4 | 3-0  |

| Bit Value      | 0  | 1  | 1     | 0    | 0   | 0   | 1  | 1  | 0     | 0             | 0    | 0   | -  | -  | 0  | 0    | 0     | 0          | 0    | 0  | 1    | 0     | 1     | 1   | -   | -    |

| Component:     |    | S  | erial | Cloc | kMI | )iv |    |    | Serie | $alCl_{\ell}$ | nckN | Div |    |    | TC | TF . | Serie | $_{il}Tri$ | oDel | av | Seri | alPre | otoci | ol. |     |      |

The following table lists a few common Serial clock frequency settings used with BiSS B/C protocol:

| SerialClockMDiv | Serial Clock NDiv | Serial Clock Frequency |

|-----------------|-------------------|------------------------|

| 24 (\$18)       | 0 (\$0)           | 4.0 MHz                |

| 99 (\$63)       | 0 (\$0)           | 1.0 MHz                |

| 99 (\$63)       | 1 (\$1)           | 500.0 kHz              |

| 99 (\$63)       | 2 (\$2)           | 250.0 kHz              |

#### Matsushita Protocol

The following list shows typical settings of **Acc84E**[i].**SerialEncCtrl** for a Matsushita serial encoder. The serial clock frequency is set 20 times higher than the external clock frequency, which is the bit transmission frequency  $f_{bit}$ , to permit oversampling of the input signal.

SerialClockMDiv: // Serial clock freq. = 20x bit transmission freq.  $= (5 / f_{bit}) - 1$ SerialClockNDiv: = 0// No further division SerialTrigClockSel: = 0// Use phase clock if possible SerialTrigEdgeSel: = 0// Use rising clock edge if possible SerialTrigDelay: = 0// Can increase from 0 if possible to reduce latency SerialProtocol: = \$0C // Shows Matsushita protocol is programmed into IC

For example, for a 2.5 MHz bit transmission rate, SerialClockMDiv = (5 / 2.5) - 1 = 1 (\$01) and Acc84E[i].SerialEncCtrl is set to \$01000C for triggering on the rising edge of phase clock without delay.

| <br>2          |    |    |       |      |     |     |    |    |       |       |      |     |    |    |    |      |       |       |      |    |      |       |       |     |     |     |

|----------------|----|----|-------|------|-----|-----|----|----|-------|-------|------|-----|----|----|----|------|-------|-------|------|----|------|-------|-------|-----|-----|-----|

| Hex Digit (\$) |    |    | 0     |      |     |     | 1  |    |       |       | 0    |     |    |    | 0  |      |       |       | 0    |    |      |       | C     |     | -   | -   |

| Script Bit #   | 23 | 22 | 21    | 20   | 19  | 18  | 17 | 16 | 15    | 14    | 13   | 12  | 11 | 10 | 9  | 8    | 7     | 6     | 5    | 4  | 3    | 2     | 1     | 0   | -   | -   |

| C Bit #        | 31 | 30 | 29    | 28   | 27  | 26  | 25 | 24 | 23    | 22    | 21   | 20  | 19 | 18 | 17 | 16   | 15    | 14    | 13   | 12 | 11   | 10    | 9     | 8   | 7-4 | 3-0 |

| Bit Value      | 0  | 0  | 0     | 0    | 0   | 0   | 0  | 1  | 0     | 0     | 0    | 0   | -  | -  | 0  | 0    | 0     | 0     | 0    | 0  | 1    | 1     | 0     | 0   | -   | -   |

| Component:     |    | S  | erial | Cloc | kMT | )iv |    |    | Serie | alCli | ackN | Div |    |    | TC | TF . | Serie | ılTri | σDel | av | Seri | alPri | otoci | ol. |     |     |

The following table lists the only Serial clock frequency setting used with Matsushita protocol:

| Serial Clock MDiv | Serial Clock NDiv | Serial Clock Frequency |

|-------------------|-------------------|------------------------|

| 1 (\$01)          | 0 (\$0)           | 50.0 MHz               |

### Mitsubishi Protocol

The following list shows typical settings of **Acc84E**[i].**SerialEncCtrl** for a Mitsubishi serial encoder. The serial clock frequency is set 20 times higher than the external clock frequency, which is the bit transmission frequency  $f_{bit}$ , to permit oversampling of the input signal.

// Serial clock freq. = 20x bit transmission freq. SerialClockMDiv:  $= (5 / f_{bit}) - 1$ SerialClockNDiv: = 0// No further division SerialTrigClockSel: = 0// Use phase clock if possible SerialTrigEdgeSel: = 0// Use rising clock edge if possible SerialTrigDelay: = 0// Can increase from 0 if possible to reduce latency SerialProtocol: = \$0D// Shows Mitsubishi protocol is programmed into IC

For example, for a 2.5 MHz bit transmission rate, SerialClockMDiv = (5 / 2.5) - 1 = 1 (\$01) and Acc84E[i].SerialEncCtrl is set to \$01000D for triggering on the rising edge of phase clock without delay.

| Hex Digit (\$) |    |    | 0     |      |     |     | 1  |    |      |      | 0    |     |    |    | 0  |      |       |      | 0    |    |      |      | D     |            | -   | -   |

|----------------|----|----|-------|------|-----|-----|----|----|------|------|------|-----|----|----|----|------|-------|------|------|----|------|------|-------|------------|-----|-----|

| Script Bit #   | 23 | 22 | 21    | 20   | 19  | 18  | 17 | 16 | 15   | 14   | 13   | 12  | 11 | 10 | 9  | 8    | 7     | 6    | 5    | 4  | 3    | 2    | 1     | 0          | -   | -   |

| C Bit #        | 31 | 30 | 29    | 28   | 27  | 26  | 25 | 24 | 23   | 22   | 21   | 20  | 19 | 18 | 17 | 16   | 15    | 14   | 13   | 12 | 11   | 10   | 9     | 8          | 7-4 | 3-0 |

| Bit Value      | 0  | 0  | 0     | 0    | 0   | 0   | 0  | 1  | 0    | 0    | 0    | 0   | -  | -  | 0  | 0    | 0     | 0    | 0    | 0  | 1    | 1    | 0     | 1          | -   | -   |

| Component:     | •  | S  | orial | Clac | LMI | )iv |    |    | Sori | alCl | ackN | Div |    |    | TC | TF . | Serie | 1Tri | aDel | av | Sori | alPr | otoci | $\alpha I$ |     |     |

The following table lists the only Serial clock frequency setting used with Mitsubishi protocol:

| SerialClockMDiv | Serial Clock ND iv | Serial Clock Frequency |

|-----------------|--------------------|------------------------|

| 1 (\$01)        | 0 (\$0)            | 50.0 MHz               |

Mitsubishi Serial Encoder on HG-□ type servo motors can only be queried at 55.5µsec±1.0µsec (18 kHz), 111µsec±1.0µsec (9 kHz) and 222µsec±1.0µsec (4.5 kHz). If the request cycle is other than the above cycles the data will not be latched properly.

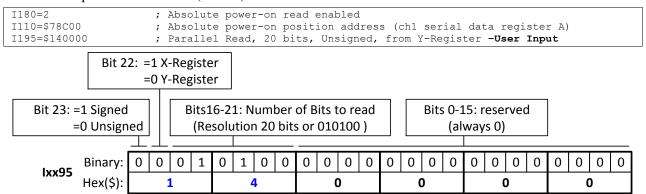

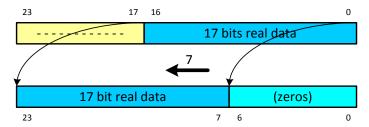

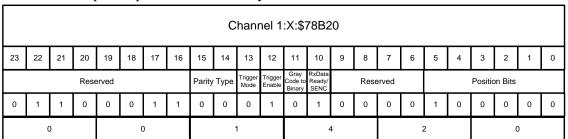

## **Single-Channel Setup Element**

Each channel of the FPGA has a 24-bit saved setup element **Acc84E**[*i*].**Chan**[*j*].**SerialEncCmd** (saved element in Power PMAC only and non-saved in Turbo PMAC) that specifies exactly how the channel's serial encoder interface will operate, given the protocol, trigger timing, and frequency specified by the multi-channel element. It has multiple components that specify different aspects of this interface. Not all components are used in every protocol.

| Power PMAC                      | Turbo PAMC   |           | Cha       | nnel      |           |

|---------------------------------|--------------|-----------|-----------|-----------|-----------|

| Channel Control Register        | Base Address | 1 (j=0)   | 2 (j=1)   | 3 (j=2)   | 4 (j=3)   |

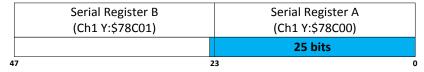

| ACC84E[0].Chan[j].SerialEncCmd  | \$78C00      | Y:\$78C00 | Y:\$78C04 | Y:\$78C08 | Y:\$78C0C |

| ACC84E[4].Chan[j].SerialEncCmd  | \$79C00      | Y:\$79C00 | Y:\$79C04 | Y:\$79C08 | Y:\$79C0C |

| ACC84E[8].Chan[j].SerialEncCmd  | \$7AC00      | Y:\$7AC00 | Y:\$7AC04 | Y:\$7AC08 | Y:\$7AC0C |

| ACC84E[12].Chan[j].SerialEncCmd | \$7BC00      | Y:\$7BC00 | Y:\$7BC04 | Y:\$7BC08 | Y:\$7BC0C |

| ACC84E[1].Chan[j].SerialEncCmd  | \$78D00      | Y:\$78D00 | Y:\$78D04 | Y:\$78D08 | Y:\$78D0C |

| ACC84E[5].Chan[j].SerialEncCmd  | \$79D00      | Y:\$79D00 | Y:\$79D04 | Y:\$79D08 | Y:\$79D0C |

| ACC84E[9].Chan[j].SerialEncCmd  | \$7AD00      | Y:\$7AD00 | Y:\$7AD04 | Y:\$7AD08 | Y:\$7AD0C |

| ACC84E[13].Chan[j].SerialEncCmd | \$7BD00      | Y:\$7BD00 | Y:\$7BD04 | Y:\$7BD08 | Y:\$7BD0C |

| ACC84E[2].Chan[j].SerialEncCmd  | \$78E00      | Y:\$78E00 | Y:\$78E04 | Y:\$78E08 | Y:\$78E0C |

| ACC84E[6].Chan[j].SerialEncCmd  | \$79E00      | Y:\$79E00 | Y:\$79E04 | Y:\$79E08 | Y:\$79E0C |

| ACC84E[10].Chan[j].SerialEncCmd | \$7AE00      | Y:\$7AE00 | Y:\$7AE04 | Y:\$7AE08 | Y:\$7AE0C |

| ACC84E[14].Chan[j].SerialEncCmd | \$7BE00      | Y:\$7BE00 | Y:\$7BE04 | Y:\$7BE08 | Y:\$7BE0C |

**Acc84E**[*i*].**Chan**[*j*].**SerialEncCmd** is comprised of the following components. These components cannot be accessed as independent data structure elements, so the value of the element must be "built up" from the value of the individual components.

| Component           | Script<br>Bits | Hex<br>Digit # | C<br>Bits | Functionality                                  |

|---------------------|----------------|----------------|-----------|------------------------------------------------|

| SerialEncCmdWord    | 23 – 16        | 1 – 2          | 31 – 24   | Serial encoder output command                  |

| SerialEncParity     | 15 – 14        | 3              | 23 – 22   | Serial encoder parity type                     |

| SerialEncTrigMode   | 13             | 3              | 21        | Serial trigger mode: continuous or one-shot    |

| SerialEncTrigEna    | 12             | 3              | 20        | Serial trigger enable                          |

| SerialEncGtoB       | 11             | 4              | 19        | Serial SSI data Gray-to-binary convert control |

| SerialEncEna/       | 10             | 4              | 18        | Serial encoder circuitry enable (write)        |

| SerialEncDataReady  |                |                |           | Serial encoder received data ready (read)      |

| SerialEncStatusBits | 09 – 06        | 4 – 5          | 17 – 14   | Serial encoder SPI number of status bits       |

| SerialEncNumBits    | 05 – 00        | 5 – 6          | 13 – 08   | Serial encoder bit length control              |

The full element can be viewed in the following format. In the Script environment (Both in Turbo and Power PMAC), it is accessed as a 24-bit element. In the C environment (Only in Power PMAC), it is accessed as a 32-bit element with the real data in the high 24 bits.

| Hex Digit (\$) |    |    |       |      |     |      |    |    |    |      |    |    |    |     |    |     |     |    |    |    |     |      |   |   | -   | -   |

|----------------|----|----|-------|------|-----|------|----|----|----|------|----|----|----|-----|----|-----|-----|----|----|----|-----|------|---|---|-----|-----|

| Script Bit #   | 23 | 22 | 21    | 20   | 19  | 18   | 17 | 16 | 15 | 14   | 13 | 12 | 11 | 10  | 9  | 8   | 7   | 6  | 5  | 4  | 3   | 2    | 1 | 0 | -   | -   |

| C Bit #        | 31 | 30 | 29    | 28   | 27  | 26   | 25 | 24 | 23 | 22   | 21 | 20 | 19 | 18  | 17 | 16  | 15  | 14 | 13 | 12 | 11  | 10   | 9 | 8 | 7-4 | 3-0 |

| Bit Value      |    |    |       |      |     |      |    |    |    |      |    |    |    |     | -  |     |     |    |    |    |     |      |   |   | -   | -   |

| Component:     |    | S  | erial | Ence | Cmd | Word | 1  |    | Pa | ritv | TM | TE | GB | Ena |    | Sta | tus |    |    |    | Num | Rits |   |   |     |     |

This section provides information about

**Acc84E**[*i*].**Chan**[*j*].**SerialEncCmd** that is common to all protocols. . For more detailed and protocol-specific information, refer to the corresponding section of the manual.

The 8-bit component *SerialEncCmdWord* is used to define a command value sent to the serial encoder in a protocol-specific manner. This value can be changed during an application for different functionality, such as resetting an encoder. Not all protocols require a command value.

The 2-bit component *SerialEncParity* defines the parity type to be expected for the received data packet (for those protocols that support parity checking). A value of 0 specifies no parity; a value of 1 specifies odd parity; a value of 2 specifies even parity. (A value of 3 is reserved for future use.)

The 1-bit component *SerialEncTrigMode* specifies whether the encoder is to be repeatedly sampled or just one time. A value of 0 specifies continuous sampling (every phase or servo cycle as set by the multichannel element **Acc84E**[*i*].**SerialEncCtrl**); a value of 1 specifies one-shot sampling.

The 1-bit component *SerialEncTrigEna* specifies whether the encoder is to be sampled or not. A value of 0 specifies no sampling; a value of 1 enables sampling of the encoder. If sampling is enabled with *SerialEncTrigMode* at 0, the encoder will be repeatedly sampled (every phase or servo cycle as set by the multi-channel element **Acc84E[i].SerialEncCtrl**) as long as *SerialEncTrigEna* is left at a value of 1. However, if sampling is enabled with *SerialEncTrigMode* at 1, the encoder will be sampled just once, and the ACC-84E's IC will automatically set *SerialEncTrigEna* back to 0 after the sampling.

The 1-bit component *SerialEncGtoB* specifies whether the data returned in SSI protocol undergoes a conversion from Gray format to numerical-binary format or not. A value of 0 specifies that no conversion is done; a value of 1 specifies that the incoming data undergoes a Gray-to-binary conversion.

The 1-bit component <code>SerialEncEna / SerialEncDataReady</code> has separate functions for writing to and reading from the register. When writing to the register, this bit represents <code>SerialEncEna</code>, which enables the driver circuitry for the serial encoder. This bit must be set to 1 to use any protocol of serial encoder on the channel. If there is an alternate use for the same signal pins, this bit must be set to 0 so the encoder drivers do not conflict with the alternate use. <code>Note that you cannot read back the value you have written to this bit!</code>

When reading from the register, you get the *SerialEncDataReady* status bit indicating the state of the serial data reception. It reports 0 during the data transmission indicating that valid new data is not yet ready. It reports 1 when all of the data has been received and processed. This is particularly important for slower interfaces that may take multiple servo cycles to complete a read; in these cases, the bit should be polled to determine when data is ready.

The 4-bit component *SerialEncStatusBits* specifies the number of status bits the interface will expect from the encoder in the SPI protocol. The valid range of settings is 0 to 12.

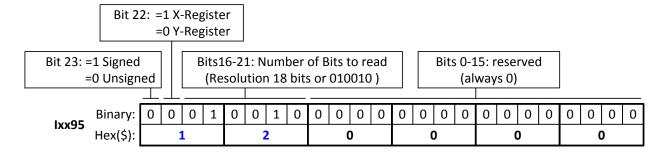

The 6-bit component SerialEncNumBits specifies the number of data bits the interface will expect from the encoder in the SSI, EnDat, or BiSS protocol. The valid range of settings for these protocols is 12-63. In other protocols, the number of bits is not specified this way, and this value does not matter, so this component is usually left at 0.

When used in the Script environment, **Acc84E**[*i*].**Chan**[*j*].**SerialEncCmd** is a 24-bit element. When used in the C environment, it is a 32-bit element, with real data in the high 24 bits, so its value in the C environment is 256 times greater than its value in the Script environment.

#### SSI Protocol

The following list shows typical settings of Acc84E[i].Chan[j].SerialEncCmd for an SSI encoder.

SerialEncCmdWord: = 0// No command word supported for SSI protocol

SerialEncParity: = ?? // Encoder-specific parity check

SerialEncTrigMode: = 0// Continuous triggering SerialEncTrigEna: // Enable triggering = 1

SerialEncGtoB: = ??// Encoder-specific data format SerialEncEna: // Enable driver circuitry = 1

// No status bits supported for SSI protocol SerialEncStatusBits: =0

SerialEncNumBits: = ??// Encoder-specific number of position bits returned

For example, for an SSI encoder with 25 position bits in Gray-code format with odd parity, Acc84E[i].Chan[j].SerialEncCmd would be set to \$005C19. (It may report back as \$005819 if the data-

ready status bit is not set.)

| Hex Digit (\$) |               |    | 0  |    |    |    | 0  |    |    |    | 5   |     |    |    | C  |    |    |    | 1  |    |     |     | 9 |   | -   | -   |

|----------------|---------------|----|----|----|----|----|----|----|----|----|-----|-----|----|----|----|----|----|----|----|----|-----|-----|---|---|-----|-----|

| Script Bit #   | 23            | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13  | 12  | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3   | 2   | 1 | 0 | -   | -   |

| C Bit #        | 31            | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21  | 20  | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11  | 10  | 9 | 8 | 7-4 | 3-0 |

| Bit Value      | -             | -  | -  | -  | -  | -  | -  | -  | 0  | 1  | 0   | 1   | 1  | 1  | -  | -  | -  | -  | 0  | 1  | 1   | 0   | 0 | 1 | -   | -   |

|                | C 1E C 1117 1 |    |    |    |    |    |    |    |    | ٠. | T14 | Tr. | OD |    |    | G. |    |    |    |    | N 7 | D., |   |   |     |     |

Component: SerialEncCmdWord Parity TM TE GB Ena Status NumBits

#### EnDat2.1/2.2 Protocol

The EnDat interface in the ACC-84E supports four 6-bit command codes that are sent directly to the encoder:

- 000111 (\$07) for reporting position (EnDat2.1)

- 101010 (\$2A) for resetting the encoder (EnDat2.1)

- 111000 (\$38) for reporting position with possible additional information (EnDat2.2)

- 101101 (\$2D) for resetting the encoder (EnDat2.2)

These 6 bits fit at the low end of the 8-bit *SerialEncCmdWord* command field of **Acc84E**[*i*].**Chan**[*j*].**SerialEncCmd**.

By the EnDat standard, EnDat2.2 encoders should be able to accept and process EnDat2.1 command codes as well. However, not all encoders sold as meeting the EnDat2.2 standard can do this.

For EnDat2.2 encoders, the ACC-84E (starting 1<sup>st</sup> quarter 2014) also supports controller requests for additional information from the encoder through the use of Memory Range Select (MRS) codes. To implement these, the *SerialEncCmdWord* command field contains the MRS code. (In this mode, the ACC-84E sends the 111000 command code – report position with additional information – to the encoder.)

The following MRS codes are supported in the EnDat2.2 standard:

- \$40 Send additional info 1 w/o data content (NOP)

- \$41 Send diagnostic values

- \$42 Send position value 2 word 1 LSB

- \$43 Send position value 2 word 2

- \$44 Send position value 2 word 3 MSB

- \$45 Acknowledge memory content LSB

- \$46 Acknowledge memory content MSB

- \$47 Acknowledge MRS code

- \$48 Acknowledge test command

- \$49 Send test value word 1 LSB

- \$4A Send test value word 2

- \$4B Send test value word 3 MSB

- \$4C Send temperature 1

- \$4D Send temperature 2

- \$4F Stop sending additional information 1

- \$50 Send additional info 2 w/o data contents (NOP)

- \$51 Send commutation

- \$52 Send acceleration

- \$53 Send commutation & acceleration

- \$54 Send limit position signals

- \$55 Send limit position signals & acceleration

- \$56 Currently not assigned

- \$5F Stop sending additional information 2

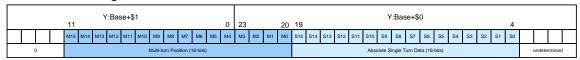

The response from the encoder to specific MRS code data requests from the encoder depends on the availability of that data in the encoder. The additional information provided from supported MRS codes will be found in status elements Acc84E[i].Chan[j].SerialEncDataC and SerialEncDataD.

The following list shows typical settings of **Acc84E**[*i*].**Chan**[*j*].**SerialEncCmd** for position reporting from an EnDat encoder.

SerialEncCmdWord: = {cmd/MRS code} // Command code

SerialEncParity: = 0 // No parity check supported for EnDat protocol

SerialEncTrigMode: = 0 // Continuous triggering (EnDat2.2)

SerialEncTrigEna: = 1 // Enable triggering

SerialEncGtoB: = 0 // No Gray code supported for EnDat protocol

SerialEncEna: = 1 // Enable driver circuitry

SerialEncStatusBits: = 0 // No status bits supported for EnDat protocol

SerialEncNumBits: = {enc spec} // Encoder-specific number of position bits returned

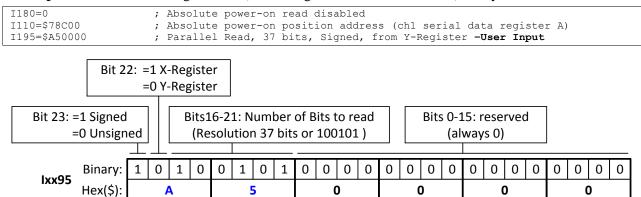

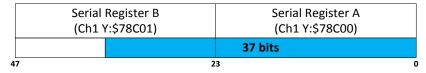

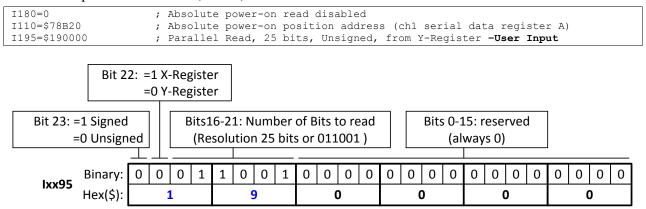

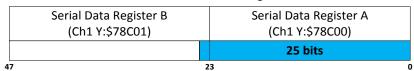

For example, for an EnDat2.2 encoder with 37 position bits, **Acc84E**[*i*].**Chan**[*j*].**SerialEncCmd** would be set to \$381425 for continuous position reporting. (It may report back as \$381025 if the data-ready status bit is not set.)

| l | pg           |                  |    | 3  |    |    |    | 8  |    |              |      | 1  |    |    |     | 4  |      |      |    | 2  |    |     |      | 5 |   | -   | -   |

|---|--------------|------------------|----|----|----|----|----|----|----|--------------|------|----|----|----|-----|----|------|------|----|----|----|-----|------|---|---|-----|-----|

| Ī | Script Bit # | 23               | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15           | 14   | 13 | 12 | 11 | 10  | 9  | 8    | 7    | 6  | 5  | 4  | 3   | 2    | 1 | 0 | -   | -   |

| Ī | C Bit #      | 31               | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23           | 22   | 21 | 20 | 19 | 18  | 17 | 16   | 15   | 14 | 13 | 12 | 11  | 10   | 9 | 8 | 7-4 | 3-0 |

| Ī | Bit Value    | -                | 0  | 1  | 1  | 1  | 0  | 0  | 0  | -            | -    | 0  | 1  | -  | 1   | -  | -    | -    | -  | 1  | 0  | 0   | 1    | 0 | 1 | -   | -   |

|   | Component:   | SerialFncCmdWord |    |    |    |    |    |    |    | $p_{\alpha}$ | rit, | TM | TF | GR | Ena |    | Star | fire |    |    |    | Num | Rite |   |   |     |     |

This same encoder can be reset with a command word value of 45 (\$2D) sent in one-shot mode with **Acc84E**[*i*].**Chan**[*j*].**SerialEncCmd** set to \$2D3425.

| Hex Digit (\$) |    |    | 2     |      |     |      | D  |    |     |      | 3  |    |                 |     | 4  |      |    |    | 2  |    |     |      | 5 |   | -   | -   |

|----------------|----|----|-------|------|-----|------|----|----|-----|------|----|----|-----------------|-----|----|------|----|----|----|----|-----|------|---|---|-----|-----|

| Script Bit #   | 23 | 22 | 21    | 20   | 19  | 18   | 17 | 16 | 15  | 14   | 13 | 12 | 11              | 10  | 9  | 8    | 7  | 6  | 5  | 4  | 3   | 2    | 1 | 0 | -   | -   |

| C Bit #        | 31 | 30 | 29    | 28   | 27  | 26   | 25 | 24 | 23  | 22   | 21 | 20 | 19              | 18  | 17 | 16   | 15 | 14 | 13 | 12 | 11  | 10   | 9 | 8 | 7-4 | 3-0 |

| Bit Value      | -  | 0  | 1     | 0    | 1   | 1    | 0  | 1  | -   | -    | 1  | 1  | -               | 1   | -  | -    | -  | -  | 1  | 0  | 0   | 1    | 0 | 1 | -   | -   |

| Component:     |    | S  | erial | Enc( | Cmd | Word | 1  |    | Pai | ritv | TM | TE | $\overline{GB}$ | Ena |    | Stat | us |    |    |    | Num | Bits |   |   |     |     |

For an EnDat2.1 encoder with 24 position bits, **Acc84E**[*i*].**Chan**[*j*].**SerialEncCmd** would be set to \$073418 for one-shot position reporting (at power-up). It will report back as \$073018 until the data is received.

| 1 | Hex Digit (\$) |    |    | 0     |      |     |      | 7  |    |     |      | 3  |    |    |     | 4  |      |     |    | 1  |    |     |      | 8 |   | -   | -   |

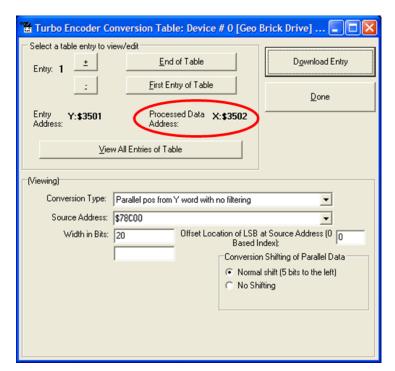

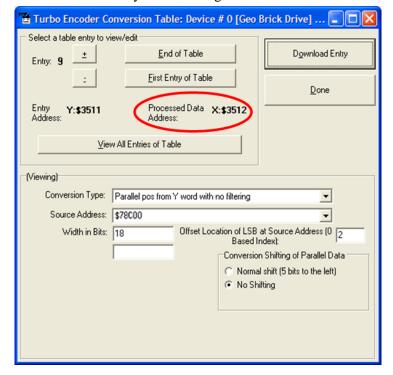

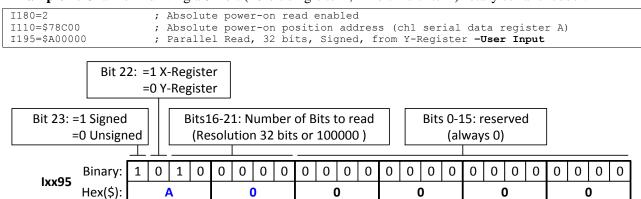

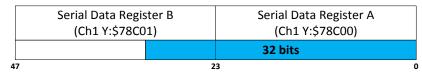

|---|----------------|----|----|-------|------|-----|------|----|----|-----|------|----|----|----|-----|----|------|-----|----|----|----|-----|------|---|---|-----|-----|