| Technical<br>Information<br>Manual   |

|--------------------------------------|

| Revision n. 5<br>30 April 2007       |

|                                      |

|                                      |

|                                      |

| <b>MOD. V1495</b><br>GENERAL PURPOSE |

CAEN will repair or replace any product within the guarantee period if the Guarantor declares that the product is defective due to workmanship or materials and has not been caused by mishandling, negligence on behalf of the User, accident or any abnormal conditions or operations.

CAEN declines all responsibility for damages or injuries caused by an improper use of the Modules due to negligence on behalf of the User. It is strongly recommended to read thoroughly the CAEN User's Manual before any kind of operation.

CAEN reserves the right to change partially or entirely the contents of this Manual at any time and without giving any notice.

# **Disposal of the Product**

The product must never be dumped in the Municipal Waste. Please check your local regulations for disposal of electronics products.

# TABLE OF CONTENTS

| 1. | GE                  | ENERAL DESCRIPTION              |    |

|----|---------------------|---------------------------------|----|

|    | 1.1.                | Overview                        | 6  |

|    | 1.2.                | BLOCK DIAGRAM                   |    |

|    |                     |                                 |    |

| 2. | TE                  | CCHNICAL SPECIFICATIONS         |    |

| 2  | 2.1.                | PACKAGING                       | 8  |

| 2  | 2.2.                | Power requirements              | 8  |

| 2  | 2.3.                | FRONT PANEL DISPLAYS            | 8  |

| 2  | 2.4.                | FRONT PANEL                     | 9  |

| 2  | 2.5.                | MOTHERBOARD SPECIFICATIONS      | 10 |

| 2  | 2.6.                | MEZZANINE SPECIFICATIONS        | 10 |

| 2  | 2.7.                | MEZZANINE BOARDS INSTALLATION   | 11 |

| 2  | 2.8.                | FRONT PANEL CONNECTOR CABLING   | 11 |

| 3. | OP                  | PERATING MODES                  | 13 |

|    |                     |                                 |    |

| •  | 3.1.<br><i>3.1.</i> | TIMERS                          |    |

|    | 3.1.                |                                 |    |

|    | 3.2.                | FPGA PROGRAMMING                |    |

|    | 3.2.<br>3.2.        |                                 |    |

|    | ¥73.                | AL INVERDED OF                  | 11 |

| 4. | VIV                 | ME INTERFACE                    | T  |

| 4  | 4.1.                | REGISTER ADDRESS MAP            |    |

|    | 4.1.                | 7 0                             |    |

|    | 4.2.                | CONTROL REGISTER                |    |

|    | 4.3.                | STATUS REGISTER                 |    |

|    | 4.4.                | INTERRUPT LEVEL REGISTER        |    |

|    | 4.5.                | INTERRUPT STATUS-ID REGISTER    |    |

|    | 4.6.                | GEO Address Register            |    |

|    | 4.7.                | Module Reset Register           |    |

|    | 4.8.                | FIRMWARE REVISION REGISTER      |    |

|    | 4.9.                | SCRATCH16 REGISTER              |    |

|    | 4.10.               | SCRATCH32 REGISTER              |    |

|    | 4.11.               | SELECT VME FPGA FLASH REGISTER  |    |

| 4  | 4.12.               | SELECT USER FPGA FLASH REGISTER | 20 |

| 4  | 4.13.               | VME FPGA FLASH MEMORY           | 20 |

| 4.14.      | USER FPGA FLASH MEMORY                                       | 20 |

|------------|--------------------------------------------------------------|----|

| 4.15.      | USER FPGA CONFIGURATION REGISTER                             | 21 |

| 5. V1      | 495 USER FPGA REFERENCE DESIGN KIT                           | 22 |

| 5.1.       | Introduction                                                 | 22 |

| 5.2.       | DESIGN KIT                                                   |    |

| 5.2        |                                                              |    |

| 5.2        | .2. COIN_REFERENCE Design                                    | 23 |

| 5.3.       | INTERFACE DESCRIPTION                                        |    |

| 5.3        |                                                              |    |

| 5.3<br>5.3 |                                                              |    |

| 5.3        |                                                              |    |

| 5.3        | , ,                                                          |    |

| 5.3<br>5.3 | <b>&gt;</b>                                                  |    |

| 5.3        | · ·                                                          |    |

| 5.4.       | REFERENCE DESIGN DESCRIPTION                                 | 27 |

| 5.5.       | REGISTER DETAILED DESCRIPTION                                | 31 |

| 5.5        | 0 ( , , , , ,                                                |    |

| 5.5<br>5.5 | 0 ( , , , ,                                                  |    |

| 5.5<br>5.5 | •                                                            |    |

| 5.5        | 5. Delay Unit using PDLs                                     | 34 |

| 5.5        |                                                              |    |

| 5.6.       | QUARTUS II WEB EDITION PROJECT                               | 36 |

| 5.7.       | Firmware upgrade                                             |    |

| 5.7<br>5.7 | - 78                                                         |    |

| 3.7        | .2. VME FFOA Opgraae                                         | 42 |

| LIST       | OF FIGURES                                                   |    |

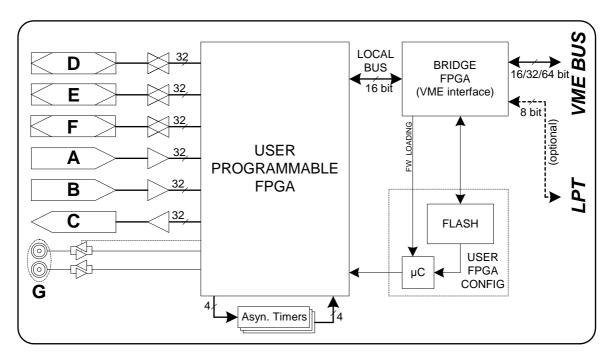

| Fig. 1.1   | : Mod. V1495 Block Diagram                                   | 7  |

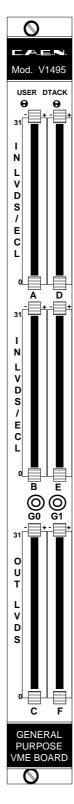

| Fig. 2.1   | : MODEL V1495 FRONT PANEL (WITH A395A/B/C PIGGY BACK BOARDS) | 9  |

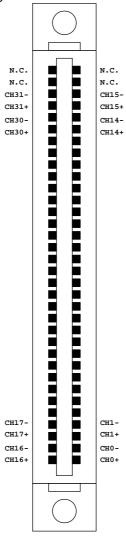

| Fig. 2.2   | : MULTIPIN CONNECTOR PIN ASSIGNMENT                          | 11 |

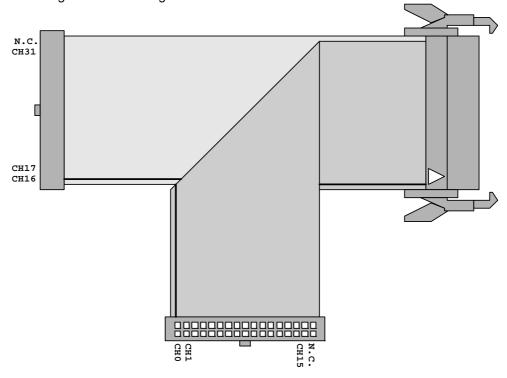

| Fig. 2.3   | : Mod. A967 Cable Adapter                                    | 12 |

| Fig. 3.1   | : TIMERS DIAGRAM                                             | 14 |

| Fig. 3.2   | : GATE PULSE EXAMPLE                                         | 14 |

| Fig. 3.3   | : TIMER2 AND TIMER3 USED TOGETHER FOR HANDLING A GATE PULSE  | 15 |

| Fig. 3.4   | : FPGA VME diagram                                           | 15 |

| Fig. 3.5   | : FPGA USER diagram                                          | 16 |

| Fig. 4.1   | : Interrupt Level Register                                   | 18 |

| Fig. 4.2   | : Interrupt Vector Register                                  | 19 |

| FIG. 4.3   | : GEOGRAPHICAL ADDRESS REGISTER                              | 19 |

| Fig. 4.4: Firmware Revision Register                           | 19 |

|----------------------------------------------------------------|----|

| Fig. 4.5: USER FPGA Configuration Register                     | 21 |

| Fig. 5.1: USER FPGA block diagram                              | 22 |

| Fig. 5.2: Front Panel Ports Interface Diagram                  | 28 |

| Fig. 5.3: PDL_CONTROL bit fields                               | 33 |

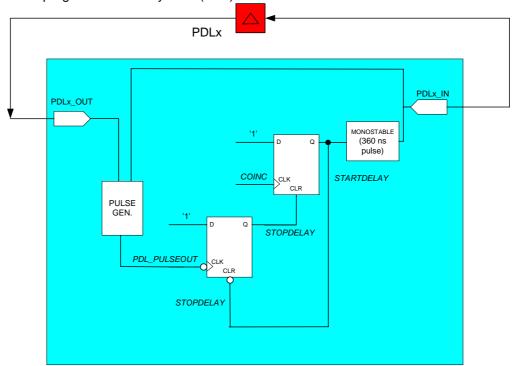

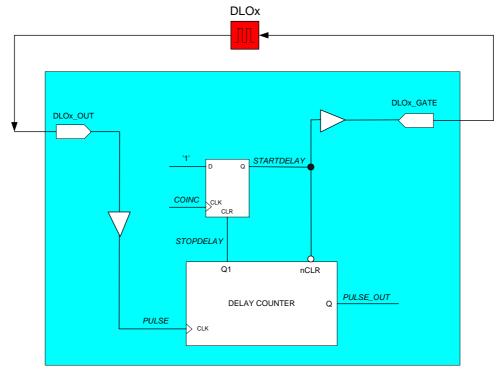

| Fig. 5.4: Delay Unit with PDLs                                 | 34 |

| Fig. 5.5: PDLs Delay line timing                               | 34 |

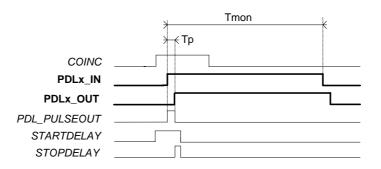

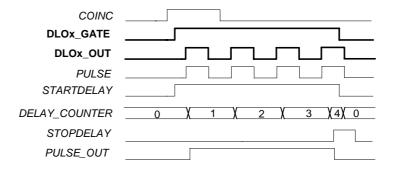

| Fig. 5.6: Delay Unit with DLOs                                 | 35 |

| Fig. 5.7: DLOs Delay line timing                               | 35 |

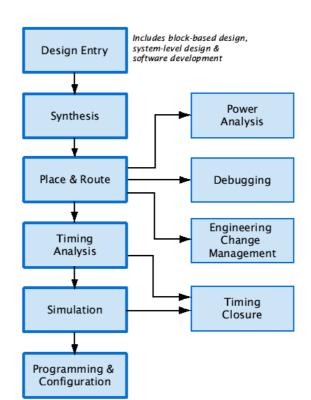

| Fig. 5.8: Quartus II project flow                              | 37 |

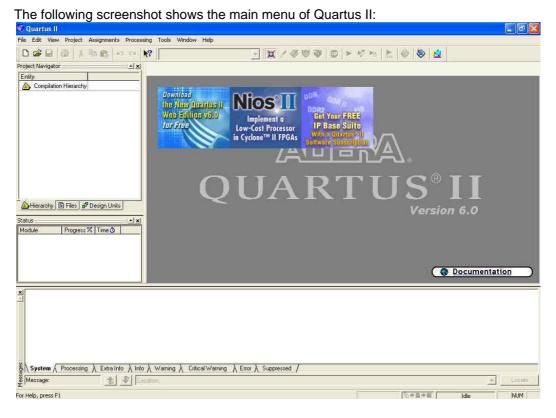

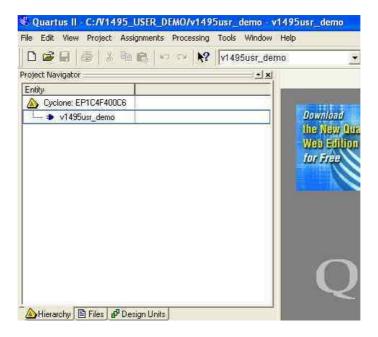

| Fig. 5.9: Quartus II main menu                                 | 37 |

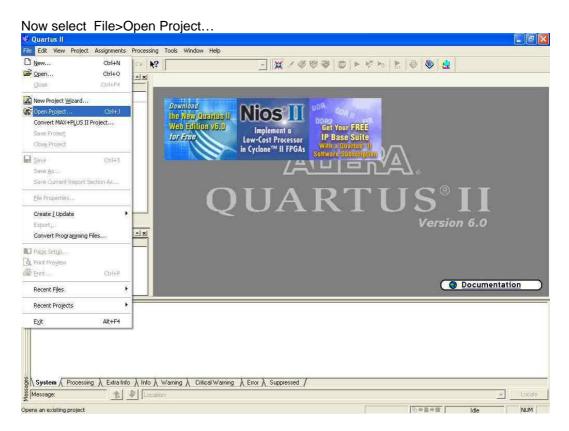

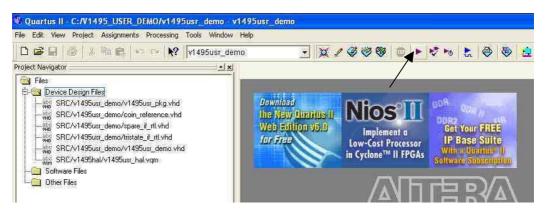

| Fig. 5.10: Quartus II file menu                                | 38 |

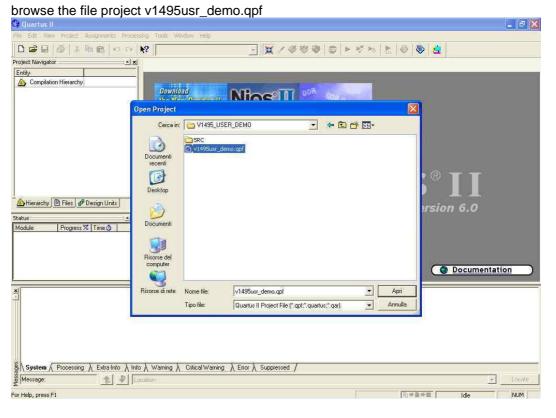

| Fig. 5.11: Quartus II project browser                          | 38 |

| Fig. 5.12: Quartus II netlist                                  | 39 |

| Fig. 5.13: Quartus II hierarchical structure                   | 40 |

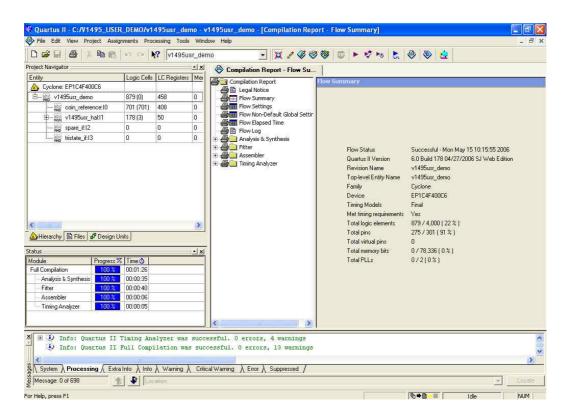

| Fig. 5.14: Quartus II compiler launching                       | 40 |

| Fig. 5.15: Quartus II compiling summary                        | 41 |

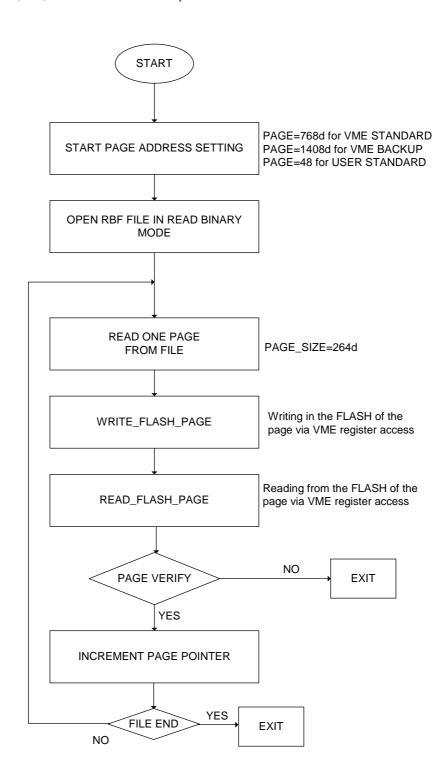

| Fig. 5.16: Flash programming algorithm flow-chart              | 43 |

| LIST OF TABLES                                                 |    |

| Table 2.1: Model V1495 and mezzanine boards power requirements | 8  |

| Table 2.2: V1495 Motherboard I/O sections                      | 10 |

| Table 2.3: V1495 Mezzanine boards                              | 10 |

| TABLE 4.1: ADDRESS MAP FOR THE MODEL V1495                     | 17 |

| TABLE 4.2: ROM ADDRESS MAP FOR THE MODEL V1495                 | 17 |

| TABLE 5.1: COIN_REFERENCE SIGNALS                              | 23 |

| Table 5.2: V1495 Mezzanine Expansion Ports signals             | 26 |

| TABLE 5.3: PDL CONFIGURATION INTERFACE SIGNALS                 | 26 |

| TABLE 5.4: DELAY LINES AND OSCILLATORS SIGNALS                 | 27 |

| TABLE 5.5: SPARE INTERFACE SIGNALS                             | 27 |

| Table 5.6: LED Interface signals                               | 27 |

| Table 5.7: COIN_REFERENCE register map                         | 29 |

| TARLE 5.8: SELECTION OF THE DELAY LINE                         | 32 |

# 1. General description

#### 1.1. **Overview**

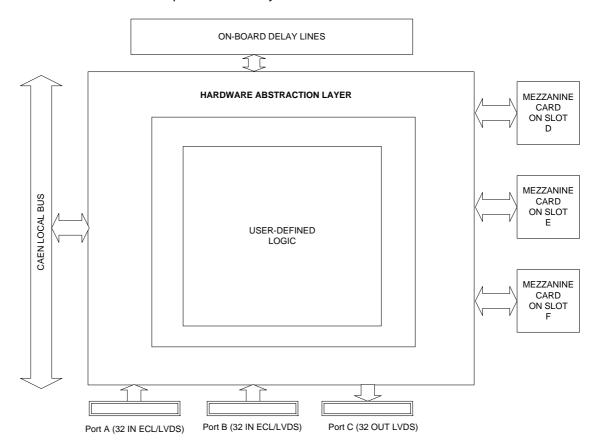

The Mod. V1495 is a VME 6U board, 1U wide, suitable for various digital Gate/Trigger/Translate/Buffer/Test applications, which can be directly customised by the User, and whose management is handled by two FPGA's:

FPGA "Bridge", which is used for the VME interface and for the connection between the VME interface and the 2nd FPGA (FPGA "User") through a proprietary local bus. FPGA "Bridge" manages also the programming via VME of the FPGA "User".

FPGA "User", which manages the front panel I/O channels. FPGA "User" is provided with a basic firmware which allows to perform coincidence matrix, I/O register and asynchronous timers functions.

FPGA "User" can be also free reprogrammed by the user with own custom logic function (see § 5.1). It is connected as slave to the FPGA "Bridge" via CAEN Local Bus, whose protocol shall be used in order to communicate with the FPGA "Bridge" and thus with the VME bus.

The I/O channel digital interface is composed by four sections (A, B, C, G) placed on the motherboard (see § 1.2). The channel interface can be expanded in the D, E, F sections by using up to 3 mezzanine boards (see § 2.6 and § 2.7), which can be added, choosing between the four types developed in order to cover the I/O functions and the ECL, PECL, LVDS, NIM, TTL electrical standard (see § 1.2). The maximum number of channels can be expanded up to 194.

The FPGA "User" can be programmed "on the fly" directly via VME, without external hardware tools, without disconnecting the board from the set up, without resetting it or turning the crate off, allowing quick debug operations by the developer with his own firmware. A flash memory on the board can store the different programming file, which can be loaded to the FPGA "User" at any moment.

Four independent digital programmable asynchronous timers are available for Gate/Trigger applications. It is possible to chain them for generating complex Gate/Trigger pulse.

# 1.2. Block Diagram

Fig. 1.1: Mod. V1495 Block Diagram

# 2. Technical specifications

## 2.1. Packaging

The module is housed in a 6U-high, 1U-wide VME unit. The board is provided the VME P1, and P2 connectors and fits into both VME standard and V430 backplanes.

## 2.2. Power requirements

The power requirements of the modules are as follows:

Table 2.1: Model V1495 and mezzanine boards power requirements

| Power supply | Mod. V1495 | Mod. A395A | Mod. A395B | Mod. A395C | Mod. A395D |

|--------------|------------|------------|------------|------------|------------|

| +5 V         | 1 A        | 0.1 A      | 0.1 A      | 1.4 A      | 1.1 A      |

# 2.3. Front panel displays

The front panel (refer to § 2.4) hosts the following LEDs:

**DTACK:** Colour: green.

Function: it lights up green whenever a VME read/write

access to the board is performed.

**USER:** Colour: green / orange / red.

Function: programmable.

# 2.4. Front Panel

**Document type:**

User's Manual (MUT)

Fig. 2.1: Model V1495 front panel (with A395A/B/C piggy back boards)

### 2.5. **Motherboard Specifications**

Title:

The Mod. V1495 Motherboard is composed by four I/O sections (see § 1.2), described in the following table:

Table 2.2: V1495 Motherboard I/O sections

| Board | No. of Ch. | Direction         | Logic                                                     | Signal                                                                                                                     | Bandwidth | Front panel connector                                        |

|-------|------------|-------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------|--------------------------------------------------------------|

| A     | 32         | Input             | Direct                                                    | LVDS/ECL/PECL (single ended TTL optional) 1100hm Rt. Extended Common Mode input range –4V to +5V; Fail Safe input feature. | 200MHz    | Robinson Nugent P50E-<br>068-P1-SR1-TG type,<br>(34+34) pins |

| В     | 32         | Input             | Direct                                                    | LVDS/ECL/PECL (single ended TTL optional) 110ohm Rt. Extended Common Mode input range -4V to +5V; Fail Safe input feature. | 200MHz    | Robinson Nugent P50E-<br>068-P1-SR1-TG type,<br>(34+34) pins |

| С     | 32         | Output            | Direct                                                    | LVDS<br>100ohm RI                                                                                                          | 250MHz    | Robinson Nugent P50E-<br>068-P1-SR1-TG type,<br>(34+34) pins |

| G     | 2          | I/O<br>selectable | TTL IN=Direct TTL OUT=Direct NIM IN=Invert NIM OUT=Direct | NIM/TTL<br>selectable<br>Open/50ohm Rt<br>selectable                                                                       | 250MHz    | LEMO 00                                                      |

### **Mezzanine Specifications** 2.6.

The four I/O Mezzanine boards developed so far are described in the following table:

Table 2.3: V1495 Mezzanine boards

| Board | No. of Ch. | Direction         | Logic                                                     | Signal                                                                                                                                                    | Bandwidth | Front panel connector                                        |

|-------|------------|-------------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------------------------------------------------------|

| A395A | 32         | Input             | Direct                                                    | LVDS/ECL/<br>PECL<br>(single ended<br>TTL optional)<br>110ohm Rt.<br>Extended<br>Common Mode<br>input range –4V<br>to +5V; Fail<br>Safe input<br>feature. | 200MHz    | Robinson Nugent P50E-<br>068-P1-SR1-TG type,<br>(34+34) pins |

| A395B | 32         | Output            | Direct                                                    | LVDS<br>100ohm RI                                                                                                                                         | 250MHz    | Robinson Nugent P50E-<br>068-P1-SR1-TG type,<br>(34+34) pins |

| A395C | 32         | Output            | Direct                                                    | ECL                                                                                                                                                       | 300MHz    | Robinson Nugent P50E-<br>068-P1-SR1-TG type,<br>(34+34) pins |

| A395D | 8          | I/O<br>selectable | TTL IN=Direct TTL OUT=Direct NIM IN=Invert NIM OUT=Direct | NIM/TTL<br>selectable<br>Open/50ohm Rt<br>selectable                                                                                                      | 250MHz    | LEMO 00                                                      |

Title:

In order to install one A395x-series mezzanine board on the V1495 motherboard it is necessary to follow these steps:

- Remove (unscrew) the metal cover (one at will)

- Plug the mezzanine board into the 100 pin connector on the motherboard

- Fix the mezzanine board with the screws

Mod. V1495 General Purpose VME Board

### **WARNING!**

If you wish to install three A395C's on the module, please contact us at: support.nuclear@caen.it

# 2.8. Front panel connector cabling

Motherboard I/O sections A, B, C and A395A, A395B and A395C Mezzanine boards feature the Robinson Nugent P50E-068-P1-SR1-TG multipin connector, whose pin set is shown in the following figure:

Fig. 2.2: Multipin connector pin assignment

The CAEN Mod. A967 Cable Adapter allows to adapt each Robinson Nugent Multipin Connector into two 1" 17+17-pin Header-type male connectors (3M, 4634-7301) with locks through two 25 cm long flat cables.

Fig. 2.3: Mod. A967 Cable Adapter

# 3. Operating modes

### 3.1. Timers

Gate/Trigger applications require the production of an output signal with programmable width (Gate), whenever an input signal (Trigger) occurs.

Gates can be produced in several ways, according to the system set up, which can be either synchronous or asynchronous.

### Synchronous systems:

Input signals are referred to a system clock: they can be sampled by the clock itself and the output is a gate signal (obtained with a counter) whose width (and delay) is a multiple of the clock period. If the application requires a width (and delay) of the Gate signal synchronous but with step resolution higher than the system clock period, this can be achieved by enabling the PLL in the USER FPGA and enter the reference clock on channel G0.

### Asynchronous systems:

Input signals are not referred to a system clock. As a consequence the gate signal will be generated without any time reference. It is possible to use the implementation described above, with the freedom of choosing the clock source between external or 40MHz internal. The resulting Gate signal will have stable duration, but with maximum position jitter equal to one clock period.

Such position jitter can be rejected by using the asynchronous timers present on the V1495, which allow to generate references synchronous with the occurred trigger.

### 3.1.1. Timer0, Timer1

Each timer is based on a programmable delay line. FPGA USER drives a STARTx pulse and, after the programmed delay, it receives the return signal PULSEx. The time difference between transmission and reception (logic implementation inside the FPGA USER) can be used to drive a gate signal. The programming of the delay time can be done manually as binary value either via 8 bit dip switches (SW4 and SW5) or via VME register, with a 1ns step resolution (max step delay = 255ns). The software setting has higher priority with respect to the dip switches.

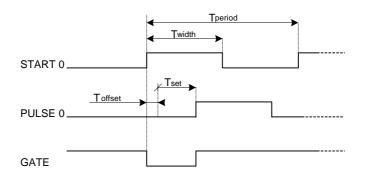

The following figure shows a diagram of the timers usage:

Title:

Mod. V1495 General Purpose VME Board

```

Tdly=Toffset + Tset

Toffset = 30 \pm 2ns

Tset = SETBINARY * 1ns

STARTx-WIDTHMIN = 320ns recommended

(22ns absolute min.)

STARTx-PERIODMIN = 640ns recommended

(46ns absolute min.)

```

Fig. 3.1: Timers diagram

The use of STARTx signals with timing shorter than those recommended is possible, although the linearity on the set delay scale is no longer guaranteed.

#### 3.1.2. Timer2, Timer3

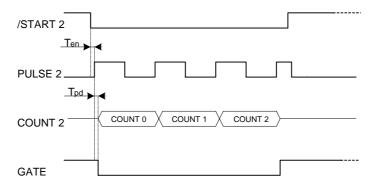

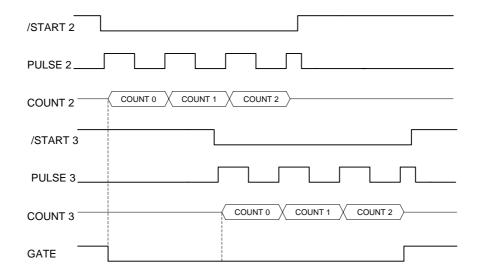

Each timer is made up of one digital circuit which produces a typical fixed time base with 10ns period and 50% duty cycle. These timers are proposed for generating any Gate pulse > 10ns with a 10ns step. The following figure shows an example of a Gate generation made with Timer2 and n.3 PULSE width.

Fig. 3.2: Gate pulse example

FPGA USER drives a /STARTx pulse and after TEN time FPGA USER will receive a PULSEx clock signal. A counter with clock = PULSEx implemented in the FPGA USER, allows to generate a pulse with programmable duration. It is possible to reduce to one half (5ns) the counter step by advancing the counter on both sides of PULSEx. Since the circuit is completely digital, no recovery time is necessary between one stop and the following start: it is thus possible to generate multiple gate pulses with very high rate. Timer2 and Timer3 can be used together for handling one single Gate pulse from multiple overlapped triggers.

**Revision:**

Fig. 3.3: Timer2 and Timer3 used together for handling a Gate pulse

### 3.2. **FPGA Programming**

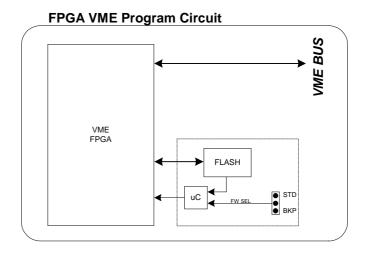

The programming of FPGA VME and FPGA USER are handled by two independent microcontrollers + flash memory. The updating of the firmware contained in the flash memories does not require the use of external tools and can be executed via VME. The flash related to FPGA VME contains the firmware dedicated to the interface of the board with the FPGA USER and the VME bus; such firmware is developed by CAEN. The flash related to the FPGA USER contains the firmware developed by the User according to his own application requirements.

#### 3.2.1. **FPGA VME**

The microcontroller provides the firmware uploading at board's power on. The flash memory contains two versions of the firmware, which can be selected manually via jumper (Standard or Backup).

Fig. 3.4: FPGA VME diagram

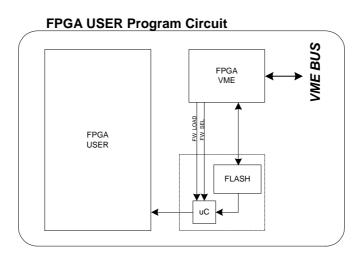

#### 3.2.2. FPGA USER

The microcontroller provides the firmware uploading at board's power on. The flash memory contains one firmware image only (Standard).

Fig. 3.5: FPGA USER diagram

FPGA VME aim is to handle the operation of FPGA USER, which can be programmed on the fly, i.e. without turning off the system, thus allowing quick debug operations by the Developer.

Register implemented on FPGA VME allows the following operations:

- FPGA USER flash memory programming.

- FPGA USER updating.

**Revision:**

# 4. VME Interface

### Register address map 4.1.

The Address map for the Model V1495 is listed in Table 4.1. All register addresses are referred to the Base Address of the board, i.e. the addresses reported in the Tables are the offsets to be added to the board Base Address.

Table 4.1: Address Map for the Model V1495

| ADDRESS               | REGISTER/CONTENT            | ADDR    | DATA | Read/Write |

|-----------------------|-----------------------------|---------|------|------------|

| Base + 0x0000÷0x7FFC  | USER FPGA Access            | A24/A32 | D16  | R/W (*)    |

| Base + 0x8000         | Control Register            | A24/A32 | D16  | R/W        |

| Base + 0x8002         | Status Register             | A24/A32 | D16  | R          |

| Base + 0x8004         | Interrupt Level             | A24/A32 | D16  | R/W        |

| Base + 0x8006         | Interrupt Status-ID         | A24/A32 | D16  | R/W        |

| Base + 0x8008         | Geo Address_Register        | A24/A32 | D16  | R          |

| Base + 0x800A         | Module Reset                | A24/A32 | D16  | W          |

| Base + 0x800C         | Firmware revision           | A24/A32 | D16  | R          |

| Base + 0x800E         | Select VME FPGA Flash(**)   | A24/A32 | D16  | R/W        |

| Base + 0x8010         | VME FPGA Flash memory(**)   | A24/A32 | D16  | R/W        |

| Base + 0x8012         | Select USER FPGA Flash(**)  | A24/A32 | D16  | R/W        |

| Base + 0x8014         | USER FPGA Flash memory(**)  | A24/A32 | D16  | R/W        |

| Base + 0x8016         | USER FPGA Configuration(**) | A24/A32 | D16  | R/W        |

| Base + 0x8018         | Scratch16                   | A24/A32 | D16  | R/W        |

| Base + 0x8020         | Scratch32                   | A24/A32 | D32  | R/W        |

| Base + 0x8100÷0x801FE | Configuration ROM(**)       | A24/A32 | D16  | R          |

<sup>(\*)</sup> Read/Write capability depends on USER FPGA implementation.

#### 4.1.1. Configuration ROM

The following registers contain some module's information according to the Table 3.2, they are D16 accessible (read only):

OUI: manufacturer identifier (IEEE OUI)

Version: purchased version **Board ID: Board identifier**

Revision: hardware revision identifier

Serial MSB: serial number (MSB) Serial LSB: serial number (LSB)

Table 4.2: ROM Address Map for the Model V1495

| Description      | Address | Content |

|------------------|---------|---------|

| checksum         | 0x8100  |         |

| checksum_length2 | 0x8104  |         |

| checksum_length1 | 0x8108  |         |

| checksum_length0 | 0x810C  |         |

Filename: Number of pages: Page: 00117/04:V1495.MUTx/05 V1495\_REV5.DOC 17

<sup>(\*\*)</sup> See § 5.7

| Description | Address | Content |

|-------------|---------|---------|

| constant2   | 0x8110  |         |

| constant1   | 0x8114  |         |

| constant0   | 0x8118  |         |

| c_code      | 0x811C  |         |

| r_code      | 0x8120  |         |

| oui2        | 0x8124  | 0x00    |

| oui1        | 0x8128  | 0x40    |

| oui0        | 0x812C  | 0xE6    |

| vers        | 0x8130  |         |

| board2      | 0x8134  | 0x00    |

| board1      | 0x8138  | 0x05    |

| board0      | 0x813C  | 0xD7    |

| revis3      | 0x8140  |         |

| revis2      | 0x8144  |         |

| revis1      | 0x8148  |         |

| revis0      | 0x814C  |         |

| sernum1     | 0x8180  |         |

| sernum0     | 0x8184  |         |

These data are written into one Flash page; at Power ON the Flash content is loaded into the Configuration ROM.

# 4.2. Control Register

(Base Address + 0x8000, read/write, D16)

This register allows performing some general settings of the module.

Not used for VME FPGA Rev 0.0. Foreseen for future development

# 4.3. Status Register

(Base + 0x8002, read only, D16)

This register contains information on the status of the module.

Not used for VME FPGA Rev 0.0. Foreseen for future development

# 4.4. Interrupt Level Register

(Base Address + 0x8004, read/write, D16)

The 3 LSB of this register contain the value of the interrupt level (Bits 3 to 15 are meaningless). Default setting is 0x0. In this case interrupt generation is disabled. Not implemented in VME FPGA Rev 0.0. Available in next releases

Fig. 4.1: Interrupt Level Register

**NPO:** 00117/04:V1495.MUTx/05

**Filename:** V1495\_REV5.DOC

Number of pages: Page:

3

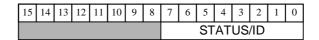

# 4.5.

Title:

(Base Address + 0x8006, read/write, D16)

**Interrupt Status-ID Register**

Mod. V1495 General Purpose VME Board

This register contains the STATUS/ID that the V1495 places on the VME data bus during the Interrupt Acknowledge cycle (Bits 8 to 15 are meaningless). Default setting is 0xDD. Not implemented in VME FPGA Rev 0.0. Available in next releases

Fig. 4.2: Interrupt Vector Register

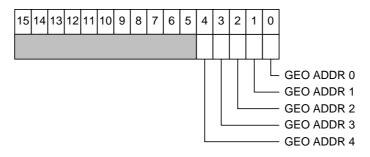

### 4.6. **GEO Address Register**

(Base Address + 0x8008, read, D16) The register content is the following:

Fig. 4.3: Geographical address register

This register allows readback of the level of GEO pins for the selected board. The register content is valid only for the VME64X board version. The register content for the VME64 version is 0x1F.

### 4.7. **Module Reset Register**

(Base Address + 0x800A write only, D16)

A dummy access to this register allows to generate a single shot RESET of the module.

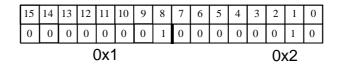

### 4.8. **Firmware Revision Register**

(Base Address + 0x800C, read only, D16)

This register contains the firmware revision number coded on 8 bit. For instance, the REV. 1.2 register content is:

Fig. 4.4: Firmware Revision Register

## 4.9. Scratch16 Register

Document type:

User's Manual (MUT)

(Base Address + 0x8018, D16, read/write)

This register allows to perform 16 bit test accesses for test purposes.

### 4.10. Scratch32 Register

(Base Address + 0x8020, D32, read/write)

This register allows to perform 32 bit test accesses for test purposes.

### 4.11. Select VME FPGA Flash Register

(Base Address + 0x800E, read/write, D16)

This register allows the VME FPGA configuration update (stored into on-board flash memory) via VMEBUS.

The configuration can be updated by the user by means of the V1495Upgrade software (developed and distributed by CAEN), see § 5.7.

### 4.12. Select USER FPGA Flash Register

(Base Address + 0x8012, read/write, D16)

This register allows USER FPGA configuration update (stored into on-board flash memory) via VMEBUS.

The configuration can be updated by the user by means of the V1495Upgrade software (developed and distributed by CAEN), see § 5.7.

# 4.13. VME FPGA Flash Memory

(Base Address + 0x8010, read/write, D16)

This register allows the VME FPGA configuration update (stored into on-board flash memory) via VMEBUS.

The configuration can be updated by the user by means of the V1495Upgrade software (developed and distributed by CAEN), see § 5.7.

# 4.14. USER FPGA Flash Memory

(Base Address + 0x8014, read/write, D16)

This register allows the USER FPGA configuration update (stored into on-board flash memory) via VMEBUS.

The configuration can be updated by the user by means of the V1495Upgrade software (developed and distributed by CAEN), see § 5.7.

**Document type:**

# 4.15. USER FPGA Configuration Register

(Base Address + 0x8016, read/write, D16)

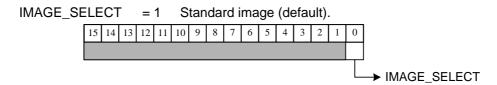

This register allows the update of the USER FPGA configuration. A write access to this register generates a configuration reload. The configuration image (Standard) will be uploaded into the USER FPGA as the IMAGE\_SELECT bit is set to 1:

Fig. 4.5: USER FPGA Configuration Register

# 5. V1495 USER FPGA Reference Design Kit

#### 5.1. Introduction

The CAEN V1495 board provides a user-customizable FPGA (called USER FPGA). The COIN\_REFERENCE reference design illustrates how to use the USER FPGA to implement a Coincidence Unit & I/O Register Unit. This design can be customised by the user in order to adapt its functionality to his own needs.

Fig. 5.1: USER FPGA block diagram

### 5.2. **Design Kit**

#### 5.2.1. V1495HAL

The V1495 Hardware Abstraction Layer (V1495HAL) is a HDL module provided, in Verilog format at netlist level, in order to help the hardware interfacing.

00117/04:V1495.MUTx/05

Filename: V1495\_REV5.DOC Number of pages:

#### COIN\_REFERENCE Design 5.2.2.

Title:

The COIN\_REFERENCE design VHDL entity is the interface to the V1495HAL. If the User wishes to use V1495HAL to develop his own application on the V1495 platform, the VHDL entity must not be modified: this means that signals names and function of the COIN\_REFERENCE entity must be used, as shown in the following table:

Table 5.1: COIN\_REFERENCE signals

| PORT NAME      | DIRECTION          | WIDTH                                | DESCRIPTION                         |  |  |  |  |  |

|----------------|--------------------|--------------------------------------|-------------------------------------|--|--|--|--|--|

| GLOBAL SIGNALS |                    |                                      |                                     |  |  |  |  |  |

| NLBRES         | IN                 | 1                                    | Async Reset (active low)            |  |  |  |  |  |

| LCLK           | IN                 | 1                                    | Local Bus Clock (40 MHz)            |  |  |  |  |  |

|                | REGISTER INTERFACE |                                      |                                     |  |  |  |  |  |

| REG_WREN       | IN                 | 1                                    | Write pulse (active high)           |  |  |  |  |  |

| REG_RDEN       | IN                 | 1                                    | Read pulse (active high)            |  |  |  |  |  |

| REG_ADDR       | IN                 | 16                                   | Register address                    |  |  |  |  |  |

| REG_DIN        | IN                 | 16                                   | Data from CAEN Local Bus            |  |  |  |  |  |

| REG_DOUT       | OUT                | 16                                   | Data to CAEN Local Bus              |  |  |  |  |  |

| USR_ACCESS     | IN                 | 1                                    | Current register access is          |  |  |  |  |  |

|                |                    |                                      | at user address space(Active high)  |  |  |  |  |  |

|                | V1495              | Front Panel Ports (PORT A,B,C,G) INT | TERFACE                             |  |  |  |  |  |

| A_DIN          | IN                 | 32                                   | In A (32 x LVDS/ECL)                |  |  |  |  |  |

| B_DIN          | IN                 | 32                                   | In B (32 x LVDS/ECL)                |  |  |  |  |  |

| C_DOUT         | OUT                | 32                                   | Out C (32 x LVDS)                   |  |  |  |  |  |

| G_LEV          | OUT                | 1                                    | Output Level Select (0=>TTL; 1=>    |  |  |  |  |  |

|                |                    |                                      | NIM)                                |  |  |  |  |  |

| G_DIR          | OUT                | 1                                    | Output Enable (0=>Output, 1=>Input) |  |  |  |  |  |

| G_DOUT         | OUT                | 2                                    | Out G - LEMO (2 x NIM/TTL)          |  |  |  |  |  |

| G_DIN          | IN                 | 2                                    | In G – LEMO (2 x NIM/TTL)           |  |  |  |  |  |

|                | V1495 Mez          | zanine Expansion Ports (PORT D,E,F)  | INTERFACE                           |  |  |  |  |  |

| D_IDCODE       | IN                 | 3                                    | D slot mezzanine Identifier         |  |  |  |  |  |

| D_LEV          | OUT                | 1                                    | D slot Port Signal Level Select     |  |  |  |  |  |

|                |                    |                                      | (the level selection depends on the |  |  |  |  |  |

|                |                    |                                      | mezzanine expansioon board mounted  |  |  |  |  |  |

|                |                    |                                      | onto this port)                     |  |  |  |  |  |

| D_DIR          | OUT                | 1                                    | D slot Port Direction               |  |  |  |  |  |

| D_DIN          | IN                 | 32                                   | D slot Data In Bus                  |  |  |  |  |  |

| D_DOUT         | OUT                | 32                                   | D slot Data Out Bus                 |  |  |  |  |  |

| PORT NAME     | DIRECTION | WIDTH                       | DESCRIPTION                         |  |

|---------------|-----------|-----------------------------|-------------------------------------|--|

| E_IDCODE      | IN        | 3                           | E slot mezzanine Identifier         |  |

| E_LEV         | OUT       | 1                           | E slot Port Signal Level Select     |  |

|               |           |                             | (the level selection depends on the |  |

|               |           |                             | mezzanine expansioon board mounted  |  |

|               |           |                             | onto this port)                     |  |

| E_DIR         | OUT       | 1                           | E slot Port Direction               |  |

| E_DIN         | IN        | 32                          | E slot Data In Bus                  |  |

| E_DOUT        | OUT       | 32                          | E slot Data Out Bus                 |  |

| F_IDCODE      | IN        | 3                           | F slot mezzanine Identifier         |  |

| F_LEV         | OUT       | 1                           | F slot Port Signal Level Select     |  |

|               |           |                             | (the level selection depends on the |  |

|               |           |                             | mezzanine expansioon board mounted  |  |

|               |           |                             | onto this port)                     |  |

| F_DIR         | OUT       | 1                           | F slot Port Direction               |  |

| F_DIN         | IN        | 32                          | F slot Data In Bus                  |  |

| F_DOUT OUT 32 |           | F slot Data Out Bus         |                                     |  |

|               | 1         | PDL CONFIGURATION INTERFAC  | E                                   |  |

| PDL_WR        | OUT       | 1                           | Write Enable                        |  |

| PDL_SEL       | OUT       | 1                           | PDL Selection (0=>PDL0, 1=>PDL1)    |  |

| PDL_READ      | IN        | 8                           | Read Data                           |  |

| PDL_WRITE     | OUT       | 8                           | Write Data                          |  |

| PDL_DIR       | OUT       | 1                           | Direction (0=>Write, 1=>Read)       |  |

|               | ]         | DELAY LINES AND OSCILLATORS | 1/0                                 |  |

| PDL0_OUT      | IN        | 1                           | Signal from PDL0 Output             |  |

| PDL1_OUT      | IN        | 1                           | Signal from PDL1 Output             |  |

| DLO0_OUT      | IN        | 1                           | Signal from DLO0 Output             |  |

| DLO1_OUT      | IN        | 1                           | Signal from DLO1 Output             |  |

| PDL0_IN       | OUT       | 1                           | Signal to PDL0                      |  |

| PDL1_IN       | OUT       | 1                           | Signal to PDL1 Input                |  |

| DLO0_GATE     | OUT       | 1                           | Signal to DLO0 Input                |  |

| DLO1_GATE     | OUT       | 1                           | Signal to DLO1 Input                |  |

|               |           | SPARE INTERFACE             | _                                   |  |

| SPARE_OUT     | OUT       | 12                          | SPARE Data Out                      |  |

| SPARE_IN      | IN        | 12                          | SPARE Data In                       |  |

| PORT NAME   | DIRECTION | WIDTH         | DESCRIPTION                   |

|-------------|-----------|---------------|-------------------------------|

| SPARE_DIR   | OUT       | 1             | SPARE Direction               |

|             |           | LED INTERFACE |                               |

| RED_PULSE   | OUT       | 1             | RED Led Pulse (active high)   |

| GREEN PULSE | OUT       | 1             | GREEN Led Pulse (active high) |

### 5.3. Interface description

#### 5.3.1. Global Signals

The nLBRES must be used as an asynchronous reset signal by the user. An active low pulse will be generated when a write is done at the Module Reset register address (see

The LBCLK is a 40 MHz clock. It is the FPGA main clock.

#### 5.3.2. REGISTER INTERFACE

The signals of the Register Interface allows to read/write into the USER FPGA registers, which can be accessed via VMEbus. The COIN\_REFERENCE module shows how to implement a set of registers.

The following table shows the registers map as it is provided. Each register address is coded via constants in V1495pkg.vhd file. This file allows to modify the registers map; all registers allow D16 accesses (write only, read only or read/write). Registers default value is the value after a reset for write only and read/write registers; read only registers return the status of the signals read by the FPGA and have no default value.

The Register Interface allows to abstract the VME registers access. The User can access a simple register interface: two signals (REG\_WREN e REG\_RDEN) are pulses with a one clock cycle duration which enables respectively a write or a read access to a register. REG\_ADDR signal represents the register address.

### Writing into a register:

In case of a write operation into a register via VME, the 16 bit datum is available through the REG\_DIN signal. The datum is guaranteed stable on the CLK leading edge where REG\_WREN is active. The register access is valid only when USR\_ACCESS is at logic level = 1.

### Reading from a register:

In case of a read operation from a register via VME, the datum to be returned must drive the REG\_DOUT and be stable on the CLK leading edge, where REG\_RDEN is active. The register access is valid only when USR\_ACCESS is at logic level = 1.

Title:

#### 5.3.3. V1495 Front Panel Ports (PORT A,B,C,G) INTERFACE

These signals allows to handle the interface with the motherboard ports A, B, C, G. A\_DIN and B\_DIN signals show the logic level of A and B ports (32 bit, input only). The output logic level on port C can be set via C\_DOUT signal.

The logic level on port G (LEMO connectors) can be set via G\_LEV signal; the direction via G\_DIR, the datum to be written via G\_DOUT or to be read via G\_DIN.

#### 5.3.4. V1495 Mezzanine Expansion Ports (PORT D,E,F) INTERFACE

These signals allows to handle the interface with the piggy back board ports D, E, F. The following table explains the available signals:

Table 5.2: V1495 Mezzanine Expansion Ports signals

| Port: | Signal:   | Function:                                 | Applies to:          |

|-------|-----------|-------------------------------------------|----------------------|

| D     | D_DIR     | Selects direction                         | Bidirectional port   |

|       | D_DIN     | Read the logic level                      | Input/Bidirectional  |

|       | D_DOUT    | Set the logic level                       | Output/Bidirectional |

|       | D_ IDCODE | Read IDCODE for piggy back identification | All                  |

|       | D_LEV     | Set the logic level                       | Output/Bidirectional |

| E     | E_DIR     | Selects direction                         | Bidirectional port   |

|       | E_DIN     | Read the logic level                      | Input/Bidirectional  |

|       | E_DOUT    | Set the logic level                       | Output/Bidirectional |

|       | E_IDCODE  | Read IDCODE for piggy back identification | All                  |

|       | E_LEV     | Set the logic level                       | Output/Bidirectional |

| F     | F_DIR     | Selects direction                         | Bidirectional port   |

|       | F_DIN     | Read the logic level                      | Input/Bidirectional  |

|       | F_DOUT    | Set the logic level                       | Output/Bidirectional |

|       | F_ IDCODE | Read IDCODE for piggy back identification | All                  |

|       | F_LEV     | Set the logic level                       | Output/Bidirectional |

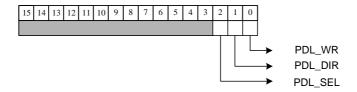

#### 5.3.5. PDL Configuration Interface

PDL Configuration Interface signals are as follows:

**Table 5.3: PDL Configuration Interface signals**

| PDL WR    | OUT | 1 | Write Enable                     |

|-----------|-----|---|----------------------------------|

| _         |     |   |                                  |

| PDL_SEL   | OUT | 1 | PDL Selection (0=>PDL0, 1=>PDL1) |

| PDL_READ  | IN  | 8 | Read Data                        |

| PDL_WRITE | OUT | 8 | Write Data                       |

| PDL_DIR   | OUT | 1 | Direction (0=>Write, 1=>Read)    |

### 5.3.6. Delay Lines and Oscillators I/O

Delay Lines and Oscillators signals are as follows (see also § 5.5.5 and § 5.5.6):

Table 5.4: Delay Lines and Oscillators signals

| PDL0_OUT  | IN  | 1 | Signal from PDL0 Output |

|-----------|-----|---|-------------------------|

| PDL1_OUT  | IN  | 1 | Signal from PDL1 Output |

| DLO0_OUT  | IN  | 1 | Signal from DLO0 Output |

| DLO1_OUT  | IN  | 1 | Signal from DLO1 Output |

| PDL0_IN   | OUT | 1 | Signal to PDL0          |

| PDL1_IN   | OUT | 1 | Signal to PDL1 Input    |

| DLO0_GATE | OUT | 1 | Signal to DLO0 Input    |

| DLO1_GATE | OUT | 1 | Signal to DLO1 Input    |

### 5.3.7. SPARE Interface

These signals allow to set and read the status of SPARE pin present on the board.

**Table 5.5: SPARE Interface signals**

| SPARE OUT  | OUT | 12 | SPARE Data Out  |

|------------|-----|----|-----------------|

| SI AKE_OUT | 001 | 12 | SI ARE Data Out |

| SPARE_IN   | IN  | 12 | SPARE Data In   |

| SPARE_DIR  | OUT | 1  | SPARE Direction |

### 5.3.8. LED Interface

These signals, when active for one clock cycle, allow to generate a blink of the relevant Led.

**Table 5.6: LED Interface signals**

| RED_PULSE   | OUT | 1 | RED Led Pulse (active high)   |

|-------------|-----|---|-------------------------------|

|             |     |   |                               |

| GREEN_PULSE | OUT | 1 | GREEN Led Pulse (active high) |

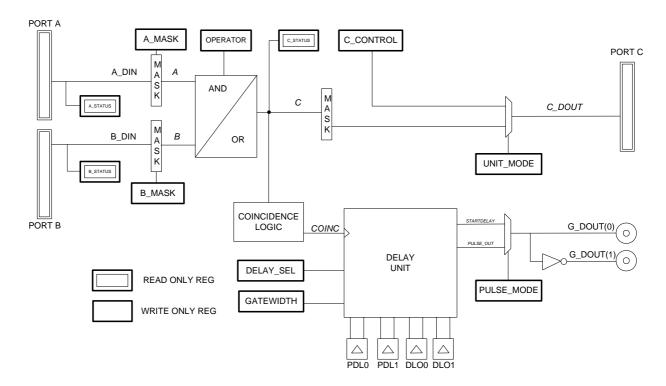

# 5.4. Reference design description

The reference design preloaded into the USER FPGA is given as a design guide. It is a full functional application of the usage of the board as a concidence and/or I/O register unit. This reference design give access to A,B,C,G ports. So no mezzanine expansion cards are needed in order to use this design.

The MODE register can be used to set the preferred operating mode. When the board is switched on, the default operating mode is I/O Register mode.

In I/O Register Mode, C port is directly driven by the C\_CONTROL register. The coincidence is anyway still active so that a pulse in generated on G port when a coincidence event is detected.

In Coincidence Mode, the C port is used to report the coincidence operator on A and B port. In this case the C port can be masked through a mask register (C\_MASK).

A gate pulse is generated on G port when data patterns on input ports A and B satisfy a trigger condition.

The trigger condition implemented in this reference design is true when a bit-per-bit logic operation on port A and B

is true. The logic operator applied to Port A and B is selectable by means of a register bit (MODE Register Bit 4).

If MODE bit 4 is set to '0', an AND logic operation is applied to corresponding bits in Port A and B (i.e. A(0) AND B(0), A(1) AND B(1) etc.).

In this case, a trigger is generated if corresponding A and B port bits are '1' at the same time

If MODE bit 4 is set to '1', an OR logic operation is applied to corresponding bits in Port A and B (i.e. A(0) OR B(0), A(1) OR B(1) etc.).

In this case, a trigger is generated if there is a '1' on one bit of either port A or B.

Port A and B bits can be singularly masked through a register, so that a '1' on that bit doesn't generate any trigger.

Expansion mezzanine cards can be directly controlled through registers already implemented in this design.

The expansion mezzanine is identified by a unique identification code that can be read through a register.

Fig. 5.2: Front Panel Ports Interface Diagram

The following table illustrates the the register map of the USER FPGA reference design (COIN\_REFERENCE).

NPO:

Filename:

Number of pages:

Page:

00117/04:V1495.MUTx/05

V1495\_REV5.DOC

43

28

### Table 5.7: COIN\_REFERENCE register map

| ADDRESS | DATA SIZING                                                                    | ACCESS                                                                                                                                                                                                                                                                                              | NOTES                                                                                                                                                                                                                                                                                                                                                                                                                                         | DEFAULT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0000  | D16                                                                            | RO                                                                                                                                                                                                                                                                                                  | Port A status. This register reflects                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         |                                                                                |                                                                                                                                                                                                                                                                                                     | A[15:0] bit status.                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0x0002  | D16                                                                            | RO                                                                                                                                                                                                                                                                                                  | Port A status. This register reflects                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         |                                                                                |                                                                                                                                                                                                                                                                                                     | A[31:16] bit status.                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0x0004  | D16                                                                            | RO                                                                                                                                                                                                                                                                                                  | Port B status. This register reflects                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         |                                                                                |                                                                                                                                                                                                                                                                                                     | B[15:0] bit status.                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0x0006  | D16                                                                            | RO                                                                                                                                                                                                                                                                                                  | Port B status. This register reflects                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         |                                                                                |                                                                                                                                                                                                                                                                                                     | B[31:16] bit status.                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0x0008  | D16                                                                            | RO                                                                                                                                                                                                                                                                                                  | Port C status. This register reflects                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         |                                                                                |                                                                                                                                                                                                                                                                                                     | C[15:0] bit status.                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0x000A  | D16                                                                            | RO                                                                                                                                                                                                                                                                                                  | Port C status. This register reflects                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |